AD7747数据手册

Optoma奥图码EP774说明书

目录 (1)用法注意 (3)介绍 (6)产品包装清单 (6)投影仪外观 (7)遥控 (13)遥控器操作范围 (15)投影仪和遥控器按钮 (15)装入遥控器电池 (16)安装与操作 (17)连接输入设备 (17)启动和关闭投影仪 (19)设置访问密码(安全锁) (21)调节投影仪高度 (23)调节缩放、焦距和梯形校正 (24)调节音量 (24)屏幕显示菜单控件 (25)设置OSD语言 (26)菜单设置 (27)OSD菜单要览 (27)图像菜单 (28)菜单显示 (30)设置菜单 (32)颜色设置菜单 (36)语言菜单 (37)管理菜单 (38)附录 (40)更换投影灯 (40)重新设置投影灯 (43)清洁投影仪 (44)使用Kensington®锁 (44)常见问题和解决方案 (45)有关故障排除的提示 (45)LED 错误消息 (46)图像问题 (47)投影灯问题 (47)遥控器问题 (48)音频问题 (48)对投影仪进行维修 (49)规格 (50)投影距离和投影大小 (50)时钟模式表 (51)投影仪尺寸 (52)法规 (53)FCC警告 (53)加拿大 (53)安全认证 (53)EN 55022警告 (53)符合RoHS (53)祝贺并感谢您选用Optoma DLP投影仪。

重要说明:强烈建议您在使用投影仪之前仔细阅读本章。

这些安全和使用说明可确保您常年都能安全地使用投影仪。

请保留此手册,以供将来参考。

注意设备和手册中使用的警告符号用于警告您注意危险情况。

本手册中使用的下列文本框用于提醒您注意重要信息。

注意:提供有关当前主题的其他信息。

重要说明:提供不应忽视的其他信息。

告诫:提醒您注意可能会损坏设备的情况。

警告:提醒您注意可能会损坏设备、造成危险或引起人身伤害的情况。

整本手册中,部件名和OSD菜单中的项目都用粗体表示,如下例所示:“按遥控器上的菜单按钮打开OSD。

”遥控器有些遥控器具有一个用于指示屏幕上项目的激光器。

毕业设计说明书 模数转换器AD7718

前言近几年来,计算机技术和微电子技术得到了飞速的发展,在本文中,讲述了在智能仪器板上应用24位A/D转换器AD7718。

主要功能是进行数据的采集,数据采集系统是计算机向外部模拟世界采集数据必经的途径,有时也叫预处理系统。

在智能仪器中,把被检测对象的信号送入微处理器中进行处理,或者将微处理器中的控制信号输出,对受控对象进行控制,被测量的信号要经过多次的变换或反变换,每次变换都具有一定的目的。

传感器是被测信号的第一次变换,它是将非电量信号变换成电信号。

为了将它输入到微机中进行实时处理,需要再进行滤波、放大,变换成标准的电信号送给A/D转换器进行二次变换,模拟的电信号被转换成数字量送入微型机中,以便对其进一步的处理。

在将传感器信号输入微处理器的过程中,或从微处理器输出控制信号时,必须对信号的特征量及其大小、系统的关键性指标、成本允许范围等作出全面的综合考虑。

在设计中ADC用的是AD7718,它是一个24位的A/D转换器,转换的速度可以控制,一般在100ms的时候最佳。

在文章中详细讲述了AD7718的内部结构和它的一些寄存器。

并对实验结果进行分析。

第一章、总体设计方案这次的设计是在“智能仪器板”上应用A/D转换器。

下面就以两中不同分辨率的ADC进行比较。

一个是12位的AD574A,另一个是24位的AD7718。

经过比较后可以得知他们的不同特点。

1、设计方案一:使用AD574A为主要元器件。

AD574A为一完善的中档、中速ADC,按逐次逼近式工作,最大转换时间为35s 。

备有4位三段三态门输出,可以在宽的温度范围内保持线形并不丢码,内有高稳定度时钟及齐纳二极管稳定电源,采用28脚塑料或陶瓷双列直插式封装,功耗低。

看下图说明采用+5V及+15V电源供电。

本片的失调调节和双极性零点偏移是通过改变注入DAC的参考电流来完成。

图1-1 AD574A的结构图AD574A的数字部分主要包括控制逻辑,时钟、SAR及三态门输出等部分。

低功耗24位模数转换器AD7787

低功耗 24 位模数转换器 AD7787 1 概述 7787 是公司推出的适用于低频测量的低功耗、低噪声、双通道、 24 位 Σ-Δ 模数转换器。

它利用片内时钟电路工作,因而无需用户提供时钟源。

7787 的数据输出速率可由软件设置,这一特性使其转换速率可在 95——120 之间变化。

该芯片采用 10 脚封装,非常适合用需要高分辨率、低功耗的便携式 仪器、温度测量、传感器测量、称重仪等。

7787 的主要特点如下 ●可在 25——525 电压范围内工作。

正常模式下的最大工作电流为 75μ,掉电模式下为 1μ; ●95 转换速率下的噪声为 11μ;范文先生网收集整理 ●22 位有效分辨率时的峰峰值分辨率为 195 位; ●内部非线性度 35; ●具有 50 和 60 同步抑制功能; ●具有内部时钟振荡器和监控通道; ●内含轨至轨输入缓冲器; ●带有三线制串行接口,与、、及兼容;●工作温度范围为-40——+105℃。

2 引脚排列及功能 7787 的引脚排列如图 1 所示。

3 工作原理 7787 的内部结构功能框图如图 2 所示。

它内部集成了一个 Σ-Δ 调制器、一个缓冲器和一个片内数字滤波器。

数字滤波器的主要功能是提供正常模式抑制。

在 166 默认转换速率条件下,它能提供 50 和 60 的同步抑制。

7787 采用内部时钟电路工作,因而无需外接时钟源。

时钟频率以 2、4、8 因子分频后应用于调制器和滤波器,从而可降低 芯片的功耗。

当采用 5 单电源供电、缓冲器使能且时钟以最大速率工作时,7787 的功耗电流最大仅为 160μ 7787 有 5 个片内寄存器通信寄存器、状态寄存器、模式寄存器、滤波 器寄存器和数据寄存器。

所有对 7787 的设置和控制都是通过这些寄存器来实现的。

7787 具有三种工作模式,分别为单转换模式、连续转换模式和连续模 式。

31 单转换模式 单转换模式时的转换时序如图 3 所示。

电子论文-eAD7745的微电容加速度计测量电路设计与实现

四层,中间两层分别为完整的地、电源平面,数字电 源/地平面和模拟电源/地平面是分开的。

图5加速度计电路电源、地连接示意 由于加速度计电路在加速度测试时会不断振 动,所有的跳线必须非常稳固。跳线开关可能不太 适用,本文采用0fl电阻来连接所有的跳线。其中, 数字地平面和模拟地平面由一个oQ电阻单点相连 以实现星型接地。另外一个oQ可选电阻可用于数 字电源和模拟电源的连接,方便提供三种供电模式。 2.2旁路和滤波 本文的电路中,稳压直流电源旁采用了100弘F 的解耦电容,其他每个有源器件旁都接上了芯片数 据手册中推荐大小的解耦电容。模拟电源经过1【型 低通滤波器滤波,其中的电感值和电容值分别为0.5 pH和1 pF。 AD7745的两根串行通讯接口线上串接可选滤 波电阻,该滤波电阻可降低串行通讯接口线上的瞬 时电流。另外,每个模拟器件的电源引脚上也都串 联了一个可选滤波电阻。 2.3器件布局和布板 为了最小化器件间的共阻抗耦合,大模拟信号 (例如驱动电动机的电流、电压信号)必须和小模拟 信号(例如运放上的或A/D输入端上的信号)隔开, 这两者都必须远离数字信号。 布板时首先要考虑的就是器件的布局。本文电 路中的器件分为两大类:数字器件类,包括微控制器 89C51和max232串口;小信号模拟器件类,包括 D/A参考电压芯片ADR392,AD7745和D/A。如 图6所示,模拟器件类放置在最右边;数字器件类中 的晶振和max232串口频率最高,最可能产生传导 和辐射噪声,因此最靠近电路板上的接插件放置。 其中,红色的大块面积是地平面,用于为嘈杂或易受 干扰的电路部分提供法拉第屏蔽:包括两个电源、晶 振及模拟电路部分。 布板时其次要考虑的问题是电源和地策略,每 种器件类的电源及电流返回路径最好分开,以减小 共阻抗耦合。

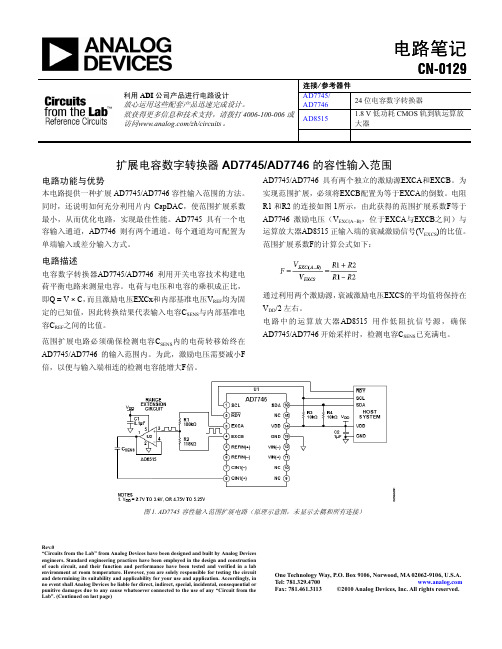

如图1,AD7745核心由一个二阶(}△或电荷平衡) 调制器和一个三阶数字滤波器组成,该芯片既可以 测电容,也可以当作普通A/D使用。它上面还集成 了一个多路复用器,一个振荡源(方波发生器)和两 个CAPDAC;以及一个温度传感器,一个电压基准、 一个时钟发生器;还有控制校准逻辑单元和IzC串 行接口。

AD7747ARUZ资料

24-Bit Capacitance-to-Digital Converterwith Temperature SensorAD7747Rev. 0Information furnished by Analog Devices is believed to be accurate and reliable. However , no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners.One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781.329.4700 Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.FEATURESCapacitance-to-digital converterNew standard in single chip solutionsInterfaces to single or differential grounded sensors Resolution down to 20 aF (that is, up to 19.5-bit ENOB) Accuracy: 10 fF Linearity: 0.01%Common-mode (not changing) capacitance up to 17 pF Full-scale (changing) capacitance range ±8 pF Update rate: 5 Hz to 45 HzSimultaneous 50 Hz and 60 Hz rejection at 8.1 Hz update Active shield for shielding sensor connection Temperature sensor on-chipResolution: 0.1°C, accuracy: ±2°C Voltage input channel Internal clock oscillator2-wire serial interface (I 2C® compatible) Power2.7 V to 5.25 V single-supply operation 0.7 mA current consumptionOperating temperature: −40°C to +125°C 16-lead TSSOP packageAPPLICATIONSAutomotive, industrial, and medical systems for Pressure measurement Position sensing Proximity sensing Level sensing Flow metering Impurity detectionGENERAL DESCRIPTIONThe AD7747 is a high-resolution, Σ-Δ capacitance-to-digital converter (CDC). The capacitance to be measured is connected directly to the device inputs. The architecture features inherent high resolution (24-bit no missing codes, up to 19.5-bit effective resolution), high linearity (±0.01%), and high accuracy (±10 fF factory calibrated). The AD7747 capacitance input range is ±8 pF (changing), and it can accept up to 17 pF common-mode capacitance (not changing), which can be balanced by a program-mable on-chip digital-to-capacitance converter (CAPDAC). The AD7747 is designed for single-ended or differential capacitive sensors with one plate connected to ground. For floating (not grounded) capacitive sensors, the AD7745 or AD7746 are recommended.The part has an on-chip temperature sensor with a resolution of 0.1°C and accuracy of ±2°C. The on-chip voltage reference and the on-chip clock generator eliminate the need for any external components in capacitive sensor applications. The part has a standard voltage input that, together with the differential reference input, allows easy interface to an external temperature sensor, such as an RTD, thermistor, or diode.The AD7747 has a 2-wire, I 2C-compatible serial interface. The part can operate with a single power supply of 2.7 V to 5.25 V . It is specified over the automotive temperature range of −40°C to +125°C and is housed in a 16-lead TSSOP package.FUNCTIONAL BLOCK DIAGRAMVDDCIN1(+)SDA SCLRDYCIN1(–)05469-001Figure 1.AD7747Rev. 0 | Page 2 of 28TABLE OF CONTENTSFeatures..............................................................................................1 Applications.......................................................................................1 General Description.........................................................................1 Functional Block Diagram..............................................................1 Revision History...............................................................................2 Specifications.....................................................................................3 Timing Specifications..................................................................5 Absolute Maximum Ratings............................................................6 ESD Caution..................................................................................6 Pin Configuration and Function Descriptions.............................7 Typical Performance Characteristics.............................................8 Output Noise and Resolution Specifications..............................11 Serial Interface................................................................................12 Read Operation...........................................................................12 Write Operation..........................................................................12 AD7747 Reset..............................................................................13 General Call.................................................................................13 Register Descriptions.....................................................................14 Status Register.............................................................................15 Cap Data Register.......................................................................15 VT Data Register........................................................................15 Cap Setup Register.....................................................................16 VT Setup Register.......................................................................16 EXC Setup Register....................................................................17 Configuration Register..............................................................18 Cap DAC A Register..................................................................19 Cap DAC B Register...................................................................19 Cap Offset Calibration Register...............................................20 Cap Gain Calibration Register..................................................20 Volt Gain Calibration Register.................................................20 Circuit Description.........................................................................21 Overview.....................................................................................21 Capacitance-to-Digital Converter............................................21 Active AC Shield Concept.........................................................21 CAPDAC.....................................................................................21 Single-Ended Capacitive Configuration.................................22 Differential Capacitive Configuration.....................................22 Parasitic Capacitance.................................................................23 Parasitic Resistance....................................................................23 Parasitic Serial Resistance.........................................................23 Capacitive Gain Calibration.....................................................23 Capacitive System Offset Calibration......................................24 Internal Temperature Sensor....................................................24 External Temperature Sensor...................................................24 Voltage Input...............................................................................25 V DD Monitor................................................................................25 Typical Application Diagram....................................................26 Outline Dimensions.......................................................................27 Ordering Guide.. (27)REVISION HISTORY1/07—Revision 0: Initial VersionAD7747Rev. 0 | Page 3 of 28SPECIFICATIONSV DD = 2.7 V to 3.6 V or 4.75 V to 5.25 V; GND = 0 V; EXC = ±V DD × 3/8; −40°C to +125°C, unless otherwise noted. Table 1.Parameter Min Typ Max Unit Test Conditions/Comments CAPAC I T I VE I NPUT Conversion Input Range ±8.192 pF 1 Factory calibrated Integral Nonlinearity (INL)2 ±0.01 % of FSR 1No Missing Codes 224 Bit Conversion time ≥ 124 ms Resolution, p-p 16.5 Bit Conversion time 124 ms, see Table 5 Resolution Effective 19.1 Bit Conversion time 124 ms, see Table 5 Output Noise, rms 11.0 aF/√Hz Conversion time 124 ms, see Table 5 Absolute Error 3 ±10 fF 1 25°C, V DD = 5 V, after offset calibrationOffset Error 4, 5 32 aF 1After system offset calibration,excluding effect of noise 4System Offset Calibration Range 5 ±1 pFOffset Deviation over Temperature 20.4 fF See Figure 6Gain Error 6 0.02 0.11 % of FS 125°C, V DD = 5 V Gain Drift vs. Temperature 2 −23 −26 −29 ppm of FS/°CPower Supply Rejection 20.5 4 fF/V Normal Mode Rejection 5 72 dB 50 Hz ± 1%, conversion time 124 ms 60 dB 60 Hz ± 1%, conversion time 124 ms CAPDAC Full Range 17 21 pF 6-bit CAPDAC Differential Nonlinearity (DNL) 0.3 LSB See Figure 16 Drift vs. Temperature 2 26 ppm of FS/°CEXCITATIONFrequency 16 kHzAC Voltage Across Capacitance ±V DD × 3/8 V To be configured via digital interface Average DC Voltage Across Capacitance V DD /2 V TEMPERATURE SENSOR 7 V REF internal Resolution 0.1 °CError 2±0.5 ±2 °C Internal temperature sensor ±2 °C External sensing diode 8 VOLTAGE INPUT 7 V REF internal or V REF = 2.5 V Differential VIN Voltage Range ±V REF V Absolute VIN Voltage 2 GND − 0.03 V DD + 0.03 V Integral Nonlinearity (INL) ±3 ±15 ppm of FS No Missing Codes 2 24 Bit Conversion time = 122.1 ms Resolution, p-p 16 Bits Conversion time = 62 ms,see Table 6 and Table 7Output Noise 3 μV rms Conversion time = 62 ms,see Table 6 and Table 7Offset Error ±3 μV Offset Drift vs. Temperature 15 nV/°CFull-Scale Error 2, 90.025 0.1 % of FS Full-Scale Drift vs. Temperature 5 ppm of FS/°C Internal reference 0.5 ppm of FS/°C External reference Average VIN Input Current 300 nA/V Analog VIN Input Current Drift ±50 pA/V/°C Power Supply Rejection 80 dB Internal reference, V IN = V REF /2 90 dB External reference, V IN = V REF /2AD77471 Capacitance units: 1 pF = 10−12 F; 1 fF = 10−15 F; 1 aF = 10−18 F. Full scale (FS) = 8.192 pF; full-scale range (FSR) = ±8.192 pF.2 Specification is not production tested, but is supported by characterization data at initial product release.3 Factory calibrated. The absolute error includes factory gain calibration error, integral nonlinearity error, and offset error after system offset calibration, all at 25°C.At different temperatures, compensation for gain drift over temperature is required.4 The capacitive input offset can be eliminated using a system offset calibration. The accuracy of the system offset calibration is limited by the offset calibration register LSB size (32 aF) or by converter + system p-p noise during the system capacitive offset calibration, whichever is greater. To minimize the effect of the converter + system noise, longer conversion times should be used for system capacitive offset calibration. The system capacitance offset calibration range is ±1 pF; the larger offset can be removed using CAPDACs.5 Specification is not production tested, but guaranteed by design.6 The gain error is factory calibrated at 25°C. At different temperatures, compensation for gain drift over temperature is required.7 The VTCHOP bit in the VT SETUP register must be set to 1 for the specified temperature sensor and voltage input performance.8 Using an external temperature sensing diode 2N3906, with nonideality factor n f = 1.008, connected as in Figure 37, with total serial resistance <100 Ω.9 Full-scale error applies to both positive and negative full scale.Rev. 0 | Page 4 of 28AD7747Rev. 0 | Page 5 of 28TIMING SPECIFICATIONSV DD = 2.7 V to 3.6 V , or 4.75 V to 5.25 V; GND = 0 V; Input Logic 0 = 0 V; Input Logic 1 = V DD ; −40°C to +125°C, unless otherwise noted. Table 2.Parameter Min Typ Max Unit Test Conditions/Comments SERIAL INTERFACE 1, 2 See Figure 2 SCL Frequency 0 400 kHz SCL High Pulse Width, t HIGH 0.6 μs SCL Low Pulse Width, t LOW 1.3 μs SCL, SDA Rise Time, t R 0.3 μs SCL, SDA Fall Time, t F 0.3 μs Hold Time (Start Condition), t HD;STA 0.6 μs After this period, the first clock is generated Setup Time (Start Condition), t SU;STA 0.6 μs Relevant for repeated start condition Data Setup Time, t SU;DAT0.1 μs Setup Time (Stop Condition), t SU;STO 0.6 μs Data Hold Time, t HD;DAT (Master) 0 μs Bus-Free Time (Between Stop and Start Condition, t BUF ) 1.3 μs1 Sample tested during initial release to ensure compliance.2All input signals are specified with input rise/fall times = 3 ns, measured between the 10% and 90% points. Timing reference points at 50% for inputs and outputs. Output load = 10 pF.Figure 2. Serial Interface Timing DiagramAD7747Rev. 0 | Page 6 of 28ABSOLUTE MAXIMUM RATINGST A = 25°C, unless otherwise noted. Table 3.Parameter RatingPositive Supply Voltage V DD to GND −0.3 V to +6.5 VVoltage on any Input or Output Pin to GND−0.3 V to V DD + 0.3 V ESD Rating (ESD Association Human Body Model, S5.1)2000 VOperating Temperature Range −40°C to +125°CStorage Temperature Range −65°C to +150°CJunction Temperature 150°C TSSOP Package θJA(Thermal Impedance-to-Air)128°C/W TSSOP Package θJC(Thermal Impedance-to-Case) 14°C/W Peak Reflow Soldering Temperature Pb Free (20 sec to 40 sec) 260°C Stresses above those listed under Absolute Maximum Ratingsmay cause permanent damage to the device. This is a stressrating only and functional operation of the device at these orany other conditions above those indicated in the operationalsection of this specification is not implied. Exposure to absolutemaximum rating conditions for extended periods may affect device reliability. ESD CAUTIONAD7747Rev. 0 | Page 7 of 28PIN CONFIGURATION AND FUNCTION DESCRIPTIONS05469-003SDA NC VDDGNDVIN(–)VIN(+)NCNCNC = NO CONNECTFigure 3. Pin ConfigurationIAD7747Rev. 0 | Page 8 of 28TYPICAL PERFORMANCE CHARACTERISTICS80–80–8–7–6–5–4–3–1–2805469-004INPUT CAPACITANCE (pF)I N L (p pm )6040200–20–40–6001234567 Figure 4. Capacitance Input Integral Nonlinearity;V DD = 5 V, CAPDAC = 0x3F2000–3000–5015005469-005TEMPERATURE (ºC)G A I N E R R O R (p p m )10000–1000–2000–250255075100125 Figure 5. Capacitance Input Gain Drift vs. Temperature;V DD = 5 V, CIN(+) to GND = 8 pF.20–0.30–5015005469-006TEMPERATURE (ºC)O F F S E T E R R O R (f F )–250255075100125.15.10.050–0.05–0.10–0.15–0.20–0.25Figure 6. Capacitance Input Offset Drift vs. Temperature;V DD = 5 V, CIN(+) Open 10–5060050005469-007CAPACITANCE SHLD TO GND (pF)C A P E R R O R (f F )–20–10–30–4050100150200250300350400450550Figure 7. Capacitance Input Error vs. Capacitance Between SHLD and GND;CIN(+) to GND = 8 pF, V DD = 2.7 V, 3 V, 3.3 V, and 5 V10–5060050005469-008CAPACITANCE SHLD TO GND (pF)C A P E R R O R (f F )–20–10–30–4050100150200250300350400450550Figure 8. Capacitance Input Error vs. Capacitance Between SHLD and GND;CIN(+) to GND = 25 pF, V DD = 2.7 V, 3 V, 3.3 V, and 5 V10–5060050005469-009CAPACITANCE CIN TO SHLD (pF)C A P E R R O R (f F )–20–10–30–4050100150200250300350400450550Figure 9. Capacitance Input Error vs. Capacitance Between CIN(+) and SHLD;CIN(+) to GND = 8 pF, V DD = 2.7 V, 3 V, 3.3 V, and 5VAD7747Rev. 0 | Page 9 of 28150–15001k 05469-010PARALLEL RESISTANCE (M Ω)C A P E R R O R (f F )1010010050–50–100Figure 10. Capacitance Input Error vs. Parallel Resistance;CIN(+) to GND = 8 pF, V DD = 5 V0–100020005469-058CIN TO SHLD RESISTANCE (k Ω)C A P E R R O R (f F )–100–200–300–400–500–600–700–800–900255075100125150175Figure 11. Capacitance Input Error vs. Resistance Between CIN1(+) and SHLD;CIN(+) to GND = 8 pF, V DD = 5 V100–10000.09105469-059CIN TO SHLD RESISTANCE (M Ω)C A P E R R O R (f F )–1000–200–300–400–500–600–700–800–9000.270.480.96525100Figure 12. Capacitance Input Error vs. Resistance Between CIN(+) and SHLD;CIN(+) to GND = 25 pF, V DD = 5 V 1.0–1.00.0110005469-066SHLD TO GND RESISTANCE (M Ω)C A P E R R O R (p F )0.11.010.00.80.60.40.20–0.2–0.4–0.6–0.8Figure 13. Capacitance Input Error vs. Resistance Between SHLD and GND;CIN(+) to GND = 8 pF; V DD = 5 V10–100110005469-067SERIAL RESISTANCE (k Ω)C A P E R R O R (f F )100–10–20–30–40–50–60–70–80–90Figure 14. Capacitance Input Error vs. Serial Resistance;CIN(+) to GND = 8 pF and 25pF, V DD = 5 V0.2–0.62.55.505469-062VDD (V)C A P E R R O R (f F)–0.2–0.43.0 3.54.0 4.55.0Figure 15. Capacitance Input Power Supply Rejection (PSR);CIN(+) to GND = 8 pFAD7747Rev. 0 | Page 10 of 28200–20006405469-050CAPDAC CODEC A PD A C D N L (fF )150100500–50–100–1508162432404856Figure 16. CAPDAC Differential Nonlinearity (DNL)2.0–2.0–5015005469-034TEMPERATURE (°C)E R R O R (°C )1.51.00.50–0.5–1.0–1.5–250255075100125Figure 17. Internal Temperature Sensor Error vs. Temperature1.0–3.0–5015005469-035TEMPERATURE (°C)E R R O R (°C )0.50–0.5–1.0–1.5–2.0–2.5–250255075100125Figure 18. External Temperature Sensor Error vs. Temperature–12001k05469-051INPUT SIGNAL FREQUENCY (Hz)G A I N (d B )–20–40–60–80–100100200300400500600700800900Figure 19. Capacitive Channel Frequency Response;Conversion Time = 22 ms–120020005469-052INPUT SIGNAL FREQUENCY (Hz)G A I N (d B)–20–40–60–80–100255075100125150175Figure 20. Capacitive Channel Frequency Response;Conversion Time = 124 ms–120040005469-039INPUT SIGNAL FREQUENCY (Hz)G A I N (d B )–20–40–60–80–10050100150200250300350Figure 21. Voltage Channel Frequency Response;Conversion Time = 122.1 msOUTPUT NOISE AND RESOLUTION SPECIFICATIONSThe AD7747 resolution is limited by noise. The noise performance varies with the selected conversion time.Table 5 shows typical noise performance and resolution for the capacitive channel. These numbers were generated from 1000 data samples acquired in continuous conversion mode, at an excitation of 16 kHz, ±V DD × 3/8, and with all CIN and SHLD pins connected only to the evaluation board (no external capacitors). Table 6 and Table 7 show typical noise performance and resolution for the voltage channel. These numbers were generated from 1000 data samples acquired in continuous conversion mode with VIN pins shorted to ground.RMS noise represents the standard deviation and p-p noise represents the difference between minimum and maximum results in the data. Effective resolution is calculated from rms noise, and p-p resolution is calculated from p-p noise.Table 5. Typical Capacitive Input Noise and Resolution vs. Conversion Time (Bold line represents default setting)Conversion Time (ms) Output DataRate (Hz)−3 dB Frequency(Hz)RMS Noise(aF/√Hz)RMSNoise(aF)P-PNoise(aF)Effective Resolution(Bits)P-P Resolution(Bits)22.0 45.5 43.6 28.8 190 821 16.4 14.323.9 41.9 39.5 23.2 146 725 16.8 14.5 40.0 25.0 21.8 11.1 52 411 18.3 15.3 76.0 13.2 10.9 11.2 37 262 18.7 15.9 124.0 8.1 6.9 11.0 29 174 19.1 16.5 154.0 6.5 5.3 10.4 24 173 19.3 16.5 184.0 5.4 4.4 10.0 21 141 19.6 16.8 219.3 4.6 4.0 9.0 18 126 19.9 17.0Table 6. Typical Voltage Input Noise and Resolution vs. Conversion Time, Internal Voltage ReferenceConversion Time (ms) Output DataRate (Hz)−3 dB Frequency(Hz)RMS Noise(μV)P-P Noise(μV)Effective Resolution(Bits)P-P Resolution(Bits)20.1 49.8 26.4 11.4 62 17.6 15.2 32.1 31.2 15.9 7.1 42 18.3 15.7 62.1 16.1 8.0 4.0 28 19.1 16.3 122.1 8.2 4.0 3.0 20 19.5 16.8Table 7. Typical Voltage Input Noise and Resolution vs. Conversion Time, External 2.5 V Voltage ReferenceConversion Time (ms) Output DataRate (Hz)−3 dB Frequency(Hz)RMS Noise(μV)P-P Noise(μV)Effective Resolution(Bits)P-P Resolution(Bits)20.1 49.8 26.4 14.9 95 18.3 15.6 32.1 31.2 15.9 6.3 42 19.6 16.8 62.1 16.1 8.0 3.3 22 20.5 17.7 122.1 8.2 4.0 2.1 15 21.1 18.3SERIAL INTERFACEThe AD7747 supports an I2C-compatible 2-wire serial interface. The two wires on the I2C bus are called SCL (clock) and SDA (data). These two wires carry all addressing, control, and data information one bit at a time over the bus to all connected peripheral devices. The SDA wire carries the data, while the SCL wire synchronizes the sender and receiver during the data transfer. I2C devices are classified as either master or slave devices.A device that initiates a data transfer message is called a master, while a device that responds to this message is called a slave. To control the AD7747 device on the bus, the following protocol must be followed. First, the master initiates a data transfer by establishing a start condition, defined by a high-to-low transition on SDA while SCL remains high. This indicates that the start byte follows. This 8-bit start byte is made up of a 7-bit address plus an R/W bit indicator.All peripherals connected to the bus respond to the start condition and shift in the next 8 bits (7-bit address + R/W bit). The bits arrive MSB first. The peripheral that recognizes the transmitted address responds by pulling the data line low during the ninth clock pulse. This is known as the acknowledge bit. All other devices withdraw from the bus at this point and maintain an idle condition. An exception to this is the general call address, which is described later in this document. The idle condition is where the device monitors the SDA and SCL lines waiting for the start condition and the correct address byte. The R/W bit determines the direction of the data transfer. A Logic 0 LSB in the start byte means that the master writes information to the addressed peripheral. In this case, the AD7747 becomes a slave receiver. A Logic 1 LSB in the start byte means that the master reads information from the addressed peripheral. In this case, the AD7747 becomes a slave transmitter. In all instances, the AD7747 acts as a standard slave device on the I2C bus.The start byte address for the AD7747 is 0x90 for a write and0x91 for a read.READ OPERATIONWhen a read is selected in the start byte, the register that is currently addressed by the address pointer is transmitted on to the SDA line by the AD7747. This is then clocked out by the master device and the AD7747 awaits an acknowledge from the master.If an acknowledge is received from the master, the address auto-incrementer automatically increments the address pointer register and outputs the next addressed register content on to the SDA line for transmission to the master. If no acknowledge is received, the AD7747 returns to the idle state and the address pointer is not incremented.The address pointer’s auto-incrementer allows block data to be written or read from the starting address and subsequent incremental addresses. In continuous conversion mode, the address pointer’s auto-incrementer should be used for reading a conversion result. That means the three data bytes should be read using one multibyte read transaction rather than three separate single byte transactions. The single byte data read transaction may result in the data bytes from two different results being mixed. The same applies for six data bytes if both the capacitive and thevoltage/temperature channel are enabled.The user can also access any unique register (address) on a one-to-one basis without having to update all the registers. The address pointer register’s contents cannot be read.If an incorrect address pointer location is accessed, or if the user allows the auto-incrementer to exceed the required register address, the following applies:•In read mode, the AD7747 continues to output various internal register contents until the master device issues ano acknowledge, start, or stop condition. The addresspointer auto-incrementer’s contents are reset to point tothe status register at Address 0x00 when a stop condition is received at the end of a read operation. This allows thestatus register to be read (polled) continually withouthaving to constantly write to the address pointer.•In write mode, the data for the invalid address is not loaded into the AD7747 registers, but an acknowledge isissued by the AD7747.WRITE OPERATIONWhen a write is selected, the byte following the start byte is always the register address pointer (subaddress) byte, which points to one of the internal registers on the AD7747. The address pointer byte is automatically loaded into the address pointer register and acknowledged by the AD7747. After the address pointer byte acknowledge, a stop condition, a repeated start condition, or another data byte can follow from the master.A stop condition is defined by a low-to-high transition on SDA while SCL remains high. If a stop condition is ever encountered by the AD7747, it returns to its idle condition and the address pointer is reset to Address 0x00.If a data byte is transmitted after the register address pointer byte, the AD7747 loads this byte into the register that is currently addressed by the address pointer register, sends an acknowledge, and the address pointer auto-incrementer automatically increments the address pointer register to the next internal register address. Thus, subsequent transmitted data bytes are loaded into sequentially incremented addresses. If a repeated start condition is encountered after the address pointer byte, all peripherals connected to the bus respond exactly as outlined above for a start condition, that is, a repeated start condition is treated the same as a start condition. When a master device issues a stop condition, it relinquishes control ofthe bus, allowing another master device to take control of the bus. Therefore, a master wanting to retain control of the bus issues successive start conditions known as repeated start conditions.AD7747 RESETTo reset the AD7747 without having to reset the entire I 2C bus, an explicit reset command is provided. This uses a particular address pointer word as a command word to reset the part and upload all default settings. The AD7747 does not respond to the I 2C bus commands (do not acknowledge) during the default values upload for approximately 150 μs (max 200 μs). The reset command address word is 0xBF. GENERAL CALLWhen a master issues a slave address consisting of seven 0s with the eighth bit (R/W bit) set to 0, this is known as the general call address. The general call address is for addressing every device connected to the I 2C bus. The AD7747 acknowledges this address and read in the following data byte.If the second byte is 0x06, the AD7747 is reset, completely uploading all default values. The AD7747 does not respond to the I 2C bus commands (do not acknowledge) during the default values upload for approximately 150 μs (200 μs maximum). The AD7747 does not acknowledge any other general call commands.P 981–7981–798S SDATASCLOCKSTART ADDR ACK ACKDATAACKSTOPSUBADDRESS 1–705469-011Figure 22. Bus Data TransferWRITE SEQUENCEREAD SEQUENCE05469-012Figure 23. Write and Read Sequences。

12位A_D转换器ADS774JP及其在高精度检测系统中的应用

-35-12位A/D转换器ADS774J P及其在高精度检测系统中的应用兰州工业高等专科学校电气系周征A pp lication of ADS774JP12bit A/D Converter in Hi g h-PreciseMicro p rocessor Detection S y stemZhou Zhen g摘要:ADS774J P是美国Burr-Bown公司生产的12位A/D转换器,它所需外围器件少、接口方便且运算速度快,可用于高精度检测系统。

文中介绍了12位A/D转换芯片ADS774J P的主要特点,分析了ADS774J P的转换时序,给出了该转换器在高精度微机检测系统中的硬件接口电路和软件程序。

关键词:模数转换芯片;单片机;A/D;ADS774J P分类号:T N79+2文献标识码:B文章编号:1006-6977(2003)04-0035-03●新特器件应用12位A/D转换器ADS774J P及其在高精度检测系统中的应用1引言在微机检测系统中,由于传统的传感器信号是模拟信号,所以必须通过A/D转换器将其变换为数字信号后才能被计算机使用。

在笔者开发的便携式多路在线测试系统中,其系统所要求的测量范围是-50~+50V,检测精度为5‰。

由于12位A/D转换器的转换精度为0.0024V,可以满足系统要求的检测精度指标,因此,在综合了便携式多路在线测试系统的技术要求后,笔者选择12位A/D转换器ADS774J P作为模拟量输入通道的转换核心。

2ADS774J P简介ADS774J P是美国BURR-BOWN公司推出的一款12位A/D芯片,它的引脚排列如图1所示。

ADS774J P芯片采用28脚DIP封装,采用单5V电源供电;片内含有采样保持、电压基准和时钟等电路,该芯片所需外围电路少,接口方便,运算速度快,因此对缩短系统开发周期,增强系统可靠性极为有利。

ADS774J P采用CM OS工艺制造和电荷重新分配技术进行逐次逼近来实现A/D转换,该芯片转换速度快(最大转换时间不超过8.5μs)、功耗低(最大功耗小于120mW)。

电容数字转换器AD774的工作原理和应用

电容数字转换器AD774的工作原理和应用作者:郭强谢康姜海明王浩来源:《现代电子技术》2008年第14期摘要:AD774是AD公司生产的具有总线接口的电容数字转换器。

该转换器支持单端电容输入和差分式电容输入,同时在片内集成了温度传感器,可以用于代替系统中的温度传感器。

该芯片广泛的应用于生化探测、压力探测、电压探测、杂质探测等领域。

介绍AD774的功能原理和工作模式,同时给出一种使用该芯片的实际应用。

关键词:Σ-Δ调制器;差分式电容输入;单端电容输入;总线(chool of Optoelectronic Information,University of Electronic cience and echnology of China,Chengdu,61Abstract:Companyhis converter supports single-ended capacitive input and differential capacitive input,and integrates a temperature sensor which can instead of temperature sensor in systemhis chip is used in biochemistry detection,pressure detection,voltage detection and impurity detectionhe principle andKeywords:Σ-Δ modu lator;differential capacitive input;single-1 引言AD774是AD公司生产的具有高的分辨率、低功耗的电容数字转换器。

该芯片性能稳定,操作方便,可以和多种电容传感器一起开发各种实际产品。

AD774的主要特点如下:(1) 电容数字转换器具有单端电容探测器或者差分式电容探测器接口;分辨率:4 aF;精确度:4 fF;线性度:001%;在普通模式下,电容高达17 pF;可测量电容范围:-可容忍高达60 pF的寄生电容;更新频率:10~60 z。

AD7747中文数据手册

应用

汽车电子、工业和医疗系统,用于: 压力测量 位置检测 近程传感 液位检测 流量计 杂质检测

功能框图

VDD TEMP SENSOR VIN(+) VIN(–) MUX CIN1(+) CIN1(–) SHLD EXCITATION CAP DAC 2

05469-001

CLOCK GENERATOR

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 Fax: 781.461.3113 ©2007 Analog Devices, Inc. All rights reserved.

AD7747

24-BIT GENERATOR

DIGITAFACE

SDA SCL

CONTROL LOGIC CALIBRATION VOLTAGE REFERENCE

RDY

CAP DAC 1

REFIN(+)

REFIN(–)

GND

图1

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Speci cations subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

独立工作模式下的ADS774在X荧光分析仪上的应用

的封装类型包括 o3 .”或06 .”宽,2 脚DP 8 I 封装及 2 脚的 8 S I封装形式 。 OC A87 可以在2 D74 种模式一I作:一种是完全控制模式, F 即每一次转换过程都 由微处理器完全控制; 另一种是独立运 行模式,即仅仅通过R 厄的输入来控制转换。 D74 4 AS7  ̄状态 J 输出信号SAU提供了转换器当前的状态。 TTS 当状态信号为高

1 、 接低电平,人 接 M U( 2 西 0 P 微处理器 )的 P .,R 接转 30 厄 换启动脉冲输入。 出状态信号SAU连MU 32 I O, 输 T TS P 的P .( T ) N

。

一

1 A S 7 简介 D 74

AS7是一种1位逐次逼近式模数转换器, 种模拟 D74 2 有4

输入范 围:0 +O 、 一 2 、 5 +V 一O +O , 1 ~ IV 0 +0 一 ~ S 和 l ~ IV 有 2

8 位数据输出信号则与锁存器7I3 3 4 C7 的输入相连,锁存器 I

的输 出可直接连接到微处理器 的数据总线 。

位或8 位可选输出,单一十 供电。 5V A S74 D 7 采用低功耗CM 3艺和新的电容阵列技术, OS 2 包

维普资讯

独

立

工

作模式下的As7在x 。74 荧光分析仪上的应用

A p i a i n o D 7 4 n X R y F1 o e c n e A a y e n e t n - 1 n o e p ] c t o f A S 7 i - a u r s e c n l z r u d r S a d a o e M d

一

态, 无法从输出端读出正 确数 在此期间, 线上的信 据, 输出

新型单片AD转换器AD7710中文资料

输入采样速率,fs 参考输入 REF IN(+)-REF IN(-)Voltage

输入采样速率, fs

0.5 0.25 (4) 0.5 0.25 2 ±0.003 ±0.006 1 0.3

uV/℃ typ uV/℃ typ

放大倍数为 1,2 放大倍数为 4,8,16,32,64,128

uV/℃ typ uV/℃ typ ppm/℃ typ %of FSRmax %of FSRmax uV/℃ typ uV/℃ typ

4,8,16,32,64,128

单极补偿误差(2)

(4)

单极补偿漂移(5)

双极零误差(2) 双极零漂移(5)

增益漂移 双极负极满量程误差(25℃)(2) 最小时间比最大时间 双极负极满量程漂移(5)

模拟输入/基准电压源输入 普通模式输入抑制

普通模式电压范围 标准模式 50HZ 抑制 标准模式 60HZ 抑制 普通模式 50HZ 抑制 普通模式 60HZ 抑制 直流漏电流(25℃) 最短时间比最长时间 采样电容

第一页

特性: 充电平衡 ADC

24 位,不丢失码 非线性度为 0.0015% 双通道可编程增益前端 增益范围为 1 到 128 差动输入 低通滤波器,截止频率可通过编程设置 校准系数可读写 具有串口的双向微控制器 可选择内外基准参考电源 可提供单端或者双端补偿 功耗低(一般为 25mW),还有待机模式(一般为 7mW) 应用: 天平,温差热电偶,过程控制,快速转换器,色谱分析仪(可编程控制及数字控制,工业 仪器仪表,传感器信号采集控制) 一般说明:

可选型号

R=小块集成电路

第五页

时间特性(1,2):(DVdd=+5V±5%;AVdd=+5 或+10V±5%;Vss=0V 或-5V±

ADS774数据手册

查询ADS774供应商© 1991 Burr-Brown Corporation PDS-1109F Printed in U.S.A. July, 1995®ADS7742SPECIFICATIONSELECTRICALAt T A = T MIN to T MAX , V DD = +5V, V EE = –15V to +5V, sampling frequency of 117kHz, f IN= 10kHz; unless otherwise specified.ADS7743®SPECIFICATIONS (CONT)ELECTRICALAt T A = T MIN to T MAX , V DD = +5V, V EE = –15V to +5V, sampling frequency of 117kHz, f IN = 10kHz; unless otherwise specified.The information provided herein is believed to be reliable; however, BURR-BROWN assumes no responsibility for inaccuracies or omissions. BURR-BROWN assumes no responsibility for the use of this information, and all use of such information shall be entirely at the user’s own risk. Prices and specifications are subject to change without notice. No patent rights or licenses to any of the circuits described herein are implied or granted to any third party. BURR-BROWN does not authorize or warrant any BURR-BROWN product for use in life support devices and/or systems.T Same specification as ADS774JE, JP, JU.NOTES: (1) With fixed 50Ω resistor from REF OUT to REF IN. This parameter is also adjustable to zero at +25°C. (2) FS in this specification table means Full Scale Range. That is, for a ±10V input range, FS means 20V; for a 0 to +10V range, FS means 10V. (3) Maximum error at T MIN and T MAX . (4) Based on using V EE =+5V, which is the Control Mode. See the section "S/H Control Mode and ADC774 Emulation Mode." (5) Using internal reference. (6) This is worst case change in accuracy from accuracy with a +5V supply. (7) V EE is optional, and is only used to set the mode for the internal sample/hold. When V EE = –15V, I EE = –1mA typ; when V EE = 0V, I EE = ±5µA typ; when V EE = +5V, I EE = +167µA typ.®ADS7744ABSOLUTE MAXIMUM RATINGSV EE to Digital Common.......................................................+V DD to –16.5V V DD to Digital Common ..............................................................0V to +7V Analog Common to Digital Common....................................................±1V Control Inputs (CE, CS, A O , 12/8, R/C)to Digital Common ..................................................–0.5V to V DD +0.5V Analog Inputs (Ref In, Bipolar Offset, 10V IN )to Analog Common ......................................................................±16.5V 20VIN to Analog Common ..................................................................±24V Ref Out..........................................................Indefinite Short to Common,Momentary Short to V DDMax Junction Temperature ............................................................+165°C Power Dissipation ........................................................................1000mW Lead Temperature (soldering,10s).................................................+300°C Thermal Resistance, θJA : Plastic DIPs........................................100°C/WSOIC...................................................100°C/WThis integrated circuit can be damaged by ESD. Burr-Brown recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degrada-tion to complete device failure. Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.PACKAGE/ORDERING INFORMATIONTEMPERATURELINEARITY PACKAGE DRAWINGPRODUCT SINAD (1)RANGE ERROR PACKAGE NUMBER (2)ADS774JE 68dB 0°C to +70°C ±1LSB 28-Pin 0.3" Plastic DIP 246ADS774KE 70dB 0°C to +70°C ±1/2LSB 28-Pin 0.3" Plastic DIP 246ADS774JP 68dB 0°C to +70°C ±1LSB 28-Pin 0.6" Plastic DIP 215ADS774KP 70dB 0°C to +70°C ±1/2LSB 28-Pin 0.6" Plastic DIP215ADS774JU 68dB 0°C to +70°C ±1LSB 28-Lead SOIC 217ADS774KU70dB0°C to +70°C±1/2LSB28-Lead SOIC217NOTES: (1) SINAD is Signal-to-(Noise + Distortion) expressed in dB. (2) For detailed drawing and dimension table, please see end of data sheet, or Appendix C of Burr-Brown IC Data Book.CONNECTION DIAGRAMADS7745®FREQUENCY SPECTRUM (±1V, 20kHz Input)M a g n i t u d e (d B )Input Frequency (kHz)0–60–12010–100–80–40–202030405055®ADS7746THEORY OF OPERATIONIn the ADS774, the advantages of advanced CMOS technol-ogy—high logic density, stable capacitors, precision analog switches—and Burr-Brown’s state of the art laser trimming techniques are combined to produce a fast, low power analog-to-digital converter with internal sample/hold.The charge-redistribution successive-approximation circuitry converts analog input voltages into digital words.A simple example of a charge-redistribution A/D converter with only 3 bits is shown in Figure 1.latch S 1 in position “R” or “G”. Similarly, the second approximation is made by connecting S 2 to the reference and S 3 to GND, and latching S 2 according to the output of the comparator. After three successive approximation steps have been made the voltage level at the comparator will be within 1/2LSB of GND, and a digital word which represents the analog input can be determined from the positions of S 1, S 2and S 3.OPERATIONBASIC OPERATIONFigure 2 shows the minimum connections required to oper-ate the ADS774 in a basic ±10V range in the Control Mode (discussed in detail in a later section.) The falling edge of a Convert Command (a pulse taking pin 5 LOW for a mini-mum of 25ns) both switches the ADS774 input to the hold state and initiates the conversion. Pin 28 (STATUS) will output a HIGH during the conversion, and falls only after the conversion is completed and the data has been latched on the data output pins (pins 16 to 27.) Thus, the falling edge of STATUS on pin 28 can be used to read the data from the conversion. Also, during conversion, the STATUS signal puts the data output pins in a High-Z state and inhibits the input lines. This means that pulses on pin 5 are ignored, so that new conversions cannot be initiated during the conver-sion, either as a result of spurious signals or to short-cycle the ADS774.The ADS774 will begin acquiring a new sample as soon as the conversion is completed, even before the STATUS output falls, and will track the input signal until the next conversion is started. The ADS774 is designed to complete a conversion and accurately acquire a new signal in 8.5µs max over the full operating temperature range, so that conversions can take place at a full 117kHz.CONTROLLING THE ADS774The Burr-Brown ADS774 can be easily interfaced to most microprocessor systems and other digital systems. The microprocessor may take full control of each conversion, orthe converter may operate in a stand-alone mode, controlled only by the R/C input. Full control consists of selecting an 8- or 12-bit conversion cycle, initiating the conversion, and reading the output data when ready—choosing either 12 bits all at once, or the 8 MSB bits followed by the 4 LSB bits in a left-justified format. The five control inputs (12/8, CS, A 0,R/C, and CE) are all TTL/CMOS-compatible. The functions of the control inputs are described in Table II. The control function truth table is shown in Table III.STAND-ALONE OPERATIO NFor stand-alone operation, control of the converter is accom-plished by a single control line connected to R/C. In this mode CS and A 0 are connected to digital common and CE and 12/8 are connected to +5V. The output data areFIGURE 1. 3-Bit Charge Redistribution A/D.INPUT SCALINGPrecision laser-trimmed scaling resistors at the input divide standard input ranges (0V to +10V, 0V to +20V, ±5V or ±10V) into levels compatible with the CMOS characteristics of the internal capacitor array.SAMPLINGWhile sampling, the capacitor array switch for the MSB capacitor (S 1) is in position “S”, so that the charge on the MSB capacitor is proportional to the voltage level of the analog input signal. The remaining array switches (S 2 and S 3) are set to position “G”. Switch S C is closed, setting the comparator input offset to zero.CONVERSIONWhen a conversion command is received, switch S 1 is opened to trap a charge on the MSB capacitor proportional to the analog input level at the time of the sampling com-mand, and switch S C is opened to float the comparator input.The charge trapped in the capacitor array can now be moved between the three capacitors in the array by connecting switches S 1, S 2, and S 3 to positions “R” (to connect to the reference) or “G” (to connect to GND), thus changing the voltage generated at the comparator input.During the first approximation, the MSB capacitor is con-nected through switch S 1 to the reference, while switches S 2and S 3 are connected to GND. Depending on whether the comparator output is HIGH or LOW, the logic will thenADS7747®presented as 12-bit words. The stand-alone mode is used in systems containing dedicated input ports which do not require full bus interface capability.Conversion is initiated by a HIGH-to-LOW transition of R/C. The three-state data output buffers are enabled when R/C is HIGH and STATUS is LOW. Thus, there are two possible modes of operation; data can be read with either a positive pulse on R/C, or a negative pulse on STATUS. In either case the R/C pulse must remain LOW for a minimum of 25ns.Figure 3 illustrates timing with an R/C pulse which goes LOW and returns HIGH during the conversion. In this case,the three-state outputs go to the high-impedance state in response to the falling edge of R/C and are enabled for external access of the data after completion of the conver-sion.Figure 4 illustrates the timing when a positive R/C pulse is used. In this mode the output data from the previous conver-sion is enabled during the time R/C is HIGH. A new conversion is started on the falling edge of R/C, and the three-state outputs return to the high-impedance state until the next occurrence of a HIGH R/C pulse. Timing specifica-tions for stand-alone operation are listed in Table IV.FULLY CONTROLLED OPERATION Conversion LengthConversion length (8-bit or 12-bit) is determined by the state of the A 0 input, which is latched upon receipt of a conver-sion start transition (described below). If A 0 is latched HIGH, the conversion continues for 8 bits. The full 12-bit conversion will occur if A 0 is LOW. If all 12 bits are readFIGURE 2. Basic ±10V Operation.following an 8-bit conversion, the 4LSBs (DB0-DB3) will be LOW (logic 0). A 0 is latched because it is also involved in enabling the output buffers. No other control inputs are latched.CONVERSION STARTThe converter initiates a conversion based on a transition occurring on any of three logic inputs (CE, CS, and R/C) as shown in Table III. Conversion is initiated by the last of the three to reach the required state and thus all three may be dynamically controlled. If necessary, all three may change state simultaneously, and the nominal delay time is the same regardless of which input actually starts the conversion. If it is desired that a particular input establish the actual start of conversion, the other two should be stable a minimum of 50ns prior to the transition of the critical input. Timing relationships for start of conversion timing are illustrated in Figure 5. The specifications for timing are contained in Table V.The STATUS output indicates the current state of the con-verter by being in a high state only during conversion.During this time the three state output buffers remain in a high-impedance state, and therefore data cannot be read during conversion. During this period additional transitions of the three digital inputs which control conversion will be ignored, so that conversion cannot be prematurely termi-nated or restarted. However, if A 0 changes state after the beginning of conversion, any additional start conversion transition will latch the new state of A 0, possibly resulting in an incorrect conversion length (8 bits vs 12 bits) for thatconversion.®ADS7748DESIGNATION DEFINITION FUNCTIONCE (Pin 6)Chip Enable Must be HIGH (“1”) to either initiate a conversion or read output data. 0-1 edge may be used to initiate a (active high)conversion.CS (Pin 3)Chip Select Must be LOW (“0”) to either initiate a conversion or read output data. 1-0 edge may be used to initiate a (active low)conversion.R/C (Pin 5)Read/Convert Must be LOW (“0”) to initiate either 8- or 12-bit conversions. 1-0 edge may be used to initiate a conversion.(“1” = read)Must be HIGH (“1”) to read output data. 0-1 edge may be used to initiate a read operation.(“0” = convert)A O (Pin 4)Byte Address In the start-convert mode, A O selects 8-bit (A O = “1”) or 12-bit (A O = “0”) conversion mode. When reading Short Cycle output data in two 8-bit bytes, A O = “0” accesses 8 MSBs (high byte) and A O = “1” accesses 4 LSBs and trailing “0s” (low byte).12/8 (Pin 2)Data Mode Select When reading output data, 12/8 = “1” enables all 12 output bits simultaneously. 12/8 = “0” will enable the (“1” = 12 bits)MSBs or LSBs as determined by the A O line.(“0” = 8 bits)TABLE II.Control Line Functions.Binary (BIN) Output Input Voltage Range and LSB Values Analog Input Voltage Range Defined As:±10V ±5V 0V to +10V 0V to +20V One Least Significant Bit FSR 20V 10V 10V 20V (LSB)2n 2n2n2n2nn = 878.13mV 39.06mV 39.06mV 78.13mV n = 124.88mV 2.44mV 2.44mV 4.88mV Output Transition Values FFE H to FFF H + Full-Scale Calibration+10V – 3/2LSB +5V – 3/2LSB +10V – 3/2LSB +20V – 3/2LSB 7FFF H to 800H Midscale Calibration (Bipolar Offset)0V – 1/2LSB 0V – 1/2LSB +5V – 1/2LSB +10V – 1/2LSB 000H to 001HZero Calibration ( – Full-Scale Calibration)–10V + 1/2LSB–5V + 1/2LSB0V +1/2LSB0V +1/2LSBTABLE I.Input Voltages, Transition Values, and LSB Values.READING OUTPUT DATAAfter conversion is initiated, the output data buffers remain in a high-impedance state until the following four logic conditions are simultaneously met: R/C HIGH, STATUS LOW, CE HIGH, and CS LOW. Upon satisfaction of these conditions the data lines are enabled according to the state of inputs 12/8 and A 0. See Figure 6 and Table V for timing relationships and specifications.In most applications the 12/8 input will be hard-wired in either the HIGH or LOW condition, although it is fully TTL and CMOS-compatible and may be actively driven if de-sired. When 12/8 is HIGH, all 12 output lines (DB0-DB11)are enabled simultaneously for full data word transfer to a 12-bit or 16-bit bus. In this situation the A 0 state is ignored when reading the data.When 12/8 is LOW, the data is presented in the form of two 8-bit bytes, with selection of the byte of interest accom-plished by the state of A 0 during the read cycle. When A 0 is LOW, the byte addressed contains the 8MSBs. When A 0 is HIGH, the byte addressed contains the 4LSBs from the conversion followed by four logic zeros which have been forced by the control logic. The left-justified formats of the two 8-bit bytes are shown in Figure 7. Connection of the ADS774 to an 8-bit bus for transfer of the data is illustrated in Figure 8. The design of the ADS774 guarantees that the A 0 input may be toggled at any time with no damage to the converter; the outputs which are tied together in Figure 8cannot be enabled at the same time. The A 0 input is usually driven by the least significant bit of the address bus, allow-ing storage of the output data word in two consecutive memory locations.TABLE III.Control Input Truth Table.ADS7749®FIGURE 4. R/C Pulse High — Outputs Enabled Only WhileR/C Is High.FIGURE 3. R/C Pulse Low—Outputs Enabled After Conver-sion.SYMBOL PARAMETERMIN TYPMAXUNITS t HRL Low R/C Pulse Width 25ns t DS STS Delay from R/C200ns t HDR Data Valid After R/C Low 25ns t HRH High R/C Pulse Width 100ns t DDRData Access Time150nsTABLE IV.Stand-Alone Mode Timing. (T A = T MIN to T MAX ).SYMBOL PARAMETERMINTYPMAXUNITSConvert Modet DSC STS delay from CE 60200ns t HEC CE Pulse width 5030ns t SSC CS to CE setup5020ns t HSC CS low during CE high 5020ns t SRC R/C to CE setup500ns t HRC R/C low during CE high 5020nst SAC A O to CE setup0ns t HAC A O valid during CE high5020nsRead Modet DD Access time from CE 75150ns t HD Data valid after CE low 2535ns t HL Output float delay 100150ns t SSR CS to CE setup 500ns t SRR R/C to CE setup 0ns t SAR A O to CE setup5025ns t HSR CS valid after CE low 0ns t HRR R/C high after CE low 0ns t HAR A O valid after CE low50ns t HSSTATUS delay after data valid75150375nsTABLE V.Timing Specifications, Fully Controlled Operation. (T A = T MIN to T MAX ).FIGURE 5. Conversion Cycle Timing.FIGURE 6. Read Cycle Timing.®ADS77410S/H CONTROL MODEAND ADC774 EMULATION MODEThe Emulation Mode allows the ADS774 to be dropped into most existing ADC774 sockets without changes to other system hardware or software. In existing sockets, the analog input is held stable during the conversion period so that accurate conversions can proceed, but the input can change rapidly at any time before the conversion starts. The Emula-tion Mode uses the stability of the analog input during the conversion period to both acquire and convert in a maximum of 8µs (8.5µs over temperature.) In fact, system throughput can be increased, since the input to the ADS774 can start slewing before the end of a conversion (after the acquisition time), which is not possible with existing ADC774s.The Control Mode is provided to allow full use of the internal sample/hold, eliminating the need for an external sample/hold in most applications. As compared with sys-tems using separate sample/hold and A/D, the ADS774 in the Control Mode also eliminates the need for one of the control signals, usually the convert command. The com-mand that puts the internal sample/hold in the hold state also initiates a conversion, reducing timing constraints in many systems.The basic difference between these two modes is the assumptions about the state of the input signal both before and during the conversion. The differences are shown in Figure 9 and Table VI. In the Control Mode, it is assumed that during the required 1.4µs acquisition time the signal is not changing faster than the ADS774 can track. No assump-tion is made about the input level after the convert command arrives, since the input signal is sampled and conversion begins immediately after the convert command. This means that a convert command can also be used to switch an input multiplexer or change gains on a programmable gain ampli-fier, allowing the input signal to settle before the next acquisition at the end of the conversion. Because aperture jitter is minimized in the Control Mode, a high input fre-quency can be converted without an external sample/hold.In the Emulation Mode, a delay time is introduced between the convert command and the start of conversion to allow the ADS774 enough time to acquire the input signal before converting. This increases the effective aperture delay time from 0.02µs to 1.6µs, but allows the ADS774 to replace the ADC774 in most circuits without additional changes. In designs where the input to the ADS774 is changing rapidly in the 200ns prior to a convert command, system perfor-mance may be enhanced by delaying the convert command by 200ns.When using the ADS774 in the Emulation Mode to replace existing converters in current designs, a sample/hold ampli-fier often precedes the converter. In these cases, no addi-tional delay in the convert command will be needed. The existing sample/hold will not be slewing excessively when going from the sample mode to the hold mode prior to a conversion.In both modes, as soon as the conversion is completed the internal sample/hold circuit immediately begins slewing to track the input signal.ADS77411®In particular, the unused input pin should not be connected to any capacitive load, including high impedance switches.Even a few pF on the unused pin can degrade acquisition time.Coupling between analog input and digital lines should be minimized by careful layout. For instance, if the lines must cross, they should do so at right angles. Parallel analog and digital lines should be separated from each other by a pattern connected to common.If external full scale and offset potentiometers are used, the potentiometers and associated resistors should be as close as possible to the ADS774.POWER SUPPLY DECOUPLINGOn the ADS774, +5V (to Pin 1) is the only power supply required for correct operation. Pin 7 is not connected inter-nally, so there is no problem in existing ADC774 sockets where this is connected to +15V. Pin 11 (V EE ) is only used as a logic input to select modes of control over the sampling function as described above. When used in an existing ADC774 socket, the –15V on pin 11 selects the ADC774Emulation Mode. Since pin 11 is used as a logic input, it is immune to typical supply variations.INSTALLATIONLAYOUT PRECAUTIONSAnalog (pin 9) and digital (pin 15) commons are not con-nected together internally in the ADS774, but should be connected together as close to the unit as possible and to an analog common ground plane beneath the converter on the component side of the board. In addition, a wide conductor pattern should run directly from pin 9 to the analog supply common, and a separate wide conductor pattern from pin 15to the digital supply common.If the single-point system common cannot be established directly at the converter, pin 9 and pin 15 should still be connected together at the converter. A single wide conductor pattern then connects these two pins to the system common.In either case, the common return of the analog input signal should be referenced to pin 9 of the ADC. This prevents any voltage drops that might occur in the power supply common returns from appearing in series with the input signal.The speed of the ADS774 requires special caution regarding whichever input pin is unused. For 10V input ranges, pin 14(20V Range) must be unconnected, and for 20V input ranges, pin 13 (10V Range) must be unconnected. In both cases, the unconnected input should be shielded with ground plane to reduce noise pickup.S/H CONTROL MODE ADC774 EMULATION MODE(Pin 11 Connected to +5V) (Pin 11 Connected to 0V to –15V)SYMBOL PARAMETER MINTYP MAX MIN TYP MAX UNITS t AQ + t CThroughput Time:12-bit Conversions 88.588.5µs 8-bit Conversions 6 6.36 6.3µs t CConversion Time:12-bit Conversions 6.4 6.4µs 8-bit Conversions 4.4 4.4µs t AQ Acquisition Time 1.4 1.4µs t AP Aperture Delay 201600ns t JAperture Uncertainty0.310nsTABLE VI. Conversion Timing, T MIN to T MAX .FIGURE 9. Signal Acquisition and Conversion Timing.®ADS77412connected either to Pin 9 (Analog Common) for unipolar operation, or to Pin 8 (2.5V Ref Out), or the external reference, for bipolar operation. Full-scale and offset adjust-ments are described below.The input impedance of the ADS774 is typically 50kΩ in the 20V ranges and 12kΩ in the 10V ranges. This is signifi-cantly higher than that of traditional ADC774 architectures, reducing the load on the input source in most applications. INPUT STRUCTUREFigure 12 shows the resistor divider input structure of the ADS774. Since the input is driving a capacitor in the CDAC during acquisition, the input is looking into a high imped-ance node as compared with traditional ADC774 architec-tures, where the resistor divider network looks into a com-parator input node at virtual ground.To understand how this circuit works, it is necessary to know that the input range on the internal sampling capacitor is from 0V to +3.33V, and the analog input to the ADS774 must be converted to this range. Unipolar 20V range can be used as an example of how the divider network functions. In 20V operation, the analog input goes into pin 14. Pin 13 is left unconnected and pin 12 is connected to pin 9, analog common. From Figure 12, it is clear that the input to the capacitor array will be the analog input voltage on pin 14 divided by the resistor network (42kΩ + 42kΩ || 10.5kΩ). A 20V input at pin 14 is divided to 3.33V at the capacitor array, while a 0V input at pin 14 gives 0V at the capacitor array.The main effect of the 10kΩ internal resistor on pin 12 is to provide the same offset adjust response as that of traditional ADC774 architectures without changing the external trimpot values.SINGLE SUPPLY OPERATIONThe ADS774 is designed to operate from a single +5V supply, and handle all of the unipolar and bipolar input ranges, in either the Control Mode or the Emulation Mode as described above. Pin 7 is not connected internally. This isFIGURE 10. Unipolar Configuration.The +5V supply should be bypassed with a 10µF tantalum capacitor located close to the converter to promote noise-free operations, as shown in Figure 2. Noise on the power supply lines can degrade the converter’s performance. Noise and spikes from a switching power supply are especially troublesome.RANGE CONNECTIONSThe ADS774 offers four standard input ranges: 0V to +10V, 0V to +20V, ±5V, or ±10V. Figures 10 and 11 show the necessary connections for each of these ranges, along with the optional gain and offset trim circuits. If a 10V input range is required, the analog input signal should be con-nected to pin 13 of the converter. A signal requiring a 20V range is connected to pin 14. In either case the other pin ofthe two is left unconnected. Pin 12 (Bipolar Offset) isFIGURE 11. Bipolar Configuration.FIGURE 12. ADS774 Input Structure.ADS77413®where +12V or +15V is supplied on traditional ADC774s.Pin 11, the –12V or –15V supply input on traditional ADC774s, is used only as a logic input on the ADS774.There is a resistor divider internally on pin 11 to reduce that input to a correct logic level within the ADS774, and this resistor will add 10mW to 15mW to the power consumption of the ADS774 when –15V is supplied to pin 11. To minimize power consumption in a system, pin 11 can be simply grounded (for Emulation Mode) or tied to +5V (for Control Mode.)There are no other modifications required for the ADS774 to function with a single +5V supply.CALIBRATIONOPTIONAL EXTERNAL FULL-SCALE AND OFFSET ADJUSTMENTSOffset and full-scale errors may be trimmed to zero using external offset and full-scale trim potentiometers connected to the ADS774 as shown in Figures 10 and 11 for unipolar and bipolar operation.CALIBRATION PROCEDURE—UNIPOLAR RANGESIf external adjustments of full-scale and offset are not required, replace R 2 in Figure 10 with a 50Ω 1% metal film resistor and connect pin 12 to pin 9, omitting the other adjustment components.If adjustment is required, connect the converter as shown in Figure 10. Sweep the input through the end-point transition voltage (0V + 1/2LSB; +1.22mV for the 10V range, +2.44mV for the 20V range) that causes the output code to be DB0 ON (HIGH). Adjust potentiometer R 1 until DB0 is alternately toggling ON and OFF with all other bits OFF. Then adjust full scale by applying an input voltage of nominal full-scale minus 3/2LSB, the value which should cause all bits to be ON. This value is +9.9963V for the 10V range and +19.9927V for the 20V range. Adjust potentiometer R 2 until bits DB1-DB11 are ON and DB0 is toggling ON and OFF.CALIBRATION PROCEDURE—BIPOLAR RANGES If external adjustments of full-scale and bipolar offset are not required, replace the potentiometers in Figure 11 by 50Ω, 1% metal film resistors.If adjustments are required, connect the converter as shown in Figure 11. The calibration procedure is similar to that described above for unipolar operation, except that the offset adjustment is performed with an input voltage which is 1/2LSB above the minus full-scale value (–4.9988V for the ±5V range, –9.9976V for the ±10V range). Adjust R 1 for DB0 to toggle ON and OFF with all other bits OFF. To adjust full-scale, apply a DC input signal which is 3/2LSB below the nominal plus full-scale value (+4.9963V for ±5V range, +9.9927V for ±10V range) and adjust R 2 for DB0 to toggle ON and OFF with all other bits ON.。

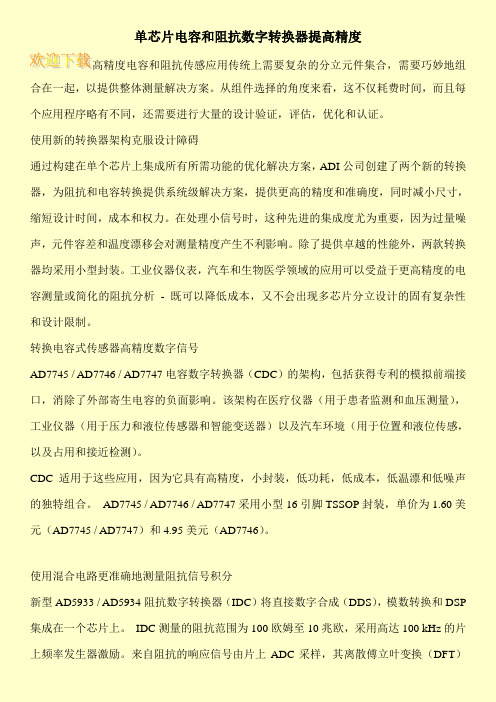

单芯片电容和阻抗数字转换器提高精度

单芯片电容和阻抗数字转换器提高精度高精度电容和阻抗传感应用传统上需要复杂的分立元件集合,需要巧妙地组合在一起,以提供整体测量解决方案。

从组件选择的角度来看,这不仅耗费时间,而且每个应用程序略有不同,还需要进行大量的设计验证,评估,优化和认证。

使用新的转换器架构克服设计障碍通过构建在单个芯片上集成所有所需功能的优化解决方案,ADI公司创建了两个新的转换器,为阻抗和电容转换提供系统级解决方案,提供更高的精度和准确度,同时减小尺寸,缩短设计时间,成本和权力。

在处理小信号时,这种先进的集成度尤为重要,因为过量噪声,元件容差和温度漂移会对测量精度产生不利影响。

除了提供卓越的性能外,两款转换器均采用小型封装。

工业仪器仪表,汽车和生物医学领域的应用可以受益于更高精度的电容测量或简化的阻抗分析- 既可以降低成本,又不会出现多芯片分立设计的固有复杂性和设计限制。

转换电容式传感器高精度数字信号AD7745 / AD7746 / AD7747电容数字转换器(CDC)的架构,包括获得专利的模拟前端接口,消除了外部寄生电容的负面影响。

该架构在医疗仪器(用于患者监测和血压测量),工业仪器(用于压力和液位传感器和智能变送器)以及汽车环境(用于位置和液位传感,以及占用和接近检测)。

CDC适用于这些应用,因为它具有高精度,小封装,低功耗,低成本,低温漂和低噪声的独特组合。

AD7745 / AD7746 / AD7747采用小型16引脚TSSOP封装,单价为1.60美元(AD7745 / AD7747)和4.95美元(AD7746)。

使用混合电路更准确地测量阻抗信号积分新型AD5933 / AD5934阻抗数字转换器(IDC)将直接数字合成(DDS),模数转换和DSP 集成在一个芯片上。

IDC测量的阻抗范围为100欧姆至10兆欧,采用高达100 kHz的片上频率发生器激励。

来自阻抗的响应信号由片上ADC采样,其离散傅立叶变换(DFT)。

AnaChip AH174 数据手册

AH174Inverted Output Hall Effect Latch For High TemperatureFeatures- Bipolar Hall effect latch sensor - 3.5V to 20V DC operation voltage - Open collector pre-driver - 25mA output sink current- Chip power reverse-connection protection - Operating temperature: C 125~C 40°+°− - Package: SIP3, SOT23Applications- Rotor position sensing - Current switch - Encoder- RPM detectionPin Assignment(SIP3 package)( SOT23 package)1. VCC2. GND3.OUT 1. VCC3.GND 2.OUT(Top view)General DescriptionAH174 is a single-digital-output Hall-effect sensor for high temperature operation. The device includes an on-chip Hall voltage generator for magnetic sensing, an amplifier to amplify Hall voltage, and a comparator to provide switching hysteresis for noise rejection, and an open-collector output pre-driver. An internal bandgap regulator is used to provide temperature compensated supply voltage for internal circuits and allows a wide operating supply range. While the magnetic flux density (B) is larger than threshold Bop, the OUT pin turns off (High). If B removed toward Brp, the OUT pin is latched “off” state prior to B < Brp. When B < Brp, the OUT pin go into “ on ” state.Pin DescriptionsNameDescriptionVCC Input power GND GroundOUTInverted output stageOrdering InformationAH174X -X X X -XPacking A :TapingW: SOT23Package Lead Blank: NormalWafer Body Magnetic CharacteristicsA~Z : if necessary to specify查询AH174供应商Inverted Output Hall Effect Latch For High TemperatureBlock DiagramAMPREG.132VCC OUTGNDApplication CircuitMDriver &Control LogicI a I b I cI A I C I BH B H A H CM: Three Phase Hall MotorDigital Hall Effect Sensor Hall Motor DriverRPM sensingThree Phase Hall MotorInverted Output Hall Effect Latch For High TemperatureAbsolute Maximum Ratings ( at Ta= 25°C )CharacteristicsSymbolRatingUnitSupply voltage VCC 20 VOutput “off ” voltage V out (off) 20 V Output “on” currentI o (sink) 25 mA Operating Temperature range T opt -40~+125 °C Storage Temperature range T stg-65~+150°CSIP 550 mWPower Dissipation SOT23 PD230 mWElectrical Characteristics ( Ta= 25°C )ParameterSymbolConditionsMin.Typ.Max.UnitSupply voltageVcc —3.5 - 20 VOutput saturation voltage Vout(sat)VCC=12V, OUT ”ON” Io =10mA- 300 400 mV Supply currentIccVCC=12V, OUT ”OFF”- 3.5 6 mAMagnetic Characteristics (Ta= 25°C )(1mT = 10 Gauss)A gradeParameterSymbolMin.Typ.Max.UnitOperate Point Bop 15 - 60 Gauss Release PointBrp-60--15GaussHysteresis Bhy - 80 - GaussB gradeParameterSymbolMin.Typ.Max.UnitOperate Point Bop 5 - 80 Gauss Release PointBrp-80--5GaussHysteresis Bhy - 80 - GaussInverted Output Hall Effect Latch For High TemperatureOperating CharacteristicsMarking sideSB hyV satV cc( O u t p u t V o l t a g e )B rpB op( Magnetic flux density )Marking sideS ( SIP3 )( SOT23 )N NMarking Information(1) SOT23(2) SIP3XX YM XM : Month (A~L)(Top View)174 YWW XY : YearWW : Nth week(Top View)ID codeA~Z: Non-Lead Free a~z : Lead FreeInverted Output Hall Effect Latch For High TemperaturePackage Information(1) Package Type: SIP-3LActive Area DepthSensor Location1232.10mm1.55mm0.51mm NOMBRANDED SURFACEPackage Dimension1.57mm 1.47mm4.17mm 4.04mm1.82mm15.50mm 13.00mm1231.27mm0.41mm0.41mm45º45º0.38mm0.7mm3.10mm 2.97mmInverted Output Hall Effect Latch For High Temperature(2) Package Type: SOT23-3LLeEH EDA 2A 1b(3x)ASEE VIEW CVIEW CL1θ1(4x)θ2(4x)e1θGAUGE PLANE SEATING PLANEC0.103X2131.45mm0.8mm( Sensing point )Dimensions In MillimetersDimensions In InchesSymbolMin. Nom. Max. Min. Nom. Max.A 1.05 - 1.35 0.041 - 0.053 A1 0.05 - 0.15 0.002 - 0.006 A2 1.00 1.10 1.20 0.039 0.043 0.047 b 0.25 - 0.50 0.010 - 0.020 C 0.08 - 0.20 0.003 - 0.008 D 2.70 2.90 3.00 0.106 0.114 0.118 E 1.50 1.60 1.70 0.059 0.063 0.067 HE 2.60 2.80 3.00 0.102 0.110 0.118 L 0.30 - 0.55 0.012 - 0.022 L1 0.50 0.60 0.70 0.020 0.024 0.028 e 1.80 1.90 2.00 0.071 0.075 0.079 e1 0.85 0.95 1.05 0.033 0.037 0.041θ 0o 5o 10o 0o 5o 10oθ1 3o 5o 7o 3o5o 7o θ2 6o 8o 10o 6o 8o 10o。

ANALOG DEVICES ADG417 数据手册

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.Tel: 781/329-4700World Wide Web Site: Fax: 781/326-8703© Analog Devices, Inc., 1998REV.AInformation furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.aLC 2MOS Precision Mini-DIP Analog SwitchADG417FEATURES44 V Supply Maximum Ratings V SS to V DD Analog Signal Range Low On Resistance (<35 ⍀)Ultralow Power Dissipation (<35 W)Fast Switching Times t ON (160ns max)t OFF (100ns max)Break-Before-Make Switching Action Plug-In Replacement for DG417APPLICATIONSPrecision Test Equipment Precision Instrumentation Battery Powered Systems Sample Hold SystemsFUNCTIONAL BLOCK DIAGRAMSWITCH SHOWN FOR ALOGIC "1" INPUTPRODUCT HIGHLIGHTS1.Extended Signal RangeThe ADG417 is fabricated on an enhanced LC 2MOS process,giving an increased signal range that extends to the supply rails.2.Ultralow Power Dissipation 3.Low R ON4.Single Supply OperationFor applications where the analog signal is unipolar, the ADG417 can be operated from a single rail power supply.The part is fully specified with a single +12 V power supply and will remain functional with single supplies as low as +5V.GENERAL DESCRIPTIONThe ADG417 is a monolithic CMOS SPST switch. This switch is designed on an enhanced LC 2MOS process that provides low power dissipation yet gives high switching speed, low on resis-tance and low leakage currents.The on resistance profile of the ADG417 is very flat over the full analog input range ensuring excellent linearity and lowdistortion. The part also exhibits high switching speed and high signal bandwidth. CMOS construction ensures ultralow power dissipation making the parts ideally suited for portable and battery powered instruments.The ADG417 switch, which is turned ON with a logic low on the control input, conducts equally well in both directions when ON and has an input signal range that extends to the supplies.In the OFF condition, signal levels up to the supplies are blocked. The ADG417 exhibits break-before-make switching action for use in multiplexer applications. Inherent in the design is low charge injection for minimum transients when switching the digital input.查询ADG417供应商B VersionT Version–40؇C to–55؇C toParameter+25؇C +85؇C+25؇C +125؇CUnits Test Conditions/CommentsANALOG SWITCH Analog Signal Range V SS to V DDV SS to V DDV R ON2525Ω typ V D = ±12.5 V, I S = –10 mA 35453545Ω max V DD = +13.5 V, V SS = –13.5 V LEAKAGE CURRENTSV DD = +16.5 V, V SS = –16.5 V Source OFF Leakage I S (OFF)±0.1±0.1nA typ V D = ±15.5 V, V S = ϯ15.5 V;±0.25±5±0.25±15nA max Test Circuit 2Drain OFF Leakage I D (OFF)±0.1±0.1nA typ V D = ±15.5 V, V S = ϯ15.5 V;±0.25±5±0.25±15nA max Test Circuit 2Channel ON Leakage I D , I S (ON)±0.1±0.1nA typ V S = V D = ±15.5 V;±0.4±5±0.4±30nA max Test Circuit 3DIGITAL INPUTSInput High Voltage, V INH 2.4 2.4V min Input Low Voltage, V INL 0.80.8V max Input Current I INL or I INH±0.005±0.005µA typ V IN = V INL or V INH±0.5±0.5µA max DYNAMIC CHARACTERISTICS 2t ON100100ns typ R L = 300 Ω, C L = 35 pF;160200145200ns max V S = ±10 V; Test Circuit 4t OFF6060ns typ R L = 300 Ω, C L = 35 pF;100150100150ns max V S = ±10 V; Test Circuit 4Charge Injection 77pC typ V S = 0V, R L = 0 Ω,C L = 10nF; Test Circuit 5OFF Isolation 8080dB typ R L = 50 Ω, f = 1 MHz;Test Circuit 6C S (OFF)66pF typ CD (OFF)66pF typ C D , C S (ON)5555pF typ POWER REQUIREMENTS V DD = +16.5 V, V SS = –16.5 V I DD0.00010.0001µA typ V IN = 0 V or 5 V12.512.5µA max I SS 0.00010.0001µA typ 12.512.5µA max I L0.00010.0001µA typ V L = +5.5 V12.512.5µA maxNOTES 1Temperature ranges are as follows: B Version: –40°C to +85°C; T Version: –55°C to +125°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.REV. A–2–ADG417–SPECIFICATIONSDual Supply 1(VDD = +15 V ؎ 10%, V SS = –15 V ؎ 10%, V L = +5 V ؎ 10%, GND = 0 V, unless otherwise noted)ORDERING GUIDEModel Temperature Range Package Options*ADG417BN –40°C to +85°C N-8ADG417BR–40°C to +85°CSO-8*N = Plastic DIP, SO = 0.15" Small Outline IC (SOIC).ADG417REV. A –3–Single Supply 1 B VersionT Version–40؇C to–55؇C toParameter+25؇C +85؇C+25؇C +125؇CUnits Test Conditions/CommentsANALOG SWITCH Analog Signal Range 0 to V DD0 to V DDV R ON4040Ω typ V D = +3 V, +8.5 V, I S = –10 mA 6070Ω max V DD = +10.8 VLEAKAGE CURRENTV DD = +13.2 VSource OFF Leakage I S (OFF)±0.1±0.1nA typ V D = 12.2 V/1 V, V S = 1 V/12.2 V;±0.25±5±0.25±15nA max Test Circuit 2Drain OFF Leakage I D (OFF)±0.1±0.1nA typ V D = 12.2 V/1 V, V S = 1 V/12.2 V;±0.25±5±0.25±15nA max Test Circuit 2Channel ON Leakage I D , I S (ON)±0.1±0.1nA typ V S = V D = 12.2 V/1 V;±0.4±5±0.4±30nA max Test Circuit 3DIGITAL INPUTSInput High Voltage, V INH 2.4 2.4V min Input Low Voltage, V INL 0.80.8V max Input Current I INL or I INH±0.005±0.005µA typ V IN = V INL or V INH±0.5±0.5µA max DYNAMIC CHARACTERISTICS 2t ON180250180250ns max R L = 300 Ω, C L = 35 pF;V S = +8 V; Test Circuit 4t OFF8511085110ns max R L = 300 Ω, C L = 35 pF;V S = +8 V; Test Circuit 4Charge Injection 1111pC typ V S = 0V, R S = 0 Ω,C L = 10nF; Test Circuit 5OFF Isolation 8080dB typ R L = 50 Ω, f = 1 MHz;Test Circuit 6C S (OFF)1313pF typ CD (OFF)1313pF typ C D , C S (ON)6565pF typ POWER REQUIREMENTS V DD = +13.2 V I DD 0.00010.0001µA typ V IN = 0 V or 5 V 12.512.5µA max I L0.00010.0001µA typ V L = +5.5 V12.512.5µA maxNOTES 1Temperature ranges are as follows: B Version: –40°C to +85°C; T Version: –55°C to +125°C.2Guaranteed by design, not subject to production test.Specifications subject to change without notice.(VDD = +12 V ؎ 10%, V SS = 0 V, V L = +5 V ؎ 10%, GND = 0 V, unless otherwise noted)Table I.Truth TableLogic Switch Condition 0ON 1OFFPIN CONFIGURATIONDIP/SOICSS LV DD NC = NO CONNECTREV. A–4–ADG417ABSOLUTE MAXIMUM RATINGS 1(T A = +25°C unless otherwise noted)V DD to V SS . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .+44 V V DD to GND . . . . . . . . . . . . . . . . . . . . . . . . . .–0.3 V to +25 V V SS to GND . . . . . . . . . . . . . . . . . . . . . . . . . .+0.3 V to –25 V V L to GND . . . . . . . . . . . . . . . . . . . . . .–0.3 V to V DD + 0.3 V Analog, Digital Inputs 2 . . . . . . . . . . . . .V SS – 2 V to V DD +2 V or 30 mA, Whichever Occurs First Continuous Current, S or D . . . . . . . . . . . . . . . . . . . . .30 mA Peak Current, S or D . . . . . . . . . . . . . . . . . . . . . . . . .100 mA (Pulsed at 1 ms, 10% Duty Cycle Max)Operating Temperature RangeIndustrial (B Version) . . . . . . . . . . . . . . . . .–40°C to +85°C Extended (T Version) . . . . . . . . . . . . . . . .–55°C to +125°C Storage Temperature Range . . . . . . . . . . . . .–65°C to +150°C Junction Temperature . . . . . . . . . . . . . . . . . . . . . . . . . .150°CPlastic Package, Power Dissipation . . . . . . . . . . . . . . .400 mW θJA , Thermal Impedance . . . . . . . . . . . . . . . . . . . .100°C/W Lead Temperature, Soldering (10 sec) . . . . . . . . . . .+260°C SOIC Package, Power Dissipation . . . . . . . . . . . . . . . .400 mW θJA , Thermal Impedance . . . . . . . . . . . . . . . . . . . .155°C/W Lead Temperature, SolderingVapor Phase (60 sec). . . . . . . . . . . . . . . . . . . . . . .+215°C Infrared (15 sec) . . . . . . . . . . . . . . . . . . . . . . . . . .+220°CNOTES 1Stresses above those listed under Absolute Maximum Ratings may cause perma-nent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those listed in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Only one absolute maximum rating may be applied at any one time.2Overvoltages at IN, S or D will be clamped by internal diodes. Current should be limited to the maximum ratings given.V D (V S )Analog voltage on terminals D, S.C S (OFF)“OFF” switch source capacitance.C D (OFF)“OFF” switch drain capacitance.C D , C S (ON)“ON” switch capacitance.t ONDelay between applying the digital control input and the output switching on.t OFFDelay between applying the digital control input and the output switching off.V INLMaximum input voltage for logic “0.”V INH Minimum input voltage for logic “1.”I INL (I INH )Input current of the digital input.Charge Injection A measure of the glitch impulse transferredfrom the digital input to the analog output during switching.Off Isolation A measure of unwanted signal couplingthrough an “OFF” channel.I DDPositive supply current.I SS Negative supply current.I L Logic supply current.TERMINOLOGYV DD Most positive power supply potential.V SS Most negative power supply potential in dual supplies. In single supply applications, it may be connected to GND.V L Logic power supply (+5 V).GND Ground (0 V) reference.S Source terminal. May be an input or an output.D Drain terminal. May be an input or an output.IN Logic control input.R ONOhmic resistance between D and S.I S (OFF)Source leakage current with the switch “OFF.”I D (OFF)Drain leakage current with the switch “OFF.”I D , I S (ON)Channel leakage current with the switch “ON.”CAUTIONESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection.Although the ADG417 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.R O N – ⍀500153010–1020–15401050–5V S , V D – VoltsFigure 1.R ON as a Function of V D (V S ): Dual Supply Voltage500153010–1020–15401050–5R O N – ⍀V S , V D – VoltsFigure 2.R ON as a Function of V D (V S ) for Different Temperatures0.02–0.030.00–0.02–0.010.01L E A K A G E C U R R E N T – n AV S , V D – VoltsFigure 3.Leakage Currents as a Function of V S (V D )10015602054008010R O N – ⍀V S , V D – VoltsFigure 4.R ON as a Function of V D(V S ): Single Supply VoltageR O N – ⍀V S , V D – Volts10060204080Figure 5.R ON as a Function of V D (V S ) for Different Temperatures0.006–0.0040.002–0.0020.0000.004L E A K A G E C U R R E N T – n AV S , V D – VoltsFigure 6.Leakage Currents as a Function of V S (V D )Typical Performance Characteristics–ADG417REV. A –5–REV. A–6–ADG41710mA 1nA101A10nA 10100nA 101mA 10A 100A101010FREQUENCY – HzI S U P P L YFigure 7.Supply Current vs. Input Switching Frequency 050100150200250300SUPPLY VOLTAGE – Voltst – n sFigure 8.Switching Time vs. Power SupplyADG417REV. A –7–Test CircuitsTest Circuit 2.Off Leakage Test Circuit 3.On LeakageI V STest Circuit 1.On ResistanceV SV OUT V INSSV OUTTest Circuit 4.Switching TimesOUT3VV INV V SSV OUTTest Circuit 5.Charge InjectionV SS V OUTV V Test Circuit 6.Off IsolationREV. A–8–ADG417C 1974a –0–9/98P R I N T E D I N U .S .A .OUTLINE DIMENSIONSDimensions shown in inches and (mm).8-Lead Plastic DIP (N-8)PLANE0.014 (0.356)0.045 (1.15)0.325 (8.25)0.300 (7.62)0.008 (0.204)8-Lead SOIC (SO-8)(Narrow Body)؇。

ANALOG DEVICES AN-774 数据手册