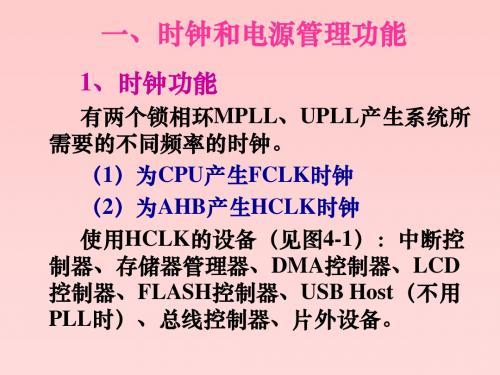

FLCK、HCLK和PCLK的关系

S3C2440时钟设置详解

S3C2440A中的时钟控制逻辑可以产生必须的时钟信号,包括CPU的FCLK,AHB总线外设的HCLK以及APB总线外设的PCLK。

S3C2440A包含两个锁相环(PLL):一个提供给FCLK、HCLK和PCLK,另一个专用于USB模块(48MHz)。

时钟控制逻辑可以不使用PLL来减慢时钟,并且可以由软件连接或断开各外设模块的时钟,以降低功耗。

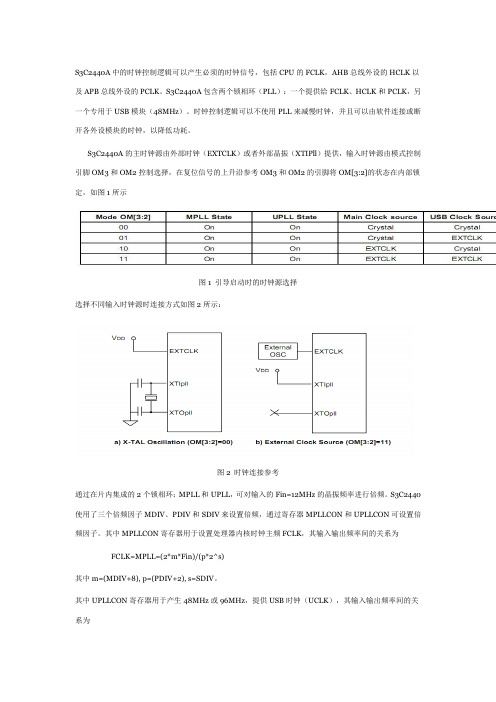

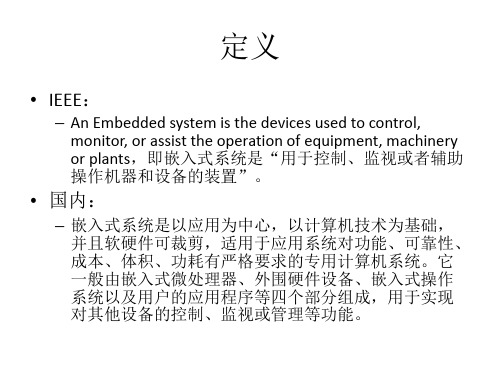

S3C2440A的主时钟源由外部时钟(EXTCLK)或者外部晶振(XTIPll)提供,输入时钟源由模式控制引脚OM3和OM2控制选择,在复位信号的上升沿参考OM3和OM2的引脚将OM[3:2]的状态在内部锁定,如图1所示图1 引导启动时的时钟源选择选择不同输入时钟源时连接方式如图2所示:图2 时钟连接参考通过在片内集成的2个锁相环:MPLL和UPLL,可对输入的Fin=12MHz的晶振频率进行倍频。

S3C2440使用了三个倍频因子MDIV、PDIV和SDIV来设置倍频,通过寄存器MPLLCON和UPLLCON可设置倍频因子。

其中MPLLCON寄存器用于设置处理器内核时钟主频FCLK,其输入输出频率间的关系为FCLK=MPLL=(2*m*Fin)/(p*2^s)其中m=(MDIV+8), p=(PDIV+2), s=SDIV。

其中UPLLCON寄存器用于产生48MHz或96MHz,提供USB时钟(UCLK),其输入输出频率间的关系为UCLK=UPLL=(m * Fin) / (p * 2^s)其中m=(MDIV+8), p=(PDIV+2), s=SDIV。

手工计算相对复杂些,我们可以根据欲得到的主频FCLK大小,直接通过查表来获知各倍频因子的设置参数,详见。

S3C2440的数据手册中提供了一个表格来查询各个输出频率和输入频率所对应的MPLL中参数m、p和s 的值,使用的时候最好只使用该表格中推荐的数值。

图3 PLL真值表通过图3的真值表,我们可以得到如果输入时钟为12MHz,输出时钟FCLK为405MHz,可以选择MDIV 为127,PDIV为2,SDIV为1。

嵌入式大纲

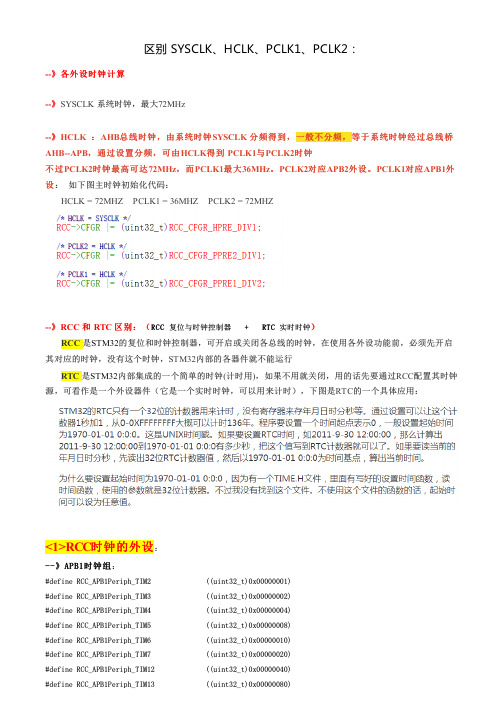

• IEEE:

– An Embedded system is the devices used to control, monitor, or assist the operation of equipment, machinery or plants,即嵌入式系统是“用于控制、监视或者辅助 操作机器和设备的装置”。

• 内核的结构往往可分为单内核(monolithic kernel), 微内核(microkernel), 超微内核(nanokernel),以 及外核(exokernel)等。 • 超微内核与外内核等其他结构是在二十世纪末的 时候在理论界发展起来的,大部分时候在实验室 里生存; • 而自二十世纪八十年代起, 大部分理论研究都集 中在以微内核为首的“新兴”结构之上;同时, 在应用领域之中, 以单内核结构为基础的操作系 统却一直占据着主导地位。图5-9是单内核操作系 统和微内核操作系统结构比较示意图。

• • • • •

1)FLCK、HCLK和PCLK的关系 S3C2440有三个时钟FLCK、HCLK和PCLK s3c2440官方手册上说P7-8写到: FCLK is used by ARM920T,内核时钟,主频。 HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD controller, the DMA and USB host block. 也就是总线时钟,包括USB时钟。 • PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,ADC, UART, GPIO, RTC and SPI.即IO接口时 钟,例如串口的时钟设置就是从PCLK来的;

[经验]arm9时钟及其设置

![[经验]arm9时钟及其设置](https://img.taocdn.com/s3/m/75f4d858777f5acfa1c7aa00b52acfc789eb9fa8.png)

左上角的那个圈中的EX TCLK与OSC这两个是arm的时钟来源,EX TCLK是外部时钟,OSC是晶体。

通过OM[2:3]来决定是用哪种方式;00OM[2:3]由硬件决定,一般接地,即为00,使用外部晶振Fin000这是arm的时钟集成模块,主要想介绍关于arm的时钟体系.00S3C2440 有2个PLL(锁相环),一个是mpll,一个是upll000pll(锁相环)00是一种产生时钟频率的东西,通常产生时钟频率都是使用晶振(晶体振荡器),不过由于频率固定或者生产成本高等一系列的原因,才产生出pll。

pll合成器有外部晶体和对晶体的特定频率加班或者分频的集成pll电路。

可以看出,pll可以在本身晶体的限制下自己diy要的频率,而且相对成本也不会很高。

000通过设置MPLLCON UPLLCON00Mpll=(2*m*Fin)/(p*(2^s))不能超过32位Upll = ( m × Fin ) / ( p × 2^s ) 00m=(MDIV+8) p=(PDIV+2) s=SDIV00MPLL通过寄存器CLKDIVN分频000会产生3中种时钟频率:FCLK,HCLK,PCLK000FCLK(CPU的频率):主要用于cpu核00HCLK:用于AHB(高速的外设总线) 通过设置CLKDIVN的【2:1】和CAMDIVN【9或者8】000PCLK:用于低速外围设备总线要先设置HCLK,再由CLKDIVN的0位决定PCLK是HCLK的1分频还是2分频000upll用于usb外设000CLKCON为时钟控制寄存器,用于使能各个模块的时钟000具体内核时钟是FLCK还是HCLK通过摄像头时钟分频(CAMDIVN)寄存器的第12位控制00这幅图让我们知道了arm时钟的产生来源,以及一系列的过程.000当arm通电的使用,FCLK不是有mpll来决定的,而是有FIN(外部输入时钟),当nRESET高电平的时候,PLL开始进行设置,这个时候OM[2:3]已经锁定了,"PLL is configured by S/Y first time" 这个地方就是PLL的寄存器都已经被设置好的时候,至于LOCKTIME是什么,这个是PLL要输出稳定的频率所需要的时候,这个时候的FCLK为0,也就是cpu这个时候是不工作的。

STM32区别 SYSCLK和HCLK和PCLK1和PCLK2

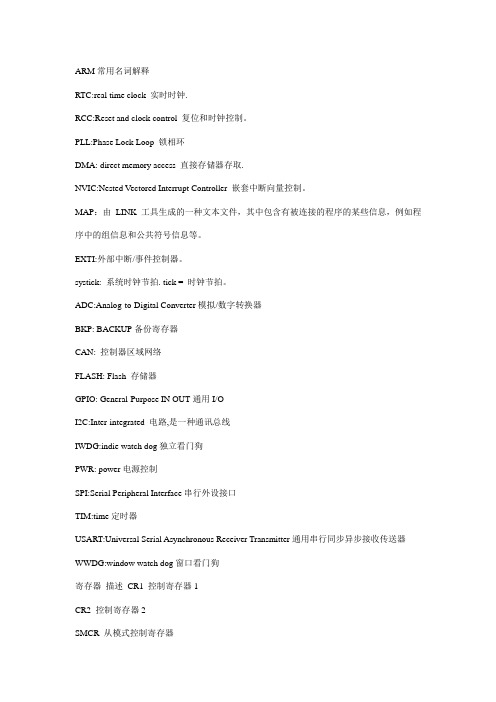

区别 SYSCLK、HCLK、PCLK1、PCLK2:--》各外设时钟计算--》SYSCLK 系统时钟,最大72MHz--》HCLK :AHB 总线时钟,由系统时钟SYSCLK 分频得到,分频得到,一般不分频,一般不分频,等于系统时钟经过总线桥等于系统时钟经过总线桥AHB--APB ,通过设置分频,可由HCLK 得到 PCLK1与PCLK2时钟不过PCLK2时钟最高可达72MHz ,而PCLK1最大36MHz 。

PCLK2对应APB2外设。

PCLK1对应APB1外设: 如下图主时钟初始化代码:HCLK = 72MHZ PCLK1 = 36MHZ PCLK2 = 72MHZ--》RCC 和 RTC 区别:(RCC RCC 复位与时钟控制器 + RTC + RTC 实时时钟)RCC 是STM32的复位和时钟控制器,可开启或关闭各总线的时钟,在使用各外设功能前,必须先开启其对应的时钟,没有这个时钟,STM32内部的各器件就不能运行RTC 是STM32内部集成的一个简单的时钟(计时用),如果不用就关闭,用的话先要通过RCC 配置其时钟源,可看作是一个外设器件(它是一个实时时钟,可以用来计时),下图是RTC 的一个具体应用:<1>RCC 时钟的外设:--》APB1时钟组:#define RCC_APB1Periph_TIM2 ((uint32_t)0x00000001)#define RCC_APB1Periph_TIM3 ((uint32_t)0x00000002)#define RCC_APB1Periph_TIM4 ((uint32_t)0x00000004)#define RCC_APB1Periph_TIM5 ((uint32_t)0x00000008)#define RCC_APB1Periph_TIM6 ((uint32_t)0x00000010)#define RCC_APB1Periph_TIM7 ((uint32_t)0x00000020)#define RCC_APB1Periph_TIM12 ((uint32_t)0x00000040)#define RCC_APB1Periph_TIM13 ((uint32_t)0x00000080)#define RCC_APB1Periph_TIM14 ((uint32_t)0x00000100) #define RCC_APB1Periph_WWDG ((uint32_t)0x00000800) #define RCC_APB1Periph_SPI2 ((uint32_t)0x00004000) #define RCC_APB1Periph_SPI3 ((uint32_t)0x00008000) #define RCC_APB1Periph_USART2 ((uint32_t)0x00020000) #define RCC_APB1Periph_USART3 ((uint32_t)0x00040000) #define RCC_APB1Periph_UART4 ((uint32_t)0x00080000) #define RCC_APB1Periph_UART5 ((uint32_t)0x00100000) #define RCC_APB1Periph_I2C1 ((uint32_t)0x00200000) #define RCC_APB1Periph_I2C2 ((uint32_t)0x00400000) #define RCC_APB1Periph_USB ((uint32_t)0x00800000) #define RCC_APB1Periph_CAN1 ((uint32_t)0x02000000) #define RCC_APB1Periph_CAN2 ((uint32_t)0x04000000) #define RCC_APB1Periph_BKP ((uint32_t)0x08000000) #define RCC_APB1Periph_PWR ((uint32_t)0x10000000) #define RCC_APB1Periph_DAC ((uint32_t)0x20000000) #define RCC_APB1Periph_CEC ((uint32_t)0x40000000)--》APB2时钟组时钟组:#define RCC_APB2Periph_AFIO ((uint32_t)0x00000001) #define RCC_APB2Periph_GPIOA ((uint32_t)0x00000004) #define RCC_APB2Periph_GPIOB ((uint32_t)0x00000008) #define RCC_APB2Periph_GPIOC ((uint32_t)0x00000010) #define RCC_APB2Periph_GPIOD ((uint32_t)0x00000020) #define RCC_APB2Periph_GPIOE ((uint32_t)0x00000040) #define RCC_APB2Periph_GPIOF ((uint32_t)0x00000080) #define RCC_APB2Periph_GPIOG ((uint32_t)0x00000100) #define RCC_APB2Periph_ADC1 ((uint32_t)0x00000200) #define RCC_APB2Periph_ADC2 ((uint32_t)0x00000400) #define RCC_APB2Periph_TIM1 ((uint32_t)0x00000800) #define RCC_APB2Periph_SPI1 ((uint32_t)0x00001000) #define RCC_APB2Periph_TIM8 ((uint32_t)0x00002000) #define RCC_APB2Periph_USART1 ((uint32_t)0x00004000) #define RCC_APB2Periph_ADC3 ((uint32_t)0x00008000) #define RCC_APB2Periph_TIM15 ((uint32_t)0x00010000) #define RCC_APB2Periph_TIM16 ((uint32_t)0x00020000) #define RCC_APB2Periph_TIM17 ((uint32_t)0x00040000) #define RCC_APB2Periph_TIM9 ((uint32_t)0x00080000) #define RCC_APB2Periph_TIM10 ((uint32_t)0x00100000) #define RCC_APB2Periph_TIM11 ((uint32_t)0x00200000)。

分子间作用力知乎

分子间作用力知乎分子间作用力是指分子之间相互作用的力量,它在物质的结构和性质中起着重要的作用。

本文将从分子间作用力的定义、分类、作用机制以及在生活和科学研究中的应用等方面展开讨论。

一、分子间作用力的定义分子间作用力是指分子之间由于电荷分布的不均匀而产生的相互吸引或排斥的力。

它是由于原子核带正电荷,而电子带负电荷,导致电荷分布不均匀,使分子具有极性或非极性,从而产生相互作用的力。

二、分子间作用力的分类分子间作用力主要分为三种类型:范德华力、氢键和离子键。

1. 范德华力:范德华力是分子间最常见的作用力之一,它是由于电子云的运动而产生的。

范德华力分为两种类型:吸引力和排斥力。

吸引力是由于两个分子之间的电子云相互重叠而产生的,而排斥力则是由于两个电子云的相互排斥而产生的。

2. 氢键:氢键是一种特殊的分子间作用力,它是由于氢原子与较电负的原子(如氧、氮和氟)之间的相互作用而产生的。

氢键的作用力较强,可以影响物质的性质和结构,如水的高沸点和氨的气味等。

3. 离子键:离子键是由正负电荷之间的相互吸引而产生的分子间作用力。

它主要存在于离子晶体中,如盐和矿石等。

离子键的作用力较强,使得离子晶体具有高熔点和良好的导电性。

三、分子间作用力的作用机制分子间作用力的作用机制主要包括静电作用、极性作用和取向作用。

1. 静电作用:分子中正负电荷之间的相互作用是分子间作用力的基础。

正负电荷之间的相互吸引使得分子间距离减小,从而增强了分子间的相互作用力。

2. 极性作用:极性分子由于分子内部的电荷分布不均匀而产生极性作用。

极性分子之间的相互作用力较强,可以使物质具有独特的性质,如溶解度和沸点等。

3. 取向作用:取向作用是指通过分子间的定向排列来增强相互作用力。

取向作用可以使分子间的相互吸引力增强,从而增加物质的稳定性和结构的有序性。

四、分子间作用力在生活和科学研究中的应用分子间作用力在生活和科学研究中有着广泛的应用。

1. 生活中的应用:分子间作用力在生活中的应用非常广泛。

ARM常用名词解释20131105

ARM常用名词解释RTC:real time clock 实时时钟.RCC:Reset and clock control 复位和时钟控制。

PLL:Phase Lock Loop 锁相环DMA: direct memory access 直接存储器存取.NVIC:Nested Vectored Interrupt Controller 嵌套中断向量控制。

MAP:由LINK工具生成的一种文本文件,其中包含有被连接的程序的某些信息,例如程序中的组信息和公共符号信息等。

EXTI:外部中断/事件控制器。

systick: 系统时钟节拍. tick = 时钟节拍。

ADC:Analog-to-Digital Converter模拟/数字转换器BKP: BACKUP备份寄存器CAN: 控制器区域网络FLASH: Flash 存储器GPIO: General-Purpose IN OUT通用I/OI2C:Inter-integrated 电路,是一种通讯总线IWDG:indie watch dog独立看门狗PWR: power电源控制SPI:Serial Peripheral Interface串行外设接口TIM:time定时器USART:Universal Serial Asynchronous Receiver Transmitter通用串行同步异步接收传送器WWDG:window watch dog窗口看门狗寄存器描述CR1 控制寄存器1CR2 控制寄存器2SMCR 从模式控制寄存器DIER DMA和中断使能寄存器SR 状态寄存器EGR 事件生成寄存器CCMR1 捕获/比较模式寄存器1CCMR2 捕获/比较模式寄存器2CCER 捕获/比较使能寄存器CNT 计数寄存器PSC 预分频数寄存器ARR 自动重载寄存器CCR1 捕获/比较寄存器1CCR2 捕获/比较寄存器2CCR3 捕获/比较寄存器3CCR4 捕获/比较寄存器4DCR DMA控制寄存器DMAR DMA猝发模式下的地址寄存器RTC:real time clock实时时钟RCC:Reset and clock control 复位和时钟控制。

分子扩散模型

分子扩散模型分子扩散模型概述分子扩散是指物质在空气或液体中由高浓度区域向低浓度区域自发移动的现象。

在工业生产、环境保护和生命科学等领域中,研究分子扩散模型是非常重要的。

本文将详细介绍分子扩散模型的相关知识。

分子扩散的基本原理分子扩散是由于物质颗粒之间的热运动而引起的。

在高浓度区域,物质颗粒互相碰撞,使得一部分颗粒向低浓度区域移动。

这种移动趋势会持续到达到平衡状态,即高浓度和低浓度之间没有更多的颗粒交换。

Fick定律Fick定律是描述分子扩散过程中物质传输速率与浓度梯度之间关系的数学公式。

Fick第一定律:物质传输速率与浓度梯度成正比,方向与浓度梯度相反。

Fick第二定律:物质传输速率随时间变化率等于物质传输速率与二次导数之积。

这两个定律可以用来解决许多分子扩散问题,如物质在半透膜中的扩散、气体在大气中的扩散等。

分子扩散模型分子扩散模型是一种数学模型,用于描述物质在不同条件下的扩散过程。

常见的分子扩散模型包括:1. Fick模型:Fick第一定律和第二定律可以用来建立物质浓度与时间、位置之间的关系。

这种模型适用于研究物质在均匀介质中的扩散过程。

2. Stefan-Boltzmann模型:该模型考虑了相变过程对分子扩散的影响,适用于研究固体和液体之间相互转化时物质传输过程。

3. Kramers-Kronig模型:该模型考虑了介质中存在多个相互作用因素对分子运动的影响。

适用于研究复杂介质中物质传输过程。

4. Monte Carlo方法:该方法通过随机抽样来计算分子运动轨迹,适用于研究非均匀介质中复杂物质传输过程。

应用1. 工业生产:分子扩散模型可以用于优化化学反应过程中物质的传输和反应速率,提高生产效率。

2. 环境保护:分子扩散模型可以用于研究大气、水体中污染物的传输和扩散规律,为环境保护提供科学依据。

3. 生命科学:分子扩散模型可以用于研究细胞膜、蛋白质等生物大分子的传输和反应过程,为药物设计和治疗提供理论支持。

单片机 各种时钟

AHB (HCLK) 时钟 = SYSCLK = 72MHz

APB2(PCLK2)时钟 = AHB时钟 = 36MHz

APB1(PCLK1)时钟 = AHB 1/2时钟 = 72MHzADC时钟 = PCLK2 1/4 = 9MHzPLL时钟 = HSE*9 = 72MHz

2、HSE:高速外部时钟信号 精度高 来源(1)HSE外部晶体/陶瓷谐振器(晶振) (2)HSE用户外部时钟

3、LSE:低速外部晶体 32.768kHz 主要提供一个精确的时钟源 一般作为RTC时钟使用

stm32单片机的将时钟信号(例如HSE)经过分频或倍频(PLL)后,得到系统时钟,系统时钟经过分频,产生外设所使用的时钟。

时钟是STM32单片机的脉搏,是单片机的驱动源。使用任何一个外设都必须打开相应的时钟。这样的好处就是,如果不使用一个外设的时候,就把它的时钟关掉,从而可以降低系统的功耗,达到节能,实现低功耗的效果。

STM32单片机的时钟可以由以下3个时钟源提供:

1、HSI:高速内部时钟信号 stm32单片机内带的时钟 (8M频率) 精度较差

③、LSI是低速内部时钟,RC振荡器,频率为40kHz。

④、LSE是低速外部时钟,接频率为32.768kHz的石英晶体。

⑤、PLL为锁相环倍频输出,其时钟输入源可选择为HSI/2、HSE或者HSE/2。倍频可选择为2~16倍,但是其输出频率最大不得超过72MHz。

系统时钟SYSCLK,它是供STM32中绝大部分部件工作的时钟源。系统时钟可选择为PLL输出、HSI或者HSE。系统时钟最大频率为72MHz,它通过AHB分频器分频后送给各模块使用,AHB分频器可选择1、2、4、8、16、64、128、256、512分频。其中AHB分频器输出的时钟送给5大模块使用:

ARM9时钟说明

S3C2440的时钟设置时间:一个嵌入式系统中,晶振就像心脏。

必须先确定晶振,设置好系统的时钟,WDT,UART,PWM,TIMER等模块才能正常工作。

和51系列单片机相比,S3C2440的时钟电路很复杂。

首先通过引脚OM2,OM3来选择时钟源。

以TQ2440开发板为例,OM2,OM3都接地,外接12M晶振,主时钟源和USB时钟源都是外部晶振。

S3C2440具有2个PLL(Phase Locked Loop:用来产生高频的电路),一个是MPLL, 用于产生FCLK,HCLK,PCLK三种频率,这三种频率分别有不同的用途:FCLK是CPU提供的时钟信号,如果提到CPU的主频是400MHz,就是指的这个时钟信号。

HCLK是为AHB总线提供的时钟信号,Advanced High-performance Bus,主要用于高速外设,比如内存控制器,中断控制器,LCD控制器,DMA 以及USB host 。

PCLK是为APB总线提供的时钟信号,Advanced Peripherals Bus,主要用于低速外设,比如WATCHDOG,IIS, I2C,SDI/MMC, GPIO,RTC ,UART,PWM,ADC and SPI等等。

另外一个是UPLL,专门用于驱动USB host/Device。

并且驱动USB host/Device的频率必须为48MHz。

时钟电路相关寄存器总共有7个,下面分别介绍。

MPLLCON(0X4C00 0004)和UPLLCON(0X4C00 0008)这两个寄存器用来设置主锁相环产生的时钟和USB锁相环产生的时钟。

MPLL=(2*m*Fin)/(p*2^s) UPLL=(m*Fin)/(p*2^s)其中m=(MDIV+8),p=(PDIV+2),s=SDIVP,M范围:1<=P<=62,1<=M<=248注意:MDIV【19:12】,PDIV【9:4】,SDIV【1:0】,当设置MPLL和UPLL值的时候,需要先设置UPLL再设置MPLL。

fick第一定律

fick第一定律菲克定律是阿道夫·菲克(Adolf Fick)于1855年提出的,指在不依靠宏观的混合作用发生的传质现象时,描述分子扩散过程中传质通量与浓度梯度之间关系的定律菲克定律包括两个内容:(1)早在1855年,菲克就提出了:在单位时间内通过垂直于扩散方向的单位截面积的扩散物质流量(称为扩散通量Diffusion flux,用J表示)与该截面处的浓度梯度(Concentration gradient)成正比,也就是说,浓度梯度越大,扩散通量越大。

这就是菲克第一定律。

(2)菲克第二定律是在第一定律的基础上推导出来的。

菲克第二定律指出,在非稳态扩散过程中,在距离x处,浓度随时间的变化率等于该处的扩散通量随距离变化率的负值。

应用菲克定律里的稳态扩散和非稳态扩散菲克第一定律只适应于J和C不随时间变化——稳态扩散(Steady-state diffusion)的场合。

所谓稳定扩散是指扩散过程中扩散物质的浓度分布不随时间变化的扩散过程,这类问题可直接用菲克第一定律解决。

对于稳态扩散也可以描述为:在扩散过程中,各处的扩散组元的浓度C只随距离x变化,而不随时间t变化,每一时刻从前边扩散来多少原子,就向后边扩散走多少原子,没有盈亏,所以浓度不随时间变化。

实际上,大多数扩散过程都是在非稳态条件下进行的。

不稳定扩散是指扩散过程中扩散物质的浓度分布随时间变化的一类扩散过程。

典型不稳定扩散中典型的边界条件可分为两种情况:第一种情况是在整个扩散中扩散质点在晶体表面的浓度C0保持不变;第二种情况是一定量的扩散物质Q由表面向内部扩散。

不稳定扩散(Nonsteady-state diffusion)的特点是:在扩散过程中,J随时间和距离变化。

通过各处的扩散通量J随着距离x在变化,而稳态扩散的扩散通量则处处相等,不随时间而发生变化。

对于非稳态扩散,就要应用菲克第二定律了。

arm9时钟频率、主频设置[说明]

![arm9时钟频率、主频设置[说明]](https://img.taocdn.com/s3/m/3c9ad855326c1eb91a37f111f18583d048640f51.png)

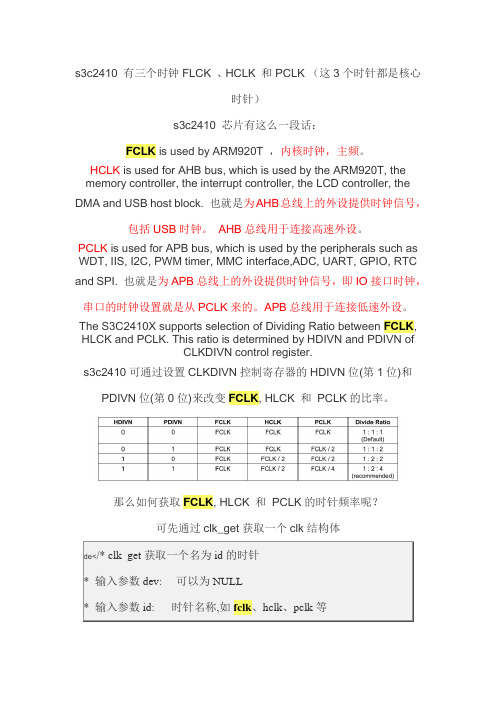

ARM9时钟频率、主频设置关于S3C2440时钟设置的理解ADS1.2中关于时钟的C代码ChangeMPllValue((mpll_val>>12)&0xff, (mpll_val>>4)&0x3f, mpll_val&3);ChangeClockDivider(key, 12);1)FLCK、HCLK和PCLK的关系S3C2440有三个时钟FLCK、HCLK和PCLKs3c2440官方手册上说P7-8写到:FCLK is used by ARM920T,内核时钟,主频。

HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD controller, the DMA and USB host block. 也就是总线时钟,包括USB时钟。

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,ADC, UART, GPIO, RTC and SPI.即IO接口时钟,例如串口的时钟设置就是从PCLK来的;那么这三个时钟是什么关系呢?这三个时钟通常设置为1:4:8,1:3:6的分频关系,也就说如果主频FLCK是400MHz,按照1:4:8的设置,那么HLCK是100MHz,PLCK是50MHz寄存器CLKDIVN表明并设置了这三个时钟的关系void ChangeClockDivider(int hdivn,int pdivn){// hdivn,pdivn FCLK:HCLK:PCLK// 0,0 1:1:1// 0,1 1:1:2// 1,0 1:2:2// 1,1 1:2:4// 2,0 1:4:4// 2,1 1:4:8// 3,0 1:3:3// 3,1 1:3:6rCLKDIVN = (hdivn<<1) | pdivn;if (hdivn == 2)rCAMDIVN = (rCAMDIVN & ~(3<<8)) | (1<<9);if (hdivn == 3)rCAMDIVN = (rCAMDIVN & ~(3<<8)) | (1<<8);}如果CLKDIVN设置为0x5,那么比例即为1:4:8,前提是CAMDIVN[9]为0.2)输入时钟FIN与主频FCLK的关系现代的CPU基本上都使用了比主频低的多的时钟输入,在CPU内部使用锁相环进行倍频。

ARM_5 时钟电源

4、时钟控制寄存器(CLKCON续3)

字段名 位 意 义 控制HCLK给LCDC时钟。 0:禁止;1:允许 控制HCLK给Flash C时钟。 0:禁止;1:允许 控制进入断电模式。 0:禁止;1:进入断电模式 初值

LCDC

NAND Flash Controller POWEROFF

5

4 3

1

1 0

(3)空闲模式:

停止为CPU提供时钟,CPU不工作 (其外设均工作)。 退出方法:任何中断请求可唤醒CPU 工作,退出空闲模式。

(4)断电模式:

时钟模块断电,除了唤醒电路之外所 有部分均不供电。系统需分成两部分供 电。此模式功耗最低。必须设置有外中断 退出方法:用中断唤醒。(1)外部中 断EINT0---15;(2)实时钟报警中断。

EXT/10 EXT/10 EXT/12 EXT/12 EXT/14 EXT/14

说明: 3、USB的UCLK均为48MHz。

四、S3C2410时钟及电源管理应用

1、锁相环的应用

锁相环主要功能是提供系统内部的运 行时钟。应用时注意以下问题: (1)系统复位后必须写一次控制寄存 器MPLLCON、UPLLCON才能使其正常 工作。即便是不改变其值也要写一次,虽 然复位后MPLL、UPLL均是使能的。

4、时钟控制寄存器(CLKCON续1)

字段名

ADC RTC

位

15 14

GPIO

UART2 UART1

13

12 11

意 义 初值 控制PCLK给ADC时钟 1 0:禁止;1:允许 控制PCLK给RTC时钟 1 0:禁止;1:允许 控制PCLK给GPIO时钟 1 0:禁止;1:允许 控制PCLK给UART2时钟 1 0:禁止;1:允许 控制PCLK给UART1时钟 1 0:禁止;1:允许

fick定律全

(有浓度变化)

➢(2)根据扩散方向

下坡扩散:原子由高浓度处向低浓度处进行的扩散。 上坡扩散:原子由低浓度处向高浓度处进行的扩散。

➢(3)根据是否出现新相

原子扩散:扩散过程中不出现新相。 反应扩散:有新相形成的扩散过程。

➢ (4)按原子的扩散方向分: 体扩散:在晶粒内部进行的扩散 短路扩散:表面扩散、晶界扩散、位错扩散等 短路扩散的扩散速度比体扩散要快得多

三、铸锭的均匀化处理

均匀化退火时溶质浓 度分布示意图如下:

铸锭枝晶偏析及均匀化 退火时的溶质浓度分布变化

设溶质浓度沿x方向为正弦曲线分布, 周期为2π, 则曲线上任一点(x)的初始 浓度C可表示为:

扩散过程的初始条件为

由扩散第二方程,可求得其正弦解为

上式表明,均匀化扩散过程中正弦曲线峰值的衰减情况。若用 表示枝晶偏析峰值衰减的程度

析、均匀化退火、冷变形后的回复和再结晶、固态相变、化学热处 理、烧结、氧化、蠕变等等。

扩散:由构成物质的微粒(离子、原子、分子)的热运动而产生的 物质迁移现象称为扩散。扩散的宏观表现是物质的定向输送。

扩散的分类

➢ (1)根据有无浓度变化

自扩散:原子经由自己元素的晶体点阵而迁移的扩散。

(纯金属或固溶体的晶粒长大)(无浓度变化)

则上式可写为

影响衰减程度的主要因素是枝晶间距l0/2、D、t

(减少偏析的措施??课堂讨论)

四、扩散方程的误差函数解

1、半无限长棒中的扩散模型

实际意义?

低碳钢的渗碳处理,材料的原始含碳量为C0,热处理时外界条件保 证其表面的碳含量始终维持在CP(碳势),经过一段时间后,求材料 的表面附近碳含量的情况。

击剑术语 flick

击剑术语 flick

在击剑术中,flick是一种技巧,用于迷惑对手并准确攻击。

它之所以被称为flick,是因为剑的尖端迅速而轻巧地移动,以便打中对手。

flick的关键在于快速而精确地变化剑的角度,从而产生迷惑性的攻击。

这种技巧可以通过突然改变方向和迅速用力量产生剑尖的抖动来实现。

与其他技巧不同,flick并不依赖于力量,而更多地依赖于速度和灵敏度。

当一名击剑手成功地使用flick时,对手很难预测并防范这一攻击,因为它的速度和轻巧使得击中的准确性更高。

虽然flick 在击剑比赛中非常有效,但它也需要大量的练习和技术来掌握。

planck定律

planck定律

【引言】

普朗克定律是量子力学的重要基石之一,由德国物理学家马克斯·普朗克于1900年提出。

这一定律的提出,标志着量子物理学的诞生,为现代科学的发展奠定了基础。

普朗克定律的核心观点是,能量不是连续的,而是以离散的“量子”形式存在。

这一观点在当时引起了巨大的轰动,颠覆了人们对物质世界的认识。

【定义和公式】

普朗克定律是指,能量的辐射和吸收不是连续的,而是以最小能量单位——“量子”的形式发生。

这个最小能量单位被称为普朗克能量,用符号E表示,公式为:E = hf,其中h为普朗克常数,f为辐射的频率。

【应用领域】

普朗克定律在多个领域有广泛的应用,如黑体辐射、光电效应、康普顿散射等。

在这些领域,普朗克定律为科学家们提供了一种新的研究方法,使他们能够更好地理解和解释实验现象。

【局限性及其改进】

尽管普朗克定律对于解释量子现象具有重要意义,但它在某些情况下也存在局限性。

例如,在处理强引力场问题时,普朗克定律无法给出满意的结果。

为了解决这一问题,科学家们提出了量子引力理论等改进措施。

【结论】

总的来说,普朗克定律是现代科学的重要基石,它揭示了量子世界的奥

秘,为人类认识自然提供了新的视角。

从黑体辐射到光电效应,再到量子引力理论,普朗克定律在现代科学的各个领域都发挥着至关重要的作用。

fick扩散定律名词解释

fick扩散定律名词解释

嘿,你知道什么是 Fick 扩散定律吗?这可真是个超有意思的东西呢!Fick 扩散定律呀,就好比是物质世界里的一场奇妙旅行。

比如说,想

象一下有一群小粒子,它们就像一群调皮的小精灵,在一个大大的空

间里跑来跑去(就像空气中的分子在不停地运动)。

Fick 扩散定律说的就是这些小粒子从高浓度的地方向低浓度的地方

扩散的规律。

这多神奇呀!好比你在一个充满香气的房间里,香气会

从香味浓的地方慢慢扩散到整个房间,让每个角落都能闻到,这其实

就是一种扩散现象呀(这不就和 Fick 扩散定律很像嘛)!

它可不是随便说说的哦,在很多领域都超级重要呢!在生物学里,

细胞之间的物质交换就遵循着这个定律;在化学中,不同物质的混合

和扩散也和它息息相关。

难道你不觉得这很厉害吗?

你想想看,如果没有 Fick 扩散定律,那这个世界会变成什么样呢?是不是很多事情都没办法顺利进行啦?就像如果香气不会扩散,那我

们怎么能在进入房间的第一时间就闻到香味呢(这简直太不可思议了吧)!

Fick 扩散定律就像是一把神奇的钥匙,打开了我们理解物质运动和

交换的大门。

它让我们能更好地研究和解释各种自然现象,帮助我们

在不同的领域取得进步和突破。

所以呀,可千万别小瞧了这个定律哦!它真的是超级重要,超级有趣的呢!

我的观点就是:Fick 扩散定律是科学世界里的一颗璀璨明珠,它虽然看似简单,却蕴含着无尽的奥秘和价值。

7 时钟和功率管理

第七章时钟和功率管理概述时钟和功率管理模块由三部分组成:时钟控制,USB控制和功率控制。

S3C2410A的时钟控制逻辑能够产生系统所需要的时钟,包括CPU的FCLK,AHB总线接口的HCLK,和APB总线接口的PCLK。

S3C2410A有两个PLL,一个用于FCLK,HCLK,PCLK,另一个用于USB模块(48MHZ)。

时钟控制逻辑能够由软件控制不将PLL连接到各接口模块以降低处理器时钟频率,从而降低功耗。

S3C2410A有各种针对不同任务提供的最佳功率管理策略,功率管理模块能够使系统工作在如下4种模式:正常模式,低速模式,空闲模式和掉电模式。

正常模式:功率管理模块向CPU和所有外设提供时钟。

这种模式下,当所有外设都开启时,系统功耗将达到最大。

用户可以通过软件控制各种外设的开关。

例如,如果不需要定时器,用户可以将定时器时钟断开以降低功耗。

低速模式:没有PLL的模式。

与正常模式不同,低速模式直接使用外部时钟(XTIpll或者EXTCLK)作为FCLK,这种模式下,功耗仅由外部时钟决定。

空闲模式:功率管理模块仅关掉FCLK,而继续提供时钟给其他外设。

空闲模式可以减少由于CPU核心产生的功耗。

任何中断请求都可以将CPU从中断模式唤醒。

掉电模式:功率管理模块断开内部电源。

因此CPU和除唤醒逻辑单元以外的外设都不会产生功耗。

要执行掉电模式需要有两个独立的电源,其中一个给唤醒逻辑单元供电,另一个给包括CPU在内的其他模块供电。

在掉电模式下,第二个电源将被关掉。

掉电模式可以由外部中断EINT[15:0]或RTC唤醒。

功能描述时钟结构图7-1描述了时钟架构的方块图。

主时钟源由一个外部晶振或者外部时钟产生。

时钟发生器包括连接到一个外部晶振的振荡器和两个PLL(MPLL和UPLL)用于产生系统所需的高频时钟。

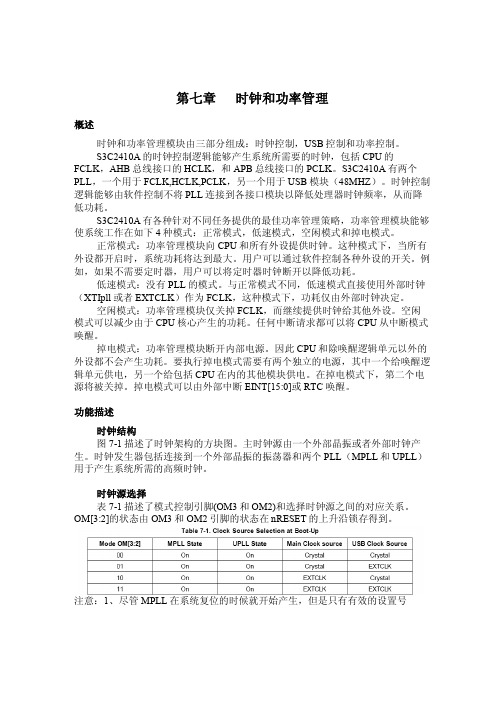

时钟源选择表7-1描述了模式控制引脚(OM3和OM2)和选择时钟源之间的对应关系。

OM[3:2]的状态由OM3和OM2引脚的状态在nRESET的上升沿锁存得到。

s3c2410时钟信号:FCLK、HCLK和PCLK

s3c2410 有三个时钟FLCK 、HCLK 和PCLK (这3个时针都是核心时针)s3c2410 芯片有这么一段话:FCLK is used by ARM920T ,内核时钟,主频。

HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD controller, the DMA and USB host block. 也就是为AHB总线上的外设提供时钟信号,包括USB时钟。

AHB总线用于连接高速外设。

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,ADC, UART, GPIO, RTC and SPI. 也就是为APB总线上的外设提供时钟信号,即IO接口时钟,串口的时钟设置就是从PCLK来的。

APB总线用于连接低速外设。

The S3C2410X supports selection of Dividing Ratio between FCLK, HLCK and PCLK. This ratio is determined by HDIVN and PDIVN ofCLKDIVN control register.s3c2410可通过设置CLKDIVN控制寄存器的HDIVN位(第1位)和PDIVN位(第0位)来改变FCLK, HLCK 和PCLK的比率。

那么如何获取FCLK, HLCK 和PCLK的时针频率呢?可先通过clk_get获取一个clk结构体再将clk_get返回的clk结构体传递给clk_get_rate,获取该时钟的频率一个例子:这里出现了另一个时针uclk,专门给usb供给时针信号。

fick扩散定律公式的结果

fick扩散定律公式的结果在研究物理和化学中,Fick扩散定律是描述物质扩散过程的基本定律之一。

Fick扩散定律给出了扩散速率和物质浓度梯度之间的关系,它的公式结果对于理解和预测扩散现象具有重要意义。

Fick扩散定律中的公式结果可以通过以下方式得到:1. Fick第一扩散定律:Fick第一扩散定律描述了扩散物质的浓度随时间和空间的变化关系。

根据Fick第一扩散定律,单位时间内通过单位面积的扩散通量与物质浓度梯度成正比。

可以用下面的公式表示:J = -D(dC/dx)其中,J表示单位时间内通过单位面积的扩散通量,D表示扩散系数,dC/dx表示物质浓度梯度。

2. Fick第二扩散定律:Fick第二扩散定律描述了在非稳态条件下的扩散现象。

根据Fick第二扩散定律,物质的浓度随时间和空间的变化满足扩散方程。

可以用下面的公式表示:∂C/∂t = D(∂^2C/∂x^2)其中,∂C/∂t表示物质浓度随时间的变化率,∂^2C/∂x^2表示物质浓度梯度的梯度。

通过上述公式,我们可以计算出扩散速率和物质浓度梯度之间的关系。

通过测量和分析这些参数,我们可以更好地理解和控制扩散现象。

Fick扩散定律的结果可以应用于许多领域。

在材料科学中,我们可以利用Fick 扩散定律来优化材料的性能和制备过程。

例如,在聚合物材料的制备过程中,通过控制物质的扩散过程,可以得到所需的材料结构和性能。

此外,Fick扩散定律也在生物学和医学领域有重要应用。

例如,在生物体内,许多生理过程依赖于物质的扩散。

通过研究和理解Fick扩散定律的结果,我们可以更好地理解生物体内的物质交换过程,从而为疾病治疗和药物传递提供指导。

总结起来,Fick扩散定律是描述物质扩散过程的基本定律之一。

它的结果给出了扩散速率和物质浓度梯度之间的关系,可以应用于各种领域,从材料科学到生物医学。

通过研究和应用Fick扩散定律的公式结果,我们可以更好地理解并控制扩散现象,为科学研究和技术应用提供基础。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

PCLK is used for APB bus, which is used by the peripherals such as WDT, IIS, I2C, PWM timer, MMC interface,ADC, UART, GPIO, RTC and SPI.即IO接口时钟,例如串口的时钟设置就是从PCLK来的;

2410的时钟和电源管理

概述

时钟和电源管理模块由3部分组成:时钟控制、USB控制、电源控制。

时钟控制部分产生3种时钟信号:CPU用的FCLK,AHB总线用的HCLK,APB总线用的PCLK。有2个锁相环,一个用于FCLK HCLK PCLK,另一个用于48MHz的USB时钟。可以通过不使能锁相环来达到慢速省电目的。

Idle Mode

关掉了给cpu的FCLK时钟,但外围设备时钟仍存在,任何到CPU的中断请求可以将cpu唤醒。

Power_off Mode

这种模式关掉了内部供电,仅有给wake_up部分的供电还存在。可以通过外部中断或实时时钟中断可以唤醒。

功能描述

时钟结构:主时钟源来自外部晶振XTlpll或外部时钟EXTCLK。

时钟源选择:通过OM[3: 2]的高低电平选择,现在我们采用00。OM[3:2]的状态在nRESET的上升沿锁存。尽管MPLL在上电复位后就开始工作,但是MPLL输出不作为系统时钟,只有对MPLLCON写入适当的数值后才可以。即使用户不想改变MPLLCON的值,也要重新写一遍才能使其起作用。

时钟控制逻辑:时钟控制逻辑决定要使用的时钟源,当锁相环被设置为一个新的值时,时钟控制逻辑切断FCLK直到PLL输出稳定。时钟控制逻辑在上电复位或从power_down状态启动时使能。

电源管理:4种模式及特点。

Power_Off模式:外部中断EINT[15:0]或RTC alarm中断可以从该模式wakeup.

进入PowerOff模式的流程:1。将GPIO端口设置为适当的状态; 2。……….

VDDi和VDDiarm的控制:在PowerOff模式,仅VDDi和VDDiarm通过PWREN管脚控制被关闭。如果PWREN为高,VDDi和VDDiarm被外部电源提供,如果为低则关闭。 尽管VDDi,VDDiarm,VDDi_MPLL,VDDi_UPLL可能被关闭,其他电源必须被提供。

UPLL=(m*FIN)/(p*2^s) where m=(MDIV+8), p=(PDIV+2), s="SDIV",同样,可以通过查表得到一个合适的值。

最后值得一提的是,在CLKDIVN的第三位DIVN_UPLL用来设置USB时钟UCLK和UPLL的关系,如果UPLL已经是48Mhz了,那么这一位应该设置为0,表示1:1的关系,否则是1:2的关系

时钟和电源管理部分寄存器

LOCKTIME: UPLL、 MPLL 锁定时间的计数值。

MPLLCON Βιβλιοθήκη UPLLCON: 这两个寄存器都有MDIV PDIV SDIV设置,对于输入12M的晶振,有相应的推荐值,产生200M和48M的频率。

CLKCON: 为各种外围接口提供时钟。

上电复位:注意上电后必须通过设置PLLCON才能使PLL作用。

在正常操作状态下改变PLL设置:通过改变PMS的值来实现。

USB时钟控制:UCLK不起作用直到UPLL被设置。

FCLK、HCLK、PCLK:可以通过HDIVN、PDIVN、CLKDIVN来改变3种时钟的比率,推荐采用1:2:4的比率。在设置完PMS的值后,需要设置CLKDIVN寄存器,该寄存器设置的值在PLL锁定后生效,只需要1.5个HCLK即可完成比率的修改。

2)输入时钟FIN与主频FCLK的关系

现代的CPU基本上都使用了比主频低的多的时钟输入,在CPU内部使用锁相环进行倍频。对于S3C2440,常用的输入时钟FIN有两种:12MHz和16.9344MHz,那么CPU是如何将FIN倍频为FCLK的呢?

S3C2440使用了三个倍频因子MDIV、PDIV和SDIV来设置将FIN倍频为MPLL,也就是FCLK

CLKSLOW: 是否打开2个PLL。

CLKDIVN: 设置CLK、 HCLK、 PCLK比率的寄存器。

ChangeClockDivider(key, 12);

1)FLCK、HCLK和PCLK的关系

S3C2440有三个时钟FLCK、HCLK和PCLK

s3c2440官方手册上说P7-8写到:

FCLK is used by ARM920T,内核时钟,主频。

HCLK is used for AHB bus, which is used by the ARM920T, the memory controller, the interrupt controller, the LCD controller, the DMA and USB host block. 也就是总线时钟,包括USB时钟。

标签: FCLK HCLK PCLK 2410的时钟和电源管理

关于3C2440 FCLK, HCLK, PCLK的关系(转载)

ADS1.2中关于时钟的C代码

ChangeMPllValue((mpll_val>>12)&0xff, (mpll_val>>4)&0x3f, mpll_val&3);

MPLL=(2*m*FIN)/(p*2^s) where m=(MDIV+8), p=(PDIV+2), s="SDIV"

寄存器MPLLCON就是用来设置倍频因子的

理论上,你可以通过设置该寄存器来实现不同的频率,然而,由于实际存在的各种约束关系,设置一个适当的频率并不容易,手册上列出了一些常用频率的表格,

那么这三个时钟是什么关系呢?

这三个时钟通常设置为1:4:8,1:3:6的分频关系,也就说如果主频FLCK是400MHz,按照1:4:8的设置,那么HLCK是100MHz,PLCK是50MHz

寄存器CLKDIVN表明并设置了这三个时钟的关系

如果CLKDIVN设置为0x5,那么比例即为1:4:8,前提是CAMDIVN[9]为0.

EINT[15:0]启动信号: EINTn管脚必须被设置为中断管脚,在启动后,相应的EINTn管脚将不被用作启动,可以被用作外部中断请求。

电池故障信号(nBATT_FLT): 当cpu不在PowerOff模式时,nBATT_FLT将要引起低电平触发的中断。当在PowerOff模式时,nBATT_FLT信号将会禁止芯片从PowerOff模式启动,故所有的wakeup信号被屏蔽,此举用来保护系统电量低时不出现故障。

电源管理模块提供了4种模式: Normal模式、Slow模式、Idle模式、Power_Off模式。

Normal Mode

该模式下如果所有外围设备都打开时电流消耗最大,允许用户通过软件关闭外围设备达到省电目的。

Slow Mode

不采用PLL的模式,能量消耗仅取决于外时钟的频率。由外部提供的时钟源作FCLK。

例如,假设输入时钟FIN=16.9344M,MDIV=110, PDIV="3", SDIV="1",

利用上面的公式,FCLK=2*16.9344*(110+8)/((2+3)*2)=399.65

3)关于USB时钟

S3C2440有两个锁相环,一个主锁相环MPLL提供给FCLK的,另外一个UPLL是提供给USB时钟(48MHz)的,与MPLL一样,UPLL的产生也是通过UPLLCON寄存器设置分频因子得到,计算公式稍有不同: