数电第四章 组合逻辑电路的设计

合集下载

《数字电子技术基础》第五版:第四章 组合逻辑电路

74HC42

二-十进制译码器74LS42的真值表

序号 输入

输出

A3 A2 A2 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7 Y8 Y9

0 0 000 0 111111111

1 0 001 1 011111111

2 0 010 1 101111111

3 0 011 1 110111111

4 0 100 1 111011111

A6 A4 A2

A0

A15 A13 A11 A9

A7 A5 A3

A1

I7 I6 I5 I4 I3 I2 I1 I00

S

74LS 148(1)

YS

YEE Y2 Y1

Y0

XX

I7 I6 I5 I4 I3 I2 I1 I0

S

74LS 148(2)

YS

YE Y2 Y1

Y0

X

&

G3

&

G2

&

G3

Z3

Z2

Z1

&

G3

0时1部分电路工作在d0a1a0d7d6d5d4d3d2d1d074ls153d22d20d12d10d23d21s2d13d11s1y2y1a1a0在d4a0a1a2集成电路数据选择器集成电路数据选择器74ls15174ls151路数据输入端个地址输入端输入端2个互补输出端74ls151的逻辑图a2a1a02274ls15174ls151的功能表的功能表a2a1a0a将函数变换成最小项表达式b将使能端s接低电平c地址a2a1a0作为函数的输入变量d数据输入d作为控制信号?实现逻辑函数的一般步骤cpcp000001010011100101110111八选一数据选择器三位二进制计数器33数据选择器数据选择器74ls15174ls151的应用的应用加法器是cpu中算术运算部件的基本单元

数字电路与逻辑设计第四章组合逻辑电路

述问题的逻辑表达式。

第四章 组合逻辑电路

设计的一般过程:

●建立给定问题的逻辑描述 ●求出逻辑函数的最简表达式 ●选择器件并对表达式变换 ● 画出逻辑电路图

弄清楚变量及函数,得 到描述给定问题的逻辑 表达式。求逻辑表达式 有两种常用方法,即真

值表法和分析法。

求出描述设计问题的 最简表达式,使逻辑电路 中包含的逻辑门最少且连 线最少。

令: 逻辑变量A、B、C --- 分别代表参加表决的3个成员, 并约定逻辑变量取值为0表示反对,取值为1表示赞成;

逻辑函数 F---- 表示表决结果。F取值为0表示被否定,F 取值为1表示通过。

按照少数服从多数的原则可知,函数和变量的关系是:当3 个变量A、B、C中有2个或2个以上取值为1时,函数F的值为1, 其他情况下函数F的值为0。

注意:在化简这类逻辑函数时,利无关项用随意性往往 可以使逻辑函数得到更好地简化,从而使设计的电路达到更 简!

第四章 组合逻辑电路

例 设计一个组合逻辑电路,用于判别以余3码表示的1 位 十进制数是否为合数。

解 设输入变量为ABCD,输出函数为 F,当ABCD表示 的十进制数为合数(4、6、8、9)时,输出F为1,否则F为0。

目的:了解给定逻辑电路的功能,评价设计方案的优劣, 吸取优秀的设计思想、改进和完善不合理方案等。

一般步骤:

第四章 组合逻辑电路

1.写出输出函数表达式 ;

2.输出函数表达式化简;

3.列出输出函数真值表 ;

4.功能评述 。

第四章 组合逻辑电路

1. 写出输出函数表达式

根据逻辑电路图写输出函数表达式时,一般从输入端开始 往输出端逐级推导,直至得到所有与输入变量相关的输出函数 表达式为止。

第四章 组合逻辑电路

设计的一般过程:

●建立给定问题的逻辑描述 ●求出逻辑函数的最简表达式 ●选择器件并对表达式变换 ● 画出逻辑电路图

弄清楚变量及函数,得 到描述给定问题的逻辑 表达式。求逻辑表达式 有两种常用方法,即真

值表法和分析法。

求出描述设计问题的 最简表达式,使逻辑电路 中包含的逻辑门最少且连 线最少。

令: 逻辑变量A、B、C --- 分别代表参加表决的3个成员, 并约定逻辑变量取值为0表示反对,取值为1表示赞成;

逻辑函数 F---- 表示表决结果。F取值为0表示被否定,F 取值为1表示通过。

按照少数服从多数的原则可知,函数和变量的关系是:当3 个变量A、B、C中有2个或2个以上取值为1时,函数F的值为1, 其他情况下函数F的值为0。

注意:在化简这类逻辑函数时,利无关项用随意性往往 可以使逻辑函数得到更好地简化,从而使设计的电路达到更 简!

第四章 组合逻辑电路

例 设计一个组合逻辑电路,用于判别以余3码表示的1 位 十进制数是否为合数。

解 设输入变量为ABCD,输出函数为 F,当ABCD表示 的十进制数为合数(4、6、8、9)时,输出F为1,否则F为0。

目的:了解给定逻辑电路的功能,评价设计方案的优劣, 吸取优秀的设计思想、改进和完善不合理方案等。

一般步骤:

第四章 组合逻辑电路

1.写出输出函数表达式 ;

2.输出函数表达式化简;

3.列出输出函数真值表 ;

4.功能评述 。

第四章 组合逻辑电路

1. 写出输出函数表达式

根据逻辑电路图写输出函数表达式时,一般从输入端开始 往输出端逐级推导,直至得到所有与输入变量相关的输出函数 表达式为止。

数字电子技术第四章 组合逻辑电路

10

& & &

F

F AB AC AB AC

____

___

0 1

C

第三步:逻辑电路

(a)

(b)

例 5 设计一个组合电路,将 8421BCD码变换为余 3 代码。

解 这是一个码制变换问题,由于均是BCD码,故输入输出均为四个端点。

A B C D 码制 变换 电路 W X Y Z

第一步:列出真值表。

A B

& &

P

N

&

C

F

&

Q

000 001 010 011 100 101 110 111

解

第一步:写出逻辑表达式。 前级→后级 (或后级→前级 )

P AB N BC Q AC F PNQ AB BC AC AB BC AC

第二步: 列出真值表。

第三步: 逻辑功能描述——三输入变量多数表决器。

F C4 S3 S2 S3S1 C 4 S9 S1 S9 S1

S3S1

__

二进制数与8421码对应表

1 C4

A3 A 2 A1 A 0

B3 B 2 B1 B 0

四位全加器 S3 S2 S1 S0

C0

&

& &

A3 A 2 A1 A 0 B2 B1 四位全加器 F S 3′ S 2′ S 1′ S 0′

__

__

__

C i 1 Ai B i B i C i 1 Ai C i 1Ci+1 NhomakorabeaSi

≥1

&

Ai Bi

1

1

数电-第四章_组合逻辑电路

4.4 若干典型的组合逻辑集成电路

逻辑表达式:

Y2 I 7 I7 Y I 1 7 I7 Y I 7 0 I7

I7 I6 I7 I6 I5 I7 I6 I5 I 4 I6 I5 I 4 I7 I6 I7 I6 I5 I 4 I3 I7 I6 I5 I 4 I3I 2 I6 I5I 4 I3 I5I 4 I 2 I 7 I 6 I 5 I 7 I 6 I 5 I 4 I 3 I 7 I 6 I 5 I 4 I 3 I 2 I1 I 6 I 5 I 6 I 4 I 3 I 6 I 4 I 2 I1

I6

I7

ST

Y2 Y1 GND

(a) 引脚排列图

ST I0

I7 (b)

I6 I5

I4

I3

I2 I1

逻辑功能示意图

4.4 若干典型的组合逻辑集成电路

ST为选通输入端,低电平有效。YS 为选通输出端,级联使用, 高位片的YS 端与低位片的ST端连接。YS 和ST配合可以实现多 级编码器之间的优先级别的控制。YEX为优先扩展输出端,是 控制标志。 YEX =0表示是编码输出; YEX =1表示不是编码输 出。

(2)、真值表

4.4 若干典型的组合逻辑集成电路

输 入 输 出

ST

1 0 0 0 0 0 0 0 0 0

I7

I6

I5

I4

I3

I2

I1

I0

Y2

1 1 0 0

Y1

1 1 0 0

Y0

1 1 0 1

Y Y EXS

1 1 0 0 0 0 0 0 0 0 1 0 1 1 1 1 1 1 1 1

数电第4章(1)组合逻辑电路的分析与设计、全加器、编码器

(3) 画逻辑图 Z RY G RY RG YG

R

&

1

Y 1

G 1

& ≥1 Z

&

&

第四章 组合逻辑电路

[补充例3]设计一个举重裁判电路。在 A B C Y

Y 为1表示 通过,0表示 否决。

011 1

(2) 列真值表

100 0

(3) 写输出表达式并化简

101 1

Y ABC ABC ABC ABC

BC ABC ABC

110 1 111 1

BC AC AB

BC AC AB (4) 画逻辑图

第四章 组合逻辑电路

A

& AB

[补充例 1] 用与非门设计一个三B变量表决电路。

& BC

BC AC AB

BC AC AB (4) 画逻辑图

& AC

≥1 Y ≥&1 Y

第四章 组合逻辑电路

[补充例2] 设计一个交通灯故障监视电路。正常情况下,红、 黄、绿灯只有一个亮,否则为故障状态,发出报警信号。

[解] (1)逻辑抽象

输入变量: R(红) Y(黄) G(绿)

1 -- 亮 0 -- 灭

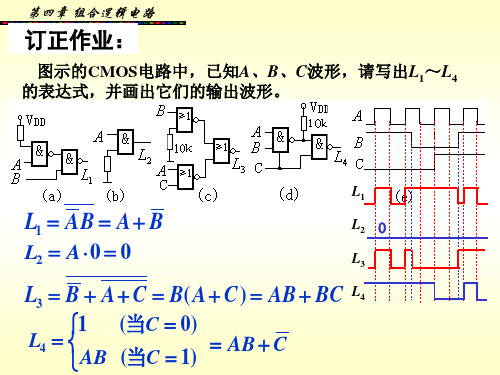

订正作业:

写出图示电路输出表达式, 说明这两个电路有何功能。

A

(当B 0)

L1 Z(高阻)(当B 1)

A

(当B 0)

L2 Z(高阻)(当B 1)

二者表达式相同,但作用不完全相同。

电路(a)是三态缓冲器,信号单向传输;

电路(b)是模拟开关,信号可双向传输。

第四章 组合逻辑电路

第四章 组合逻辑电路

4.1 4.2 组合逻辑电路的设计 4.3 常用中规模组合逻辑部件的原理和应用 4.4 组合逻辑电路中的竞争与冒险

R

&

1

Y 1

G 1

& ≥1 Z

&

&

第四章 组合逻辑电路

[补充例3]设计一个举重裁判电路。在 A B C Y

Y 为1表示 通过,0表示 否决。

011 1

(2) 列真值表

100 0

(3) 写输出表达式并化简

101 1

Y ABC ABC ABC ABC

BC ABC ABC

110 1 111 1

BC AC AB

BC AC AB (4) 画逻辑图

第四章 组合逻辑电路

A

& AB

[补充例 1] 用与非门设计一个三B变量表决电路。

& BC

BC AC AB

BC AC AB (4) 画逻辑图

& AC

≥1 Y ≥&1 Y

第四章 组合逻辑电路

[补充例2] 设计一个交通灯故障监视电路。正常情况下,红、 黄、绿灯只有一个亮,否则为故障状态,发出报警信号。

[解] (1)逻辑抽象

输入变量: R(红) Y(黄) G(绿)

1 -- 亮 0 -- 灭

订正作业:

写出图示电路输出表达式, 说明这两个电路有何功能。

A

(当B 0)

L1 Z(高阻)(当B 1)

A

(当B 0)

L2 Z(高阻)(当B 1)

二者表达式相同,但作用不完全相同。

电路(a)是三态缓冲器,信号单向传输;

电路(b)是模拟开关,信号可双向传输。

第四章 组合逻辑电路

第四章 组合逻辑电路

4.1 4.2 组合逻辑电路的设计 4.3 常用中规模组合逻辑部件的原理和应用 4.4 组合逻辑电路中的竞争与冒险

数字电路逻辑设计第四章组合逻辑电路

(4)逻辑符号(注意信号极性的表示方法)

(5)扩展举例 由两片8线—3线编码器扩展为16线—4线编码器

应用举例: 一个呼叫请求控制器,有N条输入线,连接N 个按键,请求有优先级。有唯一按键时,输出其 对应编码;有多键同时按下时,输出优先级最高 者的编码。 使用一个优先编码器,就可以满足这一电路。

(3)写出逻辑表达式 F = ABC + ABC + ABC + ABC (4)化简表达式 F = AB + AC + BC (5)因为指定用与非门 实现,所以要对表达式进行 变换。 F = AB + AC + BC = AB AC BC (6)画出电路图

也可以写或与式,再 两次求反,用或非门实现

2、输入只有原变量、使用与非门的设计

所谓输入只有原变量,没有反变量是指第一级的输入 信号只能由A、B、C、D等组成,不能出现 A B C D等。 要解决这个问题似乎很简单:将所有的反变量都加 一个反相器。 但这样简单处理的结果是门太多,为了获得最佳设 计,我们可以通过表达式变换,用尽量少的电路满足只 有原变量的要求。 例如:在只有原变量输入的条件下,实现逻辑函数 F(A,B,C,D)= m (4,5,6,7,8,9,10,11, 12,13,14) 解: 用卡诺图化简

三、译码器 译码器的工作过程与编码器相反,它将二进制编码 翻译成不同的硬件输出组合。 例如: 一个2线—4线译码器 电路如图:

(1)写出表达式 (2)列出真值表

太简单,不写了

(3)总结、归纳 通常 M 线—N线二进制译码器,满足 N=2M关系, M位二进制码输入,N条译码线输出。另有若干译码允 许端(高或低电平有效)。 当任一允许端无效时,译码器不工作,输出线全为高。 当所有允许端均有效时,译码器工作:对任一个二进 制码输入,有唯一的一条输出线为低电平,其他输出端 均为高电平。(输出线下标号=二进制码值) 按照这一原则,3线—8线二进制译码器,4线—16线 二进制译码器就很容易理解了。另外还有一些 BCD 译码 器,如4线—10线译码器。

数字电路第四章组合逻辑电路

(3)逻辑表达式:

Y A B C A B C A B C ABC A B CB C A B CB C ABC R AB BC AC AB BC AC

(4)画出电路(见仿真)

2、下图所示是具有两个输入X、Y和三个输出Z1、Z2、 Z3的组合电路。写出当X>Y时Z1 =1;X=Y时 Z2 =1;当X<Y时Z3 =1,写出电路的真值表, 求出输出方程。 解:A、列真值表: B、写出函数表达式:

可在K图中直接圈1化简得最简与或式。再对最简与或式 两次求反进行变换。 A C A B C B C

n 1 n n n n n n

B n Cn A n Cn A n B n B n C n A n Cn A n B n

C、 画出逻辑电路:

4、设计一组合电路,当接收的4位二进制数能被4整除 时,使输出为1。 A 、列真值表:数N=8A+4B+2C+D 注:0可被任何数整除 B、写逻辑函数式:画出F的K图

3、优先编码器

优先编码器常用于优先中断系统和键盘编码。与普 通编码器不同,优先编码器允许多个输入信号同时有效, 但它只按其中优先级别最高的有效输入信号编码,对级 别较低的输入信号不予理睬。

常用的MSI优先编码器有10线—4线(如74LS147)、

8线—3线(如74LS148)。

Cn 1 Cn 1 Bn Cn A n Cn A n Bn

2)、用异或门实现Dn:

An Bn C n An Bn C n An Bn C n

3)、用与非门实现 Cn+1:

Dn An Bn C n An Bn C n An BnC n An BnC n

数字电路逻辑设计第四章【可编辑PPT】

★74LS148 8-3线优先编码器 应用2

用编码器构成A/D转换器

图4.15为74LS148构 成的A/D转换器。这个 电路主要由比较器、寄 存器和编码器3部分组成。

输入信号(模拟电压), 同时加到7个比较器的反 相端,基准电源经串联 电阻分压为8级,量化单 位q=UR/7,各基准电压 分别加到比较器的同相 端。

Y S I0 N I1 N I2 N I3 N I4 N I5 N I6 N I7 N ST YEXYS ST

8线–3线优先编码器真值表如下表所示(反码形式)

输入

输出

ST IN 0 IN 1 IN 2 IN 3 IN 4 IN 5 IN 6 IN 7

Y 2 Y 1 Y 0 Y EX Y s

0 1 2 3 4 5 6 7 EN

HPRI/BIN 低位片

YS

Y0

Y1

Y2

YEX

0 1 2 3 4 5 6 7 EN

HPRI/BIN 高位片

YS

Y0

Y1

Y2

YEX

&

&

&

Y0

Y1

Y2

&

Y3

YEX

中规模优先编码器

常用的中规模优先编码器有: 8线-3线优先编码器:CT54148/CT74148、 CT54LS148/CT74LS148、CC4532 10线-4线优先编码器:CT54147/CT74147、 CT54LS147/CT74LS147、CC40147

74LS148是8-3线优先编码器

74LS148编码器功能表

输入

EI I7 I6 I5 I4 I3 I2 I1 I0

1 XXXXXXXX 0 1 1 1 1 1 11 1 0 0 XXXXXXX 0 1 0 XXXXXX 0 1 1 0 XXXXX 0 1 1 1 0 XXXX 0 1 1 1 1 0 XXX 0 1 1 1 1 1 0 XX 01111110X 011111110

数字逻辑课件第四章组合逻辑电路

波形图分析

波形图验证

通过对比理论计算和实验测量的波形 图,可以验证组合逻辑电路的功能是 否正确实现。

通过分析波形图,可以了解电路的工 作过程和特性,如信号的延迟时间、 信号的稳定性等。

组合逻辑电路的功能验证

功能验证方法

组合逻辑电路的功能验证可以通 过对比理论计算和实验测量的结 果来进行,常用的方法有仿真测

数据通路

数据通路是计算机中用于传输和处理数据的电路。数据通路中的组合逻辑电路负责将数据 从内存传输到寄存器,或者从寄存器传输到运算器进行运算,再传输回内存或寄存器存储 。

在通信系统中的应用

调制解调器

调制解调器是通信系统中用于将数字信号转换为模拟信号,或者将模拟信号转换为数字信号的电路。调制解调器中的 组合逻辑电路负责处理数字信号的编码与解码,确保数字信息能够在模拟信道中传输。

组合逻辑电路的基本组成

输入门

用于接收外部输入信号。

组合逻辑元件

如AND、OR、NOT等基本逻辑门,用于实现特定的 逻辑功能。

输出门

将逻辑电路的输出传递给外部设备或下一级电路。

组合逻辑电路的功能描述

80%

真值表

描述输入与输出之间逻辑关系的 表格,列出所有可能的输入状态 和对应的输出状态。

100%

表达式

在控制系统中的应用

01

控制器

控制器是控制系统中用于实现控制算法的电路。控制器中的组合逻辑电

路根据输入的控制信号和设定的控制参数,计算出控制输出信号,以实

现对被控对象的精确控制。

02

比较器

比较器是控制系统中用于比较输入信号与设定阈值的电路。比较器中的

组合逻辑电路根据比较结果输出相应的控制信号,以实现对被控对象的

数字电路课件第四章 组合逻辑电

输 出 Z 1 0 0 1 0 1 1 1

设计举例:

3. 选用小规模SSI器件 4. 化简

Z R' A' G' RA RG AG

5. 画出逻辑图

设计举例2、有三个班学生上自习,大教室能容纳两 个班学生,小教室能容纳一个班学生。 设计两个教室是否开灯的逻辑控制电路,用SSI 门电路实现。要求如下: (1)一个班学生上自习, 开小教室的灯。 (2)两个班上自习, 开大教室的灯。 (3)三个班上自习, 两教室均开灯。

高、低电平信号。

常用的有:二进制译码器,二-十进制译码器, 显示译码器等

一、二进制译码器

例:3线—8线译码器 输

A

2

3位二进制译码器的真值表

入

A

1

输

Y

6

出

Y

3

A Y

0 7

Y

5Байду номын сангаас

Y

4

Y

2

Y

1

Y

0

0 0 0 0 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 1 0 0 0 0 0 0 1 0 0 0 1 1 0 0 0 0 1 0 0 0 1 0 0 0 0 0 1 0 0 0 0 1 0 1 0 0 1 0 0 0 0 0 1 1 0 0 1 0 0 0 0 0 0 1 1 1 1 0 0 0 0 0 0 0

[( I 7 I 6 I 5 I 4 I 3 I 2 I1 I 0 ) S ]'

为0时,电路工 作有编码输入

输

S

1 0

' I0 ' I1 ' I2 ' I3

数电课件第四章 组合逻辑电路讲解

将有特定含义的输入信号编成不同(bù tónɡ)代码输出的 组合逻辑电路,称为编码器。

在具体硬件电路上,编码就是对输入相应信号线出现的 “有效”信号时,对该线(信号)进行编码并输出。如:一条 信号线出现高电平时,表示一个特定的含义事件发生,时常需 要对此进行编码,以通知系统;而出现低电平时表示正常,无 特殊情况发生。这是对高电平编码,信号线出现高电平时,称 为高电平有效(信号有效),出现低电平成为信号无效。

精品资料

一种(yī zhǒnɡ)技巧性方法

X1AB,XC 2ABC Y2A BAC BC Y1X1X2Y2

Y2 BC

A

00 01 11 10

0

1

1

111

Y1 BC

A

00 01 11 10

0

1

1

11

1

精品资料

X1 BC

A

00 01 11 10

0

1

1

X2 BC

A

00 01 11 10

0

111

11111

第四章 组合(zǔhé)逻辑电路

4.1 概述(ɡài shù) 4.2 组合逻辑电路的分析与设计方法 4.3 常用的组合逻辑电路 4.4 MSI分析与设计 4.5 竟争与冒险 4.6 小结

精品资料

4.1概述(ɡài shù)

组合逻辑电路特点:输出只与当前的输入情况有关,与以前 (yǐqián)的输入输出无关。结构上从输出到输入没有反馈回路。 (无记忆)

111

11

0

11111111

111

10

0

0 × × × × × × ×

000

01

0

1 0 × × × × × ×

在具体硬件电路上,编码就是对输入相应信号线出现的 “有效”信号时,对该线(信号)进行编码并输出。如:一条 信号线出现高电平时,表示一个特定的含义事件发生,时常需 要对此进行编码,以通知系统;而出现低电平时表示正常,无 特殊情况发生。这是对高电平编码,信号线出现高电平时,称 为高电平有效(信号有效),出现低电平成为信号无效。

精品资料

一种(yī zhǒnɡ)技巧性方法

X1AB,XC 2ABC Y2A BAC BC Y1X1X2Y2

Y2 BC

A

00 01 11 10

0

1

1

111

Y1 BC

A

00 01 11 10

0

1

1

11

1

精品资料

X1 BC

A

00 01 11 10

0

1

1

X2 BC

A

00 01 11 10

0

111

11111

第四章 组合(zǔhé)逻辑电路

4.1 概述(ɡài shù) 4.2 组合逻辑电路的分析与设计方法 4.3 常用的组合逻辑电路 4.4 MSI分析与设计 4.5 竟争与冒险 4.6 小结

精品资料

4.1概述(ɡài shù)

组合逻辑电路特点:输出只与当前的输入情况有关,与以前 (yǐqián)的输入输出无关。结构上从输出到输入没有反馈回路。 (无记忆)

111

11

0

11111111

111

10

0

0 × × × × × × ×

000

01

0

1 0 × × × × × ×

北京化工大学 数字逻辑-数电课件 第04章 组合逻辑电路

组合逻辑电路分析的一般步骤

逻 辑 图

输 出 表

达 式

逐 级 写 出

化 简 和 变 换

列 真 值 表

逻概 辑括 功电 能路

4-6

4.1 组合逻辑电路分析

组合逻辑电路分析例

A ≥ 1 A+B B

≥1 F

1 A ≥1 1B

A +B

异或逻辑

F A B A B (A B)(A B) AB AB (真值表略)

第4章 组合逻辑电路

概述 4.1 组合逻辑电路分析 4.2 组合逻辑电路设计 4.3 组合逻辑电路的冒险现象

4-1

数 逻 组合逻辑电路 字辑 系电 统 路 时序逻辑电路

4-2

组合逻辑电路的特点

结构特点:基本上由门电路组成;只有从 输入端到输出端的直接通路,而没有从输出 端到输入端的反馈回路;电路中不包含具有 记忆功能的存储元件

4-32

4.1.3 译码器

2线-4线译码器(BIN/OCT) Y0 A1 A0 ST

ST 1

选通输入端

地址输入端

A0 1

1

A1 1

1

&

Y0 译码输出端

Y1 A1 A0 ST Y2 A1 A0 ST

&

Y1

Y3 A1 A0 ST

ST’ A1 A0 Y’3 Y’2 Y’1 Y’0

&

1 ×× 1 1 1 1

4-36

3线-8线译码器CT54/74138

4.1.3 译码器

3线-8线译码器CT54/74138真值表

S1

S2+S3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

×

1

××× 1 1 1 1 1 1 1 1

逻 辑 图

输 出 表

达 式

逐 级 写 出

化 简 和 变 换

列 真 值 表

逻概 辑括 功电 能路

4-6

4.1 组合逻辑电路分析

组合逻辑电路分析例

A ≥ 1 A+B B

≥1 F

1 A ≥1 1B

A +B

异或逻辑

F A B A B (A B)(A B) AB AB (真值表略)

第4章 组合逻辑电路

概述 4.1 组合逻辑电路分析 4.2 组合逻辑电路设计 4.3 组合逻辑电路的冒险现象

4-1

数 逻 组合逻辑电路 字辑 系电 统 路 时序逻辑电路

4-2

组合逻辑电路的特点

结构特点:基本上由门电路组成;只有从 输入端到输出端的直接通路,而没有从输出 端到输入端的反馈回路;电路中不包含具有 记忆功能的存储元件

4-32

4.1.3 译码器

2线-4线译码器(BIN/OCT) Y0 A1 A0 ST

ST 1

选通输入端

地址输入端

A0 1

1

A1 1

1

&

Y0 译码输出端

Y1 A1 A0 ST Y2 A1 A0 ST

&

Y1

Y3 A1 A0 ST

ST’ A1 A0 Y’3 Y’2 Y’1 Y’0

&

1 ×× 1 1 1 1

4-36

3线-8线译码器CT54/74138

4.1.3 译码器

3线-8线译码器CT54/74138真值表

S1

S2+S3 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 Y7

×

1

××× 1 1 1 1 1 1 1 1

数字电子技术基础(数字电路)第四章组合逻辑电路

(7-14/29)

【例2】 用与非门设计一个码制变换电路。要求将8421码 转换为余3码。 ① 逻辑抽象 B8 B4 B2 B1

8421码 输入

8421码 转换为 余3码

E3 E2 E1

E0 余3码 输出

(7-15/29)

② 真值表 B8B4B2B1 0 0 0 0 0 0 0 1 0 0 1 0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0 1 1 0 1 1 1 1 0 1 1 1 1 E3E2E1E0 0 0 1 1 0 1 0 0 0 1 0 1 0 1 1 0 0 1 1 1 1 0 0 0 1 0 0 1 1 0 1 0 1 0 1 1 1 1 0 0

信号经不同路径传输 后到达电路中某一会 合点的时间有差异的 现象,称为竞争。

由于竞争原因而使电

路输出发生瞬时错误 的现象,称为冒险。

A

A

L

A L

(7-23/29)

2. 如何判别电路中有无冒险?

代数法判别与电路对应的表达式

判竞争: 同一变量以原变量、反变量的形式同时出 现在表达式中,则变量具有竞争能力。

电路设计

波形图 文字描述 逻辑图

【例1】 用与非门设计一个监视交通信号灯状态的逻辑电路。 每一组信号灯均由红、黄、绿灯组成。正常工作时 有且仅有一盏灯亮;出现其他状态时,发出故障信号。

① 逻辑抽象

R A G

正常工作状态 R A G

R A G

R A 红(R)、黄(A)、绿 G (G)为信号灯的状 态输入。 灯亮为1。

L2 = BC + AB × C

数字电子技术基础(第四版)-第4章-组合逻辑电路解析PPT课件

-

54

设计实例2:用2N选一数据选择器实现 N+1个变量的逻辑函数。

设计思想: ①将N个变量接数据选择器的选择输入端(即地址端) ②余下的一个变量作为数据选择器的数据输入端。

-

55

例:用74153实现三变量函数。

F (A ,B ,C ) m (1 ,3 ,5 ,6 )

解一:设B接A1,C接A0。

A

' 0

)

m2

'

...

Y7 ' ( A2 A1A0 ) m 7 '

-

45

-

46

-

47

三、用译码器构成函数发生器P186

例1:

请写出Y的逻辑函数式

Y(Y3'Y4'Y5')' Y3Y4 Y5

m3 m4 m5

m(3, 4,5)

Y A 'B C A B 'C ' A B 'C

-

48

例2:用74138构成下 列函数发生器:

F A 'B 'C A 'B C A B 'C A B C ' 0 B 'C ' ( A ' A ) B 'C A B C ' A 'B C

0 m 0 1 m 1 A m 2 A 'm 3

D 0 m 0 D 1 m 1 D 2 m 2 D 3 m 3

-

56

解二:设A接A1,B接A0。

4)画逻辑图(略)

-

31

三、优先编码器 8线-3线优先编码器

74HC148

-

1、功能表

输入:I 0 ~ I 7 ,共8个输入端

数字电路与逻辑设计:第4章 组合逻辑电路 1

Bi Ci-1

Ai 00 01 11 10

0

1

1

11

1

(a) Si 的卡诺图

Bi Ci-1

Ai 00 01 11 10

0

1

1

1 11

(b) Ci 的卡诺图

图 4.1.3

Si = Ai Bi Ci-1 + Ai Bi Ci-1 + Ai Bi Ci-1 + Ai Bi Ci-1 C i = Ai Bi + Bi Ci-1 + Ai Ci-1

输出 F 1 0 0 1 0 1 1 0

输入 D1 D2 D3 D4 1000 1001 1010 1011 1100 1101 1110 1111

输出 F 0 1 1 0 1 0 0 1

(3) 确定逻辑功能: 奇校验码产生电路

补充:分析如图所示电路的逻辑功能。

A B

&

&

&F

C

&

结论:三变量多数表决器。 输入A、B、C三变量中,只要有两个或两个以上

变量为1,则输出为1。

习题4.2 分析图P4.2电路的逻辑功能。

B

=1

C

=1

F1

&

A

1

1 F2

&

解:(1)从输入端开始,逐级推导出函数表达式 F1 = A⊕B⊕C F2 = A(B⊕C) + BC

(2)列真值表

ABC

000 001 010 011 100 101 110 111

F1 F2 00 11 11 01 10 00 00 11

A

S

B

CO

C

S A B C AB

数字电路第4章组合逻辑电路

1

1

1 1 1 数字电路第4章组合逻辑电路

当输入A、 B、C中有2个 或3个为1时, 输出Y为1, 否则输出Y为 0。所以这个 电路实际上是 一种3人表决 用的组合电路: 只要有2票或3 票同意,表决 就通过。

例

A B

逻辑图 C

≥1 Y1

≥1 Y3 1

Y

1

≥1

Y2

逻辑表 达式

Y1 A B C Y2 A B Y Y3 Y1 Y2 B A B C A B B Y3 Y1 Y2B

Y1

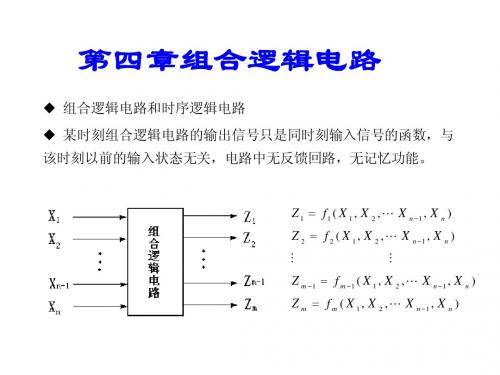

f1(I0 , I1,, In1)

Ym1 fm1(I0 , I1,, In1) 数字电路第4章组合逻辑电路

特点

组合逻辑电路特点: (1)从电路结构上看,基本由逻辑门电路组成; (2)不存在反馈,不包含记忆元件 (触发器)。

从逻辑功能上看,任一时刻的输出仅仅与该时 刻的输入有关,与该时刻之前电路的状态无关。 即时输入决定即时输出。

3级门的电路结构,只需要4个与非门,就实 现了F函数。

数字电路第4章组合逻辑电路

*小结

由此可以看出,在没有反变量输入的条件下, 组合电路的结构为3级门结构:

第1级为输入级,与非门器件的多少,取决于 函数中乘积项所包含的尾部因子种类的多少。(尾

部因子是指每个乘积项中带非号部分的因子)

第2级为中间级或称为与项级,所含器件的多少, 取决于乘积项的多少。

① 利用原函数F求F的反函数。 F的反函数由2n个最小项中,除去F中已包含的最小项

以外的全部最小项组成。 ②利用F的反函数求对偶函数F* 。

若F的反函数中最小项号码为i,则F* 中最小项号码 为(2n-1)-i。(个数相同) ③利用偶函数F* 求F,F= (F*)*

组合逻辑电路的设计

0 1 1 0 ×××××

010

0 1 1 1 0 ××××

011

0 1 1 1 1 0 ×××

100

0 1 1 1 1 1 0 ××

101

0 1 1 1 1 1 1 0×

110

0 1 1 1 1 1 1 10

111

出

YEX YS

11 10 01 01 01 01 01 01 01 01

第4章 组合逻辑电路

第4章 组合逻辑电路

Dn An BnCn An BnCn An Bn C n An BnCn An Bn Cn

Cn1 An Bn C n An Bn C n BnCn An (Bn Cn ) BnCn An (Bn Cn ) BnCn

E3 A BC BD A BC BD

E2 BC D BC BD B(C D) B(C D) B (C D)

E1 C D CD C D C D

E0 D

第4章 组合逻辑电路

③ 画逻辑电路。

该电路采用了三种门电路,速度较快,逻辑图如图4.2.4所示。

的输入、输出均为低电平有效,因此给每个输出端加一个

反相器,即可将反码输出的BCD码转换为正常的BCD码。

第4章 组合逻辑电路

图4.3.3 74LS147的逻辑符号

第4章 组合逻辑电路

表4.3.2 74LS147的功能表

I1 I2 I3 I4 I5 I6 I7 I8 I9

111 11 11 11 ××× ×× ×× × 0 ××× ×× ×× 0 1 ××× ×× × 0 1 1 ××× ×× 0 1 1 1 ××× × 0 1 1 1 1 ××× 0 1 1 1 1 1 ×× 0 1 1 1 1 1 1 ×0 1 1 1 1 1 1 1

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

与编码器相反,译码器将输入代码转换成特 定的输出信号 两种常用的译码器:

二进制译码器 数字显示译码器

30

§4.2.2 译码器

二进制译码器

译码器有n个输入信号和m个输出信号 m=2n 二进制全译码器 • 2线-4线译码器 • 3线-8线译码器 m<2n 部分译码器 • 4线-10线译码器

31

§4.2.2 译码器

输入输出关系表

1 1

1

1

F0 = I 0

F1 = I 0 I 1

F2 = I 0 I 1 I 2

14

§4.1.2 组合逻辑电路设计

设计步骤(门电路)

归纳逻辑问题

真值 表

邻接真值表

实际 问题 逻辑 归纳逻辑问题 函数

卡诺 图

选定逻辑门 类型

最简 表达式

逻辑 电路图

15

§4.2 组合逻辑电路模块及其应用

Y0 = (I1 I 2 I 4 I 6 + I3 I 4 I 6 + I5 I 6 + I7 ) ⋅ S

实用中:输入信号以低电平 低电平表示 低电平 信号输入; 但注意:输入端、输出端的记法, 使逻辑变量与信号对应关系仍为正 正 逻辑。 逻辑 23

附加输出端 使能输出端 Y S

YS = I 0 ⋅ I 1 ⋯ I 7 ⋅ S

Y2 = I 4 + I 5 + I 6 + I 7

无 关 项

x x x x x x x

x x x x x x

x x x x x

同

同

x x x x

x x x

x x

x

22

使能输入端 S 虚框内为编码器主电路

Y2 = ( I 4 + I 5 + I 6 + I 7 ) ⋅ S

Y1 = ( I 2 I 4 I 5 + I 3 I 4 I 5 + I 6 + I 7 ) ⋅ S

无 关 项

x x x x x x x

x x x x x x

x x x x x

x x x x

x x x

x x

x

21

优先编码器(续)

Y2 = I 4 ⋅ I 5 ⋅ I 6 ⋅ I 7 + I 5 ⋅ I 6 ⋅ I 7 + I 6 ⋅ I 7 + I 7

常用公式(消因子法): A + A ⋅ B = A + B

A

1 0 0

1 1 0

1 1 1 1

1 0 0 1

F = AB + A B + AB1 + B A1

= A B ⋅ A B ⋅ AB1 ⋅ B A1

反复利用合并项法则,保留相同变量,消掉相反变量 反复利用合并项法则,保留相同变量,

13

§4.1.2 设计

练习:设计一个电话信号控制电路:电路有I0(火警)、I1(盗警)和I2 (日常业务)三种输入信号,按优先次序分别从F0、F1、F2输出,在同一 时间只能有一个信号通过。要求用与非门实现。

可选 7

§4.1.1 分析

写逻辑表达式

& A B C & P & & ≥1

F

P = ABC F = AP + BP + CP = A ABC + B ABC + C ABC

化简与变换

F = ABC ( A + B + C ) = ABC + A + B + C = ABC + A B C

A B C

3线-8线译码器

Y0 = A2 A1 A0

Y1 = A2 A1 A0 Y2 = A2 A1 A0

Y3 = A2 A1 A0

Y4 = A2 A1 A0

Y5 = A2 A1 A0

Y6 = A2 A1 A0

Y7 = A2 A1 A0

32

§4.2.2 译码器

用二极管与门阵列组成 3线-8线译码器

33

§4.2.2 译码器

F 0 1 1 1 1 1 1 0

列出真值表 分析逻辑功能:“不一致电路”

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

8

§4.1.1 分析

自然二进制码至格雷码的转换电路

G3 G2 G1 G0

B3 B2 B1 B0

G3 G2 G1 G0

=1

=1

=1

B3

B2

集成译码器74138 • 常用的3线-8线译码器 S1、S2和S3 为使能端,又叫作“片选”

S = S1 S 2 S 3 = S 1 S 2 + S 3

作用: 消除干扰 功能扩展

34

§4.2.2 译码器

74138功能表

0 X

35

§4.2.2 译码器

8421 BCD码 译码器 • 7442是常用的8421BCD码译码器 4线—10线译码器

P & Q R S F AB A1 B1 11 0 0 0 0 1 10 0 0 &1 1 0 B 0 &0 0 0 1 0 1 0 0 1 &1 1 0 0 &0 F A1 0 1 1 1 0 1 0 &1 1 1 0 0 B1 0 1 0 1 1 1 1 &0 1 0 0 0 1 1 1 0 0 1 0 1 0 1 0 1 1 0 1 1 1 卡诺图中两个相邻(包括闭合、轴对称)“1格”的最小项可 1 1 0 0 0 以合并成一个与项,消去一个原变量和反变量 1 1 0 1 0 1 1 1 0 0 1 1 1 1 1

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0

0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0

0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

9

§4.1.2 组合逻辑电路设计

组合逻辑电路的设计方法

编码器 译码器 数据选择器 数值比较器 加法器

16

§4.2.1 组合逻辑电路模块 之 编码器

编码器

编码是将字母、数字、符号等信息编成一组二进制代码; 编码器对每一个有效的输入信号,都产生唯一的一组二进 制代码与之对应; 编码器是一个多输入多输出电路; 通常m个输入信号,需要n位二进制编码,m应不大于2n 。 常用的编码器有二进制编码器和二—十进制编码器两种。

7442功能表

36

§4.2.2 译码器

译码器的扩展

例题:将两片74138扩展为4线—16线译码器

37

§4.2.2 译码器

二进制权译码器的应用——实现组合逻辑函数 实现组合逻辑函数

译码器的每个输出端分别与一个最小项相对应

F = AB + BC + AC

= ABC + A BC + ABC + ABC

B1

B0

G3 = B3 G2 = B3 ⊕ B2 G1 = B2 ⊕ B1 G0 = B1 ⊕ B0

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1

低电平表示无信号输入 扩展输出端 Y EX

Y EX = Y S ⋅ S = ( I 0 + I1 + ⋅ ⋅ ⋅ I 7 ) ⋅ S

低电平表示有信号输入

24Βιβλιοθήκη 优先编码器(续)功能表

可以俗称为: “有信号输入”和“无信号输入” 指示

25

§4.2.1 编码器

优先编码器(续)

编码器的扩展 → • 16线-4线优先编码器

39

§4.2.2 译码器

数字显示译码器

能够显示数字、字母或符号的器件称为数字显示器 能把数字量翻译成数字显示器所能识别的信号的译码器称 为数字显示译码器——严格地说,应叫作“代码代换器”。 七段数字显示器(半导体数码管BS201A,含小数点八段)

数字电路与系统

2008

第四章、组合逻辑电路

1

第四章@第五版 习题

第五版 4.1;4.4;4.5 4.8;4.9;4.10;4.12 4.15;4.17;4.19; 4.23 4.25;4.27;4.28; 4.32 第四版 3.1;3.2;3.3 3.6;3.7;3.8;3.10 3.13;3.15;3.17; 3.21 3.23;3.25;3.26; 3.29

I4 I3 I2

Y2 Y1

1 1 &

Y2 Y1 Y0

I0

I1 I 0 YS Y0

27

§4.2.1 编码器

二—十进制编码器

常用8421BCD编码器 74147 优先权型

28

§4.2.1 编码器

二—十进制编码器74147功能表

输入低电平有效,输出是反码形式BCD码

29

§4.2.2 组合逻辑电路模块 之 译码器

17

§4.2.1 编码器

二进制编码器

用n位二进制代码对2n个信号进行编码 三位二进制编码器 8线—3线编码器

18

§4.2.1 编码器

电路图

表达式 输入变量仅限表中取值,其 限 约束项,化简: 它为约束项 约束项 Y2 = I 4 + I 5 + I 6 + I 7

Y1 = I 2 + I 3 + I 6 + I 7 Y0 = I1 + I 3 + I 5 + I 7

二进制译码器 数字显示译码器

30

§4.2.2 译码器

二进制译码器

译码器有n个输入信号和m个输出信号 m=2n 二进制全译码器 • 2线-4线译码器 • 3线-8线译码器 m<2n 部分译码器 • 4线-10线译码器

31

§4.2.2 译码器

输入输出关系表

1 1

1

1

F0 = I 0

F1 = I 0 I 1

F2 = I 0 I 1 I 2

14

§4.1.2 组合逻辑电路设计

设计步骤(门电路)

归纳逻辑问题

真值 表

邻接真值表

实际 问题 逻辑 归纳逻辑问题 函数

卡诺 图

选定逻辑门 类型

最简 表达式

逻辑 电路图

15

§4.2 组合逻辑电路模块及其应用

Y0 = (I1 I 2 I 4 I 6 + I3 I 4 I 6 + I5 I 6 + I7 ) ⋅ S

实用中:输入信号以低电平 低电平表示 低电平 信号输入; 但注意:输入端、输出端的记法, 使逻辑变量与信号对应关系仍为正 正 逻辑。 逻辑 23

附加输出端 使能输出端 Y S

YS = I 0 ⋅ I 1 ⋯ I 7 ⋅ S

Y2 = I 4 + I 5 + I 6 + I 7

无 关 项

x x x x x x x

x x x x x x

x x x x x

同

同

x x x x

x x x

x x

x

22

使能输入端 S 虚框内为编码器主电路

Y2 = ( I 4 + I 5 + I 6 + I 7 ) ⋅ S

Y1 = ( I 2 I 4 I 5 + I 3 I 4 I 5 + I 6 + I 7 ) ⋅ S

无 关 项

x x x x x x x

x x x x x x

x x x x x

x x x x

x x x

x x

x

21

优先编码器(续)

Y2 = I 4 ⋅ I 5 ⋅ I 6 ⋅ I 7 + I 5 ⋅ I 6 ⋅ I 7 + I 6 ⋅ I 7 + I 7

常用公式(消因子法): A + A ⋅ B = A + B

A

1 0 0

1 1 0

1 1 1 1

1 0 0 1

F = AB + A B + AB1 + B A1

= A B ⋅ A B ⋅ AB1 ⋅ B A1

反复利用合并项法则,保留相同变量,消掉相反变量 反复利用合并项法则,保留相同变量,

13

§4.1.2 设计

练习:设计一个电话信号控制电路:电路有I0(火警)、I1(盗警)和I2 (日常业务)三种输入信号,按优先次序分别从F0、F1、F2输出,在同一 时间只能有一个信号通过。要求用与非门实现。

可选 7

§4.1.1 分析

写逻辑表达式

& A B C & P & & ≥1

F

P = ABC F = AP + BP + CP = A ABC + B ABC + C ABC

化简与变换

F = ABC ( A + B + C ) = ABC + A + B + C = ABC + A B C

A B C

3线-8线译码器

Y0 = A2 A1 A0

Y1 = A2 A1 A0 Y2 = A2 A1 A0

Y3 = A2 A1 A0

Y4 = A2 A1 A0

Y5 = A2 A1 A0

Y6 = A2 A1 A0

Y7 = A2 A1 A0

32

§4.2.2 译码器

用二极管与门阵列组成 3线-8线译码器

33

§4.2.2 译码器

F 0 1 1 1 1 1 1 0

列出真值表 分析逻辑功能:“不一致电路”

0 0 0 0 1 1 1 1

0 0 1 1 0 0 1 1

0 1 0 1 0 1 0 1

8

§4.1.1 分析

自然二进制码至格雷码的转换电路

G3 G2 G1 G0

B3 B2 B1 B0

G3 G2 G1 G0

=1

=1

=1

B3

B2

集成译码器74138 • 常用的3线-8线译码器 S1、S2和S3 为使能端,又叫作“片选”

S = S1 S 2 S 3 = S 1 S 2 + S 3

作用: 消除干扰 功能扩展

34

§4.2.2 译码器

74138功能表

0 X

35

§4.2.2 译码器

8421 BCD码 译码器 • 7442是常用的8421BCD码译码器 4线—10线译码器

P & Q R S F AB A1 B1 11 0 0 0 0 1 10 0 0 &1 1 0 B 0 &0 0 0 1 0 1 0 0 1 &1 1 0 0 &0 F A1 0 1 1 1 0 1 0 &1 1 1 0 0 B1 0 1 0 1 1 1 1 &0 1 0 0 0 1 1 1 0 0 1 0 1 0 1 0 1 1 0 1 1 1 卡诺图中两个相邻(包括闭合、轴对称)“1格”的最小项可 1 1 0 0 0 以合并成一个与项,消去一个原变量和反变量 1 1 0 1 0 1 1 1 0 0 1 1 1 1 1

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 0

0 0 1 1 1 1 0 0 0 0 1 1 1 1 0 0

0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 0

9

§4.1.2 组合逻辑电路设计

组合逻辑电路的设计方法

编码器 译码器 数据选择器 数值比较器 加法器

16

§4.2.1 组合逻辑电路模块 之 编码器

编码器

编码是将字母、数字、符号等信息编成一组二进制代码; 编码器对每一个有效的输入信号,都产生唯一的一组二进 制代码与之对应; 编码器是一个多输入多输出电路; 通常m个输入信号,需要n位二进制编码,m应不大于2n 。 常用的编码器有二进制编码器和二—十进制编码器两种。

7442功能表

36

§4.2.2 译码器

译码器的扩展

例题:将两片74138扩展为4线—16线译码器

37

§4.2.2 译码器

二进制权译码器的应用——实现组合逻辑函数 实现组合逻辑函数

译码器的每个输出端分别与一个最小项相对应

F = AB + BC + AC

= ABC + A BC + ABC + ABC

B1

B0

G3 = B3 G2 = B3 ⊕ B2 G1 = B2 ⊕ B1 G0 = B1 ⊕ B0

0 0 0 0 0 0 0 0 1 1 1 1 1 1 1 1

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1 0 0 0 1 1 0 1 1

低电平表示无信号输入 扩展输出端 Y EX

Y EX = Y S ⋅ S = ( I 0 + I1 + ⋅ ⋅ ⋅ I 7 ) ⋅ S

低电平表示有信号输入

24Βιβλιοθήκη 优先编码器(续)功能表

可以俗称为: “有信号输入”和“无信号输入” 指示

25

§4.2.1 编码器

优先编码器(续)

编码器的扩展 → • 16线-4线优先编码器

39

§4.2.2 译码器

数字显示译码器

能够显示数字、字母或符号的器件称为数字显示器 能把数字量翻译成数字显示器所能识别的信号的译码器称 为数字显示译码器——严格地说,应叫作“代码代换器”。 七段数字显示器(半导体数码管BS201A,含小数点八段)

数字电路与系统

2008

第四章、组合逻辑电路

1

第四章@第五版 习题

第五版 4.1;4.4;4.5 4.8;4.9;4.10;4.12 4.15;4.17;4.19; 4.23 4.25;4.27;4.28; 4.32 第四版 3.1;3.2;3.3 3.6;3.7;3.8;3.10 3.13;3.15;3.17; 3.21 3.23;3.25;3.26; 3.29

I4 I3 I2

Y2 Y1

1 1 &

Y2 Y1 Y0

I0

I1 I 0 YS Y0

27

§4.2.1 编码器

二—十进制编码器

常用8421BCD编码器 74147 优先权型

28

§4.2.1 编码器

二—十进制编码器74147功能表

输入低电平有效,输出是反码形式BCD码

29

§4.2.2 组合逻辑电路模块 之 译码器

17

§4.2.1 编码器

二进制编码器

用n位二进制代码对2n个信号进行编码 三位二进制编码器 8线—3线编码器

18

§4.2.1 编码器

电路图

表达式 输入变量仅限表中取值,其 限 约束项,化简: 它为约束项 约束项 Y2 = I 4 + I 5 + I 6 + I 7

Y1 = I 2 + I 3 + I 6 + I 7 Y0 = I1 + I 3 + I 5 + I 7