简易数字信号传输性能分析仪

数字传输分析仪功能特点

数字传输分析仪功能特点随着科技的不断发展,数字传输已成为现代通信领域的基本要素。

数字传输技术的高效、可靠、安全和灵活性已经得到了广泛认可。

在数字传输过程中,信号可能遭受干扰,导致数据错误。

为了解决这个问题,数字传输分析仪(Digital Transmission Analyzer)应运而生。

数字传输分析仪是能够实时监测数字传输系统的设备。

数字传输分析仪用于检测和分析数字传输系统的信号质量、误码率和其他参数,以评估系统的性能和可靠性。

数字传输分析仪由硬件和软件组成,可以检测各种数字信号协议,包括SONET、SDH、Ethernet等。

本文将介绍数字传输分析仪的功能特点。

1. 精准测量参数数字传输分析仪可以精确测量数字传输系统的各种参数。

这些参数包括:信号的波特率、时钟偏移、误码率、信噪比和频谱分析等。

数字传输分析仪可以测量这些参数的精度高达0.1%。

这使得数字传输分析仪成为评估数字传输系统性能的理想工具。

2. 多功能分析数字传输分析仪不仅仅只是一个分析仪,它还具有多种功能。

数字传输分析仪可以实时监测数字传输系统的信号质量和性能,同时还可以进行多种分析,比如快速故障诊断、误码分析和频谱分析等等。

数字传输分析仪还可以同时分析多个端口的信号,在确保性能的同时,也提高了生产效率。

3. 可视化分析数字传输分析仪还可以提供可视化分析,这有助于用户更好地理解数字信号的传输过程。

数字传输分析仪提供的可视化效果包括波形图、频谱图、直方图等。

用户可以根据需要选择不同的数据视图,使得数字信号的分析更加直观和准确。

4. 数据存储和导出数字传输分析仪还可以将收集到的数据存储到设备内部或外部存储介质中。

这些数据可以用于将来的分析或备份。

数字传输分析仪还可以将数据导出到其他格式中,比如Excel、CSV等。

这使得数字传输分析仪成为工程师和技术人员优秀的数据分析工具。

5. 简单易用数字传输分析仪的操作界面通常都非常简单直观。

操作人员只需根据提示进行操作,就可以轻松完成信号测试和分析。

简易数字信号传输性能分析仪

2011年E 题 简易数字信号传输性能分析仪摘要:本设计给出了一个基于Altera Cyclone II 系列FPGA 开发芯片EPIC3T144CB 的系统,利用D 触发器级联产生m 序列数字信号和伪随机信号,用分频器实现信号10kbs 步进,信号通过一个由运放OP27构成的二阶低通滤波器,模拟信号传输信道,然后与伪随机序列进行相加,信号处理模块为由FPGA 开发板构成的接收器,用Verilog 语言编程实现适当滤波和同步时钟提取,观察眼图分析信号特性。

经测试,低通滤波器截止频率保持在10%误差内,放大增益可调范围较大。

关键词:Cyclone II FPGA m 序列 低通滤波器一、方案论证1、数字信号发生器和伪随机信号发生器经分析,数字信号发生器部分要求产生一个码元多项式为()x x x x f 84321x ++++=的m 序列信号,有如下方案。

方案一:利用集成电路芯片搭接而成,其中,要同时实现时钟源Vclock -1和传输码元的两个分立元件电路。

此方案结构简单、电路可靠、成本低且易于实现,但特别需要注意时钟源的稳定、干扰和芯片的最高工作频率,且实际调试中振荡最高频率一般只能达到几百KHz ,伪随机信号需10MHz ,不能同时实现码元信号和伪随机信号的产生。

方案二:利用单片机编程实现序列的产生。

按照生成码多项式的要求利用C 语言编程,随着m 序列位数的增加编程愈发复杂,调试困难,而且单片机难以承受10MHz 的信号频率,不能产生伪随机信号。

方案三:利用基于FPGA 的Verilog 语言编程实现序列的产生。

根据信号的产生原理,利用触发器易于实现,编程易于调试和实现,速度快。

综上所述,考虑实现精度、简易程度、调试效率和数据率10kbs 步进可调的要求,用软件易于实现,我们选用方案三。

2、低通滤波器模块方案一:由于要求滤波器的通带增益AF在0.2~4.0 范围内可调,可以用可变增益放大器AD603和开关电容滤波器MAX297 实现低通滤波器,根据MAX297输入时钟的不同来达到10kbs 步进可调的目的。

简易数字信号传输性能分析仪

简易数字信号传输性能分析仪E题:简易数字信号传输性能分析仪摘要本系统是由DSP技术以及CPLD的硬件编程技术实现的简易数字信号传输性能分析仪,主要包括信号产生电路、低通滤波电路、噪声叠加电路、数字信号解码以及眼图显示四部分。

信号发生器采用Verilog HDL将模拟硬件电路逻辑综合在CPLD芯片中,简化了电路的设计。

在FilterPro仿真软件指导下,通过调整原件参数,使用运放设计有源低通滤波器,使得设计达到要求。

加法电路通过运放将信号和噪声叠加。

使用DSP对信号进行ADC连续采样再通过过零比较捕捉到信号中的跳变沿,分析沿的间距和周期规律就可确定时钟信号的频率,即用PWM将同步信号提取并输出。

再通过编程得出信号的同步时钟频率,依此得出相应的眼图幅度。

通过电路组装、程序编写与调试、采集实验数据与分析等设计环节,顺利完成了题目的基本和发挥部分的要求,并在数字信号发生、动态程序及算法优化设计方面有一定的创新。

关键词:曼彻斯特编码、CPLD、低通滤波、DSP、眼图AbstractThis system is designed based on DSP and CPLD hardware programming technology to realize a simple digital signal transmission performance analyzer, mainly comprises four parts of signal generators, low-pass filters, digital signal analysis and display. Verilog HDL that converts the analog hardware to logic circuit in CPLD chip is adopted in Signal generators to simplify circuit design. The design requirement of low-pass filters is satisfied by adjusting the parameters and using discrete components design under the guidance of FilterPro. Through ADC continuous sampling and the zero crossing comparison by DSP, the signal’s hopping along is captured, by analyzing along the pitch and cycle the frequency of the clock signal can be determined and then uses PWM to tackle extract and output synchronous signal. Through the DSP programming signal synchronous clock frequency can be obtained, and then draw the corresponding eye amplitude. Through the circuit assembly, programming and debugging, gathering of experimental data and analysis, design including the basic and extended requirements are successfully completed, and a certain innovation on the digital signal, dynamic program and algorithm for optimal design.目录简易数字信号传输性能分析仪(E题) (3)1.任务 (3)2.要求 (3)第一章系统方案的选择与论证 (4)1.信源与信道的方案选择与论证 (4)2.信号分析电路的方案选择与论证 (5)3.显示部分的方案选择与论证 (5)第二章理论分析 (5)1.数字信号与伪随机码发生器的设计 (5)2.低通滤波器电路的设计 (6)3.加法电路的设计 (8)4.数字信号分析电路的设计 (8)5.显示电路的设计.. 错误!未定义书签。

基于FPGA的数字信号传输性能分析仪

通过测试 , 数字信号发 生器 可以生成 m序列 , 伪随机信

号 发 生 器 和 滤 波 器 已经 全 部达 到预 期 要 求 。 了完 成 对 曼 特 除

出 信号在 信道传输中的 噪声水平。 田

1 . DC— 3 DC 主 回路 拓 扑

理 电压 反 馈 信 号 、 MS 4 0 6 行 控 制 、 示 和人 机 交 换 对 P 3 19进 显

等功能 , 用直观方便。在设计过程 中充分考虑 了制作成本 使

和功耗 , 多使 用集 成 芯 片 , 以较 低 的 成 本 实现 了题 目的 要 求 。 关 键 字 : 20 ; MP 3 7DC— C 变换 器 ; P 3 19 D MS 40 6

( 1 式 )

2 过 流保 护 分 析 . 2

扩展 , 需要外接 AD、 / , / DA等 实现本题功能较为复杂 。

方案 二 : 用 M P 3 F 6 单 片机进 行 控制 。 P 3 F 6 采 S40 19 MS 4 0 19

单片机 内部集成 8 1 路 2位 A C和 2通道 1 D 2位 DA,可以 / 直接用于 电流 测量时的数据采集 , 以及数 字控制输 出 , 控制 简单 , 于实现 , 易 能够很好 的满足本题地要求 。 因此采用方案

( 者 简介 : 聪 裕 , , 北 省 武 汉 市人 , 事 测 控 技 术 作 廖 男 湖 从

与仪器研究。 )

斯特 编码 , 提取同步时钟信号之外 , 完成 了对曼 彻斯特编 还

码 的解码部分 。通过对这些结果的分析 , 成功模拟 出数字信

简易数字信号传输性能分析仪

简易数字信号传输性能分析仪本作品设计一个简易数字信号传输性能分析仪,通过对个个方案的论证,最终选择两片CPLD做为核心器件。

首先通过单片机控制时钟的分频,使用可编程逻辑器件CPLD以方便的产生不同数据率的伪随机信号,同时用12864液晶显示数据率及峰峰值。

为了滤去整流输出电压中的纹波。

通过二阶巴特沃斯滤波器滤波同时产生高增益的滤波信号。

然后叠加伪随机信号用示波器显示眼图。

对于产生的m序列是否采用曼彻斯特编码,则使用开关控制单片机来选择。

通过数字分析电路与CPLD提取同步信号,再次用示波器显示眼图。

本系统结构清晰,经过测试基本完成题目要求。

关键词:CPLD 伪随机信号巴特沃斯滤波器同步信号眼图AbstractThe work to design a simple digital signal transmission performance a nalyzer, through a program of demonstration, finally choice two CPLD devices as the core of system.The design of the first chip to control the clock by the frequency, the use of programmable logic device CPL D to easily generate different pseudo-random signal data rate, and li quid crystal display with 12864 and the peak data rate. To filter the rectifier output voltage ripple. Through second-order Butterworth fi lter with the filter while producing high-gain signal. Then superimpo sed pseudo-random signal with an oscilloscope display eye. For m-sequ ences are generated using Manchester coding is used to select single-chip switch control. Through statistical analysis to extract synchron ization signals and CPLD circuits, once again shows the eye diagram w ith an oscilloscope.The system structure is clear, after the basic co mpletion of the test question.Key words:CPLD Pseudo-random signal Butterworth filter Sync Eye diag ram简易数字信号传输性能分析仪(E题)【本科组】1系统方案本系统主要由滤波模块、数字信号(m序列)产生模块、同步信号提取模块、眼图显示方式组成。

年全国大学生电子设计竞赛试题

2020 年全国大学生电子设计竞赛试题参赛注意事项(1)2020 年8 月31 日8:00 竞赛正式开始。

本科组参赛队只能在【本科组】题目中任选一题;高职高专组参赛队在【高职高专组】题目中任选一题,也能够选择【本科组】题目。

(2)参赛队认真填写《记录表》内容,填写好的《记录表》交赛场巡视员临时保留。

(3)参赛者必需是有正式学籍的全日制在校本、专科学生,应出示能够证明参赛者学生身份的有效证件(如学生证)随时备查。

(4)每队严格限制3 人,开赛后不得半途改换队员。

(5)参赛队必需在学校指定的竞赛场地内进行独立设计和制作,不得以任何方式与他人交流,包括教师在内的非参赛队员必需迴避,对违纪参赛队取消评审资格。

(6)2020 年9 月3 日20:00 竞赛终止,上交设计报告、制作实物及《记录表》,由专人封存。

开关电源模块并联供电系统(A 题)【本科组】一、任务设计并制作一个由两个额定输出功率均为16W 的8V DC/DC 模块组成的并联供电系统(见图1)。

图1 两个DC/DC 模块并联供电系统主电路示用意二、要求1.大体要求(1)调整负载电阻至额定输出功率工作状态,供电系统的直流输出电压U O=±。

(2)额定输出功率工作状态下,供电系统的效率不低于60% 。

(3)调整负载电阻,维持输出电压U O=±,使两个模块输出电流之和I O =且按I1:I2=1:1 模式自动分派电流,每一个模块的输出电流的相对误差绝对值不大于5%。

(4)调整负载电阻,维持输出电压U O=±,使两个模块输出电流之和I O =且按I1:I2= 1:2 模式自动分派电流,每一个模块输出电流的相对误差绝对值不大于5%。

2. 发挥部份(1)调整负载电阻,维持输出电压U O=±,使负载电流I O 在~之间转变时,两个模块的输出电流可在(~)范围内按指定的比例自动分派,每一个模块的输出电流相对误差的绝对值不大于2%。

数字传输分析仪(Function of digital transmission analyzer)

数字传输分析仪(Function of digital transmissionanalyzer)数字传输分析仪又称为数字通信分析仪,它是一种专门用于数字通信系统分析与测试的仪器。

数字传输分析仪的主要作用是对通信信号进行解码、分析和检测。

数字传输分析仪具有以下几个功能特点。

1.解码能力数字传输分析仪主要用于数字通信系统的功能测试和故障分析,因此其解码能力是其最基本的功能。

在数字传输中,不同类型的数字信号的编码方式不同,而数字传输分析仪通过对数字信号进行解码,可以使用户了解到数字信号内部数据内容、格式和通讯效果等关键信息,从而判断传输是否正常。

2.测试速度快数字传输分析仪在测试速度方面比传统的测试仪器更加出色。

首先,数字传输分析仪可以同时对多路信号进行分析,从而进一步提高了测试效率。

其次,数字传输分析仪具有高精度、高稳定性的运行特性,在测试速度和精度之间达到了较好的平衡,可以满足用户在测试各种异构性数字通信系统和不同速率信号时必要的测试速度和精度要求。

3.支持多种协议随着数字通信技术的不断发展和进步,数字传输分析仪还应该支持不同的数字通信协议。

例如SONET、SDH、ATM、Ethernet、FDDI等。

数字传输分析仪具有强大的协议解析和分析能力,用户可以在同一设备上完成不同协议的测试和分析,从而提高了数字传输测试的效率和准确性。

4.提供完整的数据记录数字传输分析仪可以提供完整的数据记录,包括错误数量分布图、统计表格、历史曲线等。

这些数据记录可以帮助用户更好的了解数字信号质量状况和性能瓶颈,从而快速定位异常故障并对其进行优化和改进。

5.显示效果清晰数字传输分析仪大多配备了高品质的液晶显示屏,可以实时显示传输参数、信号时序、通信状态等。

同时,数字传输分析仪可以提供全球范围内的语言支持,方便不同语言用户的使用。

数字传输分析仪是数码通信中不可或缺的仪器,其功能之强大、智能化、快速、稳定等特点,极大的提高了通信技术的发展和应用。

简易数字信号传输性能分析仪的设计-11

简易数字信号传输性能分析仪的设计摘要:本设计是将数字基带信号通过模拟信道进行传输,接收端通过数字信号分析电路检测数字信号传输性能。

在发送端,利用特定反馈函数的8位移位寄存器产生数字基带信号和利用12位移位寄存器产生数字噪声。

利用运放设计3种不同截止频率的模拟滤波器实现信道模拟。

将通过模拟滤波器的信号与噪声相加送到分析电路进行处理。

在分析电路部分,利用锁相环进行同步时钟的提取,最后利用得到的同步时钟观察接收信号的眼图,通过眼图的观察来评判信道的优劣程度。

关键词:数字基带信号数字锁相环同步时钟眼图引言:数字信号的传输有基带和频带两种。

数字通信的优势在于其安全性和可靠性。

同步技术在数字通信中起着重要作用。

本设计主要考虑数字基带信号通过模拟信道叠加数字噪声后的同步时钟的提取和性能的分析。

1方案比较与论证1.1方案描述首先设计制作一个数字信号发生器,产生时钟信号V1-clock和m序列的数字信号V1,数字信号通过模拟低通滤波器(即模拟信道),该滤波后的信号与伪随机信号发生器产生的伪随机信号(即模拟的干扰信号)通过加法器合成信号V2a。

如图1所示。

基础部分,将开关S闭合,将同步信号V1-clock与V2a输入到双踪示波器,观察眼图,分析、估计和调整系统的性能。

发挥部分,将开关S断开,数字信号发生器将产生的m序列信号进行曼切斯特编码,将编码后的信号通过三个低通滤波器,再与伪随机信号V3合成信号V2a,并通过一个数字信号分析电路,该分析电路具有对曼切斯特码解码和提取同步信号的功能,并且在低信噪比条件下正确显示V2a信号的眼图。

1.2m序列发生器的选择方案一:硬件电路实现。

采用线性反馈移位寄存器通过加法器的逻辑组合电路实现。

该电路具有产生序列速度快特点和硬件电路固有的不便修改特性,且只能对一些特殊的本原多项式有效。

方案二:软件电路实现。

采用FPGA设计产生m序列发生器。

通过写入VHDL语言,在FPGA中实现m序列移位寄存器结构,并最终产生m序列。

简易数字信号传输性能分析仪的设计

p r o c e s s . A d i g i t a l s i g n a l g e n e r a t o r , a p s e u d o r a n d o m s i g n a l g e n e r a t o r ( a n a l o g n o i s e s o u r c e ) , a l o w - p a s s i f l t e r , a a d d e r , a n d a d i g i t a l s i g n a l a n a l y s i s c i r c u i t w e r e c o m p l e t e d . T h e s y s t e m g e n e r a t e s a d i g i t a l s i g n a l s e q u e n c e( t h e M s e q u e n c e Ma n c h e s h i t e c o d i n g s e q u e n c e )a n d a p s e u d o n o i s e s e q u e n c e ( p s e u d o r a n d o m s i g n a 1 )b y u s i n g

( 江西理l T 大学 电气 工 程 与 自动 化 学 院 , 江西 赣 州 3 4 1 0 0 0 )

摘 要 : 为 了更好 地分 析数 字信 号在传 输过 程所 受码 间干扰和 噪音 等 因素的 影响 , 文 中设计 了一

个 以F P G A 为核 心的 简 易数 字信 号 传输 性 能分析仪 , 完成 了数 字信 号发 生 器、 伪 随机信 号发 生 1 0月

江 西 理 工 大 学学报

S c i e n c e a n d T e c h n o l o g y J o u r n a l o f J i a n g x i Un i v e r s i t y o f

2011大学生电子设计竞赛题目

2011年全国大学生电子设计竞赛试题参赛注意事项(1)2011年8 月31 日8:00 竞赛正式开始。

本科组参赛队只能在【本科组】题目中任选一题;高职高专组参赛队在【高职高专组】题目中任选一题,也可以选择【本科组】题目。

(2)参赛队认真填写《登记表》内容,填写好的《登记表》交赛场巡视员暂时保存。

(3)参赛者必须是有正式学籍的全日制在校本、专科学生,应出示能够证明参赛者学生身份的有效证件(如学生证)随时备查。

(4)每队严格限制3 人,开赛后不得中途更换队员。

(5)参赛队必须在学校指定的竞赛场地内进行独立设计和制作,不得以任何方式与他人交流,包括教师在内的非参赛队员必须迴避,对违纪参赛队取消评审资格。

(6)2011年9 月3 日20:00 竞赛结束,上交设计报告、制作实物及《登记表》,由专人封存。

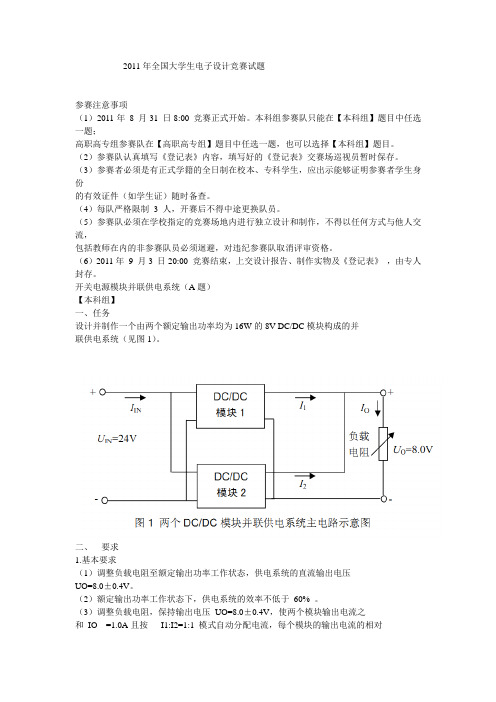

开关电源模块并联供电系统(A题)【本科组】一、任务设计并制作一个由两个额定输出功率均为16W的8V DC/DC模块构成的并联供电系统(见图1)。

二、要求1.基本要求(1)调整负载电阻至额定输出功率工作状态,供电系统的直流输出电压UO=8.0±0.4V。

(2)额定输出功率工作状态下,供电系统的效率不低于60% 。

(3)调整负载电阻,保持输出电压UO=8.0±0.4V,使两个模块输出电流之和IO =1.0A且按I1:I2=1:1 模式自动分配电流,每个模块的输出电流的相对误差绝对值不大于5%。

(4)调整负载电阻,保持输出电压UO=8.0±0.4V,使两个模块输出电流之和IO =1.5A且按I1:I2= 1:2 模式自动分配电流,每个模块输出电流的相对误差绝对值不大于5%。

2. 发挥部分(1)调整负载电阻,保持输出电压UO=8.0±0.4V,使负载电流IO在1.5~3.5A之间变化时,两个模块的输出电流可在(0.5~2.0)范围内按指定的比例自动分配,每个模块的输出电流相对误差的绝对值不大于2%。

XG2330 E1-数据传输分析仪

XG2330 E1/数据传输分析仪XG2330 E1/数据传输分析仪是一款手持式、大屏幕彩屏触摸操作的测试分析仪表,将E1电路测试功能和数据通信电路测试功能完美地组合在一起,用于对带有E1接口和数据接口的通信电路传输质量进行全面的分析、测量和评估。

除了支持常规的2M和数据通道误码测试功能外,不仅提供了对2M帧结构数据、双路E1监控、环路时延、倒换时延、输出波形、输出抖动、信号电平的测试和分析功能,还提供了PCM仿真、数据转换器分析、插入&分出等多种高级测试功能。

XG2330 E1/数据传输分析仪提供多达10种测试接口,可方便地进行传输网、接入网、数据网通道质量的测试,可广泛应用于SDH、PDH、PCM、DTU、数据协议转换器设备的研制、生产、安装、认证和维护测试。

1.基本功能1). E1接口测试∙终接模式(中断业务)下成帧/非成帧测试∙在线业务跨接(高阻)和通过(桥接)模式下误码监测、时隙分析及时隙语音监听∙成帧和非成帧传输环路时延测试∙自动保护倒换(APS)时延测试∙PCM仿真模式下模拟PCM端机进行多种误码插入和告警插入∙时隙语音插入、监听,具备听/说(Listen/Talk)功能∙频率、频偏及实时电平测试∙时钟滑动测试∙大频率发送时钟拉偏测试∙双路E1在线误码监测和时隙分析∙脉冲模板测试∙抖动测试(选件1)∙E1发送电路开路、短路实时指示2). 数据接口测试(选件2)∙支持V.24、V.35、V.36、X.21、RS-449、RS-485、EIA-530、EIA-530A等多种协议数据接口∙50b/s~57.6kb/s异步数据误码测试∙ 1.2kb/s~N×64kb/s同步数据误码测试∙DTE、DCE设备仿真模式∙可设置和监视数据接口握手线3). G.703 64kb/s同向接口测试(选件3)★∙G.703同向64kb/s误码测试∙八比特时序启用或关闭∙接收线路速率和频偏测试4). 复用解复用测试(选件4)★∙支持E1接口与V.24、V.35、V.36、X.21、RS-449、RS-485、EIA-530、EIA-530A等多种接口之间转换的同步64kb/s、N×64kb/s数据误码测试功能∙支持E1接口的任一64kb/s时隙与G.703 64kb/s同向接口之间转换的同步数据误码测试功能5). 插入&分出测试(选件5)★∙插入:支持数据和G.703同向接口的64kb/s、N×64kb/s数据适配插入到E1的任一或多个时隙中∙分出:支持E1任一或多个时隙数据适配分出到数据和G.703同向接口中∙插入+分出:支持E1与数据接口、G.703同向接口之间64kb/s、N×64kb/s数据的相互适配6). IP PING、TRACE测试7). 其它功能∙具备开通码控制业务模块功能∙自动配置功能∙实时时钟∙测试图案:伪随机码、固定码、16比特用户可编程码和QBF码∙单误码、比率误码插入和禁插∙历史告警指示功能∙测试结果数据清零功能∙手动、自动和定时测试∙完善的蜂鸣器、LED声光告警和状态指示∙按照ITU-T的G.821、G.826和M.2100标准进行误码分析∙通过以太网接口或USB接口,使用TestManager Pro软件,在PC上进行测量结果的进一步分析、整理、归档和打印输出2.主要特点∙创新设计,符合人体工程学,便于携带∙注重细节,护套防护、接头保护,提供挂绳、支架方式使用,适合不同现场工作∙ 4.3寸大屏幕(带背光)彩屏触摸操作,导航式中文菜单,操作简便∙大容量存储功能,可对测试设置、测试结果进行存储、删除和掉电保持∙E1、数据接口通信线路和协议转换器的全面分析、测试∙完善的误码、告警的产生、检测和指示∙告警、误码具有直方图分析和统计,简单直观∙最长99天的连续测试能力,可定时开启、关闭测试∙仪表管理软件可以标准A4工程报表方式输出测试结果∙仪表具备自动关机功能,有效节约电能∙可对仪表嵌入式软件进行在线升级,有效保护用户投资3.仪表配置1). XG2330 E1/数据传输分析仪标准配置表项目数量项目数量E1/数据传输分析仪1台可充电锂电池(内嵌)1块锂电池充电器1个触摸笔1支麦克风耳机1副快速操作指南卡1张E1非平衡电缆(75Ω) 2根TestManagerPro仪表测试管理软件CD(内含用户手册)1张直通头(75Ω) 1个仪表便携软包1个E1平衡测试电缆(120Ω) 1根产品合格证书1张双E1平衡测试电缆(120Ω) 1根产品保修卡1张USB电缆1根装箱单1张2). XG2330 E1/数据传输分析仪选件配置表选件代号选件项目获取方式需增加项目数量选件1抖动测试软件授权嵌入式软件及控制码1套选件2数据接口测试选件增加硬件硬件模块1个嵌入式软件及控制码1套专用数据通信接口测试电缆4根数据通信接口短路头1个选件3G.703同向接口测试选件增加硬件软件授权硬件模块1个嵌入式软件及控制码1套G.703测试电缆1根选件4复用与解复用测试选件软件授权嵌入式软件及控制码1套选件5插入与分出测试选件软件授权嵌入式软件及控制码1套数据接口测试电缆说明名称适用接口数据通信专用测试电缆ⅠV.24,RS-485,EIA-530,EIA-530A 数据通信专用测试电缆ⅡRS-449,V.36数据通信专用测试电缆ⅢX.21数据通信专用测试电缆ⅣV.354.技术指标项目说明E1 内部发送时钟2048kb/s ± 10ppm发送时钟拉偏±999ppm线路接口75Ω (非平衡),120Ω (平衡),高阻>2kΩ线路编码HDB3,AMI帧格式非成帧,PCM30,PCM30CRC,PCM31,PCM31CRC 接收灵敏度> -43dB发送时钟源内部,接口,外部2M时钟或2M信号脉冲模板测试符合ITU-T G.703要求抖动测试符合ITU-T G.823,O.172要求接收频率测试精度:±1Hz频偏测试精度:±1ppm,范围:-999ppm~+999ppm插入单音频信号频率范围:200Hz~3400Hz,步长:10Hz电平范围:-60dBm~+3dBm单音频信号测试频率范围:200Hz~3400Hz,精度:±1Hz电平范围:-60.00dBm~+3.14dBm时延测试精度:±1μsG.703 同向线路速率64kb/s±100ppm线路接口120Ω (平衡),DB44 线路编码AMI以太网接口速率10/100M兼容工作模式全双工物理接口RJ-45数据接口线路接口V.24,V.35,V.36,X.21,RS-449,RS-485,EIA-530,EIA-530A测试速率异步50,75,150,300,600bit/s,1.2,2.4,4.8,7.2,9.6,19.2,38.4,57.6kb/s同步1.2,2.4,4.8,7.2,9.6,19.2,38.4kb/s,N×64kb/s ( N=1~32)测试图案伪随机码223-1,220-1,215-1,211-1,29-1,26-1 固定码1111,0000,101016-BIT人工编码用户可编程QBF QBF1,QBF2,QBF3,QBF4LED 告警指示信号丢失、历史告警、图案失步、告警、误码类型:比特,FAS,CRC4,CODE,E-BIT 误码插入单误码,比率:10-2,10-3,10-4,10-5,10-6,10-7误码性能分析符合ITU-T G.821,G.826和M.2100要求通信接口以太网接口、USB接口充电电池7.4V聚合物锂电池充电时间外置智能快速充电器,充电时间大约需2小时外接电源DC8.4V/1.2ATestManagerPro适合中文WIN2000/XP仪表测试管理软件尺寸233mm ×110mm × 64mm (L×W×H)工作温度0℃~50℃储藏温度-30℃~70℃湿度5%~95% 非凝结重量约800g。

简易数字信号传输性能分析仪实现

噪声幅度在 10 0mY~TT L电平 内连 续可调 。接收端采用 了C 0 6 字锁相环 完成位 同步的提取 , D44 数 并输 出含噪信 号与位 同步信号 , 用之在 示波器上 实现传输信号的眼图显示与参数测量。 关键词 :P A; 同步; FG 位 全数字锁相环

中图分类号 : N3 1 文献标识码 : 文章编号 :09 3 4 (0 13 — 7 7 0 T 9 A 10 — 0 42 1 )1 74 — 2

c nI E 35 F8C N l e PC 544 8 实现简易数字信号传输性能分析仪的实现 , o I 其传输数据速率为 1—0K p 0 10 b 范围内以 1K p步进可调 , 0 bs 并设

p a e l c e o p d n i sn h o iai n e t ci n Th in t o s n h i s n h o o ss a a eo t u O o cl so e t h s o k d l o o e b t y c r n z t x r t . e s a wi n i a d t eb t y c r n u i l r u p tt si o c p o o a o gl h e n g l

n he rM nc se od r e st e tn i l n he u e o a d t i a he trc e ae usd a he tsi g s a,a d t s fN E55 2 a gn 3 nd AD 81 o a hiv h e ow —pasfle sw h c ut f t c e etrel 1 s t r i h c of i

பைடு நூலகம்

f q ece o 0 Hz2 0 h n 0 K n a . r u ni f 0 K , 0K zad5 0 Hzadgi i 0 e s 1 n n 2~4r g j sbe A n o anl d iv os po u e ya yl o n ea ut l naa gc n e adt e i rd cd cc f a d a . l h i n e b e 4 2 sq ec,htt a lu e s dut l cniu ul i 0mV— T v 1A es me tercie ue D44 iil 07m u ne ta i mpi d js be o t o s 10 e s t ia a n yn T Ll e th me i ,h ee r sdC 0 6dg a e . t a t v t

简易数字信号传输性能分析仪的设计

躐

幅度的M序列干扰码元后 ( 即输入信 号码 元信 噪 比很低的条件 下 ),依然能够正确提取出同步时钟信号,并正确显示 眼图。此 外 ,从图5 的眼图中可以看出,本系统设计的数字信号分析仪不仅 能够正确提取输入曼彻斯特码的同步时钟信号,而且还能够滤除

伪 随机 信号 的生成 多项式 为f ( )= +X+X +X +X 时 钟 1x 1 I 2 信号为1 MH ,F G 中需要 l个寄存器 ,并在1 MH 的时钟下 0 z P A 2 0 z 线性 反馈 和 移位输 出 。其 线 性移 位 寄存 器 的生 成原 理 图 和上 面 类

科 技 搽 i 刁

简 易数 字信号传输性能分析仪 的设计

葛 中芹 叶 猛

江苏 南京 2 0 3) 1 9 0 ( 京大 学电子 科学 与工程 学院 南

摘

要 :本文设 计 了一 个 系统 ,可 以实现 简 易数 字信 号传输 性 能分析 仪的 功能 。此分 析仪 主要 包括 三大模 块 :发 生器模 块 ,滤波 器模 块 和 接 收 器模 块 。数 字信 号发 生 器部 分采 用F G P A芯片 产生伪 随机 码 元序 列。 用三个 截止 频率 不 同的低 通 滤波 器模拟 信道 的 特性 ,接 收 端

用F G 从接 收 到 的码 元序 列 中提 取 出同步 时钟 信 号 ,并将 接收 到 的低信 噪 比信号 滤 除噪声后 在 示 波器上 显 示 出眼 图。经 测 试整 个 系统 PA 工作 稳 定 ,输 入信 号动 态 范围 大,眼 图清晰 ,误 码 率低 。 关键 词 :F G P A 伪 随机 码元 序列 同 步时钟信 号 眼 图

糍

其 中电压增益 :,o 1 R / q = + 4

㈩

E题简易数字信号传输性能分析仪设计报告

简易数字信号传输性能分析仪设计报告摘要:系统核心内容是位同步提取信号,通过利用FPGA自身锁相环完成。

系统以2片FPGA 芯片为核心,完成信号的生产和对信号的分析。

一块产生m序列的数字信号与m序列的伪随机信号,数字信号通过TTL电平转换,再经过可调低通滤波器,低频段信号与伪随机干扰信号叠加,模拟信号再经过AD转换,数字信号就直接进入数字信号分析电路进行处理。

然后再引出数输出信号和同步提取信号,通过示波器显示出眼幅度。

数字信号分析电路在FPGA里面生成,由VHDL语言实现。

该设计思路新颖,运用曼彻斯特编码传输信号波形,最后再解码分离出原信号,抗干扰性好,人机交互界面友好。

关键字: FPGA 数字信号滤波器位同步目录1方案设计与论证 (2)1.1数字信号发生器的设计方案 (2)1.2实现位同步的方法 (2)2 理论分析与设计 (2)2.1低通滤波器 (2)2.2位同步 (3)2.3 眼图 (3)2.4 总设计流程框图 (3)3 方案实现 (4)3.1 硬件部分 (4)3.1.1自制直流电源模块 (4)3.1.2 滤波器模块 (5)3.1.3 增益可调模块 (7)3.1.4 衰减器模块 (9)3.1.5 加法器模块 (10)3.1.6 AD转换器模块 (11)3.2 软件部分 (12)3.2.1 m序列数字信号的产生 (12)3.2.2 位同步信号的提取 (13)4 测试方案与结果 (14)4.1测试仪器 (14)4.2测试数据 (14)4.3问题讨论 (16)5 总结 (16)参考文献 (16)附录 (16)附录1 元件清单 (17)附录2 PCB图 (18)1方案设计与论证1.1数字信号发生器的设计方案方案一:用EWB生成数字信号发生器用四位二进制同步计数器74163和八选一数据选择器74151构成序列信号发生器实验电路,计数器状态输出端口接在数据选择器的地址输入端C,B,A,要输出的序列信号接对数据选择器的数据输入端。

2M数字传输性能分析仪说明书

目录1.概述 (3)2.仪表外观及组成 (4)2.1 前面板 (4)2.2 后面板 (8)2.3 侧面板 (9)2.4 上侧面板 (9)3.主菜单 (10)3.1 菜单选择 (10)3.2 快捷键 (11)4.测试设置 (12)4.1 Tx/Rx1/DATA端口设置 (12)4.2 CLK/Rx2端口设置 (18)4.3 其它设置 (20)4.4 打印设置 (22)5.专业设置 (23)5.1 帧信息设置 (23)5.2 同步信息设置 (24)5.3 ABCD设置 (24)6.测试结果 (25)6.1 常规测试结果 (25)6.2 直方图 (30)6.3 音频测试结果 (31)6.4 监听测试结果 (32)6.5 时延测试结果 (32)6.6 APS测试结果 (33)6.7 时隙分析结果 (34)6.8 G.703模板结果 (36)7.档案管理 (37)7.1 测试设置存取 (37)7.2 测试结果存取 (38)8.仪表设置 (39)8.1 显示设置 (39)8.2 打印设置 (39)8.3 时间设置 (40)9.应用举例 (40)9.1 2Mbit/s通道停业务误码测试。

(40)9.2 2M/s通道开业务误码测试 (41)9.3 64kbit/s通道测试 (42)9.4 时延测试 (44)9.5 音频测试 (45)9.6 数据测试 (45)9.7 自动保护倒换(APS)测试 (46)10.主要技术指标 (48)1. 概述2M数字传输性能分析仪,适用于数字传输系统的工程施工、工程验收及日常维护测试。

其性能可靠稳定、功能齐全、体积小巧,采用大屏幕中文显示,操作简洁容易。

2M数字传输性能分析仪可对2Mbit/s接口数字通道、同向64k、RS232、RS485、RS449、V.35、V.36、EIA530、EIA530A、X.21接口数字通道进行测试,具有两个2Mbit/s接口,可同时对两条通道进行测试。

简易数字信号传输性能分析仪

2011年全国大学生电子设计竞赛简易数字信号传输性能分析仪(E题)【本科组】2011年9月6日摘要本系统基于Xilinx Spartan 系列FPGA 设计的一个简易数字信号传输性能分析仪,ISE环境下使用V erilog语言编程,产生m序列,并且可以数据率10K~100K 的变化,从而实现数字信号发生器和为伪随机信号发生器。

利用信号经过低通滤波器和对伪随机信号的衰减求和来模拟传输信道。

数字信号分析电路利用锁相环来提取同步时钟,以此显示数字信号的眼图。

关键词:FPGA;m序列;信道模拟;低通滤波;锁相环;眼图;目录1系统方案 (1)1.1 信号发生模块的论证与选择 (1)1.2 低通滤波器的论证与选择 (1)1.3 电源模块的论证与选择 (2)2系统理论分析与计算 (2)2.1 低通滤波器设计 (2)2.1.1 定义: (2)2.1.2带外衰减: (2)2.2 m序列数字信号 (2)2.2.1 定义: (2)2.2.2 特性: (3)2.2.3 产生: (3)2.3同步信号提取 (3)2.3.1 定义: (3)2.3.2 原理: (3)2.3.3 通过数字锁相环同步频率 (4)2.4眼图显示方法: (4)2.42成因: (4)2.43 作用: (4)3电路与程序设计 (4)3.1电路的设计 (4)3.1.1系统总体框图 (4)3.1.2 数字信号发生子系统框图与电路原理图 (5)3.1.3 信号处理子系统框图与电路原理图 (6)3.1.4电源 (7)3.2程序的设计 (8)3.2.1程序功能描述与设计思路 (8)3.2.2程序流程图 (8)4测试方案与测试结果 (10)4.1测试方案 (10)4.2 测试条件与仪器 (11)4.3 测试结果及分析 (11)4.3.1测试结果(数据) (13)4.3.2测试分析与结论 (15)附录1:电路原理图 (16)附录2:源程序 (17)简易数字信号传输性能分析仪(E题)【本科组】1系统方案本系统主要由信号发生模块、低通滤波器模块、电源模块、数字信号分析模块,组成,下面分别论证这几个模块的选择。

YHD610 数据传输分析仪-产品介绍

YHD610 数据传输分析仪1. 产品概述YHD610 数据传输分析仪是一款手持仪表,外形小巧,大屏幕26万色彩屏,触摸和导航键操作于一体,多种语言显示;采用多接口集于一体设计,满足各种用户的需求特点,将E1、64K、T1、电力远动、网络IP Ping和V系列接口数据通信电路测试功能完美地组合在一起,用于对以上电路数据传输质量进行全面的分析、测量和评估;测试速率不仅仅包含从50b/s~2048kb/s数字信号,还包括电力远动模拟信号测试,除了支持常规数据通道误码监测测试功能外,还提供了对数据通道的环路时延、倒换时间、信号波形、信号抖动、信号电平的测试和分析功能,主要用于MSTP、SDH、PDH、PCM、DTU、DDN、Modem、数据协议转换器设备的研制、生产、安装、认证和维护测试;当然也满足T1标准测试。

2. 应用范围1) 通信设备数据传输质量测量2) 通信设备厂商研究3) 工程数据业务开通4) 设备和传输线路检修5) 运营商日常维护3. 产品特点1) 体积小,携带方便2) 多种接口集于一体,适应数字、模拟电路多领域测试3) 数据电路、线路全面测试功能4) bit、Code、FAS、CRC多种类型误码监测及分析5) 采用4.3寸宽屏幕真彩触摸显示6) 中文简体、英文和中文繁体多种语言任意切换7) 触摸和导航键一体,操作得心应手8) 智能自动保护;节电设计;自动屏保9) 采用行业内嵌入式系统设计的高性能、低功耗的32位微处理器10) 可充电锂电池,续航8小时以上11) 不开机可查看电池电量12) 支持U盘拷贝数据13) 内置2G容量记录存储空间,可扩展最高16G14) 可在线升级软件15) 全面的PC机数据管理系统16) 自动测试功能4. 产品功能◆E1功能✓中断业务、在线业务、通过业务、PCM音频、环路时延(同时测试8次结果)和倒换时间测试✓多种告警具有独立的指示灯和屏幕状态告警指示:无信号;AIS;帧丢失;复帧丢失;对告;图案丢失;误码;历史告警。

VePAL TX300e-10G 传输分析仪

Specifications

STM-1/4 (155/600 Mbps)

STM-1/4/16 (155/622/2488 Mbps)

Optical option Wavelength (nm) Range (km) Line rate (Mbps) Connector Line Coding

301-01-004G 301-01-005G 301-01-006G 301-01-007G 301-01-008G 301-01-009G

时钟同步

内部:±3.5ppm 稳定性符合ITU-T G.812 恢复:从接收信号通过SMA连接器的外部参数 ● 时钟:2.048 MHz,1.544 MHz (sine wave or TTL) ● 信号:2.048 Mbit/s (HDB3),1.544Mbit/s(B8ZS) Tx

频率偏移: ● 从25,000 ppm到0.1ppm步长的光口和电口

测量方式:中断方式,监测方式,穿通方式 ● 变更选择 SOH bytes ● 告警产生和错误注入 非注入通过方式 ● 信号透传

STM64, OC-192 (9.953 Gbps)

301-04-002G

301-04-003G

301-04-004G

1310 10 9.953G to 11.1G LC Duplex NRZ

1550 40 9.953G to 11.1G LC Duplex NRZ

1550 80 9.953G to 11.1G LC Duplex NRZ NRZ

DFB 1290 to 1330 2.5 -6 to -1

PIN

EML 1530 to 1565 1 -3 to +2

PIN

EML 1530 to 1565 1 0 to +4

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

摘要本系统采用ALTERA公司生产的EP3C25Q240C8FPGA作为控制核心,实现了数字信号传输性能测试,并且能较为准确的显示眼图。

其中,m序列的时钟信号采用PS2键盘输入,可以实现10Hz到1MHz连续可调,伪随机信号采用同轴电缆进行传输信号,实现了峰峰值50mVpp到5V连续可调。

在数字信号分析处理部分实现了输入曼彻斯特编码输入后同步时钟的提取,提取的时钟可以用来触发输入的原始数字信号观察眼图的形状。

在显示部分利用了VGA显示器,在SDRAM做显存配合下实现了波形和其他信息的显示,显示分辨率为800x600,显示效果很清晰,可以实现信号的分辨和其他信息的显示。

输入波形级处理上可以减小随机噪声的影响,整理出数字信号。

关键字:FPGA VGA显示 AD采样 SDRAM一、方案论证本题已经给出了系统框图如图1所示,包括以下几个模块:信号发生模块、低通滤波器、信号叠加模块、数字信号分析电路、显示模块等。

下面就各模块的方案进行比较和论证。

1.信号发生模块按照题目要求,信号发生模块包括数字信号发生器和伪随机信号发生器,要求为m序列。

其中。

数字信号发生器输出要求采用曼彻斯特编码。

方案一:利用传统的硬件电路设计实现:m序列和伪随机信号可使用硬件移位寄存器和多路异或门来设计实现,然而它的两种结构延时大,工作速度低,序列的级数受限制等缺点。

曼彻斯特编码的产生可以用曼彻斯特编解码器,而且这种器件的最高速率只有1MB/s,是对串行信号进行编解码,在电路设计中需要专门的并/串、串/并转换支持,增加了设计成本。

方案二:利用FPGA可编程逻辑器件实现。

FPGA内部为逻辑门电路,应用内部逻辑门产生移位寄存器和异或门来产生m序列和伪随机信号简单易行,具有占用硬件资源较少,实现方便,速度高且级数不受限制等优点。

因此,采用方案二。

2.低通滤波模块方案一:采用无源低通滤波。

无源滤波包括RC和LC滤波,然而无源滤波电路的通带放大倍数及其截止频率都随负载变化而变化,这个缺点常常不符合信号处理要求。

方案二:采用有源滤波。

有源滤波电路一般由RC网络和集成运放组成,可以对输入的信号进行滤波和放大,适用于信号处理。

经比较,因为题目要求滤波器的通带增益在0.2~4范围内可调,所以我们采用有源滤波对信号进行处理。

3.曼码同步时钟提取将AD信号转换为数字信号后,就需要从中提取出同步时钟了。

根据曼码的编码特性,其每位传输中都有一次电平的跳变,所以可以较为容易的提取同步时钟方案一:直接通过中间传输的数据来提取同步时钟。

因为曼码每个码元中间必有一次跳变,所以通过检测跳变边沿间隔长度可以得到两个时间,一为曼码时钟周期的1/2,另一个为曼码时钟周期。

通过程序电路测试即可得出曼码时钟周期,由于每次采样都会有一定的偏差,所以为了满足时钟的统计特性,需要对多次采集的结果进行求和后取平均值为得到的值。

方案二:采用第二种方案与曼彻斯特接收码配合生成同步时钟方案三生成的时钟误差在较长时期内的积累量会造成眼图无法识别,所以缩短时钟的适应长度同时频繁更新时钟便是一种可选方案。

在使用第二种方案生成周期计数后,附加一级输入信号边沿检测跳变判断,综合生成时钟跳变为一种方案。

原理为曼码的跳变沿必定对应着时钟的一个跳变沿,所以可以利用曼码的跳变沿对方案二生成的时钟进行实时重置达到同步的效果。

4.眼图显示模块方案一:采用示波器观察输出的眼图,输出的时钟接外部触发,然后示波器上就显示眼图。

方案二:VGA为FPGA驱动,信号经由AD转换为数字信号送入FPGA经转换后存入SDRAM中,然后多次采样信号叠加显示在VGA显示器上。

此方案可以极大的减少传输后信号转换前走线长度,较为真实的还原原传输线的特性。

但是此方案会带来SDRAM同时用为显存而产生的争用仲裁问题,访存策略会复杂些。

5.电平调整电路方案一:采用模拟开关。

将FPGA的输出端加到模拟开关的控制端,通过控制开关的通断,产生TTL电平的数字信号。

方案二:采用高速运放放大再加电压跟随。

先将输入信号用电阻分压衰减到一定值后再通过比例放大器放大。

根据要求,伪随机信号要求幅度可调,所以我们采用方案二二、理论分析与计算1.低通滤波器模块我们需要设计截止频率为100K、200K、500K的有源低通滤波器,而且滤波器的通带增益在0.2~4范围内可调,所以我们采用无限增益多路反馈滤波电路。

电路图如图2-1所示:图2-1 无限增益多路反馈滤波电路图●滤波器带外衰减计算:根据要求滤波器带外衰减不少于40 dB/十倍频。

理论上采用二阶滤波就可以到到要求,但由于示波器探头的干扰,测量的衰减不明显,所以采用两个2阶滤波器组合构成4阶有源低通滤波。

●截止频率参数计算在图3电路中,当f=0时,和均开路,故通带放大倍数为-=,传递函数为++++=则截止频率为π=,品质因数为=计算时,首先决定基准电容器的CO 容量,由于省去了输入缓冲放大器,所以应尽量选取小的容量。

再根据决定的容量,应用公式计算基准电阻RO 。

下面是截止频率时各元件的计算方法。

===⋅=⨯=+⋅==+=● 滤波器通带参数计算有源滤波的输出增益可调,通过调节图中来改变输出增益值,通过调节两级的参数,可以实现增益0.2~4范围内可调。

2. 数字信号产生模块 ● m 序列产生部分由数字信号的特征方程式f1(x)=++++得,为8级m序列,且=====,====,其8级m序列线性反馈移存器结构如图2-2所示:图2-2 8级m 序列线性反馈移存器结构所示其线性移位寄存器表示为:<=;反馈函数方程式为:<=( xor xor xor )● 伪随机信号产生部分 由数字信号 的特征方程式f2(x)=++++得,为12级伪随机信号,且=====,========,其12级伪随机序列线性反馈移存器结构如图2-2:图2-2 12级伪随机序列线性反馈移存器结构3.数据率的产生FPGA产生时钟普遍采取的方式为计数比较方式,但是这种方式存在一个缺陷,只能生成指定周期整数倍的时钟,不能完全随机指定频率。

本次设计中我们采取了一个改进后的方案,即进行定点小数对比累加方式进行时钟生成,此种方式生成的时钟可以保证在一段时间(取决于定点小数的位数,在此为65536个生成时钟周期)的统计特性上达到小数位数最小步进值乘以生成周期的精度。

虽然无法保证每个周期长度都完全相等,误差在+-主时钟周期(在此为100ns)以内,但只要生成时钟的周期远大于这个值,即可忽略其左右的偏移。

本次设计中此种方案完全满足要求。

4.同步信号提取模块生成的时钟误差在较长时期内的积累量会造成眼图无法识别,所以缩短时钟的适应长度同时频繁更新时钟便是一种可选方案。

在使用第二种方案生成周期计数后,附加一级输入信号边沿检测跳变判断,综合生成时钟跳变为一种方案。

原理为曼码的跳变沿必定对应着时钟的一个跳变沿,所以可以利用曼码的跳变沿对方案二生成的时钟进行实时重置达到同步的效果。

5.眼图显示模块考虑到本次设计显示需求和性能需求,我们选择第二种方案,即由VGA显示所有内容。

采用FPGA芯片可以很好的满足VGA显示的时序要求,同时板上的大容量SDRAM可以充当显存,在满足VGA时序要求的同时还可以留出用来存取其他非显示信息的时间,包括存储的波形等,灵活性很高。

VGA的显示分辨率可以达到800X600,分辨率75Hz,颜色位数12bit,显示效果很清晰,完全满足要求。

波形的显示需要重叠多组,为了反映出重叠点的密集程度,我们采用点计数日光可见光谱过度多色显示方法,通过颜色的不同直接反映出点出现概率的大小,较好的反映出波形的特性。

6.TTL电平调整模块题目中要求信号输出为TTL电平问题,而FPGA的I/O口输出为3.3V电平,所以我们需要把3.3V电平转换为5V电平,设计电路图如图2-3所示图2-3 TTL 电平调整电路我们使用先用100Ω电阻分压,将信号衰减一定的幅度,然后在后面加上运放进行一定比例的同相比例放大,为了提高它的带载能力,在同相放大后面加上电压跟随器,所以只需调节电位器R5就可以使输出的电平从高到低的任意数值变化。

三、 系统电路设计1. 系统组成系统框图如图3-1所示:图3-1 系统结构框图系统主要由7个模块构成:PS2输入模块、数字信号产生模块、电平调整模块、信号叠加模块、数字信号分析模块、VGA 显示模块、SDRAM 控制模块。

系统采用PS2对数据率进行数据输入,然后由FPGA 处理后产生相应的m 序列或曼彻斯特编码,数据率为10到100kbps 连续可调,然后将信号送入低通滤波器,从滤波器输出的信号与隔直的伪随机信号相叠加,送入高速AD 进行信号采集,经过FPGA 处理后,输出同步时钟,当同步时钟接入示波器的外部触发时,将叠加信号送入示波器任一通道,示波器上生成眼图,并且可以在VGA 上显示眼图。

2.各模块电路结构●低通滤波器设计低通滤波器采用4阶无限增益多路反馈滤波电路,图3-1为截止频率为200K时的滤波电路图3-1截止频率为200K时的滤波电路●T TL电平调整电路TTL电平调整电路如图2-3所示,通过改变电位器的电阻值可以使输出的电压值线性变化。

因为电位器后级有放大电路,而运放为±15V供电,所以输出的电平完全能达到100mV到TTL电平变化。

●信号叠加模块系统在伪随机信号的输出端加上了一个隔直电容,把直流偏移隔掉,相当于在那是两个交流信号的叠加,我们采用两级反相比例的加法电路,可以使共模输入电压为0。

电路图如图2-4所示:图2-4 信号叠加模块●AD输入模块本系统采用美国德州仪器的8位半半闪速结构的高阻抗并行AD,它采用CMOS工艺制造,能在高速数据转换的时候能够保持较低功耗,可提供最小20MSPS的采样率。

具体电路图如图2-5所示:图2-5 AD 采样电路显示模块为了达到较好的显示效果和IO 管脚分配的问题,本系统选择了通信协议较为简单的VGA 协议外接显示器显示。

VGA 显示需要较大容量的RAM 作为显示存储器,所以选择开发板上的片外SRAM 作为显存。

文字以软件生成16x16点阵字模形式给出。

为了让输出波形其看起来更连贯,我们采用了波形显示修正方案,将孤立的点连成线。

考虑到SRAM 的容量速度以及显示的要求,选择分辨率为800X600,刷新率为60Hz 。

采取如下控制方案:由VGA 模块生成一个Enable(SRAM 占用)信号,但此信号向外引出,可由其他模块读取。

对于较长时间连续数据可以外用模块外FIFO 作为缓存,而SRAM 控制器专注于写入读取请求处理。

四、 系统程序设计1、数字信号发生电路 如图4-1所示:图4-1 数字信号发生电路2、SDRAM 仲裁状态机如图4-2所示:图4-2 SDRAM仲裁状态机3、曼彻斯特编码同步时钟检测如图4-3所示:图4-3 曼彻斯特编码同步时钟检测五、测试方案与测量结果1.测试仪器数字存储式示波器、函数发生器、数控式线性直流稳压电源2.测试方案及结果m序列时钟信号测试的I/O口引出,然后用示波器观察输出波形的频率,计算与预将FPGA产生设输入波形的频率的误差。