微机原理及接口技术-CH6

微机原理及应用ch6-stu

微机的外部设备多种多样 工作原理、驱动方式、信息格式、以及工作速度方面彼 此差别很大 因此必须经过中间电路再与系统相连, 这部分电路被称为I/O接口电路

I/O接口完成的功能

⑴ 对输入输出数据进行缓冲和锁存 ⑵ 对信号的形式和数据的格式进行变换

⑶ 对I/O端口进行寻址

24

查询传送的两个环节

⑴ 查询环节 • 寻址状态口 • 读取状态寄存器的标志位 • 若不就绪就继续查询,直至就绪 ⑵ 传送环节 • 寻址数据口 • 输入,通过IN指令从数据端口读入数据 • 输出,通过OUT指令向数据端口输出数据

输入状态

N

就绪? Y 数据交换

25

查询传送流程

26

查询传送的两个环节

+5V

…

LED0

K7

CLK

LS273 8D 锁存器

数据 驱动器

+5V …

LED7 ;DX指向数据端口 ;从输入端口读开关状态 ;送输出端口显示 ;调子程序延时 ;重复

next:

mov dx,8000h in al,dx out dx,al call delay jmp next

22

第六章 输入/输出及接口

6.1 6.2 I/O接口概述 无条件传送方式及其接口

6.3

6.4 6.5

查询传送方式及其接口

中断传送方式及其接口 DMA传送方式

23

6.3 查询传送方式及其接口

程序查询方式(条件传送)基本原理

CPU在执行程序时需要不断查询外部设备的状态,如果设 备的数据传送没有准备好,CPU就反复查询;只有当设备就绪 (READY),CPU才能用I/O指令传送一个数据。 就绪? 就绪:满,空、闲、不忙

接口CH6

第6章 中 断

主 编 副主编

刘彦文 高 爽

张向东 刘 彤

谭 峰

中国林业出版社

6.1 概 述

中断是计算机所具有的非常重要的功能,具有中断功能的 CPU可以实现: (1) 与外设同步工作。即CPU启动需进行通信的外设,与外 设并行工作。当外设具备与CPU进行数据通信的条件后, 中断CPU并与之进行数据交换。基于这种方法,CPU可以 同时与多个外设同步工作。 (2) 实现实时处理。在计算机实时控制系统中,现场传感器 信号和驱动装置都能利用中断功能及时得到CPU的处理。 (3) 故障处理。计算机在遇到诸如电源掉电、存储器出错、 溢出等随机问题时,利用中断功能可以自行处理,不需停 机或人工干预。 (4) 在现代微型计算机中,使用中断功能可以实现多道程序 和多重任务的并行工作。

/200609/25

5

2. 中断响应 对于可屏蔽的硬件中断请求,CPU执行程序的时 候,在每条指令执行过程中检测判断有无中断请求 信号。当CPU检测到中断请求信号,且内部的中断 允许触发器的状态为1,允许中断时,CPU在执行 完现行指令后,发出INTA中断响应信号。 图6.2所示为CPU内部产生中断响应信号的逻辑电 路。对于8086/8088 CPU可以用开中断(STI)或关中 断(CLI)指令来改变中断允许触发器IF标志位的状态。 从图6.2可以看出,一旦CPU发出中断响应信号,应 立即清除中断请求信号,以避免一个中断请求被 CPU多次处理。

/200609/25

22

图6.7 8086/8088中断源

/200609/25

23

6.2.1 8086/8088外部中断

外部中断是由CPU引脚引入的请求信号。 8086/8088 CPU有两条外部中断请求引脚:NMI(非 屏蔽中断)和INTR(可屏蔽中断)引脚。 1. 非屏蔽中断NMI 从引脚NMI引入的中断请求信号称为非屏蔽中断, 上升沿有效,并且不受标志寄存器中IF位的影响。 其信号一旦有效,CPU在执行完现行指令后,立即 响应。非屏蔽中断一般用于紧急故障处理,如电源 故障、存储器错等。中断类型码为2。

ch6输入输出接口

主讲教师 王秀青

河北师范大学 职技学院 应用信息技术系 王秀青

第6章 微型计算机的输入输出

一、接口的基本概念 二、输入输出的寻址方式 三、CPU与外设交换信息的控制方式

作业

2020/1/11

微型计算机的输入输出

2

河北师范大学 职技学院 应用信息技术系 王秀青

一、接口的基本概念

2020/1/11

微型计算机的输入输出

22

河北师范大学 职技学院 应用信息技术系 王秀青

1、程序控制方式

(1)无条件传送控制方式 这是一种简单的数据传送方式,适用于任何时

候均处于“准备就绪”状态的外部设备,CPU可以 随时执行I/O指令来完成数据传送操作。认为外设随 时处于准备状态

(2)条件传送控制方式 ①查询输入 ②查询输出 例题

2020/1/11

微型计算机的输入输出

20

河北师范大学 职技学院 应用信息技术系 王秀青

8086/8088的I/O指令

(1)直接端口寻址方式 对于端口PORT的地址范围是8位,即00H—FFH

IN AL, PORT ;端口PORT的字节信息送AL OUT PORT, AL ;将AL的数据信息送到端口PORT IN AX, PORT ;端口PORT的字信息送AX, 即端口

②查询输出

D_PORT S_PORT

接口

数据端口地址

状态端口地址

数据端口(8位) 状态端口(1位)

BUSY(1位)

输入状态信息 Y

BUSY? N

准备输出数据

取数并输出数据

CPU输出数据前,先查询外设的状态端口的状态信息, 若为“空”(如BUSY=0,表示空闲),则执行输出指令把数 据送入I/O接口的数据端口。

ch06

11

6.2 I/O端口及其编址方式

计算机系统通过一组总线来连接系统的 各个功能部件,包括CPU、内存和I/O端口, 各功能部件之间的信息交换通过总线来进 行,如何区分不同内存单元和I/O端口,是 输入/输出编址方式所要讨论和解决的问题。

2014-2-22

>>微机原理<<

12

6.2 I/O端口及其编址方式

DMA操作过程

准备阶段

DMA控制器接受 CPU对其进行初始 化。设置存储器的 地址、传送的数据 字节数,工作模式 和传送方向以及对 相关的各接口电路 初始化设置

传送结束阶段

DMA控制器在传 送完成后向CPU 发出结束信号, 以便CPU撤消总 线允许信号收回 总线控制权。

数据传送阶段

2014-2-22

条件传送

在传送数据之前, CPU要执行查询程序 去查询外设的当前状 态,只有当外设处于 准备就绪(输入设备) 或空闲状态(输出设备) 时,才执行输入或输 出指令进行数据传送, 否则,CPU循环等待, 直到外设准备就绪为 止

2014-2-22

>>微机原理<<

21

6.3 CPU与I/O接口之间的数据交换方式

2014-2-22

>>微机原理<<

8

6.1 I/O接口概述

接口电路 数据缓冲 /锁存器 读/写/中断 控制逻辑 数 据 总 线 控 制 总 线 地 址 总 线 端口地址 译码 数据线 数据端口

控制线 控制端口 状态线 状态端口

外部 设备

I/O接口的基本结构

2014-2-22 >>微机原理<< 9

6.1 I/O接口概述

微机原理与接口技术CH

存储器包括硬盘、U盘、光盘等。

内存储器的特点是存取速度快 ,但容量较小;外存储器的特 点是容量大,但存取速度较慢 。

存储器的容量和速度是评价微 机性能的重要指标。

输入输出接口

输入输出接口是微机中用 于连接外部设备和软件的 部件。

输入输出接口的种类繁多, 不同的设备需要不同的接 口。

组成

微机由中央处理器、存储 器、输入输出接口等部分 组成。

微机的发展历程

第一代微机

以8位微处理器和汇编语言为主要 特征,出现于上世纪70年代初期

,主要用于科研和教学领域。

第二代微机

以16位微处理器和高级语言为主要特 征,出现于上世纪80年代初期,广泛 应用于工业控制和自动化领域。

第三代微机

以32位微处理器和操作系统为主 要特征,出现于上世纪90年代初 期,成为计算机的主流产品。

总线的性能指标包括数据传输速 率、传输方式、总线宽度等。

03

微机的指令系统

指令的基本格式

操作码

01

表示指令操作的性质,如加、减、乘、除等。

操作数

02

表示要操作的数据或数据所在的地址。

寻址方式

03

表示如何找到操作数所在地址,如立即寻址、寄存器寻址、内

存寻址等。

指令的分类与功能

数据传输指令

用于在寄存器、内存和输入/输出设 备之间传输数据,如MOV指令。

ABCD

常见的输入设备包括键盘、 鼠标、触摸屏等,常见的 输出设备包括显示器、打 印机等。

输入输出接口的性能指标 包括数据传输速率、数据 传输方式等。

总线

总线是微机中用于连接各部件的 通信线路。

微机原理及应用CH6 总线技术与I/O接口基础

(1)模块化的小板结构、开放式的灵活组态

STD 总线使得微机系统被划分成若干模块,并

制作成标准的功能模板(插件卡)。用户可根据需

要选择功能模板组成自己的微机,插件卡与外设之 间可用其他方式连接,因此可以灵活方便地构成适 应不同要求的微机系统。图6.5是基于STD总线的微 机系统的典型结构。

微机原理及应用

(2信号、1电源、1地)

引脚数目 25、 9 同上 同上 4 24

推出年份 1962年推出 1969年公布 1977 1983 1996 1975年推出 1977年公布

自动测试系统 并行接口总线

微机原理及应用

1. RS-232C、RS-422A和RS-485总线 (1)RS-232C总线 RS-232C是一种串行通信总线标准,也是数据终端 设备(DTE)和数据通信设备(DCE)之间的接口标准, 是1969年由美国电子工业协会(EIA)从CCITT远程通 信标准中导出的一个标准。当初制定这一标准的目的 是为了使不同厂家生产的设备能达到接插的兼容性, 这个标准只保证硬件兼容而不保证软件兼容。 RS-232C标准包括机械指标和电气指标,其中机械 指标规定:RS-232C标准接口通向外部的连接器(插针 和插座)是一个“D”型保护壳25针插头。

微机原理及应用

表6.3 微型计算机通信中常用的RS-232C接口信号

息通路。如CPU内部ALU、寄存器组、控制器等部件之

间的总线。 局部总线(也称内部总线):通常指微机主板上各部 件之间的信息通路。由于是一块电路板内部的总线, 故又称在板局部总线。较典型的局部总线如:IBMPC总线,ISA总线,EISA总线,VL和PCI总线等。

微机原理及应用

系统总线(也称外部总线):是指微机底板上的总线, 用来构成微机系统的各插件板、多处理器系统各CPU 模块之间的信道。较典型的系统总线如:STD-BUS, MULTI-BUS,VME等。 通信总线:它是微机系统与系统之间、微机系统与其 它仪器仪表或设备之间的信息通路。这种总线往往不 是计算机专有的,而是借用电子工业其它领域已有的 总线标准并加以应用形成的。流行的通信总线如: EIA-RS-232C、RS-422A、RS-485,IEEE-488, VXI等总线标准。

课后作业答案Ch6 微型计算机原理与接口技术课件

6.9 在中断服务程序的入口处,为什么常常要使用开中断指令?

解:中断服务程序分为两种,一种是在进入服务子程序后不允许被中断,另一种则可以被中断。

在入口处使用开中断指令表示该中断服务程序是允许被中断的服务程序,即在进入服务子 程序后允许CPU响应比它级别高的中断请求。

4

6.10 试说明8088CPU可屏蔽中断的响应过程。 解:可屏蔽中断的响应过程主要分为5个步骤,即: (1)中断请求。外设在需要时向CPU的INTR端发出一个高电平有效的中断请求信号。 (2)中断判优。若IF=1,则识别中断源并找出优先级最高的中断源先予以响应,在其处理完后,再

64利用三态门芯片74ls244作为输入接口接口地址为40fbh试画出其与8088系统总线的连1374ls244e1e2i0i165某输入接口的地址为0e54h输出接口的地址为01fbh分别利用74ls244和74ls273作为输入和输出接口

第6章 输入输出和中断技术

6.1 I/O接口的主要功能有哪些? 有哪两种编址方式?在8088/8086系统中采用哪一种编址方式? 解: I/O接口主要需具有以下几种功能: (1)I/O地址译码与设备选择。保证任一时刻仅有一个外设与CPU进行数据传送。 (2)信息的输入输出,并对外设随时进行监测、控制和管理。必要时,还可以通过I/O接口向CPU发出中断请求。 (3)命令、数据和状态的缓冲与锁存。以缓解CPU与外设之间工作速度的差异,保证信息交换的同步。 (4)信号电平与类型的转换。I/O接口还要实现信息格式转换、电平转换、码制转换、传送管理以及联络控制等功

能。 I/O端口的编址方式通常有两种:一是与内存单元统一编址,二是独立编址。8088/8086系统采用I/O端口独立编 址方式。 6.2 试比较4种基本输入输出方法的特点。(不要求) 解:在微型计算机系统中,主机与外设之间的数据传送有4种基本的输入输出方式: 无条件传送方式、查询工作方式、中断工作方式、直接存储器存取(DMA)方式。 它们各自具有以下特点: (1)无条件传送方式适合与简单的、慢速的、随时处于“准备好”接收或发送数据的外部设备,数据交换与指令 的执行同步,控制方式简单。 (2)查询工作方式针对并不随时“准备好”、且满足一定状态才能实现数据的输入/输出的简单外部设备,其控制 方式也比较简单,当CPU的效率比较低。 (3)中断工作方式是由外部设备作为主动的一方,在需要时向CPU提出工作请求,CPU在满足响应条件时响应该 请求并执行相应的中断处理程序。这种工作方式使CPU的效率提高,但控制方式相对较复杂。 (4)DMA方式适合于高速外设,是4种基本输入/输出方式中速度最高的一种。

Ch6

中断服 务程序

6 中断系统

6.1 概 述

中断工作过程

开中断:允许响应中断请求 中断服 原程序 务程序 关中断:禁止响应 中断 应 矢量 使用中断术语,描述中断 断响 中 中断请求 中 工作过程:计算机执行原 断 源 程序,某中断源突然发出 中断 返回 断点 中断请求,计算机若允许 返回 指令 响应该中断请求,则暂停 执行原程序、转去执行中 断服务程序;若不允许,则继续执行原程序;执行中断服务程序结束后, 中断返回,返回到断点处继续执行原程序。

6 中断系统

6.3 中断编程与应用

中断编程

中断服务程序 清除中断请求:一旦响应中断请求,必须立即清除中断源。否则,中 断服务程序执行结束后,该中断请求信号会再次得到CPU的响应。 TF0和TF1:响应中断请求后,自动复位; TI和RI:在中断服务程序中使用指令(CLR TI、CLR RI)进行复位; /INT0、/INT1:下降沿触发时,自动复位; 电平触发时,先使中断请求信号无效,再手动复位。 保护与恢复断点现场 参数传递:入口参数、出口参数。 中断功能程序 中断嵌套:中断响应后,将自动关闭中断。如果希望在中断服务程序 能响应更高级的中断,必须打开中断。 中断返回: RETI

中断分类

根据中断源类型:硬件中断、软件中断(中断指令) 根据计算机对中断响应的控制能力:可屏蔽中断、不可屏蔽中断

6 中断系统

6.1 概 述

中断优先级

当由多个中断源同时发出中断请求时,先响应优先级高的中断请求; 当优先级高的中断服务完成后,再响应优先级较低的。

中断嵌套

当正在为一个中断服务时,又出现了新的 中断请求时,可以响应另外一个更高优先 级的中断请求,就像子程序嵌套。

微机原理ch6

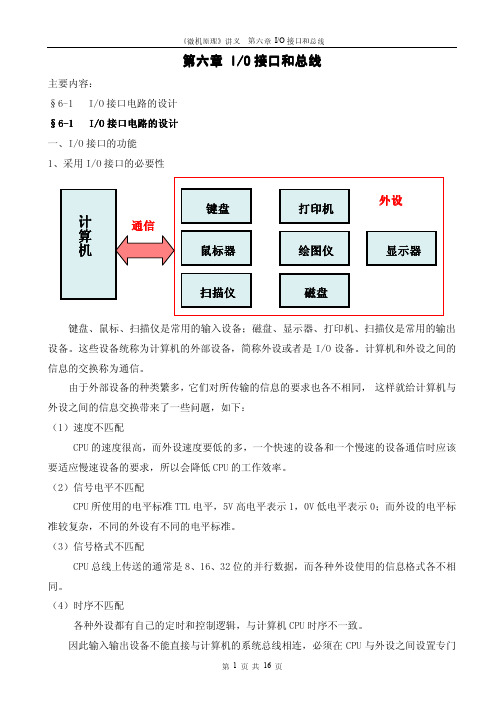

I/O接口和总线 第六章 I/O 接口和总线主要内容: §6-1 §6-1 I/O 接口电路的设计 接口电路的设计 I/O 接口电路的设计一、I/O 接口的功能 1、采用 I/O 接口的必要性键盘通信 鼠标器 绘图仪 显示器扫描仪键盘、鼠标、扫描仪是常用的输入设备;磁盘、显示器、打印机、扫描仪是常用的输出 设备。

这些设备统称为计算机的外部设备,简称外设或者是 I/O 设备。

计算机和外设之间的 信息的交换称为通信。

由于外部设备的种类繁多,它们对所传输的信息的要求也各不相同, 这样就给计算机与 外设之间的信息交换带来了一些问题,如下: (1)速度不匹配 CPU 的速度很高,而外设速度要低的多,一个快速的设备和一个慢速的设备通信时应该 要适应慢速设备的要求,所以会降低 CPU 的工作效率。

(2)信号电平不匹配 CPU 所使用的电平标准 TTL 电平,5V 高电平表示 1,0V 低电平表示 0;而外设的电平标 准较复杂,不同的外设有不同的电平标准。

(3)信号格式不匹配 CPU 总线上传送的通常是 8、16、32 位的并行数据,而各种外设使用的信息格式各不相 同。

(4)时序不匹配 各种外设都有自己的定时和控制逻辑,与计算机 CPU 时序不一致。

因此输入输出设备不能直接与计算机的系统总线相连,必须在 CPU 与外设之间设置专门1 16线总和口接外设 打印机 磁盘页章六第 义讲》理原机微《 共页 第计算机 计算机 计算机 计算机I/O接口电路。

2、接口功能 接口电路是专门为解决 CPU 与外设之间不匹配而设置的电路,它一般应具备以下基本功 能: (1)设置数据缓冲器解决速度不协调问题 经常使用锁存器和缓冲器实现此功能。

(2)设置信号电平转换电路 通过在接口电路中设置电平转换电路解决外设和 CPU 之间信号电平不一致的问题。

(3)设置信息转换逻辑以满足对各自格式的要求 将外设信息的格式转换成 CPU 可以接受的格式,如:通过 ADC 将模拟量转换成计算机可 以接受的数字量;或者通过 DAC 将计算机送出的数字量转换成模拟量去驱动外设工作。

《微机原理与接口技术》作业(修订)

*教材:中国科大《微型计算机原理与接口技术》第5版*思考题:不用写在作业本,不用上交作业;*书面题:z写在作业本上,周一上课前上交作业;z作业本必须有封面,写清课程名、班级、学号、姓名;z作业题标清题号,抄写题目;z答题留有间隙或空行。

CH1思考题:1-5、10、11、13【1.1】将下列二进制数转换成10进制数。

(1)11001010B (2)00111101B (3)01001101B (4)10100100B 【1.2】将下列16进制数转换成10进制数。

(1)12CH (2)0FFH (3)3A8DH (4)5BEH 【1.3】将下列10进制数分别转换成二进制数和16进制数。

(1)25 (2)76 (3)128 (4)134【1.4】求出下列10进制数的BCD码(压缩的BCD码和非压缩的BCD码)。

(1)327 (2)1256【1.5】将英文单词About和数字95转换成ASCII码字符串。

【1.6】求出下列10进制数的原码、反码和补码【1.7】冯•诺依曼结构的计算机由哪几部分组成?大致是如何工作的?【1.8】计算机的硬件和软件分别指什么?【1.9】什么是机器语言、汇编语言和高级语言?【1.10】画出微型计算机的基本结构框图,说明各部分的主要功能是什么。

【1.11】微型计算机系统由哪些部分组成?【1.12】说明下列名称的英文全称和中文含义。

(1)ALU (2)CPU (3)PC (4)DOS 【1.13】 8086和80386各有多少根地址总线?可直接寻址的内存空间各是多少?它们的数据总线各有多少根?CH2思考题:2-4、6、10、13-14、17-18书面题:1、5、7-9、11-12【2.1】 8086/8088CPU可直接寻址多少个内存(字节)单元?多少I/O端口?它们的外部数据总线各有多少根?【2.2】 8086CPU内部由哪两部分组成?它们大致是如何工作的?【2.3】 CPU、EU、BIU的英文全称和中文含义各是什么?【2.4】 8086CPU内部有哪些寄存器?各有什么用途?【2.5】两个带符号数1011 0100B和1100 0111B相加,运算后各标志位的值等于多少?哪些标志位是有意义的?如果把这两个数当成无符号数,相加后哪些标志位是有意义的?(参考例2.2)【2.6】说明8086引脚信号的功能:AD15~AD0、A19/S6~A16/S3、’RD、’WR、M/’IO、CLK、RESET、INTR、NMI、ALE、DT/’R、’DEN。

微机原理及接口技术CH6

独立端口编址总线结构

DB

三

AB

总CB线源自存储器 1 存储器 2 CPU

接口 1 接口 2 接口 3

存储器读写

I/O 读写 外设 1

外设 2

外设 3

端口编址方式2:存储器映像编址

(如Freescale的系列芯片)

特点:将端口看作存储单

元,仅以地址范围的不同来区 分两者。

优点:对端口的操作和对

存储单元的操作完全一样,因 此系统简单,并且对端口操作 的指令种类较多。

高位地址线与CPU的控制信号进行组合,经译码 电路产生I/O接口芯片的片选信号CS,实现系统中 的接口芯片寻址

接口地址译码的设计

接口芯片的片选信号的生成仍然可以采用存储器的译码 方式,即线译码、部分译码和全译码三种方式:

地址信号不完全

线译码

确定,所以存在地 址重叠问题,浪费

每组芯片使用一根地址线作片选 寻址空间,并可能

缺 点 : CPU 对 存 储 单 元 和

I/O端口的实际寻址空间都小于 其最大寻址空间。

统一编址总线结构

DB

三

CPU

AB

CB

总

线

存储器 1 存储器 2 接口 1 接口 2 接口 3

外设 1 外设 2 外设 3

I/O接口地址译码方法

地址译码的方法灵活多样

低位地址线直接接到I/O接口芯片的地址引脚,进 行I/O接口芯片的片内端口寻址

G2A

Y5

Y6

&

G2B

Y7

74LS138 3-8译码器

端口译码电路

课本P184 例6.2

输入输出控制方式——程序控制方式

一.无条件控制

1. 特点:要求外设数据变化缓慢,操作时间固定,可以被认为始终处于 就绪状态,如一组开关或LED显示管。

微机原理CH6 可编程外围接口芯片8255A及应用(ok)

第六章

2、方式 1(选通输入/输出工作方式) 适用场合 查询方式或中断方式的数据传送。如:与打印机的接 口。 方式1的基本功能 ① 两个选通的8位数据端口,可输入或输出 ; ② 每个端口有三条控制线(C口提供,固定指定的,不 能用程序改变) ③ 若只有一个口工作在方式1,余下的13位可工作在方 式0; ④ 方式1的两个8位数据口的输入、输出数据都能锁存。

PB7~PB0

PC1

INTE B PC2

OBFB ACKB

PC0 WR

INTRB

29

第六章

各控制联络信号的含义

① OBF (Output Buffer Full):输出缓冲器满信号 8255A送给外设的选通信号,低电平有效。 当它为低电平时,表示CPU已将数据写到8255A的指定 输出端口,外设可以将数据取走。OBF 由输出命令 WR 的上 升沿置成低电平,而外设应答信号 ACK 将其恢复成高电平。 PC7输出A口的输出缓冲器满信号,PC1输出B口的输出缓冲 器满信号。 ② ACK (Acknowledge):外设的应答信号 低电平有效,由外设送给8255A。 当它为低电平时,表示CPU输出到8255A的A口或B口的 数据已被外设取走。PC6输入A口的应答信号,PC2输入B口 的应答信号。

8255

4

第六章

二、8255A的结构和功能

5

第六章

1、数据端口A、B和C

8255A内部包含3个8位的输入输出端口A、B和 C,通过外部的24根线与外设交换数据或通信联络( 其中C口被分成C口上半部分和C口下半部分),C口 又可分为两个4位端口。

6

第六章

每个数据端口在不同的工作方式下的具体功能:

中断允许信号

微型计算机系统与接口:CH6-1

4,Cache 组织 5,数据的一致性——MESI协议 ,数据的一致性——MESI协议

修改,互斥,共享,无效

6.1.3 Cache基本概念回顾

1,Cache 原理和 Cache 的映射

高速缓存技术将高速的小容 量的静态存储器Cache和大容量 的动态主存储器连接在一起, 在Cache当中存放主存中内容的 副本,主存到Cache形成地址的 影射.处理器可以以最快的速 度直接访问Cache,而可访问的 范围却是价格低廉的大容量的 主存储器空间.

直接映射 相联映射 组相联映射

1,Cache 原理和 Cache 的映射

直接映射: 直接映射

把主存的每块分别映射到某一个固定的Cache行中 Cache行号(余数) = 主存块号 mod Cache行数

64K字节 字节16K行 字节 行 16M字节 4M块 字节 块

重复引用 两个映射 到同一行 中且来自 不同块的 字,命中 率降低!

1,内部Cache 命中(L1 Cache 访问) ,内部Cache 命中(L1 2,内部Cache 不命中(请求L2 Cache 访问) ,内部Cache 不命中(请求L2 3,L2 Cache 命中(L2 Cache 访问) 命中(L2 4,L2 Cache 不命中(主存储器访问) 5,U,V流水线L2 Cache 命中—流水线读 流水线L2 命中—

3,写策略 ,

"写直达"方法当中,写主存的开销发生在 每次写Cache时.而"写回"法使写主存的 每次写Cache时.而"写回"法使写主存的 开销发生在Cache块失效时.实验统计,写 开销发生在Cache块失效时.实验统计,写 回法与主存的通信量是写直达法的十几分之 一. 实际系统中,通常同时使用这两种写策略, 使它们在不同的情况下互相补充,在修改数 据时保持存储器数据的一致性 .

微机原理课件ch06en

2021/1/10

第19页

Loop Program Structure

• WHILE-DO Program Sequence

2021/1/10

第20页

Loop Program Structure

• WHILE-DO Program Sequence

2021/1/10

第21页

Example

• The Block-Move Program

– JZ, JNZ, JG, JL, JGE, and JLE needed because the numeric order of signed and unsigned numbers differ.

2021/1/10

第11页

JMP CX JMP EDX JMP NEAR PTR [BX] JMP FAR PTR [ECX]

2021/1/10

第14页

Branch Program Structure

• Using JMP to realize IF-THEN

– With a flag condition test

2021/1/10

2021/1/10

第7页

Far JMP

2021/1/10

第8页

Conditional Jumps

2021/1/10

第9页

Conditional Jumps

• There are many conditional jump instructions. • Conditional jump instructions, for the most part, test the

• The procedure called by the interrupt is called a handler or an interrupt service procedure (ISP).

微机原理ch6

• Most conditional jump instructions are straightforward as they often test one flag bit.

although

some test more than one

Conditional Jumps

*F=1, jump: JS JZ/JE JP/JPE JC *F=0, jump : JNS JNZ/JNE JNP/JPO JNC

• The far jump instruction sometimes appears with the FAR PTR directive.

another

way to obtain a far jump is to define a label as a far label a label is far only if it is external to the current code segment or procedure

• 5-byte far jump allows a jump to any memory location within the real memory system. • The short and near jumps are often called intrasegment jumps. • Far jumps are called intersegment jumps.

• A combination of a decrement CX and the JNZ conditional jump. • In 8086 - 80286 LOOP decrements CX.

if

CX != 0, it jumps to the address indicated by the label If CX becomes 0, the next sequential instruction executes

陈伟婷计算机组成原理-ch6 总线系统

2019/11/1

1

第六章内容概要

基本概念 总线控制 总线接口 总线标准

2019/11/1

2

6.1 基本概念

总线是构成计算机系统的互连机构,是多个系统 功能部件之间进行数据传送的公共通路。

总线的分类

内部总线:CPU内部连接各寄存器及运算部件之间 的总线。

系统总线:CPU同计算机系统的其他高速功能部件, 如存储器、通道等互相连接的总线。

SBO# SDONE

TDI TDO TCK TM S TRST# IN TA # IN T B # IN T C # ” IN T D #

2019/11/1

AD[31:0] C/BE[3:0] PAR FRAME# TRDY# IRDY# STOP# DEVSEL# IDSEL REQ# GNT# CLK RST# D[63:32] BE#[7:4] PAR64 REQ64# ACK64# LOCK# PERR# SERR# SBO#

总线复用方式 某个传输线上既传送地址信息,又传送 数据信息。为此必须划分时间片,以便 在不同的时间间隔中完成传送地址和传 送数据的任务。

共享总线的部件分时使用总线

2019/11/1

17

三、同步(定时)方式

1. 同步定时

固定的定时

串行同步:信号编码 并行同步:专用时钟信号线

优点 时序关系简单,实现简单。具有较高的传输频率。

缺点 在设备速度不一致时按最坏情况确定,总线长度不能太 长(时钟相移)

2019/11/1

18

2. 异步定时

在异步定时协议中,后一事件出现在总线上的时 刻取决于前一事件的出现,即建立在应答式或互 锁机制基础上。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

端口和接口的区别?

接口(Interface)

1、若干个端口加上相应的控 制逻辑电路构成了接口

2、一个接口包含多个端口, 端口是接口的一部分

3、对接口的访问实质是对寄 存器(端口)的访问

一定要理解

G2A

Y5

Байду номын сангаасY6

&

G2B

Y7

74LS138 3-8译码器

端口译码电路

课本P184 例6.2

输入输出控制方式——程序控制方式

一.无条件控制

1. 特点:要求外设数据变化缓慢,操作时间固定,可以被认为始终处于 就绪状态,如一组开关或LED显示管。

2. 优点:简单, CPU随时可无条件读/写数据。 3. 缺点:无法保证数据总是有效,适用面窄。

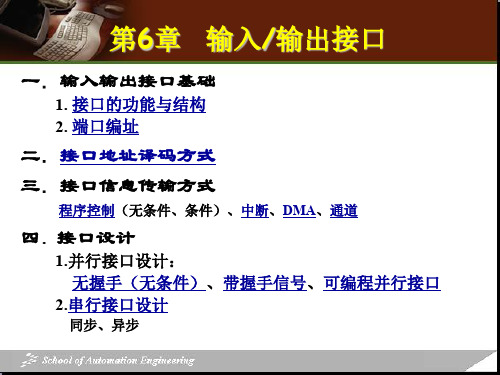

第6章 输入/输出接口

一.输入输出接口基础

1. 接口的功能与结构 2. 端口编址

二.接口地址译码方式

三.接口信息传输方式

程序控制(无条件、条件)、中断、DMA、通道

四. 接口设计

1.并行接口设计: 无握手(无条件)、带握手信号、可编程并行接口

2.串行接口设计

同步、异步

计算机与直接相联的外围设备进行数据交换的过程 通常称为输入/输出(In/Out),而与远方设备进行数据交换 的过程习惯上称为数据通信(data communication)。

部分译码

导致误操作

只有部分高位地址线参与译码形成片选信号

全译码

全部高位地址线都参与译码形成片选信号

课本P184 例6.1

练习:分析图中74LS138输出端的译码地址范围

A3 A4 A5 +5V A6 A7 A8 A9 AEN IOR IOW

0 0 0 1 0

&

A

Y0

B

Y1

C

Y2

G1

Y3

Y4

关键:设置接口电路

一. CPU与外设两者的信号不兼容,在信号类型、功能定义、逻辑定义和时序 关系上都不一致。如:信号类型有机械的、物理的、电信号等,信号形式 有脉冲、模拟量或数字量等;

二. 两者的工作速度不匹配,CPU速度高,外设速度低 ;

三. 若不通过接口,而由CPU直接对外设的操作实施控制,就会使CPU处于穷 于应付与外设打交道之中,大大降低CPU的效率;

端口编址

为了区分接口电路的各个寄存器,系统为 它们各自分配了一个地址,称为I/O端口地址, 以便对它们进行寻址并与存储器地址相区别

I/O端口有两种编址方式: 存储器映像方式、 I/O独立编址方式

存储 单元 地址

端口编址方式1:独立编址

(如Intel的系列芯片)

0000H 0001H …… F0FFH

F100H F101H …… FFFFH

I/O 端口 地址

0000H 0001H …… F…F0…0H FFFFH

特点:系统视端口和存储单元为不同的对象。 优点:系统中存储单元和I/O端口的数量可达到最大。 缺点:需专门信号来指示系统地址线上出现的是存储单元地址还

是端口地址;专用的端口操作指令比较单一;

接口举例-USB通用接口芯片

-支持USB设备的控制传输、批量传输、中断传输。 -内置控制传输的协议处理器,简化常用的控制传输。 -通过U盘文件级子程序库实现单片机读写USB 存储设备中的文件。 -并行接口包含8位数据总线,4线控制:读选通、写选通、片选、中断输出。 -…

接口举例

接口举例

接口分类

二.条件控制(查询控制)

1. 特点: CPU主动、外设被动。执行I/O操作时CPU总要先查询外设状态; 若传输条件不满足时,CPU等待直到条件满足。

2.优点:解决了CPU与外设之间的同步问题,可靠性高。 3.缺点:CPU利用率低,低优先级外设可能无法及时得到服务。

缺 点 : CPU 对 存 储 单 元 和

I/O端口的实际寻址空间都小于 其最大寻址空间。

统一编址总线结构

DB

三

CPU

AB

CB

总

线

存储器 1 存储器 2 接口 1 接口 2 接口 3

外设 1 外设 2 外设 3

I/O接口地址译码方法

地址译码的方法灵活多样

低位地址线直接接到I/O接口芯片的地址引脚,进 行I/O接口芯片的片内端口寻址

传输方式

并行接口:一次传输多个数据位 串行接口:一次只有一位数据

时序控制方式

同步接口:总线相连,同步传输 异步接口:无共同的基准时钟

程序查询方式:程序的执行实现

传输控制方式

程序中断方式:传输时由中断请求信号触发 存储器直接存取访问方式(DMA)

工作对象

通道控制器,I/O处理机 外围接口:与外设无关,是系统的一部分 外设接口:用于连接外设的接口

CPU与外设 都是面向接口而非直接联络!

端口和接口的区别?

端口(PORT)

一定要理解

一. I/O接口通常设置有若干个寄存器,用来暂存CPU和外 设之间传输的数据、状态和控制信息。

二. 一般有三类寄存器,分别是数据寄存器、状态寄存器、 控制寄存器。

三. 接口内的寄存器通常被称为端口。根据寄存器内暂存信 息的类型,分别称为数据端口、控制端口和状态端口。

高位地址线与CPU的控制信号进行组合,经译码 电路产生I/O接口芯片的片选信号CS,实现系统中 的接口芯片寻址

接口地址译码的设计

接口芯片的片选信号的生成仍然可以采用存储器的译码 方式,即线译码、部分译码和全译码三种方式:

地址信号不完全

线译码

确定,所以存在地 址重叠问题,浪费

每组芯片使用一根地址线作片选 寻址空间,并可能

独立端口编址总线结构

DB

三

AB

总

CB

线

存储器 1 存储器 2 CPU

接口 1 接口 2 接口 3

存储器读写

I/O 读写 外设 1

外设 2

外设 3

端口编址方式2:存储器映像编址

(如Freescale的系列芯片)

特点:将端口看作存储单

元,仅以地址范围的不同来区 分两者。

优点:对端口的操作和对

存储单元的操作完全一样,因 此系统简单,并且对端口操作 的指令种类较多。

四. 数据传输方式不同,有并行、串行之分。 五. 它们不能与CPU直接相连,必须经过中间电路再与系统相连,这部分电路被

称为I/O接口电路。

3/81

接口结构与功能

一.接口主要功能

数据缓冲 信号转换 联络控制

二.接口硬件结构

存储器接口、外设接口

三.接口技术组成

硬件:地址译码、读写控制、总线(数据)缓冲 软件:驱动程序(初始化、传送控制、结束控制等)