baseband description and troubleshooting

CommScope 电源优化系统说明书

The patent pending PowerShift ™dynamically to match your exact RRU power requirements.Section 1: PowerShift ™Section 2: Capacitive Jumper ..................................................................................................................03Section 3: Recommended Interconnect Power Cables ........................................................................04Section 4: General Wiring Diagram ....................................................................................................05Section 5: Rack Installation ..............................................................................................................................06Section 6: Wiring of the Module ........................................................................................................................06Section 7: Capacitive Jumper Installation ..............................................................................................08Section 8: Capacitive Jumper Mounting ............................................................................................09Section 9: Splicing Capacitive Jumper to Power ................................................................................10Section 10: Module Installation ...........................................................................................................................11Section 11: Testing and Maintenance .....................................................................................................12Section 12: Output Circuit Overload Protection . .................................................................................14Section 13: Dip Switch / RJ45 Jacks / Alarm Relay . (17)Field Engineering Services (FES)Support services, such as our Field Engineering Services (FES) Group gives CommScope customers access to technical support where and when it is needed the most — in the field. The FES team is staffed by an expert team of technicians who, in turn, are supported by some of the brightest and most experienced product line managers.Customer Service CenterUnited States and Mexico 1-800-255-1479 or 1-888-235-5732 International: +1-779-435-8579For the most current, up-to-date information on all our products and product information please visit our eCatalog section at .PowerShift ® V1 DAS Installation Instructions, Rev DGUI v1.4 − Power Module Series 1:1 and newer (firmware v1.9 and newer)The Base Unit is used in conjunction with the existing DC power plant at the installation site.1. The modules are plug-and-play for easy installation and site maintenance. 2. The base unit has capacity for four modules.3. Each module has DC input and DC output for three Remote Radio Units (RRU), for a total capacity of 12 RRU sectorsper PowerShift base unit.4.Each module unit is also provided with diagnostic indicators, explained in section 12.Section 1: PowerShift ™ V1 System ComponentsThe PowerShift V1 System Consists of two components: the Base Unit and Capacitive Jumpers.Rack Part Number: PS-R-1Module Part Number: PS-1-73Note: The PowerShift base unit will not operate without the corresponding Capacitive Jumper. Each modulerequires three Capacitive Jumpers (oneper circuit)1 Per circuit; 3 circuits per module2Input/output voltage and current range are guaranteed values, typical operating values will exceed these by about 10%; examples:Typical input cutoff (minimum) voltage: 42V x 0.9 ≈ 38VTypical output maximum current: 20A x 1.1 ≈ 22A3 Turn-on voltage is higher than cut-off voltage in order to provide hysteresis protection4 Total power = power consumed by radio + power loss in trunk cable5 RRU input voltage set-point is factory programmed (not user settable). Other voltage set-point are possible, contact CommScope 6For cable lengths outside these ranges, contact CommScope for more informationThe Capacitive Jumper is a circuit at the radio input to provide the PowerShift base unit with information regarding actual line impedance. Additionally it compensates for DC inductance of the power line further reducing power loss.Section 2: Capacitive JumperGeneral SpecificationsTypePower-only Capacitive Jumper BrandHELIAX ® FiberFeed ® Conductor Gauge, singles 6-12 AWG (10 AWG typical)Conductors, quantity 2Enclosure Color Grey Jacket ColorBlackEnvironmental SpecificationsEnvironmental Space UV resistant for outdoor and/or direct burial installations Operating Temperature Maximum value based on a standard condition of 20 °C (68 °F)Safety Voltage Rating600 VDimensionsWeight 1.1 kg | 2.5 lb Diameter Over Jacket12.395 mm | 0.488 inEnclosure 304.8 mm | 12 in (length, including cable gland nuts) 76.2 mm | 3 in (width)76.2 mm | 3 in (depth)GeneralMount Tabs includedSection 3: Recommended Interconnect Power Cables(coordinate with a CommScope representative to determine popper gauge/length) ConstructionMaterials: PWRT-210-S Construction Type Conductor Material Dielectric MaterialDrain Wire MaterialFiller MaterialGround Wire Material Insulation Material, singles Jacket MaterialOuter Shield (Braid) Coverage Outer Shield (Braid) Gauge Outer Shield (Braid) Material Outer Shield (Tape) MaterialDimensionsCable WeightDiameter Over Conductor, singlesDiameter Over Dielectric Diameter Over Drain WireDiameter Over Ground Wire Diameter Over Jacket Diameter Over Shield (Braid) Jacket Thickness Electrical Specifications Conductor dc Resistance Conductor dc Resistance NoteSafety Voltage Rating Environmental Specifications Environmental Space Operating Temperature Safety Standard General Specifications ApplicationCable TypeJacket ColorConductor Gauge, singles Conductor Type, singles Conductors, quantity Construction TypeDrain Wire GaugeGround Wire Gauge Ground Wire TypeJacket Color, singles Non-armoredTinned copperPVCTinned copper PolypropyleneTinned copperPVCPVC65 %36 AWGTinned copperAluminum/Poly, nonbonded0.30 kg/m | 0.20 lb/ft3.2004 mm per 105 strand0.1260 in per 105 strand4.7244 mm | 0.1860 in1.8800 mm per 7 strand0.0740 in per 7 strand3.200 mm | 0.126 in12.395 mm | 0.488 in10.109 mm | 0.398 in1.143 mm | 0.045 in1.06 ohms/kft | 3.47 ohms/km Maximum value based on a standard condition of 20 °C (68 °F)600 VUV resistant for outdoor and/or direct burial installations-40°C to +90 °C (-40°F to+194 °F)NEC Article 336 (Type TC)IndustrialPowerBlack8 AWGStranded2Discrete power cable12 AWG10 AWGStrandedBlack | RedPWRT-210-SSection 4: General Wiring DiagramBoxSleeve/Pendant Long cable runPower-only Capacitive JumperRemotesJunction or splice box* based on the # of RRU’s on-siteSection 5: Rack InstallationDetermine the installation depth required for the base unit, attach the side flanges in the appropriate location. 3 screws are required per side.Mount the unit in a standard 19” rack near the current DC power output breaker box.Ground the unit by installing a ground wire at the base of the unit.Section 6: Wiring of the ModuleRemove 2 small screws on the back of the unit and remove the back cover to expose the terminal screws. (replace screws to keep them with the unit)The rear of the shelf is divided into 12 individual circuits each containing a DC input and a DC output. There is a positive and negative terminal strip connection for each DC input and out. The right side pair is for the DC input and the left sideRun cables from the Base Unit Output screws to the baseband Surge Protection Device / Over Voltage Protection (SPD / OVP) input if installed. Then attach the SPD / OVP outputs to the trunk cable that runs to the Remote’s.If no SPD/OVP is installed, then connect the trunk cable directly to the Base Unit Output screws.Repeat for each circuit.Re-install the back cover of the unit when complete.the expected value in micro-Farads (µF) is 1100µF +/- 25% (i.e. 825 to 1375µF). If an open or short condition is detected then there is likely a fault in the trunk cable or in the capacitive jumper.Section 8: Capacitive Jumper MountingMethod 2: Using a multi-meter, take a resistance measurement across the Base Unit Output screws. First, take a resistance measurement to confirm the circuit is open. Second, temporarily connect (short) the two conductors together at thecapacitive jumper (i.e. at the end of the capacitive jumper cable) and take a resistance measurement; the value should be less than 3 Ohms (it is dependent on the trunk cable gauge and length).Connect the other end of the capacitive jumper to the Remote Radio Unit. See section 10 for connector installation instructions.23Loosen 4 screws to remove the cover. Screws are ARE captive to the lid but can be removed if required.1Section 9: Splicing Capacitive Jumper to Power101.6 mm (4 in)6.35 mm (1/4 in)When lid is removed inspect pre-installed jumper to be sure nothing has come loose during shipping and handling.Braided ground-48VRTNRemove 101.6 mm (4 inches) of outer shielding from the power trunk cable. Remove 6.35 mm (1/4 inch) of conductor jacketing. Install power trunk into enclosure by loosening gland nut and threading into gland opening. Connect 0 Volt conductor to the corresponding 0 Volt terminal. Connect -48 Volt conductor to the corresponding -48 Volts terminal. Connect the braided ground to its terminal. Tighten cable gland and reinstall the lid. Support the power trunk cable 152 mm (6 in) from the cablegland.Braided ground-48VRTN Power from Junction BoxCable glandCompleted 4 module (12 RRU) installationdetermine the line resistance• A major alarm will be raised on the base unit alarm relay• After the 30 second interval, the module will still enable output voltage to power up the radio; a default line resistance of 0.15 Ohms is used, which should result in an output voltage sufficient to power up the radio• Troubleshoot by confirming the capacitive jumper is connected, repeat the integrity check in Section 7• Note that PowerShift can not measure a line resistance that is > 3.5 Ohms5. If any status lights are not green, refer to the alarm information below.6. Note the following:• Cycling the input power to a circuit (off and back on) will restart the 30 second measurement interval (i.e., the module will perform a new measurement of the line resistance)• After the 30 second measurement interval is complete, the module will use the measured line resistance indefinitely;it will not attempt to re-measure the line resistance unless the input power to the circuit is cycledAlarmsThere are four LED status indicators on each PowerShift Module: 1, 2, 3 and X:1. 1, 2 and 3 represent the status of each of the three power circuits in the module.2. X represents the status of the overall module.3. Intermittent or latent failures will be indicated by the X indicator even if the individual circuits are functioning correctly.Circuit LEDs (1, 2, 3)1. Solid green LED indicates the circuit is functioning properly.2. A blinking green LED indicates the circuit is performing a line resistance measurement• This occurs every time input power is applied to the circuit (including when the input power is cycled off and back on)• The circuit LED should blink green for about 30 seconds and then change to solid green• If the LED continues to blink green after 30 seconds this indicates an alarm condition (the module is unable to measure the line resistance)Module LED (“X”)1. Solid green LED indicates the module is functioning properly.2. If the X LED is not green, but 1, 2 and/or 3 are green, the indicated circuit(s) are still functioning properly and deliveringpower, but a latent failure has occurred (e.g., a temporary over-temperature condition)See the alarm table on following page for additional information on LED status and troubleshootingThe power module is designed to shut off the output from a circuit in the event the load demand exceeds the circuit maximum output capacity of 1460W total power (radio demand + power loss in the trunk cable)Under normal circumstance an output overload should not occur; the proper design and installation of the PowerShift system ensures the maximum radio load demand and the trunk cable length do not exceed the circuit capacity.However, off-nominal events such as a short in the trunk cable or a malfunctioning radio could cause the load demand to exceed the module output capacity. In this event the module functions as follows:When circuit capacity is exceeded the module will shut off its output, the GUI appears as shown below using Circuit 1 as an example Note the following: • The GUI shows Circuit 1 has input voltage but no output voltage or current (output is shut off due to the overload condition)• The LEDs and GUI icons for Circuit 1 for “X” are yellow blinking• The GUI circuit status shows red text for “off” (no output power) and out• The alarm relay on the back of the shelf is set for a critical alarm conditionSection 12: Output Circuit Overload ProtectionModule Circuit-Overload RecoveryThe module will check the condition of the circuit about every 3-5 seconds to determine if the overload condition remains or if it has cleared; each time the circuit check is performed the applicable module circuit LED will briefly flash green and the GUI status will briefly show “okay”If the overload condition clears within 20 minutes then the module will re-enable power output of the circuitIf the overload condition has not cleared, the module will continue to keep the circuit output shut off and will continue to check the circuit condition about every 3-5 secondsAfter 20 minutes, if the circuit overload condition has not cleared, the module will latch the circuit output off and will discontinue checking the circuit condition (the applicable circuit and “X” LEDs will continue to blink yellow)Once the circuit has latched off, the user must intervene as follows to re-enable the circuit:• The circuit overload condition must be cleared• The input power to the circuit must be cycled off and back on (typically by using the DC plant circuit breaker)• The circuit will re-enable its output power, the applicable circuit LED will blink green for about 30 seconds while the line resistance is measured• After about 30 seconds:• GUI Circuit number icon and the module front panel LED are both solid green• The GUI circuit status shows “okay”• The GUI “X” icon and module LED are both solid greenModule High Temperature ProtectionT he power module is designed to protect itself from an excessive temperature (overheating) condition. Under normal operating conditions the module cooling fans provide adequate cooling for the module. However in off-nominal conditions (blockage of the module’s air intake or exhaust grill, failure of the site shelter cooling) the module will shutoff output if its internal temperature rises too high. In this event the module functions as follows:• When the internal temperature rises too high the module shuts off the output of all affected circuit(s)• There are two possible operating conditions for the module once a thermal overload has occurred: Condition 1, Critical Alarm: The high temperature condition (e.g., failure of the shelter cooling) has not beenresolved and thus the module output remains shut off. The high temperature condition must be resolved and the internal module temperature allowed to drop down below threshold before the module will re-enable its output powerCondition 2, Major Alarm: The thermal overload condition has been resolved and the module output hasre-enabled. Note that the thermal overload alarm still remains active (latched) until the user intervenes to clear the alarm• Using Circuit 1 as an example, the GUI and module LEDs will appear as shown below for the two conditions:Thermal Shutdown, Condition 1, Critical Alarm (high temperature condition is not resolved, no output power)Note the following:• The GUI shows Circuit 1 has input voltage but no output voltage or current (output is shut off due to an unresolved high temperature condition)• The GUI Circuit 1 icon and the “X” icon are both highlighted red blinking• The GUI Circuit 1 status shows “temp out-I off” indicating the circuit shutoff is due to a thermal overload• The module front panel “1” and “X” LEDs are both red blinking• The alarm relays on the back of the shelf is set for a critical alarm conditionThermal Shutdown, Condition 2, Major Alarm (high temperature condition has resolved, output power in enabled)Note the following:• The GUI shows Circuit 1 has output voltage and output currentThe GUI Circuit 1 icon shows green blinking, the “X” icon shows yellow solid•• The GUI Circuit 1 status shows “temp ” indicating there is an alarm condition on the circuit (i.e., a latched alarm for the prior thermal shutdown)• The module front panel “1” LED is green blinking, and the “X” LED is yellow solid• The alarm relays on the back of the shelf is set for a major alarm conditionModule Thermal - Overload RecoveryNote the following:• If the module is still shutdown (Condition 1, critical alarm) then the high temperature condition must first be resolved(e.g., unblock the fan, restore shelter cooling) such that the module internal temperature falls below the shutdownthreshold and the module re-enables output power (it will then be in Condition 2)• Once the module has re-enabled power (Condition 2, major alarm) the user must clear the alarm by using the GUI to click the “clear” button for each circuit that has highlighted “temp” status• The applicable circuits will change back to nominal operating condition (see below):The GUI Circuit number icon and the module front panel LED are both solid greenThe GUI circuit status shows “ok”The GUI “X” icon and module LED are both solid greenDip Switch and RJ45 jacks are present on each base unit for possible attachment to an external controller such as a GE Critical Power Standard Controller.Section 14: Dip Switch / RJ45 Jacks / Alarm RelayThe Dip switch position is factory preset for no controller with both switches down. If for any reason these switches are not set accordingly, the unit will not function properly unless configured for use with a controller. Please ensure that both switches are reset to the down position as illustrated above.Dip SwitchLocated on the side of therack behind the DATA portsAlarm Relay Connections1. The alarm status of the unit is externally accessible with the screw terminal present at the rear near the RJ45 Jacks.。

ADN8810 12位高输出电流源数据手册(版本C)说明书

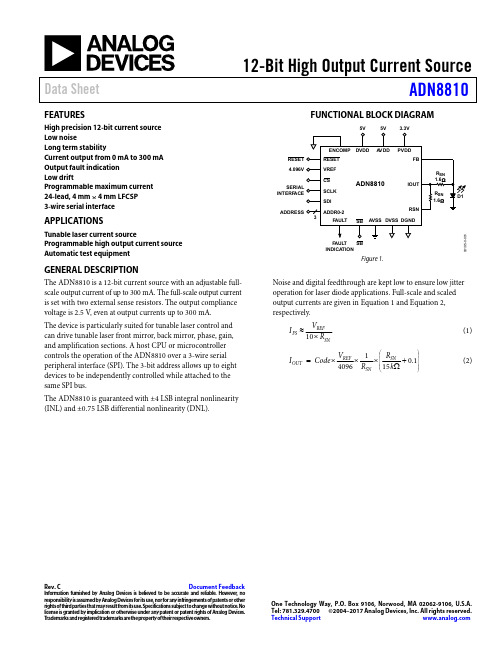

12-Bit High Output Current Source Data Sheet ADN8810Rev. C Document FeedbackInformation furnished by Analog Devices is believed to be accurate and reliable. However, noresponsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. T rademarks and registered trademarks are the property of their respective owners. O ne Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2004–2017 Analog Devices, Inc. All rights reserved. Technical Support FEATURESHigh precision 12-bit current sourceLow noiseLong term stabilityCurrent output from 0 mA to 300 mA Output fault indicationLow driftProgrammable maximum current24-lead, 4 mm × 4 mm LFCSP3-wire serial interface APPLICATIONSTunable laser current source Programmable high output current source Automatic test equipmentFUNCTIONAL BLOCK DIAGRAM3195-0 RESET4.096VSERIALINTERF ACEADDRESSSBF AULTINDICA TIONFigure 1.GENERAL DESCRIPTIONThe ADN8810 is a 12-bit current source with an adjustable full-scale output current of up to 300 mA. The full-scale output current is set with two external sense resistors. The output compliance voltage is 2.5 V, even at output currents up to 300 mA.The device is particularly suited for tunable laser control and can drive tunable laser front mirror, back mirror, phase, gain, and amplification sections. A host CPU or microcontroller controls the operation of the ADN8810 over a 3-wire serial peripheral interface (SPI). The 3-bit address allows up to eight devices to be independently controlled while attached to the same SPI bus.The ADN8810 is guaranteed with ±4 LSB integral nonlinearity (INL) and ±0.75 LSB differential nonlinearity (DNL). Noise and digital feedthrough are kept low to ensure low jitteroperation for laser diode applications. Full-scale and scaledoutput currents are given in Equation 1 and Equation 2,respectively.SNREFFS RVI⨯≈10(1)⎪⎪⎪⎪⎭⎫⎝⎛+Ω⨯⨯⨯=1.01514096kRRVCodeI SNSNREFOUT(2)ADN8810Data SheetRev. C | Page 2 of 14TABLE OF CONTENTSFeatures .............................................................................................. 1 Applications ....................................................................................... 1 Functional Block Diagram .............................................................. 1 General Description ......................................................................... 1 Revision History ............................................................................... 2 Specifications ..................................................................................... 3 Timing Characteristics ................................................................ 4 Absolute Maximum Ratings ............................................................ 5 ESD Caution .................................................................................. 5 Pin Configuration and Function Descriptions ............................. 6 Typical Performance Characteristics ............................................. 7 Terminology ...................................................................................... 9 Functional Description (10)Setting Full-Scale Output Current ........................................... 10 Power Supplies ............................................................................ 10 Serial Data Interface ................................................................... 10 Standby and Reset Modes ......................................................... 11 Power Dissipation....................................................................... 11 Using Multiple ADN8810 Devices for Additional Output Current ......................................................................................... 11 Adding Dither to the Output Current ..................................... 12 Driving Common-Anode Laser Diodes ................................. 12 PCB Layout Recommendations ............................................... 13 Suggested Pad Layout for CP-24 Package ............................... 13 Outline Dimensions ....................................................................... 14 Ordering Guide .. (14)REVISION HISTORY11/2017—Rev. B. to Rev. CChanged R S to R SN .......................................................... Throughout Change to Figure 1 ........................................................................... 1 Changes to Maximum Full-Scale Output Current Parameter and Power Supply Rejection Ratio Parameter, Table 1 ................ 3 Moved Timing Characteristics Section, Table 2, and Figure 2 ..... 4 Added Lead Temperature Range (Soldering 10 sec) Parameter, Table 3 ................................................................................................ 5 Changes to Figure 3 and Table 4 ..................................................... 6 Changes to Setting Full-Scale Output Current Section ............. 10 Changes to Adding Dither to the Output Current Section,Figure 20, and Figure 21 ................................................................ 12 Changes to PCB Layout Recommendations Section andFigure 25 .......................................................................................... 13 Updated to Outline Dimensions .................................................. 14 3/2016—Rev. A to Rev. BChanges to Figure 3 and Table 4 ...................................................... 7 Updated Outline Dimensions ....................................................... 15 Changes to Ordering Guide . (15)4/2009—Rev. 0 to Rev. A Changes to Table 3 ............................................................................. 6 Changes to Figure 25 ...................................................................... 14 Updated Outline Dimensions ....................................................... 15 Changes to Ordering Guide . (15)1/2004—Revision 0: Initial VersionData Sheet ADN8810 SPECIFICATIONSAVDD = DVDD = 5 V, PVDD = 3.3 V, AVSS = DVSS = DGND = 0 V, T A = 25°C, covering output current (I OUT) from 2% full-scale current (I FS) to 100% I FS, unless otherwise noted.Rev. C | Page 3 of 14ADN8810Data SheetRev. C | Page 4 of 141 With respect to AVSS. 2R SN = 20 Ω. 3See Table 2 for timing specifications.TIMING CHARACTERISTICS1, 21 Guaranteed by design. Not production tested.2Sample tested during initial release and after any redesign or process change that may affect these parameters. All input signals are measured with tr = tf = 5 ns (10% to 90% of DVDD) and timed from a voltage level of (V IL + V IH )/2.SCLKC SSDIRESET*ADDRESS BIT A3 MUST BE LOGIC LOW03195-0-002Figure 2. Timing DiagramData SheetADN8810Rev. C | Page 5 of 14ABSOLUTE MAXIMUM RATINGSTable 3.Parameter Rating Supply Voltage 6 VInput VoltageGND to V S + 0.3 V Output Short-Circuit Duration to GND IndefiniteStorage Temperature Range −65°C to +150°C Operating Temperature Range−40°C to +85°C Junction Temperature Range, CP Package −65°C to +150°C Lead Temperature Range (Soldering 10 sec)300°CStresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.ESD CAUTIONADN8810Data SheetRev. C | Page 6 of 14PIN CONFIGURATION AND FUNCTION DESCRIPTIONS03195-0-003FAULT ADDR0ADDR1FB RSN ADDR2NICVREF AVDD AVSS NIC DVSS117P V D D I O U T I O U T P V D D 1E N C O M P S B NOTES1. NIC = NOT INTERNALLY CONNECTED.2. EXPOSED PAD. CONNECT THE EXPOSED PAD TO DGND.Figure 3. Pin ConfigurationData SheetADN8810Rev. C | Page 7 of 14TYPICAL PERFORMANCE CHARACTERISTICSCODE1.2–0.84,500500I N L E R R O R (L S B )1,0001,5002,0002,5003,0003,5004,0001.00.2–0.2–0.4–0.60.80.600.403195-0-005Figure 4. Typical INL PlotCODE0.4–0.304,500500D N LE R R O R (L S B )1,0001,5002,0002,5003,0003,5004,0000.1–0.1–0.20.300.203195-0-006Figure 5. Typical DNL PlotTEMPERATURE (°C)0.200.15–0.20–4085–15∆I N L (L S B )1035600–0.05–0.10–0.150.100.0503195-0-007Figure 6. ∆INL vs. TemperatureTEMPERATURE (°C)0.200.15–0.20–4085–15∆D N L (L S B )1035600–0.05–0.10–0.150.100.0503195-0-008Figure 7. ∆DNL vs. TemperatureTEMPERATURE (°C)0.2580.2570.250–4085–15F U L L -S C A L E O U T P U T (A )1035600.2540.2530.2520.2510.2560.255R SN = 1.6Ω03195-0-009Figure 8. Full-Scale Output vs. TemperatureTEMPERATURE (°C)20.76520.75520.720–4085–15F U L L -S C A L E O U T P U T (m A )10356020.74020.73520.73020.72520.75020.745R SN = 20Ω20.76003195-0-010Figure 9. Full-Scale Output vs. TemperatureADN8810Data SheetRev. C | Page 8 of 14TEMPERATURE (°C)0.500.35I P V D D (m A )0.200.150.100.050.300.250.400.4503195-0-011Figure 10. PVDD Supply Current (I PVDD ) vs. Temperature120I D V D D (µA )864210TEMPERATURE (°C)03195-0-012Figure 11. DVDD Supply Current (I DVDD ) vs. Temperature1.51.0I A V D D (m A )1.41.31.21.1TEMPERATURE (°C)03195-0-013Figure 12. AVDD Supply Current (I AVDD ) vs. TemperatureFREQUENCY (Hz)100k1O U T P U T I M P E D A N C E (Ω)1k1001010k03195-0-014Figure 13. Output Impedance vs. FrequencyTIME (1µs/DIV)CSI OUTV O L T A GE (2.7V /D I V )03195-0-015Figure 14. Full-Scale Settling TimeTIME (200ns/DIV)CSI OUT03195-0-016Figure 15. 1 LSB Settling TimeData SheetADN8810Rev. C | Page 9 of 14TERMINOLOGYRelative AccuracyRelative accuracy or integral nonlinearity (INL) is a measure of the maximum deviation, in least significant bits (LSBs), from an ideal line passing through the endpoints of the DAC transfer function. Figure 4 shows a typical INL vs. code plot. The ADN8810 INL is measured from 2% to 100% of the full-scale (FS) output.Differential NonlinearityDifferential nonlinearity (DNL) is the difference between the measured change and the ideal 1 LSB change between any two adjacent codes. A specified differential nonlinearity of ± 1 LSB maximum ensures monotonicity. The ADN8810 is guaranteed monotonic by design. Figure 5 shows a typical DNL vs. code plot . Offset ErrorOffset error, or zero-code error, is an interpolation of the output voltage at code 0x000 as predicted by the line formed from the output voltages at code 0x040 (2% FS) and code 0xFFF (100% FS). Ideally, the offset error is 0 V . Offset error occurs from a combination of the offset voltage of the amplifier and offset errors in the DAC. It is expressed in LSBs.Offset DriftThis is a measure of the change in offset error with a change in temperature. It is expressed in (ppm of full-scale range)/°C. Gain ErrorGain error is a measure of the span error of the DAC. It is the deviation in slope of the output transfer characteristic from ideal. The transfer characteristic is the line formed from the output voltages at code 0x040 (2% FS) and code 0xFFF (100% FS). It is expressed as a percent of the full-scale range.Compliance VoltageThe maximum output voltage from the ADN8810 is a function of output current and supply voltage. Compliance voltage defines the maximum output voltage at a given current and supply voltage to guarantee the device operates within its INL, DNL, and gain error specifications.Output Current Change vs. Output Voltage ChangeThis is a measure of the ADN8810 output impedance and is similar to a load regulation spec in voltage references. For a given code, the output current changes slightly as output voltage increases. It is measured as an absolute value in (ppm of full-scale range)/V .O U T P U T V O L T A G E03195-0-004Figure 16. Output Transfer FunctionADN8810Data SheetRev. C | Page 10 of 14FUNCTIONAL DESCRIPTIONThe ADN8810 is a single 12-bit current output digital-to-analog converter (DAC) with a 3-wire SPI interface. Up to eight devices can be independently programmed from the same SPI bus. The full-scale output current is set with two external resistors. The maximum output current can reach 300 mA. Figure 17 shows the functional block diagram of the ADN8810.03195-0-017Figure 17. Functional Blocks, Pins, and Internal ConnectionsSETTING FULL-SCALE OUTPUT CURRENTTwo external resistors set the full-scale output current from the ADN8810. These resistors are equal in value and are labeled R SN in Figure 1. Use 1% or better tolerance resistors to achieve the most accurate output current and the highest output impedance.Equation 3 shows the approximate full-scale output current. The exact output current is determined by the data register code as shown in Equation 4. The variable code is an integer from 0 to 4095, representing the full 12-bit range of the ADN8810.SNFS R I ×≈10096.4(3)+Ω××=1.0151000,1k R R Code I SN SN OUT(4)The ADN8810 is designed to operate with a 4.096 V referencevoltage connected to VREF. The output current is directly proportional to this reference voltage. To achieve the bestperformance, use a low noise precision (the ADR292, ADR392, or REF198 is recommended).POWER SUPPLIESThere are three principal supply current paths through the ADN8810: •AVDD provides power to the analog front end of the ADN8810 including the DAC. Use this supply line topower the external voltage reference. For best performance, AVDD must be low noise.•DVDD provides power for the digital circuitry. Thisincludes the serial interface logic, the SB and RESET logic inputs, and the FAULT output. Tie DVDD to the same supply line used for other digital circuitry. It is not necessary for DVDD to be low noise.•PVDD is the power pin for the output amplifier. It canoperate from as low as 3.0 V to minimize power dissipation in the ADN8810. For best performance, PVDD must be low noise.Current is returned through the following three pins: •AVSS is the return path for both AVDD and PVDD. This pin is connected to the substrate of the die as well as the slug on the bottom of the lead frame chip scale package (LFCSP). For single-supply operation, connect this pin to a low noise ground plane.•DVSS returns current from the digital circuitry powered by DVDD. Connect DVSS to the same ground line or plane used for other digital devices in the application.•DGND is the ground reference for the digital circuitry. In a single-supply application, connect DGND to DVSS.For single-supply operation, set AVDD to 5 V , set PVDD from 3.0 V to 5 V , and connect AVSS, AGND, and DGND to ground.SERIAL DATA INTERFACEThe ADN8810 uses a serial peripheral interface (SPI) with three input signals: SDI, CLK, and CS . Figure 2 shows the timing diagram for these signals.Data applied to the SDI pin is clocked into the input shift register on the rising edge of CLK. After all 16 bits of the data-word have been clocked into the input shift register, a logic high on CS loads the shift register byte into the ADN8810. If more than 16 bits of data are clocked into the shift register before CS goes high, bits are pushed out of the register in first-in first-out (FIFO) fashion.The four MSB of the data byte are checked against the address of the device. If they match, the next 12 bits of the data byte are loaded into the DAC to set the output current. The first bit (MSB) of the data byte must be a logic zero, and the following three bits must correspond to the logic levels on pins ADDR2, ADDR1, and ADDR0, respectively, for the DAC to be updated. Up to eight ADN8810 devices with unique addresses can be driven from the same serial data bus.Table 5 shows how the 16-bit DATA input word is divided into an address byte and a data byte. The first four bits in the input word correspond to the address. Note that the first bit loaded (A3) must always be zero. The remaining bits set the 12-bit data byte for the DAC output. Three example inputs are demonstrated.•Example 1: This SDI input sets the device with an address of 111 to its minimum output current, 0 A. Connecting the ADN8810 pins ADDR2, ADDR1, and ADDR0 to VDD sets this address.• Example 2: This input sets the device with an address of 000 to a current equal to half of the full-scale output. •Example 3: The ADN8810 with an address of 100 is set to full-scale output.STANDBY AND RESET MODESApplying a logic low to the SB pin deactivates the ADN8810 and puts the output into a high impedance state. The device continues to draw 1.3 mA of typical supply current in standby. When logic high is reasserted on the SB pin, the output current returns to its previous value within 6 µs.Applying logic low to RESET sets the ADN8810 data register to all zeros, bringing the output current to 0 A. When RESET is deasserted, the data register can be reloaded. Data cannot be loaded into the device while it is in standby or reset mode.POWER DISSIPATIONThe power dissipation of the ADN8810 is equal to the output current multiplied by the voltage drop from PVDD to the output.()SN OUT OUT OUT DISS R I V PVDD I P ×−−×=²(5)The power dissipated by the ADN8810 causes a temperature increase in the device. For this reason, PVDD must be as low as possible to minimize power dissipation.While in operation, the ADN8810 die temperature, also known as junction temperature, must remain below 150°C to prevent damage. The junction temperature is approximatelyDISS JA A J P T T ×θ+=(6)where:T A is the ambient temperature in °C,θJA is the thermal resistance of the package (32°C/W). •Example 4: A 300 mA full-scale output current is required to drive a laser diode within an 85°C environment. The laser diode has a 2 V drop and PVDD is 3.3 V .Using Equation 5, the power dissipation in the ADN8810 is found to be 267 mW . At T A = 85°C, this makes the junction temperature 93.5°C, which is well below the 150°C limit. Note that even with PVDD set to 5 V , the junction temperature increases to only 110°C.USING MULTIPLE ADN8810 DEVICES FOR ADDITIONAL OUTPUT CURRENTConnect multiple ADN8810 devices in parallel to increase the available output current. Each device can deliver up to 300 mA of current. To program all parallel devices simultaneously, set all device addresses to the same address byte and drive all CS , SDI, and CLK from the same serial data interface bus. The circuit in Figure 18 uses two ADN8810 devices and delivers 600 mA to the pump laser.SERIAL INTERFACE (FROM µC OR DSP)I 600mA03195-0-018Figure 18. Using Multiple Devices for Additional Output CurrentTable 5. Serial Data Input ExamplesAddress Byte Data Byte SDI Input A3 A2 A1 A0D11 D10 D9 D8 D7 D6 D5 D4D3 D2 D1 D0 Example 1 0 1 1 1 0 0 0 0 0 0 0 0 0 0 0 0 Example 2 0 0 0 0 1 0 0 0 0 0 0 0 0 0 0 0 Example 31 01111 11 11 1 1 1 1ADDING DITHER TO THE OUTPUT CURRENTSome tunable laser applications require the laser diode bias current to be modulated or dithered. This is accomplished by dithering the V REF voltage input to the ADN8810. Figure 19 demonstrates one method.DITHERR203195-0-019Figure 19. Adding Dither to the Reference VoltageSet the gain of the dither by adjusting the ratio of R2 to R1. Increase C to lower the cutoff frequency of the high-pass filter created by C and R1. The cutoff frequency of Figure 19 is approximately 98 Hz.The AD8605 is recommended as a low offset, rail-to-rail input amplifier for this circuit.DRIVING COMMON-ANODE LASER DIODESThe ADN8810 can power common-anode laser diodes. These are laser diodes whose anodes are fixed to the laser module case. The module case is typically tied to either VDD or ground. For common anode to ground applications, a −5 V supply must be provided.In Figure 20, R SN sets up the diode current by the following equation:40965.16111.1096.4Code k R I SN ×Ω+×=(7)where Code is an integer value from 0 to 4095.Using the values in Figure 20, the diode current is 300.7 mA at a code value of 2045 (0x7FF), or half full-scale. This effectively provides 11-bit current control from 0 mA to 300 mA of diode current.The maximum output current of this configuration is limited by the compliance voltage at the IOUT pin of the ADN8810. The voltage at IOUT cannot exceed 1 V below PVDD, in this case, 4 V. The IOUT voltage is equal to the voltage drop across R S N plus the gate-to-source voltage of the external FET. For this reason, select a FET with a low threshold voltage.In addition, the voltage across the R SN resistor cannot exceed the voltage at the cathode of the laser diode. Given a forward laser diode voltage drop of 2 V in Figure 20, the voltage at the RSN pin (I × R SN ) cannot exceed 3 V . This sets an upper limit to the value of code in Equation 5.Although the configuration for anode-to-ground diodes is similar, the supply voltages must be shifted down to 0 V and −5 V , as shown in Figure 21. The AVDD, DVDD, and PVDD pins are connected to ground with AVSS connected to −5 V .The 4.096 V reference must also be referred to the −5 V supply voltage. The diode current is still determined by Equation 7. All logic levels must be shifted down to 0 V and −5 V levels as well. This includes RESET , CS , SCLK, SDI, SB , and all ADDR pins. Figure 22 shows a simple method to level shift a standard TTL or CMOS (0 V to 5 V) signal down using external FETs.NOTE: LEAVE FB WITH NO CONNECTION03195-0-020Figure 20. Driving Common-Anode-to-VDD Laser DiodesNOTE: LEAVE FB WITH NO CONNECTION03195-0-021Figure 21. Driving Common-Anode-to-Ground Laser Diodes with a NegativeSupplyRESETCS SCLK SDI03195-0-022Figure 22. Level Shifting TTL/CMOS LogicPCB LAYOUT RECOMMENDATIONSAlthough they can be driven from the same power supply voltage, keep DVDD and AVDD current paths separate on the printed circuit board (PCB) to maintain the highest accuracy; likewise for AVSS and DGND. Tie common potentials together at a single point located near the power regulator. This technique is known as star grounding and is shown in Figure 23. This method reduces digital crosstalk into the laser diode or load.LOGIC GROUNDRETURN03195-0-023Figure 23. Star Supply and Ground TechniqueTo improve thermal dissipation, solder the slug on the bottom of the LFCSP package be soldered to the PCB with multiple vias into a low noise ground plane. Connecting these vias to a copper area on the bottom side of the board further improves thermal dissipation.Use identical trace width and lengths for the two output sense resistors. These lengths are shown as X and Y in Figure 24. Differences in trace lengths cause differences in parasitic seriesresistance. Because the sense resistors can be as low as 1.37 Ω, small parasitic differences can lower both the output current accuracy and the output impedance. See the AN-619 Application Note for a sample layout for these traces.03195-0-024Figure 24. Use Identical Trace Lengths for Sense ResistorsSUGGESTED PAD LAYOUT FOR CP-24 PACKAGEFigure 25 shows the dimensions for the PCB pad layout for the ADN8810. The package is a 4 mm × 4 mm, 24-lead LFCSP . The metallic slug underneath the package must be soldered to a copper pad connected to AVSS, the lowest supply voltage to the ADN8810. For single-supply applications, this is ground. Use multiple vias to this pad to improve the thermal dissipation of the package.0.0270.011(0.28)0.020(0.50)CONTROLLING DIMENSIONS ARE IN MILLIMETERS03195-0-025Figure 25. Suggested PCB Layout for the CP-24-10 Pad LandingOUTLINE DIMENSIONS0.300.250.200.800.750.700.25 MIN2.202.10 SQ 2.000.50BSC0.500.400.30COMPLIANT TO JEDEC STANDARDS MO-220-WGGD-8.BOTTOM VIEWTOP VIEWSIDE VIEW4.104.00 SQ 3.900.05 MAX 0.02 NOM0.203 REFCOPLANARITY0.08PIN 1INDICATORFOR PROPER CONNECTION OF THE EXPOSED PAD, REFER TO THE PIN CONFIGURATION AND FUNCTION DESCRIPTIONSSECTION OF THIS DATA SHEET.02-21-2017-AEXPOSED PAD00SEATING PLANEDETAIL A (JEDEC 95)Figure 26. 24-Lead Lead Frame Chip Scale Package [LFCSP]4 mm × 4 mm Body and 0.75 mm Package Height(CP-24-10)Dimensions shown in millimetersORDERING GUIDEModel 1Temperature Range Package DescriptionPackage Option ADN8810ACPZ–40°C to +85°C 24-Lead Lead Frame Chip Scale Package [LFCSP] CP-24-10 ADN8810ACPZ-REEL7–40°C to +85°C 24-Lead Lead Frame Chip Scale Package [LFCSP] CP-24-101Z = RoHS Compliant Part.©2004–2017 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D03195-0-11/17(C)。

CS4334-KSZ资料

3.1 Digital Interpolation Filter ................................................................................................. 12 3.2 Delta-Sigma Modulator .................................................................................................... 12 3.3 Switched-Capacitor DAC ................................................................................................. 12 3.4 Analog Low-Pass Filter .................................................................................................... 12 4. SYSTEM DESIGN .................................................................................................................. 13 4.1 Master Clock .................................................................................................................... 13 4.2 Serial Clock ...................................................................................................................... 13

M7 VHF数据传输器说明书

The M7 VHF data transceiver is a rugged ½ - 5 wattVHF data radio modem with an RS-232 or optional422/485 serial interface, perfect for SCADA andtelemetry applications. Additional options includeIP65-rated (“weatherproof”) enclosure and/or GPS.Product O verviewLong-Range OperationOperating in the VHF 136-155MHz frequency band (other bands available), the RV-M7-VA radio modem works over 60 miles point-to-point and many miles with omni-directional antennas. All RV-M7 modems support store-and-forward repeating for wide-area coverage.Fast PollingThe M7 transceiver has a 5mS PLL in it, making it one of the fastest telemetry radios available, especially well suited for polled, DNP and MODBUS applications. Its can send up to 50 transmissions per second.High Speed and High EfficiencyThe RV-M7 operates with user-selectable over-the air data rates of 800 to 19200bps. Faster rates for higher efficiency or lower-speed for increased communication range.GPS OptionThe optional internal GPS allows the RV-M7 to be a powerful Automatic Vehicle Locating (AVL) system or Time Space Position Information (TSPI) reporting device.Fully ProgrammableIt is configured with a serial connection using industry-standard AT commands. Parameters such as network IDs, unit ID and transmission rate are easily configured. The M7 is easily configured through the included PC program “Radio Manager”. Digital Base BandData rate, modulation, and IF bandwidth are digitally programmed. Wide (25kHz) and Narrow (12.5kH) IF bandwidths may be user-configured. The over-the-air data rate may be adjusted to suit a particular application.Real-time diagnostics and statisticsChannel performance, RSSI, RF power, packet counters, and radio configuration are easily accessed via the serial port or remotely over-the-air.Very Low Power ConsumptionThe advanced VHF transceiver is integrated with a 32-bit microprocessor-based modem in one easy-to mount package. It has very low power consumption, and sleep modes that allow it to be active and consume a minimum amount of resources.Rugged and “Weatherproof”The RV-M7 is available with optional IP65-rated “weatherproof”connections and enclosure. All models include protection against damage from over-temperature, high VSWR, and reverse voltage.Flexible Addressing and Error CorrectionThe RV-M7 uses a 16 bit address with a 16 bit network mask, allowing for many devices to be co-located without receiving each other, as well as the creation of sophisticated network topologies.For More InformationFor more information about this or any other Raveon product, call in the U.S.A. 1-760-444-5995.RV-M7-V ATechnical Specifications are subject to change without notice.Raveon Technologies Corporation2461 Impala DriveCarlsbad, CA 92010Copyright Raveon Technologies Corp, 2012Phone: +1-760-444-5995All rights reservedFax: +1-760-444-5997Email:****************Version C3. Printed in the USAGeneral SpecificationsModel:RV-M7-Vx-oo (x=band) (oo=options) RV-M7-VM (MURS model) Size: 4.60” X 2.60” X .956 (11.7cm X 6.6cm X 2.43cm) Weight:6 ozInput Voltage: 10 – 16 VDC Current draw:Receiving data: <65mA (55mA typ. at 12VDC)Transmitting data: (1.8A @ 5w, 1.1A @ 2W typical) Frequency Band:Band Frequency A 136-155MHz Available Frequencies: B 150-174MHz SRS-M7-VBMURS 5 MURS chan. SRS-M7-VM Serial Port Baud Rates (programmable)1.2k,2.4k, 4.8k, 9.6k, 19.2k, 38.4k, 57.6k, 115.2k Over-the-air baud rates (programmable) Narrow IF: 800, 1200, 2000, 2400, 4.8k, 5142, 8K, 9.6kWide IF: 1200, 2000, 2400, 4.8k, 8k, 9.6k, 19.2k Operating ModeSimplex or Half-duplex Full Spec Operating Temperature range -30°C to +60°CTX-RX and RX-TX turn-around time <5mS Wake-up time<500mS from OFF <5mS from Sleep Front Panel LEDsPower , Status (Carr Det, TX, mode…) RF I/O ConnectorBNC (Female) Power CableRaveon P/N: RT-CB-H1 AddressingIndividual address: 65,536 Groups: 254Transmitter SpecificationsRF Power Output 500mW – 5.0 W programmable (2W max for MURS model)Maximum Duty Cycle 100% @ 2W to 40C, 25% @5W (100% w/ optional heatsink) Frequency Deviation± 2.2kHz (N) ± 3.3kHz (W)RF BandwidthFull-band without tuning Occupied bandwidth 11 kHz (-N) 16kHz(-W)TX Spurious outputs < -70dBc TX Harmonic outputs < -80dBc Occupied BandwidthPer FCCFCC Emissions Designator 11K0F1D (narrowband mode) 15K0F1D (wideband mode) Frequency Stability Better than ±2.5ppmReceiver SpecificationsRX sensitivity (1% PER, N) ................... 9600bps < -108dBm4800bps < -114dB 1200bps < -118dBRF No-tune bandwidth ......................... Full-band without tuning Adjacent Channel Selectivity ................ -70dB (1200bps Wide) Adjacent Channel Selectivity ................ -65dB (1200bps Narrow) Adjacent Channel Selectivity ................ -60dB (4800bps Narrow) Alternate Channel Selectivity ............... -70dB Blocking and spurious rejection ........... -80dBRX intermodulation rejection ............... -75dB (4800bps Narrow) RX intermodulation rejection ............... -80dB (1200bps Narrow)Interface SpecificationsSerial Interface PortConnector Type DB-9IO Voltage Levels RS-232, RS-485, RS-422(user selectable) Word length7 or 8 bits, N, O, or E Modem handshake signalsRTS, CTS, CDAT Commands OverviewChannel Number, Operating Frequency, IF bandwidth Modem StatisticsPower-savings modesUnit Address and Destination address Network Address Mask ARQ error correction on/off Baud Rate, parity, stop bitsSelect Packet or Streaming mode of data transmission Store-and-forward Repeating configurationHardware flow control operation LEDs operation or disabledFor a complete feature list see the technical manual here:/support.html。

baseband

1 ( 64 ) CONFIDENTIAL Nokia Mobile Phones08-Apr-04 错误! 错误!未知的文档属性名称RH37 BasebandTypeSubTitleHereCreator/Owner: Staffan Lamberg Function: Baseband Approver: Victor Burger Location: Lotus Notes, xyz DocMan (if stored in Unix only, pls enter path)Change History see Lotus NotesSelect this option if you maintain the change history in Lotus Notes ONLY. In that case leave the table empty.Vers. 0.1Date 19-05-03Status DraftHandled byComments Initial DraftNew A4PC Template especially for UlmCopyright © Nokia Mobile Phones2 ( 64 ) CONFIDENTIAL Nokia Mobile Phones08-Apr-04 错误! 错误!未知的文档属性名称Contents:1.2. 3.Introduction ................................................................................................................................ 4 1.1 Block diagram ...................................................................................................................... 5Abbreviations ............................................................................................................................... 7 Environmental specifications ........................................................................................................ 8 3.1 Absolute Maximum Ratings ................................................................................................ 8 3.2 Temperature Conditions ..................................................................................................... 8 3.3 Humidity and Water Resistance ........................................................................................ 8 3.4 Frequencies in Baseband ...................................................................................................... 8 3.5 PWB ...................................................................................................................................... 9 3.5.1 Characteristics of the PWB ............................................................................................. 9 3.5.2 Key Components .......................................................................................................... 10 4. Technical Specifications ......................................................................................................... 11 4.1 Baseband Core.................................................................................................................... 11 4.1.1 UPP .............................................................................................................................. 11 4.1.2 UEMEK......................................................................................................................... 11 4.1.3 External SRAM and Flash ......................................................................................... 12 4.2 Energy management ........................................................................................................ 12 4.2.1 Modes of operation .................................................................................................... 12 4.2.2 No Supply ................................................................................................................... 13 4.2.3 Backup ........................................................................................................................ 13 4.2.4 Acting Dead ................................................................................................................ 13 4.2.5 Active ........................................................................................................................... 13 4.2.6 Sleep Mode................................................................................................................. 13 4.2.7 Charging ..................................................................................................................... 14 4.3 Power distribution ................................................................................................................ 14 4.4 DC Characteristics ............................................................................................................... 15 4.4.1 Supply Voltage Ranges ................................................................................................ 15 4.4.2 Baseband regulators..................................................................................................... 16 5. Function Groups ........................................................................................................................ 16 5.1 Battery ................................................................................................................................. 16 5.2 Audio ................................................................................................................................... 17 5.2.1 Internal Microphone ................................................................................................... 17 5.2.2 Internal Speaker ........................................................................................................... 17 5.2.3 IHF Speaker ................................................................................................................. 18 5.2.4 External Audio .............................................................................................................. 19 5.2.5 External Microphone Connection ............................................................................. 19 5.2.6 IHF Speaker and Head Set Connections ...................................................................... 19 5.2.7 Test possibilities ........................................................................................................... 19 5.3 Camera................................................................................................................................ 19 5.3.1 Key Features ................................................................................................................ 20 5.3.2 Specifications ............................................................................................................... 20 5.3.3 CCP Bus ..................................................................................................................... 21 5.3.4 CCI Bus ....................................................................................................................... 21 5.3.5 UIF Bus ....................................................................................................................... 22 5.3.6 Clocks.......................................................................................................................... 22 5.3.7 Test Possibility ........................................................................................................... 22 5.4 Vibra .................................................................................................................................... 22 5.4.1 Test Possibility ........................................................................................................... 22 5.5 FCI ...................................................................................................................................... 22 5.5.1 General......................................................................................................................... 22New A4PC Template especially for Ulm Copyright © Nokia Mobile Phones3 ( 64 ) CONFIDENTIAL Nokia Mobile Phones 5.5.2 5.5.308-Apr-04 错误! 错误!未知的文档属性名称Function........................................................................................................................ 23 Test Possibility ............................................................................................................ 24 5.6 LCD Module ....................................................................................................................... 24 5.6.1 Characteristics ............................................................................................................ 24 5.6.2 LCD Connector........................................................................................................... 25 5.6.3 Test possibility ............................................................................................................ 26 5.7 Keypad ................................................................................................................................ 26 5.7.1 Test Possibility ........................................................................................................... 26 5.8 Illumination .......................................................................................................................... 27 5.8.1 Test Possibility ........................................................................................................... 28 5.9 XPress on grip LEDs ........................................................................................................... 28 5.9.1 Test Possibility ........................................................................................................... 29 5.10 SIM .................................................................................................................................. 29 5.10.1 Test Possibility ........................................................................................................ 29 6. Interfaces ................................................................................................................................... 30 6.1 BB-RF Interface ................................................................................................................... 30 6.1.1 Digital Signals ............................................................................................................. 30 6.1.2 Analogue Signals ....................................................................................................... 31 6.2 System Connector Interface ................................................................................................ 32 6.2.1 System connector ...................................................................................................... 32 6.2.2 ACI ............................................................................................................................... 33 6.2.3 FBUS ............................................................................................................................ 33 6.2.4 VOUT ........................................................................................................................... 34 6.2.5 DC Plug ........................................................................................................................ 34 7. BB Calibration ............................................................................................................................ 35 7.1 UEMEK Calibration .............................................................................................................. 35 7.1.1 Calibration Limits .......................................................................................................... 37 8. Test Points ................................................................................................................................. 38 9. Troubleshooting ......................................................................................................................... 40 9.1 Top level flow 1 .................................................................................................................... 40 9.2 Top level flow 2 .................................................................................................................... 41 9.3 Phone is dead...................................................................................................................... 42 9.4 Phone is dead 2................................................................................................................... 43 9.5 Flash faults .......................................................................................................................... 44 9.6 Flash faults 2 ....................................................................................................................... 45 9.7 Phone is jammed ................................................................................................................. 46 9.8 Phone is Jammed 2 ............................................................................................................. 48 9.9 Charger ............................................................................................................................... 49 9.10 SIM Card .......................................................................................................................... 50 9.11 Audio Faults ..................................................................................................................... 51 9.12 Audio Faults 2 .................................................................................................................. 52 9.13 Audio Faults 3 .................................................................................................................. 53 9.14 Audio Faults 4 .................................................................................................................. 54 9.15 Earpiece .............................................................................................................................. 55 9.16 Display Faults .................................................................................................................. 56 9.17 Display Faults 2................................................................................................................ 57 9.18 Keypad Faults .................................................................................................................. 58 9.19 Keypad faults 2 ................................................................................................................ 59 9.20 Camera Faults.................................................................................................................. 60 9.21 Camera faults2 ................................................................................................................. 61 9.22 Self-test ............................................................................................................................ 62 9.23 Functional Cover Interface ............................................................................................... 63New A4PC Template especially for UlmCopyright © Nokia Mobile Phones4 ( 64 ) CONFIDENTIAL Nokia Mobile Phones08-Apr-04 错误! 错误!未知的文档属性名称1. INTRODUCTION Product RH37 is a DCT4.5 Expression segment phone. There are two variants: An EGSM900 / GSM-1800 / GSM-1900 phone and a US variant, RH 49, with GSM850/1800/1900. The HW has the following features: • • • • • • • • • • • • GPRS and HSCSD with Edge in up to (2RX + 2TX) (MCS5), without edge also in (3RX + 1TX) (MCS6) DCT4 with AMR and 16 MIDI tones 128/16 Mbit Combo memory Amazon Active display with 64k colours Battery BL-5B Illuminated XPress on grips Pop-Port interface 5-way navigation key with select FCI rear side (C-cover) VGA Camera Vibra IHFThe RH37 BB is based on the DCT4/4.5 engine and is compatible to the Pop-Port accessories. The DCT4/4.5 engine consists basically of two ASICs. The UEMEK (Universal Energy Management IC including voltage regulators, charge control and audio circuits, audio IFH amplifier from DCT4.5) and the UPP (Universal Phone Processor including MCU, DSP and RAM from DCT4).New A4PC Template especially for UlmCopyright © Nokia Mobile Phones5 ( 64 ) CONFIDENTIAL Nokia Mobile Phones08-Apr-04 错误! 错误!未知的文档属性名称1.1 Block diagramThe picture below shows the main Baseband function blocks.VVCameraRF InterfaceLCDActive TFD colourFLASH128 MbitSRAMLED drivers16 MbitSIMUEMEKUPP8MFunctional Cover IFBatteryBL-5BKeyboardKeyboard IlluminationVIBRAPAIHFChargerDC jackSystemconnectorPop-PortFigure 1. Baseband block diagramUEMEK supplies both Baseband and RF with power via built in voltage regulators, which are connected to the battery. The RF parts use mainly 2.78 V and the Baseband parts 1.8V I/O voltage. The UPP core is supplied with programmable core voltage of 1.0V, 1.3V or 1.5V. UEMEK includes 7 linear LDO (Low Drop-Out) regulators for Baseband and 7 regulators for RF. It also includes 4 current sources for biasing purposes and internal usage. The UEMEK is furthermore supplying the SIM interface with a programmable voltage of 1.8V or 3V. Note: 5V SIM cards are no longer supported by DCT-4 generation Baseband. UPP operates from a 26 MHz clock coming from the RF ASIC Helga. The clock signal is divided by two down to the nominal system clock frequency of 13 MHz. The DSP and MCU contain PLLs, which can multiply the system clock to a higher frequency.New A4PC Template especially for UlmCopyright © Nokia Mobile Phones6 ( 64 ) CONFIDENTIAL Nokia Mobile Phones08-Apr-04 错误! 错误!未知的文档属性名称A real time clock function is integrated into the UEMEK, which utilizes the same 32kHz clock supply as the sleep clock. The communication between UEMEK and UPP is implemented using two bi-directional serial busses, CBUS and DBUS. The CBUS is controlled by the MCU and operates at a speed of 1 MHz. The DBUS is controlled by the MCU and operates at a speed of 13 MHz. Both processors are located in the UPP. The UEMEK ASIC handles the analog interface between the Baseband and the RF section. UEMEK provides A/D and D/A conversion of the in-phase and quadrature receive and transmit signal paths and also A/D and D/A conversions of received and transmitted audio signals to and from the user interface. The UEMEK supplies the analog TXC and AFC signals to RF section according to UPP .signal control. There are also separate signals for PDM coded audio. Digital speech processing is handled by the DSP inside UPP ASIC. UEMEK is a dual voltage circuit, the digital parts are running from the baseband supply 1.8V and the analog parts are running from the analog supply 2.78V. Also VBAT is directly used (Vibra, LED-driver, Audio amplifier). The Baseband supports both internal and external microphone inputs and speaker outputs. Keypad tones, DTMF, and other audio tones are generated and encoded by the UPP and transmitted to the UEMEK for decoding. An external vibra alert control signals are generated by the UEMEK with separate PWM outputs. EMC shielding is implemented using a soldered shielding, RF cans and PWB grounding.New A4PC Template especially for UlmCopyright © Nokia Mobile Phones7 ( 64 ) CONFIDENTIAL Nokia Mobile Phones08-Apr-04 错误! 错误!未知的文档属性名称2. ABBREVIATIONS ACI: ADC ASIC: BB: BSI DCT4: DSP: DUT: EMC: ESD: FC FR: GSM: HW: IF: IHF: IMEI: I/O IR: IrDa: LCD: LED: LDO MCU: PA Phoenix: PLL PWB: RF RTC SIM: SW: UEMEK: UI: UPP: USB: Accessory Control Interface Analogue to Digital Converter Application Specific Integrated Circuit Baseband Battery Size Indcator Digital Core Technology, generation 4 Digital Signal Processor Device under test Electro Magnetic Compatibility Electro Static Discharge Functional Cover Full Rate Global System for Mobile Communication Hardware Interface Integrated Hands Free International Mobile Equipment Identity Input/Output Infrared Infrared Data Association Liquid Crystal Display Light Emitting Diode Low Drop Out Microprocessor Control Unit Power Amplifier SW tool of DCT4 Phase Locked Loop Printed Wired Board Radio Frequency Real Time Clock Subscriber Identification Module Software Universal Energy Management User Interface Universal Phone Processor Universal Serial BusNew A4PC Template especially for UlmCopyright © Nokia Mobile Phones8 ( 64 ) CONFIDENTIAL Nokia Mobile Phones08-Apr-04 错误! 错误!未知的文档属性名称3. ENVIRONMENTAL SPECIFICATIONS 3.1 Absolute Maximum Ratings Table 1 Absolute Maximum Ratings Signal Battery Voltage (Idle) Battery Voltage (Call) Charger Input Voltage Note -0.3…5.5V Max 4.8V -0.3V …16V3.2 Temperature ConditionsTable 2. Temperature Conditions Condition Normal operating temperature Reduced functionality Storage Min -10°C -25°C -40°C Max +55°C +75°C +85°C3.3 Humidity and Water ResistanceTable 3. Humidity Conditions Condition Relative Humidity Min 5% Max 95%The module is not protected against water.3.4 Frequencies in Baseband Table 4. Frequencies in BasebandFrequency 1,2 kHz?? 32 kHz 1 MHz 6,5 MHz 3,25 MHz 13 MHz 26 MHz 40 MHzContext FCI SleepClk CBUS Display IF SIMIFUPP UEMEK Flash SIM Comment X X X X X X X X X X Min X X X X EstimationUp to 1 MHz RFConvClkDBUS, RFBUClik X RF Clk Memory ClockNew A4PC Template especially for UlmCopyright © Nokia Mobile Phones9 ( 64 ) CONFIDENTIAL Nokia Mobile Phones08-Apr-04 错误! 错误!未知的文档属性名称3.5 PWB 3.5.1 Characteristics of the PWB • • • Single PWB 8 layer board Double side assembledBurried via through internal layersRCCTOVia through all layers Blind BOTTOFigure 2. PWB vias.RCCNew A4PC Template especially for UlmCopyright © Nokia Mobile Phones10 ( 64 ) CONFIDENTIAL Nokia Mobile Phones08-Apr-04 错误! 错误!未知的文档属性名称3.5.2 Key ComponentsD1470 HW Accelerator Figure 3 Key ComponertsD2800 UPPD2200 UEMEKD3000 ComboTable 5 Key ComponentsPosition D1470 D2800 D2200 D3000Component Name HW Accelerator UPP8M UEMEKV1.1 Combo NMP DCT4Code 4370911 337B068 4371701 4341409New A4PC Template especially for UlmCopyright © Nokia Mobile PhonesConfidential Staffan Lamberg4. TECHNICAL SPECIFICATIONS4.1 Baseband Core4.1.1 UPPMain characteristics of the used UPP are:∙DSP by Texas Instruments, LEAD3 16 bit DSP core 32 bit IF max. 200 MHz∙MCU based on ARM RISC MCU core max 50 MHz∙Internal 8 Mbit SRAM (PDRAM)∙General purpose UARTS∙SIM card interface∙Accessory interface (ACI)∙Interface control for Keypad, LCD, Audio and UEM control∙Handling of BB-RF Interface4.1.2 UEMEKMain characteristics of the used UEMEK are:∙ACI support∙Audio codec∙11 Channel A/D converter∙Auxiliary A/D converter∙Real time logic∙32 KHz crystal oscillator∙SIM interface and drivers∙Security logic∙Storage of IMEI code∙Buzzer and vibra motor drivers∙ 2 LED drivers∙Voltage reference for analogue blocks∙Charging function∙Baseband regulators∙RF regulators∙RF interface convertersConfidential Staffan Lamberg4.1.3 External SRAM and FlashThe Combo-Memeory is a multi chip package memory which combines 128 Mbit (8Mx16) muxed burst multibank flash and 16 Mbit muxed CMOS PSRAM (Pseudo SRAM: DRAM with SRAM interface). These two dies are stacked on each other in one package, The functionality of the flash memory is the same as for other generic BB4.0 products.The combo is supplied by single 1,8 V for read, write and erase operations. For accelerated flash programming, VID = 9.0 V has to be applied to VPP input of the combo device.The combo memory is housed in a 44-ball FBGA.Figure 4. Combo memory4.2 Energy managementThe energy management of RH37 is based on BB 4.0 architecture. A so-called semi fixed battery (BL-5B) supplies power primarily to UEMEK ASIC and the RF PA. The UEMEK includes several regulators to supply RF and Baseband. It provides energy management including power up/down procedure.(If the main battery is not present, a cell capacitor maintains backup power supply for the RTC part of UEMEK)4.2.1 Modes of operationThe Baseband engine has six different functional modes: Since the UEMEK controls the regulated power distribution; each of these states affects the general functionality of the phone.1. No supply2. Backup3. Acting Dead4. Active5. Sleep6. ChargingConfidential Staffan Lamberg4.2.2 No SupplyIn NO_SUPPLY mode, the phone has no supply voltage. This mode is due to disconnection of main battery and backup battery or low battery voltage level in both of the batteries.Phone is exiting from NO_SUPPLY mode when sufficient battery voltage level is detected. Battery voltage can rise either by connecting a new battery with VBAT > V MSTR+ or by connecting charger and charging the battery above V MSTR+.4.2.3 BackupIn BACKUP mode the backup battery has sufficient charge but the main battery can be disconnected or empty (VBAT < V MSTR and VBACK > VBU COFF).VRTC regulator is disabled in BACKUP mode. VRTC output is supplied without regulation from backup battery (VBACK). All the other regulators are disabled.4.2.4 Acting DeadIf the phone is off when the charger is connected, the phone is powered on but enters a state called ”Acting Dead”. To the user, the phone acts as if it was switched off. A battery-charging alert is given and/or a battery charging indication on the display is shown to acknowledge the user that the battery is being charged.4.2.5 ActiveIn the Active mode the phone is in normal operation, scanning for channels, listening to a base station, transmitting and processing information. There are several sub-states in the active mode depending on if the phone is in burst reception, burst transmission, if DSP is working etc. In Active mode the RF regulators are controlled by SW writing into UEMEK´s registers wanted settings: VR1A can be enabled or disabled. VR2 can be enabled or disabled and its output voltage can be programmed to be 2.78V or 3.3V. VR4 -VR7 can be enabled, disabled, or forced into low quiescent current mode. VR3 is always enabled in Active mode.4.2.6 Sleep ModeSleep mode is entered when both MCU and DSP are in stand–by mode. Both processors control sleep-mode. When SLEEPX signal (low) is detected UEMEK enters SLEEP mode. VCORE, VIO and VFLASH1 regulators are put into low quiescent current mode. All the RF regulators are off in SLEEP. When SLEEPX=1 detected UEMEK enters ACTIVE mode and all functions are activated.The sleep mode is exited either by the expiration of a sleep clock counter in the UEMEK or by some external interrupt, generated by a charger connection, key press, headset connection etc. In sleep mode VCTCXO is shut down and 32 kHz sleep clock oscillator is used as reference clock for the Baseband.Confidential Staffan Lamberg4.2.7 ChargingIn RH37 the battery type/size is indicated by a BSI-resistor. The resistor value corresponds to a specific battery capacity. Also BTEMP, NTC resistor, is located on an engine board.The battery voltage, temperature, size and current are measured by the UEMEK controlled by the charging software running in the UPP.The charging control circuitry (CHACON) inside the UEMEK controls the charging current delivered from the charger to the battery. The battery voltage rise is limited by turning the UEMEK switch off when the battery voltage has reached 4.2 V. Charging current is monitored by measuring the voltage drop across a 220 mΩ resistor.4.3 Power distributionUnder normal conditions, the battery powers the Baseband module. Individual regulators located within the UEMEK regulate the battery voltage VBAT. These regulators supply the different parts of the phone. 8 regulators are dedicated to the RF module and 6 to the Baseband module.The VSIM regulator is able to deliver both 1,8V and 3,0 V DC and thus supporting two different SIM technologies.The regulator VCORE is likewise adjustable by the MCU. VCORE supplies the core logic of the UPP.The system connector provides a voltage to supply accessories.The white LEDs need a higher voltage supply than the battery can supply and are fed by a separate external voltage regulator.VBAT is directly distributed to the RF power amplifier, audio power amplifier and external Baseband regulators.。

compKPNS