5M40z(封装)

贴片电阻常见封装有9种

贴片电阻常见封装有9种,用两种尺寸代码来表示。

一种尺寸代码是由4位数字表示的EIA(美国电子工业协会)代码,前两位与后两位分别表示电阻的长与宽,以英寸为单位。

我们常说的0603封装就是指英制代码。

另一种是米制代码,也由4位数字表示,其单位为毫米。

下表列出贴片电阻封装英制和公制的关系及详细的尺寸:英制(inch)公制(mm)长(L)(mm)宽(W)(mm)高(t)(mm)a(mm)b(mm)020106030.60±0.050.30±0.050.23±0.050.10±0.050.15±0.05 04021005 1.00±0.100.50±0.100.30±0.100.20±0.100.25±0.10 06031608 1.60±0.150.80±0.150.40±0.100.30±0.200.30±0.20 08052012 2.00±0.201.25±0.150.50±0.100.40±0.200.40±0.20 12063216 3.20±0.201.60±0.150.55±0.100.50±0.200.50±0.20 12103225 3.20±0.202.50±0.200.55±0.100.50±0.200.50±0.20 18124832 4.50±0.203.20±0.200.55±0.100.50±0.200.50±0.20 20105025 5.00±0.202.50±0.200.55±0.100.60±0.200.60±0.20 25126432 6.40±0.203.20±0.200.55±0.100.60±0.200.60±0.20一、零件规格:(a)、零件规格即零件的外形尺寸,SMT发展至今,业界为方便作业,已经形成了一个标准零件系列,各家零件供货商皆是按这一标准制造。

华润矽微代理海立辉PT4205 PT4115 PT1102 PT4207

华润矽威科技(上海)有限公司

PT4205_DSB Rev CH_0.1

Page 4

PT4205

30V/1.2A 高调光比 LED 恒流驱动器

封装信息

SOT89-5 封装

D D1 A

E1

b1

L

e e1

b

E

c

SYMBOL A b b1 c D D1 E E1 e e1 L

MHz mV % µA µA V V V V kHz uA

VCSN VCSN_hys ICSN

关断电流

平均采样电压 采样电压迟滞 CSN管脚输入电流

IOFF DIM输入 VDIM VDIM_H VDIM_L VDIM_DC fDIM(注6) IDIM 功率开关 RSW ISWmean ILEAK 过温保护 TPROT TMAX

37266907930v12a高调光比led恒流驱动器华润矽威科技上海有限公司pagept4205dsbrevch01pt4205管脚vincsnswgnddimsot895exposedpadcsnvinswncncgndpgndadimesop8管脚描述管脚号管脚名称描述sw功率开关的漏端gnd信号和功率地dim开关使能模拟和pwm调光端csn电流采样端采样电阻接在csn和vin端之间vin电源输入端必须就近接旁路电容exposedpad散热端内部接地贴在pcb板上减小热阻esop845nc无连接接地或悬空极限参数注1符号参数参数范围单位电源电压0340sw功率开关的漏端0340csn电流采样端相对vin0360dim开关使能模拟和pwm调光端0330sw功率开关输出电流15dmax功耗注215sot895jaesop8ja工作结温范围40stg储存温度范围55kv联系人

数控车工中级考试题(附参考答案)

数控车工中级考试题(附参考答案)一、单选题(共81题,每题1分,共81分)1.工件上用于定位的表面,是确定工件位置的依据,称为()面。

A、设计基准B、定位基准C、加工基准D、测量基准正确答案:B2.职业道德不体现()。

A、从业者的工资收入B、从业者的道德观C、从业者对所从事职业的态度D、从业者的价值观正确答案:A3.框式水平仪主要应用于检验各种机床及其它类型设备导轨的直线度和设备安装的水平位置,垂直位置。

在数控机床水平时通常需要()块水平仪。

A、3B、2C、4D、5正确答案:B4.在MDI方式下可以()。

A、直接输入指令段并马上按循环启动键运行该程序段B、自动运行内存中的程序C、按相应轴的移动键操作机床D、输入程序并保存正确答案:A5.前置刀架数控车床上用正手车刀车削外圆,刀尖半径补偿指令应该是()。

A、G42B、G43C、G40D、G41正确答案:B6.用以确定公差带相对于零线位置的上偏差或下偏差称为()。

A、标准公差B、尺寸偏差C、基本偏差D、尺寸公差正确答案:C7.G03指令格式为G03X(U)_Z(W)_()_K_F_。

A、BB、VC、ID、M正确答案:C8.FANUC-Oi系统中以M99结尾的程序是()。

A、主程序B、子程序C、增量程序D、宏程序正确答案:B9.创新的本质是()。

A、标新立异B、冒险C、稳定D、突破正确答案:D10.石墨以片状存在的铸铁称为()。

A、蠕墨铸铁B、可锻铸铁C、灰铸铁D、球墨铸铁正确答案:C11.车削塑性材料时,一般应在车刀的前面磨出()。

A、退刀槽B、断屑槽C、主切削平面D、基面正确答案:B12."操作面板上的"DELET"键的作用是()。

"A、删除B、复位C、输入D、启动正确答案:A13.M20粗牙螺纹的小径应车至()mm。

A、20B、17.29C、16.75D、16正确答案:B14.万能角度尺在()范围内,应装上角尺。

电力材料附件清单

1509.36 1522.72 2942.45 9.24 402 57.6 393.3 1679.68 39.2 25.5 84.7 6700 36.4 11258 8345.7 10509 10509 10509 10509 9702.4 10374.48 2462.4 228.55 165 582.56 137.6

5SJ62 MCB DC50(直流系统) C32N 1P C6A C45N-4-1P C45N-6-1P C45N-6-2P C65D-32A-3P C65H/2P 6A AC220v C65N C10 交流 C65N C4-P2 C65N C6-P2 C65N D16 C65N P/D16A C65N/1P 6A C65N/2P 6A AC220v AC220v

MD-60-200 MD-60-230 MD-60-250 MD-60-320 MD-60-340 MD-60-380 M22*50 M20*50 Φ 12*6000 L-1500 L-6000 [10# L=500 [10#a l=3000 63*6*3200 BGL-80-230 L63*6*1415 -108000 -60*8*220 -108000 BGL-80-210 BGL-80-270 BGL-60-210 BGL-80-240 BGL-80-220 Φ 200 M16*100

个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个 个

350 350 350 400 320 320 150 410 200 200 200 170 156 156 230 240 300 450 450 414 406 115 106 450 400 400

MZ1杆型横担 L=6200 L=8200(小导线50㎜--120㎜) XHD-50/10 <63*6*1834 BGL-60-170 BGL-80-190 BGL-60-210 BGL-80-210-(-80*8φ 210) LBS-20 x 2500 M16 x 50 M18*50 MS18*310 BGL-80-150 BGL-80-170 U16-170 MD-60-170 LBS-16*2000 MS16*130 MS16*270 Φ 18 U16-150 LBS-20*200

SYN6288语音合成芯片-使用说明

北京宇音天下科技有限公司

地址:北京市海淀区上地高新技术区

010-62986600

010-62988818

第 1 页 / 共 39 页

2011 年 9 月 6 日更新

目录

SYN6288 中文语音合成芯片数据手册

1.概述 .....................................................................................................................................................................4

44命令帧举例441语音合成播放命令数据区数据区帧结构帧头长度命令字命令参数待发送文本异或校验宇音天下数据0xfd0x000x0b0x010x000xc10xd30xee0xd20xf40xcc0xec0xcf0xc2数据帧0xfd0x000x0b0x010x000xd30xee0xd20xf40xcc0xec0xcf0xc20xc1说明播放文本编码格式为gb2312的文本宇音天下不带背景音乐数据区数据区帧结构帧头长度命令字命令参数待发送文本异或校验宇音天下数据0xfd0x000x0b0x010x010xc00xd30xee0xd20xf40xcc0xec0xcf0xc2数据帧0xfd0x000x0b0x010x010xd30xee0xd20xf40xcc0xec0xcf0xc20xc0说明播放文本编码格式为gbk的文本宇音天下不带背景音乐数据区数据区帧结构帧头长度命令字命令参数待发送文本异或校验宇音天下数据0xfd0x000x0b0x010x020xbb0xa60x740xad0xb50xa40xd10xa40x55数据帧0xfd0x000x0b0x010x020xa60x740xad0xb50xa40xd10xa40x550xbb说明播放文本编码格式为big5的文本宇音天下不带背景音乐帧结构帧头数据区数据区第16页共40页2016年3月9日更新syn6288中文语音合成芯片数据手册长度命令字命令参数待发送文本异或校验宇音天下数据0xfd0x000x0b0x010x030xc30x8b0xed0x970xf30x590x290x4e0x0b数据帧0xfd0x000x0b0x010x030x8b0xed0x970xf30x590x290x4e0x0b0xc3说明播放文本编码格式为unicode的文本宇音天下不带背景音乐数据区数据区帧结构帧头长度命令字命令参数待发送文本异或校验宇音天下数据0xfd0x000x0b0x010x090xc80xd30xee0xd20xf40xcc0xec0xcf0xc2数据帧0xfd0x000x0b0x010x090xd30xee0xd20xf40xcc0xec0xcf0xc20xc8说明播放文本编码格式为gbk的文本宇音天下时同时播放背景音乐1数据区数据区帧结构帧头长度命令字命令参数待发送文本异或校验宇音天下数据0xfd0x000x0b0x010x790xb80xd30xee0xd2

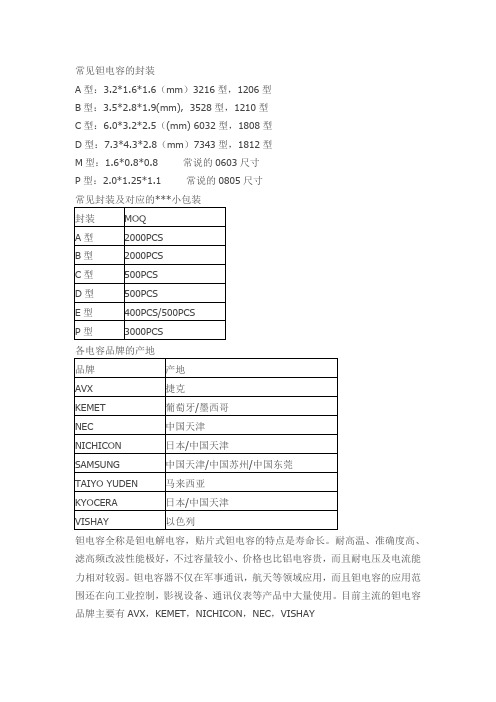

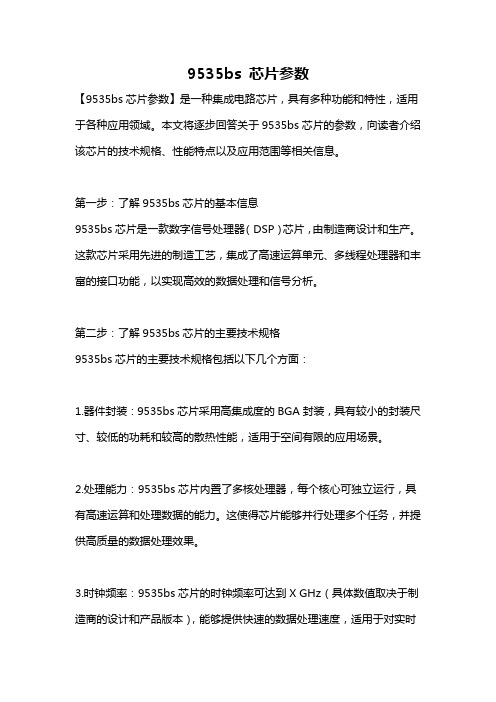

常见钽电容的封装

常见封装及对应的***小包装

封装

MOQ

A型

2000PCS

B型

2000PCS

C型

500PCS

D型

500PCS

E型

400PCS/500PCS

P型

3000PCS

各电容品牌的产地

品牌

产地

AVX

捷克

KEMET

葡萄牙/墨西哥

NEC

中国津

NICHICON

日本/中国天津

常见钽电容的封装

A型:3.2*1.6*1.6(mm)3216型,1206型

B型:3.5*2.8*1.9(mm), 3528型,1210型

C型:6.0*3.2*2.5((mm) 6032型,1808型

D型:7.3*4.3*2.8(mm)7343型,1812型

M型:1.6*0.8*0.8常说的0603尺寸

SAMSUNG

中国天津/中国苏州/中国东莞

TAIYO YUDEN

马来西亚

KYOCERA

日本/中国天津

VISHAY

以色列

钽电容全称是钽电解电容,贴片式钽电容的特点是寿命长。耐高温、准确度高、滤高频改波性能极好,不过容量较小、价格也比铝电容贵,而且耐电压及电流能力相对较弱。钽电容器不仅在军事通讯,航天等领域应用,而且钽电容的应用范围还在向工业控制,影视设备、通讯仪表等产品中大量使用。目前主流的钽电容品牌主要有AVX,KEMET,NICHICON,NEC,VISHAY

Z540中文资料(Intel)中文数据手册「EasyDatasheet - 矽搜」

Inte l proce ssor num be rs are not a m easure of pe rform ance . Proce ssor num be rs diffe re ntiate feature s within each proce ssor

Intel Virtualization Technology (Intel VT) requires a com puter system with an enabled Intel processor, BIO S, virtual m achine m onitor (VMM) and, for som e uses, certain platform software enabled for it. Functionality, perform ance or other benefits will vary depending on hardware and software configurations and m ay require a BIO S update. Software applications m ay not be com patible with all operating system s. Please check with your application vendor.

北京时代民芯科技有限公司 CLGA封装芯片测试夹具说明书

(19)国家知识产权局(12)实用新型专利(10)授权公告号 (45)授权公告日 (21)申请号 202122081758.0(22)申请日 2021.08.31(73)专利权人 北京时代民芯科技有限公司地址 100076 北京市丰台区东高地四营门北路2号专利权人 北京微电子技术研究所(72)发明人 李明远 闫静 姜扬 刘利新 常国义 闫兰丰 黄玉凤 吕学明 (74)专利代理机构 中国航天科技专利中心11009专利代理师 范晓毅(51)Int.Cl.G01R 1/04(2006.01)G01R 31/28(2006.01)(54)实用新型名称一种针对CLGA封装芯片的测试夹具(57)摘要本实用新型提供一种针对CLGA封装芯片的测试夹具,将夹具中传统的单一尺寸导向框改进为包括最大外形导向框和可拆装导向块的导向框组件,最大外形导向框中设有大于等于待测芯片最大外形尺寸上限的内腔,可拆装导向块安装于最大外形导向框,调整内腔的尺寸与待测芯片最大外形尺寸相匹配,实现待测芯片在所述内腔中的定位,进而利用导向框组件,测试座,探针和手测盖之间的配合,实现对待测芯片的测试。

本实用新型解决了陶瓷平面网格阵列封装器件公差较大、器件在测试夹具内定位不精准的问题,可以快速组装不同定位腔尺寸的导向框,不需要通过新制或者返修原有导向框的方法来兼容陶瓷封装器件的最大外形公差,节约了重新制作导向框的成本。

权利要求书2页 说明书4页 附图3页CN 216525901 U 2022.05.13C N 216525901U1.一种针对CLGA封装芯片的测试夹具,包括测试座(1),探针(2)和手测盖(4),其特征在于,还包括导向框组件(3);导向框组件(3)包括最大外形导向框(31)和可拆装导向块(32);所述最大外形导向框(31)设有顶部开口的内腔(311),所述内腔(311)的尺寸大于等于待测芯片最大外形的尺寸上限;待测芯片置于所述内腔(311)中,可拆装导向块(32)固定安装于最大外形导向框(31)上,实现待测芯片在所述内腔(311)中的定位;导向框组件(3)固定安装于测试座(1)上,手测盖(4)设于导向框组件(3)上方,用于测试时向待测芯片施加压力;测试座(1)和导向框组件(3)上分别设有第一针孔和第二针孔,探针(2)通过第一针孔固定安装于测试座(1)上,待测芯片受到所述压力时,探针(2)穿过第二针孔与待测芯片焊盘接触,实现对待测芯片的测试。

理解Altera CPLD 中的时钟

tASU tAH tADS tADH tDSS tDSH tDDS tDDH tDCO tDP tPB tBP tPPMX tAE tEB tBE tEPMX tRA tOE tOSCS tOSCH

参数

说明 地址寄存器移位信号到地址寄存器时钟的建立时间。 来自地址寄存器时钟的地址寄存器移位信号保持时间。 地址寄存器数据输入到地址寄存器时钟的建立时间。 来自地址寄存器时钟的地址寄存器数据输入保持时间。 数据寄存器移位信号到数据寄存器时钟的建立时间。 来自数据寄存器时钟的数据寄存器移位信号保持时间。 数据寄存器数据输入到数据寄存器时钟的建立时间。 来自数据寄存器时钟的数据寄存器数据输入保持时间。 输出数据移出时,从数据寄存器时钟到数据寄存器输出所产生的延时。 PROGRAM 信号到数据时钟的保持时间。 从 PROGRAM 上升沿到用户闪存 BUSY 信号上升沿之间的最大延时。 从用户闪存 BUSY 信号变低到 PROGRAM 信号变低所允许的最小延时。 配置中 busy 脉冲的最大长度。 到地址时钟的最小 ERASE 信号保持时间。 ERASE 上升沿与用户闪存 BUSY 信号上升沿之间的最大延时。 从用户闪存 BUSY 信号变低到 ERASE 信号变低所允许的最小延时。 擦除期间忙脉冲的最大长度。 最大读取访问时间。从 DRSHFT 信号变低到在数据寄存器输出端观察到数据的第一个比特之间的延时。 从 OSC_ENA 信号到达用户闪存,到 OSC 上升时钟离开 UFM 之间的延时。 OSC_ENA 上升沿到 ERASE/PROGRAM 信号上升沿之间的最大延时。 ERASE/PROGRAM 信号变低到 OSC_ENA 信号变低之间所允许的最小延时。

I/O 布局中最优情况下的引脚到引脚延时。在与输入引脚相邻的单边逻辑单元 (LE) 中实现组合逻辑 (2 个输入 “ 与 ” 门 )。显示了两个输入端的最长引脚路径。使用从相邻逻辑单元 (LE) 到输出引脚的快速 I/O 互联。

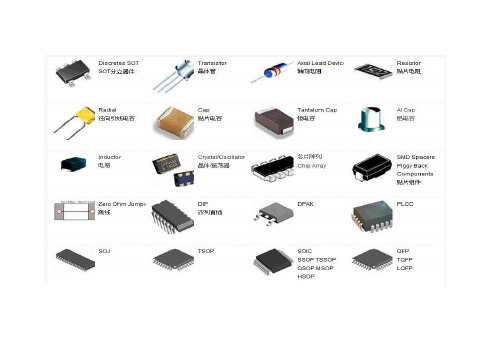

(整理)最全的芯片封装方式图文对照

芯片封装方式大全各种IC封装形式图片精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档精品文档各种封装缩写说明BGA精品文档BQFP132BGA精品文档BGA精品文档BGABGA精品文档BGACLCCCNR精品文档PGADIPDIP-tabBGA精品文档DIPTOFlat Pack精品文档HSOP28TO精品文档精品文档TOJLCCLCCCLCC(ceramic leaded chip carrier) 带引脚的陶瓷芯片载体,表面贴装型封装之一,引脚从封装的四个侧面引出,呈丁字形 。

带有窗口的用于封装紫外线擦除型EPROM 以及带有EPROM 的微机电路等。

此封装也称为 QFJ 、QFJ -G(见QFJ)。

BGALQFPDIP精品文档PGAPLCCPQFP精品文档DIPLQFP精品文档LQFP精品文档PQFPQFP精品文档QFPTQFPBGA精品文档SC-70 5LDIP精品文档SIPSOSOH精品文档SOJSOJ精品文档SOPTO精品文档SOPSOP精品文档CANTOTO精品文档TOTO3CAN精品文档CANCANCANCAN精品文档TO8TO92CAN精品文档CANTSOPTSSOP or TSOP精品文档BGABGAZIP精品文档PCDIP以下封装形式未找到相关图片,仅作简易描述,供参考:DIM单列直插式,塑料例如:MH88500QUIP蜘蛛脚状四排直插式,塑料例如:NEC7810DBGA BGA系列中陶瓷芯片例如:EP20K400FC672-3CBGA BGA系列中金属封装芯片例如: EP20K300EBC652-3MODULE方形状金属壳双列直插式例如:LH0084RQFP QFP封装系列中,表面带金属散装体例如:EPF10KRC系列DIMM电路正面或背面镶有LCC封装小芯片,陶瓷,双列直插式例如:X28C010DIP-BATTERY电池与微型芯片内封SRAM芯片,塑料双列直插式例如:达拉斯SRAM系列(五)按用途分类集成电路按用途可分为电视机用集成电路。

28种芯片封装技术的详细介绍

28种芯片封装技术的详细介绍芯片封装技术是针对集成电路芯片的外包装及连接引脚的处理技术,它将裸片或已经封装好的芯片通过一系列工艺步骤引脚,并封装在特定的材料中,保护芯片免受机械和环境的损害。

在芯片封装技术中,有许多不同的封装方式和方法,下面将详细介绍28种常见的芯片封装技术。

1. DIP封装(Dual In-line Package):为最早、最简单的封装方式,多用于代工生产,具有通用性和成本效益。

2. SOJ封装(Small Outline J-lead):是DIP封装的改进版,主要用于大规模集成电路。

3. SOP封装(Small Outline Package):是SOJ封装的互补形式,适用于SMD(Surface Mount Device)工艺的封装。

4. QFP封装(Quad Flat Package):引脚数多达数百个,广泛应用于高密度、高性能的微处理器和大规模集成电路。

5. BGA封装(Ball Grid Array):芯片的引脚通过小球焊接在底座上,具有较好的热性能和电气性能。

6. CSP封装(Chip Scale Package):将芯片封装在极小的尺寸内,适用于移动设备等对尺寸要求极高的应用。

7. LGA封装(Land Grid Array):通过焊接引脚在底座上,适用于大功率、高频率的应用。

8. QFN封装(Quad Flat No-leads):相对于QFP封装减少了引脚长度,适合于高频率应用。

9. TSOP封装(Thin Small Outline Package):为SOJ封装的一种改进版本,用于闪存存储器和DRAM等应用。

10. PLCC封装(Plastic Leaded Chip Carrier):芯片通过引脚焊接在塑料封装上,适用于多种集成电路。

11. PLGA封装(Pin Grid Array):引脚排列成矩阵状,适用于计算机和通信技术。

12. PGA封装(Pin Grid Array):引脚排列成网格状,适用于高频、高功率的应用。

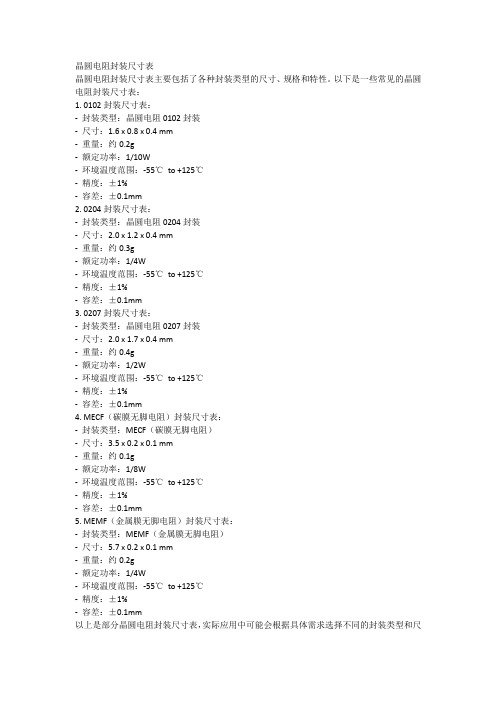

晶圆电阻封装尺寸表

晶圆电阻封装尺寸表晶圆电阻封装尺寸表主要包括了各种封装类型的尺寸、规格和特性。

以下是一些常见的晶圆电阻封装尺寸表:1. 0102封装尺寸表:-封装类型:晶圆电阻0102封装-尺寸:1.6 x 0.8 x 0.4 mm-重量:约0.2g-额定功率:1/10W-环境温度范围:-55℃to +125℃-精度:±1%-容差:±0.1mm2. 0204封装尺寸表:-封装类型:晶圆电阻0204封装-尺寸:2.0 x 1.2 x 0.4 mm-重量:约0.3g-额定功率:1/4W-环境温度范围:-55℃to +125℃-精度:±1%-容差:±0.1mm3. 0207封装尺寸表:-封装类型:晶圆电阻0207封装-尺寸:2.0 x 1.7 x 0.4 mm-重量:约0.4g-额定功率:1/2W-环境温度范围:-55℃to +125℃-精度:±1%-容差:±0.1mm4. MECF(碳膜无脚电阻)封装尺寸表:-封装类型:MECF(碳膜无脚电阻)-尺寸:3.5 x 0.2 x 0.1 mm-重量:约0.1g-额定功率:1/8W-环境温度范围:-55℃to +125℃-精度:±1%-容差:±0.1mm5. MEMF(金属膜无脚电阻)封装尺寸表:-封装类型:MEMF(金属膜无脚电阻)-尺寸:5.7 x 0.2 x 0.1 mm-重量:约0.2g-额定功率:1/4W-环境温度范围:-55℃to +125℃-精度:±1%-容差:±0.1mm以上是部分晶圆电阻封装尺寸表,实际应用中可能会根据具体需求选择不同的封装类型和尺寸。

晶圆电阻封装尺寸的选择应考虑电路设计、功率要求和空间限制等因素。

9535bs 芯片参数

9535bs 芯片参数【9535bs芯片参数】是一种集成电路芯片,具有多种功能和特性,适用于各种应用领域。

本文将逐步回答关于9535bs芯片的参数,向读者介绍该芯片的技术规格、性能特点以及应用范围等相关信息。

第一步:了解9535bs芯片的基本信息9535bs芯片是一款数字信号处理器(DSP)芯片,由制造商设计和生产。

这款芯片采用先进的制造工艺,集成了高速运算单元、多线程处理器和丰富的接口功能,以实现高效的数据处理和信号分析。

第二步:了解9535bs芯片的主要技术规格9535bs芯片的主要技术规格包括以下几个方面:1.器件封装:9535bs芯片采用高集成度的BGA封装,具有较小的封装尺寸、较低的功耗和较高的散热性能,适用于空间有限的应用场景。

2.处理能力:9535bs芯片内置了多核处理器,每个核心可独立运行,具有高速运算和处理数据的能力。

这使得芯片能够并行处理多个任务,并提供高质量的数据处理效果。

3.时钟频率:9535bs芯片的时钟频率可达到X GHz(具体数值取决于制造商的设计和产品版本),能够提供快速的数据处理速度,适用于对实时性要求较高的应用。

4.存储容量:9535bs芯片内置了一定的存储容量,可用于存储程序代码、数据或缓存数据等。

此外,芯片还支持外部存储器接口,方便扩展存储容量。

5.通信接口:9535bs芯片集成了多种通信接口,例如UART、SPI、I2C 等,可用于与外部设备进行数据交换和通信。

这使得芯片在数据传输和通信方面具有很强的灵活性和可扩展性。

第三步:了解9535bs芯片的性能特点9535bs芯片具有以下性能特点:1.高性能:9535bs芯片采用创新的设计和先进的制造工艺,具有优异的性能和强大的计算能力。

其多核处理器和高频时钟使得芯片在数据处理和计算方面表现出色。

2.低功耗:9535bs芯片在设计上注重优化功耗,采用了低功耗的电子元件和智能的功耗管理技术。

这使得芯片在工作时能够有效降低功耗,延长电池寿命,适用于便携设备和低功耗应用。

芯片常用封装及尺寸说明

来源:互联网

关键贴装型封装之一。在印刷基板的反面按列方式制作出球形凸点用以代替引脚,在印刷基板的正面装配LSI芯片,然后用模压树脂或灌封方法进展密封。也称为凸点列载体(PAC)。引脚可超过200,是多引脚LSI用的一种封装。封装本体也可做得比QFP(四侧引脚扁平封装)小。例如,引脚中心距为1.5mm的360引脚BGA仅为31mm见方;而引脚中心距为0.5mm的304引脚QFP为40mm见方。而且BGA不用担忧QFP那样的引脚变形问题。该封装是美国Motorola公司开发的,首先在便携式等设备中被采用,今后在美国有可能在个人计算机中普及。最初,BGA的引脚(凸点)中心距为1.5mm,引脚数为225。现在也有一些LSI厂家正在开发500引脚的BGA。BGA的问题是回流焊后的外观检查。现在尚不清楚是否有效的外观检查方法。有的认为,由于焊接的中心距较大,连接可以看作是稳定的,只能通过功能检查来处理。美国Motorola公司把用模压树脂密封的封装称为OMPAC,而把灌封方法密封的封装称为GPAC(见OMPAC和GPAC)。

2

带缓冲垫的四侧引脚扁平封装。QFP封装之一,在封装本体的四个角设置突起(缓冲垫)以防止在运送过程中引脚发生弯曲变形。美国半导体厂家主要在微处理器和ASIC等电路中采用此封装。引脚中心距0.635mm,引脚数从84到196左右(见QFP)。

ñù>btÿ+q¾î*€AK„ð Ñ_=ïšXš‹%¢j%_Vh^ŸgfuÞl±"ÕFKÛ__M.,8½v¯ß_§_!Y˜_˜½6xidf_8røÀëiynÖ6< ñ_ã_“_" Qžc(éŒP –d_Ö_8³LžË‚_Å•°X²b%LÐ"0Õ _ ¦…y¸¸1<rf ¿_ÒwZxL¼ mþÌDëƒ-ˆÁí¬_c>|û ßöËù_Ð\X_Û`žþCå=ƒ_¯_ä;Pkˆ4vJ)!ã_Ïw±〞_]¢ínݾçÁ_ÛwõVêh5ÍÕªu…A¬‚f¯_"_†R]Y ÔT¥,ÑW(5Úl2as¹ý_–%ä<_¤Á_BšÑÞ_$_LÄtÌ3ï_»±8psÊl¶ˆ$Юd ÏL ¹úÞÐä8XÌeåj|__·ûûú¯`°*‘òád__ÄíKƒæI;_F¹l~8–xóÊù·®œ %â%&º¶A«Vëaòý~Ûô—súÖŸõ—v_î_ ¥MâÆúªŽúz´〞_No_ž0Œ}*.P^_Ž«Ù\8ì__ù™_m__0¨〞Ë` _I0_ó__E刂B©Âe_ EI_rxY›#½[â_K(P_gÒ,‰€TiÕ~—3î´uwTmß±½¦_«F"V_þuþ ÷._4〞__>y®Ðß¼6ãÆ ‘sU©¡Î ŽD‚Ü_ñO|¢£m§ˆ__ÆÃ_Ø‹'‹©Õ‹£~ìûÈð×öÞµ_ÿgÁÿ~c ÙË÷¹_œïoõw6çŸ[,Ö>Œµû¬å_kß_ÿeöwlé_†ïý_hmò¿¶ù_G_ŒJ.Ø5_lðÀ_£_‡fž ~tzh0Ã_l€yëôüßý ÿ)__?ÿ¹S__4fB…oýù·nÞ_9þøî# ì°Û3R‘_Î_ÿô?^ûÖ?¿íM±$__T`__̬ ÇMÄc_ñŠ£ÓHŒF5V__CI_C«_®~‘H_ð[£_. ì_||ã1tDh©L¡QFÃ_—e"_JE9òŒDÖãòºÀ À'¥Q)+Lef›wxxV-V¿ýÖ›_£_ï_³_xû|ã_Ä?ü_15uçÇ_ÚåºþÄÿûg࣡µh镺ή.èUON__xw`yq±_Ög%5“ã_×®»>†Ô_žÍ_¹|dhâíK×_–Wp_ÔÔׄü¾_gnß¼9¤ È_êk0þ¹zåæå+C3s_‰_ŠS〞¯_4ù_¼aôê¡á_—¤Lžæ‘JœO〞é$__†b©_£MÅb_%îtz¼./†C_̱‹y6p¹€Ý®µÇP¢ß‰ç÷KîµnÙZ_ü÷;ѾVɯ…ë¿¿

555的pcb封装尺寸 -回复

555的pcb封装尺寸-回复关于555的PCB封装尺寸的问题,首先我们需要了解什么是555。

555是一款经典的定时集成电路,由于其简单易用的特性,被广泛应用于计时、脉冲生成、波形发生等领域。

而当我们需要将555芯片应用于PCB 设计时,就需要考虑其封装尺寸的问题。

PCB封装尺寸是指555芯片在PCB板上所占据的空间大小。

对于PCB 设计师来说,了解和选择合适的封装尺寸是非常重要的,因为它直接关系到PCB布局的合理性和整体尺寸的控制。

555芯片通常有多种封装尺寸可供选择,常见的有DIP(双列直插封装)和SMD(表面贴装封装)两种类型。

下面将分别介绍这两种封装尺寸的细节。

DIP封装是一种常见的封装形式,特点是引脚可插入插座中。

DIP封装的555芯片一般分为8引脚和14引脚两种尺寸。

其中,8引脚封装的555芯片尺寸大约为9.4mm x 6.4mm,14引脚封装的555芯片尺寸大约为19.81mm x 6.4mm。

这两种尺寸的DIP封装适合手动焊接,容易安装和拆卸,适用于一些需要频繁更换器件的应用场景。

SMD封装是现代电子产品常用的封装形式,特点是引脚焊盘直接焊接在PCB板上。

555芯片的SMD封装有多种类型,常见的有SOIC(小型轮廓集成电路)和SOT(小型外形封装)两种尺寸。

SOIC封装的555芯片一般分为8引脚和14引脚两种尺寸。

其中,8引脚SOIC封装的大小约为4.9mm x 3.9mm,14引脚SOIC封装的大小约为9.9mm x 3.9mm。

SOIC封装适合自动化生产和表面贴装技术,有较好的防尘、防潮和抗震性能,能够满足大批量生产的需求。

SOT封装的555芯片一般分为8引脚和14引脚两种尺寸。

其中,8引脚SOT封装的大小约为2.9mm x 2.8mm,14引脚SOT封装的大小约为4.9mm x 4.8mm。

SOT封装由于体积小,适合于设计紧凑的电子产品,如手机、数码相机等。

在选择555芯片的封装尺寸时,我们需要根据具体应用场景和PCB 设计要求来进行选择。

钽电容封装大全及技术参数

A 型的尺寸3.2 X1.6 X1.6 俗称: A(3216)

B型的尺寸 3.5 X2.8 X1.9 俗称: B(3528)

C型的尺寸 6.0X 3.2X 2.6 俗称: C(6032)

D 型的尺寸7.3 X4.3 X2.9 俗称: D(7343) 厚度2.9英寸

E 型的尺寸7.3 X4.3 X4.1 俗称: E(7343) 厚度4.1英寸

V 型的尺寸7.3X 6.1 X3.45 俗称: V(7361)

J(1608)

P(2012)也就是0805的

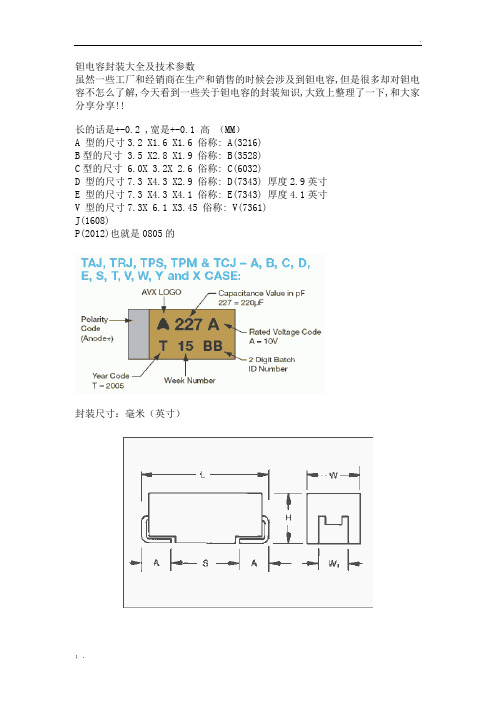

封装尺寸:毫米(英寸)

Code

EIA

Code

L±0.20(0.008)

W+0.20(0.008)

-0.10 (0.004)

334

474

684

A

A

A

A/B

A/B

B

B/C

B/C

1.0

1.5

2.2

105

155

225

A

A

A

A/B

A

A/B

A/B

A/B

A/B/C

A/B/C

B/C

C/D

C/D

3.3

4.7

6.8

335

475

685

A

A

A

A/B

A/B

A/B

A/B

A/B

A/B/C

A/B

B

B/C

B/C

B/C/D

C/D

C/D

D

D

10

15

22

106

V

7361-38

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

04R-00384- 1.0

Package

Outline

64-Pin Plastic Enhanced Quad Flat (EQFP) - Wire Bond - A:1.20 - D2:4.5

All dimensions and tolerances conform to ASME Y14.5M – 1994. Controlling dimension is in millimeters. Pin 1 may be indicated by an ID dot, or a special feature, in its proximity on package surface.

Altera Corporation

04R-00384-1.0

0.15 g (Typ.) Printed on moisture barrier bag

Package Outline Dimension Table

Symbol A A1 A2 D D1 D2 E E1 E2 L L1 S b c e 0 0.20 0.13 0.09 3.50 0.45 3.50 Millimeters Min. 0.05 0.95 Nom . 1.00 9.00 BSC 7.00 BSC 4.50 9.00 BSC 7.00 BSC 4.50 0.60 1.00 REF 0.18 0.40 BSC 3.5 7 0.23 0.20 5.50 0.75 5.50 Max. 1.20 0.15 1.05

July 2011

Altera Corporation

04R-00384-1.0

2

Altera Device Package Information

Package Outline

TOP VIEW

BOTTOM VIEW

Pin 64

Pin 64

Pin 1 Pin 1 ID

Pin 1

Pin 16

Pin 16

See Detail A

Detail A

04R-00384-1.0

July 2011

Altera Corporation

Altera Device Package Information

3

Document Revi sion Hi story

Table 1 shows the revision history for this document.

Package Information

Description Ordering Code Reference Package Acronym Leadframe Material Lead Finish (plating) JEDEC Outline Reference Lead Coplanarity Weight Moisture Sensitivity Level Specification E EQFP Copper Regular: 85Sn:15Pb (Typ.) Pb-free: Matte Sn MS-026 Variation: ABD-HD 0.003 inch (0.08mm)

Table 1. Document Revision History Date

July 2011Version源自1.0 Initial release

Changes

101 Innovation Drive San Jose, CA 95134 July 2011

© 2011 Altera Corporation. All rights re served. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Re g. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trad emarks and service marks are the property of their respective holders as described at /common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera’s standard warranty, but reserves the right t o make changes to any products and services at any time without notice. Altera assumes no responsibility or liability ar ising out of the applic ation or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers a re advised to obtain the latest version of device specifications before relying on any published information and before placing orders for pr oducts or services.