数字集成电路课程设计74hc138

74HC138_中文资料(工程师必备蓝桥)

74HC138:工程师必备的蓝桥芯片详解一、74HC138芯片概述1. 输入端:具有3个地址输入端(A、B、C)和1个使能端(E1、E2A、E2B);2. 输出端:共有8个输出端(Y0至Y7),分别对应8种不同的输入状态;3. 逻辑功能:当使能端有效时,根据地址输入端的组合,选择一个输出端为低电平,其余输出端为高电平;4. 驱动能力:输出端可驱动8个TTL负载。

二、74HC138芯片引脚功能1. A、B、C:地址输入端,用于选择输出端;2. E1:使能端1,低电平有效;3. E2A、E2B:使能端2,用于扩展译码器,低电平有效;4. Y0至Y7:输出端,对应8种不同的输入状态。

三、74HC138芯片工作原理74HC138芯片的工作原理如下:1. 当使能端E1为低电平,且E2A和E2B中至少有一个为高电平时,芯片处于工作状态;2. 根据地址输入端A、B、C的组合,选择一个输出端为低电平,其余输出端为高电平;3. 当使能端无效时,所有输出端均为高电平。

四、74HC138芯片应用示例假设我们需要设计一个电路,根据输入的三个开关状态(A、B、C),控制8个LED灯的亮灭。

具体步骤如下:1. 将74HC138芯片的A、B、C端分别连接到三个开关;2. 将E1端接地,确保芯片始终处于工作状态;3. 将E2A和E2B端接高电平,扩展译码器功能;4. 将Y0至Y7端分别连接到8个LED灯的正极,负极接地;5. 根据开关状态,对应的LED灯会点亮。

五、74HC138芯片的优势与应用场景74HC138芯片以其独特的优势,在多个领域发挥着重要作用:1. 优势:高集成度:一个小巧的芯片就能实现八路译码功能;低功耗:CMOS工艺制造,功耗较低,适用于电池供电设备;稳定性强:输出端具有高抗干扰能力,确保电路稳定运行;兼容性好:与TTL逻辑电平兼容,便于与其他数字电路芯片配合使用。

2. 应用场景:数字电路设计:用于地址译码、信号分配等;自动化控制:实现多种控制信号的切换;仪器仪表:用于多通道选择和信号处理;计算机及外设:用于接口电路设计,实现数据传输和控制。

74HC138概述

74HC138概述1.输入输出电压范围广:74HC138可以接受2V到6V的输入电压,同时其输出也可以在整个电源电压范围内工作。

2.低功耗:相较于传统的TTL器件,CMOS技术使得74HC138具有较低的功耗,能够有效降低电路的发热和功耗。

3.高速操作:74HC138在1.5V至6V的电源电压下,其传输延迟非常小,可以实现高速操作。

4.集成电路设计:74HC138具有集成电路设计的优势,可以将多个逻辑门的功能集成在一颗芯片中,从而减少了电路板上的元器件数量和连线数量。

5.三-八线译码器解码器:74HC138具有三个输入引脚(A0,A1和A2)和八个输出引脚(Y0至Y7)。

根据输入的二进制编码,译码器可以将其转换为相应的输出信号。

6.节省IO口:通过使用74HC138,可以将一个微控制器的输出端口连接到译码器的输入端口,从而实现多个输入/输出设备的控制。

这样就可以节省大量的IO口,提高系统的扩展性。

7.灵活的应用:74HC138可以用于地址译码器的设计,用于选择存储器、IO设备和外围设备。

同时,它也可以用于多路选择器、多维逻辑交叉开关等应用。

8.可靠性:74HC138具有较高的可靠性和稳定性,能够在各种环境条件下稳定工作。

使用74HC138进行地址译码器设计时,用户可以通过将地址总线连接到译码器的输入引脚,将存储器、IO设备和外围设备连接到译码器的输出引脚,从而实现对这些设备的选择和控制。

通过对输入信号和输出信号的编码和解码,地址译码器能够根据用户的需求正确选择所需的设备。

总之,74HC138是一种高性能的三-八线译码器解码器,具有广泛的应用领域和诸多优势。

在数字电路设计中,使用74HC138可以简化电路结构、节省资源、提高系统性能和可靠性,因此在电子工程领域有着重要的地位和作用。

译码器74HC138中文资料

译码器74HC138中文资料2010-01-01 08:00集成电路介绍:译码器74HC138中文资料74hc138 3-8线译码器,译码器也称解码器,译码过程实际上是一种翻译过程,即编码的逆过程。

译码器的输入是n位二值代码,输出是m个表征代码原意的状态信号(或另一种代码)。

一般情况下有m小于等于2的n次方,即译码器输入线比输出线要少。

译码器按其功能可分为三大类:(1)变量译码器:将输入的二进制代码还原为原始输入信号。

例如有两位二进制代码(0 ,1),可经译码器还原为四个信号状态(0,0)(0,1)(1,0) (1,1)(2)代码变换译码器:用于将一个数据的不同代码之间的相互转换。

例如二-十进制译码器可将8421码转换为十个状态。

(3)显示译码器:将数字、文字或符号的代码还原成相应的数字、文字、符号并显示出来的电路74hc138 3-8线译码器/CD74HC138 ,CD74HC238和CD74HCT138 , CD74HCT238是高速硅栅CMOS解码器,适合内存地址解码或数据路由应用。

hc138 作用原理于高性能的存贮译码或要求传输延迟时间短的数据传输系统,在高性能存贮器系统中,用这种译码器可以提高译码系统的效率。

将快速赋能电路用于高速存贮器时,译码器的延迟时间和存贮器的赋能时间通常小于存贮器的典型存取时间,这就是说由肖特基钳位的系统译码器所引起的有效系统延迟可以忽略不计。

HC138 按照三位二进制输入码和赋能输入条件,从8 个输出端中译出一个低电平输出。

两个低电平有效的赋能输入端和一个高电平有效的赋能输入端减少了扩展所需要的外接门或倒相器,扩展成24 线译码器不需外接门;扩展成32 线译码器,只需要接一个外接倒相器。

在解调器应用中,赋能输入端可用作数据输入端。

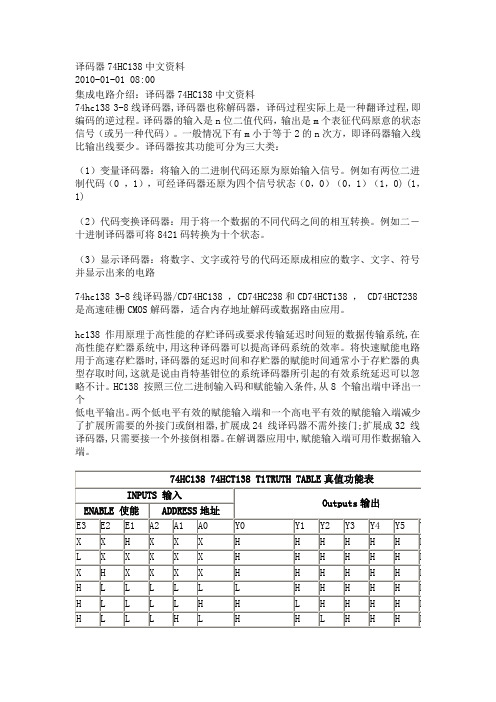

H L L L H H H H H L H H H H L L H L L H H H H L H H H L L H L H H H H H H L H H L L H H L H H H H H H L H L L H H H H H H H H H HCD74HC238, CD74HCT238 T1TRUTH TABLE真值表INPUTS 输入Outputs输出ENABLE 使能ADDRESS地址E3 E2 E1 A2 A1 A0 Y0 Y1 Y2 Y3 Y4 Y5 Y6 X X H X X X L L L L L L L L X X X X X L L L L L L L X H X X X X L L L L L L L H L L L L L H L L L L L L H L L L L H L H L L L L L H L L L H L L L H L L L L H L L L H H L L L H L L L H L L H L L L L L L H L L H L L H L H L L L L L H L H L L H H L L L L L L L H H L L H H H L L L L L L L图1 引脚图图2 功能图图3 测试电路和波形应用电路:图4 舞台发光二极管灯光图5 可编程时钟定时器电路由上表可见74HC138译码器输出低电平有效。

(完整word版)实验四74HC138译码器实验

实验四 74HC138译码器实验一、实验目的与要求1、掌握74HC138译码器的工作原理,熟悉74HC138译码器的具体运用连接方法,了解74HC138是如何译码的。

2、认真预习本节实验内容,尝试自行编写程序,填写实验报告二、实验内容1、编写程序:使用82C55的PC0、PC1、PC2控制74HC138的数据输入端,通过译码产生8选1个选通信号,轮流点亮8个LED指示灯。

2、运行程序,验证译码的正确性。

1C3区C3区C3B4区:CS、A0、A1——A3区:CS1、A0、A12、调试程序,查看运行结果是否正确。

五、实验程序及流程图。

MODEL TINYCon_8255 EQU0F003H;8255控制口PC_8255 EQU 0F002H;8255 PC口.STACK 100.CODESTART:MOV DX,Con_8255MOV AL,80HOUT DX,AL;8255初始化,PC口作输出用MOV DX,PC_8255MOV AL,0START1:OUT DX,ALCALL DelayINC ALJMP START1Delay PROC NEAR;延时Delay1:XOR CX,CXLOOP $RETDelay ENDPEND START六、实验结果8个LED灯循环亮灭。

七、实验总结74HC138译码器通过将ABC三个口表示的十进制数转换为Y0-Y7显示的二进制数实现译码,并且可与控制端口一起实现对地址的选择。

还可以将74HC138译码器与8255的三个端口连在一起,实现对它的编程控制。

利用74HC138制作4线—16线译码器

《组合逻辑电路的分析与设计》————利用74HC138制作4线—16线译码器院系:电子与信息工程学院利用74HC138制作4线—16线译码器一、实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

二、实验仪器1、数字电路实验箱2、74HC138 3-8线译码器 2片三、实验原理1、CMOS器件74HC138的逻辑功能及应用74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

其引脚排列如下图(一)所示图(一)74HC138功能表如下表(一)所示:输入输出E1(非)E2(非)E3A2A1AY0(非)Y1(非)Y2(非)Y3(非)Y4(非)Y5(非)Y6(非)Y7(非)H L H L L L L H H H H H H H H L H L L H H L H H H H H H H L H L H L H H L H H H H H H L H L H H H H H L H H H H H L H H L L H H H H L H H H H L H H L H H H H H H L H H H L H H H L H H H H H H L H L L H H H H H H H H H H H LL X X X X X H H H H H H H H X H X X X X H H H H H H H H表(一)3、用两个3线-8线译码器构成4线-16线译码器。

数字电子线路实验报告_译码器及其应用

数电实验报告实验三译码器及其应用一、实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

4、学习译码器的扩展。

二、实验仪器1、数字逻辑电路实验板1块2、74HC138 3-8线译码器2片3、74HC20 双4输入与非门1片三、实验原理1、中规模集成译码器74HC13874HC138是集成3线-8线译码器,在数字系统中应用比较广泛。

图3-1是其引脚排列。

其中A2 、A1 、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

74HC138真值表如下:74HC138引脚图为:74HC138工作原理为:当S1=1,S2+S3=0时,电路完成译码功能,输出低电平有效。

其中:2、译码器应用因为74HC138 三-八线译码器的输出包括了三变量数字信号的全部八种组合,每一个输出端表示一个最小项,因此可以利用八条输出线组合构成三变量的任意组合电路。

四、实验内容1、译码器74HC138 逻辑功能测试(1)控制端功能测试测试电路如图:按上表所示条件输入开关状态。

观察并记录译码器输出状态。

LED指示灯亮为0,灯不亮为1。

(2)逻辑功能测试将译码器使能端S1、2S、3S及地址端A2、A1、A0 分别接至逻辑电平开关输出口,八个输出端依次连接在逻辑电平显示器的八个输入口上,拨动逻辑电平开关,按下表逐项测试74HC138的逻辑功能。

2、用74HC138实现逻辑函数Y=AB+BC+CA如果设A2=A,A1=B,A0=C,则函数Y的逻辑图如上所示。

用74HC138和74HC20各一块在实验箱上连接下图线路。

并将测试结果下面的记录表中。

3、用两个3线-8线译码器构成4线-16线译码器。

利用使能端能方便地将两个3/8译码器组合成一个4/16译码器,如下图所示。

五、实验结果记录:2、74HC138实现逻辑函数Y=AB+BC+CA,实验结果记录:六、实验注意事项1、注意集成电路输入控制端和输出控制端的信号。

集成电路课程设计--含2个 2-4线译码器的74HC139芯片

集成电路课程设计----含2个2-4线译码器的74HC139芯片一.目的与任务本课程设计是《集成电路分析与设计》的实践课程,其主要目的是为了在了解了集成电路的基本结构的基础上进一步的学习集成电路的设计,本次设计通过对TANNER TOOLS PRO工具的使用让我们能够从简单入手到能设计一个完整的芯片,。

并进行电路仿真对比。

二.课程设计题目、内容及要求2.1 设计题目1.器件名称:一个3-8译码器的74HC138芯片;2.要求的电路性能指标:(1)可驱动10个LSTTL电路(相当于15pF电容负载);(2)输出高电平时,︱IoH︱≤20uA,Voh,min=4.4V;(3)输出低电平时,︱IoL︱≤4mA,Vol,max=0.4V;(4)输出级充放电时间tr = tf,tpd<25ns;(5)工作电源5V,常温工作,工作频率fwork =30MHz,总功耗Pmax=150mW。

2.2 设计内容(1)功能分析及逻辑设计(2)电路设计(3)估算功耗与延时(4)电路模拟与仿真(5)版图设计(全手工、层次化设计)(6)版图检查:DRC与LVS(7)后仿真(选做)(8)版图数据提交2.3 设计要求(1)独立完成设计74HC138 芯片的全过程;(2)设计时使用的工艺及设计规则:MOSIS:mamin08;(3)根据所用的工艺,选取合理的模型库;(4)选用以lambda(λ)为单位的设计规则;(5)全手工、层次化设计版图;(6)达到指导书提出的设计指标要求。

三、74HC139电路简介3.1 通用74HC139芯片的引脚图74HC139芯片包含两个2-4译码器,它的通用引脚图入图1其中,(1A0、1A1)和(2A0、2A1)分别为两个译码器的地址输入端,而1E (以下取名为Csa )和2E (以下取名为Csb )分别为两个译码器的使能端(低电平有效),1Y0~1Y7和2Y0~2Y7为译码器的数据输出端。

3.2通用74HC139的真值表 通用74HC139的真值表如表一3.3通用74HC139的逻辑表达式根据表一,我们可以很容易得到一下的逻辑表达式 Y0=E+A1+A0=01A A E ∙∙ Y1=E+A1+0A =01A A E ∙∙ Y2=E+1A +A0=01A A E ∙∙ Y3=E+1A +0A =01A A E ∙∙3.4通用74HC139的逻辑图,如图2所示图二所示为通用74HC139芯片的其中一个译码器的逻辑图。

微机原理上机实验(六+十)实验报告 74HC138译码器实验 16x16点阵显示实验

微机原理上机实验报告实验六:74HC138译码器实验实验十:LED 16x16点阵显示实验微机原理上机实验(六)实验报告实验六:74HC138译码器实验一、实验目的1、掌握74HC138译码器的工作原理,熟悉74HC138译码器的具体运用连接方法,了解74HC138是如何译码的。

2、认真预习本节实验内容,尝试自行编写程序,填写实验报告二、实验内容1、编写程序:使用8255的PC0、PC1、PC2控制74HC138的数据输入端,通过译码产生8选1个选通信号,轮流点亮8个LED指示灯。

2、运行程序,验证译码的正确性。

三、实验原理图四、实验步骤1、连线说明:F7区:A、B、C ——D3区:PC0、PC1、PC2F7区:G1、G2A、G2B ——C1区:VCC、GND、GNDF7区:JP63 ——F4区:JP18(LED指示灯)D3区:CS、A0、A1 ——A3区:CS1、A0、A12、调试程序,查看运行结果是否正确五、实验代码Con_8255 EQU 0273H ;8255控制口PC_8255 EQU 0272H ;8255 PC口_STACK SEGMENT STACK ;设置堆栈段DW 100 DUP(?)_STACK ENDSCODE SEGMENTSTART PROC NEARASSUME CS:CODE, SS:_STACKMOV DX,Con_8255MOV AL,80HOUT DX,AL ;8255初始化,PC口作输出用,向8255的控制口输入置位/复位控制字10000000B,PC0~PC7全部复位MOV DX,PC_8255MOV AL,0START1: OUT DX,AL 将00000000B输入8255的PC口CALL Delay 延时INC AL AL加一JMP START1 循环Delay PROC NEAR ;延时Delay1: XOR CX,CX ;CX清零LOOP $ 当前位置循环一次后推出RETDelay ENDPSTART ENDPCODE ENDSEND START六、实验思考题1.在应用系统中,74HC138通常用来产生片选信号,请读者考虑一下,应如何处理?将输入信号转换为三位无符号二进制数,将转换后的数据由低到高分别输入74HC138的A、B、C口,即可实现对最多8的模块的片选功能。

利用74HC138制作4线—16线译码器

《组合逻辑电路的分析与设计》————利用74HC138制作4线—16线译码器院系:电子与信息工程学院利用74HC138制作4线—16线译码器一、实验目的1、掌握译码器的测试方法。

2、了解中规模集成译码器的功能,管脚分布,掌握其逻辑功能。

3、掌握用译码器构成组合电路的方法。

二、实验仪器1、数字电路实验箱2、74HC138 3-8线译码器 2片三、实验原理1、CMOS器件74HC138的逻辑功能及应用74HC138译码器可接受3位二进制加权地址输入(A0, A1和A2),并当使能时,提供8个互斥的低有效输出(Y0至Y7)。

74HC138特有3个使能输入端:两个低有效(E1和E2)和一个高有效(E3)。

除非E1和E2置低且E3置高,否则74HC138将保持所有输出为高。

利用这种复合使能特性,仅需4片74HC138芯片和1个反相器,即可轻松实现并行扩展,组合成为一个1-32(5线到32线)译码器。

任选一个低有效使能输入端作为数据输入,而把其余的使能输入端作为选通端,则74HC138亦可充当一个8输出多路分配器,未使用的使能输入端必须保持绑定在各自合适的高有效或低有效状态。

其引脚排列如下图(一)所示图(一)74HC138功能表如下表(一)所示:表(一)3、用两个3线-8线译码器构成4线-16线译码器。

利用使能端能方便地将两个 3/8译码器组合成一个4/16译码器,如下图图(二)所示。

图(二)四、实验结果记录:1、74HC138逻辑功能测试结果记录如下表表(二)所示:输入输出E 1E2+E3A2A1AY0(非)Y1(非)Y2(非)Y3(非)Y4(非)Y5(非)Y6(非)Y7(非)1 0 0 0 0 0 1 1 1 1 1 1 1 1 0 0 0 1 1 0 1 1 1 1 1 1 1 0 0 1 0 1 1 0 12 1 1 1 1 1 0 0 1 1 1 1 1 0 1 1 1 1 1 0 1 0 0 1 1 1 1 0 1 1 1 1 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 1 1 0 1 1 1 1 1 1 1 1 1 1 0 0 X X X X 1 1 1 1 1 1 1 1 X 1 X X X 1 1 1 1 1 1 1 1表(二)2、测试部分图片如下图图(三)、图(四)、图(五)、图(六)图(七)所示:图(三)图(四)图(五)图(六)图(七)五、实验心得:通过这次试验,使我学到了不少实用的知识,更重要的是,做实验的过程,思考问题的方法,这与做其他的实验是通用的,真正使我受益匪浅。

74HC138

54138/741383线-8线译码器简要说明:138为3线-8线译码器,共有54/74S138和54/74LS138两种线路结构型式,其主要电特性的典型值如下:型号 T pd (ABC->Y)(3级) P DCT54S138/CT74S138 8ns 245mWCT54LS138/CT74LS13822ns 32mW当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。

利用G1、/(G2A)和/(G2B)可级联扩展成24线译码器;若外接一个反相器还可级联扩展成32线译码器。

若将选通端中的一个作为数据输入端时,138还可作数据分配器。

管脚图:引出端符号:A、B、C 译码地址输入端G1 选通端/(G2A)、/(G2B) 选通端(低电平有效)Y0~Y7 译码输出端(低电平有效)功能表:/G2*=G2A+G2BH=高电平L=低电平X=任意极限值电源电压------------------------------------------------7V输入电压54/74S138----------------------------------------5.5V54/74LS138---------------------------------------7V 工作环境温度54×××------------------------------ -55~125℃74×××------------------------------------0~70℃ 贮存温度-------------------------------------- -65~150℃推荐工作条件:CT54S138/CT74S138 CT54LS138/CT74LS138单位最小额定最大最小额定最大54 4.5 5 5.54.5 5 5.5V 电源电压Vcc74 4.75 5 5.254.75 5 5.25输入高电平电压V IH 2 2 V54 0.80.7V 输入低电平电压V IL74 0.80.8输出高电平电流I OH-1000-400 µA54 20 4mA 输出低电平电流I OL74 20 8逻辑图静态特性(T A 为工作环境温度范围)`S138`LS138 参数 测试条件【1】 最小最大最小最大 单位 VIK 输入钳位电压Vcc 最小 IIK=-12mA -1.2 -1.5 V54 2.5 2.5VOH 输出高电平电压 Vcc=最小,VIH=2V,VIL=最大,IOH=最大 74 2.7 2.7 V54 0.5 0.4 VOL 输出低电平电压 VCC=最小,VIH=2V,VIL=最大,IOL=最大 740.5 0.5 V VI=5.5V 1 II 最大输入电压时输入电流 Vcc=5VVI=7V 0.1 mA IH 输入高电平电流Vcc=5V,VIH=2.7V 50 20 μA VI=5.5V 1 II 最大输入电压时输入电流 Vcc=最大VI=7V0.1 mA IIH 输入高电平电流 Vcc=最大 VIH=2.7V50 20 μAVIL=0.4V -0.4VIL 输入低电平电流Vcc=最大VIL=0.5V-2 mA 54-40 -100-6 -40 IOS 输出短路电流Vcc=最大 74-40-100-5 -42 mA Icc 电源电流Vcc=最大7410mA 【1】:测试条件中的“最大”和“最小”用推荐工作条件中的相应值。

(完整版)74hc138数码管应用

单片机动态扫描驱动数码管一、本文内容提要本刊第四期介绍了单片机外接键盘的原理,并给出了应用实例。

本期将介绍单片机动态驱动段式数码管。

通过该讲,读者可以掌握段式数码管的工作原理和如何通过动态驱动的方法设计电路以及程序。

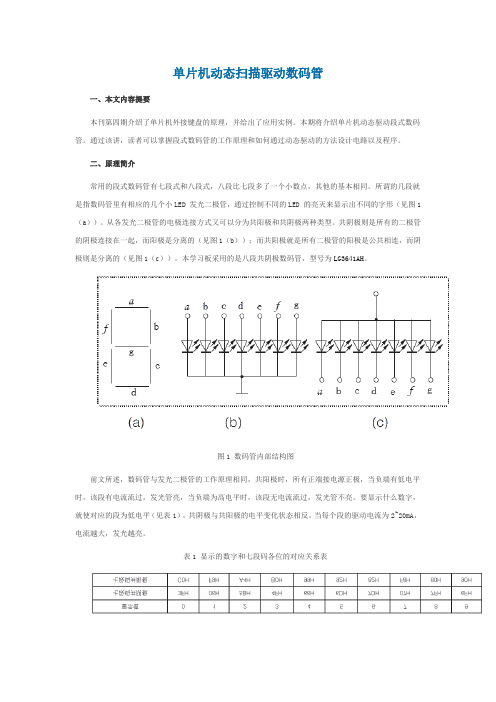

二、原理简介常用的段式数码管有七段式和八段式,八段比七段多了一个小数点,其他的基本相同。

所谓的几段就是指数码管里有相应的几个小LED 发光二极管,通过控制不同的LED 的亮灭来显示出不同的字形(见图1(a))。

从各发光二极管的电极连接方式又可以分为共阳极和共阴极两种类型。

共阴极则是所有的二极管的阴极连接在一起,而阳极是分离的(见图1(b));而共阳极就是所有二极管的阳极是公共相连,而阴极则是分离的(见图1(c))。

本学习板采用的是八段共阴极数码管,型号为LG3641AH。

图1 数码管内部结构图前文所述,数码管与发光二极管的工作原理相同,共阳极时,所有正端接电源正极,当负端有低电平时,该段有电流流过,发光管亮,当负端为高电平时,该段无电流流过,发光管不亮。

要显示什么数字,就使对应的段为低电平(见表1)。

共阴极与共阳极的电平变化状态相反。

当每个段的驱动电流为2~20mA,电流越大,发光越亮。

表1 显示的数字和七段码各位的对应关系表常用的七段式数码管的硬件驱动设计方法有:静态驱动与动态驱动。

静态驱动即指每个数码管的数据线都有一个单独的数据锁存器,数据锁存器输入的数据由使能端控制,当使能端为高电平时,数据线上的数据(要显示的七段码)进入显示器,使能端与地址译码器的输出相连,要显示那位,则选通那位的地址,在软件设计上不要求程序循环,也不存在显示数字发生闪烁。

但是这样会占用很多口线。

动态显示是将所有位数码管的段选线并联在一起,由位选线控制是哪一位数码管有效。

这样一来,就没有必要每一位数码管配一个锁存器,从而节省了口线,地简化了硬件电路。

所谓动态扫描显示即轮流向各位数码管送出字形码和相应的位选,利用发光管的余辉和人眼视觉暂留作用,使人的感觉好像各位数码管同时都在显示。

单片机课件设计—74HC138译码器实验

单片机课件设计—74HC138译码器实验设计者:王凡(20070901140)蒋太明(20070901136)设计者所在班级:计算机科学系应用0703班51单片机74HC138译码器实验设计流程一.实验目的熟悉译码器的使用方法,灵活应用74HC138进行电路设计。

二.实验设备及器件IBM PC 机一台DP-51PROC 单片机综合仿真实验仪一台三.实验内容1. 编写程序,通过单片机的P1 口控制74HC138的数据输入端,从而选通相应的数据输出位。

2. 将译码数据输出端口连接到8 个LED 指示灯,验证译码的正确性。

四.实验要求通过实验掌握译码器的工作原理和实际应用方法。

表3.3 74HC138真值表和管脚图五.实验步骤1. 短接A3 区JP4 接口上的短路帽,将A3 区A、B、C、/G1、/G2A、/G2B 与A2区的P10~P15相连。

如图3.9 所示。

图3.9 实验9 原理图2. 将D1 区的LED1、LED2、LED3 分时连接到A3 区译码数据输出接口/Y0~/Y7。

3. 打开程序调试软件,下载运行编写好的软件程序,查看程序运行结果是否正确。

六.实验预习要求认真阅读本书这一节的实验内容,提前做好实验准备工作。

七.实验参考程序ORG 8000H ;此为硬件仿真程序,使用软件仿真或直接运行,应改为0000HLJMP MainORG 8100H ;此为硬件仿真程序,使用软件仿真或直接运行,应改为0100HMAIN:MOV SP,#60HMOV R4,#0DJNZ R4,$;设置译码器使能CLR P1.5CLR P1.4SETB P1.3;译码数据输入CLR P1.0 ;设置A=0CLR P1.1 ;设置B=0SETB P1.2 ;设置C=1SJMP $;END。

74hc138的工作原理

74hc138的工作原理74HC138是一种集成电路,它是一个3-8线解码器。

它具有8个输出位线(Y0至Y7)和3个输入位线(A0、A1和A2)。

工作原理如下:当74HC138的使能端(E1、E2和E3)为高电平时,解码器开始工作。

使能端的状态可以通过逻辑门或外部信号来控制。

使能端为低电平时,解码器处于无效状态,输出线的状态是未定义的。

输入位线(A0、A1和A2)用于选择要输出的位线。

通过调整输入位线的状态,可以选择8个输出位线中的一个进行激活。

接下来,我们将更详细地描述74HC138的工作原理。

1. 输入编码:输入位线(A0、A1和A2)用于输入编码信息。

通过将这些位线连接到逻辑高电平或逻辑低电平,可以选择需要激活的输出位线。

具体而言,有8种不同的输入编码方式可以选择一个或多个输出位线。

2. 译码和输出:根据输入编码的不同组合,解码器将选择一个或多个输出位线进行激活。

当输入编码为特定模式时,相应的输出位线将被拉低,其他输出位线将保持高电平状态。

这意味着在激活位线上会有一个低电平信号。

例如,当输入编码为000时,输出位线Y0将被选中;当输入编码为001时,输出位线Y1将被选中;以此类推,当输入编码为111时,输出位线Y7将被选中。

请注意,如果使用74HC138的使能端(E1、E2和E3)为低电平,则解码器的输出位线的状态将保持未定义,无论输入编码的状态如何。

3. 逻辑门操作:在74HC138电路中,逻辑门用于控制使能端的状态。

当使能端为高电平时,解码器工作;当使能端为低电平时,解码器处于无效状态。

这意味着无论输入编码如何,输出位线的状态都将是未定义的。

逻辑门操作的目的是选择解码器的工作模式。

通过将多个74HC138连接到逻辑门或其他逻辑电路,可以实现更复杂的逻辑功能。

总结:74HC138是一种3-8线解码器,可以将输入编码转换为相应的输出位线。

通过选择不同的输入编码组合,可以选择一个或多个输出位线进行激活。

【精品】集成电路课程设计74hc138

目录【摘要】.................................................... 错误!未指定书签。

1。

设计目的与任务........................................... 错误!未指定书签。

2。

设计要求及内容........................................... 错误!未指定书签。

3。

设计方法及分析........................................... 错误!未指定书签。

3.174HC138芯片简介...................................... 错误!未指定书签。

3.2工艺和规则及模型文件的选择........................... 错误!未指定书签。

3。

3电路设计............................................ 错误!未指定书签。

3.3.1输出级电路设计................................. 错误!未指定书签。

3.3。

2.内部基本反相器中的各MOS尺寸的计算........... 错误!未指定书签。

3.3。

3.四输入与非门MOS尺寸的计算................... 错误!未指定书签。

3.3。

4.三输入与非门MOS尺寸的计算................... 错误!未指定书签。

3。

3.5.输入级设计................................... 错误!未指定书签。

3。

3.6.缓冲级设计................................... 错误!未指定书签。

3。

3.7.输入保护电路设计............................. 错误!未指定书签。

3.4。

功耗与延迟估算..................................... 错误!未指定书签。

74HC138译码器实验

74HC138译码器实验74HC138译码器实验一、实验目的掌握74138电路的基本知识及由软件编译的译码器控制方式。

二、实验说明译码器是可以将输入二进制代码的状态翻译成输出信号,以表示其原来含义的电路。

三、实验步骤由软件控制138译码器的工作方式,可以改变A,B,C 的端口而改变其译码输出JD6口接8位发光二极管JD10,显示译码输出值。

本实验要用到单片机最小应用系统(F1区)、八位逻辑电平输出(B1区)、十六位逻辑电平显示(I4区)和译码器模块(C5区)。

1、单片机最小应用系统CPU 的P1口JD1F 接138译码器上的JD2C,而138译码器的JD3C 接到十六位逻辑显示JD2I ,A 、B 、C 接八位逻辑电平输出的K2,K1,K0。

(K2为低位,K0为高位如要选择Y1,K2、K1、K0对应的值为001)2、用串行数据通信线连接计算机与仿真器,把仿真器插到模块的锁紧插座中,请注意仿真器的方向:缺口朝上。

3、打开Keil uVision2仿真软件,首先建立本实验的项目文件,接着添加“TH27_74138译码程序.ASM ”源程序,进行编译,直到编译无误。

4、编译无误后,全速运行程序。

改变K0,K1,K2的状态观察发光二极管的显示,是否与控制端口的对应。

5、也可以把源程序编译成可执行文件,用ISP 烧录器烧录到89S52/89S51芯片中。

(ISP 烧录器的使用查看附录二)四、实验程序(见光盘中的程序文件夹)五、原理图A 1B 2C3G2A 4G2B 5G16Y77Y69Y510Y411Y312Y213Y114Y015U6C 74LS13812345678JD2C12345678JD3C Y0-7ABC。

7.1 74HC138测试电路设计与搭建

根据图 7-3 所示搭建 74HC138 测试电 路, 74HC138 测试板卡的正面如图 7-4 所示。根据图 7-3, 使用 LK8820 提供 的万能测试板焊接 74HC138 测试电路 板, 将焊接完成的 74HC138 测试电路 板插到 DUT 板卡的正面, 使用杜邦线将 74HC138 测试电路板与 DUT板卡连接 起来。

图7-1 74HC138引脚图

7.1.2 认识74HC138

2. 74HC138芯片的真值表

74HC138 真值表如表 7-2 所示。

表7-2 74HC138真值表

7.1.2 认识74HC138

3. 74HC138芯片的工作原理

图7-2 74HC138工作原理

7.1.3 74HC138测试电路设计与搭建

《集成电路封装与测试》课程

项目七:74HC138 芯片测试

7.1 74HC138 测试电路设计与搭建

74HC138测试电路设计与搭建

知识目标

7.1.1 任务描述

利用 LK8820 集成电路测试平台和 LK230T 集成电路应用开发资源系统, 根据 74HC138 译码器工作原理, 完成 74HC138 测试电路设计与搭建, 要求如下。 (1)测试电路能实现 74HC138 的开短路、 静态工作电流、 直流参数及功能测试。 (2)74HC138 测试电路的搭建, 采用基于测试区的测试方式, 也就是把 LK8820 与LK230T 的测 试区结合起来, 完成 74HC138 测试电路搭建。 74HC138 是一款高速 CMOS 元器件, 具有传输延迟时间短、 高性能的特点。 例如, 在高性能存 储器系统中, 使用 74HC138 译码器可以提高译码系统的效率。

74hc138的应用原理

74HC138的应用原理介绍74HC138是一种三到八线解码器,通常被用于数字电路设计中。

它具有识别三个输入信号,并将其映射到八个输出之一的功能。

本文将介绍74HC138的工作原理及其应用。

工作原理74HC138由三个二输入正逻辑门和一个三输入与非门组成。

它的三个输入(A0,A1和A2)可以表示八个不同的输入组合,输出由Y0到Y7表示。

通过设置三个输入信号中的不同组合,可以选择要激活的输出。

接下来,我们将详细介绍74HC138的应用原理。

使用示例以下是一个使用74HC138的示例电路图:python +—–+ +—–+ A0 —-| |————–| | | 74HC138 Y0 —- | A1 —-| |————–| | + +—–+ + +—–+ A2 —-| | | | | Decoder | | Register | | | | | E1 —-| | | | E2 —-| | | | E3 —-| | | | +————+ +————+ | | | | | 74LS138 | | 74LS175 | | | | | | | | | +————+ +————+ ```在上述电路中,输入A0,A1和A2信号用于选择要激活的输出。

74HC138芯片将输入信号和输出互相连接,并通过输出信号将电流传递到68LS175寄存器芯片。

功能以下是74HC138的功能:1.选择输出信号:通过设置输入A0,A1和A2的不同组合,可以选择激活的输出。

共有八个输出(Y0到Y7)。

2.输入信号:74HC138接收三个输入信号(A0,A1和A2)。

3.解码功能:74HC138将输入信号解码为对应的输出信号。

4.数字电路集成:74HC138是一个数字电路集成芯片,通过一片芯片就能实现数字信号的输入和输出。

应用领域74HC138广泛应用于以下领域:1.数字系统设计:74HC138用于基于数字信号的系统设计,如计算机、电子设备等。

74HC138系列单片机控制LED数码管的原理图解析

74HC138系列单片机控制LED数码管的原理图解析LED小灯是一种简单的LED,只能通过亮和灭来表达简单的信息。

而这节课我们要来学习一种能表达更复杂信息的器件——LED数码管。

先给大家提供一张原理图看一下,如图5-3所示。

这是比较常见的数码管的原理图,我们板子上一共有6个数码管。

前边有了 LED 小灯的学习,数码管学习就会轻松的多了。

从图5-3可以看出来,数码管共有 a、b、c、d、e、f、g、dp 这么8个段,而实际上,这8个段每一段都是一个LED 小灯,所以一个数码管就是由8个LED 小灯组成的。

我们看一下数码管内部结构的示意图,如图5-4。

数码管分为共阳和共阴两种,共阴数码管就是8只 LED 小灯的阴极是连接在一起的,阴极是公共端,由阳极来控制单个小灯的亮灭。

同理,共阳数码管就是阳极接在一起,大家可以认真研究下图5-4。

细心的同学会发现,图5-3的数码管上边有2个com,这就是我们数码管的公共端。

为什么有2个呢,一方面是2个可以起到对称的效果,刚好是10个引脚,另外一个方面,公共端通过的电流较大,我们初中就学过,并联电路电流之和等于总电流,用2个 com 可以把公共电流平均到2个引脚上去,降低单条线路承受的电流。

从我们开发板的电路图上能看出来,我们所用的数码管都是共阳数码管,一共有6个,如图5-5所示。

6个数码管的 com 都是接到了正极上,当然了,和 LED 小灯电路一样,也是由74HC138 控制三极管的导通来控制整个数码管的使能。

先来看最右边的DS1 这个数码管,原理图上可以看出,控制DS1 的三极管是 Q17,控制 Q17 的引脚是 LEDS0,对应到 74HC138 上边就是 U3 的 Y0 输出,如图5-6所示。

我们现在的目的是让 LEDS0 这个引脚输出低电平,相信大家现在可以根据前边学过的知识独立把ADDR0、ADDR1、ADDR2、ADDR3、ENLED 这4个所需输入的值写出来了,现在大家不要偷懒,根据74HC138 的手册去写一下,不需要你记住这些结论,但是遇到就写一次,锻炼过几次后,遇到同类芯片自己就知道如何去解决问题了。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录1.目的与任务 (1)2.教学内容基要求 (1)3.设计的方法与计算分析 (1)3.1 74H C138芯片简介 (1)3.2 电路设计 (3)3.3功耗与延时计算 (6)4.电路模拟 (14)4.1直流分析 (15)4.2 瞬态分析 (17)4.3功耗分析 (19)5.版图设计 (19)5.1 输入级的设计 (19)5.2 内部反相器的设计 (19)5.3输入和输出缓冲门的设计 (22)5.4内部逻辑门的设计 (23)5.5输出级的设计 (24)5.6连接成总电路图 (24)5.3版图检查 (24)6.总图的整理 (26)7.经验与体会 (26)8.参考文献 (26)附录 A 电路原理图总图 (28)附录B总电路版图 (29)集成1. 目的与任务本课程设计是《集成电路分析与设计基础》的实践课程,其主要目的是使学生在熟悉集成电路制造技术、半导体器件原理和集成电路分析与设计基础上,训练综合运用已掌握的知识,利用相关软件,初步熟悉和掌握集成电路芯片系统设计→电路设计及模拟→版图设计→版图验证等正向设计方法。

2. 教学内容基本要求2.1课程设计题目及要求器件名称:3-8译码器的74HC138芯片 要求电路性能指标:⑴可驱动10个LSTTL 电路(相当于15pF 电容负载); ⑵输出高电平时,OH I ≤20uA,min,OH V =4.4V; ⑶输出低电平时,OLI ≤4mA ,manOL V , =0.4V⑷输出级充放电时间r t =ft ,pdt <25ns ;⑸工作电源5V ,常温工作,工作频率workf =30MHZ ,总功耗maxP =15mW 。

2.2课程设计的内容 1. 功能分析及逻辑设计; 2. 电路设计及器件参数计算;3. 估算功耗与延时;4. 电路模拟与仿真;5. 版图设计;6. 版图检查:DRC 与LVS ;7. 后仿真(选做);8. 版图数据提交。

2.3课程设计的要求与数据1. 独立完成设计74HC138芯片的全过程;2. 设计时使用的工艺及设计规则: MOSIS:mhp_ns5;3. 根据所用的工艺,选取合理的模型库;4. 选用以lambda(λ)为单位的设计规则;3. 设计的方法与计算分析3.1 74HC138芯片简介74HC138是一款高速CMOS器件,74HC138引脚兼容低功耗肖特基TTL 系列图3-1 74HC138管脚图表3-1 74HC138真值表由于74HC138芯片是由两个2-4译码器组成,两个译码器是独立的,所以,这里只分析其中一个译码器。

由真值表可以看出,Cs为片选端,当其为0时,芯片正常工作,当其为1时,芯片封锁。

A1、A0为输入端,Y0-Y3为输出端,而且是低电平有效。

分析其逻辑功能,可以得到逻辑表达式:图3-2 74HC138逻辑图3.2 电路设计本次电路设计采用的是ml2_typ.md 模型的各参数。

其参数如下: N 管:oxε =3.9×8.85×1210-F/mNμ=700410-⨯Vsm /2m t ox μ1.0= V V tn 0.1= P 管:oxε=3.9×8.85×1210-F/m Vs m p /1030024-⨯=μm1.0μ=ox t V V tp 0.1-=3.2.1输出级电路设计据要求,输出级等效电路如图3-3所示,输入Vi 为前一级的输出,可认为是理想的输出,即iLV =SS V ,iHV =DD V 。

图3-3 输出级等效电路⑴输出级N 管N(W/L)的计算当输入为高电平时,输出为低电平,N 管导通,后级TTL 有较大的灌电流输入,要求OLI ≤4mA ,manOL V ,=0.4V ,依据MOS 管的理想电流统一方程式:])()[()(2221D T G S T G LW t ds V V V V V V I oxox -----⋅⋅⋅=με可以求出N(W/L)的值。

其主要计算如下:()()[]222d tn g S tn g n ox ox dsn NV V V V V V t I L W -----=⎪⎭⎫⎝⎛με=4.06.71070085.89.351.0104103⨯⨯⨯⨯⨯⨯⨯⨯--≈109 ⑵输出级P 管()pL W/的计算当输入为低电平时,输出为高电平,P 管导通。

同时要求N 管和P 管的充放电时间fr t t =,分别求出这两个条件下的()min,/P L W极限值,然后取大者。

①以OHI ≤20uA,VV OH 4.4min ,=为条件计算()min,/P L W极限值,用MOS 管理想电流方程统一表达式:])()[()(2221D T G S T G LW t ds V V V V V V I oxox -----⋅⋅⋅=με可以求出()pL W/的值。

其主要计算如下:()()[]222dtp g s tp g p ox ox dsp P V V V V V V t I L W -----=⎪⎭⎫⎝⎛με=()22412664.34103501085.89.3101.010202-⨯⨯⨯⨯⨯⨯⨯⨯⨯----≈0.75≈1②N 管和P 管的充放电时间r t 和ft 表达式分别为()()()⎥⎦⎤⎪⎪⎭⎫ ⎝⎛--+⎢⎣⎡--⎪⎭⎫ ⎝⎛⋅⋅=ddtn dd tn dd tn dd dd tn n n ox ox L fV V V V V V V V V W L t C t 2019ln 11.022με()()()⎥⎦⎤⎪⎪⎭⎫ ⎝⎛--+⎢⎢⎣⎡--⎪⎭⎫ ⎝⎛⋅⋅=⋅dd tp dd tpddtp dd ddtp p p ox ox L r V V V V VVV V V W L t C t 2019ln 11.022με以fr t t =计算()min,/P L W的值。

其计算如下:设()()()⎥⎦⎤⎪⎪⎭⎫ ⎝⎛--+⎢⎣⎡--⎪⎭⎫ ⎝⎛⋅=ddtn dd tn ddtn dd dd tn n n ox oxV V V V V V V V V W L t Kn 2019ln 11.022με()()()⎥⎦⎤⎪⎪⎭⎫ ⎝⎛--+⎢⎢⎣⎡--⎪⎭⎫ ⎝⎛⋅=⋅dd tp dd tpddtpdd dd tp p pox oxV V V V VV V V V W L t Kp 2019ln 11.022με由fr t t =,故有()()()⎥⎦⎤⎪⎪⎭⎫ ⎝⎛--+⎢⎢⎣⎡--⎪⎭⎫ ⎝⎛⋅dd tp dd tpddtpdd dd tp p pV V V V VV V V V W L 2019ln 11.0221μ代入数据,化简可以得=⎪⎭⎫ ⎝⎛p W L n W L ⎪⎭⎫ ⎝⎛37,代入109=⎪⎭⎫ ⎝⎛nL W 255=⎪⎭⎫⎝⎛PL W比较两种方法的P L W ⎪⎭⎫ ⎝⎛,取其中的最大值,即取255=⎪⎭⎫⎝⎛PL W()()()=⎥⎦⎤⎪⎪⎭⎫ ⎝⎛--+⎢⎣⎡--⎪⎭⎫ ⎝⎛⋅ddtn dd tn ddtn dd dd tn n n V V V V V V V V V W L 2019ln 11.0221μ3.2.2内部基本反相器中的各MOS 尺寸的计算内部基本反相器如图3-4所示,它的N 管和P 管尺寸依据充放电时间r t 和ft 方程来求。

关键点是先求出式中的L C (即负载)。

图3-4 内部反相器它的负载由以下内部反相器(如右图所示)的负载由CL 以下三部分电容组成:①本级漏极的PN 结电容CPN ;②下级的栅电容Cg ;③连线杂散电容CS 。

①本级漏极PN 结电容CPN 计算 C PN =C j ×(Wb )+C jsw (2W+2b)其中C j 是每um 2的结电容,Cjp 是每um 的周界电容,b 为有源区宽度,可从设计规则获取。

在这里,最小孔为2λ×2λ,孔与多晶硅栅的最小间距为2λ,孔与有源区边界的最小间距为2,则取b =6λ。

总的漏极PN 结电容应是P 管 的和N 管的总和,即:C PN =(C j,n ×W N +C j,p ×W P )b +C jsw ,n ×(2W N +2b)+ C jsw ,p ×(2W P +2b)采用的模型参数有:24./102m F C N j -⨯= m F C n jsw /1019.-⨯=24./102m F C P j -⨯= m F C P jsw /1019.-⨯=代入数据到PN C 的式子得)103.0622(10)103.0622(10103.06)102102(6969644-------⨯⨯⨯++⨯⨯⨯+⨯+⨯⨯⨯⨯+⨯⨯=P N P N PN W W W W C = 15910102.7))(102106.3(---⨯++⨯+⨯N P W W =F W W P N 159102.7)(1036.2--⨯++⨯ ②栅电容Cg 计算1471226,,1053.41011085.89.3)106.0()255109()()(----⨯=⨯⨯⨯⨯⨯⨯+=+=⎪⎪⎭⎫ ⎝⎛+⎪⎪⎭⎫ ⎝⎛=+=ox ox P N oxox p ox oxN P g N g g t L W W t A tA C C C εεε③连线杂散电容Cs一般C PN +C g ≈10C S ,可忽略C S 作用。

所以,内部基本反相器的总负载电容L C 为上述各电容计算值之和。

即有149141591025.5)(1036.21053.4102.7)(1036.2-----⨯++⨯=⨯+⨯++⨯=+=P N P N g PN L W W W W C C C根据tr=tf=2.5ns 的条件 P N W W 73=Np W W 37=。

[]λλ42.3106.974.0106.0)1025.57101036.2(10385.89.3105.274.0106.010385.89.31025.5)(1036.2105.274.0103001085.89.3101025.5)(1036.2105.27614914261414942412714949≈=⨯=⨯⨯⨯⨯+⨯⨯=⨯⨯⨯⨯⨯⨯⨯⨯⨯⨯⨯⨯++⨯=⨯⨯⎪⎭⎫ ⎝⎛⨯⨯⨯⨯⨯⨯⨯++⨯=⨯-----------------p p p P P N PP N W W W W W W W L W W 即224==⎪⎭⎫⎝⎛λλP L W 1273=⨯=⎪⎭⎫⎝⎛NL W 由于仿真时候阈值电压过小,所以把宽长比都调为43.2.3 内部逻辑门MOS 尺寸的计算,内部反相器,与非门,内部反相器,与非门==P P 4⎪⎭⎫⎝⎛⎪⎭⎫ ⎝⎛⎪⎭⎫⎝⎛⎪⎭⎫ ⎝⎛L W L W L W L W N N代入内部反相器的宽长比,可以算出逻辑MOS 尺寸:244P P =⎪⎭⎫⎝⎛⎪⎭⎫ ⎝⎛=⎪⎭⎫⎝⎛⎪⎭⎫ ⎝⎛,内部反相器,与非门,内部反相器,与非门==L W L W L W L W N N为了方便绘图,把与非门的pmos宽长比设定为4图3-5 内部逻辑门电路3.2.4输入级设计由于本电路是与TTL兼容,TTL的输入电平V iH可能为2.4V,如果按正常内部反相器进行设计,则N1、P1构成的CMOS将有较大直流功耗。