RS编解码的FPGA实现

基于CycloneⅢ构成的RS编码系统

基于CycloneⅢ构成的RS编码系统苗鑫;邓攀;殷奎喜【摘要】本文采用Ahera公司的FPGA器件CycloneIII系列EP3CIO作为核心器件构成了R-S(255,223)编码系统;利用QuartusⅡ9.0作为硬件仿真平台,用硬件描述语言Verilog_HDL实现编程,并且通过JTAG接口与EP3C10连接。

R—S(Reed—Solomon)码是一类纠错能力很强的特殊的非二进制BCH码,能应对随机性和突发性错误,广泛应用于各种通信系统中和保密系统中。

R—S (255,223)x6能够检测32字节长度和纠错16字节长度的连续数据错误信息。

%This paper uses Altera company FPGA Cyclone III series EP3C10 devices as a core component of R-S (255223) coding system;Using Quartus II 9.0 as a hardware emulation platform, using hardware description language Verilog__HDL programming, and through the JTAG interface and EP3C10 conneetion.R-S ( Reed-Solomon ) code is a kind of special non binary BCH code which's error correction capability is very strong, can deal with random and burst error, widely used in all kinds of communication systems and security systems.R-S (255223) code is capable of detecting and correcting the length of 32 bytes 16 byte length of continuous data error information.【期刊名称】《电子设计工程》【年(卷),期】2012(020)004【总页数】4页(P189-192)【关键词】CycloneⅢ;QuartusⅡ9.0;Verilog_HDL;R—S(255;223).码【作者】苗鑫;邓攀;殷奎喜【作者单位】南京师范大学物理科学与技术学院,江苏南京210046;南京师范大学物理科学与技术学院,江苏南京210046;南京师范大学物理科学与技术学院,江苏南京210046【正文语种】中文【中图分类】TN911.22R-S码是用其发明人的名字Reed和Solomon命名的。

RS译码BM算法及IBM算法

RS译码BM算法及IBM算法1966年,berlekamp利用迭代算法译bch码,避免了矩阵的逆计算,从而大大加快了译码速度。

1969年,j.l.massey从序列综合的角度重新推导了该算法,给出了迭代译码算法与序列的最短移位寄存器综合之间的关系。

我们称这一算法为berlekamp-massey算法(bm算法)。

在介绍RS码的BM算法之前,我们需要介绍RS码的伴随译码算法:让传输的码字多项式为C(x)?中国?1xn?1.c1x?c0ll错误个数为t的错误图样多项式为e(x)?etxt?...?e1x1,其中xi称为错误位置数,该位置的错误值是ei。

接收序列多项式r(x)?c(x)?e(x)?rn?1x则伴随式sj?r(?m0?j?1n?1l?...?r1x?r0)? e(?m0?j?1)j?1,2,..., D一?et(?t)lm0?j?1?...?e1(?l1)m0?j?1L伴随仅取决于传输过程中发生的错误模式,与编码数据无关。

顺序我席(i=1,2,…,t)然后Sj?etxtm0?J1.e1x1m0?J1j?1,2,..., D一我们希望从这d-1个方程求出2t(?d?1)个未知数ei、xi(i?1,2,...,t)定义错误位置多项式? (x)??(1?xxi)?1.1x??2x2?。

??txti?1t则由?(xi)?0(i?1,2,...,t),可以得到? 11?? 1xi?1.2xi?2.伊克西?T0上式两端同乘以eixim0?j?1?t,我们有eixim0?J1.TIxim0?J1.T1.2eixim0?J1.T2.teixim0?J1.0上式对i=1,2,...,t求和得到? e(xii?1tm0?j?1?ti?1xim0?j?1?t?1?2xim0?j?1?t?2?…?ixim0?j?1)?0即sj?t??1sj?t?1??2sj?t?2?...??tsj?0由上式可以得到如下递推关系sj??(?1sj?1?2sj?2?..?tsj?t)j?T1.D一此关系式可以用线性反馈移位寄存器表示,如下图2.4RS码的解码问题变成:已知D?1.伴随,设计一个最小阶的连接多项式?(x)?1??1x???2x2?...??txt的线性反馈移位寄存器(即最短线性反馈移位寄存器),生成这个伴随序列。

RS纠错编码原理及其实现方法

0110

6

α6

α (α 2 + α ) = α 3 + α 2 (mod p(α ))

1100

12

α7

α (α 3 + α 2 ) = α 3 + α +1 (mod p(α ))

1011

11

α8

α (α 3 + α +1) = α 2 +1 (mod p(α ))

0101

5

α9

α (α 2 +1) = α 3 + α (mod p(α ))

mi 表示第 i 个信息码, p j 表示第 j 个校验码

各个校验码可从下列线性方程组求得。

h11m1 + h12m2 + ... + h1k mk +1p1 + 0 p2 + ... + 0 pr = 0 h21m1 + h22m2 + ... + h2k mk + 0 p1 +1p2 + ... + 0 pr = 0 ... hr1m1 + hr2m2 + ... + hrk mk + 0 p1 + 0 p2 + ... +1pr = 0

4、RS 码的生成矩阵

G = [Ik p]

左边是 k × k 阶单位方阵。这相当于码字多项式的第 n −1次至 n − k 次的系数是信息位。而

其余的位校验位。

根据前面的定义 c(x) 是 g(x) 的倍式

c(x) = m(x)xn−k + r(x) = 0(mod g(x)) ( m(x)xn−k 表示在信息组后面插 n − k 个

RS编码

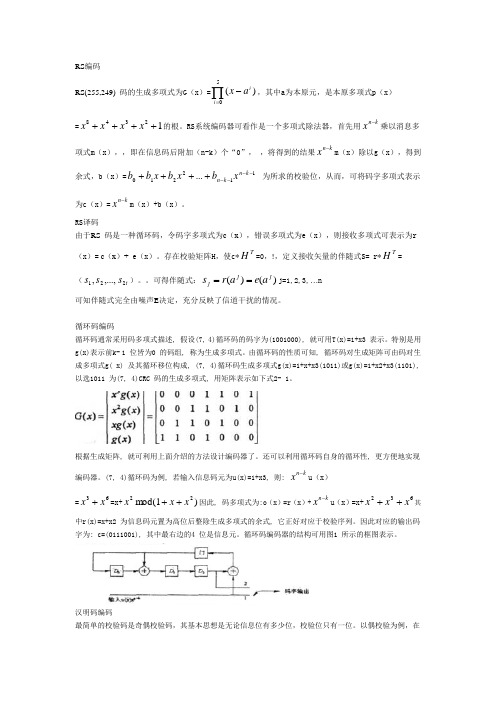

RS 编码RS(255,249) 码的生成多项式为G (x )=∏=-5)(i ia x ,其中a 为本原元,是本原多项式p (x )=12348++++xxxx 的根。

RS 系统编码器可看作是一个多项式除法器,首先用kn x-乘以消息多项式m (x ),,即在信息码后附加(n-k )个“0”, ,将得到的结果kn x -m (x )除以g (x ),得到余式,b (x )=112210...----++++k n k n xb x b x b b 为所求的校验位,从而,可将码字多项式表示为c (x )=kn x -m (x )+b (x )。

RS 译码由于RS 码是一种循环码,令码字多项式为c (x ),错误多项式为e (x ),则接收多项式可表示为r (x )= c (x )+ e (x )。

存在校验矩阵H ,使c*TH=0,!,定义接收矢量的伴随式S= r*TH=(t s s s 221,...,,)。

可得伴随式:)()(jjj a e a r s ==j=1,2,3,…n 可知伴随式完全由噪声E 决定,充分反映了信道干扰的情况。

循环码编码循环码通常采用码多项式描述, 假设(7, 4)循环码的码字为(1001000), 就可用T(x)=1+x3 表示。

特别是用g(x)表示前k- 1 位皆为0 的码组, 称为生成多项式。

由循环码的性质可知, 循环码对生成矩阵可由码对生成多项式g( x) 及其循环移位构成, (7, 4)循环码生成多项式g(x)=1+x+x3(1011)或g(x)=1+x2+x3(1101), 以选1011 为(7, 4)CRC 码的生成多项式, 用矩阵表示如下式2- 1。

根据生成矩阵, 就可利用上面介绍的方法设计编码器了。

还可以利用循环码自身的循环性, 更方便地实现编码器。

(7, 4)循环码为例, 若输入信息码元为u(x)=1+x3, 则: kn x-u (x )=63x x +=x+)1m od(22x x x ++因此, 码多项式为:o (x )=r (x )+kn x -u (x )=x+632x xx++其中r(x)=x+x2 为信息码元置为高位后整除生成多项式的余式, 它正好对应于校验序列。

基于FPGA的RS编码器的设计与实现.

基于FPGA的RS编码器的设计与实现1 RS编码原理RS编码是一种线性的块编码,其表示形式为RS(N,K)。

当编码器接收到一个数据信息序列,该数据信息序列被分割成若干长度为K的信息块,并通过运算将每个数据信息块编码成长度为N的编码数据块。

在RS码中的码元符号不是二进制而是多进制符号,其中2m进制使用更为广泛。

能纠正t个错的RS 码具有,如表1参数所示。

上述参数,t表明最多可以纠正t个随机错误符号。

由于RS码是对多进制符号纠错,RS码可用于纠正突发错误,比如能纠两个八进制符号错误的RS(7,3)码,每个符号可用3 bit二进制符号表示。

八进制的RS(7,3)码相当于二进制的(21,9)码,因此纠两个符号就相当于纠连续6 bit二进制符号的突发错误,然而二进制的(2l,9)码却没有纠6 bit突发错误的能力,它能纠任何2个随机错误以及长度≤4的突发错误。

通用的RS编码的运算步骤:(1)确定RS编码器的生成多项式g(x),这里选用了最为常用的生成多项式,如式(1)所示。

式中a定义为m阶初等多项式p(x)的根它可生成全部GF域的元素。

(有关GF域的内容可参阅相关书籍)。

以RS(15,9)为例,RS(15,9)的生成多项式,如式(2)(2)通过对取模运算产生校验信息多项式p(x)如式(3)式中m(x)表示RS编码码字中的数据信息,它是K一1阶的线性多项式。

(3)通过加法运算生成最终的编码后的多项式c(x)如式(4)RS码的编码主要是围绕码的生成多项式g(x)进行的,一旦生成多项式确定了,则码就完全确定了。

2 RS编码的设计实现在一些特定应用域中,RS码的设计与实现是比较困难的。

RS码是在有限域上进行的代数运算,不同于常用的二进制系统,实现相对复杂一些,其复杂度主要决定于有限域的大小、码字的长度、采用的编码算法等,编码器的实现方式主要有以下几种:(1)微处理器实现的RS编码。

通用的微处理器采用查表(Table—lookup)方法可以实现RS编码,首先需要产生有限域运算中的系数,存于内存中,就可以通过查表的方法实现编码了。

RS编码rs(204,188)设计原理

11.9.2 RS(204, 188)译码器的设计RS码在通信系统、数字电视和计算机存储系统中应用很广泛。

例如,DVB(数字电视)标准中信道编/解码采用RS(204, 188);ATM网络中使用RS(128, 124)作为前向纠错编码(Forward Error Correcting, FEC)。

本节将以DVB标准中定义的RS(204, 188)译码器为例,详细介绍基于改进的BM迭代算法、pipeline结构的译码的所有技术细节。

考虑到译码器的可扩展性、可维护性,实例中尽可能地使用参数化、模块化的设计。

读者可在实例代码基础上作很小的改动,就能实现不同需要的RS译码器。

1. 应用背景在数字通信、数字电视中,信道编码的使用提高了数据传输的质量。

虽然增加了传输带宽,但信道编码减小了数据传输出现误码的概率,同时也减小了所需要的信噪比(signal-to-noise rate)。

在大多数应用中,将RS码与卷积码级联使用进行纠错。

在自信源至接收的过程中,数字电视信号的编码包括信源编码、信道编码及加密。

信道编码又称做前向纠错编码,其目的是提高信息传送或传输的可靠性,当传输差错在一定范围内,接收机都能将误码纠正过来。

必须指出,信道编码并非指信号经上变频发送出去后,在传输信道中(有线、卫星或地面)进行编码,而是指经过编码后便匹配信道传输和减少差错。

因此,自信源编码后的所有编码包括能量随机化扰码、卷积、交织、Reed-Solomon编码等都可划为信道编码。

典型的数字电视信道编码如图11-73所示。

为信息位,t为能纠正误码的最大的码位,且RS外码编码的特点是纠正与本组有关的误码,尤其对纠正突发性的误码最有效。

通常,n、k、t分别为204、188和8。

如图11-74所示为"EN 300 429"有线数字电视(DVB-C)标准规定的发送端(Cable Head-end)框图,其中包括了数据帧结构(Framing structure)、信道编码及调制。

RS系列编译码器的设计与FPGA实现

RS系列编译码器的设计与FPGA实现RS系列编译码器是一种纠错编码器,用于在数字通讯系统中,对比特流进行纠错。

RS编译码器具有强大的纠错能力和低的延迟,因此被广泛应用于数据传输系统。

本文详细介绍了RS编译码器的设计与FPGA实现。

首先,本文介绍了RS编译码器的基本原理。

RS编译码器采用的是非二元域的有限域GF(q)的运算,其中q为素数幂。

RS 编码器基于Berlekamp-Massey算法实现,该算法能够快速求解改正错误多项式的系数,从而实现纠错功能。

RS译码器则基于Forney算法实现,该算法能够快速求出受损位置的错误位的值,从而实现修正错误的功能。

接着,本文详细介绍了RS编译码器的硬件设计。

RS编码器的设计涉及到加法器和乘法器的设计。

由于非二元域的加法和乘法不同于二元域,因此需要在硬件设计中进行特殊处理。

本文提出了一种快速乘法器的设计方法,通过分别实现GF(q)域的高32位和低32位的乘法,从而实现更快的运算速度。

此外,本文还设计了各种状态机、寄存器和时钟管理电路,以实现流水线操作和低延迟的运算。

最后,本文介绍了RS编译码器的FPGA实现。

本文使用Xilinx公司的FPGA器件,通过Verilog HDL语言进行编码,将RS编译码器实现在FPGA芯片上。

通过仿真和验证,本文证明了RS编译码器能够在FPGA芯片上进行快速的纠错和译码操作。

此外,本文还提出了一些可优化的设计,以进一步提高RS编译码器的性能和可靠性。

例如,可以对乘法器的位宽进行优化,选择更快的加法器实现方式等。

综上所述,本文介绍了RS编译码器的设计与FPGA实现。

RS 编译码器是数字通讯系统中常见的纠错编码器,本文所提出的设计和优化方法可以进一步提高RS编译码器的运算速度和可靠性。

RS码译码算法及其实现的研究

RS码译码算法及其实现的研究RS码译码算法及其实现的研究摘要:纠错编码在信息传输中起到了至关重要的作用,其中纠错码是最常用的一种编码方式。

RS码作为一种具有高纠错能力的纠错码,被广泛应用于存储介质、数字通信和数据传输等领域。

本文将详细介绍RS码的编码和译码原理,以及RS 码译码算法的研究进展和实现方法。

一、引言在现代通信系统中,由于信道和介质的不完美性,信息传输过程中常常伴随着噪声和错误,导致数据传输错误率的增加。

为了提高数据传输的可靠性和冗余性,人们引入了纠错码,用于在数据传输过程中对错误进行修正。

二、RS码的原理RS码全称为Reed-Solomon码,是一种基于有限域的纠错码。

RS码利用了有限域GF(q)上的多项式编码理论,通过在数据流中引入冗余位进行编码和译码,从而实现错误的检测和纠正。

1. 编码原理RS码的编码原理是将信息数据流进行多项式编码,然后再添加纠错码,生成一个较长的编码后数据流进行传输。

具体编码流程如下:(1)将n个信息符号划分为m个长度为t的子串,其中m = n / t,t为RS码的最小距离;(2)将每个子串看作一个特定的数字,代入t-1次幂相乘的多项式中;(3)将每个子串多项式求模,得到t-1阶多项式;(4)在多项式后方添加r个纠错码位,使整个编码构成一个长度为t+r的新多项式;(5)重复以上步骤,直到对所有信息子串进行编码处理。

2. 译码原理RS码的译码原理是利用多项式除法实现。

译码时,首先接收到一个由编码器生成的编码后数据流,然后通过解码器进行解码,恢复原始信息数据流。

具体译码流程如下:(1)通过接收到的数据流计算相应的符号多项式;(2)使用Berlekamp-Massey算法,计算出多项式的最小生成多项式,从而确定修正多项式;(3)对错误位置进行定位,然后使用Forney算法计算纠错多项式;(4)使用译码器获得纠正后的数据流。

三、RS码的译码算法研究进展1. 经典的译码算法目前,根据实际应用需求,已经提出了许多RS码译码算法。

基于FPGA的RS422总线故障注入系统

图2 :功 能板 硬 件 框 图

按照配置参 数选择故障用例库 、 时钟 、串口速度等

上升沿数据输 出,下降沿采样数据的接 口,故

障注入设备能够通过高频信号,在邻近时 钟下 降沿时将数据输出,反之对于上升沿采 样数据 的接 口,也能够在邻近时钟上升沿时将 数据输

电子技术 ・ E l e c t r o n i c T e c h n o l o g y

战障 注 入设 各

接收 故 障 注 入 前端 的 配 霞参 数

根 据 配 置参 数 配 置F P G A ̄寄 存 器

…

…

…

一

- r ………

汁 算故 障 参 数 ,并 且发送 故障 参 数至 F P G A

出。

1 . 2同步/ 异步R s 4 2 2 数据通信接 口故障注入

1 . 2 . 1 R S 4 2 2数 据 转 发 包 括 端 到 端 通 信 ;b ) 可对每 一 比特 数据

根据 故障参数修改数据

对 于 秒 脉 冲 信 号 的 向 后 延 时 输 出 , 故 障

输入设备对接收到的秒脉冲信号,向后随即延 时一段时间后输出,对于向前提前输出,故障 输入设备对接收到的秒脉冲信号,首先直接输 出秒脉冲信号 ,之后延时一段时间后输出;对 于更改秒脉冲信号低脉冲信号的宽度,故障输 入设备随机增加或者减小秒脉冲信号低 电平的 持续时间实现故障的注入;对于秒脉冲 信号的 输出停止,故障输入设备直接将 秒脉冲输出端 口的信号输出停止,此时输出端 口的电平信号 可以随机为高 电平或者低 电平信号,对于正常 情况 下,输 出的秒脉 冲R S 4 2 2 接 口故障注入

基于FPGA的参数可调RS422接口电路设计实现

WA NG J u n c h a o, W AN G He n g l i a n g

( Mi n i s t r y o f E d u c a t i o n K e y L a b o r a t o r y o f E l e c t r o n i c I n f o r ma t i o n C o u n t e me r a s u r e a n d S i mu l a t i o n ,

接 口 电路 设 计 。 该 设 计 以 A h e r a的 C y c l o n e 系列 芯 片 E P 3 C 8 0 F ' 7 8 0 1 7作 为 控 制 芯 片 , 以 A D I的 A D M 2 6 8 7 E B R I Z 作 为

基于FPGA的高速RS编解码器设计与实现

De i n a m p e e t to ff s n o e sg nd i l m n a i n o a t RS e c d r

a d d c d r b sd o n e o e a e n FPGA

GU h l. Z Ya —i H0U n . n Ho g mi

储 系统 中。

R (5 ,9 )编解 码器 采用 一 些有 效 的方 法 实 现 , S 25 1 1

在面积允 许 的情 况 下 , 好 地 提 高 了编 解 码 速 度 。 更 文中首先 研究 G (s 有 限域 的乘 法 器 和 求 逆器 的 F 2)

逻辑 电路 实 现 , 分 别讨 论 R 再 s编码 器 和 解 码器 的 设 计实 现 。

o c p n y・ cu ac

Ke od :Dg a Vdo Bodat g( V ) S e cd g ad dcdn ;Fe rg m al G t y w rs it i rac i il e s n D B ;R noi eo i n n g id Por m be ae l a

raie b i ee twa s a c r i g t er dfee t c aa tr t s h n o e s d sg e sn aall e lzd y d f r n y c od n o t i i r n h rce si 、T e e c r i e i d u i g p r l h i c d n e s cu e he d c e s d sg e u ig p r l li v rine s BM l rtm mp e n t e d ue,  ̄ tr ,t e o r i e i d sn a al —n eso s d n e l a g i h t i lme t i k y mo l a o o s lo — p tbl to sa o td o i lme ti v rin.Usn o ia o fte a o e me o st ep p r o k u a emeh d i d p e t mpe n n eso i ga c mbn t n o b v td a e i h h h

基于FPGA的RS(255,239)译码器的设计与实现

基于FPGA的RS(255,239)译码器的设计与实现胡雪川;刘会杰【摘要】In order to solve the problem such as the complexity of RS decoding process,low decoding speed , expensive specific RS decoder and so on that exists when the RS code is decoded, the RS (255,239) code is taken as an example, and the RS decoding theory based on the improved non-inversion Berlekamp-Massey (BM) iterative algorithm is introduced. On the FPGA platform, each submodule of the decoder has been designed and simulated by using the Verilog hardware description language and the software of Xilinx ISE 13.4. Pipeline approach is used in the entire decoder design process. Timing simulation results show that if there exists no more than eight errors, after 295 inherent delay, the decoder can output the corrected code word continuously in each clock cycle, and the ability of error correcting of RS decoder meets the expectations.%为了解决在RS译码中存在的译码过程复杂、译码速度慢和专用译码器价格高等问题,以RS(255,239)码为例,采用了基于改进的无求逆运算的 Berlekamp-Massey(BM)迭代算法。

FPGA RS锁存器报告

一、实验原理在数字系统中,为了协调各部分的工作状态,常常要求某些锁存器在同一时刻动作,这样输出状态受输入信号直接控制的基本锁存器就不适用了。

为此,必须引入同步信号,使这些锁存器只有在同步信号到达时才按输入信号改变状态。

由同步信号控制的锁存器称为同步锁存器或钟控锁存器,同步信号也叫做时钟信号,用CP表示。

常见的钟控锁存器有钟控RS锁存器和锁控D锁存器等。

二、实验目的(1)熟悉ISE9.1的开发环境,掌握工程的生成方法。

(2)熟悉XUPV2Pro实验环境。

(3)了解Verilog HDL语言在FPGA中的使用。

(4)通过锁存器的设计实验了解数字电路设计。

三、实验内容(1)用Verilog语言设计锁存器。

(2)RS锁存器二的实现,D锁存器的实现。

(3)使用ChipScope-Pro生成ILA/ICON核,在线观测调试。

四、(RS锁存器)实验步骤(1)在D:\Xinlinx91i\目录下,新建名为rsuocun的新工程。

器件族类型(Device Family)选择”Virtex2P”器件型号(Device)选“XC2VP30 ff896-7”综合工具(Synthesis Tool)选“XST(VHDL/Verilog)”仿真器(Simulator)选“ISE Simulator”(2)设计输入:输入上面所提到的代码,保存后如图1.1所示。

(3)功能仿真a)在sources窗口“sources for”中选择“Behavioral Simulation”。

b)用“Test Bench WaveForm”添加激励源,如图1.2所示。

仿真波形分析如下:开始在0到100ns内的是R,S均为0,则不能确定状态,这是RS锁存器的不允许状态。

Q1,Q2是两个互为相反的变量,其波形可以观察到。

观察波形可知,当R为1,S为0时,输出的Q1为0,Q2为1,实现置0功能;当R为0,S为1时,输出的Q1为1,验证了电路的置1功能;当R,S均为1的时候,电路输出保持原状态不变。

东南大学2011年基于教师科研的SRTP验收结果公示

东南大学教务处

校机教〔2012〕143号

关于公布“东南大学2011年基于教师科研的SRTP项目”结

题验收结果的通知

各院(系)、项目指导老师、项目负责人:

东南大学2011年基于教师科研的SRTP项目已于2012年10月20日完成结题验收工作。

立项的123项目中,有119个项目参加本次结题验收,根据专家的现场评审和综合评定,最终评定结果为优秀25项、良好44项、通过38项、不通过1项、整改后验收11项。

另外有4项没有参加本次验收。

项目验收结果见附件。

对于本次验收结果为整改后验收的项目,学校将于该通知发布之日起2个月内组织最后一次验收。

对于无故没有参加本次答辩的项目,请所在院(系)终止使用项目剩余经费,其额度将计入下一年度学院“基于教师科研的SRTP项目”经费中,并且减少所在院系下一年度立项项目数。

附件:东南大学2011年基于教师科研的SRTP项目结题验收结果一览表

二〇一二年十一月十三日

主题词:基于教师 SRTP 结题验收结果通知

抄送:学生处科技处团委档案馆

东南大学教务处 2012年11月13日印发。

哈尔滨工业大学工学硕士学位论文非...

工学硕士学位论文基于UWB通信系统信道编解码的FPGA实现柯海英哈尔滨工业大学2008年12月国内图书分类号:TN911.22国际图书分类号:621.39工学硕士学位论文基于UWB通信系统信道编解码的FPGA实现硕士研究生:柯海英导师:许洪光副教授申请学位:工学硕士学科、专业:通信与信息工程所在单位:深圳研究生院答辩日期:2008年12月授予学位单位:哈尔滨工业大学Classified Index: TM151.3U.D.C: 621.3Dissertation for the Master Degree of Engineering IMPLEMENTATION OF FPGAFOR CHANNEL CODINGBASED ON UWB SYSTEM Candidate: KeHaiying Supervisor:Asso.Prof. Xu Hongguang Academic Degree Applied for:Master of EngineeringSpecialty:Communication and Information systemAffiliation:Shenzhen Graduate School Date of Defence:December, 2008Degree-Conferring-Institution:Harbin Institute of Technology哈尔滨工业大学工学硕士学位论文摘要由于通信信道固有的噪声和衰落特性,加上存储媒介的缺陷等原因,以及新的通信业务和信息业务的不断涌现,用户对信息传输的质量要求和速率要求不断提高。

信道编码提高了信息传输的可靠性,但是常用的信道编码理论对于UWB系统还未有充分的探讨。

本课题研究的目的在于通过信道纠错码中的级联码仿真试验,为UWB 信道纠错码提供试验和实践依据,为考察UWB通信系统的信道编码纠错能力提供参考依据。

RS码在无线高保真音频传输系统中的应用

RS码在无线高保真音频传输系统中的应用刘杰;董金明【摘要】在现代社会中,随着无线技术的发展,越来越多的无线设备占据着家庭中的每一个角落.然而无线传输存在着传输带宽以及误码率等因素的限制.在无线音频传输中,想要获得高保真的效果,就必须在带宽以及误码率方面加以着重考虑.讨论了在无线传输误码率问题上RS码所带来的纠错能力以及其实现方法,并且给出了一种可行的低成本的无线音频传输系统的解决方案.【期刊名称】《现代电子技术》【年(卷),期】2007(030)015【总页数】3页(P19-21)【关键词】RS码;无线传输;高保真;音频缡码;纠错【作者】刘杰;董金明【作者单位】北京航空航天大学,电子信息工程学院,北京,100083;北京航空航天大学,电子信息工程学院,北京,100083【正文语种】中文【中图分类】TN919.72;TNG19.3在现代社会中,越来越多的无线设备占据着家庭的每一个角落,无线连接比有线连接带给了消费者更大的使用空间以及更灵活的使用方法。

随着无线技术的发展,音频传输也开始走向无线。

设计人员在进行无线音频电路设计时,有一个重要因素必须优先考虑:优良的音质。

在无线音频传输中,想要获得高保真的效果,就必须在带宽以及误码率方面加以着重考虑。

本文讨论了RS码在无线传输上的纠错性能及其实现方法,并且给出了一种可行的低成本的无线高保真音频传输系统的解决方案。

1 高保真音质的标准高保真音频音质的基准通常以CD的音质来衡量。

CD数字音频要求每个音频信号通道具有44.1 kHz的采样频率和16 b的分辨率,双声道产生的数据流为1.41Mb/s。

蓝牙是目前市场上应用最多的音频传输的解决方案,可是他的带宽不够充足。

蓝牙1.2的数据传输率标称值为1 Mb/s,而其实际传输率为720 kb/s左右,这样的数据传输率只能满足于传输语音或经压缩处理所产生的音频流,并且蓝牙设备一般较为昂贵。

对比蓝牙,本文所讨论的方案成本较为低廉,并且满足44.1 kHz的采样频率和16 b分辨率的CD音质标准。

CMMB标准中RS编码的FPGA实现

CMMB标准中RS编码的FPGA实现

栗芬环

【期刊名称】《电视技术》

【年(卷),期】2010(034)012

【摘要】简要介绍了移动电视传输标准CMMB中RS(里德-索罗门)编码的特点.采用Matlab进行算法验证,并用FPGA实现.字节交织使用乒乓流水线结构,缩短了等待时间.针对k=176设计出节约成本的编码器.提出利用VGA接口获取FPGA验证数据源,使用"编码-解码-重现"的模式对RS编码器充分验证.

【总页数】3页(P52-53,68)

【作者】栗芬环

【作者单位】华南理工大学,电子与信息学院,广东,广州,510640

【正文语种】中文

【中图分类】TN919.81

【相关文献】

1.用FPGA实现数字电缆电视系统中的RS编码器 [J], 陈磊;夏天;龚建荣

2.ITU-T J.83B系统中RS编码器的设计与FPGA实现 [J], 张燕

3.L-DACS1中高速多模式RS编码的FPGA实现 [J], 刘海涛;杨志强;李重仪

4.CMMB 系统中 RS 编码器的设计与实现 [J], 杨俊逸

5.CMMB系统中RS编码器的实现 [J], 谭泽富; 谢红

因版权原因,仅展示原文概要,查看原文内容请购买。

基于通信系统编解码芯片的逻辑综合研究

基于通信系统编解码芯片的逻辑综合研究舒钰【摘要】未来大批量、小型化、低功耗设备对专用处理芯片的需求迫切,本文针对通信系统编解码芯片复杂的时钟、复位、IO设计,分别采用多生成时钟、内部复位、虚拟时钟的设置,有效的实现芯片时序的收敛,达到了较好的综合结果.【期刊名称】《现代导航》【年(卷),期】2017(008)001【总页数】5页(P33-37)【关键词】逻辑综合;时序约束;生成时钟【作者】舒钰【作者单位】中国电子科技集团公司第二十研究所,西安 710068【正文语种】中文【中图分类】TP311通信系统可为应用平台提供抗干扰、保密的数据通信和数字语音, 实时或近实时的传输各种传感器信息, 提高应用平台的协调能力和使用效能, 这就要求通信信息的传输、处理、分发要做到安全、及时和有效。

但在通信过程中常会遇到突发性的故意干扰而导致信息错误,因此高效、高性能的纠错编码技术成为实际工程应用中最关键和最热点的问题。

RS码既能纠随机错误,又能纠突发错误,而且纠错码随着分组大小的增加而纠错性能更加有效, 其实现的复杂度要低于相同长度的其他编码方法,己经在通信系统得到了广泛的应用[1]。

本文针对通信系统RS编解码部分自主开发了一款专用ASIC芯片,由于原代码中RAM、ROM、FIFO等IP调用的是FPGA内部的IP核,这些IP核均不可直接移植,在芯片化实现过程中,对以上IP进行了自主开发。

针对规模较大的存储器,采用标准的存储器IP,并按照原FPGA存储器接口的时序定义,添加外围控制电路,保证端口时序和功能的一致性;针对小容量的RAM/ROM,采用基于寄存器阵列的存储方案,地址读写采用查找表的访问形式实现;另外本项目中移位寄存器存在数目多,种类多,位宽小的特点,采用基于存储器的方案不具有灵活性,故采用基于寄存器阵列的流水线结构实现。

本文主要使用Synopsys 公司的Design Compiler 完成逻辑综合,同时探索了专用ASIC芯片综合的设计流程和方法,特别是根据芯片自身特点,在逻辑综合流程中制定了有效的时序收敛策略,最终使芯片满足了设计的时序要求。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

该文对软件实现RS码纠错纠删译码进行讨论,并涉及建立有限域的对数表和反对数表、RS码的生成多项式产生的RS码编码等有关问题。

8.学位论文丁丹萍微小卫星通信中基于FPGA的RS码编译码器的设计与实现2006

研制发射微小卫星,是我国利用空间技术服务经济建设、造福人类的重要途径。现代微小卫星在短短20年里能取得长足的发展,主要取决于微小卫星自身的一系列特点:重量轻,体积小,成本低,性能高,安全可靠,发射方便、快捷灵活等。在卫星通信系统中,由于传输信道的多径和各种噪声的影响,信号在接收端会引起差错,通过信道编码环节,可对这些不可避免的差错进行检测和纠正。

2.分析了天线相关(即相关瑞利衰落信道)对空时分组码的影响,提出了级联RS码的空时分组码模型,仿真表明,级联RS码能够有效的提高系统性能,大大的降低了系统误码率。

3.在熟悉正交频分复用基本原理的基础上,提出了基于RS码的OFDM系统,利用Simulink对系统进行仿真,仿真数据表明在RS码信道编码在大信噪比时误码率大大降低。

虽然RS编译码的算法已经比较成熟,但是由于RS码种类较多,具体应用不同,所以很难有适应各种系统的硬件实现。本文的主要目的就是开发基于IEEE802.16d 系统的RS编译码器的硬件实现,以求达到系统最好的性价比。

通过对标准中RS码特点的分析,对传统的RS译码器进行改进,提出了一种适用于该标准的RS译码方法。利用循环码的性质,改进伴随式计算模块,减少延迟时间;利用16d系统中RS码中已知删除位置的特点,简化删除位置多项式计算电路;通过对RS码实际应用环境的分析,减少利用迭代方法解关键方程时所需的基本单元数目。最终利用Verilog语言实现硬件电路,在FPGA上验证通过并应用于WiMAX 802.16d系统。

2009,38(3)

针对信道编码的盲识别问题,首次提出了RS码的盲识别方法.先针对无误码的情况,通过基于矩阵行向量化简(RREF)的方法估计RS码的码长、本原多项式和生成多项式等参数;继而,针对有误码的情况,通过基于RREF、容错矩阵分解(FTMD)和伽罗华域的傅里叶变换(GFFT)方法估计码长、本原多项式和生成多项式等参数,这是一个全新的研究课题,在智能通信、信息截获、密码分析等领域有重要的应用.仿真实验表明文中提出的方法在误码率为10-3的情况下,对于RS码的识别概率高于85%.

5.学位论文吴瑕RS码的研究与应用2001

该文主要是从工程应用的角度,讨论了RS码的几种编译码算法,并且着重论述了RS码的两个应用和如何用FPGA设计编译码器.该文主要的研究结果如下:1.介绍了信道编码的发展、应用,讨论了两种编码器的实现,并且论述了一种如何降低编码器复杂度的方法.2.详细研究了RS码的编译码原理,论述了几种经典的RS码的代数译码算法,并且比较了它们的实现复杂度.3.详细研究了无线ATM交换机的信道特性,提出了对ATM信元进行保护的RS码编码方案,并且论证了该方案的可行性.设计了ATM交换机中编译码器模块.4.详细研究了DVB系统中MPEG-2所选用的纠错码方案;并且结合实际项目,提出了适用于DVB上行信道的可行的纠错编码方案,设计出了MPEG-2流中的译码器模块.5.根据Euclid迭代译码算法,用FPGA设计实现了RS编译码器.

RS码的提出已有40余年的历史。经过几十年的发展,其理论基础已经比较完善。RS码有其特殊的代数结构,是一种建立在有限域基础上的多进制循环码,在编码和译码方面都有优势。可以利用一般的循环码编码器进行编码,结构非常简单。而且,其生成多项式结构比较特殊,即多项式的根是有限域上本原多项式根的连续次幂。根据这种结构,可以推导出相对于普通循环码而言较简单的译码方法。另外,还可以用迭代的算法来实现RS译码,非常适合VLSI实现。常用的迭代译码算法有伯利坎普-梅西算法(Berlekamp-massey),欧几里德(Euclid)算法等。

在微小卫星通信链路中,信道编码器的任务是差错控制。本文采用符合空间数据系统咨询委员会CCSDS标准的链接码进行信道编码,即内码为

(2,1,6)的卷积码,外码为(255,223)的RS码,中间进行交织操作。其中,里德-索罗蒙码(简称RS码)是一种重要的非二进制BCH码,是分组码中纠错能力最强的纠错码,一次可以纠正多个突发错误,广泛地用于空间通信中。

本文针对南京航空航天大学自行研制的微小卫星通信分系统的技术要求,在用SystemView和C语言仿真的基础上,用硬件描述语言Verilog设计了RS(255,223)编码器和译码器,使用Modelsim软件进行了功能仿真,并通过Xilinx公司的软件ISE对设计进行综合、布局布线,最后生成可下载的比特流文件下载到Xilinx公司的型号为XC3S2000的FPGA芯片中,完成了电路的设计并实现了编码译码的功能,表明本文设计的信道编解码器的正确性和实用性,满足了微小卫星通信分系统的技术要求。

4.以设计可复用的IP核为目的,用VerilogHDL硬件描述语言描述,以模块化设计方法设计一个RS编解码器,最后通过AlteraQuartusⅡ分析综合仿真,实现硬件电路。

3.期刊论文刘健.谢锘.周希元.LIU Jian.XIE Nuo.ZHOU Xi-yuan RS码的盲识别方法-电子科技大学学报

学位授予单位:东南大学

1.学位论文许拔深空通信中RS码的编译码算法研究2004

本文主要对应用于深空信道编码的RS码进行了研究。首先从信道编码的基本定理入手论述了在有干扰存在的信道上进行无差错传输的可能性,这是纠错编码研究的理论依据与努力方向。然后介绍了与纠错编码相关的代数基本知识,简单介绍几种常见的纠错编码码型,重点研究了RS码的时域编译码算法,并对具体参数的RS码的编译码实现过程进行了分析,在建立恰当的信道模型的基础上对RS码性能进行仿真分析,进一步提出了RS码频域编译码方法;在文章第三部分中对卷积码与Turbo码做了简单地介绍,文章最后简单论述了深空通信的信道特点,对国外现有的编译码系统进行了介绍与比较,并在此基础上针对我国具体国情与现实需要提出了这个课题即将采用的方案。

9.学位论文王卿RS码在卫星通信中的应用2003

该文分析了卷积码、RS码及其级联码的纠错原理与性能;针对"卫星数据采集系统"的特点提出了一种适用于该系统的级联码信道编码方案,并对该编码方案进行了仿真;然后用可编程逻辑器件实现了该方案中的RS码编解码器.RS译码器采用改进了的BM—Chien—Forney译码算法.实验结果表明,该信道编码方案具有良好的纠错性能,可以满足系统要求.

2.学位论文王虹级联RS码系统在瑞利衰落信道下的性能仿真及RS码的IP核设计2006

本文探讨了级联RS码系统在瑞利衰落信道下的性能,基于RS码的空时分组码系统,以及基于RS码的正交频分复用系统,并设计了RS编译码器IP核

,通过仿真验证了设计的正确性,主要完成的工作有以下几个方面:

1.给出了瑞利衰落信道的仿真模型,对RS码的性能指标进行了详细的分析。

6.学位论文罗开杰RS码编译码及其快速实现2001

在数字通信系统中可靠和快速往往是一对矛盾.若要快速,则必然使得每一个码元所占的时间缩短、波形变窄、能量减少,从而在受到干扰后产生错误的可能性增加,传送消息的速率变慢.如何较合理地解决可靠性和速度这一对矛盾,是正确设计一个通信系统的关键问题之一.该文详细介绍了信道编码中使用较多的循环码,BCH码和RS码的基本概念,同时对RS码的编译码算法进行了计算模拟仿真.把著名的RS码迭代译码算法进行了一定的修改,使其具有很多重复和递归结构,然后用基于VHDL的CPLC/FPGA技术流水线型实现.结果表明这个通过流水线型处理的系统在获取高的译码速度方面有很大的优势,并且它能同时纠通信信道中的随便机错和突发错.这样就较好地解决了这个问题.该文同时给出了可编程逻辑器件一般使用流程.文章的最后对当今最为热门的两种码卷积码和TURBO码也作一些介绍.

东南大学

硕士学位论文

RS编解码的FPGA实现

姓名:俞旋

申请学位级别:硕士

专业:软件工程(IC)指导教师:李智群;刘慎功

20080901

RS编解码的FPGA实现

作者:俞旋

4.学位论文高庆峰IEEE 802.16d系统中RS编译码器的设计与实现2008

IEEE 802.16d标准是WSolomon(RS)码是IEEE 802.16d 标准中信道编码的重要组成部分。信道编码经过几十年的发展,已经成为一门比较成熟的技术,在现代通信系统中有重要的应用。RS码是一种重要的信道编码,具有很强的纠错能力,尤其对于突发信道,其纠错能力可以充分的发挥。RS码是一种线性分组码,在应用中还可以与卷积码组成级联码,以提高系统的整体性能。在级联码中,卷积码通常作为内码,来纠正随机错误;RS码通常作为外码,来纠正突发错误。在IEEE 802.16d 系统中,RS码便是作为级联码的形式出现的。

10.会议论文曹沛先RS码的编译码的计算机模拟2002

对差错控制中的RS码的编码及其用Massey-Berlekamp算法(迭代算法)译码进行了模拟,然后,根据计算机模拟数字声音广播移动接收信道所产生的差错序列,并把RS码进行了符号交错,模拟了几组参数变化对性能改善的影响.

本文链接:/Thesis_Y1424494.aspx

授权使用:浙江工业大学图书馆(wfzjgydx),授权号:2bf9998c-a032-4e97-a6b1-9e690149b067

下载时间:2011年1月12日