数字逻辑Chapter 6

数字逻辑第六章课件

2. 应用举例

A3 =0时,片Ⅰ工作,片Ⅱ禁止

(1)功能扩展(利用使能端实现)

仿真 扩展位 控制 图3-9 用两片74LS138译码器构成4线—16线译码器 A3 =1时,片Ⅰ禁止,片Ⅱ工作 使能端

(2) 实现组合逻辑函数F(A,B,C)

F ( A, B, C ) mi (i 0 ~ 7)

Ai 0 0 0 0 1 1 1 1 Bi 0 0 1 1 0 0 1 1 Ci-1 0 1 0 1 0 1 0 1 Si 0 1 1 0 1 0 0 1 Ci 0 0 0 1 0 1 1 1

Si Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 Ai Bi Ci 1 Ai ( Bi Ci 1 Bi Ci 1 ) Ai ( Bi Ci 1 Bi Ci 1 ) Ai ( Bi Ci 1 ) Ai ( Bi Ci 1 ) Ai Bi Ci 1

试将8421BCD码转换成余3BCD码 (1)真值表 (2)卡诺图

0 1 2 3 4 5 6 7 8 9 10 8421码 余3码 B3 B2 B1 B0 E3 E2 E 1 E0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 0 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 0 0 1 1 1 0 1 0 1 1 0 0 0 0 1 1 0 1 0 0 1 0 1 1 1 1 0 1 0 1 0 0 0 1 0 1 1 1 0 0 1 1 1 0 0 1 0 1 0

Yi S mi mi ( S 1, i 0,1,2,7)

比较以上两式可知,把3线—8线译码器 74LS138地址输入端(A2A1A0)作为逻辑函数的输 入变量(ABC),译码器的每个输出端Yi都与某一 个最小项mi相对应,加上适当的门电路,就可以利 用译码器实现组合逻辑函数。

数字逻辑第六版习题答案2

W= AB+ACD X = BC+BD+BCD Y = CD+CD Z=D

A 0 0 0 0 0 1 1 1 1 1

B 0 1 1 1 1 0 0 0 0 1

C 1 0 0 1 1 0 0 1 1 0

D 1 0 1 0 1 0 1 0 1 0

W 0 0 0 0 0 0 0 0 1 1

X 0 0 0 0 1 1 1 1 0 0

Y 0 0 1 1 0 0 1 1 0 0

Z 0 1 0 1 0 1 0 1 0 1

这是一个余三码 至 8421 BCD 码转换的电路

7. 下图是一个受 M 控制的 4 位二进制码和格雷码的相互转换电路。M=1 时,完 成自然二进制码至格雷码转换;M=0 时,完成相反转换。请说明之

解:Y3=X3

Y2 X2 X3

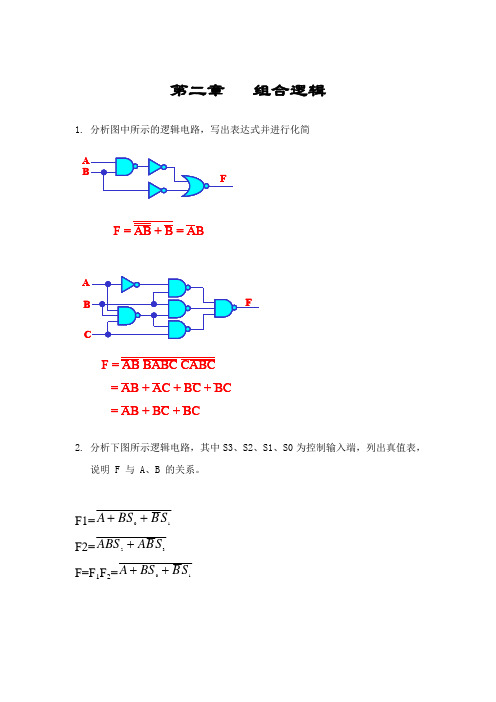

F=F1F2 F1 F1 F1 F1

S3 S2 S1 S0 × × × × × × × × 0 0 1 1 0 1 0 1

F=F1F2 A AB AB 0

3. 分析下图所示逻辑电路,列出真值表,说明其逻辑功能。

解: F1= AB C 真值表如下:

ABC A BC B C = A B C A BC ABC

Y2 0 0 0 1 0 1 1 1

Y3 1 0 0 0 0 0 0 0

Y1 A B C Y 2 BC A( B C )

于是得: Y 3 A B C A B C

10. 用两片双四选一数据选择器和与非门实现循环码至 8421BCD 码转换。

解:(1)函数真值表、卡诺图如下;

十进制数 0 1 2 3 4 5 6 7 8 9 8421码 0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 余三码 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100

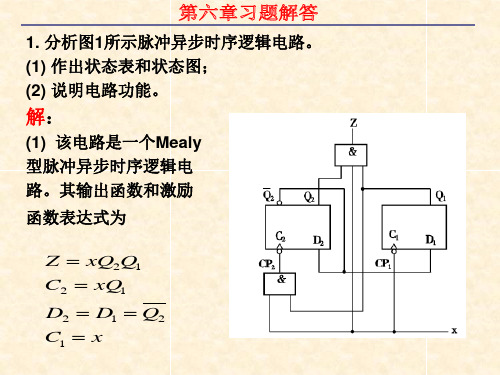

数字逻辑 第六章习题答案

根据真值表画出激励函数和输出函数卡诺图(略),化简后可 得:

(5) 画出逻辑电路图 根据激励函数和输出函数表达式,可画出实现给定功能的逻 辑电路如图11所示。该电路存在无效状态10,但不会产生挂 起现象,即具有自启动功能。

7 试用与非门构成的基本R-S触发器设计一个 脉冲异步模4加1计数器。 解(1) 设电路输入脉冲为x,状态变量为 y1y0,其状态表如表9所示。

(2)该电路的状态图、状态表

(3)该电路是一个“x1—x2—x3”序列检测器。

4 分析图7所示脉冲异步时序电路,作出时间 图并说明该电路逻辑功能。

解:(1) 该电路是一个 Moore型脉冲异步时序逻辑 电路,其输出即电路状态。激 励函数表达式为

(2)电路次态真值表

(3)时间图

(4)该电路是一个模4计数器。

(4) 确定激励函数和输出函数 确定激励函数和输出函数时注意: ● 对于多余状态y2y1=10和不允许输入x2x1=11,可作为无关条 件处理; ● 当输入x2x1=00时,电路状态保持不变; ● 由于触发器时钟信号作为激励函数处理,所以,可假定次态 与现态相同时,触发器时钟信号为0,T端为d。 据此,可列出激励函数和输出函数真值表如表8所示。

(2) 根据状态表和RS触发器的功能表,可列出激 励函数真值表如表10所示。

Байду номын сангаас

(3)化简后,可得激 励函数最简表达式为:

(4)根据激励函数表达式,可画出逻辑电路 图如图12所示。

5 用D触发器作为存储元件,设计一个脉冲异 步时序电路。该电路在输入端x的脉冲作用 下,实现3位二进制减1计数的功能,当电 路状态为“000”时,在输入脉冲作用下输 出端Z产生一个借位脉冲,平时Z输出0。

数字逻辑第6章

(4)画出时间图并说明电路功能 假定输入端x1、x2、x3出现脉冲的顺序依次为x1 - x2 - x1 x3 - x1 - x2 - x3 - x1 - x3 - x2,根据状态表或状态图可作出时间 图图6.7所示。

图中,假定电路状态转换发生在输入脉冲作用结束时,因此, 转换时刻与脉冲后沿对齐。 由状态图和时间图可知,该电路当3个输入端按x1、x2、x3 的顺序依次出现脉冲时,产生一个“1”输出信号,其他情况 下输出为“0”。因此,该电路是一个“x1—x2—x3”序列检测

脉冲异步时序逻辑电路的分析

一、分析方法与步骤

1.分析方法 脉冲异步时序逻辑电路的分析方法与同步时序逻辑电路大致相同。 分 析过程中同样采用状态表、状态图、时间图等作为工具。

注意两点:

(1)当存储元件采用时钟控制触发器时,对触发器的时钟控制端应作 为激励函数处理。 分析时应特别注意触发器时钟端何时有脉冲作用,仅当时钟端有脉冲作 用时,才根据触发器的输入确定状态转移方向,否则,触发器状态不变。 (2)由于不允许两个或两个以上输入端同时出现脉冲,加之输入端无 脉冲出现时,电路状态不会发生变化。因此,分析时可以排除这些情况, 从而使分析过程和使用的图、表得以简化。

脉冲异步时序逻辑电路的设计

(3)状态编码 由于最简状态表中有4个状态,故需用两位二进制代码 表示。设状态变量用y2、y1表示,根据相邻编码法的原则, 可采用表6.12所示编码方案。并由表6.11、表6.12得到二进 制状态表如表6.13所示

脉冲异步时序逻辑电路的设计

(4)确定输出函数和激励函数 假定次态与现态相同时,令时钟端取值为0,D端取值 随意;次态与现态不同时,令D端取值与次态相同,时钟 端取值为1(有脉冲出现)。

数字逻辑第六章

LDB ( Q2 Q1 ) T2

ADD Q2Q1 (电平信号控制)

CLR Q2 Q1 (电平信号控制)

1

2

P172 例6 举例

T 1 T1 T2

T1

2

3

4

5

6

7

8

T2

CLR

LDA LDB ADD

P172 例6 举例

例2

已知ASM图如下,用PLA阵列和一定数量的D触发器实现。

3个状态-----需要2个触发器

S0 S1 S2 S3

函数发生器

4

Ai i = 0,1,2,3

4

Bi

子系统ALU

74LS181功能表

演示_74LS181功能

74LS181

● 二、寄存器堆

寄存器

通用寄存器: 暂存参与ALU运算的数据和结果。4、8、16、32位

专用寄存器: 状态寄存器、指令寄存器、程序计数器

ALU A E A0~3 B E B0~3 双端口寄存器组

数字系统

要求

最上层系 统设计

划分

若干子系统

划分

若干功能块

From top to down 自上而下

设计控制器 简单的模块

时序机

数字系统的设计方法

概念设计 系统验证 系统设计和描述

系统划分 设计者

功能验证

子系统功能描述

综合 电子系统设计自动化 EDA Electronic Design Automation 芯片 数字系统的设计流程

0

1

X

S2

S3

1 0 P169 例4演示 ASM图举例

1

X

Z=1

例3 同步时序状态机如图所示,其中X1、X2是两个外部输入信号,Z是 输出信号。将时序状态机转换为ASM图。

数字逻辑第四版白中英第六章

第六章数字系统6.1 数字系统的基本概念6.2 数据通路6.3 由顶向下的设计方法6.4 小型控制器的设计6.5 微程序控制器的设计6.6 数字系统设计实例返回目录6.1 数字系统的基本概念6.1.1 一个数字系统实例6.1.2 数字系统的基本模型6.1.3 数字系统与逻辑功能部件的区别6.1.1 一个数字系统实例数字系统是由许多基本的逻辑功能部件有机连接起来完成某种任务的数字电子系统,其规模有大有小,复杂性有简有繁。

图6.1表示生产线上药片计数和装瓶控制显示系统的组成框图,它是一个典型的数字系统应用模型。

图6.1 药片装瓶计数显示系统框图6.1.2 数字系统的基本模型图6.2数字系统基本模型6.1.3 数字系统与逻辑功能部件的区别6.2 数据通路6.2.1 总线结构6.2.2 数据通路实例6.2.1 总线结构1.总线的概念图6.3 总线原理示意图2.总线的逻辑结构图6.4多路选择器构成的数据总线图6.5(a)三态门构成的数据总线图6.5(b)三态门构成的数据总线6.2.2 数据通路实例图6.6数据通路6.3 由顶向下的设计方法6.3.1 数字系统的设计任务6.3.2 算法状态机和算法流程图6.3.1 数字系统的设计任务•数字系统的设计任务主要包括下列几部分:(1)对设计任务进行分析,根据课题任务,把所要设计的系统合理地划分成若干子系统,使其分别完成较小的任务。

(2)设计系统控制器,以控制和协调各子系统的工作。

(3)对各子系统功能部件进行逻辑设计。

•【例2】设计一个简单的8位二进制无符号数并行加法运算器,使之能完成两数相加并存放累加和的要求。

图6.7 累加运算器基本框图6.3.2 算法状态机和算法流程图图6.8 状态及其时间关系•(2)分支框。

•(3)条件输出框。

•(4)状态单元。

图6.9 算法流程图的基本图形•【例3】将图6.10(a )所示的米里机状态图转换成ASM 流程图。

•【例4】将图6.11(a )所示的四状态机转换成ASM 流程图。

第6章 格与布尔代数

借助于子代数给子格下的定义: Def 设(L, +, ∙)是格, M L, 若(M, +, ∙)是 格, 则称(M, +, ∙)为(L, +, ∙)的子格(sunlattice).

显然, (M, +, ∙)为(L, +, ∙)的子格 M关于+和 ∙封闭.

Remark 设(L, +, ∙)是格, M L, (M, )是 格与(M, )是子格存在差异. 正因为这样, 才 借助于子代数对子格定义.

(L, )与(L, )? Def 对于任意关于格(L, )的命题, 将命题前 提和结论中的(1) 改为; (2)+ 改为; (3) 改 为+;(4)0改为1;(5)1改为0所得到的命题称 为原命题的对偶命题. Theorem 6-2 对于任意关于格(L, )的真命题, 其对偶命题亦为真.

Chapter 6 格与布尔代数

格论(1935)是一种重要的代数结构, 它是计算机语 言的指称语义的理论基础,在计算机应用逻辑研 究中有着重要作用. 布尔代数是英国数学家George Boole在1847年左右 在对逻辑思维法则进行研究时提出的,后来很多 数学家特别是E. V. Hungtington和E. H. Stone对布 尔代数的进行了一般化研究,在1938年C. E. Shannon发表的A Symbolic Analysis of Relay and Switching Circuits 论文,为布尔代数在工艺技术

2.格的两种定义的等价性 格的这两种定义是否是一回事? Theorem 6-7 偏序格(L, )与代数格(L, +, ∙)是 等价的. Proof () () x, y L : x y x y x. (1) 是偏序.

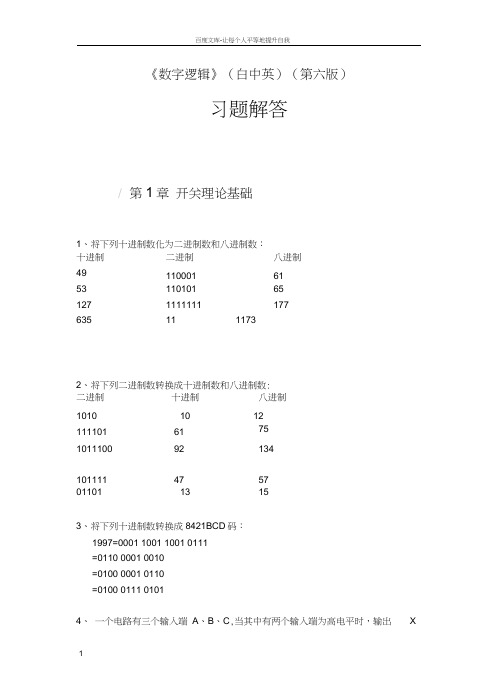

数字逻辑(白中英)(第六版)习题解答

《数字逻辑》(白中英)(第六版)习题解答/ 第1章开关理论基础1、将下列十进制数化为二进制数和八进制数:十进制二进制八进制49 110001 6153 110101 65127 1111111 177635 11 11732、将下列二进制数转换成十进制数和八进制数:二进制十进制八进制1010 10 12111101 61 751011100 92 134101111 47 5701101 13 153、将下列十进制数转换成8421BCD码:1997=0001 1001 1001 0111=0110 0001 0010=0100 0001 0110=0100 0111 01014、一个电路有三个输入端A、B、C,当其中有两个输入端为高电平时,输出X为高电平,试列出真值表,并写出X的逻辑表达式[解]:先列出真值表,然后写出X的逻辑表达式ABC X /0 0 0 P 00 0 1/■ 00 1 0 /00 1 1 11 0 0 01 0 1 1/1 1 0 11 1 1 0X ABC ABC ABC5、求下列函数的值:当A,B,C 为0,1,0 时:AB BC =1(A B C)(A B C) =1(AB AC)B =1当A,B,C 为1,1,0 时:AB BC =0(A B C)(A B C) =1(AB AC)B =1当A,B,C 为1,0,1 时:AB BC =0\ (A B C)(A B C) =1\ (AB AC)B =06用真值表证明恒等式A B C A B C成立。

证明:------- ■------------------------ --------------------------ABC ABC ABC0 0 0、0 00 0 1 \ 1 10 1 0 \ 1 10 1 1 、0 01 0 0 1 1 /1 0 1 0 \0 /1 1 0 0 \01 1 1 1 1所以由真值表得证。

姜书艳 数字逻辑设计及应用 12

Input Cord Word (输入 编码) Enable Inputs

Output Cord Word (输出 编码)

(使能输入)

实现正常映射功能)

Digital Logic Design and Application (数字逻辑设计及应用)

Most Commonly Used Case (一种最常用的情况) Decoder(译码器)

件如译码器、编码器、多路选择器、多路分配器、异或 门、比较器、全加器、三态器件等作为设计的基本元素

完成更为复杂的组合逻辑电路设计的方法。

6

Digital Logic Design and Application (数字逻辑设计及应用)

6.1 Documentation Standard (文档标准)

Digital Logic Design and Application (数字逻辑设计及应用)

6.2 Circuit Timing (电路定时)

Propagation Delay (传播延迟)

—— A Signal Path as the Time that it takes for a Change at the Input to Produce a Change at the Output of the Path (信号通路输入端的变化引起输出端变化所需的时间)

6.1.3 Signal Name and Active Levels (信号名和有效电平)

Name An

a Signal (信号的命名)

Active Level Associated with a Signal

High Low •Asserted (有效) •Deasserted(无效) •Negated(取消)

《数字逻辑基础》课件

• 数字逻辑概述 • 数字逻辑基础概念 • 组合逻辑电路 • 时序逻辑电路 • 数字逻辑电路的实现

01

数字逻辑概述

数字逻辑的定义

01

数字逻辑是研究数字电路和数字 系统设计的理论基础,它涉及到 逻辑代数、逻辑门电路、组合逻 辑和时序逻辑等方面的知识。

02

数字逻辑是计算机科学和电子工 程学科的重要分支,为数字系统 的设计和分析提供了基本的理论 和方法。

详细描述

布尔代数是逻辑代数的一个分支,它研究的是逻辑变量和逻辑运算的规律。布尔代数包括基本的逻辑 运算,如与、或、非等,以及一些复合运算,如异或、同或等。布尔代数在数字电路设计中有广泛应 用。

逻辑函数的表示方法

总结词

逻辑函数是指一种特定的函数,它将输 入的逻辑值映射到输出的逻辑值。

VS

详细描述

逻辑函数是指一种特定的函数,它将输入 的逻辑值映射到输出的逻辑值。在数字电 路中,逻辑函数通常用真值表、逻辑表达 式、波形图等形式来表示。理解逻辑函数 的表示方法对于数字电路设计和分析非常 重要。

数字逻辑电路的测试与验证

测试目的

确保电路功能正确、性能稳定。

测试方法

采用仿真测试和实际测试两种方法。

验证手段

逻辑仿真、时序仿真和布局布线仿真等。

谢谢您的聆听

THANKS

逻辑门电路

总结词

逻辑门电路是实现逻辑运算的电路,它是数字电路的基本单 元。

详细描述

逻辑门电路是实现逻辑运算的电路,它是数字电路的基本单 元。常见的逻辑门电路有与门、或门、非门等。这些门电路 可以实现基本的逻辑运算,并能够组合起来实现更复杂的逻 辑功能。

数字逻辑第6章习题参考解答.docx

第6章习题参考解答6-3画出74x27三输入或非门的德摩根等效符号。

解:图形如下浒"3 .............. ::BAWD5 ........ :OH6-10在图X6.9电路中采用74AHCT00替换74LS00,利用表6-2的信息,确定从输入端到输出端的最大吋间延迟。

解:该图中从输入到输出需要经过6个NAND2;每个NAND2 (74AHCT00)的最大时间延迟为9 ns;所以从输入端到输出端的最大时间延迟为:54 nso6-31 BUT门的可能定义是:“如果Al和Bl为1,但A2或B2为0,则Y1为1; Y2 的定义是对称的。

”写出真值表并找出BUT门输出的最小“积之和”表达式。

画出用反相门电路实现该表达式的逻辑图,假设只冇未取反的输入可用。

你可以从74x00、04、10、20、30组件中选用门电路。

解:真值表如下利用卡诺图进行化简,可以得到最小积Z 和表达式为Y1=A1B1A2,+A1B1B2, Y2=A 1' • A2 B2+B 1' A2 B2Y2采用74x04得到各反相器 采用74x10得到3输入与非 采用74x00得到2输入与非 实现的逻辑图如下:6-32做出练习题6-31定义的BUT 门的CMOS 门级设计,可以采用各种反相门逻辑的 组合(不一定是二级“积Z 和”),要求使用的品体管数目最少,写出输出表达式并画出 逻辑图。

解:CMOS 反相门的晶体管用量为基本单元输入端数量的2倍;对6・31的函数式进行变换:yi = A1B1-A2'+41 ・ Bl • B2'=(41 • Bl ) •(A2'+B2‘) =(A1 ・ Bl )(A2 • B2) Y2 = A2-B2-AY+A2- B2 • BV=⑷.B2)•⑷+B1) =(A2 • B2)-(A1 • Bl )利用圈■圈逻辑设计,可以得到下列结构:Y\ = ((41 • B1)+(A2 • B2『) Y2 = ((A2 • B2),+(A1 • Bl ))HANDS74X0011H AN Di-Y13(A2 B2 A1 丁 (A2 B2 时“翔此 .....dz >Y2 674X10HANDS 5HANDS5^133 2./1U3㈣D36(A1 EM A2)1此结构晶体管用量为20只(原设计屮晶体管用量为40只)6-20采用一片74x138或74x 139二进制译码器和NAND 门,实现下列单输出或多数 出逻辑函数。

(完整word版)数字逻辑第六章

第六章时序逻辑电路1 :构成一个五进制的计数器至少需要()个触发器A:5B:4C:3D:2您选择的答案: 正确答案: C知识点:n个触发器可构成一个不大于2n进制的计数器。

A -————-————-——-——--——------——--——----——--———-——-—-———————--—-—————-——--————-—2 :构成一个能存储五位二值代码的寄存器至少需要()个触发器A:5B:4C:3D:2您选择的答案:正确答案: A知识点:一个触发器能储存1位二值代码,所以用n个触发器组成的寄存器能储存n位二值代码。

—-————-—---—---—-—-——--—-—-—----————---—---———--—---—--——---—-------—-——--——3 : 移位寄存器不具有的功能是()A:数据存储B:数据运算C:构成计数器D:构成译码器您选择的答案: 正确答案: D知识点:移位寄存器不仅可以存储代码,还可以实现数据的串行—并行转换、数值的运算、数据处理及构成计数器。

-—-—————---—--——--—-——---——-———-—--—---——---————-————-----——-—--—-————--————4 :下列说法不正确的是()A:时序电路与组合电路具有不同的特点,因此其分析方法和设计方法也不同B:时序电路任意时刻的状态和输出均可表示为输入变量和电路原来状态的逻辑函数C:用包含输出与输入逻辑关系的函数式不可以完整地描述时序电路的逻辑功能D:用包含输出与输入逻辑关系的函数式可以完整地描述时序电路的逻辑功能您选择的答案:正确答案: D知识点:时序逻辑电路的逻辑关系需用三个方程即输出方程、驱动方程及状态方程来描述。

——---—-——-—————--—-——----—---—-—---—-——--—-—------————-——--——--———--—-------5 : 下列说法正确的是( )A:时序逻辑电路某一时刻的电路状态仅取决于电路该时刻的输入信号B:时序逻辑电路某一时刻的电路状态仅取决于电路进入该时刻前所处的状态C:时序逻辑电路某一时刻的电路状态不仅取决于当时的输入信号,还取决于电路原来的状态D:时序逻辑电路通常包含组合电路和存储电路两个组成部分,其中组合电路是必不可少的您选择的答案: 正确答案: C知识点:时序逻辑电路的特点:时序逻辑电路中,任意时刻的输出不仅取决于该时刻的输入,还取决于电路原来的状态.时序逻辑电路通常包含组合电路和存储电路两个组成部分,其中存储电路是必不可少的。

逻辑与计算机设计基础第五版课后答案chapter06

逻辑与计算机设计基础第五版课后答案Chapter066.1 填空题1.逻辑电路中,5个逻辑门包括与门、或门、非门、与非门和或非门。

2.组合逻辑电路是由逻辑门组成的。

3.子电路是由节点和逻辑门组成的。

4.逻辑门的输入端数称为其阶数。

5.卡诺图的横纵坐标是逻辑变量。

6.卡诺图上的每个矩形对应一个最小项。

7.复杂逻辑函数可以用几个较小的逻辑单元构成。

8.门电路可不断扩展到更复杂的逻辑电路。

9.简化布尔函数是优化逻辑电路的一种方法。

10.简化布尔函数可以减少电路中的逻辑门数量。

6.2 选择题1.LogicWorks软件包含设计逻辑电路所需的全部功能,以下哪个是LogicWorks的主要特点?A. 用户界面简洁易用,适合初学者使用。

B. 提供了强大的绘图工具和仿真工具。

C. 方便学生理解和掌握基本逻辑电路的设计方法。

D. 以上三项都是。

答案:D2.LogicWorks 是一个集成功能强大的绘图工具和仿真工具于一身的逻辑设计软件,它具有如下特点,除了__B__之外全部是()。

A. 用户界面简介易用,适合初学者使用。

B. 它可以为学生编写和作业设计电路图。

C. 提供由身强大的仿真工具。

D. 方便学生理解和掌握基本逻辑电路的设计方法。

答案:B3.在 LogicWorks 软件中,可以通过输入“ EN ” 来实现一个与逻辑电路的启停。

假设“ EN ” 通入值为高电位则电路启动,“ EN ” 通入值为低电位则电路停止。

A. 对B. 错答案:A4.LogicWorks 中连接点上的箭头表示其状态,仅当断头朝上是高电平表示 1,断头朝下是低电平表示 0。

A. 对B. 错答案:B5.以下哪一项是LogicWorks软件中可以直接编辑数字逻辑电路的操作?A. 点击元件图形中每个连接点上方那一根看不见的电线就可以显示与进一步编辑节点的名称。

B. 在每个连接点上方那根看不见的线上点击鼠标右键可以弹出含有描述节点名称的对话框。

C. 鼠标左键只点击连接点上方的连线,可以改变该位的电平状态。

数字逻辑-第6讲

计数顺序

N 进制 计数器 计数规 律举例0 1 2 3 4 5

计 数 状 态 Q2 Q1 Q0 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 0 0 0

具有 5 个独 立的状态,计满 5 个计数脉冲后, 电路状态自动进 入循环。故为五 进制计数器。

计数的最大数目称为计数器的“模”,用 M 表示。 模也称为计数长度或计数容量。 五进制计数器也称模 5 计数器;十进制计数器则 n 个触发器有 2n 种输出,最多可实现模 2n 计数。 为模 10 计数器;3 位二进制计数器为模 8 计数器。

Q

Q

Y

n 1 Q2n1 1 0 2 n 1 Q1n 1 1 0 1 n 1 0 0 Q0n 1 1 1 0

0 1 0 1 0 1 0

Y 0 1 1 00

1

1

1

0 1 0 1 0 1 0 1

1 1 1 1 0 0 0 0

0 0 0 0 1 1 0 0

时序电路的一般方框图如下:

X(x1,x2…xi)代表输入信号 Y(y1,y2…yj)代表输出信号

Q(q1,q2…ql)代表存储电路的 输出

Z(z1,z2…zk)代表存储 电路的输入信号

这些信号之间的关系可用三个向量函数表示: Y(tn) = F[X(tn),Q(tn)] Q(tn+1) = G[Z(tn),Q(tn)] Z(tn) = H[X(tn),Q(tn)] 输出方程 状态方程 驱动方程

计数器用作分频器

CP Q0 Q1 计数器为什么能用作分频器? 怎么用?

f Q0 1 f CP 2 1 f CP 4 1 f CP 8 1 f CP 16

f Q1

f Q2 f Q3

数字逻辑第6章习题解答

习题六6.1 可编程逻辑器件有哪些主要特点?PLD作为一种通用型可编程逻辑器件,而它的逻辑功能又是由用户通过对器件编程来自行设定的。

它可以把一个数字系统集成在一片PLD上,而不必由芯片制造厂商去设计和制作专用集成芯片。

采用PLD设计数字系统和中小规模相比具有如下特点:(1) 减小系统体积:单片PLD有很高的密度,可容纳中小规模集成电路的几片到十几片。

(低密度PLD小于700门/片,高密度PLD每片达数万门,最高达25万门)。

(2) 增强逻辑设计的灵活性:使用PLD器件设计的系统,可以不受标准系列器件在逻辑功能上的限制;用户可随时修改。

(3) 缩短设计周期:由于可完全由用户编程,用PLD设计一个系统所需时间比传统方式大为缩短;(4) 用PLD与或两级结构实现任何逻辑功能,比用中小规模器件所需的逻辑级数少。

这不仅简化了系统设计,而且减少了级间延迟,提高了系统的处理速度;(5) 由于PLD集成度高,测试与装配的量大大减少。

PLD可多次编程,这就使多次改变逻辑设计简单易行,从而有效地降低了成本;(6) 提高系统的可靠性:用PLD器件设计的系统减少了芯片数量和印制板面积,减少相互间的连线,增加了平均寿命, 提高抗干扰能力,从而增加了系统的可靠性;(7) 系统具有加密功能:多数PLD器件,如GAL或高密度可编程逻辑器件,本身具有加密功能。

设计者在设计时选中加密项,可编程逻辑器件就被加密。

器件的逻辑功能无法被读出,有效地防止电路被抄袭。

6.2 常见PLD器件有哪些主要类型?常见PLD器件根据可编程逻辑器件问世的时间,我们把PLA、PAL和GAL称为早期的可编程逻辑器件,把CPLD及FPGA称为近代的可编程逻辑器件。

也有人把它们分别称为低密度PLD和高密度PLD。

6.3 简述PAL和PLA在结构上的主要区别。

PAL是由可编程的与阵列、固定的或阵列和输出电路三部分组成。

有些PAL器件中,输出电路包含触发器和从触发器输出端到与阵列的反馈线,便于实现时序逻辑电路。

数字逻辑知识点

TTL与MOS集成逻辑门多余输入端的处理:

与门/与非门——多余输入端接高电平

或门/或非门——多余输入端接低电平

要牢记各种门电路的逻辑符号!(教材P243~244)

第三章布尔代数与逻辑函数化简

基本公式

基本法则:

代入法则:逻辑等式中的任何变量A,都可用另一函数Z代替,等式仍然成立。

第四章组合逻辑电路

组合逻辑电路的定义

组合逻辑电路的分析过程:

(1)由给定的逻辑电路图,写出输出端(关于输入)的逻辑表达式;

(2)列出真值表;

(3)从真值表概括出逻辑功能;

(4)对原电路进行改进设计,寻找最佳方案(这一步不一定都要进行)。

组合逻辑电路的设计步骤:

(1)将文字描述的逻辑命题变换为真值表,这是十分重要的一步。

由反演律(参见第三章摩根定理)可以看出,利用“与”和“非”可以得出“或”;利用“或”和“非”可以得出“与”。因此,“与非”、“或非”、“与或非”这三种复合运算中的任何一种都能实现“与”、“或”、“非”的功能,即这三种复合运算各自都是完备集。

集成逻辑门

由于软件工程专业没有电路、模拟电子的先修课程,此部分涉及到电路细节部分不作要求,只概念性地了解相关集成逻辑芯片的逻辑功能及芯片系列的参数等。

两种表示法:

或:

(满足约束关系式的输入变量取值为“合法”取值,

不满足约束关系式的输入变量取值为“非法”取值——无关项×)

有利于逻辑函数的化简时可以利用相应的无关项。

逻辑函数的描述方法常用的有:

真值表法、布尔代数法、卡诺图法、逻辑图法、波形(时序)图法

(其中 布尔代数法、逻辑图法具有“多样性”)

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

D

Yi D mi

A0A1 1-to-4 Demultiplexers 1/2 74x139

G_L A B G A B Y0 Y1 Y2 Y3 Y0_L Y1_L Y2_L Y3_L

Y2 I7 I6 I4 I3

Y1 I7 I6 I3 I2

Y0 I7 I5 I3 I1

2. Priority Encoders

Interrupt System 74×148 EI I0 I1 A2 A1 A0

H7 I7 H6 I6 I7 H5 I5 I6 I7 H4 I4 I5 I6 I7 H3 I3 I4 I5 I6 I7 H2 I2 I3 I4 I5 I6 I7 H1 I1 I2 I3 I4 I5 I6 I7 H0 I0 I1 I2 I3 I4 I5 I6 I7

Output F

Select

F D0 A1 A0 D1 A1 A0 D2 A1A0 D3 A1A0

Y Y_L

F Di mi

i 0

3

Ex.6-5

Input BCD Codes X.

X3 X2 X1 X0 0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 0 1 1 1 1 1 1 0 0 1 1

Z 2 (Y1_L Y3_L Y7_L ) Z3 (Y2_L Y3_L Y5_L )

Z 4 (Y0_L Y2_L Y4_L Y7_L )

74×138 “1” G1 G2A G2B Y0 Y1 Y2 Y3 C B A A B C Y4

Z4

Z3

Y5 Y6

Y7

Z2

Z1

Output F=1 if X÷3=Integer, else F=0 . 74×151 Truth Table F=X0’ F

1 0 0 1 0 0 1 0 0 1 d

F=X0 F=0

X0

0 1 0 1 0 1

X1 X2 X3

EN A B C D0 D1

Y

Y

F=X0’ F=X0

D2 D3 D4 D5 D6 D7

Y0

Y1 Y2 Y3 Y4 Y5 Y6

Y0_L

Y1_L

Y2_L Y3_L Y4_L Y5_L Y6_L Y7_L

B

C High

EN G1 G2 A G2 B

②Output: Indicating Input Code Word: Y7,Y6,Y5,Y4,Y3,Y2,Y1,Y0

Y7

Yi EN mi

For 74×138

Yi_L mi

If

G1 1 G2A 0 G2B 0

Z (Y3_L Y4_L Y5_L Y7_L)

1

Z1 ((m3 m4 m5 m6 )) (m3 m4 m5 m7 ) Z 2 ((m1 m3 m7 )) (m1 m3 m7 ) Z3 ((m2 m3 m5 )) (m2 m3 m5 ) Z4 ((m0 m2 m4 m7 )) (m0 m2 m4 m7 )

A B C D

a b c d e f g

6.3 Encoders

1. 8-3 Encoders Description: ①Input: 1-out-of 8 Codes ②Output: 3bit Binary Codes Don’t Care Term

2n~n

I7 0 0 0 I6 0 0 0 0 0 0 1 0 I5 0 0 0 0 0 1 0 0 I4 0 0 0 0 1 0 0 0

Yi_L (EN mi )

Ex.6-1

4-16 Decoders

Ex.6-2

5-32 Decoders

Ex.6-3 Design Combinational Logic Circuit using 74×138.

Z1 AC ABC ABC Z BC ABC 2 Z 3 AB ABC Z 4 ABC BC ABC

F F_L

1 0 0 0 1 0 0 1 1 0 1 0 … 1 1 1 1

F X0 X3X2X1 X0 X3X2X1 X0 X3X2X1 X0 X3X 2X1

32-to-1 Multiplexer

Demultiplexers Y0 Y1 Y2 Y3

Soln.

Z1 AC( B B) ABC ABC m3 m4 m5 m6 Z 2 BC( A A) ABC m1 m3 m7 Z3 AB(C C) ABC m2 m3 m5 Z 4 ABC BC( A A) ABC m0 m2 m4 m7

1/2 74x139 G_L A B G A B

Y0 Y1 Y2 Y3

Y0_L Y1_L Y2_L Y3_L

1 0

0 0 0

× × 0 0

0 1 1 1 0 1

1 1

1 1 0

1 1

1 0 1

1 1

0 1 1

1 0

1 1 1

1/2 74x139 G A B Y0 Y1 Y2 Y3

74×138 2. 3-8 Decoders 74×138 Enable and Output are Active Low Description: ①Input: 3bit Binary Number: A,B,C Enable Control: G1,G2A,G2B G1 G2A G2B Low A

Y2 EN I1I0 EN m2 Y3 EN I1I0 EN m3

I0 I1 EN

n~2n

Binary Decoders Truth Table

EN I1 I0 0 1 1 1 1 × × 0 0 0 1 1 1 0 1 Y3 Y2 Y1 Y0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0

A2 H7 H6 H4 H3 A1 H7 H6 H3 H2 A0 H7 H5 H3 H1

I2

I3 I4 I5 I6 I7 GS EO

IDEL I0 I1 I2 I3 I4 I5 I6 I7

EO: IDEL GS=EO’ IF EI=0

2-4 Decoder

Y3

Y2

Y1 Y0

I0 I1

EN

Y0 Y1 Y2 Y3

Logic Symbol

1/2 74x139

74×139

Dual 2-4 Decoder Enable and Output are Active Low Truth Table

G A B Y3 Y2 Y1 Y0

G

A B

Y0 Y1 Y2 Y3

Low

A4

A3 A2 A1 A0

Ex.6-4 32-5 Encoders

6.4 Three-State Devices Address Bus Data Bus Floppy Hard Disk Disk Driver Driver Display

CDROM

CPU

ROM Keyboard Just one device active at one time! Hi-Z to Low or High is slower than Low or High to Hi-Z. SDRAM Printer

2. Seven-Segment Decoders

a f e 74×48 d g ba b c d e a b c d e

f f

g dp g dp 74×49

74×49

BI

Common-cathode BI: Blanking Input D,C,B,A: BCD Codes Input a,b,c,d,e,f,g: Seven-Segment Codes Output

Binary Encoders Truth Table

I3 0 0 0 1 0 0 0 0 I2 0 0 1 0 0 0 0 0 I1 0 1 0 0 0 0 0 0 I0 Y2 Y1 Y0 1 0 0 0 0 0 0 0 0 0 0 0 1 1 1 1 0 0 1 0 1 0 1 0 1 0 1

0 0 0 0 1

Chapter 6

Combinational Logic Design Practices

Preface

6.1 Documentation Standards

1.A Specification ■Define Input and Output ■Exact Description for Function of a Circuit 2.A Block Diagram ■Base Interconnection of a Circuit 3.A Schematic Diagram Don’t modify if have not licence ■The Final and all Details of Description for Interconnection of a Circuit 4.A Timming Diagram ■The Cause-and-effect Delays between Critical Signals 5.A Structured Logic Device Description ■The all Details of Description for CPLD or FPGA etc. 6.A Circuit Description ■The Special Description of a Circuit