基于FPGA的数字滤波器的设计

基于FPGA的IIR低通数字滤波器的设计

文件 时调 用 已建立好 的模 块 。测 试仿 真结 果表 明基于 F GA设计 的 IR数字滤 波器 达到 了设计 要求 。 P I

关键 词 :I I R数字 滤波 器 级 联型 中图分 类号 :T 1 N7 3 F GA P 文章 编号 :1 0 .8 22 1)20 2 .3 0 34 6 (0 20 .0 40

小截 断误 差的考 虑 , 据设计 指标 首先 利用 Mal 依 t b进行 参数 的计算 并进行 量化 ,同时获得 系统 的幅频 响应 、 a 单位 冲击 响应等 系统 基本信 息 。随后 在分 析 IR 数字 滤波器 内部 乘法器 、加 法器 的输入 输 出基础上 ,调 用 I Q ats I u r 软件 调试 程序 建立乘 法器 和加 法器模 块 ,依据 自顶 向下的设 计思想 搭建 整体 电路 ,并在 建立项 层 uI

据 幅度 特 性 指 标 要 求 设 计 了 一个 输 入 8位 、输 出

8位 的 IR低 通 数 字滤 波 器 。 I

频谱分析等领域 。数字滤波器按照响应方 式的不 同 ,可 分 为 FR ( 限长 脉 冲 响 应 )滤 波 器 和 IR I 有 I ( 限长 脉 冲 响应 ) 波 器 ] 比较 于 FR 数 无 滤 。相 I

Ab tat On ido IR d i l l rw ihhs8i usa d8o tusi ds ndbsdo PG I src: ekn I i t f t hc a n t n u t s ei e ae nF A.n f g ai e p p g tr so elain o sdrn erai h ut g err rt 'tep rmeesaecm ue n em frai t .cniei dces g tectn ro, sl h aa t r o p td ad z o g n i y r q a te yui t bb sdo eing ieie h se fr aino a ntd ep nead u ni db sn Mal ae nd s ud l .Tes tm i om t m g i erso s n z g a g n y n o f u ip l e o s r l curd L trbsdo ea a s p t n u u IRdgtl l rn e m us rs ne e s aq i . ae ae t n l io i u do t tf I ii f t n r e p a ao e , nh y sf n a p o ai e i mut l ainada dr c ie Quru it n erdt tpmut l aina da drm c ie l lpi t n d e hn , ats s r s re s lpi t n d e a hn d i c o ma H a f o eu i c o mo

基于FPGA的FIR数字滤波器的实现

G r a p h ) 算法进 一步 简化 C S D编码 . 然后采 用 A l t e r a 公

司的 F P G A芯片来实现信号处理中的 F I R数字滤波器.

实验证 明这是 一种 F I R数 字 滤 波 器 的 较 好 的 设 计 选 择, 具 有 应 用 价值

HUA Z e , ZHAO Xi n g -h a n g , F U Z h a o - y a n g , L U Yo u , Z HANG Ni

( 1 ) 从最低有效位开始 . 用 1 0 …( ) - 1 取 代 所 有 大 于 2的 1 序 列 。此 外 还 需 用 1 1 0 — 1 取代 1 0 1 1 。 ( 2 ) 从最高有效位开始 , 用0 1 1 代替 1 0 - 1 。 例如 :

( 9 1 ) 1 0 = ( 1 0 1 1 0 1 1 ) 2 - ( 1 1 0 旷1 0 - 1 ) 佳c s D

收稿 日期 : 2 01 3 — 0 9 —1 0 修稿 日期 : 2 0 1 3 —1 0 —1 0

作 者 简介 : 陈剑 冰 , 男, 本科 , 研 究 方 向 为信 号 处理

④ 现 代 计算 机 2 0 1 3 . 1 0 中

Ap p l i c a t i o n o f He t e r O g e n e Ou S Sy s t e m I n t e g r a t i o n i n I n t e l l i g en t Tr a n s p or t a t i o n I n t e g r a t e d I n f o r ma t i o n PI a t f Or m

★基 金 项 目: 广 东省 科 技 厅 产 学研 项 目( No _ 2 0 1 2 B 0 9 1 1 0 0 3 4 9 ) 、 广 东省 经 信 委 项 目( No . G DE I D2 0 1 0 I s 0 3 4 ) 、 广 州市 越 秀 区科 技 项 目 ( No . 2 0 1 2 一 G X一 0 0 4 )

基于FPGA的IIR数字滤波器的设计与实现

关 键 词 : 阶 节 ,R 数 字 滤波 器 ,P 二 I I F GA

Ab ta t s rc

Ths ap nr du s eho sig as a i p erito ce a m t d ofu n c c ded s o der oc s ec nd or bl k whch i ba e on PGA o m pl s F t i emen h pr c— tte i i n

张书召 ( 桐柏 鑫 泓银 制 品有限 责任公 司 , 南 西峡 4 4 5 ) 河 7 7 0

彭 杰 ( 广东工业大学 自动化学院, 广东 广州 5 0 9 ) 10 0

摘 要

介 绍一 种 使 用 二 阶 节级 联 方 法在 F GA 上 实现 任 意 阶 数 的 I ( 限 脉 冲 响 应 ) 数 字 滤 波 器 的 原 理 和 方 法 。 首 先 在 P I 无 R

pe a d meh d o n r e u e I ( f i mp le rs o s ) dgtlf e i th i ri a c r a c t e ur— i n to fa y od rn mb rf R i it i us e p n e nn e ii i r r , e ft n c od n e wi rq i a l Fst t l e h e

1 I I R数 字 滤 波器 的 原 理 和 设计

_

al

丫

bl

. a I 2

丫

b 2

数 字滤 波 器 从 实 现 的 网络 结 构 或 者 从 单位 脉 冲响 应 的 长 度

图 1 直 接 n型 结 构

不 同 ,可 以 分 为 无 限 脉 冲响 应 (R)滤 波 器 和 有 限 脉 冲 响 应 I I

基于FPGA乘法器的FIR滤波器系统设计

基于FPGA乘法器的FIR滤波器系统设计FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,可以根据设计者的需求和要求进行编程,实现各种数字电路功能。

FIR (Finite Impulse Response)滤波器是一种常用的数字滤波器,其特点是能够对输入信号的有限长度的响应进行滤波处理。

本文将介绍基于FPGA乘法器的FIR滤波器系统设计。

首先,介绍FIR滤波器的原理。

FIR滤波器是一种线性时不变系统,其输出信号由输入信号的加权和组成。

FIR滤波器的输入经过一串系数的加权运算后,得到滤波器的输出。

FIR滤波器的传输函数为:H(z) = b0 + b1*z^(-1) + b2*z^(-2) + ... + bn*z^(-n)其中,bi是滤波器的系数,n是滤波器的阶数,z为单位延迟。

FIR 滤波器的输出信号可以表示为:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)其中,x是输入信号,y是输出信号。

FIR滤波器的阶数决定了滤波器的性能,阶数越高,滤波器的频率响应越陡峭。

接下来,介绍基于FPGA乘法器的FIR滤波器系统设计。

FPGA乘法器是FPGA中的一种硬件资源,通常用于实现乘法运算。

FPGA乘法器的乘法操作可以并行地执行,可以大大提高FIR滤波器的运算速度。

在设计基于FPGA乘法器的FIR滤波器系统时,首先需要确定FIR滤波器的阶数和系数。

根据滤波器的需求,可以选择不同的阶数和系数。

然后,根据FIR滤波器的传输函数,可以将其转化为差分方程形式。

差分方程形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(n-n)然后,将差分方程形式转化为数据流形式。

数据流形式中的每一步计算只涉及到少量的数据,可以并行地执行。

数据流形式如下:y(n) = b0*x(n) + b1*x(n-1) + b2*x(n-2) + ... + bn*x(0)接下来,需要将数据流形式转化为硬件电路。

基于FPGA的数字匹配滤波器的设计

摘 要 : 字 匹配滤 波 器( MF在 通信 和 雷达接 收机 中应用 广 泛, 数 D ) 文章 分析 了 匹配 滤 波器 的重要 参数 和 电路基 本 结构 , 结合 数字 匹配滤 波器

在扩 频 系统 中的应 用 , 出 了基 于 F R滤波 器的 I 核 设计 数 字 匹配滤波 器和折 叠数 字 匹配滤 波器 的 F G 实现 方 法。 给 I P PA

文章 编 号 :0 6 4 I( 00)6 06 — 2 10 — 3 12 1 1— 14 0

O 引言

匹 配 滤 波器 在通 信 、 达 最 佳 接 收机 以 及 扩 频 通 信 中 P 雷 N码 捕 获 中 被 广 泛 应 用 , 随着 高 速度 F G P A器 件 的 出现 及相 应 E A软 件 D 的成 熟 , 于 F G 的数 字 匹配 滤 波 器 ( F) 计和 实 现成 为研 究 基 PA DM 设 热 点 l 与传 统 的声 表 面 波 匹配 滤 波 器 相 比较 , l l 。 数字 匹配 滤 波 器 有着 特 殊 的优 点 : 理 增 益 高 , 编 程 能 力 强 , 存 在 固 有 噪 声 , 有 噪 处 可 不 没 图 1 传 统 FR 型 双 路 匹 配滤 波 器 结 构 I 声 积 累 问 题 , 且 处 理 信 号 的形 式 灵 活 。 采 用 F G 设计 数 字 匹 配 而 PA 结 构 的 顺 序相 反 , 加法 器 链 的 延 迟 替 代 了直接 型 FR结 构 中延 迟 且 I 滤 波 器 , 本 较低 , 积减 小 , 统 的 整体 性 能 很 高 。 成 体 系 移 位 寄 存 器 的作 用 。 然 , 置 结 构 的 等 待 时 间小 , 关长 度 的 改 变 显 倒 相 1 MF重 要 参数 D 但 匹配滤波器 的量化位数和抽样 频率在数 字匹配滤波器设计 中 也 非常 方 便 , 对 前 级 的带 负载 能 力 要 求 较 高 。 由于 乘法 器 系数 仅 1 ,可 以用 加 或 者 减 的 运 算 就 可 以代 替 实 际 意 义上 的乘 法运 一 是 两 个 非 常 重 要 的参 数 , 化 位 数 越 多 、 量 抽样 频 率 越 高 , 配 滤 波器 为+ /1 匹 所 简 倒 I 的性 能 越 好 , 硬 件代 价 也 越 大 , 实 际 应 用 下 , 该 实 际 根 据 情 况 算 , 以加 法 器 代 替 了乘 法器 , 化 了 电路 。 置 型 FR 匹配 滤 波器 但 在 应 二者 都 兼 顾 到 。 献川 多 比特 量 化 D 文 对 MF在 高 斯 白噪声 及 单 频 干扰 结 构 图 如 图 2所 示。 下 的性 能 与 模 拟 滤波 器 ( 化 无 穷 阶 数 滤 波 器 ) 行 了 比较 , 结论 量 进 其 是 : 高 斯 白 噪声 下 , 在 当超 过 两 比特 量 化 时 D MF的输 出信 噪 比 , 与 模 拟 滤 波 器 非 常 接 近 非 相 干 固 定 振 幅 正 弦 波 干扰 下 , 化 阶 数 在 量 超过 3比特时 , 输出信 噪比将会有 2 B差距。所以如果在高增益扩 d 频 系统 中 D MF的 相 关 长 度 较 长 ,为避 免 硬 件 代 价 太 大 可 采 用 3比 特量 化 方 案 。 样 在 保 证性 能 的 同时 , 件 规 模将 大 大减 少 。 设 在 这 硬 假 扩频 系统 中以 4信于码元速率采样率进行过采样。设计 中 P N码长 为 17 2 ,采用全周期相关 ,那么数字匹配滤波器的抽头系数有 5 8 0 个。对于 F G P A器 件 , 可以通过下式计算所需资 源数 : 占用触 发器 数: 每个 样 点 量 化 位 数× 采 样 率 x N码 序 列 位 长 。 过 P

基于 FPGA 的数字滤波器设计与实现

基于 FPGA 的数字滤波器设计与实现引言:数字滤波器是现代信号处理的重要组成部分。

在实际应用中,为了满足不同信号处理的需求,数字滤波器的设计与实现显得尤为重要。

本文将围绕基于 FPGA的数字滤波器的设计与实现展开讨论,介绍其工作原理、设计方法以及优势。

同时,还将介绍一些实际应用场景和案例,以展示基于 FPGA 的数字滤波器在实际应用中的性能和效果。

一、数字滤波器的基本原理数字滤波器是一种将输入信号进行滤波处理,改变其频谱特性的系统。

可以对频率、幅度和相位进行处理,实现信号的滤波、去噪、增强等功能。

数字滤波器可以分为无限脉冲响应滤波器(IIR)和有限脉冲响应滤波器(FIR)两种类型。

IIR滤波器是通过递归方式实现的滤波器,其输出信号与过去的输入信号和输出信号相关。

FIR滤波器则是通过纯前馈结构实现的,其输出信号仅与过去的输入信号相关。

两种类型的滤波器在性能、复杂度和实现方式上存在一定差异,根据具体的应用需求选择适合的滤波器类型。

二、基于 FPGA 的数字滤波器的设计与实现FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,通过可编程逻辑单元(PLU)、可编程连线(Interconnect)和可编程I/O(Input/Output)实现。

其可编程性使得 FPGA 成为数字滤波器设计与实现的理想平台。

1. FPGA的优势FPGA具有以下几个优势,使得其成为数字滤波器设计与实现的首选平台:灵活性:FPGA可以根据设计需求进行自定义配置,可以通过修改硬件逻辑来满足不同应用场景的需求。

可重构性:FPGA可以重复使用,方便进行修改和优化,减少芯片设计过程中的成本和风险。

高性能:FPGA具有并行处理的能力,可以实现多通道、高速率的实时数据处理,满足对于实时性要求较高的应用场景。

低功耗:FPGA可以进行功耗优化,通过减少冗余逻辑和智能布局布线来降低功耗。

2. 数字滤波器的实现方法基于 FPGA 的数字滤波器的实现方法主要有两种:直接法和间接法。

基于FPGA_的数字滤波器设计

332023年4月上 第07期 总第403期信息技术与应用China Science & Technology Overview进行相乘后,再积分运算,去除时间无关的干扰信号,获I/O 资源,含一个LTC 1407A 模数转换器和一个收稿日期:2022-10-10作者简介:周钧(1987—),男,壮族,广西南宁人,硕士研究生,工程师、硬件设计师,研究方向:FPGA、网络通信。

基于FPGA 的数字滤波器设计周 钧 樊 闯(中车大连电力牵引研发中心有限公司,辽宁大连 116000)摘 要:本文主要对一种基于FPGA 技术的数字锁相滤波器的设计。

结合Xilinx 开发平台,根据噪声信号非时间相干特性进行数字滤波器设计,在SPARTAN-3E 硬件板上完成了硬件协同仿真测试,同时给出测试结果。

测试结果表明,该数滤波器的消除噪声满足技术要求。

关键词:FPGA ;非时间相干特性;数字滤波图1 数字滤波设计原理342023年4月上 第07期 总第403期信息技术与应用China Science & Technology Overview示器。

示波器Tektronix TPS 2024:带宽为200MHz,最高取样速率:2.0GS/s,具有4个通道。

信号发生器HM-8030:频率50MHz 至10MHz,具备高纯度和幅度稳定性。

3.基于FPGA 的数字滤波器设计3.1 设计框架FPGA 设计框架如图2所示。

块,滤波模块和LCD 显示模块这些二级模块组成;(5)各二级模块根据功能划分,将各自功能用VHDL 进行编码设计。

二级模块经过仿真实现,在顶层模块进行结合,实现一整套系统功能。

3.3.1 模数转换设计ADC 芯片将采集的模拟信号离散化为单个离散采样值。

再将采样值转为数字值,根据板卡搭载的ADC 芯片[4]simulation 仿真产生的模拟信号可以非常接近,但是始图3 测试验证(a)测试1(b)测试2China Science & Technology Overview信息技术与应用0,4 V(max 0,223 V)(max 0,239 V)(max 0,233 V)(max 0,214 V)(max 0,234 V)352023年4月上 第07期 总第403期。

基于FPGA的数字滤波器设计与实现

基于FPGA的数字滤波器设计与实现数字滤波器是信号处理中常用的工具,可以通过滤除不需要的频率成分或者增强需要的频率成分对信号进行处理。

在数字信号处理领域,基于FPGA的数字滤波器设计与实现是一项重要的研究课题。

本文将介绍FPGA数字滤波器的设计原理、实现方法和应用领域。

首先,我们来了解一下FPGA(可编程逻辑门阵列)是什么。

FPGA是一种可重构的硬件平台,它由大量的可编程逻辑门电路构成。

相比于传统的ASIC(专用集成电路)设计,FPGA具有更高的灵活性和可重构性,可以实现多种不同的电路功能。

在数字滤波器设计中,FPGA可以用来实现各种类型的滤波器,如低通滤波器、高通滤波器、带通滤波器和带阻滤波器等。

FPGA数字滤波器的设计通常包括以下几个步骤:1. 规格定义:确定滤波器的工作频率范围、滤波器类型(如FIR滤波器或IIR滤波器)、滤波器阶数和滤波器的性能指标等。

2. 滤波器设计:根据规格定义,选择适合的滤波器结构和滤波器系数设计方法,如窗函数法、频率采样法或者最小二乘法等。

设计好的滤波器可以通过MATLAB等工具进行模拟验证。

3. 滤波器实现:将滤波器设计转化为可在FPGA上实现的硬件描述语言(如VHDL或Verilog)。

在这个步骤中,需要将滤波器结构转化为逻辑电路,并根据具体的FPGA平台选择适合的资源分配和布局策略。

4. 仿真验证:使用EDA(电子设计自动化)工具对滤波器进行仿真验证,确保其在FPGA上的功能和性能与设计规格一致。

5. 实际实现:将经过仿真验证的滤波器设计烧录到FPGA 芯片中,并进行实际的性能测试。

测试结果可以与仿真结果进行比较,来评估滤波器的实现质量。

FPGA数字滤波器的设计和实现具有以下几个优势:1. 高性能:FPGA提供了大量的逻辑资源和高速IO接口,可以实现复杂的滤波器结构和算法,并能够处理高速数据流。

2. 低功耗:相比于通用处理器,FPGA的功耗较低,可以在不牺牲性能的情况下降低系统的功耗。

基于fpga的滤波器设计与实现

基于fpga的滤波器设计与实现基于FPGA的滤波器设计与实现一、引言滤波器是信号处理中常用的一种工具,它可以通过剔除或增强信号中的特定频率分量来改变信号的特性。

而基于FPGA的滤波器是一种利用可编程逻辑器件FPGA来实现滤波功能的方法。

本文将介绍基于FPGA的滤波器的设计与实现过程。

二、滤波器的基本原理滤波器主要通过改变信号的频谱特征来实现滤波效果。

它可以分为两类:低通滤波器和高通滤波器。

低通滤波器通过剔除高频分量,保留低频分量;高通滤波器则相反,剔除低频分量,保留高频分量。

滤波器的设计需要根据具体的需求选择合适的滤波器类型和参数。

三、基于FPGA的滤波器设计与实现基于FPGA的滤波器设计与实现可以分为以下几个步骤:1. 确定滤波器类型和参数:根据实际需求,选择合适的滤波器类型和参数。

例如,如果需要设计一个低通滤波器,需要确定截止频率和滤波器阶数等参数。

2. 数字滤波器设计:将滤波器的模拟设计转化为数字滤波器的设计。

常见的数字滤波器设计方法有FIR滤波器设计和IIR滤波器设计。

FIR滤波器是一种无反馈的滤波器,具有线性相位特性;IIR滤波器则具有反馈结构,可以实现更高阶的滤波器。

3. 将数字滤波器转化为FPGA可实现的结构:将数字滤波器转化为FPGA可实现的结构,可以采用直接形式实现、级联形式实现或者管线化实现等方法。

其中,直接形式实现是最简单直观的方法,但其硬件资源占用较多;级联形式实现可以减少硬件资源的占用,但增加了延迟;管线化实现则可以兼顾硬件资源和延迟。

4. 使用HDL语言进行FPGA设计:使用HDL语言,如VHDL或Verilog,进行FPGA设计。

根据设计的结构和功能,编写相应的HDL代码。

在编写代码时,需要注意代码的可重用性和可维护性,以便后续的设计和调试。

5. 硬件验证和性能优化:完成HDL代码后,进行FPGA的硬件验证和性能优化。

通过仿真和验证,确保设计的正确性和稳定性。

同时,可以根据实际需求对硬件进行优化,如减小资源占用、降低功耗等。

基于FPGA的FIR数字滤波器的设计和实现

基于FPGA的FIR数字滤波器的设计和实现摘要:本文基于FPGA平台实现了一种FIR数字滤波器,通过对滤波器的设计与实现过程的详细介绍,展示了FPGA在数字滤波器中的应用优势。

首先介绍了数字滤波器的原理及其在信号处理中的重要性,并对FPGA及其特点进行了概述。

接着,详细介绍了FIR滤波器的原理以及其在FPGA上的实现步骤,分析了滤波器设计中需要考虑到的各种因素。

最后,通过实验验证了FPGA上实现的FIR滤波器的性能,并对优化策略进行了讨论。

关键词:FPGA,FIR滤波器,数字信号处理,性能优化1. 引言数字滤波器是现代信号处理的重要组成部分,通过选择性地传递或抑制输入信号的特定频率组成部分,对信号进行处理和改善。

FIR滤波器是数字滤波器中最常用的一种类型,具有线性相位特性、稳定性较强以及易于实现等优势。

而FPGA作为一种可编程逻辑器件,具有灵活性高、可重构性强等特点,成为实现数字滤波器的理想平台。

2. FIR滤波器的原理FIR滤波器是一种线性时不变系统,其输出仅和当前输入值以及过去若干个输入值有关。

该滤波器的输出可以通过输入信号的线性加权和来计算,其中,每个输入值的加权系数通过FIR 滤波器的系数来确定。

FIR滤波器的系数决定了它对不同频率分量的响应,从而实现了信号的滤波目的。

3. FIR滤波器在FPGA上的实现步骤(1)选择合适的FPGA平台和开发工具,如Xilinx FPGA平台和Vivado开发工具。

(2)根据所要设计的滤波器的需求,确定其采样频率、截止频率和滤波器类型等参数,并进行系统级设计。

(3)根据所选参数,设计FIR滤波器的传递函数,并确定滤波器的阶数和系数。

(4)通过数学运算或者通过滤波器设计软件生成滤波器的差分方程。

(5)根据生成的差分方程,使用HDL(HardwareDescription Language)进行滤波器的编写。

(6)进行FPGA的综合、布局与布线、下载与验证,完成滤波器的硬件实现。

基于FPGA的FIR滤波器的设计(毕业设计) 可用

目录摘要 (2)英文摘要 (3)1 引言 (3)1.1国内外研究现状 (4)1.2本论文的研究内容及主要工作 (6)2 FIR数字滤波器设计 (6)2.1数字滤波器基础 (6)2.1.1 数字滤波器简介 (6)2.1.2 FIR数字滤波器的结构 (7)2.2 FIR数字滤波器设计方法 (8)2.2.1 窗函数法 (8)2.2.2 频率采样法 (9)2.2.3 等波纹最佳逼近法 (11)2.2.4 三种设计方法的比较......................... 错误!未定义书签。

3 FPGA 设计优点以及分布式算法 (12)3.1 使用FPGA器件进行开发的优点 (13)3.2分布式算法 (14)3.2.1 分布式算法基础 (14)3.2.2 有符号的DA系统 (15)4 基于FPGA的FIR滤波器设计 (15)4.1基于M ATLAB的FIR数字低通滤波器抽头系数的提取 (16)4.1.1 滤波器的设计指标 (16)4.1.2 滤波器的具体设计方法 (16)4.1.3 参数提取与量化 (17)4.2FIR滤波器的FPGA实现 (19)4.2.1 模块划分 (19)4.2.2 FIR滤波器各模块的实现 (20)4.2.3 FIR滤波器的顶层设计 (30)4.3FIR滤波器的系统仿真验证 (32)4.4系统硬件 (36)4.4.1 系统框图 (36)4.4.2 部分芯片简介 (36)4.4.3 AD、DA电路原理图 (39)4.5测试波形及现场照片 (39)4.6数据误差分析 (40)结论 (41)参考文献 (41)附件 (42)基于FPGA的FIR滤波器的设计摘要:本文设计了一个基于FPGA的16阶FIR低通滤波器,使用分布式算法作为滤波器的硬件实现算法,并对其进行了详细的讨论。

针对分布式算法中LUT规模过大的缺点,采用多块查找表的方式减小硬件规模。

在设计中采用了自顶向下的层次化、模块化的设计思想,将整个滤波器划分为多个模块,利用VHDL语言的描述方法进行了各个功能模块的设计,最终完成了FIR数字滤波器的系统设计。

基于FPGA的级联型IIR数字滤波器的设计

蕾 帅

b l

O 1

O1

1

1

K n

- yu u ot l p

0 。 x !X 0 ]口Ⅱ

O 0 D

x L x

X 2 3 X e ¥ 1 X 4

版 社 , 0 2 1. 2 0 , 0

I 弘 X | X 铀 8

图2 IO 字滤波器仿真 图 数 I

[]刘 凌, 2 胡永生译 . 数字信号 处理的F G 实现 [] 北京 : PA M. 清华大 学 出版 社 , 0 3 5 20 ,. []邹 彦, 3 庄 严等. D 技术与数字系统设计 [ ] 北京 : EA M. 电子工业 出版社,074 20,. [3潘 4 松 , 国栋 . H L 王 V D 实用 教程 [] 成 都 : M. 电子 科技 大学 出版

对相位要求不高的地方 ,选择 IR I 滤波器可 以充分发挥其经 济高效 的特 点。。IR I 滤波作为信 号处理领域 中最 基本的一

种处理方法 被广泛地 应用于雷达 、通信 、语音处理 等许多

研 究 领域 。

2 IR 波器级联单元的设计方案 滤 I 任何一个IR I数字滤波器都 可以由多个 二阶滤波器级联

y n 1 。其 中y u 是 反馈 输入信 号 ,X ( )是输 入信 号。 (一 ) or n 补码乘加模块 的设计主要用来 实现输 入序列 ()、 ( } ”} 一 与 )

结构如 图1 所示 。

图 1 的x n 作 为 F G 接 口上 的A D 件 的 转 换 数 据 输 中 () PA /器

此方案使得设计 灵活 ,设计周期短 ,节省资源。

特性 。I R I滤波器用 较低 的阶数获得高 的选择性 ,所用 的存 储单元少,信号延迟小 ,经济且 高效。F R I 滤波器 ,要用较 高的阶数才 能达 到高的选择性 。 因此在对 相位要 求较高 的 场合,F R I 占据 了统 治地位 ;在对 滤波器选择性要求较高而

基于fpga的滤波器设计与实现

基于fpga的滤波器设计与实现基于FPGA的滤波器设计与实现一、引言滤波器是信号处理中常用的工具,用于去除信号中的噪声或不需要的频率成分。

在数字信号处理中,滤波器可以通过软件算法实现,但随着现代电子技术的发展,使用基于FPGA的滤波器可以实现更高效、实时的信号处理。

本文将介绍基于FPGA的滤波器设计与实现的方法和步骤。

二、FPGA的基本原理FPGA(Field Programmable Gate Array)是一种可编程逻辑器件,由大量的逻辑门、存储单元和可编程连接组成。

FPGA的特点是可重构性强,可以根据需要编程实现各种逻辑功能。

在数字信号处理中,可以将滤波器的算法实现在FPGA中,利用其并行处理的能力来提高处理速度和效率。

三、滤波器的基本原理滤波器可以根据其频率响应的特点分为低通滤波器、高通滤波器、带通滤波器和带阻滤波器等。

滤波器的设计目标是在保留需要的信号成分的同时,去除不需要的噪声或频率成分。

常用的滤波器设计方法有FIR滤波器和IIR滤波器。

四、基于FPGA的滤波器设计步骤1. 确定滤波器的类型和设计要求:根据信号处理的需求,确定滤波器的类型(低通、高通等)和性能指标(截止频率、通带衰减等)。

2. 确定滤波器的结构:选择合适的滤波器结构,如直接形式、级联形式等。

3. 设计滤波器的传递函数:根据滤波器的类型和设计要求,设计出满足要求的传递函数。

4. 将传递函数转化为差分方程:根据所选滤波器结构,将传递函数转化为差分方程。

5. 实现差分方程的计算:将差分方程转化为FPGA可以计算的形式,使用硬件描述语言(如Verilog、VHDL)编写计算模块。

6. 将计算模块综合到FPGA中:使用相应的工具将计算模块综合到FPGA中,生成比特流文件。

7. 下载比特流文件到FPGA:将生成的比特流文件下载到FPGA中,使其开始工作。

8. 测试和优化:对设计的滤波器进行测试,并根据测试结果进行优化,以满足设计要求。

一种基于FPGA的分布式FIR数字滤波器设计

i m F R p s ii f t scr u t o x mp e t i e n i h o g f h U r h o I lw a sd gt l r ic i fre a l ,i lme t n t r u h o e L T,a d r n h h f rg s r F — t f o l ai e s mp o t d e dt e s i e it . i a t e n n h it b td a g rt m i lt d n h e ut h w t a e o t l tu t r al f ciey a p id i i l s a y t e d s u e l o h i s i r i s mu ae ,a d t e rs l s o h t h p i s t ma sr cu ec l ef t l p l n w r e s e v e e sain dg t in r c s ig mo u e tt ii s a p o e sn d l ,w i h h s u e il r g a o l a gl h c a s d o F ed P o r mma l t ra a d r e o r e f c iey f b e Gae A r y h r wae r s u c s ef t l e v

基于FPGA的FIR数字滤波器设计

基于FPGA的数字滤波器设计院系:信息科学与工程学院专业班:通信工程1102班姓名:李羚学号:20111181082指导教师:周忠强王军舰2015年5月基于FPGA的FIR数字滤波器设计摘要随着公元的第二十一个世纪的到来,今天我们进入了一个科技日新月异的时代。

在现代电子数字系统中,滤波器都以一个不可缺少的身份出现。

其中,FIR数字滤波器又以其良好的线性特性被广泛和有针对性的大量使用。

众所周知,灵活性和实时性是工程实践中对数字信号处理的基本要求。

在以往使用的各种滤波器技术中,不难发现有许许多多的问题。

但是,随着现代计算机技术在滤波问题上的飞跃,派生出一个全新的分支——数字滤波器。

利用可编程逻辑器件和EDA技术,使用FPGA来实现FIR 滤波器,可以同时兼顾实时性和灵活性。

基于FPGA的FIR数字滤波器的研究势在必行。

本论文讨论基于FPGA的FIR数字滤波器设计,针对该毕业设计要做的基本工作有如下几点:(一)掌握有限冲击响应FIR(Finite Impulse Response,FIR)的基本结构,研究现有的实现方法。

对各种方案和步骤进行比较和论证分析,然后针对目前FIR数字滤波器需要的特点,速度快和硬件规模小,作为指导思想进行设计计算。

(二)基于硬件FPGA的特点,利用Matlab软件以及窗函数法设计滤波器。

对整个FPGA 元件,计划采用模块化、层次化设计思想,从而对各个部分功能进行更为详细的理解和分工设计。

最终FIR数字滤波器的设计语言选择VHDL硬件编程语言。

(三)设计中的软件仿真使用Altera公司的综合性PLD开发软件Quartus II,并且利用Matlab工具进行对比仿真,在仿真的过程中,对比证明,本论文设计的滤波器的技术指标已经全部达标。

关键词:数字滤波器Matlab 可编程逻辑元件模块化算法Based On FPGA Design Of FIR Digital FiltersMajor:Electronic And Information Engineering Department(Information Engineering)Student: YangChengjie Supervisor:FengLiuAbstractAs we have entered the twenty first century,our technology is changing continuously with the times. In the modern electronic digital systems,filters are indispensable. Among them,the FIR digital filters are widely used with the excellent linear characteristic. As is well-known to us all,flexibility and real-time quality are the basic requirements in digital signal processing of engineering practice. Since we have used a variety of filter technology in the past,it is not difficult for us to find many problems in it. Moreover,with the development of modern computer technology in filter,a new branch - digital filter has derived. We make use of the programmable logic devices and EDA technology,together with the FPGA to design the FIR filter,which is real-time and flexible. In a nutshell,it is imperative to do the research in the FIR digital filters based on the technology of FPGA. This thesis is focused on the design of the FIR digital filters based on the technology of FPGA. Several points are worth mentioning here:(1)To understand and master the basic structure of the limited shock Response FIR (Finite Impulse Response,FIR),research existing realization method,to use various solutions to compare and analyze the steps and demonstrations; then,to do the self design and correction concerning the characteristics of the present FIR digital filters,that is,fast in speed and small scale in hardware.(2) To design FIR filter based on the characteristics of FPGA hardware. In the design process,ready to use of Matlab software and window function method design filter. As far as the whole FPGA components are concerned,we plan to carry on the modularized and hierarchic design,in order to have a more detailed understanding of the function of eachpart and make a division of design. Eventually,FIR digital filters will adopt the VHDL hardware programming language.(3) To adopt the comprehensive PLD development software Quartus II of the Altera company in the design of the software simulation. And we will use of the Matlab tools for the simulation 。

基于FPGA的FIR数字滤波器设计的开题报告

1.2 FIR与IIR滤波器相比具有的优势

具有严格的线性相位又具有任意的幅度 FIR滤波器的单位采样响应是有限长的,因 而滤波器性能稳定 FIR滤波器由于单位冲击响应是有限长的, 因而可用快速傅里叶变换(FFT)算法来实 现过滤信号,可大大提高运算效率

1.3 使用FPGA器件进行研究的优点

基于FPGA的FIR数字 滤波器设计

摘要

目前,在数字信号处理和电子应用技术领域,滤波器作为 一个不可少的组成部分,处在一个十分重要的地位,已经 广泛应用于通信、语音、图像、自动控制、军事、航空、 航天、医疗和家用电器等众多领域,并日益显示出其巨大 的应用价值。 在经典滤波器采用的电路中,若要同时满足多个技术指标 或达到较高的精度,往往设计复杂、结构庞大、元件数量 多,并且还可能达不到要求。随着利用计算机技术解决滤 波器设计的不断深入,派生出了一个新的分支,即数字滤 波器,同模拟滤波器相比,它具有精度高、灵活性好、便 于大规模集成等突出优点。近二十年来,FPGA技术的飞速 发展为数字滤波器的设计和实现开辟了一条广阔的道路。

5.1 相关概念说明

数字滤波器(Digital filter) 是由数字乘法器、加法器和延时单元组成 的一种装置。其功能是对输入离散信号的 数字代码进行运算处理,以达到改变信号 频谱的目的。可认为是一个离散时间系统 按预定的算法,将输入离散时间信号转换 为所要求的输出离散时间信号的特定功能 装置

效能 上 市 时 间 成本 可靠性 长 期 维 护

-突破顺序执行 -用户的变更时间短 -跟随系统需求变化 -不需要使用作业系统 - 可 重 设 性 质

2.1 国内外研究现状概括

自从XilinX公司1985年推出第一片FPGA以来,由 于集成度高、方便易用、开发和上市周期短,使 得FPGA器件在数字设计和电子生产中得到迅速 普及和应用,发展潜力十分巨大。现在FPGA已 经发展到可以利用硬件乘加器、片内储存器、逻 辑单元、流水处理技术等特有的硬件结构,高速 完成FFT 、FIR 、复数乘加、卷积、三角函数以 及矩阵运算等数字信号处理。这样可以完成信号 处理的主要技术,如中频采样、参数估计、自适 应滤波、脉冲压缩、自适应波束形成和旁瓣对消 等。

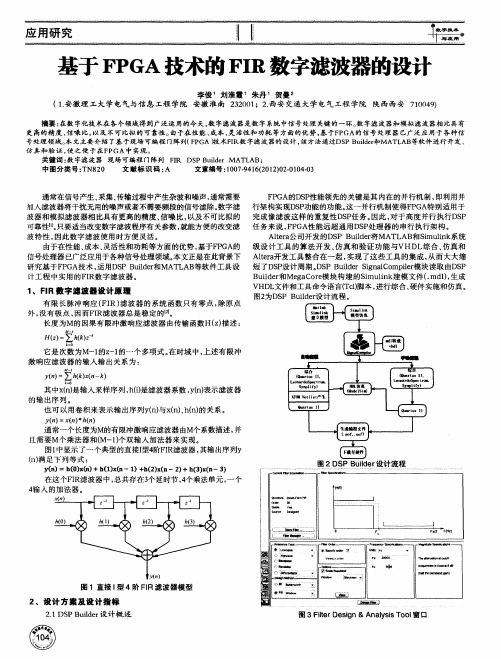

基于FPGA技术的FIR数字滤波器的设计

通常一个长度为M的有 限冲激响应滤波器 由M个系数描述 , 并 静 且需要M个乘法器和( M—1个双输入加法器 来实现 。 ) 图l 中显示 了一个典型的直 接I 阶F R 型4 I 滤波器 , 其输出序列y 执 束瓣 一 ~ () 足 下 列 等 式 : n满

应 用 研 究

基于 F G P A技术的 F R数字滤波器的设计 I

李俊 ’刘淮霞 ,朱丹 ,贺曼2

(. 1 安徽理工大学电气与信息工程 学院 安徽淮南 22 0 ;2西安交通大学电气工程学院 陕西西安 70 4) 30 1 . 10 9

摘要 : 数 字化技 术在 各 个领 域得 到广 泛 运 用的今 天 , 字滤波 器是 数 字 系统 中信 号 处理 关键 的一 环 。 字滤 波器和 模拟 滤 波 器相 比具有 在 数 数 更 高的精 度 、 噪 比 , 及不 可 比拟 的 可 靠性 。 于在 性 能 、 信 以 由 成本 、 活性和 功耗 等方 面 的优 势 , 于F GA的信 号 处 理 器 已广泛 应 用 于各 种信 灵 基 P

: ;

yn ()=h O xn +h 1xn一1 h 2x n一2 +h S xn一3 () () ( ) ( )+ ( ) ( ) () ( )

图 2D ule 设 计 流 程 SP B i r d

在这个FR滤波器 中 , I 总共存 在3 个延时节,个乘法单元, 4 一个 4 入 的加 法 器 。 输

1 I 、FR数字滤波器设计原理

有 限长脉冲响 应( I 滤波器 的系统 函数 只有零点 , F R) 除原 点 外 , 有 极 点 , 而 FR滤 波 器 总 是 稳 定 的【 没 因 I 长度 为M的因果有 限冲激 响应滤波器 由传 输函数H() z 描述 :

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

重庆大学本科学生毕业设计(论文)基于FPGA的数字滤波器的设计学生:黄建华学号:********指导教师:***专业:电子信息工程重庆大学通信工程学院二O一三年六月Graduation Design(Thesis) of Chongqing University Design of Digital Filter Based on FPGAUndergraduate: Huang JianhuaSupervisor: Yang LishengMajor: Electronic Information EngineeringCollege of Communication EngineeringChongqing UniversityJune 2013摘要数字信号处理在通信、雷达、声纳等中有着广泛的应用。

数字滤波器的设计是数字信号处理的关键技术之一,有着十分重要的理论和实际意义。

随着数字技术的不断发展,在许多场合,数字滤波器正在快速取代模拟滤波器。

FPGA(现场可编程门阵列)在现代数字电路设计中发挥着越来越重要的作用。

从设计简单的接口电路到设计复杂的状态机,FPGA所扮演的角色已经不容忽视。

本论文完成了基于FPGA的FIR和IIR数字滤波器的设计与实现。

本论文首先理论分析讨论了数字滤波器的设计方法,并使用MATLAB工具验证采用哪种窗函数来设计FIR数字滤波器,使用哪种模拟滤波器原型映射IIR数字滤波器。

然后根据模拟滤波器的技术指标来确定数字滤波器的技术指标,在MATLAB环境下按照数字滤波器的技术指标设计数字滤波器,并得到滤波器系数,编程实现系数量化,并且比较分析量化前后系统响应的差异,由此得到合适的量化等级。

然后在ISE软件平台下根据MATLAB工具得到的量化系数,使用VHDL语言进行FIR和IIR滤波器算法模块编程,同时对AMP电路(可编程预放大器)模块、AD电路(模拟到数字转换器)模块和DA电路(数字到模拟转换器)模块分别进行编程配置,并且对各模块进行严格的软件仿真验证,其中AMP电路模块、AD电路模块和DA电路模块必须进行硬件验证。

最后将所有软件和硬件验证无误的模块整合,下载到FPGA硬件中,进行功能验证。

验证结果符合设计要求。

关键词:FIR滤波器,IIR滤波器,MATLAB,FPGA,VHDLABSTRACTDigital signal processing has been widely used in communications, radar, sonar and many other fields. The design of digital filter is one of the key technologies of digital signal processing, which has a very important theoretical and practical significance. As digital technology continues to develop, on many occasions, the digital filter is rapidly replacing analog filters. FPGA (field-programmable gate array) in modern digital circuit design is playing an increasingly important role. From the design simple interface circuit to the design of the complex state machine, FPGA's role has not been to ignore. This thesis accomplishes a FPGA-based FIR and IIR digital filter design and implementation. This thesis first theoretically analyses the method of digital filter design ,with MATLAB tool verifying which window function is suitable for the FIR digital filter design, which analog filter prototype maps IIR digital filter . And according to the technical specifications of the analog filter the paper determines the specifications of the digital filter. Next in the MATLAB environment in accordance with the technical specifications of the digital filter the paper designs digital filters.And the paper gets the filter coefficients, programming to quantify the coefficients. And the paper has comparative analysis of before and after quantitative differences the system response, thereby obtaining a suitable quantization levels. Then in the ISE software platform according to the obtained quantized coefficients with MATLAB tools, the paper uses VHDL language to program FIR and IIR filter algorithm module. While the AMP circuit (programmable pre-amplifier) module, AD circuit (analog to digital converter) circuit module and DA (digital to analog converter) module are programmed to be configured. And each module has rigorous software simulation, where AMP, AD and DA circuit module must have hardware verification. Finally the paper integrates all the software and hardware verification correct modules, downloading to the FPGA hardware for the functional verification. The Verified result meets the design requirements.Key words:FIR filter, IIR filter, MATLAB, FPGA, VHDL目录摘要 (I)ABSTRACT (II)目录 (III)1 绪论 (1)1.1 课题研究背景及意义 (1)1.2 国内外研究现状 (1)1.3 研究思路 (3)2 FIR数字滤波器简介 (4)2.1 FIR数字滤波器的原理 (4)2.2 FIR数字滤波器的基本结构 (4)2.3 线性相位FIR数字滤波器的结构 (5)2.4 FIR数字滤波器的设计方法 (6)3 IIR数字滤波器简介 (7)3.1 IIR数字滤波器的原理 (7)3.2 IIR数字滤波器的基本结构 (7)3.3 IIR数字滤波器的设计方法 (8)4 MATLAB程序设计 (11)4.1 MATLAB简介 (11)4.2 FIR滤波器设计 (11)4.3 IIR滤波器设计 (15)5 VHDL程序设计 (21)5.1 VHDL语言简介 (21)5.2 DA电路配置 (21)5.3 AMP电路配置 (25)5.4 AD电路配置 (28)5.5 FIR滤波器设计 (31)5.6 IIR滤波器设计 (34)5.7 总体设计 (37)6 结论 (40)参考文献 (41)1 绪论1.1 课题研究背景及意义数字信号处理(Digital Signal Processing,DSP)技术是从20世纪60年代以来,随着信息学科和计算机学科的高速发展而迅速发展起来的一门新兴学科。

因为多数科学和工程遇到的是模拟信号,所以以前都是研究模拟信号处理的理论和实现。

但是模拟信号处理难以做到高精度,受环境影响较大,可靠性差,且不灵活等。

随着电子技术的飞速发展,加之数字信号处理技术的不断成熟和完善,数字信号处理已经逐渐取代模拟信号处理。

相比于模拟信号处理,数字信号处理具有精度高、灵活性高、可靠性强、容易大规模集成、时分复用、可获得高性能指标、二维和多维处理等优点[1]。

数字信号处理广泛应用在滤波与变换、通信、语音、图像、消费电子、工业控制和自动化、医疗、军事等领域。

并且,数字信号处理在数字汇聚、远程会议系统、融合网络、数字图书馆、多媒体通信、个人信息终端等新兴领域有很大的应用前景。

数字滤波器是数字信号处理中很重要的一个分支。

数字滤波器是对数字信号实现滤波的离散时间系统,它将输入的数字序列通过特定运算转变为所需的数字序列[2]。

根据冲激响应函数的时域特性,可将数字滤波器分为两种,即无限长冲激响应IIR滤波器和有限长冲激响应FIR滤波器。

数字滤波器一般由数字乘法器、加法器和延时单元组成的一种算法或装置。

模拟滤波器分为有源和无源的,有源滤波器主要由集成运放、电阻、电容构成,无源的滤波器主要由R,L,C构成[3]。

模拟滤波器的物理构成导致存在电压漂移、温度漂移和噪声等问题。

模拟滤波器还存在一个很严重的问题,当技术指标改变时,其常常要更换电容、电感、运放等元件,相当繁琐。

FPGA(Field-Programmable Gate Array),即现场可编程门阵列,与早期的PROM、PLA、PAL、GAL、EPLD等可编程器件相比,在结构、工艺、集成度、功能、速度和灵活性方面都有很大的改进和提高[4]。