AS和JTAG配置方式演示实验

基于FPGA的1GHz数据采集卡研制 (1)

摘要摘要目前高速数据采集在电子产业中的应用越来越广泛,尤其是在软件无线电和遥感,数字示波器、孔径雷达等需要解决大带宽信号的采集和处理的方面。

高速数据采集系统的要求包括具有高的数据采样速率和分辨率,大的模拟输入带宽和大容量存储设备等。

本文结合“瞬态高速运动目标测试雷达系统"对数据采集的要求,设计了采样速率为1Gsps的采集卡。

为了达到系统要求的采样速率,设计采用E2V公司的高速模数转换芯片AT84AD001,并通过三线串行接口设置使其工作在并行交错采样模式下。

使用大规模可编程逻辑器件(FPGA)作为系统时序和逻辑的核心,实现对高速数据的接收以及后续存储电路和USB2.0接口电路的控制。

存储电路部分选用4片镁光公司的大容量SDRAM实现对数据的缓存,并通过USB2.0接口芯片CY7C68013实现与上位机之间的数据交互。

另外,高速电路板的设计过程不同于普通的电路,设计时必须要对电源完整性和信号完整性进行全方位考虑,论文对电路板设计要注意的事项进行了讨论。

论文给出了数据采集卡调试验证的过程,并对其中存在的一些问题进行了分析和修正。

关键词:高速A/D采样;并行交替模数转换;异步FIFO;SDRAM;USB2.02高速数据采集卡及工作原理行多通道采样技术,即并行时间交替(Time.interleaved)技术。

并行时间交替采样是对同一模拟信号直接输入到n片A/D(或者一个芯片的11个通道),A/D按照各自的采样时钟工作,n片A/D的采样时钟的相位差为360/n度,系统的采样率为n片(或n个通道)AJD的总和【10l。

下面结合本系统所采用的ADC芯片AT94AD001B详细阐述其工作过程:系统所用的AT84AD001B中含有两个独立的ADC转换器,时钟CLKO和CLKl的频率相同,相位差为360/2,即相差180度。

其中一路在CLKO的上升沿取样,采样点为奇数点;另一路在CLKI的上升沿取样,采样点为偶数点。

FPGA下载配置指南

1 FPGA的上电启动原理FPGA是基于RAM结构的,当然了,也有基于FLASH结构的,但RAM结构的是主流,也是我们讨论的重点。

而RAM是易失存储器,在掉电后保存在上面的数据就丢失了,重新上电后需要再下载一次才可以。

因此,我们肯定不希望每次重新上电后都用PC去下载一次,工程实现也不允许我们这么做。

所以,通常FPGA旁边都有一颗配置芯片,它通常是一片FLASH,或者是并行或者是串行接口的。

不管是串行还是并行的FLASH,它们的启动加载原理基本相同,后面我们会专门讨论。

FPGA器件有三类配置下载方式:主动配置方式(AS)、被动配置方式(PS)和最常用的基于JTAG的配置方式。

AS和PS模式主要是将bit流下载到配置芯片中;而JTAG模式则既能将代码下载到FPGA中直接在线运行(速度快,调试时优选),也能够通过FPGA将bit流下载到配置芯片中。

由于JTAG方式灵活多用,所以我们的VIP板就只预留了JTAG接口。

AS配置方式:AS配置方式由FPGA器件引导配置操作过程,它控制着外部存储器及其初始化过程,EPCS系列配置芯片如EPCS1,EPCS4,EPCS16等配置器件专供AS模式。

使用Altera串行配置器件来完成,FPGA器件处于主动地位,配置器件处于从属地位。

配置数据通过DATA0引脚送入 FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS配置方式:PS配置方式则由外部计算机或其它控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

JTAG配置方式:JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA实验指导书(1)

实验一组合逻辑3-8译码器的设计 .................... 错误!未定义书签。

实验二基于FPGA的数字钟的设计 ................... 错误!未定义书签。

实验三基于NIOS的交通灯实验 .......................... 错误!未定义书签。

实验四静态图像显示 ............................................. 错误!未定义书签。

实验一组合逻辑3-8译码器的设计一、实验目的:1、通过3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、掌握组合逻辑电路的静态测试方法。

3、初步了解可编程器件设计的全过程。

二、实验步骤:1、打开QuartusII软件。

2、选择路径。

选择File/New Project Wizard,指定工作目录,指定工程和顶层设计实体称;注意:工作目录名不能有中文。

3、添加设计文件。

将设计文件加入工程中。

单击“Next”,如果有已经建立好的VHDL 或者原理图等文件可以在File name中选择路径然后添加,或者选择Add All添加所有可以添加的设计文件(.VHDL ,.Verilog原理图等)。

如果没有直接点击“Next”,等建立好工程后再添加也可,这里我们暂不添加。

4、选择FPGA器件。

Family选择Cyclone II,Available device选EP2C35F484C8,Packge选择Any,Pin Count 选择484,Speed grade选择Any;点击“Next”。

5、选择外部综合器、仿真器和时序分析器。

Quartus II支持外部工具,可通过选中来指定工具的路径。

这里我们不做选择,默认使用Quartus II自带的工具。

6、结束设置。

单击“Next”,弹出“工程设置统计”窗口,上面列出了工程的相关设置情况。

最后单击“Finish”,结束工程设置。

7、建立原理图文件。

USB_Blaster安装和使用

6安装USB下载线驱动安装软件以后,我们还需要安装USB BLASTER(下载线)的驱动。

USB BLASTER 的驱动是有Quartus II软件提供的在安装过程中,大家要注意点,就是驱动的路径是:X:\altera\11.1\quartus\drivers\usb-blaster千万不要进入X32或x64文件路径下。

如果您是WIN7系统用户,如果出现不能安装的情况,请将防火墙,杀毒软件都关掉,然后重新安装。

在这里,我简单说明一下USB下载线的使用方法。

支持两种下载方式,一种是JTAG方式,一种是AS方式。

对应的在核心板上有两个10针的接口,上面有标识AS口和JTAG口。

USB下载线一端与电脑的USB口相连接,另一端与JTAG口或者AS口相连。

在同一时刻,我们只能使用其中一个接口。

其中JTAG方式负责FPGA在线仿真,程序通过USB下载线下载到FPGA内部SRAM 中。

由于FPGA是基于SRAM技术的,所以掉电以后,程序会丢失;AS方式是将程序下载到FPGA外部的配置芯片EPCSX中的,EPCSX实质是一种串行FLASH,因此,掉线以后,程序不会丢失。

每次上电,EPCSX中的程序都会自动加载到FPGA 中,然后再开始运行。

USB BLASTER本身就有仿真和下载两种功能,因此,FPGA开发过程中只需要USB BLASTER既可以实现在线仿真和程序固化两个功能。

其中JTAG方式主要用于在线仿真,而AS方式用于最终的程序固化到外部的配置芯片EPCSX中。

程序下载测试上述过程都完成以后,接下来,我们就要试试是否可以进行下载程序了,您也一定期待已久了吧,那现在我们就开始吧。

在光盘中,我们为大家准备了已经编译好的固件测试程序,在文件夹测试固件下。

下面我将为大家演示如何进行下载测试。

在这里要首先要说一下,拿到光盘以后,建议大家先将光盘内容拷贝到硬盘中,还有一点要注意的,就是不要放到含有中文和空格的路径下。

大华智能交通摄像机二次开发智能算法JTAG调试说明

(2) 挂载 DSP 运行: 挂载设备后, 运行/home/loadk (3) 连接 JTAG,进入 CCS 调试模式.

8/9

注:若要显示YUV原图,需要将YUV转换成CCS支持的标准YUV格式才能正常显示。

9/9

在 DHSDK_algProcess 函数处设置断点。当程序停在断点后,点击菜单选项 ToolsImage Analyser, 会出现设置图像属性的界面。 这里以 2592*2048 大小的 YUV 图像为例,观察 Y 分量的设置如下:pFrame-yAddr 是 Y 地址。

然后, 在 Image 栏目中, 右键弹出选项中选择 Refresh, 当前 pFrame 包含的 YUV 图像图像的 Y 分量图就可以显示出来。如下:

3/9

1. 简介 1.1 引言 1.2 编写目的

本文档主要介绍如何使用 JTAG 仿真器调试大华智能交通摄像机二次开发算法。

1.3 范围

大华智能交通摄像机二次开发算法。

2. JTAG 使用说明 2.1 JTAG 配置文件

1、打开 CCS 软件,点击 FileNewTarget Configurations,弹出菜单,在 General Setup 栏目中的 Connection 下拉选择兼容的仿真器如图。 Board or Device 选择 TI814x。

6/9

2.4 JTAG 调试及挂载 DSP

1、挂载 DSP 运行: (1) 新建文件 k01(只需执行一遍): cd /mnt/mtd mkdir rc.d cd rc.d touch k01 (2) 新建挂载 DSP 脚本: mount –t nfs 10.6.5.68:/home/dahua /home -o nolock,tcp cp /usr/bin/loadk /home/loadk 使用 vim 打开 loadk 脚本,将其中的/var/tmp/ipnc_rdk_fw_c6xdsp.xe674 修改 成/home/ipnc_rdk_fw_c6xdsp.xe674 (3) 重启后挂载服务器目录如/home/dahua,然后运行该目录下的 loadk 脚本: /home/loadk 即可运行用户打包出来的 DSP 程序。 2、调试 DSP 程序: (1) 编译带调试信息的 DSP 程序: 修改 Dsp\Makefile,去掉$(STRIP) $(EXE_NAME)一行 运行 make pack(或 make dsp)后在 Dsp\dspbin 会生成带调试信息的 DSP 程序 ipnc_rdk_fw_c6xdsp.xe674

FPGA配置

16

串行时钟(DCLK)在配置结束后内部振荡器关闭。下表列出 了DCLK的输出频率。对于Cyclone II FPGA,通过MSEL[]可以 选择时钟为20MHz或40MHz。 配置的时间与配置文件大小以及DCLK的频率有关,关于AS 方式配置时间的估算请见下一小节。

器件 Cyclone Cyclone II

VCC VCC VCC VCC

R1 10k 10k

R2 JTAG接 口 1 3 5 7 9 2 4 6 8 10

VCC (1)

Cyclone(Cyclone II) FP GA

nCE nSTATUS CONF_DONE nCONFIG MSEL0 MSEL1 DATA0 DCLK TCK TDO TMS TDI

12

另外,不同型号FPGA的配置文件大小不同,下表中列出了FPGA在

不压缩情况下二进制配置文件(.rbf)的最大大小。设计者可以根据配置文 件的大小来选择合适的配置器件和其它存储器。并可使用压缩功能,来

减小配置文件的大小。

器件类型 器件型号 EP1C3 数据大小(Bits) 数据大小(Bytes) 627,376 78,422

18

2.2 主动串行配置(AS)的配置时间估算

主动串行配置时间为串行配置器件数据传送到FPGA的时间,

这取决于DCLK的频率以及配置文件的大小。 以Cyclone EP1C6器件为例,非压缩的.rbf格式配置文件的

大小为1167216位、DCLK最低频率为14MHz(71ns),则最大

配置时间为: 1167216*71ns=82872336ns≈83ms

1. FPGA配置

配置(configuration)是对FPGA的内容进行编程的过程。 每次上电后都需要进行配置是基于SRAM工艺FPGA的一个特

【实验】基于FPGA数字电路实验指导

【关键字】实验基于FPGA数字电路实验指导(修改稿)湖北科技学院计算机科学与技术学院编制工程技术研究院目录第一部分实验基础知识随着科学技术的发展,数字电子技术在各个科学领域中都得到了广泛的应用,它是一门实践性很强的技术基础课,在学习中不仅要掌握基本原理和基本方法,更重要的是学会灵活应用。

因此,需要配有一定数量的实验,才能掌握这门课程的基本内容,熟悉各单元电路的工作原理,各集成器件的逻辑功能和使用方法,从而有效地培养学生理论联系实际和解决实际问题的能力,树立科学的工作作风。

一.实验的基本过程实验的基本过程,应包括:确定实验内容、选定最佳的实验方法和实验线路、拟出较好的实验步骤、合理选择仪器设备和元器件、进行连接安装和调试、最后写出完整的实验报告。

在进行数字电路实验时,充分掌握和正确利用集成器件及其构成的数字电路独有的特点和规律,可以收到事半功倍的效果,对于完成每一个实验,应做好实验预习、实验记录和实验报告等环节。

(一)实验预习认真预习是做好实验的关键。

预习好坏,不仅关系到实验能否顺利进行,而且直接影响实验效果。

预习应按本教材的实验预习要求进行,在每次实验前首先要认真复习有关实验的基本原理,掌握有关器件使用方法,对如何着手实验做到心中有数,通过预习还应做好实验前的准备,写出一份预习报告,其内容包括:1.绘出设计好的实验电路图,该图应该是逻辑图和连线图的混合,既便于连接线,又反映电路原理,并在图上标出器件型号、使用的引脚号及元件数值,必要时还须用文字说明。

2.拟定实验方法和步骤。

3.拟好记录实验数据的表格和波形座标。

4.列出元器件单。

(二)实验记录实验记录是实验过程中获得的第一手资料。

尝试过程中所尝试的数据和波形必须和理论基本一致,所以记录必须清楚、合理、正确,若不正确,则要现场及时重复尝试,找出原因。

实验记录应包括如下内容:1.实验任务、名称及内容。

2.实验数据和波形以及实验中出现的现象,从记录中应能初步判断实验的正确性。

cyclone3的配置方式

cyclone3的配置方式cyclone3的配置方式cyclone3器件使用SRAM单元保存配置信息。

因为SRAM掉电易失的特性,fpga芯片上电的时候必须重新配置。

根据期间密度和封装选择,它有如下5中配置方案(红色部分为常用配置方案,并不是所有FPGA芯片都能使用所有配置方案,具体可查看cyclone3的器件手册):1. Active serial (AS)主动串行配置2. Active parallel (AP)主动并行配置3. Passive serial (PS)被动串行配置4. Fast passive parallel (FPP)快速被动并行配置5. Joint Test Action Group (JTAG)AS和AP配置方案需要外部FLASH存储器存储配置信息。

其它3种配置方案需要外部的控制器或者下载电缆。

主动配置方案以及JTAG方案常用于单芯片系统设计。

下面重点介绍AS,AP和JTAG。

以AS配置为例介绍。

Cyclone3器件的配置芯片通常选择EPCS64,EPCS16以及EPCS4或者flash.这些芯片能够提供廉价,方便(引脚少)的解决方案。

因为FPGA芯片容量的限制,它对配置信息的大小也有所限制。

EP3C80系列器件可提供21MBITS的配置信息流容量。

MSEL【3:0】为FPGA器件的输入,用于确定配置方式。

AS模式下,它连接1101.AP模式下,它连接1011.注意要直接接 VCCA or GND,更不能悬空,避免无效配置。

查看手册可得到其它配置值。

在JTAG模式下,忽略MSEL配置,JTAG模式有优先权。

AS模式支持配置信息压缩,AP模式不支持。

压缩信息可以节约空间以及配置时间。

在Device & Pin Options――Configuration中可以选择压缩与否。

选择好器件后,参考下图连接。

POR――上电复位.复位时间由MSEL【3:0】决定。

复位结束后开始发送配置控制信号。

Altera可编程逻辑器件编程与配置

配置文件

配置文件格式及用途:

.sof :如果选择配置模式为JTAG或PS方式,使用Altera的下载电缆对FPGA 进行配置时,将用到.sof文件。这个文件是QuartusII工具自动产生的。在使 用.sof文件配置时, QuartusII下载工具将控制整个配置的顺序,并为配置数 据流内自动插入合适的头信息。其它配置文件类型都是从.sof产生出来的。 .pof : .pof文件是用来对各种Altera配置芯片进行编程的文件。要注意的是, 需要在QuartusII工具中设置编程器件类型,才可以生成该类型的.pof文件。 对一些小的FPGA ,多个FPGA的.sof文件可以放到一个.pof文件中,烧制到 一个配置器件中;而对一些较大的FPGA,如果一个配置器件不够,可以使 用多个配置器件,工具可以将配置文件分到几个配置芯片中。 .rbf : .rbf 文件是二进制的配置文件,只包含配置数据的内容。通常被用在 外部的智能配置设备上,如微处理器。例如,一种用法是将.rbf 文件通过其 它工具转换成十六进制的数组文件,编译到微处理器的执行代码中,由微处 理器将数据载入到FPGA中。当然,也可以由处理器在配置过程中完成实时 的转换工作。 .rbf 中的LSB(最低位)被首先载入到FPGA中。

(1) Although you cannot configure FLEX 6000 devices through the JTAG pins, you can perform JTAG boundary-scan testing.

FPGA配置过程

PS方式配置过程波形

FPGA配置过程

FPGA配置状态机

由目标FPGA来主动输出控制和同步信号(包括配置时钟) 给Altera专用的一种串行配置芯片(EPCS1和EPCS4等), 在配置芯片收到命令后,就把配置数据发到FPGA,完成 配置过程。

计算机组成原理 实验一 熟悉实验环境(Quartus Ⅱ) 实验报告

大学实验报告

成绩

课程名称 计算机组成原理 指导教师

实验日期 2020

院(系) 计算机学院 专业班级

实验地点

学生姓名

学号

同组人

实验项目名称

实验一 熟悉实验环境

一、 实验目的和要求

实验目的: 1. 熟悉 QuartusII 环境; 2. 学习在 QuartusII 中新建项目、文件、编译、仿真。 3. 学习使用组成原理实验箱运行 QuartusII 的项目。

1.单击 动打开。

下载按钮或是使用 Tools->Programmer 命令,编程器窗口自

2.在图中,单击“Start”按钮,计算机就开始下载编程文件,开始下载后, 屏幕上的进度条以百分数表示下载进度。下载完成后如下图所示。

注意:下载前应检查窗口中的欲下载的文件名、器件型号和下载模式是否正 确,硬件编程器是否存在等,只有上述正确才可以开始下载。

大学实验报告(附页)

3.在上图还可以单击“Device and Pin Options”按钮,在弹出的“Device and PinOptions”窗口中,单击“Unused Pins”对未使用引脚进行处理。

4.选择“As input tri-stated”(避免未使用引脚对系统中其他元器件造成 影响,保证系统可靠工作,一般可将未使用引脚设定为三态输入方式)后,单击 “确定”按钮,返回上图所示窗口。

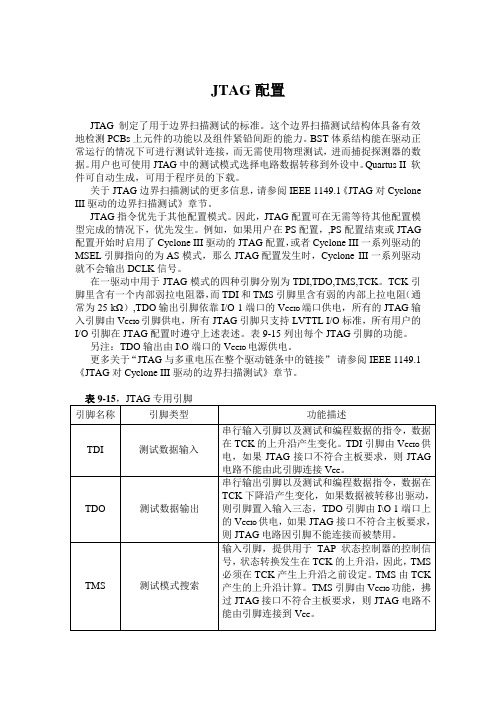

JTAG配置

JTAG配置JTAG制定了用于边界扫描测试的标准。

这个边界扫描测试结构体具备有效地检测PCBs上元件的功能以及组件紧铅间距的能力。

BST体系结构能在驱动正常运行的情况下可进行测试针连接,而无需使用物理测试,进而捕捉探测器的数据。

用户也可使用JTAG中的测试模式选择电路数据转移到外设中。

Quartus II 软件可自动生成,可用于程序员的下载。

关于JTAG边界扫描测试的更多信息,请参阅IEEE 1149.1《JTAG对Cyclone III驱动的边界扫描测试》章节。

JTAG指令优先于其他配置模式。

因此,JTAG配置可在无需等待其他配置模型完成的情况下,优先发生。

例如,如果用户在PS配置,,PS配置结束或JTAG 配置开始时启用了Cyclone III驱动的JTAG配置,或者Cyclone III一系列驱动的MSEL引脚指向的为AS模式,那么JTAG配置发生时,Cyclone III一系列驱动就不会输出DCLK信号。

在一驱动中用于JTAG模式的四种引脚分别为TDI,TDO,TMS,TCK。

TCK引脚里含有一个内部弱拉电阻器,而TDI和TMS引脚里含有弱的内部上拉电阻(通常为25 kΩ),TDO输出引脚依靠I/O 1端口的V CCIO端口供电,所有的JTAG输入引脚由V CCIO引脚供电,所有JTAG引脚只支持LVTTL I/O标准,所有用户的I/O引脚在JTAG配置时遵守上述表述。

表9-15列出每个JTAG引脚的功能。

另注:TDO输出由I\O端口的V CCIO电源供电。

更多关于“JTAG与多重电压在整个驱动链条中的链接”请参阅IEEE 1149.1《JTAG对Cyclone III驱动的边界扫描测试》章节。

在JATG配置过程中,用户可通过USB-Blaster, MasterBlaster, ByteBlaster II, ByteBlasterMV 下载线,以及Ethernet – Blaster将数据下载到驱动上的PCB中,配置驱动中使用的电缆类似于编程系统中的驱动,图9-24和9-25显示Cyclone III 驱动系列其中之一的JTAG配置。

BJ-EPM实验板介绍

BJ-EPM240CPLD开发板介绍BJ-EPM240学习板是特权同学和知名电子技术网站合作推出的一款FPGA/CPLD入门级学习板,该学习板在EDN助学活动期间以低廉的价格提供给所有注册会员,并且赠送免费的PCB板。

学习板以齐全的资料、良好的代码风格博得了广大网友的一致认可,很适合初学者入门学习。

该板子的一切相关问题都可以在EDN网站的CPLD/FPGA助学小组(网址:/1375/)里进行讨论。

该开发板配套北航出版社2010年6月出版的《深入浅出玩转FPGA》进行深入学习,并且特权同学录制了同名的《深入浅出玩转FPGA》视频教程配套。

1.BJ-EPM240学习板功能框图图1和图2是整板系统的功能框图,从图中可以清楚地看到EPM240T100学习板上丰富的外设资源及其位置分布情况。

图1 BJ-EPM学习板顶层资源分布及功能框图图2 BJ-EPM学习板底层资源分布及功能框图2.BJ-EPM240学习板基本配置●主芯片使用的是 Altera公司的MAX II系列EPM240T100C5,该芯片有240个逻辑单元,等效宏单元192个,资源比较丰富,内有8Kbit Flash的存储空间。

●50MHz有源晶振,作为系统主时钟。

●低电平复位按键,使用EPM240的全局复位管脚。

●8色VGA接口1个,让大家掌握电脑显示器的驱动原理。

●RS232串口1个,通过串口调试助手轻松实现UART通信协议。

●PS/2 接口1个,实现键盘解码,配合串口调试助手在PC机上显示键值。

●70ns快速读写的SRAM芯片IS62LV256-70U,具有32KB存储空间,让大家熟悉SRAM的读写操作。

●EEPROM 芯片AT24C02,让大家熟悉使用verilog进行I2C通信。

●4个独立按键,进行verilog脉冲采样和按键消抖控制。

●4个流水灯,配合4位按键进行Johnson计数器实验。

●蜂鸣器,实现简单的分频计数器。

●2位数码管,使用其进行计数实验。

实验一 原理图输入设计

实验一 原理图输入设计一、实验目的1.熟悉QuartusII 9.1软件的使用。

2.通过半加器的设计,让学生掌握原理图输入的设计方法。

3.初步了解可编程器件设计的全过程。

二、设计原理计算机中数的操作都是以二进制进位的,最基本的运算就是加法运算。

按照进位是否加入,加法器分为半加器和全加器电路两种。

计算机中的异或指令的功能就是求两个操作数各位的半加和。

一位半加器有两个输入、输出,如图1-1。

图1-1 一位半加器示意图表1-1 半加器真值表输入输出Bi Ai Hi Ci0 0 0 0 0 1 1 0 1 0 1 0 1 1 0 1一个半加大路的真值表如表1-1所示,根据真值表可得到半加器的函数表达式:Hi Ai Bi Ai Bi Ai Bi =∙+∙=⊕ Bi Ai Ci ∙=三、程序设计.按照表1-1半加器的电路图添加器件并连线。

要想实现半加器的功能,需在图上添加一个二输入与非门及一个二输入异或门共同组成一个半加器,同时要添加4位功能选择位M[3..0]并设置状态为0001,使得16位拨码开关接到16位数据总线上。

半加器原理图如下:四、程序分析输入输出Bi Ai Hi Ci0 0 0 00 1 1 01 0 1 01 1 0 1由表可知,Hi与Ai,Bi的关系满足异或关系,Ci与Ai,Bi的关系是与的关系。

五程序调试1.编译过程中出现Error: The core supply voltage value of '1.0V' is illegal for the currently,需要简单修改一下*.qsf文件,找到“set_global_assignment - name NOMINAL_CORE_SUPPLY_VOLTAGE”这一行代码,把里面的1.0V改成1.2V。

并保存*.qsf文件。

再次编译,程序无错误。

2添加管脚信息,综合完成后,网表信息会生成。

选择Assignments/Pin Planner进行管脚锁定,锁定所有的输入输出管脚。

FPGA固化程序(ASP模式)下载

主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式:AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS 系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。

使用Altera串行配置器件来完成。

Cyclone期间处于主动地位,配置期间处于从属地位。

配置数据通过DATA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

(见附图)PS则由外部计算机或控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

(见附图)JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

AS PS JTAG的区别:AS模式: 烧到FPGA的配置芯片里保存的,FPGA器件每次上电时,作为控制器从配置器件EPCS主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA 的编程;PS模式:EPCS作为控制器件,把FPGA当做存储器,把数据写人到FPGA中,实现对FPGA的编程。

该模式可以实现对FPGA在线可编程;JTAG:直接烧到FPGA里面的,由于是SRAM,断电后要重烧;.pof文件可以通过AS方式下载(保证byteblasterII/usb blaster连接正确);.sof文件或者转换的.jic可以通过JTAG方式下载。

FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。

在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。

在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

JTAG测试介绍PPT课件

图2 所示是边界扫描测试应用的示意图。为了测试两个J TAG 设备的连接,首先将J TAG 设备1某个输出测试脚的BSC 置为高或 低电平,输出至NDO ,然后,让J TAG设备2 的输入测试脚来捕获 (capture)从管脚输入的NDI 值,再通过测试数据通道将捕获到的数 据输出至TDO ,对比测试结果,即可快速准确的判断这两脚是否连接 可靠

JTAG测试的两大优点:

1、方便芯片的故障定位,迅速准确地测试两 个芯片管脚的连接是否可靠,提高测试检验 效率。

2、具有J TAG接口的芯片,内置一些预先定 义好的功能模式,通过边界扫描通道来使芯 片处于某个特定的功能模式,以提高系统控 制的灵活性和方便系统设计。

边界扫描

边界扫描技术的基本思想是在靠近芯片的 输入输出管脚上增加一个移位寄存器单元。 因为这些移位寄存器单元都分布在芯片的 边界上(周围),所以被称为边界扫描寄 存器(Boundary-Scan Register Cell)。

(PASS)

CAPTURE Test The CAPTURE is a fixed value from the INSTRUCTION REGISTER. It is used to check the TDI -> TDO and the TCK and TMS connections. The FLAG is added to test the connection from TDI of the tester to the board.

如上所述,TAP 控制器是边界扫描测试在TCK和TMS 的控制 下,可以选择使用指令寄存器扫描或数据寄存器扫描,以及控 制边界扫描测试的各个状态。TMS 和TDI是在TCK 的上跳 沿被采样, TDO 是在TCK 的下降沿变化。

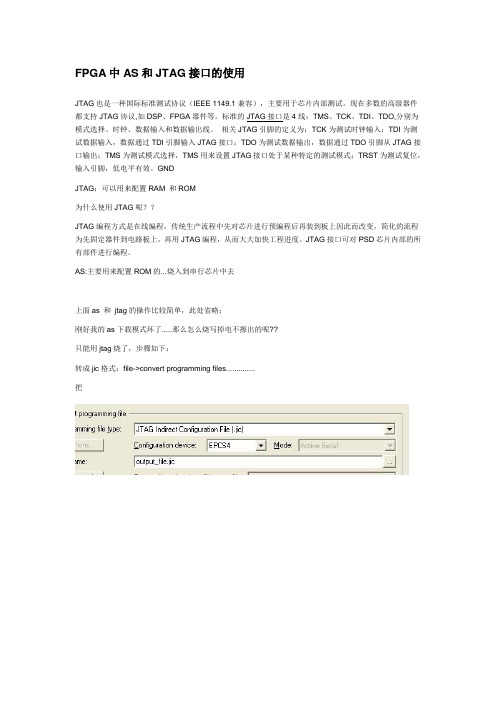

FPGA中AS和JTAG接口的使用

FPGA中AS和JTAG接口的使用

JTAG也是一种国际标准测试协议(IEEE 1149.1兼容),主要用于芯片内部测试。

现在多数的高级器件都支持JTAG协议,如DSP、FPGA器件等。

标准的JTAG接口是4线:TMS、TCK、TDI、TDO,分别为模式选择、时钟、数据输入和数据输出线。

相关JTAG引脚的定义为:TCK为测试时钟输入;TDI为测试数据输入,数据通过TDI引脚输入JTAG接口;TDO为测试数据输出,数据通过TDO引脚从JTAG接口输出;TMS为测试模式选择,TMS用来设置JTAG接口处于某种特定的测试模式;TRST为测试复位,输入引脚,低电平有效。

GND

JTAG:可以用来配置RAM 和ROM

为什么使用JTAG呢??

JTAG编程方式是在线编程,传统生产流程中先对芯片进行预编程后再装到板上因此而改变,简化的流程为先固定器件到电路板上,再用JTAG编程,从而大大加快工程进度。

JTAG接口可对PSD芯片内部的所有部件进行编程。

AS:主要用来配置ROM的...烧入到串行芯片中去

上面as 和jtag的操作比较简单,此处省略;

刚好我的as下载模式坏了.....那么怎么烧写掉电不擦出的呢??

只能用jtag烧了,步骤如下:

转成jic格式:file->convert programming files..............

把

然后进行device的选择:

successfully了吧......嘻嘻.........。

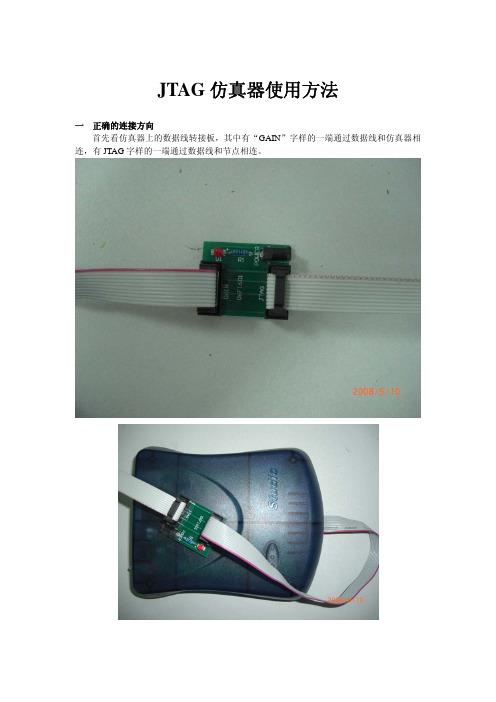

JTAG仿真器使用方法_gz

JTAG仿真器使用方法

一正确的连接方向

首先看仿真器上的数据线转接板,其中有“GAIN”字样的一端通过数据线和仿真器相连,有JTAG字样的一端通过数据线和节点相连。

二通过串口线把PC和仿真器连接起来

三连接电源,电源要插在转接板上注意:当使用外接电源时,节点的开关不要打开。

四连接节点

注意细节,数据线和节点连接时,凸起的部分朝向节点内部,如下图。

因为数据线的原因,如果仿真器找不到节点,可以把突起部分朝外,再连接。

五烧写程序

当节点正确连接后,打开avrstudio烧写程序。

步骤如下:

1 打开avrstudio,这里推荐avrstudio4.12,会弹出一个对话框,点击“cancel”

2 在如下界面上点击“CON”图标

3 点击“CON”图标后,在弹出的对话框中做如下选择

选择完毕,点击“connect”按钮。

4 正确连接后会弹出如下界面

图片中最下面的提示信息“JTAG ICE found on COM1”表示,仿真器找到了节点。

图片最上方“NO device selected”表示没有选中设备。

5 在NO device selected”中选择128芯片

6 选择好设备型号后就可以进行编程了,点击下面图片的按钮,选择要烧写的程序。

7 点击“Program”按钮即可把程序烧写到节点里了。

大西瓜FPGA开发板使用手册

该开发板的元器件采用纯机器焊接,保证在焊接质量上不存在任何的隐患!!!一、注意事项1、外接电源该开发板配套一条DC-5V的USB转公头的电源线,用来外接电脑的USB。

如果使用其他电源,请您先确认是否是5V输入,以免烧坏开发板!开发板电源接口如下:2、JTAG和AS下载JTAG和AS下载器切勿带电拔插,不然很容易烧坏FPGA的下载引脚和配置芯片。

请大家一定要注意,为了您的利益,切记切记!!!一定要先关闭了电源开关,然后再拔插JTAG 和AS接口。

AS下载配置芯片:采用EPSC1,该配置芯片存储量为1M二、开发板硬件资源1、硬件资源介绍为了让FPGA开发板的电源更为稳定,我们采用多个104电容进行滤波,保证电源的稳定。

作为一块FPGA开发板,FPGA的IO口资源是十分丰富的,由此我们将FPGA的IO口全部引出并详细地标注了各个IO口的序号,方便您日后扩接其他模块或者参与电子设计大赛时作为一块比赛用板。

2、各个硬件模块介绍及其使用(1)LED灯:8个红色高亮LED灯在使用该模块时根据原理图,配置好引脚就可以用了。

原理图如下:实验现象:(2)8位共阳数码管8位数码管采用的是共阳,用户在使用的时候要注意驱动时要采用低电平。

原理图:实验现象:(3)独立按键原理图板上实物:(4)蜂鸣器原理图:板上实物:(5)串口(MAX232)原理图:板上实物:在RXD和TXD上各上拉一个LED,用于显示串口通信时是否有数据传送。

(6)PS2原理图:板上实物:(7)VGA原理图:RGB分别有三种电阻模式输入:1K、470、240。

板上实物:(8)IIC-AT24C04 原理图板上实物(9)LCD1602/12864接口原理图:实验现象:(10)DAC-TLC5615:14M10位串行数模转换芯片。

原理图实验现象:(11)ADC-TLC549:4M8位串行模数转换芯片。

原理图:实验现象:三、开发板配套资料(1)自制开发板教程(定期更新)数字实验教程:(2)相关资料(3)电子书籍推荐书籍:《EDA 技术实用教程-Verilog (第四版)》潘松、黄继业,科学出版社《Verilog 数字系统设计教程》夏宇闻北京航空航天大学出版 Verilog HDL 数字设计与综合《深入浅出玩转FPGA》吴厚航北京航空航天大学出版Altera公司推荐FPGA/CPLD培训教材•Altera FPGA/CPLD设计(基础篇和高级篇)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

AS和JTAG配置方式演示实验

与CPLD不同,FPGA是基于RAM结构的,所以FPGA每次上电都需要重新配置,而不像CPLD那样能够直接运行固化在芯片内的代码。

大家对JTAG的下载也许都很熟悉了,但是转到FPGA的时候多多少少有些迷惑。

怎么出现配置芯片了呢?为什么有不同的下载电缆,不同的下载模式呢?

FPGA器件有三类配置下载方式:主动配置方式(AS)、被动配置方式(PS)和最常用的基于JTAG的配置方式。

AS配置方式:

AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列配置芯片如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone/ Cyclone II/ Cyclone III系列。

使用Altera串行配置器件来完成,Cyclone器件处于主动地位,配置器件处于从属地位。

配置数据通过DATA0引脚送入FPGA。

配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。

PS配置方式:

PS则由外部计算机或其它控制器控制配置过程。

通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。

配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。

JTAG配置方式:

JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 1149.1联合边界扫

描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。

FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。

在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。

在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中FPGA配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。

实际操作:

下面就SF-EP1C3V2开发板平台上如何进行AS以及JTAG模式的配置下载进行说明。

altera 的下载线一般有Blaster II/Blaster MV/USB blaster,一般的Blaster II/USB blaster下载线都可以配置JTAG模式和AS模式,而Blaster MV则无法配置AS模式,只能配置JTAG模式。

特权同学配套SF-EP1C的下载线大都是Blaster II(有些板子可能给配套了Blaster MV),也可能您购买了USB blaster,不管您拿到哪一种线都不要紧,它都能够配置代码到FPGA或者配置芯片中。

如果AS方式下载不了,那么不意味着无法将代码烧录到配置芯片中(EPCS1),您同样可以使用JTAG方式把代码下载到配置芯片中,具体操作步骤查看相关文档。

对于用户而言,这三种线最大的差别只在下载的速度上,不过再慢也就是多等几秒的事。

AS模式

该模式主要是将工程编译生成的.pof烧录到串行配置芯片(我们使用的是EPCS1)中,然后FPGA上电后从该配置芯片读取数据进行在线的一个重配置过程。

该模式下需要做如下工作:

1.将Blaster II或者USB Blaster下载线连接到开发板的P1座上;

2.给开发板上电,同时开启johnsonverilog目录下的工程;

3.点击菜单栏的Programmer,进入下载配置页面;

4.出现如下界面。

1)如果没有第一次进入该页面没有显示你的下载线为ByteBlasterII或者USB blaster,那么你需要先点击Hardware Setup进入一个对话框里选择你的下载线。

2)选择Mode后的下拉框为Active Serial Programming

3)点击Add File…,在弹出对话框选择该工程目录下的.pof文件,确定。

5.勾选Program/Configure。

然后点击Start,等待Progress到100%。

6.给开发板下电,拔下下载线(记住,一定要拔下来)。

然后重新给开发板上电,你

可以看到你下载的流水灯跑起来了。

7.你可以试试多次上电下电,代码还是流水灯。

你按下RE_COF键进行FPGA的重新

配置,那么还是流水灯在跑。

JTAG模式

JTAG模式主要是将工程编译生成的.sof烧录到FPGA中,如果下载完成后断电重新上电或者你按下RE_COF键进行FPGA的重新配置,那么你会看到你刚下载进行的代码不见了。

该模式下需要做如下工作:

1.将Blaster II或者USB Blaster下载线连接到开发板的P2座上;

2.给开发板上电,同时开启johnsonverilog目录下的工程;

3.点击菜单栏的Programmer,进入下载配置页面;

4.出现如下界面。

4)如果没有第一次进入该页面没有显示你的下载线为ByteBlasterII或者USB blaster,那么你需要先点击Hardware Setup进入一个对话框里选择你的下载线;

5)选择Mode后的下拉框为JTAG;

6)点击Add File…,在弹出对话框选择该工程目录下的.sof文件,确定;

5.勾选Program/Configure。

然后点击Start,等待Progress到100%;

6.下载完毕,无需拔下下载线,你可以看到你下载的流水灯跑起来了;

7.你可以试试多次上电下电,或者你按下RE_COF键进行FPGA的重新配置,那么你

的流水灯就不跑了。

从上面的实验过程中,你会发现JTAG的模式下进行的下载时间短暂,而AS方式下下载

的时间长一些。