max_plus2教程、ppt

MaxPlusII简易用户使用入门指南

PPT文档演模板

MaxPlusII简易用户使用入门指南

生成一个图形设计文件

•输入 LPM 符号

lpm (library parameterized megafunction) 符号的输入方法与先前符 号的输入方法相同。 在 Enter Symbol 对话框出现后,在 symbol Libraries 框中选择 “..\maxplus2\max2lib\mega_lpm” 路径。 在 Symbol Files 框中选择您需要的 lpm 符号。 双击参数框 (位于符号的右上角),输入您需要的 lpm 的参数。在 Port Status 框中选择 Unused ,可将您不需门指南

PPT文档演模板

2020/11/2

MaxPlusII简易用户使用入门指南

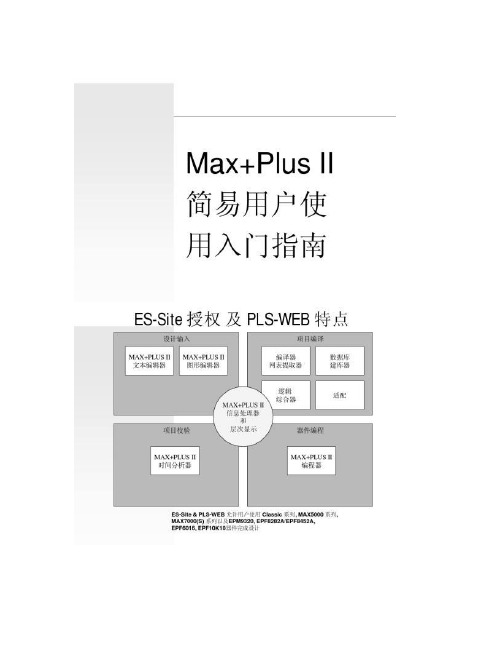

ES-Site 授权 及 PLS-WEB 特点

•设计输入

•项目编译

•MAX+PLUS II •MAX+PLUS II

•文本编辑器

•图形编辑器

•编译器 •网表提取器

•数据库 •建库器

•项目校验

输入 74 系列的符号

MAX+PLUS II 为实现不同的逻辑功能提供了许多符号,如:图元符 号 ,兆功能符号和宏功能符号。在图形编辑器文件中可直接使用以上 符号。74 系列符号的输入方法和上页图元输入的方法相同。 当 Enter Symbol 对话框出现后,在symbol Libraries 对话框中选 择 “..\maxplus2\max2lib\mf”路径。 在 Symbol Files 对话框中,选择您需要的 74 系列符号。

生成一个图形设计文件

输入 Altera 图元

选择工具按钮有效时,在图 形编辑器窗口的空白处单击 鼠标左键以确定输入位置, 然后选择Enter Symbol,或 双击鼠标左键。

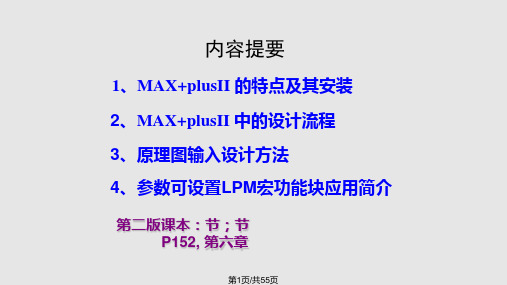

MAX+PLUS II学习课件

设计输入 提供图形、文本和波形编辑器实现图形、AHDL、VHDL、Verilog HDL或波形的输入,也可输入网表文件。 项目编译 提供了一个完全集成的编译器(Compiler),它可直接完成从网 表提取到最后编程文件的生成,包含时序模拟、适配的标准文件。 项目校验 对设计项目的功能、时序进行仿真和时序分析,判断输入输出间 的延迟。 项目编程 将你的设计下载/配臵到你所选择的器件中去。

图形 文件

文本 文件

文本 文件

图形输入 Xilinx

MAX+PLUS II 自身产生 从其他 EDA 工具输入

1.1MAX+plus II 10.2的功能

设计输入总结图

设计文件 支持文件

MAX+PLUS II 符号编辑器

MAX+PLUS II 波形编辑器

.gdf

.wdf

.sym

MAX+PLUS II 图形编辑器

1. 2MAX+plus II 10.2的系统要求

支持的操作系统 Windows 98/Me/2000 以及 Windows xp;

安装所需空间 1Gbytes;

内存要求

可用64MB,推荐内存64MB以上。

返回目录

2013-8-9 武汉工程大学邮科院校区实验中心 11

第二章 Max+PlusII的安装向导

2013-8-9

武汉工程大学邮科院校区实验中心

29

3.2 Max+PlusII的设计流程图

设计说明书

设计输入

修改设计 编译设计文件 综合、适配与优化 定时验证,时序仿真 器件编程/配置 应用系统硬件测试

MAXPLUSⅡ的使用

2.输入设计项目和存盘 输入设计项目和存盘

点击

点击

2.输入设计项目和存盘 输入设计项目和存盘

任一位置双击或 右键单击

2.输入设计项目和存盘 输入设计项目和存盘

可输入所需元件名 如:input,and2, , , Vcc,gnd ,

元件库中的元件

点击

Prim库:基本逻辑元 库 件库, 与门, 件库,如:与门,非门 Mf库:宏功能元件库, 库 宏功能元件库, 如:74161,74138 , Mega_lpm库:可调参 库 可调参 数库,如可调模值的计 数库, 数器, 数器,RAM Edif库:和Mf库类似。 库类似。 库 库类似

6.1 建立波形文件

单击 单击

6.2 输入信号节点

6.2 输入信号节点

单击

单击

单击

6.3 设置波形参量

消去该项以 便能任意设 置输入电平 位置

6.3 设置波形参量

可选10µs以 以 可选 便观察

6.4 为输入信号加上激励

选择某个对象来移动, 复制,剪切等操作 对其赋值

输入或编辑文字

选中某段波形,并直接

6.5 保存仿真波形

单击

6.6 波形仿真

单击

6.7 仿真后的波形

7.包装元件入库 包装元件入库

7.包装元件入库 包装元件入库

单击

8.顶层原理图文件调用底层元件

用户库单击

设定后可看到工程路 径指向

3.将当前设计设为工程 将当前设计设为工程

如果需要设定为工程的文件没有打开: 如果需要设定为工程的文件没有打开:

点击

4. 选定目标器件

单击

该项不要选中

5. 文本编译和排错

5. 文本编译和排错

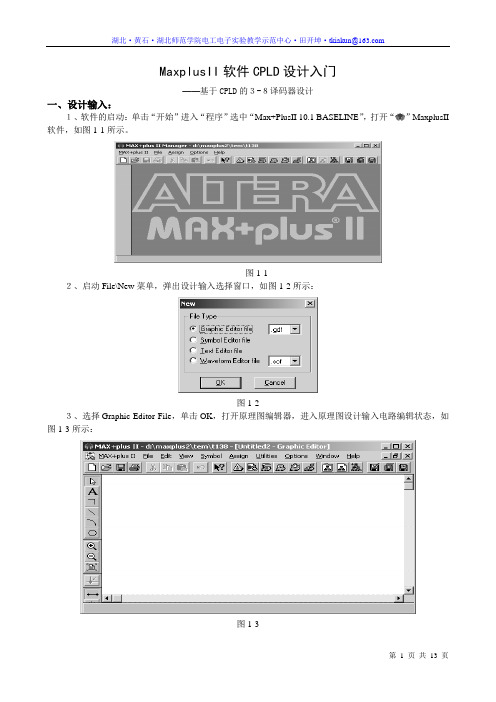

MaxplusII入门

MaxplusII软件CPLD设计入门——基于CPLD的3-8译码器设计一、设计输入:1、软件的启动:单击“开始”进入“程序”选中“Max+PlusII 10.1 BASELINE”,打开“”MaxplusII 软件,如图1-1所示。

图1-12、启动File\New菜单,弹出设计输入选择窗口,如图1-2所示:图1-23、选择Graphic Editor File,单击OK,打开原理图编辑器,进入原理图设计输入电路编辑状态,如图1-3所示:图1-34、设计输入1)放置一个器件在原理图上a、在原理图的空白处双击鼠标左键,出现图1-4。

图1-4b、在光标处输入元件名称(如:input,output,and2,and3,nand2,or2,not,xor,dff等)或用鼠标点击库元件,按下OK即可。

c、如果安放相同的元件,只要按住Ctrl键,同时用鼠标按左键拖动该元件复制即可。

d、一个完整的电路包括:输入端口input、电路元件集合、输出端口output。

e、图1-5为3-8译码器元件安放结果。

图1-52)添加连线到器件的引脚上:把鼠标移到元件引脚附近,则鼠标自动由箭头变为十字,按住鼠标左键拖动,即可画出连线。

3-8译码器原理图连线后如图1-6所示。

图1-63)标记输入/输出端口属性分别双击输入端口的“PINNAME”,当变成黑色时,即可输入标记符并回车确认;输出端口标记方法类似。

本译码器的三输入端分别标记为:A、B、C;其八输出端分别为:D0、D1、D2、D3、D4、D5、D6、D7。

如图1-7所示。

图1-74)保存原理图单击保存按钮图表,对于新建文件,出现类似文件管理器图框,请选择保存路径/文件名称保存原理图,原理图的扩展名为.gdf,本实验中取名为test1.gdf。

(注意:新建项目,一定要建立一个专门的文件夹保存项目文件,在编译过程中将有大量新文件产生。

)5)点击File\Project\Set project to current File设置此项目为当前项目文件,如图1-8所示。

第一章MAXPLUSII图形输入方式-精选

EDA技术讲义

将他们连接 成半加器

将所需元件全部调入原理图编辑窗口

连接好的原理图

首先点击这里 再点击这里

EDA技术讲义

文件名取为:h_adder.gdf 注意:要存在自己建立的 文件夹中

连接好原理图并存盘

注意选择存储位置

步骤3:将设计项目设置成工程文件(PROJECT)

最后注意此路 径指向的改变

步骤7:编程下载

在编程窗打开 的情况下选择 下载方式设置

EDA技术讲义

(1) 下载方式设定。 选择此项下 载方式

设置编程下载方式

(2) 下载

步骤7:编程下载

(1) 下载方式设定。

EDA技术讲义

下载(配置) 成功

向CPLD/FPGA器件中下载配置文件 图4-18 设置编程下载方式

步骤8:设计顶层文件

EDA技术讲义

利用鼠标左键选定引脚

鼠标左键选定要分配的管脚,拖动鼠标到要放置的位置,松开鼠标左键,即可 完成一个引脚的手动分配,依次放置所有引脚,即可完成引脚的手动分配。

EDA技术讲义

再编译一次, 将引脚信息编译进去

选择编程器, 准备将设计 好的半加器

文件下载到目 器件中去

编程窗口

EDA技术讲义

SNF文件中 的信号节点

点击“LIST” 从SNF文件中输入设计文件的信号节点

(2) 输入信号节点

EDA技术讲义

用此键选择左窗 中需要的信号 进入右窗

最后点击“OK”

列出并选择需要观察的信号节点

(3) 设置波形参量

EDA技术讲义

消去这里的勾,以便 方便设置输入电平

图4-9 列出并选择需要观察的信号节点

第1章 MAX+PLUS II 图形输入方式

Maxplus_Ⅱ基本操作方法

附录:Maxplus Ⅱ基本操作方法——图形输入法利用EDA工具进行原理图输入设计的优点是,设计者能利用原有的电路知识迅速入门,完成较大规模的电路系统设计,而不必具备许多诸如编程技术、硬件语言等新知识。

MAX+plusII提供了功能强大,直观便捷和操作灵活的原理图输入设计功能,同时还配备了适用于各种需要的元件库,其中包含基本逻辑元件库(如与非门、反向器、D触发器等)、宏功能元件(包含了几乎所有74系列的器件),以及功能强大,性能良好的类似于IP Core的巨功能块LPM库。

但更为重要的是,MAX+plusII还提供了原理图输入多层次设计功能,使得用户能设计更大规模的电路系统,以及使用方便精度良好的时序仿真器。

以传统的数字电路实验相比为例,MAX+plusII提供原理图输入设计功能具有显著的优势:∙能进行任意层次的数字系统设计。

传统的数字电路实验只能完成单一层次的设计,使得设计者无法了解和实现多层次的硬件数字系统设计;∙对系统中的任一层次,或任一元件的功能能进行精确的时序仿真,精度达0.1ns ,因此能发现一切对系统可能产生不良影响的竞争冒险现象;∙通过时序仿真,能对迅速定位电路系统的错误所在,并随时纠正;∙能对设计方案作随时更改,并储存入档设计过程中所有的电路和测试文件;∙通过编译和编程下载,能在FPGA或CPLD上对设计项目随时进行硬件测试验证。

∙如果使用FPGA和配置编程方式,将不会有如何器件损坏和损耗;∙符合现代电子设计技术规范。

传统的数字电路实验利用手工连线的方法完成元件连接,容易对学习者产生误导,以为只要将元件间的引脚用引线按电路图连上即可,而不必顾及引线的长短、粗细、弯曲方式、可能产生的分布电感和电容效应以及电磁兼容性等等十分重要的问题。

以下将以一位全加器的设计为例详细介绍原理图输入设计方法,但应该更多地关注设计流程,因为除了最初的图形编辑输入外,其它处理流程都与文本(如VHDL文件)输入设计完全一致。

MAXPLUS2使用教程

MAXPLUS2使用教程MAXPLUS II 基本使用之二授课时间:2课时授课方式:演示+讲授目的要求:掌握MAXPLUS II软件的基本使用重难点: MAXPLUS II软件的基本使用一、MAXPLUS II的基本操作。

我们以一个二选一的数据选择器的设计为例,通过图形和Verilog-HDL两种方式进行原文件的编辑。

设计实体名为21MUX,有三个输入端A,B,S,分别为数据通路A,数据通路B和选择控制S;有一个输出端Y,为数据输出端。

操作步骤:1.图形方式输入原文件运行MAXPLUS II后,单击菜单“File>New…”,在出现的新建文件窗口中,选择“Graphic Editor file”,在其后的选择框中选择“.gdf ”为扩展名。

单击OK按钮,启动MAXPLUS II图形编辑器。

在上面的图形编辑框中单击右键,在弹出的快捷菜单中选择“Enter Symbol… ”命令,进入Enter Symbol窗口。

在Symbol Library框中双击maxplus2\max2lib\mf所在路径,然后在Symbol Files框中选择21MUX,单击OK按钮。

这时,图形编辑框中出现了一个红框的标名为21MUX的元件。

这就是MAXPLUS II库中自带的一个二选一数据选择器的元件。

按相同方法打开Enter Symbol窗口,双击maxplus2\max2lib\prim所在路径,然后在Symbol Files框中选择input,单击OK按钮。

这时窗口中出现一个红框的输入引脚元件。

按上述方法再输入一个输出引脚元件,其元件名为output。

1接着在按住ctrl键和鼠标左键的同时拖动已有的那个输入引脚元件,在窗口中任意空白处放开。

这样操作一次,就得到已有元件的一个拷贝。

我们在原理图上设置三个输入引脚和一个输出引脚,但这时各输入引脚名称相同,无法区分。

给引脚命名的方法是,用鼠标左键双击引脚的默认引脚名“PIN_NAME”,然后由键盘输入自己的引脚名。

Max Plus_II指南.

器件编程利用 Altera 编程器对 MAX 和 EPROM 系列器件进行编程 1. 在Option 菜单内选择 Hardware Setup 项,然后在 Hardware Type 对话框内选择适当的Altera 编程器,最后按下 OK按钮。

2. 在编程器窗口中,检查您选择的编程文件和器件是否正确。

在对 MAX 和 EPROM 器件进行编程时,要用后缀名是.pof 的文件. 如果选择的编程文件不正确,可在 File 菜单中选择 Select Programming File 命令选择您的编程文件。

3. 将您的器件插到编程插座中。

4. 按下 Program 按钮。

编程器将检查器件,并将您的项目编程到器件中,而且还将检查器件中的内容是否正确。

器件编程通过 JTAG 实现在系统编程 n 一个编程目标文件(.pof可以通过ByteBlaster 直接编程到器件中。

1.编译一个项目, MAX+PLUS II 编译器将自动产生用于 MAX 器件的编程目标文件。

2. 将 ByteBlaster电缆的一端与微机的并行口相连,另一端10针阴级头与装可编程逻辑器件的 PCB板上的阳级头插座相连。

该 PCB板还必须为 ByteBlaster电缆提供电源。

3. 打开 MAX+PLUS II 编程器。

4. 在 Options 菜单中选择 Hardware Setup 命令. 将出现 Hardware Setup 窗口 7. 按下 OK按钮 5. 在下拉条中选择 ByteBlaster 6. 指定配置时使用的并行口器件编程设置在系统编程链 8. 在 JTAG 菜单中打开 Multi-Device JTAG-Chain 并选择 Multi-Device JTAG Chain Setup 项,进行多个器件的 JTAG 链的设置。

对话框如下所示。

9. 选择 Select Programming File 并选出您的编程文件。

MAX+PlusII实验教程PPT

2.1 原理图输入

总线绘制:总线名与分支名必须一一对应

第三章 设计进阶

3.1 MAX+plusII环境设置

用户库设置 Options/User Libraries

3.1 MAX+plusII环境设置

参数设置 Options/Preferences

3.2 MAX+plusII的文件系统

1.3 MAX+plusII设计流程

设定器件。Assign/Device EPM7128SLC84-15

1.3 MAX+plusII设计流程

为功能仿真而编译项目。 MAX+plusII/Compiler或单击

出现下图界面

选择Processing/Functional SNF Extractor

设置完毕添加IO端 口。IO端口名可与 模块端口名不同, 但宽度必须相同。 当IO端口未与模块 端口相连时,模块 端口需引出并添加 信号(节点)名, 且信号名称需与IO 端口一致

第四章 项目编译

4.1 编译过程

Hale Waihona Puke

编译器网表 提取器 数据库建立 器 逻辑综合器 分割器 适配器 时序仿真网 表提取器 装配器

与器件结构无关

界面接口开放

支持多操作平台 高度集成化

1.2 MAX+plusII的安装与卸载

License设置

点击Option/License Setup出现图示对话框 Licensed Features:已授 权功能 Unlicensed Features:未 授权功能 License File or Server Name:License文件选择

MAXplusII教程完整newPPT课件

步骤5:选择目标器件

菜单Assign项 — Device

选择 ACEX1K系列

消去这里的勾, 使所有速度级别的 器件都能显示出来

第20页/共55页

根据实验板上的 目标器件型号选 择,如选EP1K30

步骤6:对工程文件进行编译、综合和适配

菜单MAX+plus II 项— Compiler

调出编译器

第13页/共55页

波形图编辑器, 波形图输入方法, 生成 . scf 文件

(2)打开“Enter Symbol”对话框, 调入元件 方法:菜单命令,鼠标右键,双击鼠标左键

菜单命令: Symbol — Enter Symbol

双击

第14页/共55页

用户自定义库 基本逻辑元件库 常用逻辑宏功能库 参数化的模块库 网表格式的元件库

2、硬件描述语言设计输入

文本编辑器,接受VHDL、Verilog HDL等设计文件

3、波形图设计输入

波形编辑器, 波形输入文件

4、层次设计输入

支持一个设计方案中含有多个层次的设计,每个层次的 设计文件都可以是以不同方式建立的输入文件。

第8页/共55页

步骤1:为本工程创建一个文件夹

文件夹名不能用中文, 且不可带空格。

前前 设设 计计 项项 目目 文文 件件

第52页/共55页

(3)设计文件编辑操作按钮

查查 查 查

字

找找 找 找

体

字字 节 元

选

符符 点 件

择

并

符

替

号

换

字

打 增减

体

开 加小

大

VHDL 缩 缩

小

模 进进

选

板 量量

EDA技术- MAX II工具使用PPT课件

19

4.4 MAX+plusII 原理图输入设计方法 原理图设计方法的基本步骤: 步骤4:选择目标器件并编译

3. 打开编译器

选择编译器

编译窗:此编译器的功能包括网表文件提取、设计文件排错、

逻辑综合、逻辑分配、适配(结构综合)、时序仿真文件提取、

编程下载文件装配等

2021/3/18

20

4.4 MAX+plusII 原理图输入设计方法

原理图设计方法的基本步骤: 5. 加入输入信号

步骤5:时序仿真

2021/3/18

27

4.4 MAX+plusII 原理图输入设计方法

原理图设计方法的基本步骤: 6. 波形文件存盘

步骤5:时序仿真

在 File 菜单中选 择 Save as

输入文件名 默认自动名 后缀 .SCF

最后按 “OK”

2021/3/18

原理图设计方法的基本步骤:

步骤3:将设计项目设置成工程文件(PROJECT)

为了使软件对输入的项目进行处理,必须将设计文件, 如刚输入的h_adder.gdf,设置成Project(顶层文件)

最后注意此路 径指向的改变

首先点击这里 然后选择此项,将当前的原理图设计文件设置成工程(顶层文件)

如果设计文件未打开,选择“File” “Project” “Name”,在弹出的

EDA技术

MAX+plus 开发工具

பைடு நூலகம்

任课教师:安国臣 电子邮箱:

2021/3/18

1

第四部分 MAX+plus 开发工具

本部分首先回顾FPGA/CPLD开发 和ASIC设计的流程,然后分别介绍与这 些设计流程中各环节密切相关的EDA工 具软件,最后就MAX+plusII的基本情 况和EDA重用模块IP作一简述。

MAXPLUSII初步

二、文本输入法

3.4 VHDL文本输入设计方法初步

为设计全加器 新建一个文 件夹作工作库

文件夹名取为 My_prjct 注意,不可 用中文!

编辑输入并保存VHDL源文件

新建一个设 计文件

使用文本输入方 法设计,必须选择 打开文本编辑器

用键盘输入设计 文件:多路选择器 存盘文件名必须 取为:mux21a.vhd

逻辑分隔器

适配器 时序仿真网表文件提取器 装配器

2. 查看适配报告

四、引脚锁定

引脚锁定

1、选择MAX+plus II选项,并单击其中的菜单 项Floorplan Editor。 2、选择上方的“Layout”菜单,在其下拉的菜单 中先消去“Full Screen”的对勾,再选择“Device View”。

图 4-39 Device View窗

3、再次进入“Layout”菜单,在其下拉的菜单中 选择“Current Assignments Floorplan”。

可选择发光管8 作为半加器的 进位输出“co”

可选择发光管8 作为半加器的 和输出“so”

选择实验电路结构图6

可选择键8作为半 加器的输入“a” 选择键8作为半加 器的输入“b”

图4-10

消去这里的勾, 以便方便设置 输入电平

在Options菜单中消去网格对齐Snap to Grid的选择(消去对勾)

(4) 设定仿真时间。

选择END TIME 调整仿真时间 区域。

选择60微秒 比较合适

图4-11 设定仿真时间

(5) 加上输入信号。

用此键改变仿真 区域坐标到合适 位置。 点击‘1’,使拖黑 的电平为高电平

注意,此路径指 向当前的工程!

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

若在实际中碰到异常情况不能安装 及不能正常运行的,请检查你的电脑, 本软件对电脑要求不高,一般硬件上 的问题较少,主要是软件间冲突,或 者安装目录较乱等导致,请优化一下 你的电脑!

返回目录

2016/6/19 湖北众友科技EDA工作室 27

第三章 Max+PlusII的设计流程

波形输入

顶层设计文件可以是 下列格式: .gdf, .tdf, .vhd, .sch, 和.edf

Synopsys, ViewLogic, Mentor Graphics,

等厂商的EDIF文件

.gdf

.wdf

.tdf

.vhd .v

文本 文件

.sch

.edf

.xnf

图形 文件

波形 文件

文本 文件

图形 文件

2016/6/19

湖北众友科技EDA工作室

5

1.1MAX+plus II 10.2的功能

设计输入文件描述图

VHDL/Verilog

MAX+PLUS II 的符号编辑器 MAX+PLUS II 的版图编辑器

AHDL

MAX+PLUS II 的图形编辑器

MAX+PLUS II 的文本编辑器

OrCAD

顶层 文件

定时仿真 网表文件

(.snf)

划分模块

装入模块

指定和配置信息

(.acf)

设计医生

装配模块

编程文件

(.pof, .sof, .jed)

编译器的输入输 出文件描述图

第三方 EDA 仿真和定时文件

(.edo, vo, vho, sdo)

1.1MAX+plus II 10.2的功能

Altera的门阵 列转换工具包

EDIF 标准的 EDA Verilog 设计验证方式: VHDL Cadence SDF Mentor Graphics MAX+PLUS II 编译器

设计规则检查 Logic Modelling Synopsys Viewlogic 其他方式

设计输入

EDIF LPM 及其他

标准 EDA 设计输入: Cadence Mentor Graphics OrCAD Synopsys Viewlogic 其他输入方式

在主界面菜单选择“Option”>“License Setup”菜单(如图1-10所 示),“Browse”选择D:\maxplus2,并选择license.dat为授权文 件,分别点击“OK”后,退出MAX+plus II,到此注册完成。

2016/6/19

湖北众友科技EDA工作室

26

2.8MaxPlusII安装结束

目前MAX+PLUS II软件 最高版本为10.2,关于它的 安装非常简单,只要按照 安装向导安装即可。

一点通

返回目录

2016/6/19 湖北众友科技EDA工作室 12

2.1进入安装界面

(1)进入光盘中MaxPlusII10.2软件的目录,找到并运行 程序 后出现下图安装界面,点击Full/Custom/Flexlm Server按钮。

20

2.3设置安装路径

(4)进入下面窗口,同上,单击 “Next>”。

在max2Key目录安 装了MAX+PLUS II 软件的ACCESS Key Guidelines 系列文件。

2016/6/19

湖北众友科技EDA工作室

21

2.4进行安装

(4)接着出现的窗口一直单击 “Next>”,直到如下图所示开始安装:

17

2.3设置安装路径

(1)进入下面窗口,默认安装路径时,单击 “Next>”。若把软件安 装在D盘,单击“Browse”按钮进行路径设臵。

注:MaxPlusII 软件只识别英文, 建立文件(夹) 及安装路径避免 有中文!

2016/6/19

湖北众友科技EDA工作室

18

2.3设置安装路径

(2)进入下面左边窗口,键入或选择你要安装到的目录,此处所选为 “d:\maxplus2”,然后按“OK”。因该目录不存在,故会出现提示 “是否创建此目录”。选择“是(Y)”。然后返回到右边窗口,单 击 “Next>”。

等一会 儿……

2016/6/19

湖北众友科技EDA工作室

22

2.5第一次运行的注册准备

安装到100%后,将提示成功安装信息等,到此已成功安装 完本软件。在第一次运行时要对软件进行注册才可使用, 故为注册作如下工作: 安装完成后把光盘中 的license.dat 文件 复制到安装目录的 maxplus2目录下,并 去掉只读属性。

2016/6/19

湖北众友科技EDA工作室

31

MaxPlusII软件包含了设计输入、 综合、仿真及硬件配置下载等功 能于一身,集成度高,能完成整 个设计流程,功能强大!

返回目录

2016/6/19 湖北众友科技EDA工作室 28

3.1 Max+PlusII的设计过程图

2016/6/19

湖北众友科技EDA工作室

29

3.2 Max+PlusII的设计流程图

MAX+PLUS II 文本编辑器

.tdf

.vhd

.inc

用户

MAX+PLUS II

.sch

第三方 EDA 工具

.edf.lmf来自.xnf1.1MAX+plus II 10.2的功能

设计编译

通过MAX+plusⅡ编译器,可检查项目是否有错,并对项目进行 逻辑综合,然后配臵到一个ALTERA器件中,同时产生报告文件、 编辑文件和用于时间仿真的输出文件。

设计说明书

设计输入

修改设计 编译设计文件 综合、适配与优化 定时验证,时序仿真 器件编程/配置 应用系统硬件测试

应用系统投产

2016/6/19 湖北众友科技EDA工作室 30

3.3 Max+PlusII设计流程简述

在此简述一下设计流程,将在后面章节实例中进行详细 说明设计流程:

设计输入 提供图形、文本和波形编辑器实现图形、AHDL、VHDL、Verilog HDL或波形的输入,也可输入网表文件。 项目编译 提供了一个完全集成的编译器(Compiler),它可直接完成从网 表提取到最后编程文件的生成,包含时序模拟、适配的标准文件。 项目校验 对设计项目的功能、时序进行仿真和时序分析,判断输入输出间 的延迟。 项目编程 将你的设计下载/配臵到你所选择的器件中去。

1. 2MAX+plus II 10.2的系统要求

支持的操作系统 Windows 98/Me/2000 以及 Windows xp;

安装所需空间 1Gbytes;

内存要求

可用64MB,推荐内存64MB以上。

返回目录

2016/6/19 湖北众友科技EDA工作室 11

第二章 Max+PlusII的安装向导

第三方 EDA 设计文件

(.edf, .sch, .xnf)

映射文件

(.lmf)

功能仿真 网表文件

(.snf)

MAX+PLUS II 设计文件

(.gdf, .tdf, .vhd)

MAX+PLUS II 编译器

编译器网表提取模块 (包含各种网表的阅 读器) 功能、定时或链接 SNF 提取模块 EDIF、 VHDL 和 Verilog Netlist 生成模块 数据库生 成模块 逻辑综合 模块

第一章 Max+PlusII的功能及系统要求

Altera公司的MAX+PLUS II 软件是最易学、最易用的可编程逻辑器 件开发软件。其界面友好,集成化程度高,包含设计综合仿真等。

2016/6/19

湖北众友科技EDA工作室

返回目录 3

1.1MAX+plus II 10.2的功能

独立的运行环境

设计编译 验证和编程

图形 设计输入

定时仿真 逻辑综合 装入器件

文本设计输入 (AHDL, VHDL, Verilog HDL)

功能仿真

多器件划分 多器件仿真 自动错误定位 定时分析 定时驱动编译 器件编程

波形设计输入 Design Entry 分层 设计输入

版图 编辑

1.1MAX+plus II 10.2的功能

所支持的器件有:ACEX1K,EPF10K10, EPF10K10A, EPF10K20, EPF10K30A以及MAX® 7000系列(含MAX7000A, MAX7000AE, MAX7000E, MAX7000S),EPM9320, EPM9320A, EPF8452A, EPF8282A, FLEX 6000/A 系列,MAX 5000系列,ClassicTM系列。

2016/6/19

湖北众友科技EDA工作室

19

2.3设置安装路径

(3)进入下面窗口,由于前面设臵好路径,已改为D盘(最好保持一 致,无须改变),单击 “Next>”。

在max2work目录安装 了许多设计的源代码 /图,如一些VHDL, Verilog HDL的例子。

2016/6/19

湖北众友科技EDA工作室

设计校验

通过MAX+plusⅡ的定时分析器进行时序分析、功能仿真、时序 仿真和波形分析,生成一些标准文件为其他EDA工具使用。

器件编程(Programming)和配臵(Cofiguration) 在线帮助

2016/6/19

湖北众友科技EDA工作室

8

1.1MAX+plus II 10.2的功能