数字电子技术基础 ch06-2

数字电子技术基础 (2)

(3)按照电路的结构和工作原理的不同:数字电路可分为组 合逻辑电路和时序逻辑电路两类。组合逻辑电路没有记忆功 能,其输出信号只与当时的输入信号有关,而与电路以前的 状态无关。时序逻辑电路具有记忆功能,其输出信号不仅和 当时的输入信号有关,而且与电路以前的状态有关。

各数位的权编辑p是pt 16的幂

13

结论

①一般地,N进制需要用到N个数码,基数是N;运算规 律为逢N进一。

②如果一个N进制数M包含n位整数和m位小数,即 (an-1 an-2 … a1 a0 ·a-1 a-2 … a-m)2

则该数的权展开式为: (M)2 = an-1×Nn-1 + an-2 ×Nn-2 + … +a1×N1+ a0 ×N0

+a-1 ×N-1+a-2 ×N-2+… +a-m×N-m ③由权展开式很容易将一个N进制数转换为十进制数。

编辑ppt

14

十进制数

0 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15

几种进制数之间的对应关系

二进制数

八进制数

00000

0

00001

1

00010

2

00011

3

00100

u

t

模拟信号波形

对模拟信号进行传输、 处理的电子线路称为 模拟电路。

t

数字信号波形

对数字信号进行传输、 处理的电子线路称为 数字电路。

编辑ppt

5

1.1.2 数字电路的的特点与分类

1、数字电路的特点

(1)工作信号是二进制的数字信号,在时间上和 数值上是离散的(不连续),反映在电路上就是 低电平和高电平两种状态(即0和1两个逻辑值)。

数字电路技术基础 全 清华大学出版社

BCD码除842l码外,常用的还有2421码、余3码、 余3循环码、BCD格雷码等等

《数字电子技术基础》

1.2 基本逻辑函数及运算定律

基本概念 逻辑:事物的因果关系 逻辑运算的数学基础:逻辑代数 在二值逻辑中的变量取值: 0/1 逻辑代数中的变量称为逻辑变量,用字

1

11

UH

00

0

UL

0

0 t

图1.1.3 矩形脉冲数字表示方法

1.1.2 数制和码制

《数字电子技术基础》

一、数制 ①每一位的构成 ②从低位向高位的进位规则

我们常用到的: 十进制,二进制,八进制,十六进制

《数字电子技术基础》

十进制,二进制,八进制,十六进制

逢二进一 逢八进一

逢十进一

逢十六进一

《数字电子技术基础》

(a)

(b)

(c)

图1.1.1几种常见的脉冲波形

(d)

脉冲信号的参数

《数字电子技术基础》

Um tW

T

(a)

0.9Um

0.5Um

Um

0.1Um tr

tW tf T

(b)

图1.1.2 矩形脉冲参数

《数字电子技术基础》

矩形脉冲数字表示法

通常规定:0表示矩形脉冲的低电平;1表 示矩形脉冲的高电平,如图1.1.3波形所示。

十进制转换为二进制

2 129

余1

k0

2 64

余0

k1

2 32

余0

k2

2 16

余0

k3

28

余0

k4

24

余0

数字电路技术基础(全)-清华大学出版社

• 反演规则 -------对任一逻辑式

变换顺序 先括号, 然后乘,最后加

YY

, ,0 1,1 0, 原变量 反变量 反变量 原变量

不属于单个变量的 上的反号保留不变

《数字电子技术基础》

• 应用举例:

Y A( B C ) CD Y ( A BC )( C D ) AC BC A D BC D

《数字电子技术基础》

最小项的编号:

最小项

ABC ABC A BC A BC AB C AB C AB C ABC

取值 ABC 000 001 010 011 100 101 110 111

对应 10进制数 0 1 2 3 4 5 6 7

编号

m0 m1 m2 m3 m4 m5 m6 m7

《数字电子技术基础》

0011 )8421BCD

(0100101001 1000 )8421-BCD (1298 )D

BCD码除842l码外,常用的还有2421码、余3码、 余3循环码、BCD格雷码等等

《数字电子技术基础》

1.2 基本逻辑函数及运算定律

基本概念 逻辑:事物的因果关系 逻辑运算的数学基础:逻辑代数 在二值逻辑中的变量取值: 0/1 逻辑代数中的变量称为逻辑变量,用字 母A、B、C、…表示。其取值只有0或者l两 种。这里的0和1不代表数量大小,而表示两 种不同的逻辑状态,如,电平的高、低;晶 体管的导通、截止;事件的真、假等等。

1.2.2 逻辑代数的运算定律及规则

一、运算定律

证明方法:推演 真值 表

《数字电子技术基础》

用真值表证明 A B A B 的正确性。

《数字电子技术基础》

二、逻辑代数的常用公式

夏路易---数字电子技术基础课后答案

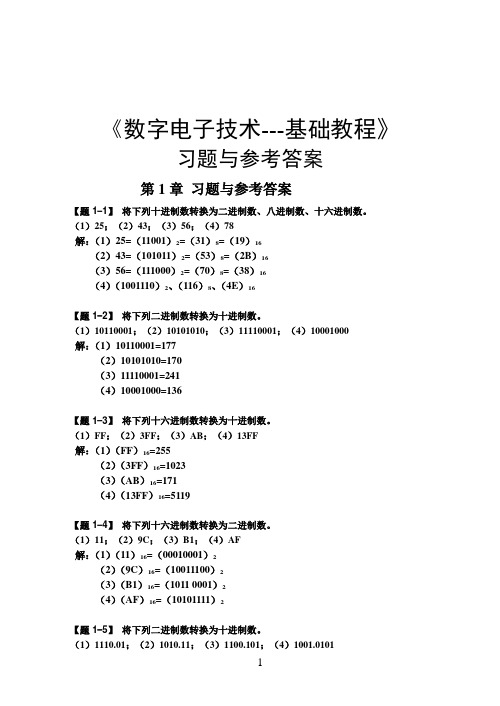

《数字电子技术---基础教程》习题与参考答案第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础2

二极管开关的转换过程

开通时间ton 当输入电压uI,由UIL跳变到UIH时,二极管D要经过导通延迟时间td、上升

时间tr之后,才能由截止状态转换到导通状态。其原因在于,当uI正跳变时, 只有当PN结中电荷量减少,PN结才由反偏转换到正偏,也即Cj放电,CD充 电

关断时间toff 当输人电压uI。由UIH跳变到UIL时,二极管D经过存储时间ts、下降时间

三极管临界饱和时的基极电流:

IBS Vc R u cc CE S1 1 2 0 0.2 3 0 m A 0.0m 6 A

因为iB>IBS,三极管工作在深度饱和状态。输出电压:

uo=UCES=0.3V 静态开关特性

截止状态

Rb +

+VCC

b c Rc

+

ui=UIL<0.5V

uo=+VCC

-

e

-

饱和状态

iC (mA) 直流负载线

VCC Q2 Rc

Q

80μA 60μA 40μA 20μA

2.3k iB

Q1 iB=0

Ω

0 UCES

VCC uCE(V)

输出特性曲线

①ui=UIL=-2V时,三极管截止,基极电流: ib≈0,ic≈0,uo≈Vcc=12V

②ui=UIH=3V时,三极管导通,基极电流:

iB

30.7mA 1mA 2.3

+VCC Rc iC

Rb b c uo

iB(μA)

iC (mA) 直流负载线

VCC Q2 Rc

Q

80μA 60μA 40μA

ui

iB

20μA

e 0 0.5 uBE(V)

0 UCES

Q1 iB=0

数字电子技术基础第2章

AB

1 1 1 0

A B

1 1 1 0

A B

1 0 0 0

AB

1 0 0 0

第2章 逻辑代数基础

2.2.2 三个重要规则

1. 代入规则

任何一个逻辑等式,如果将等式两边所出现的某一变量都

代之以同一逻辑函数,则等式仍然成立,这个规则称为代入 规则。 由于逻辑函数与逻辑变量一样,只有0、1两种取值, 所以代入规则的正确性不难理解。运用代入规则可以扩大基 本定律的运用范围。

第2章 逻辑代数基础

3

异或和同或运算的常用公式如表2.3.3所示。表中的公

式可以利用真值表或前面的公式证明。 表2.3.3 异或、同或运算的常用公式

名称 变量与 常量的 关系 交换律 结合律 分配律 反演律 调换律 奇偶律 异或公式 A 0=A A 1= A A A =1 A B=B A A B C=A (B C) A(B C)=AB AC 同或公式 A A A A A 1=A 0= A A =0 B=B A (B C)=(A C)=(A+B) B) C (A+C)

公式 1 A+1=1 A+0=A A+A=A A+ A =1 A+B=B+A (A+B)+C=A+(B+C) A+BC=(A+B)(B+C)

公式 2 A 0=0 A 1= A A A=A A A =0 A B=B A (A B) C=A (B C) A (B+C)=AB+AC

B A B L

特点:任1 则1, 全0则0

或逻辑表达式: L = A +B

数字电子技术基础第二章逻辑门电路基础[1]

![数字电子技术基础第二章逻辑门电路基础[1]](https://img.taocdn.com/s3/m/b2cf38a4227916888486d7d1.png)

(3)存储时间ts——从输入信号vi下跳变的瞬间 开始,到集电极电流iC下降到0.9ICS所需的时 间。

(4)下降时间tf——集电极电流从0.9ICS下降 到0.1ICS所需的时间。

数字电子技术基础第二章逻辑门电路 基础[1]

l (一)双极型三极管的静态开关特性

u 判断三极管工作状态的解题思路:

Ø (1)把三极管从电路中拿走,在此电路拓扑结构下求三极管 的发射结电压,若发射结反偏或零偏或小于死区电压值,则三 极管截止。若发射结正偏,则三极管可能处于放大状态或处于 饱和状态,需要进一步判断。进入步骤(2)。

Ø (2)把三极管放入电路中,电路的拓扑结构回到从前。假设 三极管处于临界饱和状态(三极管既可以认为是处于饱和状态 也可以认为是处于放大状态,在放大区和饱和区的交界区域, 此时时的三特极征管IC=既ßI有B)饱,和求状此态时时三的极特管征的VC集ES电=极0.临3V界,饱又和有电放流大I状CS 态, 进极而管求的出集基 电极极临可界能饱流和过电的流最大IBS电。流集。电极临界饱和电流ICS是三

PPT文档演模板

数字电子技术基础第二章逻辑门电路 基础[1]

(二)二极管的动态开关特性

•给二极管电路加入一个方波信号,电流的波形怎样呢?

PPT文档演模板

数字电子技术基础第二章逻辑门电路 基础[1]

PPT文档演模板

•ts为存储时 间 •tt称为渡越时 间 •tre = ts 十 tt 称 为 反 向 恢 复时间

PPT文档演模板

数字电子技术基础第二章逻辑门电路 基础[1]

第一节 二极管、三极管的开关特性

l的动态开关特性

PPT文档演模板

《数字电子技术基础》第六版--门电路-1117省名师优质课赛课获奖课件市赛课一等奖课件

S

D

B

不论D、S间有无电压, 均无法导通,不能导电

第 章 门电路

3.3.1 MOS管旳开关特征 以N沟道增强型为例研究通电情况:

数字电子技术基础 第六版

2、添加垂直电压VGS

形成电场G—B,把衬底中旳电子吸引 到上表面,除复合外,剩余旳电子在 上表面形成了N型层(反型层)为D、 S间旳导通提供了通道。

VGS(th)称为阈值电压(开启电压)

第 章 门电路

数字电子技术基础 第六版

3.3.1 MOS管旳开关特征

MOS管输入特征和输出特征

① 输入特征:直流电流为0,看进去有一种输入电 容CI,对动态有影响。

② 输出特征: iD = f (VDS) 相应不同旳VGS下得一族曲线 。

第 章 门电路

3.3.1 MOS管旳开关特征 输出特征曲线(分三个区域)

第 章 门电路

3.2.2 二极管或门 二极管构成旳门电路旳缺陷

• 电平有偏移 • 带负载能力差

数字电子技术基础 第六版

• 只用于IC内部电路

第 章 门电路

集成门电路

数字电子技术基础 第六版

集成门电路

双极型 TTL (Transistor-Transistor Logic Integrated Circuit)

第 章 门电路

数字电子技术基础 第六版

3.3.2 CMOS反相器旳电路构造和工作原理 三、输入噪声容限

噪声容限--衡量门电路旳抗干扰能力。 噪声容限越大,表白电路抗干扰能力越强。

测试表白:CMOS电路噪声容限VNH=VNL=30%VDD,且 随VDD旳增长而加大。所以能够经过提升VDD来提升噪声容限

第 章 门电路

半导体基础知识(2)

【精品PPT】数字电子技术基础全套课件-2(2024版)

如果以逻辑变量作为输入,以运算结果作为 输出,当输入变量的取值确定之后,输出的取值 便随之而定。输出与输入之间的函数关系称为逻 辑函数。Y=F(A,B,C,…)

二、逻辑函数表示方法 常用逻辑函数的表示方法有:逻辑真值表(真

值表)、逻辑函数式(逻辑式或函数式)、逻辑 图、波形图、卡诺图及硬件描述语言。它们之间 可以相互转换。

( A B)

B A

( A B)

Y (( A B) ( A B)) ( A B)( A B) AB AB

5、波形图→真值表

A

1111

0000

B

11

11

00

00

C 1111

00

Y 11

00 11

0

00 0

ABC Y 00 0 0 t 00 1 1 01 0 1 t 01 1 0 10 0 0 t 10 1 1 11 0 0 t 11 1 1

A断开、B接通,灯不亮。

将开关接通记作1,断开记作0;灯亮记作1,灯 灭记作0。可以作出如下表格来描述与逻辑关系:

功能表

开关 A 开关 B 灯 Y

A

断开 断开

灭

0

断开 闭合

灭

0

1

闭合 断开

灭

1

闭合 闭合 亮

BY

00 真 10 值

00 表

11

两个开关均接通时,灯才会 Y=A•B

亮。逻辑表达式为:

实现与逻辑的电路称为与门。

与门的逻辑符号:

A

&

Y Y=A•B

B

二、或逻辑(或运算)

或逻辑:当决定事件(Y)发生的各种条件A,B,

C,…)中,只要有一个或多个条件具备,事件(Y)

(全)数字电子技术基础课后答案夏路易

《数字电子技术基础教程》习题与参考答案(2010.1)第1章习题与参考答案【题1-1】将下列十进制数转换为二进制数、八进制数、十六进制数。

(1)25;(2)43;(3)56;(4)78解:(1)25=(11001)2=(31)8=(19)16(2)43=(101011)2=(53)8=(2B)16(3)56=(111000)2=(70)8=(38)16(4)(1001110)2、(116)8、(4E)16【题1-2】将下列二进制数转换为十进制数。

(1)10110001;(2)10101010;(3)11110001;(4)10001000 解:(1)10110001=177(2)10101010=170(3)11110001=241(4)10001000=136【题1-3】将下列十六进制数转换为十进制数。

(1)FF;(2)3FF;(3)AB;(4)13FF解:(1)(FF)16=255(2)(3FF)16=1023(3)(AB)16=171(4)(13FF)16=5119【题1-4】将下列十六进制数转换为二进制数。

(1)11;(2)9C;(3)B1;(4)AF解:(1)(11)16=(00010001)2(2)(9C)16=(10011100)2(3)(B1)16=(1011 0001)2(4)(AF)16=(10101111)2【题1-5】将下列二进制数转换为十进制数。

(1)1110.01;(2)1010.11;(3)1100.101;(4)1001.0101 解:(1)(1110.01)2=14.25(2)(1010.11)2=10.75(3)(1001.0101)2=9.3125【题1-6】将下列十进制数转换为二进制数。

(1)20.7;(2)10.2;(3)5.8;(4)101.71解:(1)20.7=(10100.1011)2(2)10.2=(1010.0011)2(3)5.8=(101.1100)2(4)101.71=(1100101.1011)2【题1-7】写出下列二进制数的反码与补码(最高位为符号位)。

数字电子技术基础第六章

解 (1) 写出电路方程式 ① 时钟方程 ② 驱动方程

D2= Q0 Q1

数字电子技术基础第六章

(2) 求电路状态方程

D2= Q0 Q1

数字电子技术基础第六章

(3)列电路状态转换真值表

D2= Q0 Q1

CP2 D2 CP1 D1 CP0 D0

000

00 1

10

0

1

001

0

1

00

1

0

010

00 0

10

Z(Z1,…Zj)

Q(Q1,…Qr)

各信号之间的逻辑关系方程组: Z=F1(X,Qn) Y=F2(X,Qn) Qn+1=F3(Y,Qn)

Y(Y1,…Yr)

输出方程 驱动方程 状态方程

数字电子技术基础第六章

6.1.2 时序逻辑电路的分类

1、从控制时序状态的脉冲源来分: 同步: 存储电路里所有触发器有一个统一的时钟源

数字电子技术基础第六章

例:分析下图逻辑电路。

解:电路中,FF1的时钟CP1未与时钟源CP相连,属异步时序电路。 ⑴ 写各逻辑方程式:

。

① 各触发器的时钟信号逻辑方程: FF0:CP0=CP,上升沿触发; FF1:CP1=Q0,仅当Q0由0→1时,Q1状态才可能改变,否则 Q1 状态保持。 ② 输出方程:

数字电子技术基础第六章

(2)用D触发器实现

数字电子技术基础第六章

例2 试设计一个同步时序电路,要求电路中触发器Q0、Q1、 Q2及输出Y端的信号与CP时钟脉冲信号波形满足下图 所示的时序关系。

解: 据题意可直接由波形图画出电路状态图。

(1) 确定触发器的类型和个数

选择3个上升沿触发的JK 触发器。

数字电子技术基础课件 第6章-2

时序图

驱动方程、状态方程、输出方程、状态转换表、状态转换图均略。 驱动方程、状态方程、输出方程、状态转换表、状态转换图均略。 从时序图可看出是一个八进制计数器

关于同步计数器的传输延时时间问题 同步计数器同样有传输延迟时间, 同步计数器同样有传输延迟时间,但触发器之间无延 而是共同对被计数CLK的延迟。 CLK的延迟 迟,而是共同对被计数CLK的延迟。

方法二:整体置数法 方法二:

小 结

1、计数器分为同步和异步两种,每一种又分为二进制和十进制以及加 计数器分为同步和异步两种, 法和减法计数器。 法和减法计数器。 2、可以用一个或多个十进制计数器组成任意进制的计数器,具体可以 可以用一个或多个十进制计数器组成任意进制的计数器, 采用置零法和置数法。 采用置零法和置数法。

10110 11 + 1 1011100

用T触发器构成的 同步二进制加法计数器

驱动方程

将驱动方程代入如下特性方程得状态方程

状态方程

输出方程

状态转换表

状态转换图

时序图

2、同步二进制减法计数器

10110 0 0 1

用T触发器构成的 同步二进制减法计数器

3、同步十进制 加法计数器

驱动方程

状态方程

第六章

一、概述

时序逻辑电路

二、同步时序逻辑电路的分析方法 第一讲 三、若干常用时序逻辑电路 1、寄存器和移位寄存器

2、计数器

第二讲

四、同步时序逻辑电路的设计方法

第三讲

第六章 计数器

时序逻辑电路

(第二讲) 第二讲)

计数器是典型的时序电路,所谓计数, 计数器是典型的时序电路,所谓计数,就是统计 时钟脉冲(CLK)的个数。还可以用于分频、定时、 时钟脉冲(CLK)的个数。还可以用于分频、定时、 产生节拍脉冲和脉冲序列以及进行数字运算等。 产生节拍脉冲和脉冲序列以及进行数字运算等。

《数字电子技术基础》第六版_第01章_数制和码制

例:

0.8125 2 整数部分= 1 =k 1 1.6250 0.6250 2 整数部分= 1 =k 2 1.2500 0.2500 2 整数部分= 0 =k 3 0.5000 0.5000 2 整数部分= 1 =k 4 1.000

第

章

数制和码制

数字电子技术基础

第六版

1.4二进制数运算

1.4.2 反码、补码和补码运算

二进制数的正、负号也是用0/1表示的。 在定点运算中,最高位为符号位(0为正,1为负) 如 +89 = (0 1011001) -89 = (1 1011001)

第

章

数制和码制

数字电子技术基础

第六版

二进制数的补码: • 最高位为符号位(0为正,1为负) • 正数的补码和它的原码相同 • 负数的补码 = 数值位逐位求反(反码) + 1

第

章

数制和码制

数字电子技术基础

第六版

1.3不同数制间的转换

一、二-十转换

例:

D Ki 2

i

K (0,1)

3 2 1 0 - 1 -2 (1011.01) 1 2 + 0 2 + 1 2 + 1 2 + 0 2 + 1 2 2

=( 11.25)10

第

章

数制和码制

数字电子技术基础

第六版

二、十-二转换

n n 1 n2 1 0 整数部分: ( S )10 kn 2 kn1 2 kn2 2 k1 2 k0 2

2( k n 2 n1 k n1 2 n2 k1 ) k0 同理 k n 2 n1 k n1 2 n 2 k1 2( k n 2 n 2 k n1 2 n3 k 2 ) k1

数字电子技术基础6

•CB555的功能表 输入

输出

RD

VI1

VI2

VO

TD状态

0

低

导通

1

>2VCC/3 >VCC/3

低

导通

1

<2VCC/3 >VCC/3 不变

不变1ຫໍສະໝຸດ <2VCC/3 <VCC/3

高

截止

1

>2VCC/3 <VCC/3

高

截止

•555能在宽电源电压范围内工作,可承受较大的负载电流。

•双极型555定时器的电源电压:5~16v,最大负载电流:200mA

• •单稳态触发器具有下列特点: •(1)电路有一个稳态和一个暂稳态。 •(2)在外来触发脉冲作用下,电路由稳态翻转到暂稳态。 •(3)暂稳态是一个不能长久保持的状态,经过一段时间后, 电路会自动返回到稳态。暂稳态的持续时间与触发脉冲无关, 仅决定于电路本身的参数。

PPT文档演模板

数字电子技术基础6

• 在t1时刻,ui1(uo)由0变为1,于是uo1(ui2)由1变为0,uo2 由0变为1。由于电容电压不能跃变,故ui3必定跟随ui2发生负跳 变。这个低电平保持uo为1,以维持已进入的这个暂稳态。 • 在这个暂稳态期间,uo2(高电平)通过电阻R对电容C充电, 使ui3逐渐上升。在t2时刻,ui3上升到门电路的阈值电压UT,使uo (ui1)由1变为0,uo1(ui2)由0变为1,uo2由1变为0。同样由于 电容电压不能跃变,故ui3跟随ui2发生正跳变。这个高电平保持uo

输出电平的变化滞后于输入,形成回环。

• ②与双稳态触发器和单稳态触发器不同, 施密特触发器属于“电平触发”型电路,不依

赖于边沿陡峭的脉冲。

数字电子技术 1章数字电子技术基础

数字电子技术基础

2、数字电路的分类

(1)按集成度分类:数字电路可分为小规模(SSI,每片 数十器件)、中规模(MSI,每片数百器件)、大规模(LSI, 每片数千器件)和超大规模(VLSI,每片器件数目大于1万) 数字集成电路。集成电路从应用的角度又可分为通用型和专用 型两大类型。

用四位自然二进制码中的前十个码字来表示十进制数码, 因各位的权值依次为8、4、2、1,故称8421 BCD码。

除了8421 BCD码外,常用的码有以下几种: 2421码: 2421码的权值依次为2、4、2、1; 余3码:余3码由8421码加0011得到; 格雷码:格雷码是一种循环码,其特点是任何相邻的两个 码字,仅有一位代码不同,其它位相同。

t

数字信号波形

对数字信号进行传输、 处理的电子线路称为 数字电路。

数字电子技术基础

1.1.2 数字电路的的特点与分类

1、数字电路的特点

(1)工作信号是二进制的数字信号,在时间上和 数值上是离散的(不连续),反映在电路上就是低电 平和高电平两种状态(即0和1两个逻辑值)。

(2)在数字电路中,研究的主要问题是电路的逻 辑功能,即输入信号的状态和输出信号的状态之间的 关系。

2、二进制数与八进制数的相互转换

(1)二进制数转换为八进制数: 将二进制数由小数点开 始,整数部分向左,小数部分向右,每3位分成一组,不够3位 补零,则每组二进制数便是一位八进制数。

【例1.2】 将二进制数001101010.010B转换为等值的八进 制数。

0 0 1 1 0 1 0 1 0 . 0 1 0 = (152.2)O

3、十进制数转换为二进制数

精品文档-数字电子技术基础(刘振庭)-第2章

于逻辑关系:当A、B中只要有一个输入为低电平时,对应的二

极管导通,输出为低电平;只有当A、B同时输入高电平时,输

出才为高电平。所以该电路实现了逻辑与的关系,逻辑表达式

为

Y=A·B

(2-1)

5

第2章 逻 辑 门 电 路 6

第2章 逻 辑 门 电 路 7

第2章 逻 辑 门 电 路

图2.2 3输入与门波形图

2.2.5 74TTL系列集成门电路 1. TTL数字集成电路的国际标准化系列产品 (1) 74系列。 (2) 74H系列。 (3) 74S系列。 (4) 74LS系列。 (5) 74ALS系列。 (6) 74AS系列。 (7) 74F系列。

58

第2章 逻 辑 门 电 路 59

第2章 逻 辑 门 电 路 60

52

第2章 逻 辑 门 电 路

图2.22 三态输出门

53

第2章 逻 辑 门 电 路 54

第2章 逻 辑 门 电 路

图2.23 另一种三态门逻辑符号

55

第2章 逻 辑 门 电 路

图2.24 三态门用于总线传输

56

第2章 逻 辑 门 电 路

图2.25 三态门的应用

57

第2章 逻 辑 门 电 路

8

第2章 逻 辑 门 电 路

2. 二极管或门 或门是一种能够实现“或”运算的逻辑电路。图2.3所示 为二极管或门电路及其逻辑符号,其中A、B为输入变量,Y为 输出变量。

9

第2章 逻 辑 门 电 路 10

第2章 逻 辑 门 电 路

输入和输出的电平关系见表2.3。从表中可知,当A、B中

只要有一个输入高电平时,输出Y即为高电平;只有当A、B都

UOH=5-0.7-0.7≈3.6 V

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

逻辑功能描 述部分,其 顺序是任意的

几种描述方式小结:

•结构描述(门级描述)方式:

一般使用Primitive(内部元件)、自定义的下层模块对电路 描述。主要用于层次化设计中。

•数据流描述方式:

一般使用assign语句描述,主要用于对组合逻辑电路建模。

•行为描述方式:

一般使用下述语句描述,可以对组合、时序逻辑电路建模。 1)initial 语句 2)always 语句 end

6.2 Verilog HDL程序的基本结构

6.2.1 简单Verilog HDL程序实例 6.2.2 Verilog HDL程序的基本结构

6.2.1 简单Verilog HDL程序实例

Verilog使用大约100个预定义的关键词定义该语言的结构 1. VerilogHDL程序由模块构成。每个模块的内容都是嵌在关键词

a b sel

0 1

out

assign out= sel ? b : a;

数 据 流 描 述

endmodule module mux2_1(out, a, b, sel) ; output out; input a, b; input sel;

assign oΒιβλιοθήκη t=(sel & b) | (~sel & a);

S A B

C=AB 6.2.1 半加器逻辑图

/* Behavioral description of a half adder */

module HalfAdder_BH(A, B, Sum, Carry); input A ,B ; output Sum ,Carry ; reg Sum ,Carry ; //声明端口数据类型为寄存器 always @(A or B) begin Sum = A ^ B; //用过程赋值语句描述逻辑功能 Carry = A & B; end endmodule

模块定义的一般语法结构如下:

module 模块名(端口名1, 端口名2, 端口名3,…); 端口类型说明(input, output, inout); 说明部分 参数定义(可选); 数据类型定义(wire, reg等); 实例化低层模块和基本门级元件; 连续赋值语句(assign); 过程块结构(initial和always) 行为描述语句; endmodule

6.2.1 简单Verilog HDL程序实例

/* Dataflow description of a half adder */

module HalfAdder_DF(A, B, Sum, Carry); input A ,B ; A output Sum ,Carry ; B wire A ,B,Sum ,Carry ; assign Sum = A ^ B; assign Carry = A & B; endmodule

数 据 流 描 述

endmodule

例 2选1数据选择器的程序实例

行为描述 module mux2_1(out, a, b, sel) ; output out; input a, b; input sel;

reg out; always @(sel or a or b) always @(sel or a or b) begin if (sel) out = b; else out = a; end begin

not U1(selnot, sel); and U2(a1, a, selnot); and U3(b1, b, sel); or U4(out, a1, b1); endmodule

电路结构描述

例 2选1数据选择器的程序实例

module mux2_1(out, a, b, sel) ; output out; input a, b; input sel;

module和endmodule两个语句之间。每个模块实现特定的功能。

2. 每个模块先要进行端口的定义,并说明输入(input) 、输出

(output)和双向(inout),然后对模块功能进行描述。 3. 除了endmodule语句外,每个语句后必须有分号。 4. 可以用/* --- */和//…..,对VerilogHDL程序的任何部分做注释。

6.2.1 简单Verilog HDL程序实例

A B S A B

C=AB

模块名

6.2.1 半加器逻辑图

/* Gate-level description of a half adder */ module HalfAdder_GL(A, B, Sum, Carry); input A ,B ; //输入端口声明 output Sum, Carry ; //输出端口声明 端口类型说明 wire A ,B , Sum ,Carry ; xor X1 (Sum, A, B ); 数据类型说明 and A1 (Carry, A, B); endmodule 功能描述

module mux2_1(out, a, b, sel) ; output out; input a, b; input sel;

reg out;

case (sel)

1’b0 : out = a; 1’b1 : out = b;

endmodule

endcase

end

endmodule

6.2.2 Verilog HDL程序的基本结构

例 2选1数据选择器的程序实例

结构描述 (门级描述) module mux2to1(a, b, sel, out); input a, b, sel; //定义输入信号 output out; //定义输出信号 wire selnot; //定义内部节点信号数据类型

//下面对电路的逻辑功能进行描述