数电实验(verilog文档)

Verilog实验报告(电子)参考模板

西安邮电大学Verilog HDL大作业报告书学院名称:电子工程学院学生姓名:专业名称:电子信息工程班级:实验一异或门设计一、实验目的(1)熟悉Modelsim 软件(2)掌握Modelsim 软件的编译、仿真方法(3)熟练运用Modelsim 软件进行HDL 程序设计开发二、实验内容my_or,my_and和my_not门构造一个双输入端的xor门,其功能是计算z=x’y+xy’,其中x和y为输入,z为输出;编写激励模块对x和y的四种输入组合进行测试仿真1、实验要求用Verilog HDL 程序实现一个异或门,Modelism仿真,观察效果。

2、步骤1、建立工程2、添加文件到工程3、编译文件4、查看编译后的设计单元5、将信号加入波形窗口6、运行仿真实验描述如下:module my_and(a_out,a1,a2);output a_out;input a1,a2;wire s1;nand(s1,a1,a2);nand(a_out,s1,1'b1);endmodulemodule my_not(n_out,b);output n_out;input b;nand(n_out,b,1'b1); endmodulemodule my_or(o_out,c1,c2);output o_out;input c1,c2;wire s1,s2;nand(s1,c1,1'b1);nand(s2,c2,1'b1);nand(o_out,s1,s2); endmodulemodule MY_XOR(z,x,y);output z;input x,y;wire a1,a2,n1,n2;my_not STEP01(n1,x);my_not STEP02(n2,y);my_and STEP03(a1,n1,y);my_and STEP04(a2,n2,x);my_or STEP05(z,a1,a2); Endmodulemodule stimulus;reg X,Y;wire OUTPUT;MY_XOR xor01(OUTPUT,X,Y);initialbegin$monitor($time,"X=%b,Y=%b --- OUTPUT=%b\n",X,Y,OUTPUT);endinitialbeginX = 1'b0; Y = 1'b0;#5 X = 1'b1; Y = 1'b0;#5 X = 1'b1; Y = 1'b1;#5 X = 1'b0; Y = 1'b1;endendmodule二、实验结果波形图:三、分析和心得通过这次的实验,我基本熟悉Modelsim 软件,掌握了Modelsim 软件的编译、仿真方法。

verilog 实验实验一具体步骤

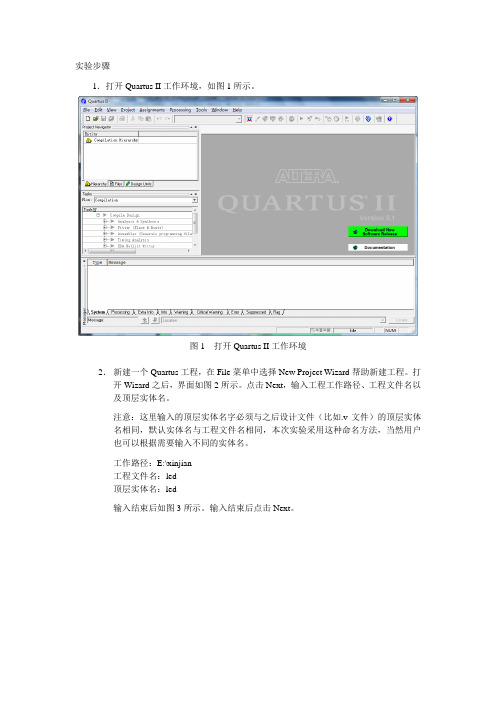

实验步骤1.打开Quartus II工作环境,如图1所示。

图1 打开Quartus II工作环境2.新建一个Quartus工程,在File菜单中选择New Project Wizard帮助新建工程。

打开Wizard之后,界面如图2所示。

点击Next,输入工程工作路径、工程文件名以及顶层实体名。

注意:这里输入的顶层实体名字必须与之后设计文件(比如.v文件)的顶层实体名相同,默认实体名与工程文件名相同,本次实验采用这种命名方法,当然用户也可以根据需要输入不同的实体名。

工作路径:E:\xinjian工程文件名:led顶层实体名:led输入结束后如图3所示。

输入结束后点击Next。

图2 New Project Wizard界面图3 输入设计工程信息3.添加设计文件,界面如图4所示。

如果用户之前已经有设计文件(比如.v文件),那么再次添加相应文件,如果没有完成的设计文件,点击Next,之后添加并且编辑设计文件。

图4 添加设计文件4.选择设计所用器件。

由于本次实验使用Altera公司提供的DE2开发板,用户必须选择与DE2开发板相对应的FPGA器件型号。

在Family菜单中选择CycloneII在Target device选项框中选择Specific device selected in ‘A vailable devices’ list 在A vailable device列表中选择EP2C35F672C6这个型号的器件。

完成后如图5所示,点击Next。

图5 选择相应器件5.设置EDA工具。

设计中可能会用到的EDA工具有综合工具、仿真工具以及时序分析工具。

在本次实验中不使用这些工具,因此点击Next直接跳过设置。

图6 设置EDA工具6.查看新建工程总结。

在基本设计完成后,Quartus II会自动生成一个总结让用户核对之前的设计(如图7所示),确认后点击Finish完成新建。

图7 新建工程总结在完成新建后,Quartus II界面中Project Navigator的Hierarchy标签栏中会出现用户正在设计的工程名以及所选用的器件型号,如图8所示。

数电实验报告2.1—基于Verilog HDL显示译码器设计

<基于Verilog HDL显示译码器设计>实验报告学生姓名:班级学号:指导老师:<实验报告内容>一、实验名称:基于Verilog HDL 显示译码器设计二、实验学时:4学时 三、实验目的:进一步掌握QuartusII 软件逻辑电路设计环境及Verilog HDL 的基本语法,熟悉设计流程及思路。

掌握显示译码器的工作原理及应用。

(提示:本实验将涉及到verilog 的条件语句(如if …else, case ….end case, for ….等)、赋值语句(如assign 等)和二进制变量位宽的定义等内容,请大家实验前做好本部分预习和自学,可参考本课本第九章内容,也可自行查找有关Verilog 设计基础的相关内容,推荐参考书:北京航空航天出版社,夏宇闻编著 )。

通过对所设计逻辑电路功能仿真,分析所设计电路逻辑功能是否正确,掌握逻辑功能仿真的方法。

四、实验内容:基于verilog 的显示译码器逻辑设计及功能仿真五、实验原理:(1)半导体发光二极管(LED )数码显示器:半导体发光二极管数码显示器由7(或8)个LED 排成“日”字形,称为七段(或八段),封装成数码管,如错误!未找到引用源。

所示。

LED 数码管内部有共阴极和共阳极两种接法。

如错误!未找到引用源。

(2)常用显示译码器管脚功能(74LS148):LCD —七段显示译码器:介绍常用的74LS148七段显示译码器,图 3为74LS4874LS48(a )图 1 图 2 CC fg a bcd e BI 7123456图 3(3)74LS48的逻辑功能:如表1:表1其译码器输出(Ya~Yg)是高电平有效,适用于驱动共阴极LED数码管,显示的字形表中所示。

因其译码器输出端的内部有上拉电阻(是2K的限流电阻),因此在与LED管连接时无需再外接限流电阻。

具体功能介绍及内部设计图,请自行上网查阅74LS48的DATASHEET。

数字电路实验说明书(1-6)

《数字逻辑与数字电路》实验指导实验1.Verilog HDL输入方式组合电路的设计多路选择器和三人表决电路的设计(1) 实验目的:进一步熟悉Quartus II的V erilog HDL文本设计流程,组合电路的设计仿真和硬件测试。

(2) 实验内容1、多路选择器的设计:根据教材5.1节的流程,利用Quartus II完成2选1多路选择器的文本编辑输入(MUX21.v)和仿真测试等步骤,给出仿真波形。

在实验系统上硬件测试,验证此设计的功能。

对于引脚锁定以及硬件下载测试,a和b分别接来自不同的时钟;输出信号接蜂鸣器。

最后进行编译、下载和硬件测试实验(通过选择键1,控制s,可使蜂鸣器输出不同音调)。

(4) 实验内容2、三人表决电路的设计:根据教材5.1节的流程,利用Quartus II完成三人表决电路的文本编辑输入(图5-36)和仿真测试等步骤,给出仿真波形。

在实验系统上硬件测试,验证此设计的功能。

对于引脚锁定以及硬件下载测试,ABC[2..0]分别接自键3、键2、键1;CLK接自时钟CLOCK0(256Hz),输出信号X接D1,输出信号Y接蜂鸣器。

最后进行编译、下载和硬件测试实验(通过按下键3、键2、键1,控制D1的亮灭)。

(5) 实验报告:根据以上的实验内容写出实验报告,包括程序设计、软件编译、仿真分析、硬件测试和详细实验过程;给出程序分析报告、仿真波形图及其分析报告。

参考ppt实验指导课件。

实验2.原理图输入方式全加器设计(1) 实验目的:熟悉利用Quartus II的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握文本和原理图输入方式设计的详细流程。

(2) 实验原理:一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相接。

(3) 实验内容1:按照教材4.6节完成半加器和1位全加器的设计,包括用文本或原理图输入,编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设置成一个元件符号入库。

verilog实验报告

verilog实验报告Verilog实验报告引言:Verilog是一种硬件描述语言(HDL),用于设计和模拟数字电路。

它是一种高级语言,能够描述电路的行为和结构,方便工程师进行数字电路设计和验证。

本实验报告将介绍我在学习Verilog过程中进行的实验内容和所获得的结果。

实验一:基本门电路设计在这个实验中,我使用Verilog设计了基本的逻辑门电路,包括与门、或门和非门。

通过使用Verilog的模块化设计,我能够轻松地创建和组合这些门电路,以实现更复杂的功能。

我首先创建了一个与门电路的模块,定义了输入和输出端口,并使用逻辑运算符和条件语句实现了与门的功能。

然后,我创建了一个测试模块,用于验证与门的正确性。

通过输入不同的组合,我能够验证与门的输出是否符合预期。

接下来,我按照同样的方法设计了或门和非门电路,并进行了相应的测试。

通过这个实验,我不仅学会了使用Verilog进行基本门电路的设计,还加深了对逻辑电路的理解。

实验二:时序电路设计在这个实验中,我学习了如何使用Verilog设计时序电路,例如寄存器和计数器。

时序电路是一种具有状态和时钟输入的电路,能够根据时钟信号的变化来改变其输出。

我首先设计了一个简单的寄存器模块,使用触发器和组合逻辑电路实现了数据的存储和传输功能。

然后,我创建了一个测试模块,用于验证寄存器的正确性。

通过输入不同的数据和时钟信号,我能够观察到寄存器的输出是否正确。

接下来,我设计了一个计数器模块,使用寄存器和加法电路实现了计数功能。

我还添加了一个复位输入,用于将计数器的值重置为初始状态。

通过测试模块,我能够验证计数器在不同的时钟周期内是否正确地进行计数。

通过这个实验,我不仅学会了使用Verilog设计时序电路,还加深了对触发器、寄存器和计数器的理解。

实验三:组合电路设计在这个实验中,我学习了如何使用Verilog设计组合电路,例如多路选择器和加法器。

组合电路是一种没有状态和时钟输入的电路,其输出只取决于当前的输入。

数电自主设计实验报告——Verilog秒表

姓名班级学号实验日期节次教师签字成绩基于BASYS2开发板的记忆秒表设计一、实验目的1、熟悉基于Verilog HDL语言输入方式的数字电路的设计方法。

2、掌握基于FPGA的设计流程。

3、熟悉BASYS2开发板的使用方法。

4、熟悉Xilinx ISE软件的使用方法。

5、培养自己独立自主设计并完成实验的能力。

二、总体设计方案或技术路线本实验利用BASYS2开发板的已有资源来进行设计实验,并用Xilinx ISE软件来编写和综合Verilog代码。

总体设计方案是设计一个带有记忆功能的秒表。

具体而言,该秒表通过BASYS2开发板的50M的时钟进行分频计时,最大计时时间为99.99s,用4位数码管动态显示计时时间,除了有基本的运行、暂停及复位清空功能,还有存储当前时间和查看存储时间的功能。

三、实验电路图BASYS2开发板原理图--数码管板上数码管为4位共阳极数码管,每段为低电平点亮,位选接了三极管增大驱动电流,同时为非逻辑,所以位选信号为低电平有效。

BASYS2开发板原理图--按键本实验用到了两个按键BTN0和BTN1,BTN0为复位按键,对应程序的clear信号,BTN1为存储按键,对应程序的btn[1]信号,按一次该按键数据存储一次,下一次按下时这一次存的数据将被替换掉。

BASYS2开发板原理图--开关本实验用到了两个开关SW7和SW1,SW7为运行、暂停开关,对应程序的sw[0]信号,开关打到上方为运行,下方为暂停,SW1为显示切换开关,对应程序的sw[1]信号,在计时暂停的前提下,将开关打到上方显示出存储的时间数据。

四、仪器设备名称、型号和技术指标硬件:BASYS2开发板软件:Xilinx ISE(编程)、Digilent Adept(下载)五、程序流程图六、程序源代码/////////////////////////////////////////////////////////程序文件`timescale 1ns / 1ps////////////////////////////////////////////////////////////////////////////////// // Company:// Engineer://// Create Date: 15:45:01 11/26/2014// Design Name:// Module Name: miaobiao// Project Name:// Target Devices:// Tool versions:// Description://// Dependencies://// Revision:// Revision 0.01 - File Created// Additional Comments://///////////////////////////////////////////////////////////秒表的顶层模块module miaobiao(input wire clk,///////////////////////////////开发板系统时钟50MHzinput wire[1:0] btn,////////////////////////两个按键:[0]复位和[1]存时间input wire[1:0] sw,/////////////////////////两个开关:[0]运行/暂停和[1]显示存储时间output wire[7:0] smg,/////////////////////数码管的8个段选信号output wire[3:0] smg_an/////////////////数码管的4个位选信号);wire clear;assign clear=btn[0];////////////////////////////////////将复位按键信号传给clear变量wire clk_1k;clkdiv #(50000) m0(clk,clear,clk_1k);//将50MHz进行5万分频输出1kHz时钟信号wire[15:0]number;timer m1(sw[0]&clk_1k,clear,number);///////////计时器模块,输出当前时间数据wire[15:0]num_save;save m2(clk,clear,btn[1],number,num_save);//////按键按下存储当前时间wire[15:0]num_display;/////////////////////////////////////////////////////////////////////////////根据开关状态选择显示内容choose_4num m3(sw,number,num_save,num_display);display m4(clk_1k,clear,num_display,smg,smg_an);///////将数字送给数码管显示endmodule///////////////////////////////////////////////////////////////////////////////4选1数据选择器模块module choose_4num(input wire[1:0]sw,input wire[15:0]number,input wire[15:0]num_save,output reg[15:0]num_display);always@(*)case(sw)0:num_display<=number;/////////////显示内容为当前时间1:num_display<=number;/////////////。

最新Verilog数字电路设计--实验报告

Verilog数字电路设计实验名称Verilog数字电路设计班级130324姓名张先炳13031205同组者廖瑞13031191自动化与电气工程学院2016年4月25日目录目录 (2)实验一简单组合逻辑设计 (1)1 实验目的 (1)2 实验设备 (1)3 实验内容 (1)4 实验代码 (1)5 仿真结果 (2)选作一:设计一个字节的比较器 (3)1 实验要求 (3)2 模块代码 (3)3 测试代码 (3)4 仿真结果 (4)实验二简单分频时序逻辑电路的设计 (4)1 实验目的 (4)2 实验设备 (4)3 实验内容 (5)4 实验代码 (5)5 仿真结果 (6)选作二:七段数码管译码电路 (6)1 实验要求 (6)2 模块代码 (7)3 测试代码 (8)4 仿真结果 (8)实验三:利用条件语句实现计数分频时序电路 (9)1 实验目的 (9)2 实验设备 (9)3 实验内容 (9)4 实验代码 (9)5 仿真结果 (11)6 实验分析 (11)选作三:设计一个单周期形状的周期波形。

(11)1 实验要求 (11)2 模块代码 (11)3 测试代码 (12)4 仿真结果 (13)实验四:用always块实现较复杂的组合逻辑 (13)1 实验目的 (13)2 实验设备 (13)3 实验内容 (13)4 实验代码 (14)5 仿真结果 (16)选作四:运用always块设计一个8路数据选择器。

(16)1 实验要求 (16)2 模块代码 (16)3 测试代码 (17)4 仿真结果 (18)实验五:在Verilog HDL中使用函数 (19)1 实验目的 (19)2 实验设备 (19)3 实验内容 (19)4 实验代码 (19)5 仿真结果 (21)选作五:设计一个带控制端的逻辑运算电路 (22)1 实验要求 (22)2 模块代码 (22)3 测试代码 (23)4 仿真结果 (25)实验六:在Verilog HDL中使用任务(task) (25)1 实验目的 (25)2 实验设备 (25)3 实验内容 (25)4 实验代码 (25)5 仿真结果 (28)选作六:冒泡法排序 (28)1 实验要求 (28)2 模块代码 (28)3 测试代码 (29)4 仿真结果 (30)选作七:串行输入排序 (30)1 实验要求 (30)2 模块代码 (31)3 测试代码 (32)4 仿真结果 (33)5 实验分析 (34)实验七:利用有限状态机进行时序逻辑的设计 (34)1 实验目的 (34)2 实验设备 (34)3 实验内容 (35)4 实验代码 (35)5 仿真结果 (37)6 实验分析 (37)选作八:楼梯灯 (37)1 实验要求 (37)2 模块代码 (38)3 测试代码 (45)4 仿真结果 (47)5 实验分析 (47)附:分工明细 (49)实验一简单组合逻辑设计1 实验目的1、掌握基本组合逻辑电路的实现方法。

verilog hdl实验报告

verilog hdl实验报告《Verilog HDL实验报告》Verilog HDL(硬件描述语言)是一种用于描述电子系统的硬件的语言,它被广泛应用于数字电路设计和硬件描述。

本实验报告将介绍Verilog HDL的基本概念和使用方法,并通过实验展示其在数字电路设计中的应用。

实验目的:1. 了解Verilog HDL的基本语法和结构2. 掌握Verilog HDL的模块化设计方法3. 熟悉Verilog HDL的仿真和综合工具的使用实验内容:1. Verilog HDL的基本语法和结构Verilog HDL是一种硬件描述语言,其语法和结构类似于C语言。

它包括模块定义、端口声明、信号赋值等基本元素。

在本实验中,我们将学习如何定义Verilog模块,并使用端口声明和信号赋值描述数字电路的行为。

2. Verilog HDL的模块化设计方法Verilog HDL支持模块化设计,可以将复杂的电路分解为多个模块,每个模块描述一个子电路的行为。

在本实验中,我们将学习如何设计和实现Verilog模块,并将多个模块组合成一个完整的数字电路。

3. Verilog HDL的仿真和综合工具的使用Verilog HDL可以通过仿真工具进行功能验证,也可以通过综合工具生成实际的硬件电路。

在本实验中,我们将使用Verilog仿真工具对设计的数字电路进行功能验证,并使用综合工具生成对应的硬件电路。

实验步骤:1. 学习Verilog HDL的基本语法和结构2. 设计一个简单的数字电路,并实现Verilog模块描述其行为3. 使用仿真工具对设计的数字电路进行功能验证4. 使用综合工具生成对应的硬件电路实验结果:通过本实验,我们学习了Verilog HDL的基本概念和使用方法,并成功设计和实现了一个简单的数字电路。

我们使用仿真工具对设计的数字电路进行了功能验证,并使用综合工具生成了对应的硬件电路。

实验结果表明,Verilog HDL在数字电路设计中具有重要的应用价值。

verilog实验报告 - 程超

西安邮电學院基于Verilog的数字电路模拟实验系部名称:通信与信息工程学院学生姓名:张宏扬专业名称:通信工程班级:通工0809学号:03081469(01)时间:2010年12月20号实验题目门级建模仿真实验一、实验内容设计的一个带有清零的顺序输出结果的计数器,q从0计数到15二、技术规范1、输入引脚:reset,clk;输出引脚:q。

2、功能:这时也个具有清零的计数器,从0到15输出的。

在其中用到了T触发器和D触发器来实现它的功能。

三、实验步骤1、在modulesim软件中对设计模块和验证模块进行书写和编译;2、对编译好的模块进行仿真。

四、源代码://脉动进位计数器顶层模块module ripple_carry_counter(q,clk,reset);output [3:0]q;input clk,reset;//生成了4个T触发器(T_FF)的实例,每个都有自己的名字T_FF tff0(q[0],clk,reset);T_FF tff1(q[1],q[0],reset);T_FF tff2(q[2],q[1],reset);T_FF tff3(q[3],q[2],reset);endmodule//触发器T_FFmodule T_FF(q,clk,reset);output q;input clk,reset;wire d;D_FF dff0(q,d,clk,reset);not n1(d,q); //非门(not)是Verilog语言的内置原语部件(primitive)endmodule//D触发器(D_FF)//带异步复位的D触发器(D_FF)module D_FF(q,d,clk,reset);output q;input d,clk,reset;reg q;//可以有许多种新结构,不考虑这些结构的功能,只需要注意设计块是如何以自顶向下的方式编写的always @(posedge reset or negedge clk)if (reset)q<= 1'b0;elseq<= d;endmodulemodule stimulus;reg clk;reg reset;wire [3:0]q;//引用已经设计好的模块实例ripple_carry_counter r1(q,clk,reset);//控制驱动设计块的时钟信号,时钟周期为10个时间单位initialclk = 1'b0; //把clk设置为0always#5 clk = ~clk; //每5个时间单位时钟翻转一次//控制驱动设计块的reset信号initialbeginreset = 1'b1;#15 reset = 1'b0;#180 reset = 1'b1;#10 reset = 1'b0;#20 $finish; //终止仿真end//监视输出initial$monitor($time, "Output q = %d",q);endmodule五、仿真结果及分析实验题目 RS锁存器一、实验内容带有延迟的RS锁存器,写出其带有延迟的Verilog门级描述。

verilog实验-计数器实验报告

v e r i l o g实验-计数器实验报告-CAL-FENGHAI-(2020YEAR-YICAI)_JINGBIAN计数器1、实现目标及介绍实验实现了一个简易的计数器,计数范围可达899(0~899),通过key4按键计数,每按下一次,计数加一,百位数显示在led上,个位与十位显示在数码管上。

为十进制计数,数码管1计数到九后置零。

数码管2获得进位加一,数码管2到9后当再次获得个位进位时再次向百位进一,点亮led1,每百位点亮一个led。

此外key4为清零键,可随时按键清零。

2、效果展示计数99清零计数100视频展示(双击观看)3、代码实现与模块分析1.顶层模块module jishuqi(input wire clk,rst, eg_data_1 (cnt[7:4]), eg_data_2 (cnt[3:0]), eg_led_1 (segment_led_1), eg_led_2 (segment_led_2) lk (clk),.rst (rst),.key (key1),.key_pulse (key_pulse));endmodule2.数码管显示模块module segment (seg_data_1,seg_data_2,seg_led_1,seg_led_2);input [3:0] seg_data_1;键消抖模块eg_data_1 (cnt[7:4]), eg_data_2 (cnt[3:0]), eg_led_1 (segment_led_1), eg_led_2 (segment_led_2) lk (clk),.rst (rst),.key (key1),.key_pulse (key_pulse));endmodule//按键消抖module debounce (clk,rst,key,key_pulse);parameter N = 2; //要消除的按键的数量input clk;input rst;input [N-1:0] key; //输入的按键output [N-1:0] key_pulse; //按键动作产生的脉冲reg [N-1:0] key_rst_pre; //定义一个寄存器型变量存储上一个触发时的按键值reg [N-1:0] key_rst; //定义一个寄存器变量储存储当前时刻触发的按键值wire [N-1:0] key_edge; //检测到按键由高到低变化是产生一个高脉冲//利用非阻塞赋值特点,将两个时钟触发时按键状态存储在两个寄存器变量中always @(posedge clk or negedge rst)beginif (!rst)beginkey_rst <= {N{1'b1}}; //初始化时给key_rst赋值全为1,{}中表示N个1key_rst_pre <= {N{1'b1}};endelsebeginkey_rst <= key; //第一个时钟上升沿触发之后key 的值赋给key_rst,同时key_rst的值赋给key_rst_prekey_rst_pre <= key_rst; //非阻塞赋值。

Verilog 实验报告

Verilog 实验报告一、实验目的本次 Verilog 实验的主要目的是通过实际编写代码和进行仿真,深入理解 Verilog 语言的基本语法、逻辑结构和时序特性,掌握数字电路的设计方法和实现过程,并能够运用Verilog 实现简单的数字逻辑功能。

二、实验环境本次实验使用的软件工具是 Xilinx Vivado 20192,硬件平台是Xilinx Artix-7 开发板。

三、实验内容(一)基本逻辑门的实现1、与门(AND Gate)使用 Verilog 语言实现一个两输入的与门。

代码如下:```verilogmodule and_gate(input a, input b, output out);assign out = a & b;endmodule```通过编写测试激励文件对该模块进行仿真,验证其逻辑功能的正确性。

2、或门(OR Gate)同样实现一个两输入的或门,代码如下:```verilogmodule or_gate(input a, input b, output out);assign out = a | b;endmodule```3、非门(NOT Gate)实现一个单输入的非门:```verilogmodule not_gate(input a, output out);assign out =~a;endmodule```(二)组合逻辑电路的实现1、加法器(Adder)设计一个 4 位的加法器,代码如下:```verilogmodule adder_4bit(input 3:0 a, input 3:0 b, output 4:0 sum);assign sum = a + b;endmodule```2、减法器(Subtractor)实现一个 4 位的减法器:```verilogmodule subtractor_4bit(input 3:0 a, input 3:0 b, output 4:0 diff);assign diff = a b;endmodule```(三)时序逻辑电路的实现1、计数器(Counter)设计一个 4 位的计数器,能够在时钟上升沿进行计数,代码如下:```verilogmodule counter_4bit(input clk, output 3:0 count);reg 3:0 count_reg;always @(posedge clk) begincount_reg <= count_reg + 1;endassign count = count_reg;endmodule```2、移位寄存器(Shift Register)实现一个 4 位的移位寄存器,能够在时钟上升沿进行左移操作:```verilogmodule shift_register_4bit(input clk, input rst, output 3:0 data_out);reg 3:0 data_reg;always @(posedge clk or posedge rst) beginif (rst)data_reg <= 4'b0000;elsedata_reg <={data_reg2:0, 1'b0};endassign data_out = data_reg;endmodule```四、实验结果与分析(一)基本逻辑门的结果通过仿真,与门、或门和非门的输出结果与预期的逻辑功能完全一致,验证了代码的正确性。

数字系统设计与Verilog HDL实验报告(二)

《数字系统设计与Verilog HDL》实验报告(二)班级:自动1003班姓名:**学号:********实验二、四位并串转换电路一、实验目的1、了解及掌握时序电路的基本结构常用数字电路;2、通过ModelSim软件编写时序电路的程序进行仿真和调试。

二、实验内容1、熟悉时序电路中时钟的同步与异步用法;2、编写一个四位并串转换设计程序以及测试该模块的测试程序,要求如下:(1)输入一个四位二进制数pin;(2)每个时钟周期按从左往右的顺序输出一位pin的二进制位的数。

三、实验步骤及源程序新建工程及文件,分别添加设计程序及测试程序,进行编译及纠错,编译通过后运行程序仿真进行调试得出结果。

设计模块:module para_to_serial4(pin,clk,reset,sout);input [3:0] pin;input clk,reset;output sout;reg sout;reg [3:0] data;always @(posedge clk or negedge reset)beginif(~reset)beginsout<=1'b0;data<=pin;endelsebegindata<={data[2:0],data[3]};sout<=data[3];endendendmodule测试模块:`timescale 1ns/1nsmodule test_para_to_ser;wire sout;reg [3:0] pin;reg clk,reset;para_to_serial4 test1(pin,clk,reset,sout);initialbeginclk=1'b0;reset=1'b0;#5 reset=1'b1;#300 $stop;endinitialpin=4'b1001;always#5 clk=~clk;endmodule四、实验结果五、实验心得体会这次试验相对于上次有了一定的难度,由于这门课程刚开始学习,我还不能很好地从宏观把握这门课程,对这门课程的认识和理解还不够深刻,所以做实验时遇到了一些困难,虽然找了一些参考资料,有一定的帮助,但最后还是有点纠结,最终在和同学的交流中才比较深刻的对实验有了了解。

verlog实验报告

Verilog实验报告1. 引言本实验旨在通过使用Verilog硬件描述语言来实现一个简单的电路设计。

Verilog是一种用于描述电路行为和结构的编程语言,可以用于设计和仿真数字电路。

本实验将通过逐步的思考过程,详细说明实验的设计和实现。

2. 设计思路首先,我们需要确定电路的功能和需要实现的功能。

在这个例子中,我们将设计一个简单的4位加法器电路。

接下来,我们需要创建一个顶层模块,该模块将包含所需的输入和输出端口,并将其他模块连接在一起。

我们可以使用以下代码创建一个顶层模块:module top_module(input [3:0] a, input [3:0] b, output [3:0] sum);// 端口声明// 内部逻辑实现endmodule然后,我们可以创建一个子模块,该模块将执行实际的加法操作。

我们可以使用以下代码创建一个加法器模块:module adder(input [3:0] a, input [3:0] b, output [3:0] sum);// 加法操作实现endmodule在加法器模块中,我们可以使用位级操作符+来执行实际的加法运算。

我们可以使用以下代码实现加法操作:assign sum = a + b;最后,我们将在顶层模块中实例化加法器模块,并将输入和输出端口连接在一起。

我们可以使用以下代码实现实例化和连接:adder adder_instance(.a(a), .b(b), .sum(sum));3. 实验结果在完成上述步骤后,我们可以编译和仿真我们的Verilog代码。

可以使用常见的Verilog仿真器(如ModelSim)来进行仿真。

在仿真期间,我们可以为输入端口输入不同的二进制数,并观察输出端口是否正确计算了输入数的和。

通过逐步调试和测试,我们可以确保电路的正确性。

4. 总结通过本实验,我们学习了使用Verilog硬件描述语言设计和实现数字电路。

我们了解了Verilog的基本语法和结构,并通过实例演示了设计一个简单的4位加法器电路的过程。

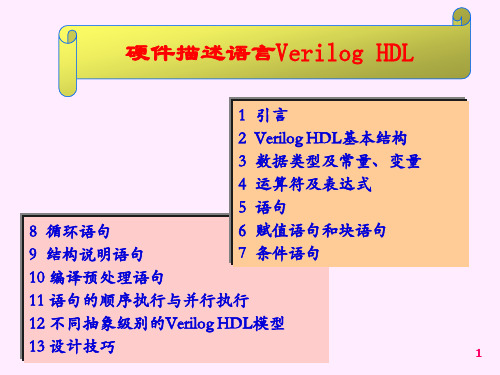

数字逻辑实验-Verilog教程

功能进行行为逻辑描述。 ➢ 程序书写格式自由,一行可以写几个语句,一个语句也可以分多

行写。 ➢ 除了endmodule语句、begin_end语句和fork_join语句外,每个语

➢ 开关级(switch level): 描述器件中三极管和储存节点

及其之间连接的模型。

5

1 引言

四、Verilog HDL的特点

▪ 语法结构上的主要特点:

➢ 形式化地表示电路的行为和结构; ➢ 借用C语言的结构和语句; ➢ 可在多个层次上对所设计的系统加以描述,语言对设计规

模不加任何限制; ➢ 具有混合建模能力:一个设计中的各子模块可用不同级别

output cout; input [7:0] data;

I/O说明

input load, cin,clk ; reg[7:0] out;

信号类型声明

always @(posedge clk)

begin

if(load) out <= data;

// 同步预置数据 功能描述

else out < = out + 1 + cin; // 加1计数

7

2 Verilog HDL基本结构

一、简单的Verilog HDL例子

[例2.1] 8位全加器

模块名(文件名)

module adder8 ( cout,sum,a,b,cin ); 端口定义

output cout; output [7:0] sum;

// 输出端口声明

I/O说明

input [7:0] a,b;

数电实验考试verilogHDL语言及参考程序

题目一:表决器电路设计一、设计任务及原理:所谓表决器就是对于一个行为;由多个人投票;如果同意的票数过半;就认为此行为可行;否则如果否决的票数过半;则认为此行为无效..七人表决器顾名思义就是由七个人来投票;当同意的票数大于或者等于4时;则认为同意;反之;当否决的票数大于或者等于4时;则认为不同意..实验中用7个拨动开关来表示七个人;当对应的拨动开关输入为‘1’时;表示此人同意;否则若拨动开关输入为‘0’;则表示此人反对..表决的结果用一个LED表示;若表决的结果为同意;则LED被点亮;否则;如果表决的结果为反对;则LED不会被点亮..同时;数码管上显示通过的票数..二、具体要求:本实验就是利用实验系统中的拨动开关模块和LED模块以及数码管模块来实现一个简单的七人表决器的功能..拨动开关模块中的K1~K7表示七个人;当拨动开关输入为‘1’时;表示对应的人投同意票;否则当拨动开关输入为‘0’时;表示对应的人投反对票;LED模块中LED1表示七人表决的结果;当LED1点亮时;表示此行为通过表决;否则当LED1熄灭时;表示此行为未通过表决..同时通过的票数在数码管上显示出来..在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明;这里不在赘述.. 端口名使用模块信号对应FPGA管脚说明S1 按键开关S1 R16 表示1号抢答者S2 按键开关S2 P14 表示2号抢答者S3 按键开关S3 P16 表示3号抢答者S4 按键开关S4 P15 表示4号抢答者S5 按键开关S5 M15 表示5号抢答者S6 按键开关S6 N16 表示6号抢答者S7 按键开关S7 N15 表示7号抢答者DOUT0 LED模块D1 L14 表决结果亮为通过LEDAG0数码管模块A段N4 抢答成功者号码显示LEDAG1数码管模块B段G4LEDAG2数码管模块C段H4参考答案:module lius;dout0;ledag;input 6:0s;output dout0;output 6:0ledag;reg 6:0led;reg 2:0k;reg clk_en;reg dout;always sbegink<=s1+s2+s3+s4+s5+s6+s0;ifk>=4begindout<=1;endelsebegindout<=0;endendalwayskbegincase k3'd0:led<=7'b0111111;3'd1:led<=7'b0000110;3'd2:led<=7'b1011011;3'd3:led<=7'b1001111;3'd4:led<=7'b1100110;3'd5:led<=7'b1101101;3'd6:led<=7'b1111101;3'd7:led<=7'b0000111;default:led<=7'b0000000;endcaseendassignledag=led;assigndout0=dout;endmodule题目二:数字电子实验设计题目:彩灯循环电路设计一、设计任务及原理:所谓彩灯循环就是对于一组彩灯16盏;通过不同的工作模式可按照一定的规律来点亮或者熄灭..我们所要求的彩灯循环电路共分4个节拍;四个节拍按照一定的顺序依次循环执行..二、具体要求:系统设有一个复位键;当按下复位键后;系统从第一节拍开始执行直到第四节拍结束;然后从第一节拍重新开始新的循环..第一节拍:16盏灯Q1~Q16从Q1开始依次点亮;直到Q16为止..每盏灯点亮的时间间隔为一秒;即Q1点亮后;间隔一秒后Q2点亮;然后依次点亮..下面类似间隔时间都为1秒第二节拍:在第一节拍的基础上;16盏灯Q1~Q16从Q16开始依次熄灭;直到Q1为止..每盏灯熄灭的时间间隔为一秒;即Q16熄灭后;间隔一秒后Q15熄灭;然后依次熄灭直到全部熄灭为止..下面类似间隔时间都为1秒第三节拍: 16盏灯Q1~Q16从两端开始依次点亮;即Q1、Q16先点亮;然后Q2、Q15再点亮;直到全部16盏等点亮为止..每盏灯点亮的时间间隔为一秒..第四节拍:在第三节拍的基础上;16盏灯Q1~Q16从中间开始依次熄灭;即Q8、Q9先熄灭;然后Q7、Q10再熄灭;直到全部16盏灯熄灭为止..每盏灯熄灭的时间间隔为一秒..在此实验中数码管、LED、拨动开关与FPGA 的连接电路和管脚连接在以前的实验中都做了详细说明;这里不在赘述.. 端口名使用模块信号对应FPGA管脚说明S1 按键开关S1 R16 表示复位按键Q1 Q1 L14 Q2 Q2 M14Q3 Q3 N14Q4 Q4 N13Q5 Q5 P12 参考答案:module liu2clk;ret;led;input clk;ret;output16:1 led;wire ret_en;reg 16:1led1;reg 5:0i;j;k;l;m;reg 31:0cout;reg clk_en;assignret_en=ret;alwaysposedge clk or negedge ret_enbeginif~ret_enbeginled1<=16'b0000000000000000;i<=0;endelsebeginifclk_enbeginj<=0;k<=0;i<=i+1;ifi<=16begin//dex<=i;//l<=0;//m<=0;led1i<=1;//led1i-j<=0;endelse ifi>16&&i<=32beginj<=k2+1;k<=k+1;led1i-j<=0;//dex<=dex-1;endelse ifi>32&&i<=40begin//dex<=dex+1;//l<=2m+17;led1i-32<=1;led149-i<=1;endelse ifi>40&&i<=48beginled1i-32<=0;led149-i<=0;//dex<=dex-1;endelsebegini<=0;led1<=16'b0000000000000000;endendendendassignled=led1;endmodule题目三:汽车尾灯控制电路设计一、设计任务及原理:假设汽车尾部左右两侧各有3个指示灯;1汽车正常运行时;指示灯全灭..2左转弯时;左侧3个指示灯按照左循环顺序点亮1HZ..3 右转弯时;右侧3个指示灯按照右循环顺序点亮1HZ..4临时刹车时;所有指示灯同时闪烁1HZ..二、具体要求:尾灯与汽车运行状态表开关控制运行状态左尾灯右尾灯S1 S0 D1 D2 D3 D4 D5 D60 0 正常运行灯灭灯灭0 1 左转弯按照D3;D2;D1顺序循环点亮灯灭1 0 右转弯灯灭按照D4;D5;D6顺序循环点亮1 1 临时停车1HZ频率同时闪烁1HZ频率同时闪烁在此实验中数码管、LED、拨动开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明;这里不在赘述..端口名使用模块信对应FPGA管号脚S1 按键开关S1 R16S2 按键开关S2 P14D1 LED模块D1 L14D2 LED模块D2 M14D3 LED模块D3 N14D4 LED模块D4 N13D5 LED模块D5 P12D6 LED模块D6 N12 脉冲源50MHZ CP J3 参考程序:module lwfclk;ledag;s;input clk;input 1:0s;output5:0ledag;reg5:0led;reg1:0i;j;k;reg31:0cout;reg clk_en;alwaysposedge clkbeginifclk_enbeginifs==2'b00begini<=0;j<=0;k<=0;led<=6'b000000;endelse ifs==2'b01beginled<=6'b000000;k<=0;j<=0;i<=i+1;ifi==2'b01beginled<=6'b001000;endifi==2'b10beginled<=6'b010000;endifi==2'b11beginled<=6'b100000;i<=0;endendelse ifs==2'b10beginled<=6'b000000;k<=0;i<=0;j<=j+1;ifj==2'b01beginled<=6'b000100;endifj==2'b10beginled<=6'b000010;endifj==2'b11beginled<=6'b000001;j<=0;endendelse ifs==2'b11beginled<=6'b000000;i<=0;j<=0;k<=k+1;ifk==2'b01beginled<=6'b000000;endifk==2'b10beginled<=6'b111111;k<=0;endendendendassignledag=led;endmodule题目四:数字电子实验设计题目:抢答器电路设计一、设计任务及原理:抢答器在各类竞赛性质的场合得到了广泛的应用;它的出现;消除了原来由于人眼的误差而未能正确判断最先抢答的人的情况..抢答器的原理比较简单;首先必须设置一个抢答允许标志位;目的就是为了允许或者禁止抢答者按按钮;如果抢答允许位有效;那么第一个抢答者按下的按钮就将其清除;同时记录按钮的序号;也就是对应的按按钮的人;这样做的目的是为了禁止后面再有人按下按钮的情况..总的说来;抢答器的实现就是在抢答允许位有效后;第一个按下按钮的人将其清除以禁止再有按钮按下;同时记录清楚抢答允许位的按钮的序号并显示出来;这就是抢答器的实现原理..二、具体要求:本实验的任务是设计一个四人抢答器;用按键模块的S8来作抢答允许按钮;用S1~S4来表示1号抢答者~4号抢答者;同时用LED模块的LED1~LED4分别表示于抢答者对应的位子..具体要求为:按下S8一次;允许一次抢答;这时S1~S4中第一个按下的按键将抢答允许位清除;同时将对应的LED点亮;用来表示对应的按键抢答成功..数码管显示对应抢答成功者的号码..在此实验中数码管、LED、按键开关与FPGA的连接电路和管脚连接在以前的实验中都做了详细说明;这里使用模块信号对应FPGA管脚说明不在赘述.. 端口名S1 按键开关S1 R16 表示1号抢答者S2 按键开关S2 P14 表示2号抢答者S3 按键开关S3 P16 表示3号抢答者S4 按键开关S4 P15 表示4号抢答者S8 按键开关S12 M15 开始抢答按键DOUT0 LED模块D1 L14 1号抢答者灯DOUT1 LED模块D2 M14 2号抢答者灯DOUT2 LED模块D3 N14 3号抢答者灯DOUT3 LED模块D4 N13 4号抢答者灯LEDAG0数码管模块A段N4 抢答成功者号码显示LEDAG1数码管模块G4B段LEDAG2数码管模块H4C段参考程序:module liu1s1;s2;s3;s4;s8;led;ledag;input s1;s2;s3;s4;input s8;output 6:0ledag;output 3:0led;reg 3:0led;reg k;reg 6:0ledag1;//initial// k<=0;always s8beginifs8==0begin k<=1;led<=4'b0000;ledag1<=7'b0111111;end elsebeginifk==1beginif~s1beginled<=4'b1000;ledag1<=7'b0000110;k<=0;endelse if~s2beginled<=4'b0100;ledag1<=7'b1011011;k<=0;endelse if~s3beginled<=4'b0010;ledag1<=7'b1001111;k<=0;endelse if~s4beginled<=4'b0001;ledag1<=7'b1100110;k<=0;endendendendassignledag=ledag1; endmodule。

数电仿真Modelsim设计实验报告VerilogHDL语言

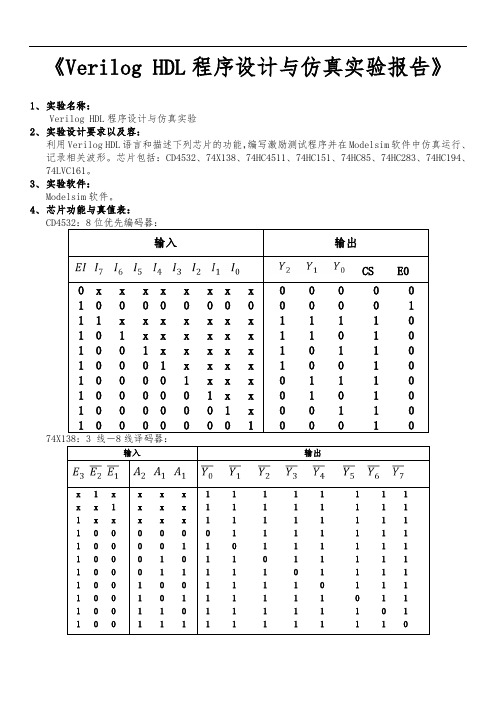

《Verilog HDL程序设计与仿真实验报告》1、实验名称:Verilog HDL程序设计与仿真实验2、实验设计要求以及容:利用Verilog HDL语言和描述下列芯片的功能,编写激励测试程序并在Modelsim软件中仿真运行、记录相关波形。

芯片包括:CD4532、74X138、74HC4511、74HC151、74HC85、74HC283、74HC194、74LVC161。

3、实验软件:Modelsim软件。

4、芯片功能与真值表:输入输出CS E00 x x x x x x x x1 0 0 0 0 0 0 0 01 1 x x x x x x x1 0 1 x x x x x x1 0 0 1 x x x x x1 0 0 0 1 x x x x1 0 0 0 0 1 x x x1 0 0 0 0 0 1 x x1 0 0 0 0 0 0 1 x1 0 0 0 0 0 0 0 10 0 0 0 00 0 0 0 11 1 1 1 01 1 0 1 01 0 1 1 01 0 0 1 00 1 1 1 00 1 0 1 00 0 1 1 00 0 0 1 0输入输出x 1 xx x 11 x x1 0 01 0 01 0 01 0 01 0 01 0 01 0 01 0 0x x xx x xx x x0 0 00 0 10 1 00 1 11 0 01 0 11 1 01 1 11 1 1 1 1 1 1 11 1 1 1 1 1 1 11 1 1 1 1 1 1 10 1 1 1 1 1 1 11 0 1 1 1 1 1 11 1 0 1 1 1 1 11 1 1 0 1 1 1 11 1 1 1 0 1 1 11 1 1 1 1 0 1 11 1 1 1 1 1 0 11 1 1 1 1 1 1 074HC4511:七段显示译码器:十进制或功能输入输出字形LE a b c d e f g0 1 2 3 4 5 6 7 8 9101112131415 01111111111111111111111111111111100 0 00 0 0 100 1 000 1 10 1 0 00 1 0 10 1 1 00 1 1 110 0 01 0 0 11 0 1 01 0 1 11 1 0 01 1 0 11 1 1 01 1 1 11 1 1 1 1 1 00 1 1 0 0 0 01 1 0 1 1 0 11 1 1 1 0 0 10 1 1 0 0 1 11 0 1 1 0 1 10 0 1 1 1 1 01 1 1 0 0 0 01 1 1 1 1 1 11 1 1 1 0 1 10 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 00 0 0 0 0 0 0123456789熄灭熄灭熄灭熄灭熄灭熄灭灯测试x x 0 x x x x 1 1 1 1 1 1 1 8 灭灯x 0 1 x x x x 0 0 0 0 0 0 0 熄灭锁存 1 1 1 x x x x * *输入输出使能选择Y1 0 0 0 0 0 0 0 x x x0 0 00 0 10 1 00 1 11 0 01 0 11 1 00 10 1 1 174HC85:4位数值比较器:74HC283:4位二进制全加器:输入输出功能清零控制信号时钟串行输入并行输入CR CP 右移左移LHHHHx xL LL HL HH Lxx↑↑↑x xx xL xH xx Lx x x xx x x xx x x xx x x xx x x xL L L LLHH H H LH H↑↑x Hx xx x x x74LVC161:4位二进制同步计数器:输入输出清零CR 预支PE使能C E P C E T时钟CP预支数据输入进位TCL H H H H xLHHHx xx xL xx LH Hx↑xx↑x x x xx x x xx x x xx x x xL L L L保持保持保持L##L#5、实验具体设计:CD4532-8位优先编码器:模块设计代码:module CD4532(EI,I,Y,GS,EO);//8位优先编码器input EI;input [7:0] I;output reg [2:0] Y;output reg GS,EO;always (EI,I)beginif(EI==0) begin Y=3'd0; GS=0; EO=0; endelse//当EI=1时,实现优先编码器的功能beginGS=1; EO=0;//当编码器输入信号有效时,设定GS、EO的输出值if(I[7]) Y=3'd7; else//根据I的高位情况对Y的输出进行控制if(I[6]) Y=3'd6; elseif(I[5]) Y=3'd5; elseif(I[4]) Y=3'd4; elseif(I[3]) Y=3'd3; elseif(I[2]) Y=3'd2; elseif(I[1]) Y=3'd1; elseif(I[0]) Y=3'd0;elsebegin Y=3'd0; GS=0; EO=1; end//当编码器输入信号无效时,设定GS、EO的输出值 endendendmodule对应testbench设计代码:`timescale 1ns/1ns //设定仿真时间间隔单位,之后的testbench中这句代码功能类似module CD4532_tb;reg [7:0] D_in;// 设定testbench输入数据类型为reg型 reg EI_in;wire [2:0] Q_result;// / 设定testbench输出数据类型为wire型wire GS_result,EO_result;initialbeginEI_in=0;//初始化相关数据的值D_in=8'b0000_0001;#80 EI_in=1;#80 $stop();//上一个语句执行完毕后的80个时间单位后仿真终止endalways #10 //每隔10个时间单位执行一次beginif(D_in==8'b1000_0000)D_in=8'b0000_0001;elseD_in=(D_in<<1);endCD4532 U1(.EI(EI_in),.I(D_in),.Y(Q_result),.GS(GS_result),.EO(EO_result)); endmodule74X138-3 线-8线译码器:模块设计代码:module _74X138(A,EN,Y);//3 线-8线译码器,输出为低电平有效input [2:0] A;input EN;//使能端output reg [7:0] Y;integer k;always (A,EN)beginY=8'b1111_1111;for(k=0;k<=7;k=k+1)beginif((EN==1)&&(A==k))Y[k]=0;//EN=1时根据输入的A进行译码elseY[k]=1;//使能无效时或输入无效endendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74X138_tb;reg [2:0] A_in;reg EI_in;wire [7:0] Y_result;initialbeginEI_in=0;A_in=3'b000;#80 EI_in=1;#160 $stop();endalways #10beginif(A_in==3'b111)A_in=3'b000;elseA_in=A_in+1;end_74X138 U1(.A(A_in),.EN(EI_in),.Y(Y_result));endmodule74HC4511-七段显示译码器:模块设计代码:module _74HC4511(D,LE,BL,LT,a,b,c,d,e,f,g);//七段显示译码器input [3:0] D;//输入信号端口input LE,BL,LT;//控制信号output reg a,b,c,d,e,f,g;always(LE,BL,LT,D)beginif(LT==0) {a,b,c,d,e,f,g}=7'b111_1111;//显示器全亮else if(BL==0) {a,b,c,d,e,f,g}=7'b000_0000;//显示器全灭else if(LE==0) {a,b,c,d,e,f,g}={a,b,c,d,e,f,g};//显示器保持当前显示elsecase(D)//根据输入的8421BCD码进行译码4'd0: {a,b,c,d,e,f,g}=7'b111_1110;//04'd1: {a,b,c,d,e,f,g}=7'b011_0000;//14'd2: {a,b,c,d,e,f,g}=7'b110_1101;//24'd3: {a,b,c,d,e,f,g}=7'b111_1001;//34'd4: {a,b,c,d,e,f,g}=7'b011_0011;//44'd5: {a,b,c,d,e,f,g}=7'b101_1011;//54'd6: {a,b,c,d,e,f,g}=7'b001_1111;//64'd7: {a,b,c,d,e,f,g}=7'b111_0000;//74'd8: {a,b,c,d,e,f,g}=7'b111_1111;//84'd9: {a,b,c,d,e,f,g}=7'b111_1011;//9default:{a,b,c,d,e,f,g}=7'b000_0000;//非8421BCD码输入时,不译码 endcaseendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC4511_tb;reg [3:0] D_in;reg LE_in,BL_in,LT_in;wire A,B,C,D,E,F,G;initialbegin//开始为全亮LE_in=1;//保持,低电平有效BL_in=1;//全灭,低电平有效LT_in=0;//全亮,低电平有效D_in=4'b0000;#100 begin LE_in=1; BL_in=0; LT_in=1; end//全灭#100 begin LE_in=1; BL_in=1; LT_in=1; end//正常显示 #100 begin LE_in=0; BL_in=1; LT_in=1; end//保持#100 $stop();endalways #10beginif(D_in==4'd9)D_in=4'b0000;elseD_in=D_in+1;end_74HC4511 U1(D_in,LE_in,BL_in,LT_in,A,B,C,D,E,F,G); endmodule74HC151-八选一数据选择器:模块设计代码:module _74HC151(S,D,E,Y0,Y1);//八选一数据选择器input [2:0] S;//控制信号input [7:0] D;//输入信号input E;//使能端output reg Y0,Y1;//Y0,Y1分别为同相和反相输出信号always(E,S,D)beginif(~E)begin Y0=0; Y1=1; end//不工作,输出默认信号elsebegincase(S)//根据控制信号选择不同通道的输入信号作为输出3'b000: begin Y0=D[0]; Y1=~Y0; end//03'b001: begin Y0=D[1]; Y1=~Y0; end//13'b010: begin Y0=D[2]; Y1=~Y0; end//23'b011: begin Y0=D[3]; Y1=~Y0; end//33'b100: begin Y0=D[4]; Y1=~Y0; end//43'b101: begin Y0=D[5]; Y1=~Y0; end//53'b110: begin Y0=D[6]; Y1=~Y0; end//63'b111: begin Y0=D[7]; Y1=~Y0; end//7default: begin Y0=0; Y1=~Y0; end//若控制信号不符合要求则输出默认信号endcaseendendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC151_tb;reg [2:0] S_in;reg [7:0] D_in;reg E_in;wire Y0_result,Y1_result;initialbeginE_in=0;S_in=3'b000;D_in=8'b0010_0110;#80 E_in=1;#80 D_in=8'b1001_1110;#80 E_in=0;#80 $stop();endalways #10beginif(S_in==3'b111)S_in=3'b000;elseS_in=S_in+1;end_74HC151 U1(S_in,D_in,E_in,Y0_result,Y1_result);Endmodule74HC85-4位数值比较器:模块设计代码:module _74HC85(A,B,I0,I1,I2,Fab0,Fab1,Fab2);//4位数值比较器,以下均为高电平有效 input [3:0] A,B;//输入信号input I0,I1,I2;//低位比较结果,依次为低位A=B,A<B,A>Boutput reg Fab0,Fab1,Fab2;//输出信号Fab0,Fab1,Fab2依次为A=B,A<B,A>B.reg F000,F001,F002,F110,F111,F112,F220,F221,F222,F330,F331,F332;//中间节点,依次对应Ai=Bi,Ai<Bi,Ai>Bi.i为位数(0~3)always(A,B,I0,I1,I2)beginif(A[3]>B[3])//比较第4位begin F330=0; F331=0; F332=1; endelse if(A[3]<B[3])begin F330=0; F331=1; F332=0; endelsebegin F330=1; F331=0; F332=0; endif(A[2]>B[2])//比较第3位begin F220=0; F221=0; F222=1; endelse if(A[2]<B[2])begin F220=0; F221=1; F222=0; endelsebegin F220=1; F221=0; F222=0; endif(A[1]>B[1])//比较第2位begin F110=0; F111=0; F112=1; endelse if(A[1]<B[1])begin F110=0; F111=1; F112=0; endelsebegin F110=1; F111=0; F112=0; endif(A[0]>B[0])//比较第1位begin F000=0; F001=0; F002=1; endelse if(A[0]<B[0])begin F000=0; F001=1; F002=0; endelsebegin F000=1; F001=0; F002=0; end//输出结果如下if((F000&&F110&&F220&&F330)&&I0)//低位进位信号出错begin Fab2=0; Fab1=0; Fab0=1; endelse if((F000&&F110&&F220&&F330)&&(~I0&&I1&&I2))//低位进位信号出错begin Fab2=0; Fab1=0; Fab0=0; endelse if((F000&&F110&&F220&&F330)&&(~I0&&~I1&&~I2))//低位进位信号出错begin Fab2=1; Fab1=1; Fab0=0; endelse//低位进位信号正常beginFab2=F332||F330&&F222||F330&&F220&&F112||F330&&F220&&F110&&F002||F330&&F220&&F110&&F000&&I2;Fab1=F331||F330&&F221||F330&&F220&&F111||F330&&F220&&F110&&F001||F330&&F220&&F110&&F000&&I1;Fab0=F330&&F220&&F110&&F000&&I0;endendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC85_tb;reg [3:0] A_in,B_in;reg I0_in,I1_in,I2_in;wire Fab0_result,Fab1_result,Fab2_result;initialbeginI0_in=0;I1_in=0;I2_in=0;A_in=4'b1010;B_in=4'b0111;#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位A_in=4'b0100; B_in=4'b1001; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 begin I0_in=0; I1_in=0; I2_in=0; //低位归位A_in=4'b0010; B_in=4'b0010; end#10 begin I0_in=1; I1_in=0; I2_in=0; end//低位A=B#10 begin I0_in=0; I1_in=1; I2_in=0; end//低位A<B#10 begin I0_in=0; I1_in=0; I2_in=1; end//低位A>B#10 $stop();end_74HC85 U1(A_in,B_in,I0_in,I1_in,I2_in,Fab0_result,Fab1_result,Fab2_result); endmodule74HC283-4位二进制全加器:模块设计代码:module _74HC283(A,B,Ci,Co,S);//4位二进制全加器input Ci;//低位进位信号input [3:0] A,B;//输入信号output reg [3:0] S;//输出结果output reg Co;//高位进位信号Co=C[3]reg [3:0] C,G,P;integer k;always(A,B,Ci)beginfor(k=0;k<4;k=k+1)beginG[k]=A[k]&&B[k];P[k]=A[k]&&~B[k]||~A[k]&&B[k];endC[0]=G[0]||P[0]&&Ci;C[1]=G[1]||P[1]&&C[0];C[2]=G[2]||P[2]&&C[1];C[3]=G[3]||P[3]&&C[2];S[0]=P[0]&&~Ci||~P[0]&&Ci;S[1]=P[1]&&~C[0]||~P[1]&&C[0];S[2]=P[2]&&~C[1]||~P[2]&&C[1];S[3]=P[3]&&~C[2]||~P[3]&&C[2];Co=C[3];endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC283_tb;reg [3:0] A_in,B_in;reg Ci_in;//低位进位信号wire [3:0] S_out;//本位相加结果wire Co_out;//高位进位信号initialbeginCi_in=0;A_in=4'b1010;B_in=4'b0111;#10 begin A_in=4'b0011; B_in=4'b1111; end#10 begin A_in=4'b0101; B_in=4'b1001; end#10 begin A_in=4'b1111; B_in=4'b0010; end#10 $stop();endalways #5beginCi_in=~Ci_in;//循环改变低位进位信号end_74HC283 U1(A_in,B_in,Ci_in,Co_out,S_out);endmodule74HC194-4位双向移位寄存器:模块设计代码:module _74HC194(S0,S1,Dsl,Dsr,CP,CR,D,Q);//4位双向移位寄存器_P339 input S0,S1;//输入端口input Dsr,Dsl;//串行数据输入input CP,CR;//时钟和清零input [3:0] D;//并行数据输入output reg [3:0] Q;//输出结果always(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零elsecase({S1,S0})2'b00:Q<=Q;//输出保持不变2'b01:Q<={Q[2:0],Dsr};//右移,低位移向高位2'b10:Q<={Dsl,Q[3:1]};//左移,高位移向低位2'b11:Q<=D;//并行置数endcaseendendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74HC194_tb;reg [3:0] D_in;//并行数据输入reg S0_in,S1_in;//控制信号输入端口reg Dsr_in,Dsl_in;//串行数据输入reg CP_in,CR_in;//时钟和清零,清零为低电平有效wire [3:0] Q_out;//输出结果initialbeginCP_in=1;CR_in=1;S0_in=1;S1_in=1;//开始先输入串行数据Dsr_in=0;Dsl_in=0;D_in=4'b0110;#243 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号endalways #15//循环调整控制输入信号,周期60nsbegincase({S1_in,S0_in})2'b00:begin S1_in=0; S0_in=1; end2'b01:begin S1_in=1; S0_in=0; end2'b10:begin S1_in=1; S0_in=1; end2'b11:begin S1_in=0; S0_in=0; endendcaseendalways #10//循环调整串行数据输入信号,周期40nsbegincase({Dsr_in,Dsl_in})2'b00:begin Dsr_in=0; Dsl_in=1; end2'b01:begin Dsr_in=1; Dsl_in=0; end2'b10:begin Dsr_in=1; Dsl_in=1; end2'b11:begin Dsr_in=0; Dsl_in=0; endendcaseend_74HC194 U1(S0_in,S1_in,Dsl_in,Dsr_in,CP_in,CR_in,D_in,Q_out);endmodule74LVC161-4位二进制同步计数器:模块设计代码:module _74LVC161(CEP,CET,PE,CP,CR,D,TC,Q);//4位二进制同步计数器_P340 input CEP,CET,PE,CP,CR;//输入端口input [3:0] D;//并行数据输入output TC;//进位输出output reg [3:0] Q;//输出结果wire CE;assign CE=CEP&CET;//CE=1时计数器计数assign TC=CET&PE&(Q==4'b1111);//产生进位输出信号always(posedge CP, negedge CR)beginif(~CR) Q<=4'b0000;//异步清零else if(~PE) Q<=D;//PE=0,同步输入数据else if(CE)beginif((TC==1)&&(Q==4'b1111))Q<=4'b0000;//计数器计满后自动归零elseQ<=Q+1'b1;//加1计数endelse Q<=Q;//保持输出不变endendmodule对应testbench设计代码:`timescale 1ns/1nsmodule _74LVC161_tb;reg CEP_in,CET_in,PE_in,CP_in,CR_in;//输入端口reg [3:0] D_in;//并行数据输入wire TC_out;//进位输出wire [3:0] Q_out;//输出结果initialbeginCEP_in=0;CET_in=1;PE_in=0;CP_in=1;CR_in=1;D_in=4'b1101;#10 begin PE_in=1;D_in=4'b1001; end#20 begin CEP_in=1; CET_in=1; end#220 begin PE_in=0; end#23 CR_in=~CR_in;#20 $stop();endalways #5beginCP_in=~CP_in;//周期为10ns的时钟信号end_74LVC161 U1(CEP_in,CET_in,PE_in,CP_in,CR_in,D_in,TC_out,Q_out);endmodule6、输出仿真波形以及相关数据:CD4532-8位优先编码器:以下波形由上至下依次是:D_in, EI_in, Q_result, GS_result, EO_result;74X138-3 线-8线译码器:以下波形由上至下依次是:A_in, EI_in, Y_result;74HC4511-七段显示译码器:以下波形由上至下依次是:D_in, LE_in, LT_in, A, B, C, D, E, F, G;74HC151-八选一数据选择器:以下波形由上至下依次是:S_in, D_in, E_in, Y0_result, Y1_result;74HC85-4位数值比较器:以下波形由上至下依次是:A_in, B_in, I0_in, I1_in, I2_in, Fab0_result, Fab1_result, Fab2_result;74HC283-4位二进制全加器:以下波形由上至下依次是:A_in, B_in, S_out, Co_out;74HC194-4位双向移位寄存器:以下波形由上至下依次是:D_in, S0_in, S1_in,Dsr_in, Dsl_in, CP_in, CR_in, Q_out;74LVC161-4位二进制同步计数器:以下波形由上至下依次是:CEP_in, CET_in, PE_in, CP_in, CR_in, D_in, T_out, Q_out;7、仿真结果分析:仿真输出波形符合预期,与芯片的功能表描述的功能相符。

Verilog数字钟数电实验报告

专业:电子信息工程班级:电信1305班日期:2015.5.5 第3次实验姓名:康健组别: 6 指导教师:成绩:实验课题:EDA多功能数字钟1、已知条件Quartus II软件、FPGA实验开发装置。

2、主要技术指标以数字形式显示时、分、秒的时间;小时计数器为同步24进制;要求手动校时、校分。

3、实验用仪器PC、FPGA开发板、示波器、稳压电源等4、电路工作原理所谓的时钟,其实本质上就是计数器。

以开发板上的晶振时钟作为时间基准。

然后通过分频模块(计数器)进行分频,得到1Hz的脉冲信号作为秒的信号脉冲,然后用模60的计数器构成秒的计数单元。

每记60下就自动清零且产生进位信号。

将这个进位信号作为分的计数器的使能信号,其中,分计数器也是模为60的计数器。

这里的计数器都是由模10和模6 组成的BCD码的计数器。

个位和十位分别是一个四位的数字。

同理,每记满60,分计数器就会产生一个进位信号,这个进位信号作为小时的使能信号。

小时的计数器就是模24的BCD计数器。

注意,这里的整个电路都是用1HZ的频率作为时间脉冲的,也就是说,这个电路是同步时序的电路。

通过使能,来控制各个部分的时序逻辑。

将小时和分的使能信号在总是为有效电平和下一级进位信号做选择,就是时钟调时状态和正常计时状态的切换。

当在调时状态的时候,时钟每完成一个周期,无论是分钟还是小时,就向前加1,。

最后,将分钟和小时通过译码器连接到数码管。

将秒直接连接到LED灯,完成整个工程的基本功能(扩展功能见选作的实验报告)。

5、电路设计与调试1、模10计数器的设计2、模6计数器的设计3、模60计数器设计(分、秒计数)4、模24计数器设计(小时计数)5、译码器设计6、分频器设计7、时钟整体结构设计6、电路的仿真:1、小时进位的验证:2、分钟进位的验证:3、秒进位的验证:4、testbench的源代码:7、主要技术指标的测量:板子上电以后,将程序下载到板子里面,按复位(rst),时钟开始从零点正常计时。

数电编程实验报告

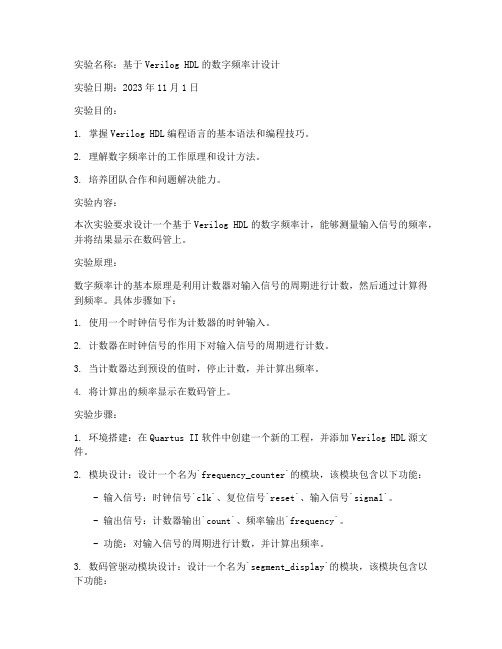

实验名称:基于Verilog HDL的数字频率计设计实验日期:2023年11月1日实验目的:1. 掌握Verilog HDL编程语言的基本语法和编程技巧。

2. 理解数字频率计的工作原理和设计方法。

3. 培养团队合作和问题解决能力。

实验内容:本次实验要求设计一个基于Verilog HDL的数字频率计,能够测量输入信号的频率,并将结果显示在数码管上。

实验原理:数字频率计的基本原理是利用计数器对输入信号的周期进行计数,然后通过计算得到频率。

具体步骤如下:1. 使用一个时钟信号作为计数器的时钟输入。

2. 计数器在时钟信号的作用下对输入信号的周期进行计数。

3. 当计数器达到预设的值时,停止计数,并计算出频率。

4. 将计算出的频率显示在数码管上。

实验步骤:1. 环境搭建:在Quartus II软件中创建一个新的工程,并添加Verilog HDL源文件。

2. 模块设计:设计一个名为`frequency_counter`的模块,该模块包含以下功能:- 输入信号:时钟信号`clk`、复位信号`reset`、输入信号`signal`。

- 输出信号:计数器输出`count`、频率输出`frequency`。

- 功能:对输入信号的周期进行计数,并计算出频率。

3. 数码管驱动模块设计:设计一个名为`segment_display`的模块,该模块包含以下功能:- 输入信号:计数器输出`count`、数码管段选信号`seg`。

- 输出信号:数码管显示信号`display`。

- 功能:将计数器输出转换为数码管显示信号。

4. 顶层模块设计:设计一个名为`top`的顶层模块,该模块包含以下功能:- 输入信号:时钟信号`clk`、复位信号`reset`、输入信号`signal`。

- 输出信号:数码管显示信号`display`。

- 功能:调用`frequency_counter`和`segment_display`模块,实现数字频率计的功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

// 本实验的代码还未提交,但是都进行仿真通过。

不保证老师那边没问题。

// 1、N进制加法计数器异步清零// 这里是24进制,更改下对应的二进制位数和进制就可以了。

module count_24(clk, reset, enable, full, out);input clk, reset, enable;output full;output [4:0] out;reg [4:0] out;always @(posedge clk or posedge reset)beginif(reset)out <= 5'b00000;elsebeginif(enable)beginif(out == 23)out <= 0;elseout <= out + 1;endelseout <= out;endendassign full = (out == 23) ? 1 : 0;endmodule// 2、16位数控分频器只能进行偶数次分频,最小二分频module div_16bits(clk, rst, ctrl, fout); // only even divinput clk, rst;input [15:0] ctrl;output fout;reg fout, full;reg [15:0] data;always @(posedge clk or posedge rst) // 异步清零beginif(rst)data <= {16{1'b0}};elsebeginif(data == {16{1'b1}})begindata <= ctrl;full <= 1'b1;endelsebegindata <= data + 1'b1;full <= 1'b0;endendendalways @(posedge full) // 进行二分频,同时调节占空比为 50% fout = ~fout;endmodule// 3、含并行置位的8位移位寄存器设计module reg_pe8(clk, func, para, ser_in, qout, data);input clk, func, ser_in; // func :功能选择 1:移位 0:置位input [7:0] para; // 并行输入output qout; // 输出左移位output [7:0] data; // 并行输出reg qout;reg [7:0] data;always @(posedge clk)beginif(~func)begindata <= para;qout <= para[7];endelse{qout, data[7:0]} <= {data[7:0], ser_in};endendmodule// 4、16位定时计数器设计、// 顶层模块module time_count_16(taclk, aclk, smclk, inclk, tasel,divder, ctrl, taclr, ta_ifg, t_clk, count);input taclk, aclk, smclk, inclk; // clk input to select input [1:0] tasel; // 时钟信号选择input taclr;output ta_ifg, t_clk;input [1:0] divder;input [3:0] ctrl;output [3:0] count;reg [4:0] div;wire clk;always @(divder)case(divder)2'd0: div = 1;2'd1: div = 2;2'd2: div = 4;2'd3: div = 8;endcase// 模块例化,差不多相当于函数调用注意:.taclk(taclk) 前面有个点号tasel_4 taclk_sel_ic(taclk, aclk, smclk, inclk, tasel, clk);div_16bits div_clk_ic(clk, taclr, div, t_clk);count_16bits count_clk_ic(t_clk, taclr, ctrl, count, ta_ifg);endmodule// 模块一:时钟选择模块输入四个时钟: TACLK, ACLK, SMCLK, INCLKmodule tasel_4(taclk, aclk, smclk, inclk, tasel, clk_out);input taclk, aclk, smclk, inclk;input [1:0] tasel;output clk_out;reg clk_out;always @(tasel)case(tasel)2'b00: clk_out = taclk;2'b01: clk_out = aclk;2'b10: clk_out = smclk;2'b11: clk_out = inclk;endcaseendmodule// 模块二:分频模块,对上面选择的时钟信号进行分频,可是写的分频器不能进行一分// 频,只能进行偶数次分频,即最小二分频。

module div_16bits(clk, rst, ctrl, fout); // only even divinput clk, rst;input [15:0] ctrl;output fout;reg fout, full;reg [15:0] data;always @(posedge clk or posedge rst) // 异步清零beginif(rst)data <= {16{1'b0}};elsebeginif(data == {16{1'b1}})begindata <= ctrl;full <= 1'b1;endelsebegindata <= data + 1'b1;full <= 1'b0;endendendalways @(posedge full) // 进行二分频,同时调节占空比为 50%fout = ~fout;endmodule// 模块三: 16位计数器(TAR)可进行预置数module count_16bits(clk, reset, data_in, data_out, full); // data_in 预置数input clk, reset;output full;input [3:0] data_in;output [3:0] data_out;reg [3:0] data_out;always @(posedge clk or posedge reset) // 异步清零beginif(reset)data_out <= data_in;elsebeginif(data_out == 4'b1111)data_out <= data_in;elsedata_out <= data_out + 1'b1;endendassign full = (data_out == 4'b1111) ? 1'b1 : 1'b0;endmodule// 5、频率和占空比可调PWM 设计// 顶层模块// clk 时钟信号 ctrl 周期控制字 pwm_ctrl 脉宽控制字// 上届的实验指导书有模块结构图,对照着看就明白了。

module pwm_ctrl(clk, ctrl, pwm_ctrl, out);input clk;input [7:0] ctrl, pwm_ctrl;output out;wire fout;wire [7:0] counter;// 同上例进行模块例化div_8 div_8_ic(clk, ctrl, fout);counter_8 counter_8_ic(fout, counter);comp_8 comp_8_ic(counter, pwm_ctrl, out); endmodule// 模块一: 8位数控分频器module div_8(clk, ctrl, fout);input clk;input [7:0] ctrl;output fout;reg fout, out_tmp;reg [7:0] counter;always @(posedge clk)beginif(counter == 8'b1111_1111)begincounter <= ctrl;out_tmp <= 1'b1;endelsebegincounter <= counter + 1'b1;out_tmp <= 1'b0;endendalways @(posedge out_tmp)fout <= ~fout;endmodule// 模块二 8位计数器module counter_8(clk, counter);input clk;output [7:0] counter;reg [7:0] cnt_temp;assign counter = cnt_temp;always @(posedge clk)beginif(cnt_temp == 8'b1111_1111)cnt_temp <= 8'b0000_0000;elsecnt_temp <= cnt_temp + 1'b1;endendmodule// 模块三数值比较器module comp_8(counter, ctrl, pwm_out);input [7:0] counter, ctrl;output pwm_out;assign pwm_out = (counter > ctrl) ? 1'b1 : 1'b0; endmodule。