RK2705 Datasheet

EG8405datasheet_V1.0

3W防失真、超低EMI立体声D类音频功放版本变更记录3W防失真、超低EMI立体声D类音频功放目录1. 特点 (3)2. 概述 (3)3. 应用领域 (4)4. 引脚 (4)4.1. 引脚定义 (4)4.2. 引脚描述 (4)5. 结构框图 (5)6. 典型应用电路 (6)7. 电气特性 (6)7.1 极限参数 (6)7.2 典型参数 (7)7.3 直流特性 (7)7.4 交流特性 (7)7.5 模拟特性 (8)8. 应用信息 (8)8.1工作模式 (8)8.2防失真功能(NCN) (9)8.3电源退耦 (10)8.4输入电容 (10)8.5模拟基准旁路电容(C BYP) (10)8.6电源开启/关闭时噼噗噪声 (11)8.7欠压锁定(UVLO) (11)8.8短路电流保护(SCP) (11)8.9过温保护(OTP) (11)8.10电磁辐射(EMI) (11)9. 封装尺寸 (12)3W防失真、超低EMI立体声D类音频功放EG8405芯片数据手册V1.01. 特点⏹防失真功能⏹宽的工作电源2.5V-5.5V⏹超优异的全带宽EMI抑制性能⏹免LC滤波器数字调制,直接驱动扬声器⏹高输出功率:3.0W@PVDD=VDD=5.0V,R L=4Ω,THD+N=10%⏹高效率:88%@PVDD=VDD=5.0V, R L=4Ω,P O=1W⏹低THD+N:0.1%@PVDD=VDD=5.0V, R L=4Ω,P O=1W⏹通道隔离度:80dB@f IN=1KHz,A V=18dB⏹高信噪比SNR: 90dB@ PVDD=VDD=5.0V, A V=18dB⏹优异的“噼噗-咔嗒”(Pop-Click)噪声抑制性能⏹关断功能⏹过流保护功能⏹过热保护功能⏹欠压保护功能⏹无铅SOP16封装2. 概述EG8405是一款带防失真功能且具有超低EMI的立体声免输出滤波器D类音频功率放大器。

在电源电压5V、THD+N=10%、4Ω负载的条件下,输出高达3W的功率,在性能与AB类放大器相媲美的同时,效率高达88%。

LM7905_DataSheet

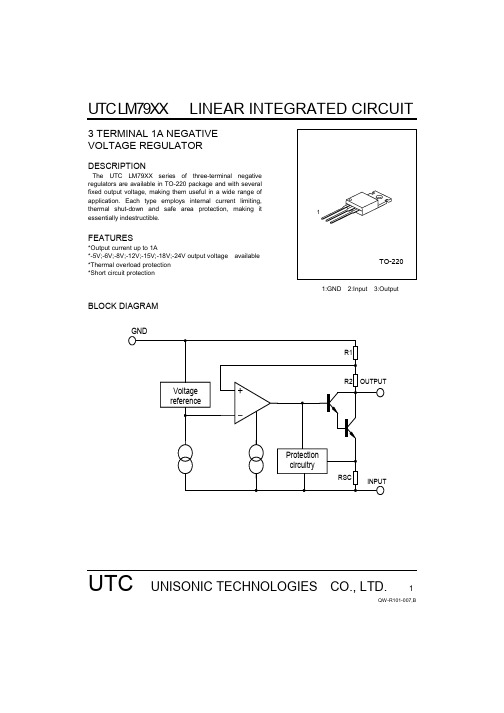

UTC LM79XXLINEAR INTEGRATED CIRCUITUTC UNISONIC TECHNOLOGIES CO., LTD.1QW-R101-007,B3 TERMINAL 1A NEGATIVE VOLTAGE REGULATORDESCRIPTIONThe UTC LM79XX series of three-terminal negativeregulators are available in TO-220 package and with several fixed output voltage, making them useful in a wide range of application. Each type employs internal current limiting, thermal shut-down and safe area protection, making it essentially indestructible.FEATURES*Output current up to 1A*-5V;-6V;-8V;-12V;-15V;-18V;-24V output voltage available *Thermal overload protection *Short circuit protection1:GND 2:Input 3:OutputBLOCK DIAGRAMUTC LM79XXLINEAR INTEGRATED CIRCUITUTC UNISONIC TECHNOLOGIES CO., LTD.2QW-R101-007,BABSOLUTE MAXIMUM RATINGS (Ta=25°C) PARAMETER SYMBOLVALUE UNITInput voltageVi -35 V Thermal resistance junction-airR θ JA 65 °C /W Thermal resistance junction-casesR θ JC 5 °C /W Operating Temperature Topr 0 ~ +125 °C Storage TemperatureTstg-65 ~ +150°CUTC7905 ELECTRICAL CHARACTERISTICS(Refer to test circuits, 0<Tj<125°C ,Io=500mA,Vi=-10V,Ci=33uF,Co=1uF, unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITTj=25°C-4.80-5.0 -5.20 V Output voltageVo 5.0mA<Io<1.0A,Po<15W Vi=-7V to -20V -4.75 -5.25VLine regulation ∆Vo Tj =25°C,Vi=-7V to -25V 10 100 mV Tj=25°C,Vi=-8V to -12VmV Load regulation ∆Vo Tj =25°C,Io=5.0mA to 1.5A10 100 mV Tj=25°C,Io=250mA to 750mA 3 50 mV Quiescent current I Q Tj=25°C3 6 mA Quiescent current change ∆I QIo=5mA to 1.0A 0.05 0.5 mA Vi=-7V to -25V 0.1 1.3 mA Output voltage drift ∆Vo/∆T Io =5mA -0.4 mV/°C Output noise voltage V N f=10hz to 100kHz,Ta=25°C 100 µV Ripple rejection RR f=120Hz, Vi=-8V to -18V 54 60 dB Dropout voltage Vo Io=1.0A,Tj=25°C 2 V Short circuit current Isc Vi=-35V,Ta=25°C 300 mA peak current Ipk Tj=25°C2.2 AUTC7906 ELECTRICAL CHARACTERISTICS(Refer to test circuits, 0<Tj<125°C ,Io=500mA,Vi=-11V,Ci=2.2uF,Co=1uF,unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITTj=25°C-5.76-6.00 -6.24 V Output voltageVo5.0mA<Io<1.0A,Po<15W Vi=-8V to -21V -5.70 -6.30 VLine regulation ∆Vo Tj =25°C,Vi=-8V to -25V10 120 mVTj=25°C,Vi=-9V to -13V5 60 mV Load regulation ∆Vo Tj =25°C,Io=5.0mA to 1.5A10 120 mVTj=25°C,Io=250mA to 750mA 3 60 mV Quiescent currentI Q Tj=25°C3 6 mA Quiescent current change ∆I QIo=5mA to 1.0A 0.5 mAVi=-8V to -25V 1.3 mAOutput voltage drift ∆Vo/∆T Io =5mA -0.5 mV/°COutput noise voltage V N f=10hz to 100kHz,Ta=25°C 130 µV Ripple rejection RR f=120Hz, Vi=-9V to -19V 54 60 dB Dropout voltage Vo Io=1.0A,Tj=25°C 2 V Short circuit current Isc Vi=-35V,Ta=25°C 300 mA peak currentIpk Tj=25°C2.2 AUTC LM79XX LINEAR INTEGRATED CIRCUITUTC UNISONIC TECHNOLOGIES CO., LTD.3QW-R101-007,BUTC7908 ELECTRICAL CHARACTERISTICS(Refer to test circuits, 0<Tj<125°C ,Io=500mA,Vi=-14V,Ci=2.2uF,Co=1uF,unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITTj=25°C-7.68-8.0 -8.32 V Output voltageVo5.0mA<Io<1.0A,Po<15W Vi=-10.5V to -23V -7.60 -8.40 VLine regulation ∆Vo Tj =25°C,Vi=-10.5V to -25V 10 100 mV Tj=25°C,Vi=-11.5V to -17V5 80 mV Load regulation ∆Vo Tj =25°C,Io=5.0mA to 1.5A12 160 mV Tj=25°C,Io=250mA to 750mA4 80 mV Quiescent current I Q Tj=25°C3 6 mA Quiescent current change ∆I QIo=5mA to 1.0A 0.05 0.5 mA Vi=-11.5V to -25V 0.1 1.0 mA Output voltage drift ∆Vo/∆T Io =5mA -0.6 mV/°C Output noise voltage V N f=10hz to 100kHz,Ta=25°C 175 µV Ripple rejection RR f=120Hz, Vi=-11.5V to -21.5V 54 60 dB Dropout voltage Vo Io=1.0A,Tj=25°C 2 V Short citcuit current Isc Vi=-35V,Ta=25°C 300 mA peak current Ipk Tj=25°C2.2 AUTC7912 ELECTRICAL CHARACTERISTICS(Refer to test circuits, 0<Tj<125°C ,Io=500mA,Vi=-18V,Ci=2.2uF,Co=1uF,unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITTj=25°C-11.52-12.0 -12.48 V Output voltageVo5.0mA<Io<1.0A,Po<15W Vi=-14.5V to -27V -11.40 -12.60 V Line regulation ∆Vo Tj =25°C,Vi=-14.5V to -30V12 240 mVTj=25°C,Vi=-16V to -22V6 120 mV Load regulation ∆Vo Tj =25°C,Io=5.0mA to 1.5A12 240 mVTj=25°C,Io=250mA to 750mA 4 120 mV Quiescent currentI Q Tj=25°C3 6 mA Quiescent current change ∆I QIo=5mA to 1.0A 0.05 0.5 mAVi=-14.5V to -30V 0.1 1.0 mAOutput voltage drift ∆Vo/∆T Io =5mA -0.8 mV/°COutput noise voltage V N f=10hz to 100kHz,Ta=25°C 200 µV Ripple rejection RR f=120Hz, Vi=-15V to -25V 54 60 dB Dropout voltage Vo Io=1.0A,Tj=25°C 2 V Short circuit current Isc Vi=-35V,Ta=25°C 300 mA peak currentIpk Tj=25°C2.2 AUTC LM79XX LINEAR INTEGRATED CIRCUITUTC UNISONIC TECHNOLOGIES CO., LTD.4QW-R101-007,BUTC7915 ELECTRICAL CHARACTERISTICS(Refer to test circuits, 0<Tj<125°C , Io=500mA,Vi=-23V,Ci=2.2uF,Co=1uF,unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITTj=25°C-14.40-15.0 -15.60 V Output voltageVo5.0mA<Io<1.0A,Po<15W Vi=-17.5V to -30V -14.25 -15.75 VLine regulation ∆Vo Tj =25°C,Vi=-17.5V to -30V 12 300 mV Tj=25°C,Vi=-20V to -26V6 150 mV Load regulation ∆Vo Tj =25°C,Io=5.0mA to 1.5A 12 300 mV Tj=25°C,Io=250mA to 750mA 4 150 mV Quiescent current I Q Tj=25°C3 6 mA Quiescent current change ∆I QIo=5mA to 1.0A 0.05 0.5 mA Vi=-17.5V to -30.5V 0.1 1.0 mA Output voltage drift ∆Vo/∆T Io =5mA -0.9 mV/°C Output noise voltage V N f=10hz to 100kHz,Ta=25°C 250 µV Ripple rejection RR f=120Hz, Vi=-18.5V to -28.5V 54 60 dB Dropout voltage Vo Io=1.0A,Tj=25°C 2 V Short circuit current Isc Vi=-35V,Ta=25°C 300 mA peak current Ipk Tj=25°C2.2 AUTC7918 ELECTRICAL CHARACTERISTICS(Refer to test circuits, 0<Tj<125°C ,Io=500mA,Vi=-27V,Ci=2.2uF,Co=1uF,unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITTj=25°C-17.28-18.0 -18.72 V Output voltageVo5.0mA<Io<1.0A,Po<15W Vi=-21V to -33V -17.10 -18.90 V Line regulation ∆Vo Tj =25°C,Vi=-21V to -33V15 360 mVTj=25°C,Vi=-24V to -30V8 180 mV Load regulation ∆Vo Tj =25°C,Io=5.0mA to 1.5A15 360 mVTj=25°C,Io=250mA to 750mA 5.0 180 mV Quiescent currentI Q Tj=25°C3 6 mA Quiescent current change ∆I QIo=5mA to 1.0A 0.5 mAVi=-21V to -32V 1.0 mAOutput voltage drift ∆Vo/∆T Io =5mA -1 mV/°COutput noise voltage V N f=10hz to 100kHz,Ta=25°C 300 µV Ripple rejection RR f=120Hz, Vi=-22V to -32V 54 60 dB Dropout voltage Vo Io=1.0A,Tj=25°C 2 V Short circuit current Isc Vi=-35V,Ta=25°C 300 mA peak currentIpk Tj=25°C2.2 AUTC LM79XX LINEAR INTEGRATED CIRCUITUTC UNISONIC TECHNOLOGIES CO., LTD.5QW-R101-007,BUTC7924 ELECTRICAL CHARACTERISTICS(Refer to test circuits, 0<Tj<125°C ,Io=500mA,Vi=-33V,Ci=2.2uF,Co=1uF,unless otherwise specified)PARAMETER SYMBOL TEST CONDITIONS MIN TYP MAX UNITTj=25°C-23.04-24 -24.96 V Output voltageVo5.0mA<Io<1.0A,Po<15W Vi=-27V to -38V -22.80 -25.20 VLine regulation ∆Vo Tj 25°C,Vi=-27V to -38V15 480mVTj=25°C,Vi=-30V to -36V8 240 mV Load regulation ∆Vo Tj 25°C,Io=5.0mA to 1.5A15 480 mVTj=25°C,Io=250mA to 750mA 5.0 240 mV Quiescent currentI Q Tj=25°C3 6 mA Quiescent current change ∆I QIo=5mA to 1.0A 0.5 mAVi=-27V to -38V 1.0 mAOutput voltage drift ∆Vo/∆T Io =5mA -1 mV/°COutput noise voltage V N f=10hz to 100kHz,Ta=25°C 400 µV Ripple rejection RR f=120Hz, Vi=-28V to -38V 54 60 dB Dropout voltage Vo Io=1.0A,Tj=25°C 2 V Short circuit current Isc Vi=-35V,Ta=25°C 300 mA peak currentIpk Tj=25°C2.2 AAPPLICATION CIRCUITSFig.1 Fixed output regulatorFig.2 Split power supply(+-15V,1A)UTC LM79XX LINEAR INTEGRATED CIRCUITFig.3 Circuit for increasing output voltageUTC UNISONIC TECHNOLOGIES CO., LTD. 6QW-R101-007,B。

XLIN__GC2755 CSP DataSheet release V1.0

1.2 Features

Standard optical format of 1/5 inch Output formats: Raw Bayer 10bit/8bit Power supply requirement: AVDD28: 2.7~3.0V DVDD18: 1.7~1.9V IOVDD: 1.7~3.0V PLL support Windowing support MIPI interface support Horizontal/Vertical mirror Image processing module Package: CSP/COB/wafer

Power Consumption SNR Dark Current Sensitivity Dynamic range Operating temperature: Stable Image temperature Optimal lens chief ray angle(CRA) Package type Input clock frequency

1/5’’ Full HD CMOS Image Sensor GC2755 CSP Datasheet V1.0

2014-06-30

GalaxyCore Inc.

GC2755 CMOS Image Sensor

Revision History

Version 1.0 2014.06.30 Document Release

1.4 Technical Specifications

Parameter

Optical Format Pixel Size Active pixel array ADC resolution Max Frame rate Power Supply

GC2755 CSP DataSheet_规格书_V1.0

GC2755 Datasheet

2 / 30

GC2755 CMOS Image Sensor

Content

1. Sensor Overview ............................................................. 4

1.1 General Description ...................................................................................... 4 1.2 Features......................................................................................................... 4 1.3 Application ................................................................................................... 5 1.4 Technical Specifications ............................................................................... 5

6. Two-wire Serial Bus Communication ............................ 16

6.1 Protocol....................................................................................................... 16 6.2 Serial Bus Timing ....................................................................................... 17

施工材料物料表

Required Item(s) for Designer Approval Prior Fabrication 交由业主单位审核的要求

p Seaming Diagram 车缝加工图 p Strike-Off 印刷图 p Finish Sample 完成面样品 p Cutting 拼接对缝图

p Shop Dwgs 设计深化图 n Prototype 实品打样 p Certificate 检测证明 p LEED 绿色认证要求

PICTORIAL VIEW NOT IN SCALE

Item Code 项目编号

Description 项目说明

Location 位置

PT-01

白色哑光乳胶漆

墙面/石膏板天花区/展车区 墙面

Detailed Specification 详细内容

Finish/Color 饰面/颜色

Dulux 83YY 88/033 Clinic White

p Shop Dwgs 设计深化图 n Prototype 实品打样 p Certificate 检测证明 p LEED 绿色认证要求

Notes 备注

图片只作参考之用承办商必须以实际尺寸为准。

9

PROJECT 工程名称

环旭电子项目—工装工程

PROJECT NO. 工程编号

ISSUE DATE 递交日期

Notes 备注

图片只作参考之用承办商必须以实际尺寸为准。

5

PROJECT 工程名称

环旭电子项目—工装工程

Revision Date 修改日期

PROJECT NO. 工程编号

ISSUE DATE 递交日期

MATERIAL SPECIFICATIONS 材料规范

XL7025 DC-DC转换芯片演示板说明书

页数:第1 页,共7 页描述221073A01是为产品XL7025制作的演示板,用于DC16V~75V输入,输出15V,输出最大0.3A的应用演示,最高转换效率可以达到85%以上。

XL7025是开关降压型DC-DC转换芯片,最高输入电压100V;固定开关频率150KHz,可减小外部元器件尺寸。

芯片具有出色的线性调整率与负载调整率,输出电压支持1.25V~20V间任意调节。

芯片内部集成过流保护、过温保护、短路保护等可靠性模块。

XL7025为TO252-5L封装,采用标准外部元器件,应用灵活。

DEMO原理图D2VOUT=1.25*(1+R2/R1)引脚介绍页数:第2 页,共7 页物料清单2.CINA、D3用于输入尖峰电压吸收。

性能数据转换效率(不包含输入防反接部分电路)页 数:第 3 页, 共 7 页转换效率: 线性调整率和负载调整率:0.100.150.200.250.3020253035404550556065707580859095Efficiency VS Output currentE f f i c i e n c y (%)Ouput current(A) VIN=24V,VOUT=15V,IOUT=0.1~0.3A VIN=36V,VOUT=15V,IOUT=0.1~0.3A VIN=48V,VOUT=15V,IOUT=0.1~0.3A VIN=60V,VOUT=15V,IOUT=0.1~0.3A VIN=72V,VOUT=15V,IOUT=0.1~0.3A0.100.150.200.250.3014.214.414.614.815.015.215.415.615.8Output voltage VS Output currentO u t p u t v o l t a g e (V )Output current(mA)VIN=24V,VOUT=15V,IOUT=0.1A~0.3A VIN=36V,VOUT=15V,IOUT=0.1A~0.3A VIN=48V,VOUT=15V,IOUT=0.1A~0.3A VIN=60V,VOUT=15V,IOUT=0.1A~0.3A VIN=72V,VOUT=15V,IOUT=0.1A~0.3A热插拔上电输出电压波形:VIN=36VIOUT=0AIOUT=0.3AVIN=48VIOUT=0AIOUT=0.3A页数:第4 页,共7 页VIN=60VIOUT=0A IOUT=0.3A蓝色通道:输入电压波形,10V/格;紫色通道:输出电压波形,5V/格;秒格:1mS/格。

NEC2705

PHOTOCOUPLERPS2705-1HIGH ISOLATION VOLTAGE AC INPUT RESPONSE TYPE SOP MULTI PHOTOCOUPLER−NEPOC Series −The mark shows major revised points.Document No. PN10243EJ02V0DS (2nd edition) Date Published March 2006 CP(K)©NEC Compound Semiconductor Devices, Ltd. 1988, 2006DESCRIPTIONThe PS2705-1 is an optically coupled isolator containing a GaAs light emitting diode and an NPN silicon phototransistor.This package is SOP (Small Outline Package) type and has shield effect to cut off ambient light. It is designed for high density mounting applications.FEATURES• AC input response• High isolation voltage (BV = 3 750 Vr.m.s.) • High current transfer ratio (CTR = 100% TYP.) • SOP (Small Outline Package) type• High-speed switching (t r = 3 µs TYP., t f = 5 µs TYP.) • Ordering number of taping product : PS2705-1-F3, F4 • Safety standards• UL approved: File No. E72422 • BSI approved: File No. 8219/8220 • CSA approved: File No. CA 101391• DIN EN60747-5-2 (VDE0884 Part2) approved (Option)APPLICATIONS• Hybrid IC • Telephone/FAX • FA/OA equipment• Programmable logic controllers • Power supplyData Sheet PN10243EJ02V0DS2PACKAGE DIMENSIONS (in millimeters)MARKING EXAMPLEData Sheet PN10243EJ02V0DS3ORDERING INFORMATIONPart NumberOrder NumberSolder Plating SpecificationPacking StyleSafety StandardApprovalApplication Part Number *1PS2705-1 PS2705-1-A Pb-Free Magazine case 100 pcs Standard products PS2705-1 PS2705-1-F3PS2705-1-F3-AEmbossed Tape 3 500 pcs/reel (UL, BSI, CSA PS2705-1-F4 PS2705-1-F4-Aapproved) PS2705-1-V PS2705-1-V-A Magazine case 100 pcs DIN EN60747-5-2 PS2705-1-V-F3 PS2705-1-V-F3-AEmbossed Tape 3 500 pcs/reel(VDE0884 Part2)PS2705-1-V-F4 PS2705-1-V-F4-A Approved (Option)*1 For the application of the Safety Standard, following part number should be used.Data Sheet PN10243EJ02V0DS4ABSOLUTE MAXIMUM RATINGS (T A = 25°C, unless otherwise specified)Parameter Symbol Ratings UnitDiode Forward Current (DC) I F± 50mAPower Dissipation Derating∆P D /°C 0.8 mW/°CPower Dissipation P D 80 mWPeak Forward Current *1I FP ± 1 ATransistor Collector to Emitter Voltage V CEO 40 VEmitter to Collector VoltageV ECO 6 V Collector Current I C 80 mAPower Dissipation Derating∆P C /°C 1.5 mW/°CPower Dissipation P C 150 mWIsolation Voltage *2BV 3 750 Vr.m.s. Operating Ambient Temperature T A –55 to +100 °C Storage TemperatureT stg–55 to +150°C*1 PW = 100 µs, Duty Cycle = 1%*2 AC voltage for 1 minute at T A = 25°C, RH = 60% between input and output Pins 1-2 shorted together, 3-4 shorted together.Data Sheet PN10243EJ02V0DS5ELECTRICAL CHARACTERISTICS (T A = 25 °C)Parameter Symbol Conditions MIN. TYP. MAX. UnitDiode Forward VoltageV FI F = ± 5 mA 1.1 1.4 V Terminal Capacitance C t V = 0 V, f = 1 MHz 60pF Transistor Collector to Emitter DarkCurrentI CEOI F = 0 mA, V CE = 40 V100nACoupledCurrent Transfer Ratio (I C /I F )*1CTR I F = ± 5 mA, V CE = 5 V 50100 300 %CTR Ratio *2CTR 1/CTR 2I F = ± 5 mA, V CE = 5 V 0.3 1.0 3.0Collector Saturation VoltageV CE (sat)I F = ± 10 mA, I C = 2 mA0.3 VIsolation Resistance R I-O V I-O = 1 kV DC 1011Ω Isolation Capacitance C I-O V = 0 V, f = 1 MHz0.4pFRise Time *3 t r V CC = 5 V, I C = 2 mA, R L = 100 Ω 3 µsFall Time *3t f5*1 CTR rank M: 50 to 150 (%) L: 100 to 300 (%)N: 50 to 300 (%)*2 CTR 1 = I C1/I F1, CTR 2 = I C2/I F2I F1I F2V CE*3 Test circuit for switching timeV CCOUTΩData Sheet PN10243EJ02V0DS6TYPICAL CHARACTERISTICS (T A = 25°C, unless otherwise specified)1005025075255075100Ambient Temperature T A (˚C)D i o d e P o w e r D i s s i p a t i o n P D (m W )DIODE POWER DISSIPATION vs.AMBIENT TEMPERATURE20015010050025*******Ambient Temperature T A (˚C)T r a n s i s t o r P o w e r D i s s i p a t i o n P C (m W )TRANSISTOR POWER DISSIPATION vs.AMBIENT TEMPERATURE1.5 mW/˚CForward Voltage V F (V)F o r w a r d C u r r e n t I F (m A )FORWARD CURRENT vs.FORWARD VOLTAGEAmbient Temperature T A (˚C)COLLECTOR TO EMITTER DARKCURRENT vs. AMBIENT TEMPERATUREC o l l e c t o r t o E m i t t e rD a r k C u r r e n t I CE O (n A )Collector Saturation Voltage V CE (sat) (V)C o l l e c t o r C u r r e n t I C (m A )COLLECTOR CURRENT vs.COLLECTOR SATURATION VOLTAGEFORWARD CURRENT vs.FORWARD VOLTAGEForward Voltage V F (V)F o r w a r d C u r r e n t I F (m A )806040200–40–60–80–20–1.200.4 1.2 1.6–1.6–0.8–0.40.8Remark The graphs indicate nominal characteristics.Data Sheet PN10243EJ02V0DS71.20.60.00.81.00.40.202550100–50–2575Ambient Temperature T A (˚C)NORMALIZED CURRENT TRANSFER RATIO vs. AMBIENT TEMPERATUREN o r m a l i z e d C u r r e n t T r a n s f e r R a t i o C T RNormalized to 1.0 at T A = 25 ˚C,I F = 5 mA, V CE = 5 V3002501505002001000.050.55500.1110Forward Current I F (mA)C u r r e n t T r a n s f e r R a t i o C T R (%)CURRENT TRANSFER RATIO vs.FORWARD CURRENTV CE = 5 VLoad Resistance R L (Ω)SWITCHING TIME vs.LOAD RESISTANCES w i t c h i n gT i m e t ( s )µLoad Resistance R L (Ω)SWITCHING TIME vs.LOAD RESISTANCES w i t c h i n g T i m e t (s )µFrequency f (kHz)N or m a l i z e d G a i n G VFREQUENCY RESPONSECollector to Emitter Voltage V CE (V)C o l l e c t o r C u r r e n t I C (m A )COLLECTOR CURRENT vs.COLLECTOR TO EMITTER VOLTAGERemark The graphs indicate nominal characteristics.Data Sheet PN10243EJ02V0DS86Time (Hr)LONG TERM CTR DEGRADATIONC T R (R e l a t i v e V a l u e )Remark The graph indicates nominal characteristics.TAPING SPECIFICATIONS (in millimeters)Data Sheet PN10243EJ02V0DS 9Data Sheet PN10243EJ02V0DS10NOTES ON HANDLING1. Recommended soldering conditions(1) Infrared reflow soldering • Peak reflow temperature 260°C or below (package surface temperature) • Time of peak reflow temperature 10 seconds or less • Time of temperature higher than 220°C 60 seconds or less • Time to preheat temperature from 120 to 180°C 120±30 s• Number of reflows Three• Flux Rosin flux containing small amount of chlorine (The flux with a maximum chlorine content of 0.2 Wt% is recommended.)P a c k a g e S u r f a c e T e m p e r a t u r e T (˚C )Time (s)Recommended Temperature Profile of Infrared Reflow(2) Wave soldering • Temperature 260°C or below (molten solder temperature) • Time10 seconds or less• Preheating conditions 120°C or below (package surface temperature)• Number of times One (Allowed to be dipped in solder including plastic mold portion.)• Flux Rosin flux containing small amount of chlorine (The flux with a maximum chlorine content of 0.2 Wt% is recommended.)(3) Soldering by soldering iron• Peak temperature (lead part temperature) 350°C or below • Time (each pins)3 seconds or less• Flux Rosin flux containing small amount of chlorine (The flux with a maximum chlorine content of 0.2 Wt% is recommended.)(a) Soldering of leads should be made at the point 1.5 to 2.0 mm from the root of the lead. (b) Please be sure that the temperature of the package would not be heated over 100°C.(4) Cautions• FluxesAvoid removing the residual flux with freon-based and chlorine-based cleaning solvent.2. Cautions regarding noiseBe aware that when voltage is applied suddenly between the photocoupler’s input and output or between collector-emitters at startup, the output transistor may enter the on state, even if the voltage is within the absolute maximum ratings.3. Measurement conditions of current transfer ratios (CTR), which differ according to photocouplerCheck the setting values before use, since the forward current conditions at CTR measurement differ according to product.When using products other than at the specified forward current, the characteristics curves may differ from the standard curves due to CTR value variations or the like. This tendency may sometimes be obvious, especially below I F = 1 mA.Therefore, check the characteristics under the actual operating conditions and thoroughly take variations or the like into consideration before use.USAGE CAUTIONS1.Protect against static electricity when handling.2.Avoid storage at a high temperature and high humidity.Data Sheet PN10243EJ02V0DS 11Data Sheet PN10243EJ02V0DS12SPECIFICATION OF VDE MARKS LICENSE DOCUMENT (VDE0884)Parameter Symbol Speck UnitApplication classification (DIN VDE 0109) for rated line voltages ≤ 300 Vr.m.s. IV for rated line voltages ≤ 600 Vr.m.s. III Climatic test class (DIN IEC 68 Teil 1/09.80) 55/100/21Dielectric strengthMaximum operating isolation voltageU IORM 710 V peak Test voltage (partial discharge test, procedure a for type test and random test) U pr 850 V peak U pr = 1.2 × U IORM , P d < 5 pCTest voltage (partial discharge test, procedure b for all devices test) U pr = 1.6 × U IORM , P d < 5 pC U pr 1 140 V peakHighest permissible overvoltage U TR 6 000 V peak Degree of pollution (DIN VDE 0109) 2 Clearance distance > 5 mm Creepage distance> 5 mm Comparative tracking index (DIN IEC 112/VDE 0303 part 1) CTI 175 Material group (DIN VDE 0109) III a Storage temperature range T stg –55 to +150 °C Operating temperature range T A –55 to +100°C Isolation resistance, minimum valueV IO = 500 V dc at T A = 25 °C Ris MIN. 1012 Ω V IO = 500 V dc at T A MAX. at least 100 °C Ris MIN. 1011Ω Safety maximum ratings(maximum permissible in case of fault, see thermal derating curve) Package temperatureTsi 150 °C Current (input current I F , Psi = 0) Isi 200 mA Power (output or total power dissipation) Psi 300 mW Isolation resistanceV IO = 500 V dc at T A = 175 °C (Tsi)Ris MIN.109ΩData Sheet PN10243EJ02V0DS13When the product(s) listed in this document is subject to any applicable import or export control laws and regulation of the authority having competent jurisdiction, such product(s) shall not be imported or exported without obtaining the import or export license.M8E 00. 4 - 0110The information in this document is current as of March, 2006. The information is subject to changewithout notice. For actual design-in, refer to the latest publications of NEC's data sheets or data books, etc., for the most up-to-date specifications of NEC semiconductor products. Not all products and/or types are available in every country. Please check with an NEC sales representative for availability and additional information.No part of this document may be copied or reproduced in any form or by any means without prior written consent of NEC. NEC assumes no responsibility for any errors that may appear in this document.NEC does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from the use of NEC semiconductor products listed in this document or any other liability arising from the use of such products. No license, express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC or others.Descriptions of circuits, software and other related information in this document are provided for illustrative purposes in semiconductor product operation and application examples. The incorporation of these circuits, software and information in the design of customer's equipment shall be done under the full responsibility of customer. NEC assumes no responsibility for any losses incurred by customers or third parties arising from the use of these circuits, software and information.While NEC endeavours to enhance the quality, reliability and safety of NEC semiconductor products, customers agree and acknowledge that the possibility of defects thereof cannot be eliminated entirely. To minimize risks of damage to property or injury (including death) to persons arising from defects in NEC semiconductor products, customers must incorporate sufficient safety measures in their design, such as redundancy, fire-containment, and anti-failure features.NEC semiconductor products are classified into the following three quality grades:"Standard", "Special" and "Specific". The "Specific" quality grade applies only to semiconductor products developed based on a customer-designated "quality assurance program" for a specific application. The recommended applications of a semiconductor product depend on its quality grade, as indicated below. Customers must check the quality grade of each semiconductor product before using it in a particular application."Standard":Computers, office equipment, communications equipment, test and measurement equipment, audioand visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots"Special":Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disastersystems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)"Specific":Aircraft, aerospace equipment, submersible repeaters, nuclear reactor control systems, lifesupport systems and medical equipment for life support, etc.The quality grade of NEC semiconductor products is "Standard" unless otherwise expressly specified in NEC's data sheets or data books, etc. If customers wish to use NEC semiconductor products in applications not intended by NEC, they must contact an NEC sales representative in advance to determine NEC's willingness to support a given application.(Note)(1)"NEC" as used in this statement means NEC Corporation, NEC Compound Semiconductor Devices, Ltd.and also includes its majority-owned subsidiaries.(2)"NEC semiconductor products" means any semiconductor product developed or manufactured by or forNEC (as defined above).••••••NEC Compound Semiconductor Devices Hong Kong Limited E-mail: ncsd-hk@ (sales, technical and general)Hong Kong Head Office T aipei Branch OfficeKorea Branch OfficeTEL: +852-3107-7303TEL: +886-2-8712-0478TEL: +82-2-558-2120FAX: +852-3107-7309 FAX: +886-2-2545-3859FAX: +82-2-558-5209NEC Electronics (Europe) GmbH http://www.ee.nec.de/TEL: +49-211-6503-0 FAX: +49-211-6503-1327California Eastern Laboratories, Inc. / TEL: +1-408-988-3500 FAX: +1-408-988-02790504NEC Compound Semiconductor Devices, Ltd. / E-mail: salesinfo@ (sales and general) techinfo@ (technical)Sales Division TEL: +81-44-435-1573 FAX: +81-44-435-1579For further information, please contact。

OV7725 datasheet

© 2006 OmniVision Technologies, Inc.VarioPixel, OmniVision, and the OmniVision logo are registered trademarks of OmniVision Technologies, Inc.Version 1.0, September 12, 2006OmniPixel2 and CameraChip are trademarks of OmniVision Technologies, Inc.These specifications are subject to change without notice.Advanced Information Preliminary DatasheetOV7725 Color CMOS VGA (640x480) C AMERA C HIP TM SensorO mniision®with OmniPixel2TM TechnologyGeneral DescriptionThe OV7725 C AMERA C HIP ™ image sensor is a low voltage CMOS device that provides the full functionality of a single-chip VGA camera and image processor in a small footprint package. The OV7725 provides full-frame,sub-sampled or windowed 8-bit/10-bit images in a wide range of formats, controlled through the Serial CameraApplications•Cellular and picture phones •Toys•PC Multimedia•Digital still camerasKey SpecificationsOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OFunctional DescriptionFigure2 shows the functional block diagram of the OV7725 image sensor. The OV7725 includes:•Image Sensor Array (total array of 656 x 488 pixels, with active pixels 640 x 480 in YUV mode)•Analog Signal Processor•A/D Converters•Test Pattern Generator•Digital Signal Processor (DSP)•Image Scaler•Timing Generator2Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006Functional DescriptionVersion 1.0, September 12, 2006Proprietary to OmniVision Technologies, Inc.3OImage Sensor ArrayThe OV7725 sensor has an image array of 656x 488pixels for a total of 320,128 pixels, of which 640x 480pixels are active (307,200 pixels). Figure 3 shows a cross-section of the image sensor array.Figure 3 Image Sensor ArrayIn addition to the A/D conversion, this block also has the following functions:•Digital Black-Level Calibration (BLC)•Optional U/V channel delay •Additional A/D range controlsIn general, the combination of the A/D Range Multiplier and A/D Range Control sets the A/D range and maximum value to allow the user to adjust the final image brightness as a function of the individual application.Test Pattern GeneratorOL /I OH drive currentthe C AMERA C HIP sensor operation. Refer to OmniVision Technologies Serial Camera Control Bus (SCCB)Specification for detailed usage of the serial control port.4Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006OV7725Color CMOS VGA OmniPixel2™ C AMERA C HIP ™ SensorOPin DescriptionTable 1Pin DescriptionPin NumberName Pin Type Function/DescriptionA1ADVDD Power ADC power supplyA2RSTB Input System reset input, active lowA3VREFH Reference Reference voltage - connect to ground using a 0.1 µF capacitor A4FSIN Input Frame synchronize input A5SCL Input SCCB serial interface clock input A6D0a a. D[9:0] for 10-bit Raw RGB data (D[9] MSB, D[0] LSB)Output Data output bit[0]B1ADGND Power ADC groundB2VREFN Reference Reference voltage - connect to ground using a 0.1 µF capacitor B3AVDD Power Analog power supply B4AGND Power Analog groundB5SDA I/O SCCB serial interface data I/O B6HREF Output HREF outputC1PWDN Input (0)b b. Input (0) represents an internal pull-down resistor.Power Down Mode Selection0:Normal mode1:Power down mode C6VSYNC Output Vertical sync output D1D5Output Data output bit[5]D6D4Output Data output bit[4]E1D7Output Data output bit[7]E2D1Output Data output bit[1]E3DVDD Power Power supply (+1.8 VDC) for digital logic core E4PCLK Output Pixel clock outputE5DOVDD Power Digital power supply for I/O (1.7V ~ 3.3V)E6D6Output Data output bit[6]F1D9c c. D[9:2] for 8-bit YUV or RGB565/RGB555 (D[9] MSB, D[2] LSB)Output Data output bit[9]F2D3Output Data output bit[3]F3XCLK Input System clock input F4DOGND Power Digital ground F5D2Output Data output bit[2]F6D8OutputData output bit[8]Electrical CharacteristicsVersion 1.0, September 12, 2006Proprietary to OmniVision Technologies, Inc.5OElectrical CharacteristicsNOTE:Exceeding the Absolute Maximum ratings shown above invalidates all AC and DC electrical specifications and may result in permanent device damage.Table 2Operating ConditionsParameterMin Max Operating temperature -20°C +70°C Storage temperature a a.Exceeding the stresses listed may permanently damage the device. This is a stress rating only and functional operation of the sensor at these and any other condition above those indicated in this specification is not implied. Exposure to absolute maximum rating conditions for any extended period may affect reliability.-40°C+125°CTable 3 Absolute Maximum RatingsAmbient Storage Temperature-40ºC to +95ºCSupply Voltages (with respect to Ground)V DD-A4.5 V V DD-C 3 V V DD-IO4.5 VAll Input/Output Voltages (with respect to Ground)-0.3V to V DD-IO +0.5V Lead-free Temperature, Surface-mount process 245ºCTable 4DC Characteristics (-20°C < T A < 70°C)Symbol ParameterConditionMin Typ Max Unit V DD-A DC supply voltage – Analog – 3.0 3.3 3.6V V DD-C DC supply voltage – Digital Core – 1.62 1.8 1.98V V DD-IO DC supply voltage – I/O power – 2.5– 3.3V I DDA Active (Operating) Current See Note a a. V DD-A = 3.3V, V DD-C = 1.8V, V DD-IO = 3.3VI DDA = ∑{I DD-IO + I DD-C + I DD-A }, f CLK = 24MHz at 30 fps YUV output, no I/O loading 10 + 8bb. I DD-C = 10mA, I DD-A = 8mA, without loading mA I DDS-SCCB Standby Current See Note cc. V DD-A = 3.3V, V DD-C = 1.8V, V DD-IO = 3.3VI DDS-SCCB refers to a SCCB-initiated Standby, while I DDS-PWDN refers to a PWDN pin-initiated Standby 1mA I DDS-PWDN Standby Current 1020µA V IH Input voltage HIGH CMOS0.7 x V DD-IOV V IL Input voltage LOW 0.3 x V DD-IOV V OH Output voltage HIGH CMOS0.9 x V DD-IOV V OL Output voltage LOW 0.1 x V DD-IOV I OH Output current HIGH See Note dd. Standard Output Loading = 25pF, 1.2K Ω8mA I OL Output current LOW 15mA I LInput/Output LeakageGND to V DD-IO ± 1µAOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OTable 5 Functional and AC Characteristics (-20°C < T A < 70°C)Symbol Parameter Min Typ Max Unit Functional CharacteristicsA/D Differential Non-Linearity+ 1/2LSBA/D Integral Non-Linearity+1LSBAGC Range30dBRed/Blue Adjustment Range12dB Inputs (PWDN, CLK, RESET#)f CLK Input Clock Frequency102448MHzt CLK Input Clock Period2142100ns t CLK:DC Clock Duty Cycle455055% t S:RESET Setting time after software/hardware reset1ms t S:REG Settling time for register change (10 frames required)300ms SCCB Timing (see Figure4)f SCL Clock Frequency400KHzt LOW Clock Low Period 1.3μs t HIGH Clock High Period600ns t AA SCL low to Data Out valid100900ns t BUF Bus free time before new START 1.3μs t HD:STA START condition Hold time600ns t SU:STA START condition Setup time600ns t HD:DAT Data-in Hold time0μs t SU:DAT Data-in Setup time100ns t SU:STO STOP condition Setup time600ns t R, t F SCCB Rise/Fall times300ns t DH Data-out Hold time50ns Outputs (VSYNC, HREF, PCLK, and D[9:0] (see Figure5, Figure6, Figure7, and Figure8)t PDV PCLK[↓] to Data-out Valid5ns t SU D[9:0] Setup time15ns t HD D[9:0] Hold time8ns t PHH PCLK[↓] to HREF[↑]05ns t PHL PCLK[↓] to HREF[↓]05nsAC Conditions:• V DD: V DD-C = 1.8V, V DD-A = 3.3V, V DD-IO = 3.3V • Rise/Fall Times: I/O: 5ns, MaximumSCCB: 300ns, Maximum • Input Capacitance: 10pf• Output Loading: 25pF, 1.2KΩ to 3.3V• f CLK: 24MHz6Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006Timing SpecificationsVersion 1.0, September 12, 2006Proprietary to OmniVision Technologies, Inc.7OTiming SpecificationsFigure 4 SCCB Timing DiagramOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OFigure 7 QVGA Frame Timing8Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006Timing SpecificationsVersion 1.0, September 12, 2006Proprietary to OmniVision Technologies, Inc.9OFigure 9 RGB 565 Output Timing DiagramOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OFigure 11 RGB 444 Output Timing Diagram10Proprietary to OmniVision Technologies, Inc.Version 1.0, September 12, 2006Register Set Table6 provides a list and description of the Device Control registers contained in the OV7725. For all register Enable/Disable bits, ENABLE = 1 and DISABLE = 0. The device slave addresses are 42 for write and 43 for read.Table 6 Device Control Register List (Sheet 1 of 11)Address (Hex)RegisterNameDefault(Hex)R/W Description00GAIN00RW AGC – Gain control gain settingBit[7:0]:AGC[7:0] (see GREEN[7:6] (0x03) for AGC[9:8])•Range: [00] to [FF]01BLUE80RW AWB – Blue channel gain setting •Range: [00] to [FF]02RED80RW AWB – Red channel gain setting •Range: [00] to [FF]03GREEN00RW AWB – Green channel gain setting •Range: [00] to [FF]04COM100RW Common Control 1Bit[7:2]:ReservedBit[1:0]:AGC 2 MSBs, AGC[9:8]05BAVG00RW U/B Average LevelAutomatically updated based on chip output format06GAVG00RW Y/Gb Average LevelAutomatically updated based on chip output format07RAVG00RW V/R Average LevelAutomatically updated based on chip output format08AECH00RW Exposure Value – AEC MSBsBit[7:5]:AEC[15:8] (see register AEC for AEC[7:0]} Automatically updated based on chip output format09COM201RW Common Control 2Bit[7:5]:ReservedBit[4]:Soft sleep modeBit[3:2]:Pixel clock output delay control•Range: [00] to [11]Bit[1:0]:Output drive capability00:1x01:2x10:3x11:4x0A PID77R Product ID Number MSB (Read only) 0B VER21R Product ID Number LSB (Read only)0C COM310RW Common Control 3Bit[7]:Vertical flip image ON/OFF selectionBit[6]:Horizontal mirror image ON/OFF selectionBit[5]:Swap B/R output sequence in RGB output modeBit[4]:Swap Y/UV output sequence in YUV output modeBit[3]:Swap output MSB/LSBBit[2]:Tri-state option for output clock at power-down period 0:Tri-state at this period1:No tri-state at this periodBit[1]:Tri-state option for output data at power-down period 0:Tri-state at this period1:No tri-state at this periodBit[0]:Sensor color bar test pattern output enable0D COM441RW Common Control 4Bit[7:6]:PLL frequency control00:Bypass PLL01:PLL 4x10:PLL 6x11:PLL 8xBit[5:4]:AEC evaluate window00:Full window01:1/2 window10:1/4 window11:Low 2/3 window Bit[3:0]:Reserved0E COM501RW Common Control 5Bit[7]:Auto frame rate control ON/OFF selectionBit[6]:Auto frame rate control speed selectionBit[5:4]:Auto frame rate max rate control00:No reduction of frame rate01:Max reduction to 1/2 frame rate10:Max reduction to 1/4 frame rate11:Max reduction to 1/8 frame rate Bit[3:2]:Auto frame rate active point control00:Add frame when AGC reaches 2x gain01:Add frame when AGC reaches 4x gain10:Add frame when AGC reaches 8x gain11:Add frame when AGC reaches 16x gain Bit[1]:ReservedBit[0]:AEC max step control0:AEC increase step has limit1:No limit to AEC increase step0F COM643RW Common Control 6Bit[7:1]:ReservedBit[0]:Auto window setting ON/OFF selection when format changes(Hex)Name(Hex)R/W Description10AEC40RW Exposure ValueBit[7:0]:AEC[7:0] (see register AECH for AEC[15:8])11CLKRC80RW Internal ClockBit[7]:ReservedBit[6]:Use external clock directly (no clock pre-scale available)Bit[5:0]:Internal clock pre-scalarF(internal clock) = F(input clock)/(Bit[5:0]+1)•Range: [0 0000] to [1 1111]12COM700RW Common Control 7Bit[7]:SCCB Register Reset0:No change1:Resets all registers to default values Bit[6]:Resolution selection0:VGA1:QVGABit[5]:ITU656 protocol ON/OFF selectionBit[4]:ReservedBit[3:2]:RGB output format control00:GBR4:2:201:RGB56510:RGB55511:RGB444Bit[1:0]:Output format control00:YUV01:Processed Bayer RAW10:RGB11:Bayer RAW13COM88F RW Common Control 8Bit[7]:Enable fast AGC/AEC algorithmBit[6]:AEC - Step size limit0:Step size is limited to vertical blank1:Unlimited step sizeBit[5]:Banding filter ON/OFFBit[4]:Enable AEC below banding valueBit[3]:Fine AEC ON/OFF controlBit[2]:AGC EnableBit[1]:AWB EnableBit[0]:AEC Enable(Hex)Name(Hex)R/W Description14COM94A RW Common Control 9Bit[7]:Histogram or average based AEC/AGC selection Bit[6:4]:Automatic Gain Ceiling - maximum AGC value000:2x001:4x010:8x011:16x100:32x10164x110:128x111:Not allowedBit[3]:ReservedBit[2]:Drop VSYNC output of corrupt frameBit[1]:Drop HREF output of corrupt frameBit[0]:Reserved15COM1000RW Common Control 10Bit[7]:Output negative dataBit[6]:HREF changes to HSYNCBit[5]:PCLK output option0:Free running PCLK1:PCLK does not toggle during horizontal blank Bit[4]:PCLK reverseBit[3]:HREF reverseBit[2]:VSYNC option0:VSYNC changes on falling edge of PCLK1:VSYNC changes on rising edge of PCLK Bit[1]:VSYNC negativeBit[0]:Output data range selection0:Full range1:Data from [10] to [F0] (8 MSBs)16RSVD XX–Reserved17HSTART23 (VGA)3F (QVGA)RW Horizontal Sensor Size18HSIZEA0 (VGA)50 (QVGA)RWHorizontal Frame (HREF column) end high 8-bit (low 2bits are atHREF[1:0])19VSTRT07 (VGA)03 (QVGA)RW Vertical Frame (row) start high 8-bit (low 1 bit is at HREF[6])1A VSIZEF0 (VGA)78 (QVGA)RW Vertical Sensor Size1B PSHFT40RW Data Format - Pixel Delay Select (delays timing of the D[9:0] data relative to HREF in pixel units)•Range: [00] (no delay) to [FF] (256 pixel delay which accounts for whole array)1C MIDH7F R Manufacturer ID Byte – High(Read only = 0x7F) 1D MIDL A2R Manufacturer ID Byte – Low(Read only = 0xA2) 1E RSVD XX–Reserved(Hex)Name(Hex)R/W Description1F LAEC00RW Fine AEC Value - defines exposure value less than one line period20COM1110RW Common Control 11Bit[7:2]:ReservedBit[1]:Single frame ON/OFF selection Bit[0]:Single frame transfer trigger21RSVD XX–Reserved22BDBase FF RW Banding Filter Minimum AEC Value23DBStep01RW Banding Filter Maximum Step24AEW75RW AGC/AEC - Stable Operating Region (Upper Limit) 25AEB63RW AGC/AEC - Stable Operating Region (Lower Limit)26VPT D4RW AGC/AEC Fast Mode Operating RegionBit[7:4]:High nibble of upper limit of fast mode control zone Bit[3:0]:High nibble of lower limit of fast mode control zone27RSVD XX–Reserved28REG28??RW Register 28Bit[7:2]:ReservedBit[1]:Frame sync option (in external frame sync mode, set this bit to 1)Bit[0]:Auto frame adjust option0:Always decrease frame rate by 21:Decrease frame rate by inserting dummy verticalsync equal to maximum exposure lines29HOutSize A0 (VGA)50 (QVGA)RW Horizontal Data Output Size MSBs (2 LSBs at register EXHCH[1:0])2A EXHCH00RW Dummy Pixel Insert MSBBit[7:4]: 4 MSB for dummy pixel insert in horizontal direction Bit[3]:ReservedBit[2]:Vertical data output size LSBBit[1:0]:Horizontal data output size 2 LSBs2B EXHCL00RW Dummy Pixel Insert LSB8 LSB for dummy pixel insert in horizontal direction2C VOutSize F0 (VGA)78 (QVGA)RW Vertical Data Output Size MSBs (LSB at register EXHCH[2])2D ADVFL00RW LSB of Insert Dummy Lines in Vertical Direction (1 bit equals 1 line) 2E ADVFH00RW MSB of Insert Dummy Lines in Vertical Direction2F YAVE00RW Y/G Channel Average Value30LumHTh80RW Histogram AEC/AGC Luminance High Level Threshold31LumLTh60RW Histogram AEC/AGC Luminance Low Level Threshold(Hex)Name(Hex)R/W Description32HREF00RW Image Start and Size ControlBit[7]:Mirror image edge alignmentBit[6]:Vertical HREF window start control LSBBit[5:4]:Horizontal HREF window start control LSBsBit[3]:Data output bit shift test pattern ON/OFF control Bit[2]:Vertical sensor size LSBBit[1:0]:Horizontal sensor size 2 LSBs33DM_LNL00RW Dummy Line Low 8 Bits34DM_LNH00RW Dummy Line High 8 Bits35ADoff_B80RW AD Offset Compensation Value for B Channel36ADoff_R80RW AD Offset Compensation Value for R Channel37ADoff_Gb80RW AD Offset Compensation Value for Gb Channel38ADoff_Gr80RW AD Offset Compensation Value for Gr Channel39Off_B80RW Analog Process B Channel Offset Compensation Value 3A Off_R80RW Analog Process R Channel Offset Compensation Value 3B Off_Gb80RW Analog Process Gb Channel Offset Compensation Value 3C Off_Gr80RW Analog Process Gr Channel Offset Compensation Value3D COM1280RW Common Control 12Bit[7:6]:ReservedBit[5:0]:DC offset compensation for analog process3E COM13E2RW Common Control 13Bit[7]:Analog processing channel BLC ON/OFF control Bit[6]:ADC channel BLC ON/OFF controlBit[5:0]:Reserved3F COM141F RW Edge Enhancement AdjustmentBit[7:4]:ReservedBit[3:2]:AD offset compensation optionx0:Use R/Gr channel value for B/Gb01:Use B/Gb channel value for R/Gr11:Use B/Gb/R/Gr channel value independently Bit[1:0]:Analog processing offset compensation optionx0:Use R/Gr channel value for B/Gb01:Use B/Gb channel value for R/Gr11:Use B/Gb/R/Gr channel value independently40COM15C0RW Common Control 15Bit[7:4]:ReservedBit[3]:AD add 128 bit offsetBit[2:0]:Reserved41COM1608RW Common Control 16Bit[7:2]:ReservedBit[1:0]:BLC target 2 LSBs42TGT_B80RW BLC Blue Channel Target Value (Hex)Name(Hex)R/W Description43TGT_R80RW BLC Red Channel Target Value 44TGT_Gb80RW BLC Gb Channel Target Value 45TGT_Gr80RW BLC Gr Channel Target Value46LCC000RW Lens Correction Control 0Bit[7:3]:ReservedBit[2]:Lens correction control select0:R, G, and B channel compensation coefficient isset by registers LCC3 (0x49)1:R, G, and B channel compensation coefficient isset by registers LCC5 (0x4B), LCC3 (0x49), andLCC6 (0x4C), respectivelyBit[1]:ReservedBit[0]:Lens correction enable0:Disable1:Enable47LCC100RW Lens Correction Option 1 – X Coordinate of Lens Correction Center Relative to Array Center48LCC200RW Lens Correction Option 2 – Y Coordinate of Lens Correction Center Relative to Array Center49LCC350–Lens Correction Option 3G channel compensation coefficient when LCC0[2] (0x46) is 1 R, G, and B channel compensation coefficient when LCC0[2] is 04A LCC430–Lens Correction Option 4 – radius of the circular section where no compensation applies4B LCC550RW Lens Correction Option 5 (effective only when LCC0[2] is high) 4C LCC650RW Lens Correction Option 6 (effective only when LCC0[2] is high)4D FixGain00RW Analog Fix Gain AmplifierBit[7:6]:Gb channel fixed gainBit[5:4]:Gr channel fixed gainBit[3:2]: B channel fixed gainBit[1:0]:R channel fixed gain4E AREF0EF RW Sensor Reference Control •Range: [00] to [FF]4F AREF110RW Sensor Reference Current ControlBit[7:4]:Sensor reference current controlBit[3]:Internal regulator ON/OFF selection Bit[2]:ReservedBit[1:0]:Analog reference control50AREF260RW Analog Reference Control •Range: [00] to [FF]51AREF300RW ADC Reference Control •Range: [00] to [FF]52AREF400RW ADC Reference Control •Range: [00] to [FF](Hex)Name(Hex)R/W Description53AREF524RW ADC Reference Control •Range: [00] to [FF]54AREF67A RW Analog Reference Control •Range: [00] to [FF]55AREF7FC RW Analog Reference Control •Range: [00] to [FF]56-5F RSVD XX–Reserved60UFix80RW U Channel Fixed Value Output 61VFix80RW V Channel Fixed Value Output 62AWBb_blk FF RW AWB Option for Advanced AWB63AWB_Ctrl0F0RW AWB Control Byte 0Bit[7]:AWB gain enableBit[6]:AWB calculate enableBit[5]:ReservedBit[4:0]:WBC threshold 264DSP_Ctrl11F RW DSP Control Byte 1Bit[7]:FIFO enable/disable selectionBit[6]:UV adjust function ON/OFF selectionBit[5]:YUV444 to 422 UV channel option selection Bit[4]:Color matrix ON/OFF selectionBit[3]:Interpolation ON/OFF selectionBit[2]:Gamma function ON/OFF selectionBit[1]:Black defect auto correction ON/OFFBit[0]:White defect auto correction ON/OFF65DSP_Ctrl200RW DSP Control Byte 2Bit[7:4]:ReservedBit[3:0]:Scaling control66DSP_Ctrl310RW DSP Control Byte 3Bit[7]:UV output sequence optionBit[6]:ReservedBit[5]:DSP color bar ON/OFF selectionBit[4]:ReservedBit[3]:FIFO power down ON/OFF selectionBit[2]:Scaling module power down control 1Bit[1]:Scaling module power down control 2Bit[0]:Interpolation module power down control67DSP_Ctrl400RW DSP Control Byte 468AWB_bias00RW AWB BLC Level Clip69AWBCtrl15C RW AWB Control 16A AWBCtrl211RW AWB Control 26B AWBCtrl3A2RW AWB Control 36C AWBCtrl401RW AWB Control 4(Hex)Name(Hex)R/W Description6D AWBCtrl550RW AWB Control 56E AWBCtrl680RW AWB Control 66F AWBCtrl780RW AWB Control 770AWBCtrl80F RW AWB Control 871AWBCtrl900RW AWB Control 972AWBCtrl1000RW AWB Control 1073AWBCtrl110F RW AWB Control 1174AWBCtrl120F RW AWB Control 1275AWBCtrl13FF RW AWB Control 1376AWBCtrl14FF RW AWB Control 1477AWBCtrl15FF RW AWB Control 1578AWBCtrl1610RW AWB Control 1679AWBCtrl1770RW AWB Control 177A AWBCtrl1870RW AWB Control 187B AWBCtrl19F0RW AWB Control 197C AWBCtrl20F0RW AWB Control 207D AWBCtrl21F0RW AWB Control 217E GAM10E RW Gamma Curve 1st Segment Input End Point 0x04 Output Value 7F GAM21A RW Gamma Curve 2nd Segment Input End Point 0x08 Output Value 80GAM331RW Gamma Curve 3rd Segment Input End Point 0x10 Output Value 81GAM45A RW Gamma Curve 4th Segment Input End Point 0x20 Output Value 82GAM569RW Gamma Curve 5th Segment Input End Point 0x28 Output Value 83GAM675RW Gamma Curve 6th Segment Input End Point 0x30 Output Value 84GAM77E RW Gamma Curve 7th Segment Input End Point 0x38 Output Value 85GAM888RW Gamma Curve 8th Segment Input End Point 0x40 Output Value 86GAM98F RW Gamma Curve 9th Segment Input End Point 0x48 Output Value 87GAM1096RW Gamma Curve 10th Segment Input End Point 0x50 Output Value 88GAM11A3RW Gamma Curve 11th Segment Input End Point 0x60 Output Value 89GAM12AF RW Gamma Curve 12th Segment Input End Point 0x70 Output Value 8A GAM13C4RW Gamma Curve 13th Segment Input End Point 0x90 Output Value 8B GAM14D7RW Gamma Curve 14th Segment Input End Point 0xB0 Output Value 8C GAM15E8RW Gamma Curve 15th Segment Input End Point 0xD0 Output Value8D SLOP20RW Gamma Curve Highest Segment Slope - calculated as follows: SLOP[7:0] = (0x100 - GAM15[7:0]) x 4/38E DNSTh00RW De-noise Threshold(Hex)Name(Hex)R/W Description8F EDGE000RW Edge Enhancement Control 0Bit[7:5]:ReservedBit[4:0]:Edge enhancement strength control90EDGE108RW Edge Enhancement Control 1Bit[7:4]:ReservedBit[3:0]:Edge enhancement threshold control91DNSOff10RW Auto De-noise Threshold Control92EDGE21F RW Edge Enhancement Strength Low Point Control 93EDGE301RW Edge Enhancement Strength High Point Control 94MTX12C RW Matrix Coefficient 195MTX224RW Matrix Coefficient 296MTX308RW Matrix Coefficient 397MTX414RW Matrix Coefficient 498MTX524RW Matrix Coefficient 599MTX638RW Matrix Coefficient 69A MTX_Ctrl9E RW Matrix ControlBit[7]:Matrix double ON/OFF selection Bit[6]:ReservedBit[5]:Sign bit for MTX6Bit[4]:Sign bit for MTX5Bit[3]:Sign bit for MTX4Bit[2]:Sign bit for MTX3Bit[1]:Sign bit for MTX2Bit[0]:Sign bit for MTX19B BRIGHT00RW Brightness Control9C CNST40RW Contrast Control9D CNST_ctr00RW Contrast Control Center9E UVADJ011RW Auto UV Adjust Control 0Bit[7:4]:Auto UV adjust offset control 4 LSBs Bit[3:0]:Auto UV adjust threshold control9F UVADJ102RW Auto UV Adjust Control 1Bit[7:3]:Auto UV adjust valueBit[2]:ReservedBit[1]:Auto UV adjust stop controlBit[0]:Auto UV adjust offset control MSBA0SCAL000RW Scaling Control 0A1SCAL140RW Scaling Control 1 – for horizontal scaling control A2SCAL240RW Scaling Control 2 – for vertical scaling controlA3FIFOdlyM06RW FIFO Manual Mode Delay ControlA4FIFOdlyA00RW FIFO Auto Mode Delay Control(Hex)Name(Hex)R/W DescriptionRegister SetOA5RSVD XX –ReservedA6SDE 00RW Special Digital Effect Control A7USAT 40RW U Component Saturation Control A8VSAT 40RW V Component Saturation Control A9HUE080RW Hue Control 0AAHUE180RWHue Control 1AB SIGN 06RWSign Bit for Hue and ContrastBit[7:4]:ReservedBit[3:2]:Contrast sign bit Bit[1:0]:Hue sign bitAC DSPAuto FF RWDSP Auto Function ON/OFF ControlBit[7]:AWB auto threshold control Bit[6]:De-noise auto threshold controlBit[5]:Edge enhancement auto strength control Bit[4]:UV adjust auto slope controlBit[3]:Auto scaling factor control (register SCAL0 (0xA0))Bit[2]:Auto scaling factor control (registers SCAL1 (0xA1 and SCAL2 (0xA2))Bit[1:0]:ReservedNOTE: All other registers are factory-reserved. Please contact OmniVision Technologies for reference register settings.Table 6Device Control Register List (Sheet 11 of 11)Address (Hex)Register Name Default (Hex)R/W DescriptionOV7725Color CMOS VGA OmniPixel2™ C AMERA C HIP ™ SensorOPackage SpecificationsThe OV7725 uses a 28-ball Chip Scale Package 2 (CSP2). Refer to Figure 12 for package information, Table 7 for package dimensions and Figure 13 for the array center on the chip.Figure 12 OV7725-CSP2 Package SpecificationsNote: For OVT devices that are lead-free, all part marking letters are lower case. Underlining the last digit of the lot number indicates CSP2 is used.Package SpecificationsOSensor Array CenterFigure 13 OV7725 Sensor Array CenterOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor OChief Ray AngleFigure 14 OV7725 Chief Ray AnglePackage SpecificationsOIR Reflow Ramp Rate Requirements OV7725 Lead-Free Packaged DevicesFigure 15 IR Reflow Ramp Rate RequirementsNote: For OVT devices that are lead-free, all part marking letters are lower caseOV7725Color CMOS VGA OmniPixel2™C AMERA C HIP™ Sensor ONote:•All information shown herein is current as of the revision and publication date. Please refer to the OmniVision web site () to obtain the current versions of alldocumentation.•OmniVision Technologies, Inc. reserves the right to make changes to their products or to discontinue any product or service without further notice (It is advisable to obtain current product documentation prior to placing orders).•Reproduction of information in OmniVision product documentation and specifications is permissible only if reproduction is without alteration and is accompanied by all associatedwarranties, conditions, limitations and notices. In such cases, OmniVision is not responsibleor liable for any information reproduced.•This document is provided with no warranties whatsoever, including any warranty of merchantability, non-infringement, fitness for any particular purpose, or any warrantyotherwise arising out of any proposal, specification or sample. Furthermore, OmniVisionTechnologies, Inc. disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this document. No license, expressed or implied, byestoppels or otherwise, to any intellectual property rights is granted herein.•‘OmniVision’, ’VarioPixel’ and the OmniVision logo are registered trademarks of OmniVision Technologies, Inc. ’OmniPixel2’ and ’CameraChip’ are trademarks of OmniVision Technologies, Inc. All other trade, product or service names referenced in this release may be trademarks or registered trademarks of their respective holders. Third-party brands, names, and trademarks are the property of their respective owners.For further information, please feel free to contact OmniVision at info@.OmniVision Technologies, Inc.1341 Orleans DriveSunnyvale, CA USA(408) 542-3000。

MK2705中文资料

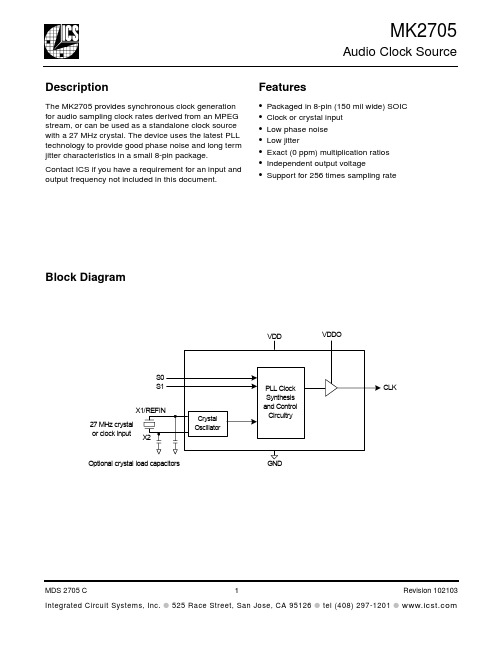

MK2705Audio Clock SourceDescriptionThe MK2705 provides synchronous clock generationfor audio sampling clock rates derived from an MPEGstream, or can be used as a standalone clock sourcewith a 27 MHz crystal. The device uses the latest PLLtechnology to provide good phase noise and long termjitter characteristics in a small 8-pin package.Contact ICS if you have a requirement for an input andoutput frequency not included in this document.Features•Packaged in 8-pin (150 mil wide) SOIC•Clock or crystal input•Low phase noise•Low jitter•Exact (0 ppm) multiplication ratios•Independent output voltage•Support for 256 times sampling rateBlock DiagramPin AssignmentOutput Clock Selection TablePin DescriptionsS1S0Input Frequency (MHz)Output Frequency (MHz)00278.192012711.2896102712.288112724.576Pin NumberPin NamePin TypePin Description1X1/REFIN Input Connect this pin to a 27 MHz crystal or clock input 2VDD Power Power supply for crystal oscillator and PLL.3S0Input Output frequency selection. Determines output frequency per table above. On-chip pull-up. 4GND Power Connect to ground.5CLK Output Clock output.6S1Input Output frequency selection. Determines output frequency per table above. On-chip pull-up. 7VDDO Power Power supply for output stage.8X2InputConnect this pin to a 27 MHz crystal. Leave open if using a clock input.Application InformationSeries Termination ResistorClock output traces should use series termination. T o series terminate a 50Ω trace (a commonly used trace impedance), place a 33Ω resistor in series with the clock line and as close to the clock output pin as possible. The nominal impedance of the clock output is 20Ω.Decoupling CapacitorsAs with any high-performance mixed-signal IC, the MK2705 must be isolated from system power supply noise to perform optimally.Decoupling capacitors of 0.01µF must be connected between each VDD and the PCB ground plane. To further guard against interfering system supply noise, the MK2705 should use one common connection to the PCB power plane as shown in the diagram on the next page. The ferrite bead and bulk capacitor help reduce lower frequency noise in the supply that can lead to output clock phase modulation.Recommended Power Supply Connection for Optimal Device PerformanceCrystal Load CapacitorsIf a crystal is used, the device crystal connections should include pads for capacitors from X1 to ground and from X2 to ground. These capacitors are used to adjust the stray capacitance of the board to match the nominally required crystal load capacitance. To reduce possible noise pickup, use very short PCB traces (and no vias) been the crystal and device.The value of the load capacitors can be roughly determined by the formula C = 2(C L - 6) where C is the load capacitor connected to X1 and X2, and C L is the specified value of the load capacitance for the crystal.A typical crystal C L is 18 pF, so C = 2(18 - 6) = 24 pF. Because these capacitors adjust the stray capacitance of the PCB, check the output frequency using your final layout to see if the value of C should be changed. PCB Layout RecommendationsObserve the following guidelines for optimum device performance and lowest output phase noise:1) Each 0.01µF decoupling capacitor should be mounted on the component side of the board as close to the VDD pin as possible. No vias should be used between decoupling capacitor and VDD pin. The PCB trace to VDD pin should be kept as short as possible, as should the PCB trace to the ground via. Distance of the ferrite bead and bulk decoupling from the device is less critical.2) The external crystal should be mounted next to the device with short traces. The X1 and X2 traces should not be routed next to each other with minimum spaces, instead they should be separated and away from other traces.3) To minimize EMI and obtain the best signal integrity, the 33Ω series termination resistor should be placed close to the clock output.4) An optimum layout is one with all components on the same side of the board, minimizing vias through other signal layers (the ferrite bead and bulk decoupling capacitor can be mounted on the back). Other signal traces should be routed away from the MK2705. This includes signal traces just underneath the device, or on layers adjacent to the ground plane layer used by the device.Absolute Maximum RatingsStresses above the ratings listed below can cause permanent damage to the MK2705. These ratings, which are standard values for ICS commercially rated parts, are stress ratings only. Functional operation of the device at these or any other conditions above those indicated in the operational sections of thespecifications is not implied. Exposure to absolute maximum rating conditions for extended periods can affect product reliability. Electrical parameters are guaranteed only over the recommended operating temperature range.Recommended Operation ConditionsDC Electrical CharacteristicsUnless stated otherwise, VDD = 3.3 V ±10%, Ambient Temperature 0 to +70°CItemRatingSupply Voltage, VDD 4.5 VAll Inputs and Outputs-0.5 V to VDD+0.5 V Ambient Operating Temperature 0 to +70°C Storage Temperature -65 to +150°C Junction Temperature 175°C Soldering Temperature260°CParameterMin.Typ.Max.UnitsAmbient Operating Temperature0+70°C Power Supply Voltage (measured in respect to GND)+3.0+3.6VParameterSymbolConditions Min.Typ.Max.UnitsOperating Voltage VDD 3.0 3.6V VDDO 1.8VDD V Input High Voltage V IH 2V Input Low Voltage V IL 0.8V Output High Voltage V OH I OH = -4 mA VDD-0.4V Output High Voltage V OH I OH = -20 mA 2.4VOutput Low Voltage V OL I OL = 20 mA 0.4V Supply Current IDD No Load 24mA Short Circuit Current I OS Each output ±65mA Nominal Output Impedance Z OUT 20ΩInput CapacitanceC IN Input pins7pF Internal pull-up resistor valueR PU120k ΩAC Electrical CharacteristicsUnless stated otherwise, VDD = 3.3 V ±10%, Ambient Temperature 0 to +70° CNote 1: Measured with 15 pF loadParameterSymbolConditionsMin.Typ.Max.UnitsInput frequency 27MHz Output duty cycle t OD VDD/2, Note 14549 to 5155%Output clock rise time t OR 20% to 80%, Note 1 1.5ns Output clock fall time t OF80% to 20%, Note 1 1.5ns Jitter, short term peak to peak, Note 1175ps Jitter, long term10 us delaypeak to peak, Note 1300ps Frequency synthesis error 0ppm Single sideband phase noise10 kHz offset-110dBcPackage Outline and Package Dimensions (8-pin SOIC, 150 mil Body)Package dimensions are kept current with JEDEC Publication No. 95Ordering InformationWhile the information presented herein has been checked for both accuracy and reliability, Integrated Circuit Systems (ICS) assumes no responsibility for either its use or for the infringement of any patents or other rights of third parties, which would result from its use. No other circuits, patents, or licenses are implied. This product is intended for use in normal commercial applications. Any other applications such as those requiring extended temperature range, high reliability, or other extraordinary environmental requirements are not recommended without additional processing by ICS. ICS reserves the right to change any circuitry or specifications without notice. ICS does not authorize or warrant any ICS product for use in life support devices or critical medical instruments.Part / Order NumberMarkingShipping packagingPackageTemperatureMK2705S MK2705S Tubes 8-pin SOIC 0 to +70° C MK2705STRMK2705STape and Reel8-pin SOIC0 to +70° C。

INA270AQDRQ1;INA271AQDRQ1;中文规格书,Datasheet资料

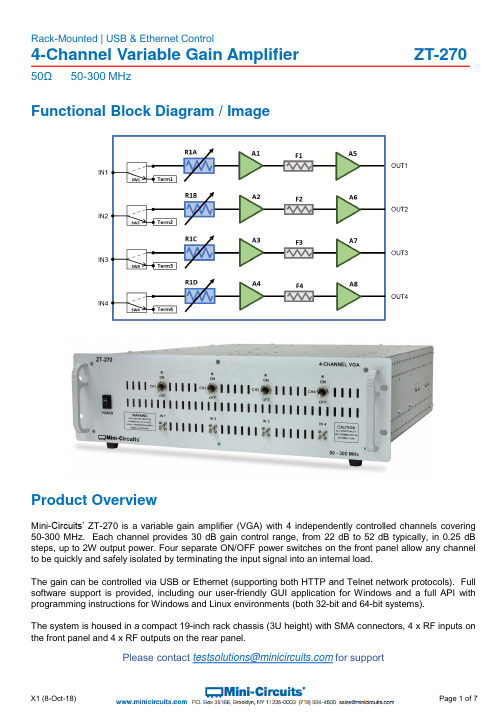

12345678OUTV+NCIN+BUF INPRE OUTGNDIN–D PACKAGE(TOP VIEW)NC – No internal connectionINA270-Q1,INA271-Q1 SBOS401B–JULY2007–REVISED FEBRUARY2010 VOLTAGE-OUTPUT UNIDIRECTIONAL-MEASUREMENT CURRENT-SHUNT MONITORSCheck for Samples:INA270-Q1,INA271-Q1FEATURES APPLICATIONS•Power Management•Qualified for Automotive Applications•Automotive•Wide Common-Mode Range:–16V to80V•Telecom Equipment•CMRR:120dB•Notebook Computers•Accuracy:•Battery Chargers–±2.5-mV Offset(Max)•Cell Phones–±1%Gain Error(Max)•Welding Equipment–20-m V/°C Offset Drift(Max)–55-ppm/°C Gain Drift(Max)•Bandwidth:Up to130kHz•Two Transfer Functions Available:–14V/V(INA270)–20V/V(INA271)•Quiescent Current:900m A(Max)•Power Supply:2.7V to18V•Provision for FilteringDESCRIPTION/ORDERING INFORMATIONThe INA270and INA271family of current-shunt monitors with voltage output can sense voltage drops across current shunts at common-mode voltages from–16V to80V,independent of the supply voltage.The INA270 and INA271pinouts readily enable filtering.The INA270and INA271are available with two output voltage scales:14V/V and20V/V.The130-kHz bandwidth simplifies use in current-control loops.The INA270and INA271operate from a single2.7-V to18-V supply,drawing a maximum of900m A of supply current.They are specified over the extended operating temperature range of–40°C to125°C and are offered in an SO-8package.ORDERING INFORMATION(1)T A GAIN PACKAGE(2)ORDERABLE PART NUMBER TOP-SIDE MARKING14INA270AQDRQ1INA270–40°C to125°C SOIC–D Reel of250020INA271AQDRQ1INA271(1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIweb site at .(2)Package drawings,thermal data,and symbolization are available at /packaging.Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of TexasInstruments semiconductor products and disclaimers thereto appears at the end of this data sheet.PRODUCTION DATA information is current as of publication date.Copyright©2007–2010,Texas Instruments Incorporated Products conform to specifications per the terms of the Texas−16V to +80INA270-Q1,INA271-Q1SBOS401B –JULY 2007–REVISED FEBRUARY 2010This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.FUNCTIONAL BLOCK DIAGRAMABSOLUTE MAXIMUM RATINGS (1)over operating free-air temperature range (unless otherwise noted)VALUEV SSupply voltage18V Differential analog input voltage range (V IN+–V IN–)–18V to 18V Common-mode analog input voltage range–16V to 80VV O Analog output voltage range (OUT and PRE OUT)(GND –0.3)V to (V++0.3)VI I Input current (any pin)5mA q JA Package thermal impedance (2)(3)97.1°C/W T J Maximum junction temperature 150°C T A Operating free-air temperature range –40to 125°C T stg Storage temperature range–65to 150°C Human-Body Model HBM)2000V ESDElectrostatic discharge ratingMachine Model (MM)100V Charged-Device Model (CDM)1000V(1)Stresses beyond those listed under "absolute maximum ratings"may cause permanent damage to the device.These are stress ratings only,and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions"is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)Maximum power dissipation is a function of T J (max),q JA ,and T A .The maximum allowable power dissipation at any allowable ambient temperature is P D =(T J (max)–T A )/q JA .Operating at the absolute maximum T J of 150°C can affect reliability.(3)The package thermal impedance is calculated in accordance with JESD 51-7.2Submit Documentation Feedback Copyright ©2007–2010,Texas Instruments IncorporatedINA270-Q1,INA271-Q1 SBOS401B–JULY2007–REVISED FEBRUARY2010RECOMMENDED OPERATING CONDITIONSMIN MAX UNITV S Supply voltage 2.718VT A Operating free-air temperature–40125°CELECTRICAL CHARACTERISTICSV S=5V,V CM=12V,V SENSE=100mV,PRE OUT connected to BUF IN(unless otherwise noted)PARAMETER TEST CONDITIONS T A(1)MIN TYP MAX UNIT Input(V S–0.2)/V SENSE Full-scale input voltage V SENSE=V IN++V IN–25°C0.15VGainV CM Common-mode input voltage Full range–1680VV IN+=–16V to80V25°C80120CMRR Common-mode rejection dBV IN+=12V to80V Full range10012025°C±0.5 2.5V OS Offset voltage,RTI(2)mVFull range±3Input offset voltageΔV OS/ΔT Full range 2.520m V/°C temperature coefficientOffset voltage power-supplyPSR V S=2.7V to18V,V CM=18V Full range5100m V/V rejectionI IB Input bias current IN–pin Full range±8±16m AZ O Output impedance(3)PRE OUT pin25°C96kΩBuffer input bias current25°C–50nABuffer input bias current25°C±0.3nA/°C temperature coefficientOutput(V SENSE≥20mV)(4)INA27014G Gain25°C V/VINA27120G BUF Output buffer gain25°C2V/V25°C±0.2±1 Total gain error V SENSE=20mV to100mV%Full range±2Total gain errorFull range50ppm/°C temperature coefficient25°C±0.75±2.2 Total output error(5)%Full range±1±3 Nonlinearity error V SENSE=20mV to100mV25°C±0.002%Z O Output impedance OUT pin25°C 1.5ΩMaximum capacitive load No sustained oscillation25°C10nF Voltage Output(6)Swing to V+power-supply rail R L=10kΩto GND Full range V+–0.05V+–0.2VV GND+V GND+ Swing to GND R L=10kΩto GND Full range V0.0030.05(1)Full range is–40°C to125°C.(2)RTI=referred to input(3)Initial resistor variation is±30%with an additional–2200-ppm/°C temperature coefficient.(4)For output behavior when V SENSE<20mV,see Application Information(5)Total output error includes effects of gain error and V OS.(6)See Typical Characteristics curve Output Swing vs Output Current and Accuracy Variations as a Result of VSENSE and Common-ModeVoltage in the Application Information section.Copyright©2007–2010,Texas Instruments Incorporated Submit Documentation Feedback3INA270-Q1,INA271-Q1SBOS401B–JULY2007–REVISED ELECTRICAL CHARACTERISTICS(continued)V S=5V,V CM=12V,V SENSE=100mV,PRE OUT connected to BUF IN(unless otherwise noted)PARAMETER TEST CONDITIONS T A(1)MIN TYP MAX UNIT Frequency ResponseBW Bandwidth C L=5pF25°C130kHzf m Phase margin C L<10nF25°C40°SR Slew rate25°C1V/m sV SENSE=10mV to100mV,t s Settling time(1%)25°C2m sC L=5pFNoise,RTI(7)V n Voltage noise density25°C40nV/√Hz Power SupplyV OUT=2V25°C700900I Q Quiescent current m AV SENSE=0V Full range350950(7)RTI=referred to input4Submit Documentation Feedback Copyright©2007–2010,Texas Instruments IncorporatedG a i n (d B )Frequency (Hz)G a i n (d B )Frequency (Hz)101001k10k C o m m o n -M o d e a n d P o w e r -S u p p l y R e j e c t i o n (d B )Frequency (Hz)100kCOMMON-MODE AND POWER-SUPPL Y REJECTION10203040506070V O U T (V )V DIFFERENTIAL (mV)80901001101201304.03.53.02.52.01.51.00.50050100150200250300350T o t a l O u t p u t E r r o r(%e r r o r o f t h e i d e a l o u t p u t v a l u e )V SENSE (mV)TOTAL OUTPUT ERROR vs V SENSE400450500.O u t p u t E r r o r ()%Co Mo (mmo de Voltage V)n-INA270-Q1,INA271-Q1SBOS401B –JULY 2007–REVISED FEBRUARY 2010TYPICAL CHARACTERISTICST A =25°C,V S =12V,V CM =12V,V SENSE =100mV (unless otherwise noted)Copyright ©2007–2010,Texas Instruments Incorporated Submit Documentation Feedback 5I Q (µA )Output Voltage (V)O u t u t V o l t g e (V )p a Outp t ren )u ur t (C mA POSITIVE OUTPUT VOLTAGE SWINGSupply Voltage (V)O u t p u t S h o r t -C i r c u i t C u r r e n t (m A )OUTPUT SHORT -CIRCUIT CURRENTI Q (µA )V CM (V)QUIESCENT CURRENTFrequency (Hz)G a i n (d B )−PREOUT OUTPUT RESISTANCE R PREOUT (k )W 88888999991010101010111111111112INA270-Q1,INA271-Q1SBOS401B –JULY 2007–REVISED FEBRUARY 2010TYPICAL CHARACTERISTICS (continued)T A =25°C,V S =12V,V CM =12V,V SENSE =100mV (unless otherwise noted)6Submit Documentation Feedback Copyright ©2007–2010,Texas Instruments Incorporated50m V /d i v10µs/divSMALL-SIGNAL STEP RESPONSE10-mV TO 20-mV INPUT500m V /d i v10µs/divLARGE-SIGNAL STEP RESPONSE10-mV TO 100-mV INPUTINA270-Q1,INA271-Q1SBOS401B –JULY 2007–REVISED FEBRUARY 2010TYPICAL CHARACTERISTICS (continued)T A =25°C,V S =12V,V CM =12V,V SENSE =100mV (unless otherwise noted)Copyright ©2007–2010,Texas Instruments Incorporated Submit Documentation Feedback 7−16V to +80INA270-Q1,INA271-Q1SBOS401B –JULY 2007–REVISED FEBRUARY 2010APPLICATION INFORMATIONBasic ConnectionFigure 1illustrates the basic connection of the INA270and INA271.The input pins,IN+and IN–,should be connected as closely as possible to the shunt resistor to minimize any resistance in series with the shunt resistance.Power-supply bypass capacitors are required for stability.Applications with noisy or high-impedance power supplies may require additional decoupling capacitors to reject power-supply noise.Minimum bypass capacitors of 0.01m F and 0.1m F in value should be placed close to the supply pins.Although not mandatory,an additional 10-mF electrolytic capacitor placed in parallel with the other bypass capacitors may be useful in applications with particularly noisy supplies.Figure 1.INA270Basic ConnectionsPower SupplyThe input circuitry of the INA270and INA271can accurately measure beyond its power-supply voltage,V+.For example,the V+power supply can be 5V,whereas the load power-supply voltage is up to 80V.The output voltage range of the OUT terminal,however,is limited by the voltages on the power-supply pin.Selecting R SThe value chosen for the shunt resistor,R S ,depends on the application and is a compromise between small-signal accuracy and maximum permissible voltage loss in the measurement line.High values of R S provide better accuracy at lower currents by minimizing the effects of offset,while low values of R S minimize voltage loss in the supply line.For most applications,best performance is attained with an R S value that provides a full-scale shunt voltage range of 50mV to 100mV.Maximum input voltage for accurate measurements is (V S –0.2)/Gain.Transient ProtectionThe –16-V to 80-V common-mode range of the INA270and INA271is ideal for withstanding automotive fault conditions ranging from 12-V battery reversal up to 80-V transients,since no additional protective components are needed up to those levels.In the event that the INA270and INA271are exposed to transients on the inputs in excess of their ratings,external transient absorption with semiconductor transient absorbers (zeners or Transzorbs)are necessary.8Submit Documentation Feedback Copyright ©2007–2010,Texas Instruments IncorporatedINA270-Q1,INA271-Q1SBOS401B –JULY 2007–REVISED FEBRUARY 2010Use of MOVs or VDRs is not recommended except when they are used in addition to a semiconductor transient absorber.Select the transient absorber such that it will never allow the INA270and INA271to be exposed to transients greater than 80V (that is,allow for transient absorber tolerance,as well as additional voltage because of transient absorber dynamic impedance).Despite the use of internal zener-type ESD protection,the INA270and INA271are not suited to using external resistors in series with the inputs,since the internal gain resistors can vary up to ±30%,but the internal resistors are tightly matched.If gain accuracy is not important,then resistors can be added in series with the INA270and INA271inputs,with two equal resistors on each input.Output Voltage RangeThe output of the INA270and INA271is accurate within the output voltage swing range set by the power-supply pin,V+.The INA270and INA271readily enable the inclusion of filtering between the preamp output and buffer input.Single-pole filtering can be accomplished with a single capacitor because of the 96-k Ωoutput impedance at PRE OUT on pin 3(see Figure 2a).The INA270and INA271readily lend themselves to second-order Sallen-Key configurations (see Figure 2b).When designing these configurations consider that the PRE OUT 96-k Ωoutput impedance exhibits an initial variation of ±30%with the addition of a –2200-ppm/°C temperature coefficient.A.The INA270and INA271can be easily connected for first-order or second-order filtering.Remember to use the appropriate buffer gain (INA270=1.4,INA271=2)when designing Sallen-Key configurations.Figure 2.First-Order or Second-Order FilteringCopyright ©2007–2010,Texas Instruments Incorporated Submit Documentation Feedback 9G =V –V OUT1OUT2100 mV – 20 mV V RTI (refe red to inp OS r ut) =V OUT1G – 100 mV ((INA270-Q1,INA271-Q1SBOS401B –JULY 2007–REVISED FEBRUARY 2010Accuracy Variations as a Result of V SENSE and Common-Mode VoltageThe accuracy of the INA270and INA271current-shunt monitors is a function of two main variables:V SENSE (V IN+–V IN–)and common-mode voltage,V CM ,relative to the supply voltage,V S .V CM is expressed as (V IN++V IN–)/2;however,in practice,V CM is seen as the voltage at V IN+because the voltage drop across V SENSE is usually small.This section addresses the accuracy of these specific operating regions:Normal Case 1:V SENSE ≥20mV,V CM ≥V S Normal Case 2:V SENSE ≥20mV,V CM <V SLow V SENSE Case 1:V SENSE <20mV,–16V ≤V CM <0Low V SENSE Case 2:V SENSE <20mV,0V ≤V CM ≤V S Low V SENSE Case 3:V SENSE <20mV,V S <V CM ≤80V Normal Case 1:V SENSE ≥20mV,V CM ≥V SThis region of operation provides the highest accuracy.Here,the input offset voltage is characterized and measured using a two-step method.First,the gain is determined by Equation 1.(1)Where:V OUT1=Output voltage with V SENSE =100mV V OUT2=Output voltage with V SENSE =20mVThen the offset voltage is measured at V SENSE =100mV and referred to the input (RTI)of the current-shunt monitor,as shown in Equation 2.(2)In Typical Characteristics ,the Output Error vs Common-Mode Voltage curve shows the highest accuracy for thethis region of operation.In this plot,V S =12V;for V CM ≥12V,the output error is at its minimum.This case is also used to create the V SENSE ≥20mV output specifications in Electrical Characteristics .Low V SENSE Case 1:V SENSE <20mV,–16V ≤V CM <0;and Low V SENSE Case 3:V SENSE <20mV,V S <V CM ≤80VAlthough the INA270family of devices are not designed for accurate operation in either of these regions,some applications are exposed to these conditions.For example,when monitoring power supplies that are switched on and off while V S is still applied to the INA270or INA271,it is important to know what the behavior of the devices is in these regions.As V SENSE approaches 0mV,in these V CM regions,the device output accuracy degrades.A larger-than-normal offset can appear at the current-shunt monitor output with a typical maximum value of V OUT =60mV for V SENSE =0mV.As V SENSE approaches 20mV,V OUT returns to the expected output value with accuracy as specified in Electrical Characteristics .Figure 3illustrates this effect using the INA271(Gain =20).10Submit Documentation Feedback Copyright ©2007–2010,Texas Instruments Incorporated分销商库存信息:TIINA270AQDRQ1INA271AQDRQ1。

瑞芯微RK2706 RK2705固件修改屏驱动工具的使用方法

瑞芯微RK2706 RK2705固件修改屏驱动工的使用方法(与Rkw文件生成工具一起使用)

声明:本人使用有效,不过我的是改以前mp4可以用的固件,我的不知道是不是CR**板

我们都知道现在有一个名为“固件编辑器V1.0”的工具,不过很多人都不会用,就好像这样

不过我们可以在ouput文件夹内的SYSTEM文件夹里面新建个sy sset.dat文件即可打开该工具,记住,是新建一个空的sy sset.dat文

件,已有就替换0kb的

就是这样

,看清了,软件文件夹里有output文件夹,里面是4文件夹,

我们确定一下,

,有什么联想,对了,rk w生成工具

我们把resource文件夹复进去

再打开软件,按确定,就会调用rk w生成工具,在resource文件夹就会生成RK27SDK.RKW固件了

使用说明就是这样了。

MIC22705YML EV评估板1MHz,7A集成开关高效同步斜坡调压电源MLF和MicroLea