台积电(TSMC)采用QuartzDRC

帕克原子力 台积电-概述说明以及解释

帕克原子力台积电-概述说明以及解释1. 引言1.1 概述帕克原子力和台积电作为两个不同领域的重要企业,具有各自独特的特点和发展历程。

帕克原子力是一家专注于核能领域的公司,而台积电则是全球领先的半导体制造企业。

本文将分析和比较这两家企业的概况,以及它们在各自领域的技术特点、应用领域和发展成就。

帕克原子力是一家致力于核能技术研发和应用的公司。

该公司在核能领域具备丰富的经验和技术实力,其主要业务涵盖核反应堆研发、核燃料生产和核电站建设。

帕克原子力致力于推动核能的发展和应用,旨在提供清洁、高效、可持续的能源解决方案。

通过研发先进的核反应堆技术和核燃料科技,该公司为全球范围内的核电站建设和运行提供了可靠的支持。

相比之下,台积电是一家全球知名的半导体制造企业。

作为领先的芯片制造商,台积电在半导体技术领域具备领先的技术实力和创新能力。

公司提供先进的制程技术和解决方案,为客户提供高品质的半导体产品。

台积电凭借其卓越的制造能力和稳定的供应链,成为众多全球知名半导体公司的合作伙伴。

其技术实力和创新能力在行业内享有很高的声誉。

本文将重点介绍帕克原子力和台积电的公司简介、技术特点和成就,并进行比较和分析。

通过对这两个企业的研究,可以更好地了解它们在各自领域中的地位和贡献,进一步探讨核能和半导体技术在未来的发展趋势和应用前景。

1.2 文章结构文章结构部分主要是介绍本文的整体结构以及各个章节的内容安排。

本文分为引言、正文和结论三个部分。

首先,引言部分包括概述、文章结构和目的三个小节。

在概述中,将简要介绍本文要讨论的两个主题——帕克原子力和台积电。

接着,在文章结构部分,将详细介绍本文的目录结构,即各章节的安排和主要内容。

最后,在目的部分,将说明本文撰写的目的,即通过对比帕克原子力和台积电的技术实力、成就和发展,分析它们在各自领域的优势和劣势。

接下来,正文部分分为帕克原子力和台积电两个大节。

帕克原子力部分包括简介、技术特点和应用领域三个小节。

IMDS材料数据系统使用指南(10.0版本)

1.4 1.5 1.6 127 日 2013 年 4 月 23 日

2013 年 5 月 24 日 2013 年 6 月 27 日

2013 年 12 月 12 日 2014 年 3 月 17 日 2014 年 7 月 13 日 2015 年 2 月 27 日 2015 年 4 月 27 日 2015 年 6 月 10 日 2015 年 6 月 11 日 2015 年 7 月 10 日

第3页

目录

1 IMDS – 简介.............................................................................................................................................................................................................. 7 2 IMDS – 使用入门 ...................................................................................................................................................................................................... 8

IMDS 服务中心 欧洲 | 电话: +36 1778-9821 | 电子邮件: imds-helpdesk-english@ 中国 | 电话: + 86 27 8743-1668 | 电子邮件: imds-eds-helpdesk-china@

tsmc市场分析报告

tsmc市场分析报告市场分析报告:台积电(TSMC)一、市场概述台积电(TSMC)是全球领先的半导体制造公司,总部位于台湾。

作为全球最大的代工制造商之一,台积电生产高端、中端和低端的半导体芯片,广泛用于计算机、通信、消费电子和汽车等领域。

二、市场规模与趋势半导体市场是一个巨大的市场,随着数字化、智能化和物联网技术的发展,对半导体芯片的需求不断增长。

根据市场研究机构IC Insights的数据,2019年全球半导体市场规模为4790亿美元,预计到2024年将达到6472亿美元。

在全球半导体市场中,台积电以其领先的制造技术和高质量的产品享有很高的声誉。

根据IC Insights的统计,2019年台积电在全球半导体代工市场占有率达到了53%。

三、竞争环境虽然台积电在全球半导体代工市场占据领先地位,但仍面临激烈的竞争。

主要竞争对手包括美国的英特尔(Intel)和韩国的三星电子(Samsung Electronics)。

这些公司也是全球半导体市场的重要参与者,具有强大的技术实力和市场影响力。

与竞争对手相比,台积电在制造工艺技术上具备明显优势。

台积电拥有先进的7纳米工艺,并在研发和推出更高级别的5纳米和3纳米工艺。

这些先进的工艺技术使得台积电能够生产更小、更高性能的芯片,满足不断提升的市场需求。

四、市场机会与挑战随着人工智能、5G和物联网等新兴技术的迅猛发展,对半导体芯片的需求将进一步增长。

台积电在这些领域具有巨大的机会,可以提供高性能、低功耗的芯片解决方案。

然而,台积电也面临一些挑战。

首先,制造工艺的不断进化需要大量的研发投资,加大了成本压力。

其次,全球范围内的贸易紧张局势可能对半导体产业产生不利影响,限制了市场增长的潜力。

五、发展策略为了保持竞争优势,台积电需要继续投资研发,提高制造工艺技术水平。

特别是在新兴技术领域,如人工智能芯片、5G芯片和物联网芯片上,台积电应加大研发力度,开发并提供创新的解决方案。

台积电5nm芯片晶体管密度

台积电5nm芯片晶体管密度引言近年来,随着科技的不断发展,芯片制造技术也在逐步进化。

而台积电作为全球领先的芯片制造企业,其5nm芯片技术引起了广泛关注。

5nm芯片是目前最先进的芯片制造技术之一,其晶体管密度之高让人震惊。

本文将从台积电5nm芯片的基本概念、晶体管密度的意义和影响、以及5nm芯片晶体管密度的技术原理和未来发展进行深入探讨。

一、台积电5nm芯片的基本概念1.1 什么是5nm芯片5nm芯片是指芯片制造工艺的一种,其制程尺寸为5纳米。

芯片的制程尺寸决定了芯片上晶体管的密度和性能。

目前,5nm芯片制造技术已经被台积电成功商用,并且在手机、服务器、人工智能等领域大放异彩。

1.2 5nm芯片的特点5nm芯片相比于之前的制程如7nm、10nm等,有着更小的晶体管尺寸和更高的集成度。

其特点主要包括:高性能、低功耗、高集成度和更小的尺寸。

这使得5nm芯片能够在同样的功耗下提供更强的性能,或者在相同的性能下减少功耗,从而延长设备的续航时间。

1.3 台积电在5nm芯片上的成就台积电作为全球领先的芯片制造企业,其在5nm芯片制造方面投入了大量资金和人力,取得了显著的成就。

其5nm制程技术是继7nm之后又一次重大突破,被业界普遍认为是领先全球的先进制程技术之一。

二、晶体管密度的意义和影响2.1 晶体管密度的意义晶体管密度是指在芯片上每平方毫米的晶体管数量。

通常来说,晶体管密度越大,意味着芯片上可以集成更多的晶体管,从而提高芯片的性能和功能。

因此,晶体管密度是衡量一款芯片制程技术优劣的重要指标之一。

2.2 晶体管密度的影响晶体管密度的提高会带来多方面的影响。

首先是性能的提升,因为更多的晶体管可以带来更大的计算和处理能力;其次是功耗的降低,因为相同性能下的功耗通常与晶体管密度成正比;另外,晶体管密度的提高也会使得芯片尺寸更小,从而使得设备更加轻薄,适用于更多场景。

2.3 当前晶体管密度的挑战随着芯片制程逐渐进入纳米级尺寸,提高晶体管密度也面临着诸多挑战。

半导体芯片企业-台积电tsmc研究报告

从2016年以来台积电按工艺拆分的变化曲线可以看出:10nm工艺异军突起,在17年前两个季 度以内实现了从0到25%巨大飞跃,28nm以下工艺营收占在2018H2略有下滑。

2018台积电营收按工艺拆分

台积电营收按工艺拆分变化

数据来源:台积电,西南证券整理

数据来源:台积电,西南证券整理

P A G E 43

座超大晶圆厂的总产能已超过700万片十二寸晶圆,约占总产能1100万片的63.6%。

台积电12寸晶圆厂外景

台积电12寸晶圆厂内景

数据来源:台积电,西南证券整理

数据来源:台积电,西南证券整理

台积电 TSMC

产能 利用

台积电产能实现10%稳步增长,产能利用率超90%

台积电公司的众多客户遍布全球,为客户生产的晶片被广泛地运用在电脑产品、通讯产品、消费性、 工业用及标准类半导体等多样电子产品应用领域。如此多样化的晶片生产有助于缓和需求的波动性, 使公司得以维持较高的产能利用率及稳定的产能增长;

半导体芯片企业-台积电tsmc研究报告

科技基建,自主创芯

半导体

制造

台积电 TSMC

半导体

制造

台积电 TSMC

台积电:全球最大的晶圆代工企业

1987年,台积电成立于台湾新竹科学工业园区,开创了专业积体电路制造服务商业模Байду номын сангаас。台积电公司 专注生产由客户所设计的晶片,本身并不设计、生产或销售自有品牌产品,确保不与客户直接竞争。 时至今日,台积电公司已经是全世界最大的专业积体电路制造服务公司,单单在2017年,台积电公司 就以258种制程技术,为465个客户生产9920种不同产品。

台积电公司在北美、欧洲、日本、中国大陆,以及南韩等地均设有子公司或办事处,提供全球客户即 时的业务与技术服务。至2017年年底,台积公司员工总数超过4.8万人。

台积电 硅光芯片工艺

台积电硅光芯片工艺-概述说明以及解释1.引言1.1 概述在这一部分,我们将介绍台积电公司的硅光芯片工艺技术。

硅光芯片工艺是一种先进的半导体制造技术,可以帮助企业生产出更高性能、更节能的芯片产品。

台积电作为全球领先的半导体制造商之一,不断投入研发和创新,推动硅光芯片工艺技术的发展。

通过本文的介绍,读者将能够了解台积电在硅光芯片工艺领域的最新进展和应用。

1.2 文章结构:本文主要分为引言、正文和结论三个部分。

在引言部分中,将对台积电和硅光芯片工艺进行概述,并介绍文章的结构和目的。

在正文部分,将首先介绍台积电公司的背景和业务范围,然后详细介绍硅光芯片工艺技术,包括其原理、特点和制作过程。

接着将探讨硅光芯片工艺在不同应用领域的应用情况,如半导体、通信等行业。

在结论部分,将对硅光芯片工艺的发展趋势进行展望,分析台积电在该领域的地位,并对全文进行总结和回顾。

整体结构清晰,内容连贯,旨在全面介绍硅光芯片工艺及其在台积电公司的重要性和应用前景。

1.3 目的本文旨在探讨台积电公司在硅光芯片工艺领域的发展情况,介绍其在该领域中所采用的技术和应用领域。

通过对硅光芯片工艺技术的介绍,读者将了解到台积电在半导体制造业中的技术水平和市场地位,以及其在未来硅光芯片工艺发展趋势中所处的位置。

本文旨在为读者提供关于硅光芯片工艺领域的深入了解,帮助读者更好地了解半导体行业的发展方向和趋势。

2.正文2.1 台积电公司简介台积电是世界领先的专业半导体集成电路制造公司,总部位于台湾新竹科学园区。

公司成立于1987年,以其先进的技术和高质量的生产而闻名于业界。

台积电致力于为全球客户提供最先进的半导体制造服务,包括晶圆制造、封装和测试。

作为全球最大的专业半导体制造商之一,台积电拥有世界领先的晶圆制造技术和设备,以及一支高素质的研发团队。

公司不断推动半导体技术的创新,致力于为客户提供高性能、高可靠性的半导体产品。

台积电的客户遍布全球各个领域,包括通信、计算机、消费类电子、汽车、工业控制等。

TSMC与中国台湾国立台湾大学携手合作成功开发全球首颗40nm 3DTV芯片

的地 区, 提供独树一帜的拥有技术 创新和成本解决方案的等

离子刻蚀和化学薄膜沉积设备 , 5m ̄ 4 n 4 n 3 n / 为6 n f5 m/0 m/2 m 1

2n 8m以及更高端的器件制造提供技 术帮助和成本控制方案。

中微公 司的全球布局包括在中国大陆、 日本 、南韩 、台湾、

链 ,提供客 户完善产品及更好的服务支持。

( 本刊 通 讯 员)

新 加 坡 等 地 设 立 研 发 、制 造 、销 售 和 客 户服 务 机 构 。

( 刊 通 讯 员) 本

中微 半 导体 对 美 国泛 林 科 技

T C 与 中 国 台 湾 国 立 台 湾 大 学 M S

关 于专 利 侵 权 诉讼 第二 次 携 手 合 作 成功 开发 全 球 首 颗

中国台湾 国立台湾大学与 T MC2月 1 S 6日共同发表产 学合作成果 ,成功研发出全球第一颗以 4 n 0m制程制作的 自

由视 角 3 D电视 机 顶 盒 芯 片 , 望 较 现 行 技 术提 供 更 精 致 、 可 多 元 的 视讯 影 像 体 验 。 项 成 果 为 视 讯处 理 及 半 导 体 制 程 技术 此

第 1 卷第 2 1 期

电

子

与

封

装

炜 顺 主 持 。 友达 光 电董 事 长 李 妮 耀 先生 表 示 :“ 友达 晶材 是 台湾 及太 阳能产 业 链 中 少数 拥 有 M.e k高 质量 的 单 晶硅 晶 St e 圆制造 技 术 者 ,能 同 时提 供 客 户 多 晶硅 (oyicn 、硅 锭 P ls i ) lo ( gt I o )及硅 片 ( fr n Wae)完 整 解决 方 案 ,此 次 首 度结 合 M. St e k的高 质量 技 术 来源 与 台 湾太 阳 能上 游 产业 的 人 才 , e 既掌 握 较 高难 度 单 晶硅 技 术 ,又 以 自有技 术 发 展制 造 优 质 多 晶硅 锭 及 多 晶硅 片 ,未 来 将提 供 给 客 户 更 多样 的产 品及 服 务 。 李煜 耀 董 事 长 指 出 , 友达 在 布 局 全球 的 同时 , 也长 期 深 耕 台 湾 , 了 计划 将 大 台 中 地 区打 造 为 友 达 太 阳 能事 业 营 运 除 中心 , 持续 进 行 投 资 建 厂相 关 计 划 外 , 重 视 当 地人 才 的 培 更 育 及 促进 地 方 的 发 展 , 达 晶材 于 台湾 中港 园 区 未来 三 年 内 友 将 可 创造 1 0 工作 机 会 。 0个 0

台积电 3 纳米 晶体管密度

台积电3 纳米晶体管密度

台积电是一家全球知名的半导体制造公司,其在半导体领域的技术和实力一直处于领先地位。

最近,台积电宣布将在未来几年内推出3 纳米工艺节点,这将是半导体行业中最先进的工艺之一。

据台积电介绍,3 纳米工艺将采用FinFET 三维晶体管结构,这种结构可以提高晶体管密度,从而实现更高的性能和更低的功耗。

根据台积电的计划,3 纳米工艺将比目前的5 纳米工艺提高晶体管密度约70%,同时功耗将降低约30%。

要实现这种高密度的晶体管,台积电需要使用先进的光刻技术和化学制程。

例如,台积电将采用EUV(极紫外)光刻技术,该技术可以实现更小的芯片结构和更高的精度。

此外,台积电还将使用新型的材料和工艺,例如高介电常数材料和多层晶体管结构,以进一步提高晶体管密度和性能。

台积电的3 纳米工艺将为下一代芯片提供更高的性能和更低的功耗,这将有助于推动人工智能、物联网、5G 等领域的发展。

同时,这也将为台积电带来更多的商业机会和市场份额,巩固其在半导体行业中的领先地位。

台积电半导体工艺步骤

台积电半导体工艺步骤

以下是台积电半导体工艺步骤:

首先,芯片的制造始于晶圆的准备。

这包括对晶圆进行清洁和薄化、表面处理和对晶圆进行若干次量测和测试。

接下来,利用光刻技术为晶圆的表面添加光阻,然后使用光刻机将芯片的图案透过掩模镜透射到光刻胶层上。

光刻胶层被暴露并形成了芯片上所需的图案。

然后使用离子注入机将芯片玻璃表面掩膜应当处所需的离子注入到晶体中,以改变其电学性质,这个步骤称为掩模蚀刻。

接着,在化学腐蚀、物理镀膜、CVD(化学气相沉积)和PVD(物理气相沉积)等技术的作用下,在晶圆的表面沉积不同的金属和半导体材料。

然后再次进

行离子注入,以增强晶体的电学性质,形成pn结和MIS器件结构。

完成晶圆的所有沉积后,再进行制程清洗和蚀刻,最后再一次对晶圆进行测试并划分,即切割成多个芯片。

在产线上的后续流程包括芯片测试、封装、品质验证,然后将芯片交付给客户。

台积电 32nm 28nm 工艺密度 晶体管

台积电32nm 28nm 工艺密度晶体管1. 引言1.1 概述本文旨在探讨台积电的32nm和28nm工艺密度晶体管。

随着科技的不断进步,微电子领域对于集成电路的要求也越来越高,工艺密度晶体管的研究和应用成为了一个重要的研究方向。

台积电是全球领先的半导体制造厂商之一,其32nm 和28nm工艺密度晶体管拥有先进的技术和设计特点,具有广泛的应用前景。

1.2 文章结构本文将分为五个部分进行论述。

首先,在引言中概述了文章的目的和内容。

其次,在第二部分中详细介绍了台积电32nm工艺密度晶体管,包括工艺概述、特点以及晶体管设计与布局技术。

接着,在第三部分中探讨了台积电28nm工艺密度晶体管,包括工艺概述、特点以及晶体管设计与布局技术。

在第四部分中进行了32nm和28nm工艺密度比较分析,具体包括面积效益对比、物理封装要求对面积的影响以及运算性能指标对面积的影响等内容。

最后,在结论部分总结了本文的研究成果,并对未来的发展方向进行了展望。

1.3 目的本文的目的是深入研究和了解台积电32nm和28nm工艺密度晶体管,在探讨其工艺概述、特点以及晶体管设计与布局技术的基础上,比较分析这两种工艺密度下面积效益以及性能要求对面积的影响。

通过本文的研究,旨在为读者提供对台积电工艺密度晶体管的全面认识,并为相关领域的研究和应用提供参考依据。

2. 台积电32nm工艺密度晶体管2.1 工艺概述台积电的32nm工艺是公司在2010年推出的先进制程之一。

通过使用更小的制程节点,可以实现更高的晶体管密度和性能,从而提高芯片的性能和功耗效率。

2.2 32nm工艺特点在台积电的32nm工艺中,晶体管尺寸被缩小至32纳米,这意味着在单位面积内可以容纳更多的晶体管。

此外,该工艺采用了各种新技术和材料,如高介电常数材料、金属门结构以及超深紫外光刻技术等。

这些创新为芯片提供了更好的性能和能效。

2.3 晶体管设计与布局技术在32nm工艺中,台积电采用一系列精确的设计和布局技术来优化晶体管密度。

半导体光刻技术与专利之争

半导体光刻技术与专利之争作者:曹欣欣来源:《电脑报》2021年第46期苹果自研芯片的实力大家有目共睹,从移动端使用的A系列到电脑端用的M系列都是碾压同期竞品的存在。

近期有报道称,苹果计划最快于2023年推出由台积电代工的3nm Mac芯片,也就是第三代Apple Silicon芯片,内部代号分别为“Ibiza”、“Lobos”以及“Palma”。

在半导体制造中,3纳米工艺是继5纳米MOSFET技术节点之后的下一个技术。

三星和台积电已宣布计划将3nm半导体节点投入商业生产,它基于GAAFET(全能栅极场效应晶体管)技术,这是一种多栅极MOSFET技术。

在半导体晶圆(基板)上烧制出电路的光刻工序是半导体制造过程中最为重要的工序之一,所以近年来也成为了科技公司争夺的“技术高地”。

光刻设备由以荷兰为大本营的阿斯麦(ASML)掌握压倒性份额,据Bloomberg数据,全球五大半导体设备制造商分别为应用材料(AMAT)、阿斯麦(ASML)、东京威力科创(TEL)、科林研发(Lam Research)、科磊(KLA),这五大半导体制造商以其领先的技术、强大的资金支持占据着全球半导体设备制造业超过70%的份额。

1984年,电子巨头飞利浦和芯片机器制造商(ASMI)创建了一家新公司AMSL,目的是为了满足不断增长的半导体市场而开发光刻系统。

当时办公室尚在母公司的空地一旁的木屋内,仅有百余人陆续加入,同年推出第一个系统——PAS 2000步进机。

到了1988年,飞利浦在中国台湾成立合资代工厂后,ASML开始进军亚洲市场。

ASML 并非一帆风顺,在上世纪八九十年代也经历过倒闭危机。

几番挣扎,得到IPO的投资后,推出了突破性平台PAS 5500,才得以翻身。

1995年ASML 成为一家完全独立的上市公司,在阿姆斯特丹和纽约证券交易所上市。

2010年第一台极紫外(EUV)光刻工具原型(NXE:3100),标志着光刻新时代的开始。

台积电碳基芯片

台积电碳基芯片

台积电最近宣布研发成功了碳基芯片。

碳基芯片是以碳为材料制造的芯片,而非传统的硅元素材料。

与传统芯片相比,碳基芯片具有更高的能效、更快的运算速度和更高的散热性能。

这意味着未来的计算机可能会更加强大,运行速度更快。

碳基芯片需要的电能非常小,仅为传统芯片的几十分之一,这也意味着碳基芯片在移动设备和物联网等领域具有更广泛的应用前景。

另外,碳基芯片的散热性能非常好,因此可以降低设备使用过程中的温度,进而延长设备的使用寿命。

虽然碳基芯片的研发还处于初级阶段,但是台积电的研发已经引起了业内的广泛关注。

未来,随着碳基芯片技术的不断完善,它必将成为计算机领域的一个重要趋势。

这也将推动整个行业的创新。

东芝采用Quartz DRC和Quartz LVS用于快闪存储器设计

东芝采用Quartz DRC 和Quartz LVS 用于快闪存储器设计微捷码日前宣布,东芝公司(Toshiba Corporation)将部署Quartz(tm) DRC 和Quartz LVS 用于快闪存储器设计。

东芝公司是在32 纳米设计上验证了这两款微捷码物理验证产品的精度后才做出的这个决定。

据验证结果显示:Quartz DRC 和Quartz LVS 的先进功能可改善东芝快闪存储器设计的良率和可靠性。

传统DRC 和LVS 工具仅采用物理行为分析,这种方式不是引入了过度保守主义,就是不能识别出对产品可靠性有影响的各种效应。

在先进工艺节点,电学行为分析也是不可或缺的。

微捷码Quartz DRC 和Quartz LVS 是首款同时提供物理和电学分析的工具。

两年多来,我们一直将Quartz DRC 和Quartz LVS 用于我们的系统LSI 设计中,事实证明它们提供了我们所需的高容量、高速度、高可靠性物理验证,东芝半导体公司存储器技术主管Masaki Momodomi 表示。

通过合作验证这两款工具,我们现将用其来进行静态和动态物理验证以提高产品可靠性并缩短我们32 纳米快闪存储器设计的项目周期。

Quartz DRC 和Quartz LVS 提供了显著缩短的验证周期,同时还提供了与传统业界工具的完全兼容性,微捷码定制设计业务部总经理Anirudh Devgan 表示。

通过将这两款工具与FineSim(tm)电路仿真器完美结合,微捷码提供了一款创新性先进工艺设计解决方案。

东芝公司加大Quartz DRC 和Quartz LVS 使用力度的决定突显了微捷码产品解决32 纳米设计验证问题的非凡能力。

Quartz DRC 与Quartz LVS:快速、精确、全线性物理验证Quartz DRC 和Quartz LVS 经架构,可以用最短时间验证各种工艺节点。

台积电晶圆制造流程

台积电晶圆制造流程台积电(TSMC)是全球最大的晶圆代工厂商之一,其晶圆制造流程是指将客户设计的芯片电路图按照一定的工艺流程制造出来的过程。

以下将详细介绍台积电的晶圆制造流程。

客户将自己的芯片设计图纸提交给台积电。

这些设计图纸包含了芯片的电路结构、逻辑功能、电气特性等信息,是芯片制造的基础。

接着,台积电的工程师团队会对客户的设计图纸进行评估和分析。

他们会检查电路设计的可行性、工艺制造的可行性以及可能存在的问题,并与客户沟通,确保设计符合制造要求。

一旦设计图纸通过评估,台积电就会开始制作掩膜。

掩膜是用于将电路图案转移到硅片上的关键工具。

制作掩膜需要使用光刻技术,即通过将光线照射在光刻胶上,然后将光刻胶转移到硅片上,形成电路图案。

在制作掩膜的同时,台积电还会准备硅片。

硅片是芯片制造的基础材料,它具有良好的导电性和绝缘性能。

台积电会选择适合客户设计的硅片型号,并进行清洗和去除杂质的处理,以确保最佳的制造效果。

当掩膜和硅片准备好后,台积电就会进行光刻。

光刻是将掩膜上的图案转移到硅片上的过程。

台积电会使用紫外光照射硅片表面,然后通过化学反应将光刻胶转移到硅片上。

此时,硅片上就形成了客户设计的电路图案。

接下来是蚀刻步骤。

蚀刻是将硅片表面的材料进行去除的过程,以形成电路结构。

台积电会使用化学物质来溶解掉不需要的硅片材料,从而形成电路结构的凹槽或凸起。

完成蚀刻后,台积电会进行沉积步骤。

沉积是在硅片表面上沉积一层薄膜,以保护电路结构和提供额外的功能。

沉积可以使用化学气相沉积(CVD)或物理气相沉积(PVD)等技术,根据客户的需求选择不同的材料和方法。

随后是刻蚀步骤。

刻蚀是将薄膜上不需要的部分去除的过程。

台积电会使用化学物质或离子束来刻蚀薄膜上的材料,以形成所需的电路结构。

完成刻蚀后,台积电会进行清洗和检验。

清洗是将硅片表面的杂质和残留物去除的过程,以保证芯片的质量。

检验是对芯片进行功能和性能测试,以确保其符合规格要求。

台积电半导体工艺步骤

台积电半导体工艺步骤台积电是全球领先的半导体制造公司之一,其工艺步骤是一个极其复杂的过程,需要经过多个步骤才能完成一块芯片的制造。

下面我将详细介绍台积电半导体工艺步骤,包括前期准备、制造、检测等多个阶段。

一、前期准备阶段1.芯片设计:首先,半导体公司会根据客户的需求设计芯片的结构和功能,确定芯片的尺寸、工艺节点等参数。

2.掩膜设计:根据芯片设计的要求,设计相应的掩膜图案,用于在硅片表面形成芯片的电路结构。

3.硅片准备:选取高纯度的硅片,进行切割、清洗等处理,以便后续的制造工艺。

4.化学处理:对硅片进行化学表面处理,形成一层薄膜通常用作保护层以及与掩膜相配合。

二、制造阶段1.掩膜制备:将设计好的掩膜图案制作在掩膜片上,这里的工艺主要是光刻工艺。

2.光刻:将掩膜图案通过光刻技术转移到硅片表面,形成芯片的电路结构。

3.电镀:通过电镀技术,将金属沉积在硅片表面,形成导电线路和电极。

4.腐蚀:利用化学腐蚀技术,将多余的金属或二氧化硅腐蚀掉,形成清晰的电路结构。

5.扩散:将硅片放入高温炉中进行扩散处理,控制掺杂物在硅片中的分布,调节导电性能。

6.沉积:利用化学气相沉积技术,将所需材料沉积在硅片表面,用于制备其它部分的电路结构。

7.退火:将硅片放入高温炉中进行退火处理,使电路结构更加稳定。

8.清洗:对硅片进行清洗处理,去除表面的杂质和残留物。

三、检测阶段1.光刻检测:用显微镜等设备检查光刻图案的质量和准确性。

2.电气检测:通过测试设备对芯片进行电气性能测试,检查电路是否正常。

3.片上检测:利用激光等技术对芯片上的电路结构进行检测,发现并修复潜在的缺陷。

四、封装阶段1.芯片切割:将硅片切割成单独的芯片,以便后续的封装操作。

2.封装:将芯片放入封装机中,用塑料或金属材料封装,防止外界环境影响芯片的正常工作。

3.测试:对封装后的芯片进行性能测试,确保芯片符合质量标准。

以上是台积电半导体工艺步骤的简要介绍,整个过程需要经历多个阶段,并且每个阶段都需要精密的工艺技术和设备支持。

DRC简介

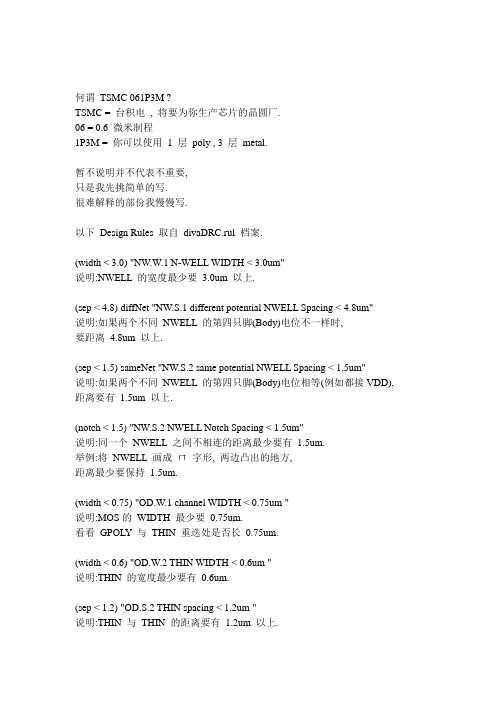

何谓TSMC 061P3M ?TSMC = 台积电, 将要为你生产芯片的晶圆厂.06 = 0.6 微米制程1P3M = 你可以使用1 层poly , 3 层metal.暂不说明并不代表不重要,只是我先挑简单的写.很难解释的部份我慢慢写.以下Design Rules 取自divaDRC.rul 档案.(width < 3.0) "NW.W.1 N-WELL WIDTH < 3.0um"说明:NWELL 的宽度最少要 3.0um 以上.(sep < 4.8) diffNet "NW.S.1 different potential NWELL Spacing < 4.8um"说明:如果两个不同NWELL 的第四只脚(Body)电位不一样时,要距离4.8um 以上.(sep < 1.5) sameNet "NW.S.2 same potential NWELL Spacing < 1.5um"说明:如果两个不同NWELL 的第四只脚(Body)电位相等(例如都接VDD), 距离要有1.5um 以上.(notch < 1.5) "NW.S.2 NWELL Notch Spacing < 1.5um"说明:同一个NWELL 之间不相连的距离最少要有 1.5um.举例:将NWELL 画成ㄇ字形, 两边凸出的地方,距离最少要保持 1.5um.(width < 0.75) "OD.W.1 channel WIDTH < 0.75um "说明:MOS的WIDTH 最少要0.75um.看看GPOLY 与THIN 重迭处是否长0.75um.(width < 0.6) "OD.W.2 THIN WIDTH < 0.6um "说明:THIN 的宽度最少要有0.6um.(sep < 1.2) "OD.S.2 THIN spacing < 1.2um "说明:THIN 与THIN 的距离要有 1.2um 以上.(notch < 1.2) "OD.S.2 THIN Notch spacing < 1.2um "说明:同一个THIN 之间不相连的地方最少要有 1.2um. 举例:将THIN 画成ㄇ字形, 两边凸出的地方,距离最少要保持 1.5um.(enc < 0.4) "OD.C.1 ndiff inside NWELL < 0.4um"说明:ndiff 是NPIMP 与THIN 重迭的区域,当NWELL 把ndiff 包起来时,ndiff 与NWELL 要保持4.0um 的距离.(sep < 1.8) "OD.C.2 ndiff outside COLDNWL < 1.8um"说明:暂不说明.(sep < 4.0) "OD.C.3 ndiff outside HOTNWL < 4.0um"说明:暂不说明.(enc < 1.8) "OD.C.4 pdiff inside NWELL < 1.8um"说明:pdiff 是PPIMP 与THIN 重迭的区域,当NWELL 把pdiff 包起来时,ndiff 与NWELL 要保持1.8um 的距离.由于PPIMP 一定包在THIN 外面,我们也可以说THIN 要与NWELL 保持 1.8um 的距离.(sep < 0.4) "OD.C.5 pdiff outside NWELL < 0.4um"说明:暂不说明.(width < 0.6) "PO.W.1-3 GPOLY width < 0.6um"说明:GPOL Y 最少要宽0.6um.(sep < 0.75) "PO.S.1 GPOLY spacing < 0.75um"说明:两个不同的GPOLY 之间要有0.75um 的距离.(notch < 0.75) "PO.S.1 GPOL Y notch Spacing < 0.75um"说明:同一个GPOL Y 之间不相连的地方最少要有 1.2um. 举例:将GPOL Y 画成ㄇ字形, 两边凸出的地方,距离最少要保持 1.5um.(sep < 0.3) "PO.C.1 GPOLY on field to THIN spacing < 0.3um"说明:暂不说明.(enc < 0.8) "PO.C.2 THIN extend GPOL Y < 0.8um"说明:当THIN 超过GPOL Y 时,GPOLY 要与THIN 保持0.8um 的距离.(enc < 0.6) "PO.O.1 GPOLY extend THIN < 0.6um"说明:当GPOL Y 超过THIN 时,GPOLY 要与THIN 保持0.6um 的距离.(geomAnd ngate NWELL) "NMOS should be in SameGnd!!"说明:暂不说明.(geomAnd pgate PWELL) "PMOS should be in NWELL!!"说明:你没有帮PMOS 画NWELL.(width < 0.9) "PP.W.1 Min. P+ IMPLANT WIDTH < 0.9um"说明:PPIMP 的宽度要大于0.9um.(sep < 0.9) "PP.S.1 P+ Implant spacing < 0.9um"说明:两个不同的PPIMP 要有0.9um 的距离.(notch < 0.9) "PP.S.1 P+ Implant Notch spacing < 0.9um"说明:同一个PPIMP 之间不相连的距离最少要有0.9um.举例:将PPIMP 画成ㄇ字形, 两边凸出的地方,距离最少要保持0.9um.(sep < 0.75) "PP.C.2 P+ Implant to ngate spacing <0.75um"说明:暂不说明.(ovlp < 0.75) "PP.C.4 P+ Implant inside to THIN inside <0.75um"说明:暂不说明.(enc < 0.3) "PP.C.5&NP.C.5 Both P+ to N+ Implant on Gpoly spacing<0.3um" 说明:暂不说明.(geomAndNot THIN IMP) "THIN has no IMP"说明:暂不说明.(geomAnd PPIMP NPIMP) "overlap implant PP.R.1&NP.R.1"说明:暂不说明.(enc < 0.45) "PP.E.1 P+ Implant extend THIN < 0.45um"说明:若THIN 在PPIMP 的里面,THIN 必需与PPIMP 保持最少0.45um 的距离.(width < 0.9) "NP.W.1 Min. N+ IMPLANT WIDTH < 0.9um"说明:NPIMP 最少要宽0.9um.(sep < 0.9) "NP.S.1 N+ Implant spacing < 0.9um"说明:两个不同的NPIMP 要有0.9um 的距离.(notch < 0.9) "NP.S.1 N+ Implant Notch spacing < 0.9um"说明:同一个NPIMP 之间不相连的地方最少要有 1.2um.举例:将NPIMP 画成ㄇ字形, 两边凸出的地方,距离最少要保持 1.5um.(sep < 0.75) "NP.C.2 N+ Implant to pgate spacing<0.75um"说明:暂不说明.(ovlp < 0.75) "NP.C.4 N+ Implant inside to THIN inside <0.75um" 说明:暂不说明.(enc < 0.45) "NP.E.1 N+ Implant extend THIN < 0.45um"说明:若THIN 在NPIMP 的里面,THIN 必需与NPIMP 保持最少0.45um 的距离.(saveDerived badconm1 "Contact without METAL1!!")说明:如果画了一个CONT, 它一定要被METAL1 覆盖.(width < 0.6) "CO.W.1 CONTACT width < 0.6"说明:CONT 最少要宽0.6um.(area > 0.36) "CO.W.1 CONTACT must be 0.6*0.6"说明:CONT 一定要画0.6um 见方.(sep < 0.6) "CO.S.1 CONTACT spacing < 0.6um"说明:两个不同的CONT 之间要有0.6um 的距离.(sep < 0.5) "CO.C.1 DIFF CONT to GATE spacing < 0.5um" 说明:GATE 是下面两层重迭的区域:1. GPOLY2. THINCONT 与GATE 要保持0.5um 的距离.(sep < 0.6) "CO.C.2 GPOLY CONT to THIN spacing<0.6um" 说明:暂不说明.(enc < 0.35) "CO.E.1 THIN extend CONT < 0.35um"说明:暂不说明.(enc < 0.4) "CO.E.3 GPOLY overlap CONT < 0.4um"说明:CONT 与GPOLY 要有0.4um 的距离.(enc < 0.4) "CO.E.4 PPIMP overlap CONT < 0.4um"说明:CONT 与PPIMP 要有0.4um 的距离.(enc < 0.4) "CO.E.5 NPIMP overlap CONT < 0.4um"说明:CONT 与NPIMP 要有0.4um 的距离.(geomAnd CONT gate) "Contact on gate is forbidden!"说明:暂不说明.(width < 0.9) "M1.W.1 METAL1 width < 0.9um"说明:METAL1 的宽度最少要有0.9um.(sep < 0.8) "M1.S.1 METAL1 spacing < 0.8um"说明:METAL1 与METAL1 之间的距离最少要0.8um.(enc < 0.3) "M1.E.1 METAL1 overlap CONT < 0.3um"说明:METAL1 将CONT 包住时,METAL1 与CONT 要有0.3um 的距离.(width < 0.7) "VIA1.W.1 VIA1 size < 0.7um"说明:VIA1 的大小要0.7um 平方.(sep < 0.7) "VIA1.S.1 VIA1 spacing < 0.7um"说明:VIA1 与VIA1 的距离最少0.7um.(enc < 0.4) "VIA1.E.1 METAL1 overlap VIA1 < 0.4um"说明:METAL1 将VIA1 包住时,METAL1 与VIA1 要有0.4um 的距离.(geomStraddle VIA1 GPOLY) "VIA1.C.2 VIA1 cross GPOLY!" 说明:VIA1 不能与GPOLY 重迭.(width < 0.9) "M2.W.1 METAL2 width < 0.9um"说明:METAL2 的宽度最少要有0.9um.(sep < 0.8) "M2.S.1 METAL2 spacing < 0.8um"说明:METAL2 与METAL2 之间的距离最少要0.8um.(notch < 0.8) "M2.S.1 METAL2 spacing < 0.8um"说明:同一个METAL2 之间不相连的距离最少要有0.8um. 举例:将METAL2 画成ㄇ字形, 两边凸出的地方,距离最少要保持0.8um.(enc < 0.4) "M2.E.1 METAL2 overlap VIA1 < 0.4um"说明:METAL2 将VIA1 包住时,METAL2 与VIA1 要有0.4um 的距离.(saveDerived badvia1 "VIA1 without METAL1!!")说明:VIA1 必需被METAL1 覆盖.(saveDerived badvia11 "VIA1 without METAL2!!")说明:VIA1 必需被METAL2 覆盖.(width < 0.7) "VIA2.W.1 VIA2 size < 0.7um"说明:VIA2 的大小要为0.7um 平方.(sep < 0.7) "VIA2.S.1 VIA2 spacing < 0.7um"说明:VIA2 与VIA2 之间的距离最少要0.7um.(enc < 0.4) "VIA2.E.1 METAL2 overlap VIA2 < 0.4um" 说明:说明:METAL2 将VIA2 包住时,METAL2 与VIA2 要有0.4um 的距离.(sep < 0.6) "VIA2.C.1 VIA2 to VIA1 spacing < 0.6"说明:VIA1 与VIA2 之间的距离最少要0.6um.(saveDerived badvia2 "VIA2 without METAL2!!")说明:VIA2 必需被METAL2 覆盖.(saveDerived badvia21 "VIA2 without METAL3!!")说明:VIA2 必需被METAL3 覆盖.(width < 0.9) "M3.W.1 METAL3 width < 0.9um" (sep < 0.8) "M3.S.1 METAL3 spacing < 0.8um" (notch < 0.8) "M3.S.1 METAL3 spacing < 0.8um" (enc < 0.4) "M3.E.1 METAL3 overlap VIA2 < 0.4um"。

台积电晶圆的作用

台积电晶圆的作用台积电晶圆的作用1. 什么是台积电晶圆?•台积电是世界领先的半导体公司之一,总部位于台湾•晶圆是半导体芯片的基础,即薄而平整的硅片•台积电晶圆是台积电生产的高质量硅基片2. 台积电晶圆在半导体行业的重要性•作为半导体制造的核心组成部分,晶圆有着重要的地位•晶圆上制造了包括处理器、内存芯片等各种集成电路的芯片•台积电晶圆的高质量和先进制造工艺,为半导体行业提供优质的硅基片3. 台积电晶圆的优势•先进制造工艺:台积电拥有世界领先的制造工艺和技术•高质量控制:台积电注重质量控制,确保晶圆的高可靠性和稳定性•可定制性:台积电可以根据客户需求定制晶圆的特性和参数4. 台积电晶圆的应用•个人电脑:处理器和内存芯片是个人电脑的核心组件,台积电晶圆为其提供了高性能的芯片•手机和平板电脑:手机芯片和闪存都需要晶圆,台积电的晶圆为手机和平板电脑提供了稳定和高效的性能•云计算和人工智能:半导体行业对于云计算和人工智能的需求日益增加,台积电晶圆的先进工艺满足了这些应用的要求5. 台积电的角色•制造商:台积电作为半导体制造商,扮演着提供高质量晶圆的角色•创新推动者:台积电不断推进制造工艺的创新,推动了整个半导体行业的发展•合作伙伴:台积电与客户紧密合作,共同实现技术和市场的突破通过台积电晶圆的制造和供应,半导体行业得以持续发展和创新。

台积电凭借其先进的工艺技术和高质量的晶圆,为各种应用领域提供了稳定和可靠的芯片基础。

6. 台积电晶圆的市场地位•台积电是全球最大的晶圆代工厂商之一,占据着重要的市场地位•许多世界知名的半导体公司选择将制造外包给台积电,以获取更高的产能和更先进的技术•台积电晶圆的高品质和高可靠性,赢得了广大客户的信任和青睐7. 台积电晶圆的未来发展趋势•更先进的制造工艺:随着科技的进步和市场需求的变化,台积电将不断提升制造工艺,实现更小、更快、更节能的芯片制造•特色晶圆的研发:为了满足不同应用领域的需求,台积电将继续研发特色晶圆,提供更多样化的选择•环境保护和可持续发展:台积电将致力于推动环境保护和可持续发展,在晶圆制造过程中注重资源的节约和废物的处理8. 小结通过对台积电晶圆的了解,我们可以看到其在半导体行业中的重要作用和地位。

台积电硅电容工艺

台积电硅电容工艺

台积电硅电容工艺是一项关键技术,广泛应用于集成电路的制造中。

它的出现极大地推动了半导体行业的发展,为我们带来了更高效、更可靠的电子产品。

让我们来了解一下什么是硅电容。

硅电容是一种能够存储电荷的电子元件,它由两个电极之间的绝缘层组成。

而台积电硅电容工艺则是一种特殊的制造工艺,用于制造这种硅电容。

台积电硅电容工艺的核心在于将硅材料转化为绝缘材料,以实现电容的功能。

在制造过程中,首先需要在硅基片上形成一层绝缘层。

这层绝缘层可以有效地隔离电极,避免电荷的泄漏。

然后,通过刻蚀和沉积等工艺步骤,将电极和绝缘层逐渐形成,最终完成硅电容的制造。

台积电硅电容工艺具有许多优势。

首先,它能够实现高集成度的制造,使得电路更加紧凑,性能更加优越。

其次,它具有较低的漏电流和较高的电容比,能够提高电子产品的稳定性和效率。

此外,台积电硅电容工艺还具有良好的耐高温性能,能够适应各种极端环境下的工作需求。

在实际应用中,台积电硅电容工艺被广泛应用于各种领域。

例如,它可以应用于存储器芯片的制造中,提高存储容量和读写速度。

同时,它还可以应用于微处理器的制造中,提高计算能力和功耗效率。

此外,它还可以应用于传感器和通信芯片等领域,为这些领域的发展提供强大支持。

台积电硅电容工艺是一项重要的技术创新,为电子产品的制造提供了可靠的基础。

它的出现不仅推动了半导体行业的发展,也为我们的生活带来了更多的便利和可能性。

随着科技的不断进步,相信台积电硅电容工艺将会有更广阔的应用前景,为人类创造更美好的未来。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

芯片设计解决方案供应商微捷码(Magma)设计自动化有限公司日前宣布,台积电(TSMC)采用QuartzDRC进行其28纳米产品质量检验装置(productqualificationvehicle,PQV)测试芯片的物理验证。

PQV作为设计数据客户的代表,将广泛应用于生产设计中。

通过实施PQV测试芯片,台积电让客户能够对取得28纳米工艺芯片成功更有信心。

台积电之所以选择QuartzDRC是因为它可在轻松满足台积电苛刻精度需求的同时提供28纳米所需的出色验证周期和容量,使得他们不仅能够创新性有效地处理测试芯片的大量数据,而且还能为包含由微捷码和其它两家主流EDA供应商所布线的电路模块的设计提供签核精度。

“在28及28纳米以下节点,设计规则复杂性正急剧攀升,”微捷码定制设计业务部总经理AnirudhDevgan表示。

“台积电在这项重要的PQV上采用微捷码物理验证软件的决定就是QuartzDRC出色容量和速度的强有力证明。

”

“台积电通过率先开发和验证最先进工艺技术从而保持其市场和技术的领导者地位,”台积电(TSMC)XX表示。

“QuartzDRC的验证周期和处理大量数据的能力令人印象深刻,让我们能够快速验证28纳米工艺,让我们的客户能够更快开始使用这款产品。

”

QuartzDRC和QuartzLVS:最快速的全线性物理验证

微捷码的QuartzDRC和LVS产品经架构,可以用最短时间验证各种工艺节点以及各种大小的集成电路(IC)设计。

微捷码公司的解决方案是首款真正线性的物理验证解决方案,通过利用现有计算资源,验证周期比现有解决方案快上一个数量级。

同时,Quartz工具可与第三方IC实现流程完全兼容,能够读取传统物理验证工具所用的各种文件格式。