一种数字射频存储器的设计

一款深亚微米射频SoC芯片的后端设计与实现

一款深亚微米射频SoC芯片的后端设计与实现张志鹏;张超;刘铁锋【摘要】随着集成电路的发展,片上系统芯片(SoC)技术广泛应用于多种领域中,越来越多的射频、模拟、存储器模块集成到一块芯片中.SoC芯片后端设计面临尺寸特征小,芯片规模大,物理设计复杂程度高等问题.良好的芯片版图设计是集成电路实现和成功的基础之一.介绍了基于台积电0.18μmULL低功耗工艺设计的射频SoC 电路结构,在此基础上,详细说明了后端版图设计流程与布局规划,重点介绍了时钟模块设计,多时钟电路及复杂时序关系设计的后端布局处理,供电设计以及布线优化方法和技巧,对各类相关芯片的后端设计具有良好的借鉴意义.%With the development of integrated circuit, the system on chip (SoC) technology is widely used in many applications, as more and more RF modules, analog modules and memory modules are embedded into one chip. The SoC back-end design confronts more challenges such as smaller feature size, larger chip area and more complex physical design. A remarkable layout design is one of the elements of the integrated circuit implemention and success. RF SoC circuit structure based on TSMC 0.18μmULL low power consumption process design is introduced,and on this basis, back-end layout design process and layout planning are explained in detail,mainly focusing on the clock generation module design,back-end processing method of multi-clock circuit and complex timing relationshipdesign,power supply plan and layout optimization methods and techniques,that supplies a good reference to many relevant kinds of beck-end chip design.【期刊名称】《微处理机》【年(卷),期】2017(038)006【总页数】6页(P1-6)【关键词】片上系统芯片;后端布局;多时钟设计;时钟生成;后端流程;供电设计【作者】张志鹏;张超;刘铁锋【作者单位】中国科学院沈阳自动化研究所网络化控制系统重点实验室,沈阳110016;中国科学院沈阳自动化研究所网络化控制系统重点实验室,沈阳110016;中国科学院沈阳自动化研究所网络化控制系统重点实验室,沈阳110016【正文语种】中文【中图分类】TP277随着集成电路的发展,片上系统芯片(SoC)技术在超大规模集成电路设计的开发与市场角度已经非常成熟,广泛应用于工业控制、智能手机、平板电脑等各类芯片中。

一文看懂数字射频存储器(DRFM)的框图及其功能

一文看懂数字射频存储器(DRFM)的框图及其功能什么是数字射频存储器(DRFM)数字射频存储器(DRFM)是一种微波信号存储系统,用于实现射频信号存储及转发功能。

数字射频存储器通过对接收到的射频信号进行高速采样、存储、变换处理和重构,实现对信号捕获和保存的高速性、干扰技术的多样性和控制的灵活性。

数字射频存储器已成为电子对抗系统中的关键组成部分。

数字射频存储器的基本工作原理数字射频存储(DRFM)的基本工作原理:首先将输入射频信号下变频为中频信号,经A/D变换后成为数字信号,写入高速存储器中。

当需要重发这一信号时,在控制器控制下读出此数字信号并由D/A变换为模拟信号。

然后用同一本振作上变频,得到射频输出信号,完成对输人信号的存储转发。

首先对量化过程进行分析,现假设基带输入信号为一个正弦信号gi(t)=Esinωit,量化位数为N,经过量化后的信号可用阶梯波y(t)表示,y(t)可以被认为是N对矩形波的叠加。

如果A/D变换的量化位数为m,那么正或负半周的量化台阶数为N=2m-1。

阶梯波的表达式为:E2n+1就是量化产生的谐波分量幅度,可由该式计算各阶谐波的功率。

在采样的过程中,为简便起见,以一位量化信号作为输入,则输入信号为:式中:E,ωi分别为输入信号的幅度和角频率。

设采样脉冲信号为fs(t),采样后的信号为fo(t),则采样过程在时域上的数学表示式为fo(t)=fi(t)fs(t),在DRFM中采用等间隔均匀采样,采样周期为Ts,采样时钟频率ωs=2πfs。

在实际电路中,采样是在采样脉冲上升的瞬间完成的。

因此采样脉冲的宽度可以看成一个窄脉宽,用τs。

来表示。

采样脉冲的傅里叶级数为:式中:Es,τs,Ts和ωs分别为采样信号的幅度、脉宽、周期和角频率。

则:。

RFID技术原理及其射频天线设计

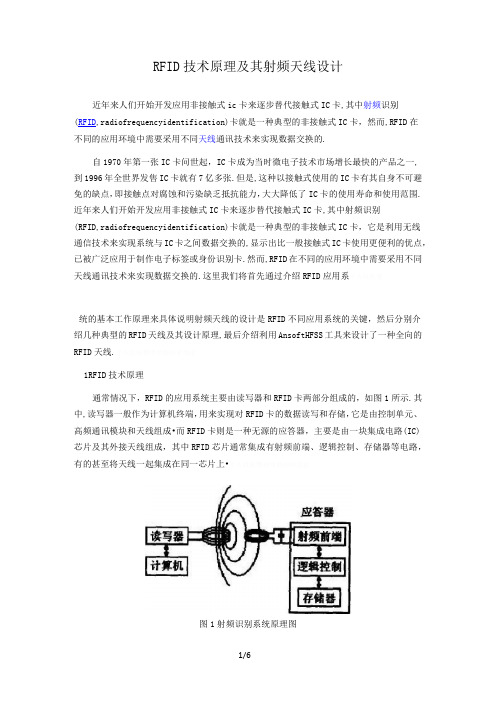

RFID技术原理及其射频天线设计近年来人们开始开发应用非接触式ic卡来逐步替代接触式IC卡,其中射频识别(RFID,radiofrequencyidentification)卡就是一种典型的非接触式IC卡,然而,RFID在不同的应用环境中需要采用不同天线通讯技术来实现数据交换的.自1970年第一张IC卡问世起,IC卡成为当时微电子技术市场增长最快的产品之一,到1996年全世界发售IC卡就有7亿多张.但是,这种以接触式使用的IC卡有其自身不可避免的缺点,即接触点对腐蚀和污染缺乏抵抗能力,大大降低了IC卡的使用寿命和使用范围.近年来人们开始开发应用非接触式IC卡来逐步替代接触式IC卡,其中射频识别(RFID,radiofrequencyidentification)卡就是一种典型的非接触式IC卡,它是利用无线通信技术来实现系统与IC卡之间数据交换的,显示出比一般接触式IC卡使用更便利的优点,已被广泛应用于制作电子标签或身份识别卡.然而,RFID在不同的应用环境中需要采用不同天线通讯技术来实现数据交换的.这里我们将首先通过介绍RFID应用系统的基本工作原理来具体说明射频天线的设计是RFID不同应用系统的关键,然后分别介绍几种典型的RFID天线及其设计原理,最后介绍利用AnsoftHFSS工具来设计了一种全向的RFID天线.1RFID技术原理通常情况下,RFID的应用系统主要由读写器和RFID卡两部分组成的,如图1所示.其中,读写器一般作为计算机终端,用来实现对RFID卡的数据读写和存储,它是由控制单元、高频通讯模块和天线组成•而RFID卡则是一种无源的应答器,主要是由一块集成电路(IC)芯片及其外接天线组成,其中RFID芯片通常集成有射频前端、逻辑控制、存储器等电路,有的甚至将天线一起集成在同一芯片上•图1射频识别系统原理图个人收集整理―仅供参考学习RFID应用系统的基本工作原理是RFID卡进入读写器的射频场后,由其天线获得的感应电流经升压电路作为芯片的电源,同时将带信息的感应电流通过射频前端电路检得数字信号送入逻辑控制电路进行信息处理;所需回复的信息则从存储器中获取经由逻辑控制电路送回射频前端电路,最后通过天线发回给读写器.可见,RFID卡与读写器实现数据通讯过程中起关键的作用是天线.一方面,无源的RFID卡芯片要启动电路工作需要通过天线在读写器天线产生的电磁场中获得足够的能量;另一方面,天线决定了RFID卡与读写器之间的通讯信道和通讯方式.目前RFID已经得到了广泛应用,且有国际标准:IS010536,IS014443,IS015693,IS018000等几种.这些标准除规定了通讯数据帧协议外,还着重对工作距离、频率、耦合方式等与天线物理特性相关的技术规格进行了规范.RFID应用系统的标准制定决定了RFID天线的选择,下面将分别介绍已广泛应用的各种类型的RFID 天线及其性能•2RFID天线类型RFID主要有线圈型、微带贴片型、偶极子型3种基本形式的天线.其中,小于1m的近距离应用系统的RFID天线一般采用工艺简单、成本低的线圈型天线,它们主要工作在中低频段.而1m以上远距离的应用系统需要采用微带贴片型或偶极子型的RFID天线,它们工作在高频及微波频段.这几种类型天线的工作原理是不相同的•2.1线圈天线当RFID的线圈天线进入读写器产生的交变磁场中,RFID天线与读写器天线之间的相互作用就类似于变压器,两者的线圈相当于变压器的初级线圈和次级线圈.由RFID的线圈天线形成的谐振回路如图2所示,它包括RFID天线的线圈电感L、寄生电容Cp和并联电容C2',其谐振频率为:f=]飞辽-C,(式中C为Cp和C2'的并联等效电容).RFID应用系统就是通过这一频率载波实现双向数据通讯的。

基于FPGA的数字存储系统硬件设计

( u i U i  ̄t o Ee r i Tcnl yG a gi u i 5 10 ,h a G i n e i l t n e o g ,u nx G i 0 4 C i l n v yf co c h o l 4 n n

【 btat i t e o a o pe edt aqitndt srg , do e fnt n wt abodpopc o apct nHg—pe i a A s c】Dga m m r cncm let a cusi , a taea t rucos i ra rs tf plao. i seds nl r il y th a i o a o n h i h e i i h g

李石林 , 吉海 , 良念 , 段 晋 谢跃 雷

( 林 电子科 技 大 学 信 息 与 通信 学 院 , 西 桂 林 5 10 ) 桂 广 40 4

【 摘

要 】数 字 存 储 器 可 以 完 成 数 据 采 集 、 据 存 储 等 功 能 , 有 很 广 泛 的 应 用 前 景。论 述 了 以 A e 数 具 hr 性 能 F G — a高 P A

Sy t m a d a e D e i n o gt lSt r g s d n se H r w r sg fDi ia o a e Ba e o FPG A

L hln, AN Jh i JN in na XI Yu li IS ii DU ia ,I La g in, E ee

统 , 以数字存储和高 速采样为技 术基础 , 般用 于射频 存储 时 间 通 过 上 位 机 设 定 。 再 把 数 据 调 出 送 给 它 一

和微波信号 的存储及转发 , 主要应用于电子对抗 和雷达等 D C 6 1 A 58 Z进行数模转换 。最后 射频 前 端把 数据 进 行上 系统整体架 领域 。它 主要 由射频前端部分和数据处理部分组 成 , 射频 变频重新发生 出去 。从而 实现上述应用要求 , 部 分主要 包括下 变频模块 和上变频模块 。本文 主要 阐述 构如 图 1 所示。 基于 FG P A的数字射频存储器数据处理部分 过 充分利 用 F G P A内

宽带DDS设计与实现

宽带DDS设计与实现安涛;石远东;郑继刚【摘要】介绍了直接数字合成器(DDS)原理。

针对传统DDS工作频率低,瞬时带宽窄,杂散大等缺点,讨论了基于现场可编程门阵列(FPGA)的并行处理技术设计宽带DDS,利用高速数/模转换器(DAC)和大规模现场可编程门阵列(FPGA)实现了宽带DDS模块的设计,在宽带干扰机、宽带雷达信号波型产生器设计等领域具有广泛的应用前景。

%This paper introduces the principle of direct digital synthesizer(DDS),aiming at the disadvantages such as the low operating frequency,narrow instantaneous bandwidth,large clutter,etc.,discusses to design wide-band DDS based on the parallel processing technique of field programmable gate array(FPGA),uses fast digital/analog converter and large-scale FPGA to realize the design of wide-band DDS module,which has expand application foreground in domains such as wide-band jammer,wide-band radar signal waveform generator design,etc..【期刊名称】《舰船电子对抗》【年(卷),期】2012(035)004【总页数】4页(P105-107,120)【关键词】宽带直接数字合成器;并行处理;宽带干扰机;宽带雷达信号波型【作者】安涛;石远东;郑继刚【作者单位】船舶重工集团公司723所,扬州225001;船舶重工集团公司723所,扬州225001;船舶重工集团公司723所,扬州225001【正文语种】中文【中图分类】TN742.10 引言1971年,J.Tierney 等人在《A digiatal Frequency Synthesizer》中第1次提出了具有工程实现可能和实际应用价值的直接数字式频率合成器(DDS)的概念[1]。

射频电路设计原理与应用

【连载】射频电路设计——原理与应用相关搜索:射频电路, 原理, 连载, 应用, 设计随着通信技术的发展,通信设备所用频率日益提高,射频(RF)和微波(MW)电路在通信系统中广泛应用,高频电路设计领域得到了工业界的特别关注,新型半导体器件更使得高速数字系统和高频模拟系统不断扩张。

微波射频识别系统(RFID)的载波频率在915MHz和2450MHz频率范围内;全球定位系统(GPS)载波频率在1227.60MHz和1575.42MHz的频率范围内;个人通信系统中的射频电路工作在1.9GHz,并且可以集成于体积日益变小的个人通信终端上;在C波段卫星广播通信系统中包括4GHz的上行通信链路和6GHz的下行通信链路。

通常这些电路的工作频率都在1GHz以上,并且随着通信技术的发展,这种趋势会继续下去。

但是,处理这种频率很高的电路,不仅需要特别的设备和装置,而且需要直流和低频电路中没有用到的理论知识和实际经验。

下面的内容主要是结合我从事射频电路设计方向研究4年来的体会,讲述在射频电路设计中必须具备的基础理论知识,以及我个人在研究和工作中累积的一些实际经验。

作者介绍ChrisHao,北京航空航天大学电子信息工程学院学士、博士生;研究方向为通信系统中的射频电路设计;负责或参与的项目包括:主动式射频识别系统设计、雷达信号模拟器射频前端电路设计、集成运算放大器芯片设计,兼容型GNSS接收机射频前端设计,等。

第1章射频电路概述本章首先给出了明确的频谱分段以及各段频谱的特点,接着通过一个典型射频电路系统以及其中的单元举例说明了射频通信系统的主要特点。

第1节频谱及其应用第2节射频电路概述第2章射频电路理论基础本章将介绍电容、电阻和电感的高频特性,它们在高频电路中大量使用,主要用于:(1)阻抗匹配或转换(2)抵消寄生元件的影响(扩展带宽)(3)提高频率选择性(谐振、滤波、调谐)(4)移相网络、负载等第1节品质因数第2节无源器件特性第3章传输线工作频率的提高意味着波长的减小,当频率提高到UHF时,相应的波长范围为10-100cm,当频率继续提高时,波长将与电路元件的尺寸相当,电压和电流不再保持空间不变,必须用波的特性来分析它们。

3bit相位量化射频存储器的研究

频 方式 的差 异进 行 比较 。

1 1 几种 储频 方式 的 比较 .

利 用正交 储 频输 出信 号 的处 理 方 法 , 以得 到 可 3i相 位量 化储频 输 出信 号 的级 数表 达式 : bt

)=

2

雷达在噪声中检测 目标的能力。射频信号存储技术

在现 代雷 达对 抗 中广 泛应 用 , 对相 参 雷 达 进 行 欺 骗

cr u t i i y. c r

Ke r s: DRF ; p a e dg t i g ADC;RAM y wo d M h ii zn s i

O 概 述

现代 雷 达 越 来 越 多 地 采 用 相 参 脉 冲 串检 测 目 标, 它不 但能 实 现 测 速 , 重 要 的是 相 参 积 累 , 高 更 提

D F 它除 了能对 相干 / 相 干雷 达欺 骗 干扰 外 , R M, 非 也 可用 于脉 冲多 普勒 雷 达 噪 声 干 扰 的射 频 源 , 可 进 并

分外, 7 第 次谐波的功率最大, 如果不采取任何处理谐

波 的措施 , 3比特相位 量化结构最坏情况 下的寄生信号

约 7 , 单比 度 为1B比 特幅 量化DF ( =2 d RM( £ ) ∑

字储 频 的基 本 原理 和各 种 不 同方 式的构 成及 一 种基 本 的应 用 电路 。

关键词 :数字射频存储器 ;相位量化 ;数据存储

Re e r h o i h s i ii i g r d o f e u n r e o y s a c n 3 tp a e d g tz n a b i r q e c y m m r

l1 0

一

维普资讯

得到 了改 善 , 最坏 情 况下 的寄 生信 号是 7次谐 波 ( 幅

数字IC设计

数字IC设计数字IC设计是指采用数字电路元件和技术,在符合设定功能要求的基础上,实现指定功能的集成电路设计。

数字IC设计是集成电路设计的一个重要分支,该设计应用面广,广泛应用于通信、计算机、工业、家用电器等领域中。

本文将从数字IC设计的概念、发展历程、设计方法、常用的设计工具等方面进行探讨。

一、数字IC设计的概念数字IC设计是指使用数字电路元件及技术,在设定的功能要求的前提下,实现指定功能的集成电路的设计。

数字IC设计是由组合逻辑、时序逻辑、存储器等数字电路元件构成的。

数字IC设计的核心是实现数字电路设计的复杂性,在各种复杂的应用领域中,进行数字电路系统的快速设计和优化。

数字IC设计的关键是实现函数逻辑关系的描述和形式化,使用数字语言,对电路系统的逻辑关系进行严格的描述和方便化的实现。

数字IC设计具有复杂性、可扩展性、可靠性、精度高、功耗低等特点。

二、数字IC设计的发展历程数字IC设计发展历程从20世纪60年代开始,到今天数十年来经历了从基础到高级的一系列发展过程。

其中有一些重要的里程碑事件,大大促进了数字IC设计的发展。

早期的数字IC设计是使用硬件直接链接模拟电路实现,其设计过程比较简单,如模拟计算器。

1971年,美国Texas Instruments公司推出了世界上第一款集成电路计算器TMS0100,该计算器采用了数字IC设计技术进行实现。

在此之后,数字IC设计开始迎来了快速的发展,人们越来越依赖集成电路和数字IC设计技术带来的方便和高效性。

20世纪80年代,数字IC的设计和制造技术日趋成熟,数字IC的速度和芯片的集成度愈加高。

随着数字IC设计技术的不断提高和发展,出现了大规模集成(LSI),超大规模集成(VLSI)和超高规模集成(UHVSI)等技术,这一系列的技术标志着数字IC设计的进一步发展。

21世纪以来,数字IC设计技术与微电子技术的迅速发展,尤其是3D器件、功能扩张技术和生物微型芯片等的出现,有力地推动了数字IC设计技术向更为高级、复杂和智能方向发展,以应对日益复杂的计算和控制技术需求。

射频电路设计DDS

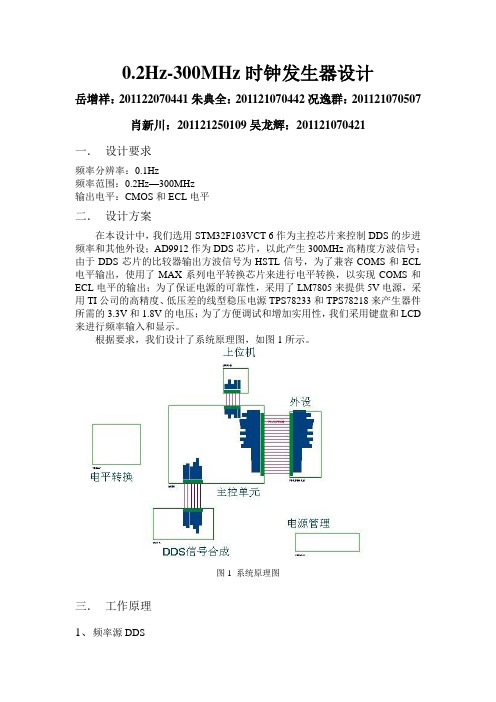

0.2Hz-300MHz时钟发生器设计岳增祥:201122070441朱典全:201121070442况逸群:201121070507肖新川:201121250109吴龙辉:201121070421一.设计要求频率分辨率:0.1Hz频率范围:0.2Hz—300MHz输出电平:CMOS和ECL电平二.设计方案在本设计中,我们选用STM32F103VCT 6作为主控芯片来控制DDS的步进频率和其他外设;AD9912作为DDS芯片,以此产生300MHz高精度方波信号;由于DDS芯片的比较器输出方波信号为HSTL信号,为了兼容COMS和ECL 电平输出,使用了MAX系列电平转换芯片来进行电平转换,以实现COMS和ECL电平的输出;为了保证电源的可靠性,采用了LM7805来提供5V电源,采用TI公司的高精度、低压差的线型稳压电源TPS78233和TPS78218来产生器件所需的3.3V和1.8V的电压;为了方便调试和增加实用性,我们采用键盘和LCD 来进行频率输入和显示。

根据要求,我们设计了系统原理图,如图1所示。

图1 系统原理图三.工作原理1、频率源DDS直接数字式频率合成器DDS(Direct Digital Synthesizer),实际上是一种分频器:通过编程频率控制字来分频系统时钟(SYSTEM CLOCK)以产生所需要的频率。

DDS 有两个突出的特点,一方面,DDS工作在数字域,一旦更新频率控制字,输出的频率就相应改变,其跳频速率高;另一方面,由于频率控制字的宽度宽(48bit 或者更高),频率分辨率高。

DDS 的内部结构如图2所示,它主要分成3 部分:相位累加器,相位幅度转换,数模转换器(DAC)。

图2 DDS内部结构图DDS的基本原理是利用采样定理,通过查表法产生波形。

DDS的结构有很多种,其基本的电路原理如图3所示。

图3 DDS基本电路原理图相位累加器由N位加法器与N位累加寄存器级联构成。

一种先进结构的数字射频存储器分析

技术 的研究 , 前 已有多种形式的 D F 用于电子战 目 RM 装备 中, 几种 国外具有代表性的 D F R M如表 1 所示 。

固有缺点 : 转发信号与输人信号不相干, 储频时间受限 以致 于不 能实 现距 离 波 门 向前拖 引 、 能产 生 高 工 作 不 比的干扰信号 、 不能对新体制雷达( 脉内线性调频 、 相 位编码 ) 形成有效的欺 骗干扰信号 , 能对 多个 辐射 不 源进行干扰等 ; 在一定 的条件下 , R M重构的射频信 DF

【 关键 词】 数字射频存储 器 ; 数字单边带调制器 ; 希尔伯特变换

中图分类号 :N 5 T 97 文 献标识码 : A

Anay i fa v nc d g t lRa i e ue c e o y l sso n Ad a e Diia d o Fr q n y M m r

维普资讯

第2 9卷

第 4期

现 代 雷 达

Mo e n Ra a d r d r

Vo. 9 No 4 12 . A r 0 7 pi 20 l

20 0 7年 4月

பைடு நூலகம்

一

种 先 进 结构 的数 字 射 频 存储 器 分 析

刘 忠 , 陈登伟 王 国玉 肖顺平 , ,

p i cp e ,h r a o p l ai n a d s e i c t n e 1 h n u n e o e df r n o g rt n o sp roma c a a tr rn i l t e ae fa p i t n p cf ai ta .T e if e c ft i e e tc n u ai n i e f r n e p r me e. c o i o l h i f o t

FIFO

( )可重 复读取 功 能 。 5

由于 S E S C I ( 具 有 以上 特性 , UP R YN S F F )

使得 它非 常适 合 于在 D M 中作 数 据存 储 与 延 RF 时存 储 器 , 面 以 9位 宽 的 7 V 8 ( 4k字节 ) 下 2 2 1 6

收 稿 日期 : 0 1 0 —2 20 — 9 0

单 路 数 据 存 储 , 设 系统 工 作 在 最 大 时 钟 频 率 假

1 0MHz , F 的延 时分 辨 率就 是 F F 的 0 上 DR M IO

读 写 时钟周 期 ( 0n ) 最 大 可存 储 脉 冲长 度 是 i s ;

摘要 提出了一种基于FF IO的数字射频存储器( I D M) 设计构想。系统对接收到的雷达信号进行

实 时 高 速 连 续 采 集 , 利 用 FF 能 够 对 采集 的 数 据 流 延 迟 一 段 恒定 时 问 的 特 性 实 现 距 离 波 门 拖 引 和 多 假 并 IO 目标 欺 骗 干 扰 。F F 的应 用 大 大 简 化 了 D F 系统 的复 杂 程 度 , 高 了 系 统 的 可 靠 性 和 稳 定Байду номын сангаас性 , 且 可 I O R M 提 并 以应用时钟分相 等技术成倍扩展干 扰机的瞬时工作带宽 。

关键 词

FF IO

DF R M

距离波门拖引

多假目 标干扰

时钟分相技术

0 引 言

现 代雷 达普 遍 采 用脉 冲压 缩 、 位编码 等 复 相 杂信号 处 理技 术 , 数字 射频 存 储 器 ( DRF 由于 M) 具 有对 付 这些 相参 波 形 的能 力 , 广 泛地应 用 于 被 电子对 抗 领域 。D M 将 接 收 的雷 达 脉 冲 采 集 RF 后存 储 , 后 重 新 调 用 这 个 信 号将 它 转 发 出去 , 然 产生 干扰 脉 冲对 敌 方 雷 达 进 行 欺 骗 干 扰 。在 理 想情 况下 , 以认 为 DR M 产 生 的 干 扰 信 号 与 可 F

基于固态存储技术的DRFM设计

基于固态存储技术的DRFM设计陈敬;谢启友;田晓波;杨埸;聂洪山;徐欣【摘要】Using the principle of modular design and taking a platform of PXIE to improve reading and writing speed,storage depth and flexibility of DRFM. High-speed reading and writing of the signals are achieved by solid-state memory techniques , the upper and lower frequency conversion modules , intermediate frequency signal collecting modules, intermediate frequency signal restore modules, memory modules and processing core are also designed. The application of solid-state memory and PXIE techniques in DRFM are studied as a main part, which provides some references for further improvement of DRFM.%为了提高数字射频存储器(DRFM)的存取速度、存储深度和系统的灵活性,采用了模块化设计原则.以PXIE 机箱为平台,运用固态存储技术实现信号的高速存取,完成了包括上、下变频模块、中频信号采集模块、中频信号还原模块、固态存储模块以及处理控制核心等电路的设计.重点研究固态存储技术和PXIE技术在DRFM中的应用,为进一步提高DRFM 的性能提供了参考.【期刊名称】《现代电子技术》【年(卷),期】2011(034)008【总页数】3页(P154-156)【关键词】DRFM;FPGA;固态存储;PXIE【作者】陈敬;谢启友;田晓波;杨埸;聂洪山;徐欣【作者单位】国防科学技术大学,电子科学与工程学院,湖南,长沙,410073;国防科学技术大学,电子科学与工程学院,湖南,长沙,410073;国防科学技术大学,电子科学与工程学院,湖南,长沙,410073;国防科学技术大学,电子科学与工程学院,湖南,长沙,410073;国防科学技术大学,电子科学与工程学院,湖南,长沙,410073;国防科学技术大学,电子科学与工程学院,湖南,长沙,410073【正文语种】中文【中图分类】TN911-340 引言随着雷达技术的快速发展,尤其是现代雷达采用了脉冲压缩、相位编码等复杂的调制技术,使得传统的电子欺骗干扰很难奏效。

rfsoc参数

RFSOC参数1. 什么是RFSOCRFSOC(RF System-on-Chip)是一种集成了射频(RF)和数字信号处理(DSP)功能的芯片。

它结合了射频前端和数字处理器,能够实现高性能的无线通信和信号处理功能。

RFSOC通常用于无线通信、雷达、无线电频谱监测等领域。

2. RFSOC参数的重要性RFSOC参数是描述RFSOC性能和功能的指标,对于选择合适的RFSOC芯片和优化系统设计非常重要。

以下是一些常见的RFSOC参数:2.1 射频参数•频率范围:RFSOC芯片能够工作的射频频率范围。

•带宽:RFSOC芯片能够处理的射频信号带宽。

•功率:RFSOC芯片的射频输出功率。

•噪声系数:RFSOC芯片的射频输入和输出接口的噪声性能。

•动态范围:RFSOC芯片能够处理的最大和最小信号强度之间的差异范围。

2.2 数字信号处理参数•时钟频率:RFSOC芯片的数字信号处理器的时钟频率。

•处理能力:RFSOC芯片能够处理的数据量和算法复杂度。

•存储容量:RFSOC芯片的内部存储器容量。

•接口:RFSOC芯片的数字信号处理器与其他设备之间的接口类型和数量。

2.3 其他参数•功耗:RFSOC芯片的功耗特性,包括待机和工作状态的功耗消耗。

•温度范围:RFSOC芯片能够正常工作的温度范围。

•封装:RFSOC芯片的封装类型和尺寸。

3. RFSOC参数的选择与优化在选择和优化RFSOC参数时,需要考虑以下几个方面:3.1 系统需求首先需要明确系统的需求,包括射频频率范围、带宽要求、信号处理能力等。

根据系统需求,选择合适的RFSOC芯片,并根据具体应用场景进行参数优化。

3.2 射频性能对于射频应用,射频性能是至关重要的。

需要选择具有较宽频率范围和较低噪声系数的RFSOC芯片。

同时,射频功率和动态范围也需要根据具体应用场景进行选择和优化。

3.3 数字信号处理能力对于数字信号处理应用,需要选择具有较高时钟频率和较大存储容量的RFSOC芯片。

数字射频存储器及其在雷达信号模拟中的应用

矍件 … … … … -

出

示 。

图 1 DRF 工 作 原 理 M

Fi 1 Prncpe f g. i i l o DR FM

图 2 AD 变 换 过 程 图

Fi 2 Pr c s fAD o ve t r g. o e s o c n ro

Absr c : i p rde c i s t e p i cp e ofDRFM t mph ss plc d o p iussgn llve t a t Th spa e s rbe h rn i l wih e a i a e n a s uro i a e l i du e y a p iud u n ia i n c d b m lt e q a tz ton. I ve he e r s in o tgi s t xp e so fDRFM u p t sgn l a e e a mp r a t o t u i a nd s v r li o t n f c o sn e O bec nsd r d.Fi a l a t r e d t o i e e nl y,a p lc to c n ro t a a c o smu a o s d o n a p ia in s e a i o r d re h i l t rba e n DRFM sa — i s t b ih d. a ls e

Ke r : y wo ds DR FM ; r d re ho sm ult ;s ro ssgn llv l a a c i aor pu i u i a e e

MOS管原理应用非常详细

MOS管原理应用非常详细MOS管,即金属-氧化物-半导体场效应晶体管,是一种常用的半导体器件。

它由金属门极、绝缘层氧化物和半导体衬底构成,通过改变门电极上的电压来控制电流的流动。

MOS管的原理和应用非常广泛,并在各个领域有着重要的作用。

首先,MOS管的工作原理是基于电场效应。

当门极上施加电压时,会产生电场,从而改变绝缘层中的电荷分布情况。

当电场增大时,绝缘层中的电荷分布受到影响,使得半导体中的载流子浓度发生变化,从而改变电流大小。

因此,通过改变门电压,可以控制MOS管的电流。

MOS管的应用非常广泛。

最常见的应用是在数字集成电路中用于逻辑门和存储器的设计。

在逻辑门中,MOS管被用于实现与门、或门、非门等基本逻辑功能。

在存储器中,MOS管则被用于SRAM(静态随机存储器)和DRAM(动态随机存储器)等存储单元的构建。

此外,MOS管还被广泛应用于模拟电路中。

由于MOS管具有输入电阻大、功耗低和可靠性高等优点,它被用于放大器、滤波器和振荡器等电路的设计。

在放大器中,MOS管可以作为信号放大的关键部分,将小信号输入经过放大后输出。

在滤波器中,MOS管可以用于实现低通滤波、高通滤波、带通滤波或带阻滤波的功能。

在振荡器中,MOS管则可以用于产生稳定的交流信号。

同时,MOS管还被用于功率器件中。

由于MOS管具有低导通电阻和大功率承受能力,它被用于开关电源、电机驱动和功率放大器等高功率电路的设计。

在开关电源中,MOS管用于控制电源的开关状态,从而实现高效率的能量转换。

在电机驱动中,MOS管用于控制电机的启停和转速,实现精确的运动控制。

在功率放大器中,MOS管用于放大音频信号或射频信号,提供更大的输出功率。

此外,MOS管还有其他一些特殊的应用。

例如,在光电子学中,MOS管可以用于光传感器的设计,通过光照的变化来改变门极电压,实现光传感效应。

在生物医学中,MOS管可以用于生物传感器的设计,通过检测生物样品中的生物分子浓度或电位变化来实现生物分析。

射频读卡器工作原理

射频读卡器工作原理射频读卡器是一种用于读取射频卡(RFID卡)的设备,其工作原理基于无线电波的相互作用。

以下是有关射频读卡器工作原理的详细信息。

1. 基本概念:射频读卡器由一个射频信号发射器和一个射频信号接收器组成。

发射器能够产生一种特定频率的射频信号,并将其发送到射频卡上。

接收器则能够接收和解读从射频卡返回的信号。

2. 无线电波传输:射频读卡器工作的核心部分是无线电波传输。

发射器通过电路将电能转换为无线电波,并将其发送到外部环境中。

射频读卡器通常使用特定频率的电磁波,通常是125kHz、13.56MHz或UHF频段。

3. 电磁感应原理:射频卡内部嵌入了一个天线,它可以接收射频读卡器发送的无线电波,并通过电磁感应的原理将其转换为电能。

当射频卡靠近射频读卡器时,两者之间会发生电磁耦合现象,从而形成一个电磁共振回路。

4. 能量传输和数据传输:在与射频读卡器进行共振之后,射频卡内的微芯片会通过接收到的电能来供电,并运行存储在芯片中的数据和处理算法。

同时,射频卡也会向射频读卡器发送反馈信号,其中包含了存储在射频卡上的信息。

5. 数据处理:射频读卡器接收到射频卡返回的信号后,会将其转换为数字信号,并通过内部的处理器和接口对其进行解码和处理。

经过处理后,读卡器可以从射频卡中读取和写入数据。

6. 通信协议:射频读卡器和射频卡之间的通信需要遵循特定的协议。

常见的射频卡通信协议包括ISO 14443、ISO 15693和ISO 18000-6C等。

这些协议规定了射频卡和读卡器之间的通信方式、数据格式和安全性等。

7. 应用领域:射频读卡器广泛应用于各个领域,包括物流、智能门禁、门诊挂号、货物追踪、仓储管理、电子商务、支付系统等。

射频读卡器具有非接触式读取、高速度、高精度、远距离读取以及多卡同时读取的优点。

总结来说,射频读卡器通过无线电波传输和电磁感应原理与射频卡进行通信。

通过将电能传输到射频卡内部的天线上,射频读卡器能够读取射频卡上的信息并进行数据处理。

DRFM在数字化干扰中的应用

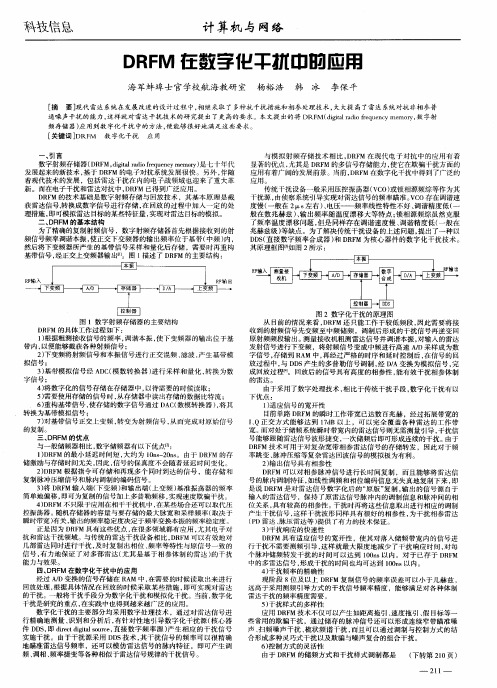

与模 拟射频存 储技术相 比 , R M在现代 电子对抗 中的应用有 着 DF 显著 的优点 , 尤其是 D F R M的多信号存储能力 , 它在欺 骗干扰方 面的 使 应 用 有 着 广 阔 的 发 展 前 景 。当 前 , R M 在 数 字 化 干 扰 中得 到 了 广泛 的 DF 应用 。 传统干扰设备一般采用 压控 振荡器( C 或锁相源频综等作为其 V O) 干扰源 , 由侦察系统引导实现对雷 达信号 的频率瞄准 。 O存 在调谐速 VC 度慢 ( 一般在 2 左 右) 电压——频 率线性 特性 不好 、 S 、 调谐 精度低 ( 一 般在数兆赫 兹 )输 出频率 随温度漂移 大等特点 ; 、 锁相源频综虽 然克服 了频率温度 漂移问题 , 是同样存在调谐 速度慢 、 但 调谐精度 低( 一般在 兆赫兹级 ) 等缺点。为了解 决传 统干扰设备的上述问题 , 提出 了一种 以 D S 直接数字频率 合成器 ) D M为核 心器件 的数字化干扰技 术。 D( 和 RF 其原理框图 如图 2 所示 :

图 1数字射频存储器 的主要结构

D M 的 具 体 工作 过 程 如 下 : RF

1根据粗测接收信 号的频 率 , ) 调谐 本振 , 使下变频器 的输 出位 于基 带 内, 以便能够截 获各种射频信号 ; 2 下变频将射频信号和本振信 号进行 正交混频 、 ) 滤波 , 产生基带模 拟信号 ; 3 基带模拟信号经 A C 模数转换器 ) ) D ( 进行采样和量化 , 转换为数 字信号 ; 4) 数字化 的信号存储在存储器 中, 将 以待需 要的时候读取 ; 5需要使用存储 的信号时 , ) 从存储器中读出存 储的数据 比特 流; 6 重构基带信号 , ) 使存储的数字信号通过 D C 数模 转换器 )将其 A( , 转换为基带模拟信号 ; 7) 对基带信号正交上变频 , 转变为射频信号 , 而完成对原始信号 从 的复制 。

wcbs硬件架构设计

wcbs硬件架构设计WCBS硬件架构设计概述WCBS(Wireless Communication Base Station)是一种无线通信基站,用于提供无线通信服务。

其硬件架构设计是保证基站正常运行的关键。

本文将对WCBS硬件架构设计进行详细介绍。

一、总体架构设计WCBS硬件架构设计分为两个主要部分:基带处理和射频处理。

基带处理部分负责数字信号的处理和调制解调,射频处理部分负责射频信号的放大和发射。

1. 基带处理基带处理部分包括处理器、存储器和数字信号处理模块。

处理器负责控制整个基站的运行,存储器用于存储数据和程序,数字信号处理模块用于对数字信号进行处理和调制解调。

2. 射频处理射频处理部分包括射频收发模块、功放模块和天线。

射频收发模块负责接收和发送射频信号,功放模块用于放大射频信号,天线用于发送和接收信号。

二、详细设计1. 基带处理详细设计基带处理部分采用高性能的处理器,具有较大的存储容量和高速的数据处理能力。

处理器采用多核架构,以支持多任务处理和并行计算。

存储器分为内存和闪存两部分,内存用于存储运行时数据,闪存用于存储程序和配置信息。

数字信号处理模块采用专用芯片,具有高速的信号处理能力和低功耗特性。

2. 射频处理详细设计射频收发模块采用高性能的射频芯片,具有较大的动态范围和高灵敏度。

射频收发模块包括射频接收机和射频发射机,通过调节接收和发射的频率和功率来实现无线通信。

功放模块采用高功率放大器,能够将射频信号放大到合适的功率级别。

天线采用高增益的天线,可以提高信号的覆盖范围和传输距离。

三、性能优化设计为了提高WCBS的性能,需要在硬件架构设计中考虑以下几个方面:1. 高可靠性WCBS是通信基站,对可靠性要求较高。

在硬件设计中,需要采用冗余设计,如双机热备份、双电源供电等,以保证基站的持续运行。

2. 高性能为了提供高质量的通信服务,WCBS需要具备高性能的硬件。

处理器和数字信号处理模块需要具备高速的数据处理能力,射频芯片需要具备高动态范围和高灵敏度。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

万方数据

了数百对差分管脚和大量的普通I,Q脚,方便与ADC和片外SRAM接口。

其片内丰富的PLI。

资源使得时钟的产生变得更加容易。

片外大容量的片外存储器(GS864436)保证了样本的海量存储。

GS864436是总线速度高达200MHz的SRAM,每片容量为2M×32b。

由于ADC的采样率为1GHz,就单路I来降数据率为1GHz×8b,如此高的数据率显然难以直接和SRAM接口。

数据将在FPGA被降速为125MHz×64b后再送到SRAM中。

因此实际应用中2片存储器拼接为64b后用来存储I路数据,2片存储Q路数据。

和信号处理单元接口的光纤采用Agilent公司的2.5Gb/s光模块。

该光模块为双向光纤,一个通道发送数据,一个通道接收。

其原理框图如图2所示。

时

制・

¨

少

处

婵

图2高速数据采集原理框图

2.2信号处理单元设计

干扰算法的复杂性决定了信号处理总的运算量是巨大的。

目前极少有独立的运算处理单元能够满足系统处理能力的要求,因此如何构建一个并行处理系统是解决大运算能力的一个必要需求,在并行处理技术中如何协调组织各个处理单元并行工作是设计的一个难点所在。

信号处理单元包括6块TS板、l块光纤接口板、1块CPU板以及2块CPCI底板组成。

光纤接口板负责接收数据采集送来的样本信号,再经过机箱的总线传把数据传输给各块DSP板,DSP板对样本作相关处理后,通过LINK口方式把产生的干扰信号送到D/A板。

作为信号处理单元的核心部件DSP板,其选择应满足实时性,大存储,高数据带宽的基本要求,同时应具备易于多板卡互连的接口。

因此考虑以TSl01为DSP运算单元的通用信号处理板,该板卡主要性能如下:(1)单板处理能力。

由4片内核时钟为300MHz的TigerSHARC—TSl01组成,总处理能力可提供7.2GFLOPs浮点处理能力;外总线时钟为75MHz。

(2)系统接口及数据带宽。

4片TSlOl之间紧耦合互连,构成一个处理簇。

簇内总带宽2GB/s;DSP簇对外提供8个Link用于板间互连,每通道125MB/s,板间总带宽1GB/s;CPCI标准总线,33/66MHz、32/64bPCI接口;支持2个ePMC背板,提供】】233/66MHz,32/64bPMC接口;32b自定义总线,可以为后插板提供数据传输;定时同步总线,可以保证处理机内所有板卡的硬件同步和时钟同步。

(3)存储容量。

每个TSl01片内带有6MbSRAM,4片TSl01共享SDRAM最高2GB,另外有2~4MBZBTSRAM内存。

信号处理单元系统结构如图3所示。

图3信号处理单元结构示意图

图4为频偏100MHz信号经过接收机变频、基带解调为I,Q信号,再经过数据采集量化、存储、光纤传输后。

在光纤接口板上所测的各项性能指标。

图中可以看到:A/D的SNR为37.2dB,镜像抑制度为33.55dB,A/D有效位数达6.12b。

上述指标证明了接收机及高速数据采集设计的正确性。

图4100MHz点频信号测试结果图

2.3干扰波形(高速DAC)设计

干扰波形通过I。

INK口接收信号处理DSP板卡发送过来的基带I,Q数据,并用片外SRAM对数据进行乒乓存储;存储后干扰波形根据系统要求对基带I,Q数据进行数/模转换,数/模转换后的基带模拟信号通过运放进行分路,一路I,Q信号送调制器,另一路I。

Q信号用于自测。

FPGA采用Altera公司的EP2S90F1020,接收DSP数据的LINK口在FPGA内部实现。

两片SRAM采用GS864436,用作基带数据的缓存。

高速DAC采用富士通800MHz,14

b分辨率高

万方数据

速DAC。

其原理组成和实物如图5所示。

图5干扰波形原理框图

图6干扰波形、数据采集、DSP板卡实物图

3SAR干扰信号的产生

鉴于该项目的主要试验对象为机载SAR,就SAR干扰信号的产生过程作简单介绍。

SAR回波的数学模型如下:

s(r,.z)一[J(r,x)W,(r)砭多h,(r,x)3眨多h2(r)(1)式中:a(r,z)为目标二维反射特性;W,(,-)为SAR发射信号距离向天线方向图;h,(r。

z)为方位响应函数,其为距离r和方位z的二维函数;h:(,-,z)为距离响应函数,其为距离,-的一维函数,与方位z无关。

可见,SAR回波信号可表示为目标散射特性a(r,z)乘以距离向天线方向图W,(r);再相继与两个脉冲响应函数h,(,..z)和h:(r,z)的卷积。

这就是SAR模拟回波产生的二维卷积算法。

二维卷积算法可用于欺骗干扰信号的产生,这时还需要根据SAR平台运动参数、平台与于扰站的相对位置进行必要的多普勒补偿。

二维卷积法具体实现算法如下:

^^假设干扰信号是场景分布函数口(t,t。

),其中t是距离向快时间;t。

是方位向慢时间。

距离走动量zxR(t。

)为:

△lR(z。

)=^厂adt。

(2)式中:A为信号波长;六。

为多普勒中心频率。

距离向的参考函数可以表示为:

srefr(£)=exp(j7c忌j2)(3)式中:调频斜率是,=B/L;B为距离向信号的带宽;Tp为距离向信号时宽。

距离向欺骗干扰的实现是对距离向信号进行卷积处理,即:

s(;,t。

)=IFFT{FFT[a(t,tm)]・

FFTEsre^(:,£。

)]exp凸47c掣]}(4)

接下来获得方位向欺骗干扰信号,方位匹配函数可以写为:

srefa(f。

)一exp{j7c^,£备)(5)式中:工,为多普勒调频斜率。

由于有斜视角引起多普勒中心不为零,对方位时域数据作相位补偿,补偿的相位函数是:

exp{27c^dt。

}(6)方位向欺骗干扰的实现是对方位向信号进行卷积处理,即:

^

s7(t,t。

)一exp(27c厶t。

)・

IFFT{FFT[s(t,t。

)]FFT[sref。

(z。

)]}(7)经过二维卷积处理之后,可获得对应场景的干扰信

^

号57(t,t。

)。

图7SAR欺骗干扰信号产生流程图

4硬件设计注意事项

整个DRFM模块工作的频率很高,设计时应该严格按照高速电路的设计原则处理每一个细节。

4.1时钟的设计

时钟电路设计的好坏直接影响高速电路的工作性能。

为了防止高速时钟受到外界干扰或向外辐射干扰,需要把时钟的电源和地与其他的电源、地分开。

差分信号可以有效的防止干扰,把送入的时钟转换为差分的LVDS或ECL等电平后再使用,可以有效提高时钟质量。

板上送到不同地方而又有相位要求的两个时钟,例如送到两路ADC的时钟,走线要等长。

并控制好阻抗。

4.2电源和地的噪声

在高速电路中30%以上的噪声来自电源和地。

对

11

3万方数据

万方数据。