野火stm32主芯片STM32F103VET6资源分配

stm32f103中文手册[9]

![stm32f103中文手册[9]](https://img.taocdn.com/s3/m/b02a2b5c49d7c1c708a1284ac850ad02de8007d8.png)

stm32f103中文手册一、概述stm32f103是一款基于ARM Cortex-M3内核的32位微控制器,具有高性能、低功耗和高集成度等特点。

它适用于各种工业控制、消费电子、医疗设备、通信和汽车应用等领域。

stm32f103的主要特性有:主频可达72MHz的ARM Cortex-M3内核,支持Thumb-2指令集和嵌套向量中断控制器(NVIC)64KB至128KB的闪存(Flash)和20KB的静态随机存储器(SRAM)7个定时器,包括3个16位通用定时器、1个16位高级定时器、2个基本定时器和1个系统滴答定时器2个12位模数转换器(ADC),每个ADC有16个通道,可达1Msps的采样率2个数字模拟转换器(DAC),每个DAC有1个通道,可达1Msps的转换率3个通用同步异步收发器(USART),支持同步和异步模式,以及智能卡、IrDA和调制解调器接口2个串行外设接口(SPI),支持全双工和单向模式,以及多主机和多从机模式2个I2C总线接口,支持标准模式(100Kbps)、快速模式(400Kbp s)和快速模式+(1Mbps)1个USB 2.0全速设备接口,支持12Mbps的数据传输率1个CAN总线接口,支持标准帧和扩展帧格式,以及时间触发通信模式37到51个通用输入输出端口(GPIO),可配置为推挽或开漏输出,上拉或下拉输入,或者复用为其他外设功能7到12个外部中断线,可配置为上升沿、下降沿或双边沿触发3个电源管理模式,包括运行模式、睡眠模式和停止模式内部8MHz的高速内部振荡器(HSI),可作为系统时钟或PLL时钟的输入源外部4至16MHz的高速外部振荡器(HSE),可作为系统时钟或PLL 时钟的输入源内部40kHz的低速内部振荡器(LSI),可作为看门狗定时器或自动唤醒单元的时钟源外部32.768kHz的低速外部振荡器(LSE),可作为实时时钟或校准HSI的时钟源可编程电压检测器(PVD),可监测电源电压是否低于设定阈值,并产生中断或复位信号可选的温度传感器,可测量芯片内部温度,并通过ADC读取可选的备份域,包括4KB的备份SRAM和20个备份寄存器,可在断电后保持数据调试功能,包括串行线调试(SWD)接口和串行线观察(SWO)输出stm32f103有多种封装形式和引脚数目,如LQFP48、LQFP64、LQFP 100等。

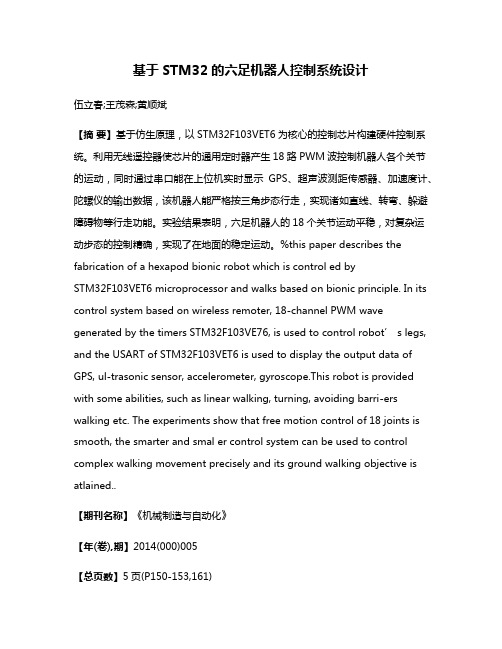

BR-STM32F103VET6最小系统板用户手册V1.0

BR-STM32F103VET6最小系统板用户手册v1.0一开发板简要功能说明1.标准ARM JTAG 20 PIN 仿真器接口, 方便连接JLINK, ULINK2等主流仿真器。

2.USB供电。

3.支持串口一下载,需要用杜邦线,将BOOT0引脚接到3.3V, 按复位键即可进入串口ISP下载。

4.8M时钟晶振,32.768khz RTC时钟晶振。

5.所有IO口均引出,方便接外部电路做实验。

6.电源指示灯D1。

7.两路LED灯D2,D3。

8.复位键K1。

9.USB接口,方便USB通讯实验。

10.SDIO TF卡接口。

11.SPI FLASH (M25P16)。

二引脚说明P1的位置,系统板图片正面下方。

P2的位置,系统板图片正面右侧。

P3的位置,系统板图片正面上方。

三例程说明下列例程在Keil uVision4下编译验证。

BR-STM32-100-V1-LED闪烁BR-STM32-100-V1-M2516-SPI (参注1)注1:M2516所用的SPI3 重映设为SPI1使用,与JTAG接口冲突,给再次下载固件造成不便。

解决方法:1)进入ISP下载模式,使用JLINK或ISP下载线下载;2) JLINK/ULINK2设置为SWD模式进行下载.BR-STM32-100-V1-SDCard-SDIO-FATFSBR-STM32-100-V1-SD读卡器BR-STM32-100-V1-串口1DEMO附:STM32F103VET6CPU频率72M,FLASH 512KB,RAM 64KB,定时器8个,SPI接口3个,IIS接口2个,IIC接口2个,USART接口5个,CAN接口1个,USB接口1个,SDIO接口1个,ADC通道16个,DAC通道2个,I/O端口80个,封装LQFP1002012-2-13。

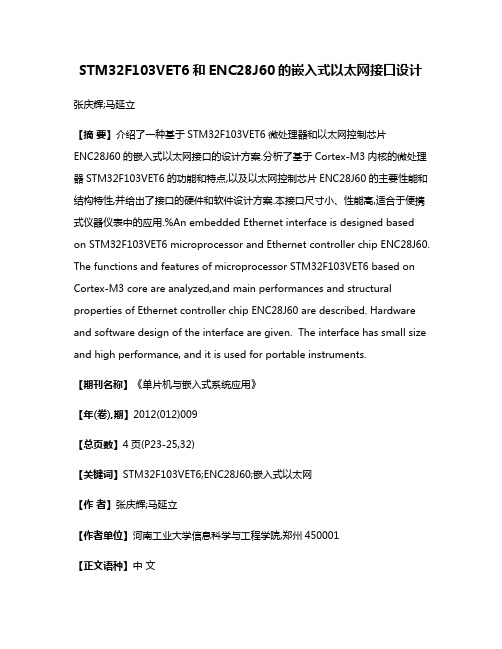

基于STM32的六足机器人控制系统设计

基于STM32的六足机器人控制系统设计伍立春;王茂森;黄顺斌【摘要】基于仿生原理,以STM32F103VET6为核心的控制芯片构建硬件控制系统。

利用无线遥控器使芯片的通用定时器产生18路PWM波控制机器人各个关节的运动,同时通过串口能在上位机实时显示GPS、超声波测距传感器、加速度计、陀螺仪的输出数据,该机器人能严格按三角步态行走,实现诸如直线、转弯、躲避障碍物等行走功能。

实验结果表明,六足机器人的18个关节运动平稳,对复杂运动步态的控制精确,实现了在地面的稳定运动。

%this paper describes the fabrication of a hexapod bionic robot which is control ed bySTM32F103VET6 microprocessor and walks based on bionic principle. In its control system based on wireless remoter, 18-channel PWM wave generated by the timers STM32F103VE76, is used to control robot’ s legs, and the USART of STM32F103VET6 is used to display the output data of GPS, ul-trasonic sensor, accelerometer, gyroscope.This robot is provided with some abilities, such as linear walking, turning, avoiding barri-ers walking etc. The experiments show that free motion control of 18 joints is smooth, the smarter and smal er control system can be used to control complex walking movement precisely and its ground walking objective is atlained..【期刊名称】《机械制造与自动化》【年(卷),期】2014(000)005【总页数】5页(P150-153,161)【关键词】STM32F103VET6;六足机器人;无线遥控;控制系统【作者】伍立春;王茂森;黄顺斌【作者单位】南京理工大学机械工程学院,江苏南京210016;南京理工大学机械工程学院,江苏南京210016;南京理工大学机械工程学院,江苏南京210016【正文语种】中文【中图分类】TP2420 引言移动机器人的发展是一个重要的科研领域,移动机器人可分为车轮式移动机器人、履带式机器人及其仿生技术的运动机器人[1]。

STM32F103VET6和ENC28J60的嵌入式以太网接口设计

STM32F103VET6和ENC28J60的嵌入式以太网接口设计张庆辉;马延立【摘要】介绍了一种基于STM32F103VET6微处理器和以太网控制芯片ENC28J60的嵌入式以太网接口的设计方案.分析了基于Cortex-M3内核的微处理器STM32F103VET6的功能和特点,以及以太网控制芯片ENC28J60的主要性能和结构特性,并给出了接口的硬件和软件设计方案.本接口尺寸小、性能高,适合于便携式仪器仪表中的应用.%An embedded Ethernet interface is designed based on STM32F103VET6 microprocessor and Ethernet controller chip ENC28J60. The functions and features of microprocessor STM32F103VET6 based on Cortex-M3 core are analyzed,and main performances and structural properties of Ethernet controller chip ENC28J60 are described. Hardware and software design of the interface are given. The interface has small size and high performance, and it is used for portable instruments.【期刊名称】《单片机与嵌入式系统应用》【年(卷),期】2012(012)009【总页数】4页(P23-25,32)【关键词】STM32F103VET6;ENC28J60;嵌入式以太网【作者】张庆辉;马延立【作者单位】河南工业大学信息科学与工程学院,郑州450001【正文语种】中文【中图分类】TP393.11引言随着以太网技术的普及和发展,基于以太网的应用接口设备也迅速普及到医疗设备、工厂电力系统等领域。

STM32F103VCT6开发板使用说明

STM32F103VCT6开发板使用说明一:开发板简单说明由内核STM32,一个串口(及串口控制芯片),一个外接flash,一个LCD屏(及LCD 控制芯片)等等构成。

Relaview仿真工具通过20针接口链接板子,另一个USB线提供电源。

二:Keil安装与破解正常安装MDK410过后,打开Keil工具File->License Management,获取软件CID后复制进破解工具Keil_Lic,如图选择芯片类型点击Generate按钮后,将序列号填入Keil软件即可(如有警告,则上述动作需要在有执行权限的系统账号下运行,如adm用户)三:样例工程创建1:需要事前说明,实际工程文件的组织结构与Keil软件界面显示的是两回事情,电脑文件系统中的结构是文件实际存储的结构,是文件真实存在的地方,而Keil软件界面看见的只是一个工程结构,只是一个组,为了方便,这些组可以取和文件系统下的文件夹一样的名字,但实际上两者是互不影响,互不关联的,组,仅仅只是一个名字,创建了组,并不会创建出对应的文件夹来。

2:STM32工程一般划分为如下几个文件夹,(1)USER,存放用户自己的具体功能程序文件;(2)CORE,存放arm内核文件,启动文件等;(3)OBJ,存放编辑过程中产生的文件;(4)SYSTEM,存放arm自己的系统文件,分两个类型,一个是寄存器版本,代码精简,但什么都要自己去控制,另一个是库函数版本,被厂家封装好,便于调用,但代码量比较臃肿;(5)HARDW ARE,存放一些基本的硬件控制文件,如IIC,LCD,LED,FLASH,按键,触摸屏等;(6)FWLib,存放了芯片上所有外设的驱动文件。

3:以一个两灯交替闪亮的程序为例,需要在对应工作文件空间建立如下几个文件夹:USER,CORE,OBJ,SYSTEM,HARDW ARE(LED)。

4:打开Keil工具,选择Project->New μVersion Project,开始创建工程如图后紧接着需要选择关联的芯片类型,我们选择STMicroelectronics->STM32F103VC,可以看见芯片的相关硬件参数,点击Ok后会提示是否需要拷贝STM 32的启动代码到工程文件中,可以选择是,为了初学,可以选择否后手工添加。

红牛开发板stm32f103zet6用户手册

红牛开发板用户手册 CopyRight@20091.概述红牛STM32开发板是以意法半导体 (ST)公司推出的基于ARM Cortex-M3系列最高配置芯片STM32F103ZE为核心组成。

板上资源:●CPU:STM32F103ZET6;(LQFP144脚,片上集成512K flash、64KRAM、12Bit ADC、DAC、PWM、CAN、USB、SDIO、FSMC等资源)●板上外扩512K SRAM, 2M NOR FLASH (板上支持最大1024kSRAM,16M的NOR FLASH)满足大容量数据采集、处理及分析要求●板上外扩128M或256M NAND FLASH(标配128M)满足彩屏上丰富的图片存储、数据表格存储,文件管理等应用● 搭配2.8寸TFT真彩触摸屏模块或3.2寸TFT真彩触摸屏模块(由用户选择),FSMC控制,彩屏模块上配置RSM1843(ADS7843、TSC2046脚对脚兼容)触摸控制器芯片,支持一个SD卡(SPI方式)可用于存储图片,支持一个AT45DBxxx 的DATA FLASH(可用于存储汉字库)● 一路CAN通信接口,驱动器芯片SN65VHD230● 两路RS232接口● 一路RS485通信接口● 一个SD卡座SDIO控制方式● 一个I2C存储器接口,标配24LC02(EEPROM)● 一个SPI存储器接口,标配AT45DB161D(DATA FLASH)● 一路ADC调节电位器输入● 三路ADC输入接线端子引出● 两路PWM输出接线端子引出● 两路DAC输出接线端子引出● 一个蜂鸣器、五个用户LED灯、一个电源指示灯,一个USB通信指示灯,● 四个用户按键,一个系统复位按键● 电源选择跳线,支持外接5V 电源供电,USB 供电或JLINK 供电 ● 板子规格尺寸:13CM X 10CM● 所有I/O 口通过2.54MM 标准间距引出,方便二次开发板上的全部硬件特性能快速帮助你评估STM32F103ZE 所有外设(USB 、motor control,、CAN,、SPI 、MicroSD card 、smartcard 、USART 、NOR Flash 、NAND flash 、 SRAM )和开发你自己的应用项目。

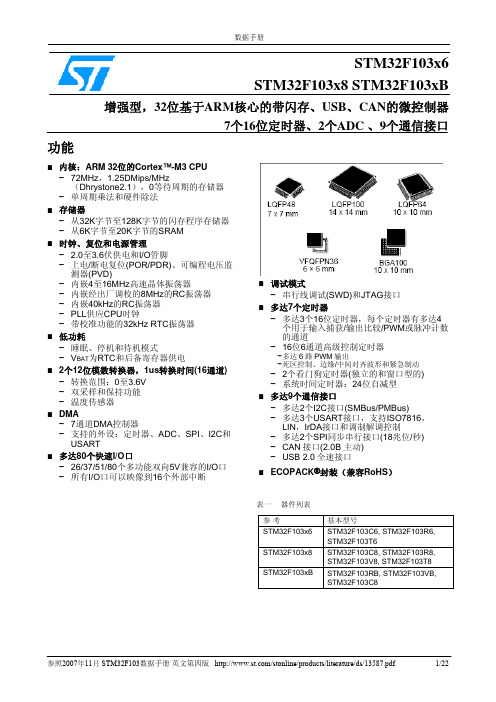

STM32F103VET6

− 睡眠、停机和待机模式 − VBAT为RTC和后备寄存器供电

■ 2个12位模数转换器,1us转换时间(16通道)

− 转换范围:0至3.6V − 双采样和保持功能 − 温度传感器

■ DMA − 7通道DMA控制器 − 支持的外设:定时器、ADC、SPI、I2C和 USART

■ 多达80个快速I/O口

− 2个看门狗定时器(独立的和窗口型的) − 系统时间定时器:24位自减型

■ 多达9个通信接口

− 多达2个I2C接口(SMBus/PMBus) − 多达3个USART接口,支持ISO7816,

LIN,IrDA接口和调制解调控制 − 多达2个SPI同步串行接口(18兆位/秒) − CAN 接口(2.0B 主动) − USB 2.0 全速接口

2 规格说明

STM32F103xx增强型系列使用高性能的ARM Cortex-M3 32位的RISC内核,工作频率为72MHz,内 置高速存储器(高达128K字节的闪存和20K字节的SRAM),丰富的增强I/O端口和联接到两条APB总 线的外设。所有型号的器件都包含2个12位的ADC、3个通用16位定时器和一个PWM定时器,还包 含标准和先进的通信接口:多达2个I2C和SPI、3个USART、一个USB和一个CAN。

ARM的Cortex-M3是32位的RISC处理器,提供额外的代码效率,在通常8和16位系统的存储空间上得 到了ARM核心的高性能。

STM32F103xx增强型系列拥有内置的ARM核心,因此它与所有的ARM工具和软件兼容。

图一是该系列产品的功能框图。

内置闪存存储器

● 高达128K字节的内置闪存存储器,用于存放程序和数据。

STM32F103xx增强型系列工作于-40°C至+105°C的温度范围,供电电压2.0V至3.6V,一系列的省电 模பைடு நூலகம்保证低功耗应用的要求。

MEMORY存储芯片STM32F103ZET6中文规格书

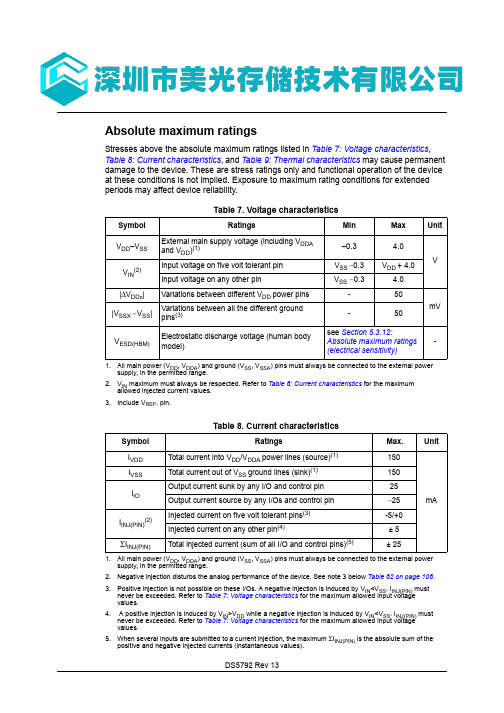

DS5792 Rev 13Absolute maximum ratingsStresses above the absolute maximum ratings listed in Table 7: Voltage characteristics , Table 8: Current characteristics , and Table 9: Thermal characteristics may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these conditions is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.Table 7. Voltage characteristicsSymbol RatingsMin Max UnitV DD –V SS External main supply voltage (including V DDAand V DD)(1)1.All main power (V DD , V DDA ) and ground (V SS , V SSA ) pins must always be connected to the external powersupply, in the permitted range.–0.3 4.0V V IN (2)2.V IN maximum must always be respected. Refer to Table 8: Current characteristics for the maximumallowed injected current values.Input voltage on five volt tolerant pin V SS − 0.3V DD + 4.0 Input voltage on any other pinV SS − 0.34.0|ΔV DDx |Variations between different V DD power pins -50mV |V SSX − V SS |Variations between all the different ground pins (3)3.Include V REF- pin.-50V ESD(HBM)Electrostatic discharge voltage (human body model)see Section 5.3.12:Absolute maximum ratings (electrical sensitivity)-Table 8. Current characteristicsSymbol RatingsMax.UnitI VDD Total current into V DD /V DDA power lines (source)(1)1.All main power (V DD , V DDA ) and ground (V SS , V SSA ) pins must always be connected to the external powersupply, in the permitted range.150mA I VSS Total current out of V SS ground lines (sink)(1)150I IO Output current sunk by any I/O and control pin 25Output current source by any I/Os and control pin − 25I INJ(PIN)(2)2.Negative injection disturbs the analog performance of the device. See note 3 below Table 62 on page 108.Injected current on five volt tolerant pins (3)3.Positive injection is not possible on these I/Os. A negative injection is induced by V IN <V SS . I INJ(PIN) mustnever be exceeded. Refer to Table 7: Voltage characteristics for the maximum allowed input voltage values.-5/+0Injected current on any other pin (4)4.A positive injection is induced by V IN >V DD while a negative injection is induced by V IN <V SS . I INJ(PIN) must never be exceeded. Refer to Table 7: Voltage characteristics for the maximum allowed input voltage values.± 5ΣI INJ(PIN)Total injected current (sum of all I/O and control pins)(5)5.When several inputs are submitted to a current injection, the maximum ΣI INJ(PIN) is the absolute sum of thepositive and negative injected currents (instantaneous values).± 25Electrical characteristics STM32F103xC, STM32F103xD, STM32F103xEDS5792 Rev 135.3 Operating conditions5.3.1General operating conditionsTable 9. Thermal characteristicsSymbol RatingsValue Unit T STG Storage temperature range –65 to +150°C T JMaximum junction temperature150°CTable 10. General operating conditionsSymbol ParameterConditionsMin Max Unitf HCLK Internal AHB clock frequency -0 72MHz f PCLK1Internal APB1 clock frequency -0 36f PCLK2Internal APB2 clock frequency -0 72V DDStandard operating voltage -2 3.6V V DDA (1)1.When the ADC is used, refer to Table 59: ADC characteristics .Analog operating voltage(ADC not used)Must be the same potential as V DD (2)2.It is recommended to power V DD and V DDA from the same source. A maximum difference of 300mVbetween V DD and V DDA can be tolerated during power-up and operation.2 3.6VAnalog operating voltage (ADC used)2.43.6V BATBackup operating voltage- 1.8 3.6V P DPower dissipation at T A = 85°C for suffix 6 or T A = 105°C for suffix 7(3)3.If T A is lower, higher P D values are allowed as long as T J does not exceed T J max (see Table 6.7: Thermalcharacteristics on page 132).LQFP144-666mW LQFP100-434LQFP64-444LFBGA100-500LFBGA144-500WLCSP64-400T AAmbient temperature for 6 suffix versionMaximum power dissipation -4085°C Low-power dissipation (4)4.In low-power dissipation state, T A can be extended to this range as long as T J does not exceed T J max (seeTable 6.7: Thermal characteristics on page 132).-40105Ambient temperature for 7 suffix versionMaximum power dissipation -40105°CLow-power dissipation (4)-40125T JJunction temperature range6 suffix version -40105°C7 suffix version-40125DS5792 Rev 13STM32F103xC, STM32F103xD, STM32F103xE Electrical characteristics5.3.2 Operating conditions at power-up / power-downThe parameters given in Table 11 are derived from tests performed under the ambienttemperature condition summarized in Table 10.5.3.3 Embedded reset and power control block characteristicsThe parameters given in Table 12 are derived from tests performed under ambient temperature and V DD supply voltage conditions summarized in Table 10.Table 11. Operating conditions at power-up / power-downSymbol ParameterConditionsMin Max Unit t VDDV DD rise time rate -0∞µs/VV DD fall time rate20∞Table 12. Embedded reset and power control block characteristicsSymbolParameterConditionsMin Typ Max UnitV PVDProgrammable voltage detector level selection PLS[2:0]=000 (rising edge) 2.1 2.18 2.26V PLS[2:0]=000 (falling edge)2 2.08 2.16PLS[2:0]=001 (rising edge) 2.19 2.28 2.37PLS[2:0]=001 (falling edge) 2.09 2.18 2.27PLS[2:0]=010 (rising edge) 2.28 2.38 2.48PLS[2:0]=010 (falling edge) 2.18 2.28 2.38PLS[2:0]=011 (rising edge)2.38 2.48 2.58PLS[2:0]=011 (falling edge) 2.28 2.38 2.48PLS[2:0]=100 (rising edge)2.47 2.58 2.69PLS[2:0]=100 (falling edge) 2.37 2.48 2.59PLS[2:0]=101 (rising edge) 2.57 2.68 2.79PLS[2:0]=101 (falling edge) 2.47 2.58 2.69PLS[2:0]=110 (rising edge) 2.66 2.78 2.9PLS[2:0]=110 (falling edge) 2.56 2.68 2.8PLS[2:0]=111 (rising edge) 2.76 2.883PLS[2:0]=111 (falling edge)2.66 2.78 2.9V PVDhyst (2)PVD hysteresis--100-mV V POR/PDR Power on/power down reset threshold Falling edge 1.8(1)1.The product behavior is guaranteed by design down to the minimum V POR/PDR value.1.88 1.96V Rising edge 1.84 1.922.0V PDRhyst (2)PDR hysteresis--40-mV T RSTTEMPO (2)2.Guaranteed by design.Reset temporization-12.54.5msElectrical characteristics STM32F103xC, STM32F103xD, STM32F103xEDS5792 Rev 13DS5792 Rev 13STM32F103xC, STM32F103xD, STM32F103xE Electrical characteristicsTable 14. Maximum current consumption in Run mode, code with data processingrunning from FlashSymbolParameterConditionsf HCLK Max (1)1.Guaranteed by characterization results.UnitT A = 85°CT A = 105°CI DDSupply current in Run modeExternal clock (2), all peripherals enabled 2.External clock is 8 MHz and PLL is on when f HCLK > 8 MHz.72 MHz 6970mA48 MHz5050.536 MHz 3939.524 MHz272816 MHz2020.58 MHz 1111.5External clock (2), all peripherals disabled 72 MHz 3737.548 MHz2828.536 MHz 2222.524 MHz16.51716 MHz 12.5138 MHz88Table 15. Maximum current consumption in Run mode, code with data processingrunning from RAMSymbolParameterConditionsf HCLK Max (1)1.Guaranteed by characterization results at V DD max, f HCLK max.UnitT A = 85°CT A = 105°CI DDSupply current in Run modeExternal clock (2), all peripherals enabled 2.External clock is 8 MHz and PLL is on when f HCLK > 8 MHz.72 MHz 6667mA48 MHz43.545.536 MHz 333524 MHz2324.516 MHz16188 MHz 910.5External clock (2), all peripherals disabled 72 MHz 3333.548 MHz2323.536 MHz 1818.524 MHz1313.516 MHz 1010.58 MHz66.5。

野火STM32开发板硬件一览表

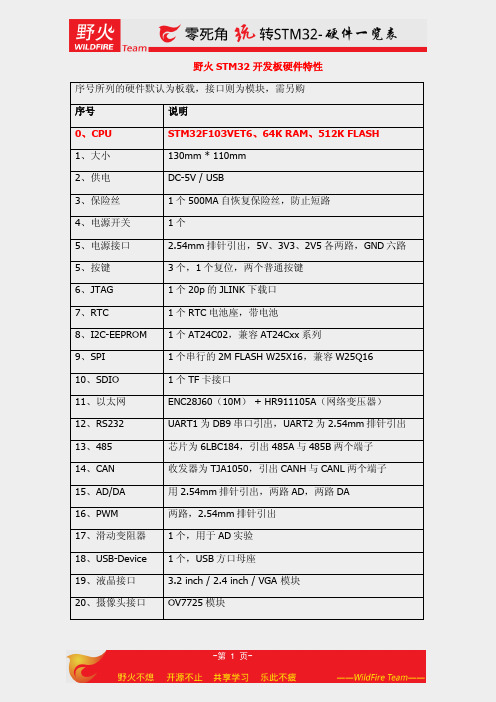

野火STM32开发板硬件特性序号所列的硬件默认为板载,接口则为模块,需另购序号说明0、CPU STM32F103VET6、64K RAM、512K FLASH1、大小130mm * 110mm2、供电DC-5V / USB3、保险丝1个500MA自恢复保险丝,防止短路4、电源开关1个5、电源接口 2.54mm排针引出,5V、3V3、2V5各两路,GND六路5、按键3个,1个复位,两个普通按键6、JTAG 1个20p的JLINK下载口7、RTC 1个RTC电池座,带电池8、I2C-EEPROM 1个AT24C02,兼容AT24Cxx系列9、SPI 1个串行的2M FLASH W25X16,兼容W25Q1610、SDIO 1个TF卡接口11、以太网ENC28J60(10M) + HR911105A(网络变压器)12、RS232 UART1为DB9串口引出,UART2为2.54mm排针引出13、485 芯片为6LBC184,引出485A与485B两个端子14、CAN 收发器为TJA1050,引出CANH与CANL两个端子15、AD/DA 用2.54mm排针引出,两路AD,两路DA16、PWM 两路,2.54mm排针引出17、滑动变阻器1个,用于AD实验18、USB-Device 1个,USB方口母座19、液晶接口 3.2 inch / 2.4 inch / VGA 模块20、摄像头接口OV7725模块21、三轴加速接口MMA7455模块22、无线接口 2.4G NRF24L01+模块23、音频接口MP3模块24、zigbee接口CC2530模块25、WIFI接口Mxchip EMW 系列 Wi-Fi 模块26、GPIO 多达40个IO可使用。

STM32F103VET6

STM32F103VET6参考《STM32F10x-英文参考手册》《零死角玩转STM32—F103指南者》秉火视频教程简介•Analog to Digital(模拟数字转换器)•三个独立ADC通道(STM32F103系列均有)•精度为12位(STM32F103系列均有)•ADC1,ADC2有18个通道(16个为内部);ADC3有根据F103系列的引脚不同而变化,一般有8个外部通道功能框图Figure 2-1 电压输入范围Figure 2-2Figure 2-A指南者开发板中,VREF+与VREF-分别连接到了3V3和地输入通道Figure 2-3输入通道分为规则通道和注入通道规则通道:平时使用,正常转换通道(16)注入通道:在规则转换时插队(4)转换顺序•规则序列寄存器 SQR1.2.3•注入序列寄存器 JSQR•注入序列寄存器JSQR 只有一个,最多支持4 个通道,具体多少个由JSQR 的JL[2:0]决定。

如果JL 的值小于4 的话,则JSQR 跟SQR决定转换顺序的设置不一样,第一次转换的不是JSQR1[4:0],而是JCQRx[4:0] ,x = (4-JL),跟SQR 刚好相反。

如果JL=00(1 个转换),那么转换的顺序是从JSQR4[4:0]开始,而不是从JSQR1[4:0]开始,触发源•软件触发•外部事件触发转换时间Figure 2-4•ADCCLK最大为14MHZ;一般经过ADC预分频器6分频得12MHZ数据寄存器规则数据寄存器•DR•16位有效•两个16位•DMA•中断读取数据(少用)注入数据寄存器•JDR•16位有效中断•EOC——end of complete•JEOC•AWD 模拟看门狗事件。

stm32f103cbt6参数

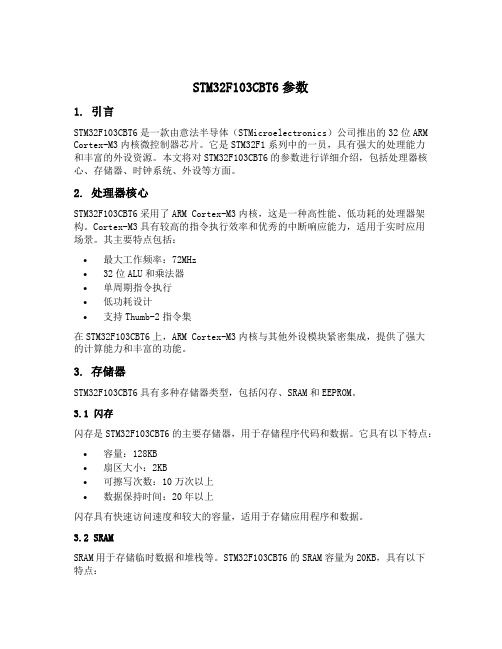

STM32F103CBT6参数1. 引言STM32F103CBT6是一款由意法半导体(STMicroelectronics)公司推出的32位ARM Cortex-M3内核微控制器芯片。

它是STM32F1系列中的一员,具有强大的处理能力和丰富的外设资源。

本文将对STM32F103CBT6的参数进行详细介绍,包括处理器核心、存储器、时钟系统、外设等方面。

2. 处理器核心STM32F103CBT6采用了ARM Cortex-M3内核,这是一种高性能、低功耗的处理器架构。

Cortex-M3具有较高的指令执行效率和优秀的中断响应能力,适用于实时应用场景。

其主要特点包括:•最大工作频率:72MHz•32位ALU和乘法器•单周期指令执行•低功耗设计•支持Thumb-2指令集在STM32F103CBT6上,ARM Cortex-M3内核与其他外设模块紧密集成,提供了强大的计算能力和丰富的功能。

3. 存储器STM32F103CBT6具有多种存储器类型,包括闪存、SRAM和EEPROM。

3.1 闪存闪存是STM32F103CBT6的主要存储器,用于存储程序代码和数据。

它具有以下特点:•容量:128KB•扇区大小:2KB•可擦写次数:10万次以上•数据保持时间:20年以上闪存具有快速访问速度和较大的容量,适用于存储应用程序和数据。

3.2 SRAMSRAM用于存储临时数据和堆栈等。

STM32F103CBT6的SRAM容量为20KB,具有以下特点:•高速访问•低功耗设计•数据保持时间:无需刷新SRAM提供了快速的读写能力,适合处理实时数据。

3.3 EEPROMEEPROM是一种可擦写、可编程的非易失性存储器,适用于存储配置信息、校准数据等。

STM32F103CBT6集成了1KB的EEPROM,具有以下特点:•容量:1KB•可擦写次数:100万次以上•数据保持时间:40年以上EEPROM可以在系统断电后仍然保存数据,确保关键信息不丢失。

MEMORY存储芯片STM32F103VCT6中文规格书

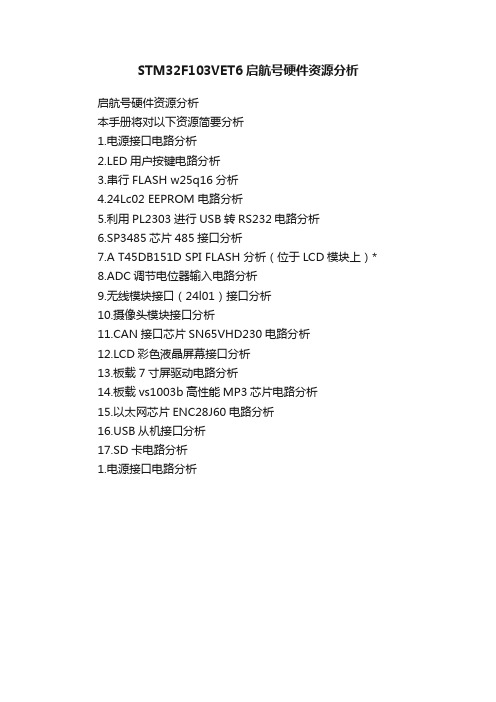

High-density performance line Arm®-based 32-bit MCU with 256 to 512KB Flash, USB, CAN, 11 timers, 3 ADCs, 13 communication interfacesDatasheet − production data Features•Core: Arm® 32-bit Cortex®-M3 CPU–72 MHz maximum frequency, 1.25DMIPS/MHz(Dhrystone 2.1) performance at 0 wait statememory access–Single-cycle multiplication and hardwaredivision•Memories–256 to 512 Kbytes of Flash memory–up to 64 Kbytes of SRAM–Flexible static memory controller with 4 Chip Select. Supports Compact Flash, SRAM,PSRAM, NOR and NAND memories–LCD parallel interface, 8080/6800 modes •Clock, reset and supply management – 2.0 to 3.6V application supply and I/Os–POR, PDR, and programmable voltage detector (PVD)–4-to-16 MHz crystal oscillator–Internal 8 MHz factory-trimmed RC–Internal 40 kHz RC with calibration–32 kHz oscillator for RTC with calibration •Low power–Sleep, Stop and Standby modes–V BAT supply for RTC and backup registers • 3 × 12-bit, 1 µs A/D converters (up to 21channels)–Conversion range: 0 to 3.6 V–Triple-sample and hold capability–Temperature sensor• 2 × 12-bit D/A converters•DMA: 12-channel DMA controller–Supported peripherals: timers, ADCs, DAC, SDIO, I2Ss, SPIs, I2Cs and USARTs •Debug mode–Serial wire debug (SWD) & JTAG interfaces–Cortex®-M3 Embedded Trace Macrocell™•Up to 112 fast I/O ports–51/80/112 I/Os, all mappable on 16 external interrupt vectors and almost all 5V-tolerant •Up to 11 timers–Up to four 16-bit timers, each with up to 4IC/OC/PWM or pulse counter and quadrature(incremental) encoder input– 2 × 16-bit motor control PWM timers with dead-time generation and emergency stop– 2 × watchdog timers (Independent and Window)–SysTick timer: a 24-bit downcounter– 2 × 16-bit basic timers to drive the DAC•Up to 13 communication interfaces–Up to 2 × I2C interfaces (SMBus/PMBus)–Up to 5 USARTs (ISO 7816 interface, LIN, IrDA capability, modem control)–Up to 3 SPIs (18 Mbit/s), 2 with I2S interface multiplexed–CAN interface (2.0B Active)–USB 2.0 full speed interface–SDIO interface•CRC calculation unit, 96-bit unique ID •ECOPACK® packagesTable 1.Device summary Reference Part numberSTM32F103xCSTM32F103RC STM32F103VCSTM32F103ZCSTM32F103xDSTM32F103RD STM32F103VDSTM32F103ZDSTM32F103xESTM32F103RE STM32F103ZESTM32F103VEJuly 2018DS5792 Rev 13Electrical characteristics STM32F103xC, STM32F103xD, STM32F103xEDS5792 Rev 13High-speed external clock generated from a crystal/ceramic resonatorThe high-speed external (HSE) clock can be supplied with a 4 to 16 MHz crystal/ceramic resonator oscillator. All the information given in this paragraph are based oncharacterization results obtained with typical external components specified in Table 23. In the application, the resonator and the load capacitors have to be placed as close aspossible to the oscillator pins in order to minimize output distortion and startup stabilization time. Refer to the crystal resonator manufacturer for more details on the resonator characteristics (frequency, package, accuracy).For C L1 and C L2, it is recommended to use high-quality external ceramic capacitors in the 5pF to 25pF range (typ.), designed for high-frequency applications, and selected to match the requirements of the crystal or resonator (see Figure 22). C L1 and C L2 are usually the same size. The crystal manufacturer typically specifies a load capacitance which is the series combination of C L1 and C L2. PCB and MCU pin capacitance must be included (10pF can be used as a rough estimate of the combined pin and board capacitance) when sizing C L1 and C L2. Refer to the application note AN2867 “Oscillator design guide for ST microcontrollers” available from the ST website .1.R EXT value depends on the crystal characteristics.Table 23. HSE 4-16 MHz oscillator characteristics (1)(2)1.Resonator characteristics given by the crystal/ceramic resonator manufacturer.2.Guaranteed by characterization results.Symbol ParameterConditionsMin Typ Max Unit f OSC_IN Oscillator frequency -4816MHz R F Feedback resistor--200-k Ω CRecommended load capacitance versus equivalent serialresistance of the crystal (R S )(3)3.The relatively low value of the RF resistor offers a good protection against issues resulting from use in ahumid environment, due to the induced leakage and the bias condition change. However, it is recommended to take this point into account if the MCU is used in tough humidity conditions.R S = 30 Ω-30-pFi 2HSE driving current V DD = 3.3 V, V IN =V SSwith 30 pF load--1mA g mOscillator transconductanceStartup 25--mA/V t SU(HSE)(4)4.t SU(HSE) is the startup time measured from the moment it is enabled (by software) to a stabilized 8 MHzoscillation is reached. This value is measured for a standard crystal resonator and it can vary significantly with the crystal manufacturerStartup timeV DD is stabilized-2-msDS5792 Rev 13Table 31. Asynchronous non-multiplexed SRAM/PSRAM/NOR read timings(1) Symbol Parameter Min Max Unit t w(NE)FSMC_NE low time5t HCLK – 1.55t HCLK + 2nst v(NOE_NE)FSMC_NEx low to FSMC_NOE low0.5 1.5nst w(NOE)FSMC_NOE low time5t HCLK – 1.55t HCLK + 1.5nst h(NE_NOE)FSMC_NOE high to FSMC_NE high hold time–1.5-nst v(A_NE)FSMC_NEx low to FSMC_A valid-0nst h(A_NOE)Address hold time after FSMC_NOE high0.1-nst v(BL_NE)FSMC_NEx low to FSMC_BL valid-0nst h(BL_NOE)FSMC_BL hold time after FSMC_NOE high0-nst su(Data_NE)Data to FSMC_NEx high setup time2t HCLK + 25-nst su(Data_NOE)Data to FSMC_NOEx high setup time2t HCLK + 25-nst h(Data_NOE)Data hold time after FSMC_NOE high0-nst h(Data_NE)Data hold time after FSMC_NEx high0-nst v(NADV_NE)FSMC_NEx low to FSMC_NADV low-5nst w(NADV)FSMC_NADV low time-t HCLK + 1.5ns 1.C L = 15 pF.1.Mode 2/B, C and D only. In Mode 1, FSMC_NADV is not used.DS5792 Rev 13Electrical characteristics STM32F103xC, STM32F103xD, STM32F103xETable 32. Asynchronous non-multiplexed SRAM/PSRAM/NOR write timings(1)(2)Symbol Parameter Min Max Unitt w(NE)FSMC_NE low time3t HCLK – 13t HCLK + 2nst v(NWE_NE)FSMC_NEx low to FSMC_NWE low t HCLK – 0.5t HCLK + 1.5nst w(NWE)FSMC_NWE low time t HCLK – 0.5t HCLK + 1.5nst h(NE_NWE)FSMC_NWE high to FSMC_NE high hold time t HCLK-nst v(A_NE)FSMC_NEx low to FSMC_A valid-7.5nst h(A_NWE)Address hold time after FSMC_NWE high t HCLK-nst v(BL_NE)FSMC_NEx low to FSMC_BL valid-0nst h(BL_NWE)FSMC_BL hold time after FSMC_NWE high t HCLK – 0.5-nst v(Data_NE)FSMC_NEx low to Data valid-t HCLK + 7nst h(Data_NWE)Data hold time after FSMC_NWE high t HCLK-nst v(NADV_NE)FSMC_NEx low to FSMC_NADV low- 5.5nst w(NADV)FSMC_NADV low time-t HCLK + 1.5ns1.C L = 15 pF.2.Guaranteed by characterization results.DS5792 Rev 13。

STM32F103VET6启航号硬件资源分析

STM32F103VET6启航号硬件资源分析启航号硬件资源分析本手册将对以下资源简要分析1.电源接口电路分析2.LED用户按键电路分析3.串行FLASH w25q16分析4.24Lc02 EEPROM 电路分析5.利用PL2303进行USB转RS232电路分析6.SP3485芯片485接口分析7.A T45DB151D SPI FLASH 分析(位于LCD模块上)*8.ADC调节电位器输入电路分析9.无线模块接口(24l01)接口分析10.摄像头模块接口分析11.CAN接口芯片SN65VHD230电路分析12.LCD彩色液晶屏幕接口分析13.板载7寸屏驱动电路分析14.板载vs1003b高性能MP3芯片电路分析15.以太网芯片ENC28J60电路分析B从机接口分析17.SD卡电路分析1.电源接口电路分析看到图了没有,这副图就是为我们整板提供电源的,当然7寸电源部分不在这里,两个USB口分别经过D9 D10 接到了VCC,而CN1是外部5V电源,也接到了VCC这样3处电源就汇聚到一起了然后经过SW1,SW1相当一开关,SW1出来的5V接到了ASM1117,这个芯片的作用是将5V电源转换成3.3V的,要求输入必须大于4.7V否则输出将可能低于3.3V,二极管D9 D10有0.2-0.7左右的管压降,这样输出就很有可能低于3.3V 那为什么要加上呢,原因在于:当同时插上外部5V电源和USB的时候,防止电流倒灌,损毁电脑的USB口,电容C11 C12 C13 C14,实际不是原理图上的容值,在板上实际用了一大一小电容分别电源到地,这样是为了得到更好的电源LD1 这个就是电源指示灯了2.LED用户按键电路分析这个就是用户可通过IO控制的led了,都是阴极接地的,我们可给IO一高电平使它发光这个R26 – R28 实际不是10K 在板子上用的471,这是根据R=U/I得到的,当然电阻能大不能小,否则可能损坏二极管这两个是按键,PC13按键松开时时高电平,按下时是低电平,这个可作外部中断,或按键扫描用,boot,这个按键相当关键,平时是低电平按下是高电平,这个可做启动方式选择使用,当上电时按住此键,stm32从系统方式启动(固化到芯片的代码)这是可从串口1现在程序这个是复位按键,stm32是低电平复位3.串行FLASH w25q16分析16M-bit/2M/byteSingle 2.7-3.6V supply这个就是W25Q16了,/cs是片选,使能芯片的,(大部分芯片在使能时的功率比不是能时的功率大)SPI-MISO是将数据串行传送到stm32的/WP 是写保护,我们用不着,所以直接拉高/HOLD这个就是终止数据传输的,当芯片在工作时,这个脚拉低后,DO保持高阻DI上的数据将无效CLK 当然就是提供时钟了,SPI传送都需要这个时钟,在时钟的上升沿或下降沿将数据锁存4.24Lc02 EEPROM 电路分析A0 – A2 芯片上说24lc 01B/02b 不用这个脚所以就接到了WP如果接地可正常读写,如果接正不能写SCL数据同步时钟SDA用来传送数据和地址的,是开漏输出所以要接上拉电阻,10K for 100KHz 1k for 400KHzSDA和SCL 接到了PB6 PB7上面这正是stm32上的IIC外设5.利用PL2303进行USB转RS232电路分析PL2303 工作需要Y5 12M的晶振USB口的D+ D- 两数据线到PL2303的数据线,串22欧的电阻是为了解决信号反射问题R58 1.5k的电阻是必须的,这样USB主机才能检测到设备的插入,并区分高速、全速设备与低速设备(在USB主机端有一下拉电阻)6.SP3485芯片485接口分析n RS-485 and RS-422 Transceiversn Operates from a single +3.3V supply n Interoperable with +5.0V logicn Driver/Receiver Enablen Low Power Shutdown Mode (SP3481) n -7V to +12V Common-Mode InputV oltage Rangen Allows up to 32 transceivers onthe serial busn Compatibility with the industry standard 75176 pinoutn Driver Output Short-Circuit Protection这个是内部结构可以看出来,RO是结收输出到PA9的DI是从PA10驱动输入的,AB 是输入输出,但A信号是B信号的反相/Re DE 分别是读写使能,所以接到同一管脚了R S 485_DIR 接到了PA47.ADC调节电位器输入电路分析额,这个就是调节VR1的电阻值,然后把电压值输入到PC5 经过iAD准换成数字值8.无线模块接口(24l01)接口分析WR I_C E 接到PA3WR I_SCK 接到PA5WR I_MISO 接到PA6WR I_MOS I 接到PA7WR I_IRQ 作为中端接到PE6WR I_C SN 接到pe59.摄像头模块接口分析此接口应该分为两部分、设置摄像头寄存器部分OV_SCL 做为摄像头的时钟控制线OV_SDA最为摄像头的数据线、读取fifo中摄像头的数据FIFO_CS 摄像头模块上的片选信号RRST 读复位信号WRST 写复位信号FIFO_RD 读使能FIFO_WE 写使能VSYNC 作为数据可读信号线XCLK 给摄像头提供时钟线10.LCD彩色液晶屏幕接口分析引脚说明FSMC-D0 –D15:这是LCD的16位数据端口,连至stm32的FSMC数据端口LCD_CS : LCD芯片使能引脚,低电平有效LCD_RS : LCD命令or数据选择端口,高电平数据有效,低电平命令有效LCD_WR :LCD写使能端口,连接到stm32的fsmc写使能端口,低电平有效LCD_RD : LCD读使能端口,低电平有效RESET: LCD复位管脚,低电平有效,为了节约管脚,直接和复位按键相连SPI-MISO SPI-MOSI SPI-SCK F-CS 是lcd上的flash操作线这是PB端口的SPI,(因SPI复用了,所以片选由软件控制)TP_CS 是触屏片选端口TP_IRQ 是触屏的中断端口触屏的SPI 和SD 和偏上FLSAH是复用的,(LCD模块上的)*注意: 3.2寸2.8寸等大部分LCD的控制芯片已固化到了屏幕下面我们是看不到的LCD在操作时(写数据和读数据时)必须注意RS这个引脚(有些手册是D/C)这是控制操作的数据还是指令,我们选用了FSMC nor 的bank1来作为lcd驱动Lcd的RS(数据or命令选择)是通过FSMC的地址确定是高低啊电平如,(这里地址不是真实地址,第一位作为RS端)向地址0x60000000 写0x80, 这是写的命令向地址0x60000001 写0x80 ,则是写的数据11.板载7寸屏驱动电路分析板载7寸屏的驱动,其实和上面说的的LCD接口一样,区别在用上面谈到的接口,其控制芯片已集成到了屏幕里面,而这里的7寸屏没有集成lcd的控制芯片,所以我们把7寸屏的控制芯片画到了板上,其原理与上面说到的一模一样,额图片有点看不清,请大家参照启航原理图吧,这是关于SSD1963的电路下面是供电部分的电路这是-7V的10.4V电路,9.9V 电路这里前端的电容相信大家都明白,是滤波储能的,后端的电容一部分是储能的,还有一部分是作为升压芯片的负载电容,没有这个电容电压是升不起来的,电感叫储能电感的电路完全参照芯片手册,放心使用*注意:在测试7寸屏的时候,务必插上JP3跳线帽12.板载vs1003b高性能MP3芯片电路分析Vs1003●能解码MPEG 1 和MPEG2 音频层III(CBR+VBR+ABR);WMA 4.0/4.1/7/8/9 5-384kbps 所有流文件;WA V(PCM+IMA AD-PCM);产生MIDI/SP-MIDI 文件。

野火stm32主芯片STM32F103VET6资源分配

野火stm32主芯片STM32F103VET6资源分配//2011 fire于广州M3芯片简介/*--------------------------------------------------------------------------------*/STM32 = 基于ARM的32位微控制器F = 通用类型103 = 增强型R = 64脚V = 100脚Z = 144脚C = 256K字节的闪存存储器D = 384K字节的闪存存储器E = 512K字节的闪存存储器H = BGAT = LQFPY = WLCSP64/*--------------------------------------------------------------------------------*/- Low-density devices are STM32F101xx and STM32F103xx microcontrollers wherethe Flash memory density ranges between 16 and 32 Kbytes.- Medium-density devices are STM32F101xx and STM32F103xx microcontrollers wherethe Flash memory density ranges between 32 and 128 Kbytes.- High-density devices are STM32F101xx and STM32F103xx microcontrollers wherethe Flash memory density ranges between 256 and 512Kbytes.STM32F103VET6片上资源/*--------------------------------------------------------------------------------*/CPU : 32-bitSRAM : 64kBFlash : 512KBFSMC : 1 Flexible Static Memory Controller for SRAM, PSRAM, NOR and NAND Flash,PLL : 1 PLL,RCC : Embedded Internal RC 8MHz and 32kHz,RTC : 1 Real-Time Clock,NVIC : 1 Nested Interrupt Controller, Power Saving Modes, JTAG and SWD,TIM : 4 Synch. 16-bit Timers with Input Capture, Output Compare and PWM,TIM : 2 16-bit Advanced Timer, 2 16-bit Basic Timer, 2 16-bit Watchdog Timers,2 个16位带死区控制和 2 个16位基本定时器独立型和窗口型紧急刹车,用于电机控用于驱动DAC制的PWM高级控制定时器SysTick : 1 SysTick Timer, 系统时间定时器,24位自减型计数器SPI/I2S : 3 SPI/I2S, 有两个可复用为 I2S: SPI1 PIN DESRIPTION* PA4 - SPI1_NSS* PA5 - SPI1_SCK* PA6 - SPI1_MISO* PA7 - SPI1_MOSISPI2 PIN DESCRIPTION* PB12 - SPI2_NSS* PB13 - SPI2_SCK* PB14 - SPI2_MISO* PB15 - SPI2_MOSII2C : 2 I2C,I2C1:PB6-I2C1_SCL、PB7-I2C1_SDAI2C2:PB10-I2C2_SCL、PB11-12C2_SDAUSART : 5 USART,PA9 - USART1(Tx) - USART1可用于程序下载PA10 - USART1(Rx)USB : 1 USB 2.0 Full Speed Interface,CAN : 1 CAN 2.0B Active,PB8 - CAN_RXPB9 - CAN_TXA/D : 3 12-bit 16-ch A/D Converter,D/A : 2 12-bit D/A Converter,SDIO : 1 SDIO,GPIO :Fast I/O PortsDMA : 12 通道 DMA 控制器支持的外设:定时器、ADC、DAC、SDIO、I2S、SPI、I2C 和 USART/*-------------------------------------------------------------------------------*/STM32F103VET6引脚功能/*-----------------------------------------------------------------------------------------------------*/脚位管脚名称类型 I/O电平主功能默认复用功能重定义功能1 PE2 I/O FT PE2 TRACECK/FSMC_A232 PE3 I/O FT PE3 TRACED0/FSMC_A193 PE4 I/O FT PE4 TRACED1/FSMC_A204 PE5 I/O FT PE5 TRACED2/FSMC_A215 PE6 I/O FT PE6 TRACED3/FSMC_A226 VBAT S - VBAT7 PC13-TAMPER-RTC (4) I/O - PC13 (5) TAMPER-RTC8 PC14-OSC32_IN (4) I/O - PC14 (5) OSC32_IN9 PC15-OSC32_OUT (4) I/O - PC15 (5) OSC32_OUT10 VSS_5 S - VSS_511 VDD_5 S - VDD_512 OSC_IN I - OSC_IN13 OSC_OUT O - OSC_OUT14 NRST I/O - NRST15 PC0 I/O - PC0 ADC123_IN1016 PC1 I/O - PC1 ADC123_IN1117 PC2 I/O - PC2 ADC123_IN1218 PC3 I/O - PC3 ADC123_IN1319 VSSA S - VSSA20 VREF- S - VREF-21 VREF+ S - VREF+22 VDDA S - VDDA23 PA0-WKUP I/O - PA0 WKUP/USART2_CTS (7)ADC123_IN0TIM2_CH1_ETRTIM5_CH1/TIM8_ETR24 PA1 I/O - PA1 USART2_RTS (7)ADC123_IN1/TIM5_CH2/TIM2_CH2 (7)25 PA2 I/O - PA2 USART2_TX (7) /TIM5_CH3/ADC123_IN2/TIM2_CH3 (7)26 PA3 I/O - PA3 USART2_RX (7) /TIM5_CH4ADC123_IN3/TIM2_CH4 (7)27 VSS_4 S - VSS_428 VDD_4 S - VDD_429 PA4 I/O - PA4 SPI1_NSS (7) /USART2_CK (7)DAC_OUT1/ADC12_IN430 PA5I/O - PA5 SPI1_SCK (7)DAC_OUT2/ADC12_IN531 PA6 I/O - PA6 SPI1_MISO (7) /TIM8_BKIN TIM1_BKIN ADC12_IN6/TIM3_CH1 (7)32 PA7 I/O - PA7 SPI1_MOSI (7) /TIM8_CH1N TIM1_CH1N ADC12_IN7/TIM3_CH2 (7)33 PC4 I/O - PC4 ADC12_IN1434 PC5 I/O - PC5 ADC12_IN1535 PB0 I/O - PB0 ADC12_IN8/TIM3_CH3 TIM1_CH2N TIM8_CH2N36 PB1 I/O - PB1 ADC12_IN9/TIM3_CH4 (7) TIM1_CH3N TIM8_CH3N37 PB2 I/O FT PB2/BOOT138 PE7 I/O FT PE7 FSMC_D4 TIM1_ETR39 PE8 I/O FT PE8 FSMC_D5 TIM1_CH1N40 PE9 I/O FT PE9 FSMC_D6 TIM1_CH141 PE10 I/O FT PE10 FSMC_D7 TIM1_CH2N42 PE11 I/O FT PE11 FSMC_D8 TIM1_CH243 PE12 I/O FT PE12 FSMC_D9 TIM1_CH3N44 PE13 I/O FT PE13 FSMC_D10 TIM1_CH345 PE14 I/O FT PE14 FSMC_D11 TIM1_CH446 PE15 I/O FT PE15 FSMC_D12 TIM1_BKIN47 PB10 I/O FT PB10 I2C2_SCL/USART3_TX (7) TIM2_CH348 PB11 I/O FT PB11 I2C2_SDA/USART3_RX (7) TIM2_CH449 VSS_1 S - VSS_150 VDD_1 S - VDD_151 PB12 I/O FT PB12 SPI2_NSS/I2S2_WS/I2C2_SMBA/USART3_CK (7)TIM1_BKIN (7)52 PB13 I/O FT PB13 SPI2_SCK/I2S2_CKUSART3_CTS (7) /TIM1_CH1N53 PB14 I/O FT PB14 SPI2_MISO/TIM1_CH2N USART3_RTS (7)54 PB15 I/O FT PB15 SPI2_MOSI/I2S2_SDTIM1_CH3N (7)55 PD8 I/O FT PD8 FSMC_D13 USART3_TX56 PD9 I/O FT PD9 FSMC_D14 USART3_RX57 PD10 I/O FT PD10 FSMC_D15 USART3_CK58 PD11 I/O FT PD11 FSMC_A16 USART3_CTS59 PD12 I/O FT PD12 FSMC_A17 TIM4_CH1/ USART3_RTS60 PD13 I/O FT PD13 FSMC_A18 TIM4_CH261 PD14 I/O FT PD14 FSMC_D0 TIM4_CH362 PD15 I/O FT PD15 FSMC_D1 TIM4_CH463 PC6 I/O FT PC6 I2S2_MCK/TIM8_CH1 TIM3_CH1 SDIO_D664 PC7 I/O FT PC7 I2S3_MCK/TIM8_CH2 TIM3_CH2 SDIO_D765 PC8 I/O FT PC8 TIM8_CH3/SDIO_D0 TIM3_CH366 PC9 I/O FT PC9 TIM8_CH4/SDIO/D1 TIM3_CH467 PA8 I/O FT PA8 USART1_CKTIM1_CH1 (7) /MCO68 PA9 I/O FT PA9 USART1_TX (7)/TIM1_CH2 (7)69 PA10 I/O FT PA10 USART1_RX (7) /TIM1_CH3 (7)70 PA11 I/O FT PA11 USART1_CTS/USBDMCAN_RX (7) /TIM1_CH4 (7)71 PA12 I/O FT PA12 USART1_RTS/USBDP/CAN_TX (7) /TIM1_ETR (7)72 PA13 I/O FT JTMS/SWDIO PA1373 未连接74 VSS_2 S - VSS_275 VDD_2 S - V DD_276 PA14 I/O FT JTCK/SWCLK PA1477 PA15 I/O FT JTDI SPI3_NSS/I2S3_WS TIM2_CH1_ETR PA15/SPI1_NSS78 PC10 I/O FT PC10 USART4_TX/SDIO_D2 USART3_TX79 PC11 I/O FT PC11 USART4_RX/SDIO_D3 USART3_RX80 PC12I/O FT PC12 USART5_TX/SDIO_CK USART3_CK81 PD0 I/O FT OSC_IN (8) FSMC_D2 (9) CAN_RX82 PD1 I/O FT OSC_OUT (8) FSMC_D3 (9) CAN_TX83 PD2 I/O FT PD2 TIM3_ETR/USART5_RX/SDIO_CMD84 PD3 I/O FT PD3 FSMC_CLK USART2_CTS85 PD4 I/O FT PD4 FSMC_NOE USART2_RTS86 PD5 I/O FT PD5 FSMC_NWE USART2_TX87 PD6 I/O FT PD6 FSMC_NWAIT USART2_RX88 PD7 I/O FT PD7 FSMC_NE1/FSMC_NCE2 USART2_CK89 PB3 I/O FT JTDO SPI3_SCK / I2S3_CK PB3/TRACESWOTIM2_CH2/SPI1_SCK90 PB4 I/O FT NJTRST SPI3_MISO PB4/TIM3_CH1/SPI1_MISO91 PB5 I/O - PB5 I2C1_SMBA/ SPI3_MOSI TIM3_CH2/SPI1_MOSII2S3_SD92 PB6 I/O FT PB6 I2C1_SCL (7) /TIM4_CH1 (7) USART1_TX93 PB7 I/O FT PB7 I2C1_SDA (7) /FSMC_NADV USART1_RXTIM4_CH2 (7)94 BOOT0 I - BOOT095 PB8 I/O FT PB8 TIM4_CH3 (7) /SDIO_D4 I2C1_SCL/CAN_RX96 PB9 I/O FT PB9 TIM4_CH4 (7) /SDIO_D5 I2C1_SDA/CAN_TX97 PE0 I/O FT PE0 TIM4_ETR/FSMC_NBL098 PE1 I/O FT PE1 FSMC_NBL199 VSS_3 S - VSS_3100 VDD_3 S - VDD_3/*------------------------------------------------------------------------------------------------------------*/。

STM32内存分布探究

STM32内存分布探究2016-2-2本人在运行ucos时遇到一个非常奇怪的问题,运行一段时间后就会莫名进入hardfault 函数,导致系统死机。

后来根据对堆栈调试,发现每次调用的函数都不一样,甚是费解。

通过map文件最后得出结论,原来在系统初始化的时候在flash里面读出了系统配置参数,在系统运行过程中会写flash,而flash定义的地址与程序代码存储的位置发生了重叠,一写数据就擦掉了一些函数,当调用到这些函数的时候就会发生未知指令的错误。

把这个参数存储地址定义的分开些就会解决这个问题。

可是,开始这个地址写好了,随着程序代码不断增多,消耗的片上flash也会增大,是个动态增长的过程,不注意很有可能发生冲突。

所以在项目开发过程中定期检查定义的参数存储地址,或者干脆把参数存储地址定义在程序地址之前。

今天详细了解一下编译后的STM32工程,堆栈内存分布情况,有助于对堆栈大小分配的理解。

打开一个基于STM32f103RET6的工程,具有512KB内置flash,以及64KBSRAM,通过map文件可以看出:名称位置地址备注RESET复位向量Flash0x08000000上电执行的第一条代码库函数代码段Flash0x08000144在程序中调用的库函数,例如字符串处理函数、内存分配函数等用户自定义函数代码段Flash0x08001110工程模板函数库、用户自定义函数编译后的代码,以函数名首字母排序.constdata Flash0x0800d07c-0x0800d680用户定义的常量剩余空间Flash名称位置地址备注.data SRAM0x20000000数据段,以及初始化的全局变量.bss SRAM0x20000268未初始化的全局变量HEAP(堆)SRAM0x200033e8启动文件定义的堆空间开始,程序调用malloc 自由分配的内存在堆上STACK (栈)SRAM0x200073e8启动文件定义的栈空间开始,各个函数中的局部变量空间分配到栈上剩余空间SRAM例如在这个工程中,flash自定义参数存储地址,不要定义在0x0800d680之前。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

A/D : 3 12-bit 16-ch A/D Converter,

D/A : 2 12-bit D/A Converter,

SDIO : 1 SDIO,

GPIO :Fast I/O Ports

DMA : 12 通道 DMA 控制器

ADC123_IN2/TIM2_CH3 (7)

Y = WLCSP64

/*--------------------------------------------------------------------------------*/

- Low-density devices are STM32F101xx and STM32F103xx microcontrollers where

12 OSC_IN I - OSC_IN

13 OSC_OUT O - OSC_OUT

14 NRST I/O - NRST

15 PC0 I/O - PC0 ADC123_IN10

/*--------------------------------------------------------------------------------*/

CPU : 32-bit

SRAM : 64kB

Flash : 512KB

FSMC : 1 Flexible Static Memory Controller for SRAM, PSRAM, NOR and NAND Flash,

D = 384K字节的闪存存储器

E = 512K字节的闪存存储器

H = BGA

T = LQFP

R = 64脚

V = 100脚

Z = 144脚

C = 256K字节的闪存存储器

STM32F103VET6引脚功能

/*-----------------------------------------------------------------------------------------------------*/

脚位 管脚名称 类型 I/O电平 主功能 默认复用功能 重定义功能

SPI2 PIN DESCRIPTION

* PB12 - SPI2_NSS

* PB13 - SPI2_SCK

* PB14 - SPI2_MISO

* PB15 - SPI2_MOSI

I2C : 2 I2C,

- High-density devices are STM32F101xx and STM32F103xx microcontrollers where

the Flash memory density ranges between 256 and 512 Kbytes.

STM32F103VET6片上资源

PLL : 1 PLL,

RCC : Embedded Internal RC 8MHz and 32kHz,

RTC : 1 Real-Time Clock,

NVIC : 1 Nested Interrupt Controller, Power Saving Modes, JTAG and SWD,

16 PC1 I/O - PC1 ADC123_IN11

17 PC2 I/O - PC2 ADC123_IN12

18 PC3 I/O - PC3 ADC123_IN13

//2011 fire于广州

M3芯片简介

/*--------------------------------------------------------------------------------*/

STM32 = 基于ARM的32位微控制器

F = 通用类型

103 = 增强型

PA10 - USART1(Rx)

USB : 1 USB 2.0 Full Speed Interface,

CAN : 1 CAN 2.0B Active,

PB8 - CAN_RX

PB9 - CAN_TX

23 PA0-WKUP I/O - PA0 WKUP/USART2_CTS (7)

ADC123_IN0

19 VSSA S - VSSA

20 VREF- S - VREF-

21 VREF+ S - VREF+

22 VDDA S - VDDA

支持的外设:定时器、ADC、DAC、SDIO、

I2S、SPI、I2C 和 USART

/*-------------------------------------------------------------------------------*/

the Flash memory density ranges between 16 and 32 Kbytes.

- Medium-density devices are STM32F101xx and STM32F103xx microcontrollers where

the Flash memory density ranges between 32 and 128 Kbytes.

TIM2_CH1_ETR

TIM5_CH1/TIM8_ETR

24 PA1 I/O - PA1 USART2_RTS (7)

2 个16位带死区控制和 2 个16位基本定时器 独立型和窗口型

紧急刹车,用于电机控 用于驱动DAC

制的PWM高级控制定时器

SysTick : 1 SysTick Timer, 系统时间定时器,24位自减型计数器

1 PE2 I/O FT PE2 CECK/FSMC_A23

2 PE3 I/O FT PE3 TRACED0/FSMC_A19

6 VBAT S - VBAT

7 PC13-

TAMPER-RTC (4) I/O - PC13 (5) TAMPER-RTC

8 PC14-

OSC32_IN (4) I/O - PC14 (5) OSC32_IN

9 PC15-

OSC32_OUT (4) I/O - PC15 (5) OSC32_OUT

10 VSS_5 S - VSS_5

11 VDD_5 S - VDD_5

SPI/I2S : 3 SPI/I2S, 有两个可复用为 I2S

: SPI1 PIN DESRIPTION

* PA4 - SPI1_NSS

* PA5 - SPI1_SCK

* PA6 - SPI1_MISO

* PA7 - SPI1_MOSI

3 PE4 I/O FT PE4 TRACED1/FSMC_A20

4 PE5 I/O FT PE5 TRACED2/FSMC_A21

5 PE6 I/O FT PE6 TRACED3/FSMC_A22

TIM : 4 Synch. 16-bit Timers with Input Capture, Output Compare and PWM,

TIM : 2 16-bit Advanced Timer, 2 16-bit Basic Timer, 2 16-bit Watchdog Timers,

ADC123_IN1/

TIM5_CH2/TIM2_CH2 (7)

25 PA2 I/O - PA2 USART2_TX (7) /TIM5_CH3/

I2C1:PB6-I2C1_SCL、PB7-I2C1_SDA

I2C2:PB10-I2C2_SCL、PB11-12C2_SDA

USART : 5 USART,

PA9 - USART1(Tx) - USART1可用于程序下载