高频-锁相环调频发射与接收

用于高频接收器和发射器的锁相环

“ VCO会发生漂移,直到造成显著的相位误差并再次开始生成 正电流脉冲或负电流脉冲。这种循环会持续相当长的一段时 间,其影响是电荷泵的输出会被某个信号(PFD输入参考频率 的次谐波)调制。由于这可能是一种低频信号,因此无法通过 环路滤波器进行衰减,从而会导致VCO输出频谱中出现非常 明显的杂散,该现象称为“间隙”效应。通过在U3的输出端和 U1及U2的CLR输入端之间添加延迟元件,可以确保不会发生 这种情况。添加延迟元件后,即使+IN和–IN相位完全对齐 时,电荷泵输出端仍会生成电流脉冲。该延迟的持续时间等 于在U3输出处插入的延迟,称为反冲防回差脉冲宽度。

图6. 双模预分频器。 1. 如果两个计数器未超时,其输出信号都为高电平。 2. 当B计数器超时时,其输出变为低电平,并立即将两个计

为处理此范围,需要考虑在可编程计数器之前加上一个固定 计数器元件,以便将超高输入频率拉低至标准CMOS的工作 频率范围内。该计数器称为预分频器,如图5所示。

然而,使用标准的预分频器会导致其他并发症。现在,系统 分辨率降低(F1 × P)。可通过使用双模预分频器来解决这个问 题(图6)。这种方法可以享有标准预分频器种种优势,又不会

这种结构已经发展成为下列情况下固有问题的一种解决方 案:需要超高频输出时使用基本N分频结构来反馈至鉴相 器。例如,我们假设需要一个间距为10 Hz的900 MHz输出。 可以使用10 MHz参考频率并将R分频器设为1000。然后,反馈 中的N值必须为90,000。这意味着,至少需要一个能够处理 900 MHz输入频率的17位计数器。

高频接收机和发射机中的锁相环-第2部分

⎜⎟ ⎝ fm ⎠

⎥ ⎦⎥

(1)

where: LPM is single-sideband phase noise density (dBc/Hz) F is the device noise factor at operating power level A (linear) k is Boltzmann’s constant, 1.38 × 10–23 J/K T is temperature (K)

4. Choose an active device that has minimal noise figure as well as low flicker frequency. The flicker noise can be reduced by the use of feedback elements.

Noise in Oscillator Systems In any oscillator design, frequency stability is of critical importance. We are interested in both long-term and short-term stability. Longterm frequency stability is concerned with how the output signal varies over a long period of time (hours, days or months). It is usually specified as the ratio, ∆f/f for a given period of time, expressed as a percentage or in dB.

锁相环在频率调制与解

1 引言锁相环(pll)是一种能跟踪输入信号相位的闭环自动控制系统。

它在无线电技术的各个领域都得到了广泛的应用。

集成环路部件以其低成本、性能优良、使用简便而得到了青睐。

它在频率调制与解调、频率合成、电视机彩色副波提取、fm立体声解码、遥控系统、频率的编码和译码等诸多方面均得到了利用。

本文介绍了集成锁相环cd4046在频率的调制与解调方面的应用。

2 集成锁相环cd4046介绍2.1 cd4046结构及性能特点它的内部结构框图如图1所示。

它是低功耗cmos型、多功能数字环。

主要参数如下:(1)工作电压3v-18v;(2)静态工作电流(15端开路)10ua;(3)最高工作频率为1.2mhz;(4)稳压管稳定电压4.45v-6.15v。

它含有两个相位比较器p c?与pcii。

pc?要求输入信号为方波,pcii则无此要求,有一个压控(频率)振荡器vco。

在两个相位比较器的输入端有一个前置放大器,可把100mv的微弱信号变为满电平的方波脉冲。

a2是低滤波器输出缓冲放大器。

cd4046采用16线双列直插式封装,各管脚功能如附表所示:图1 cd4046内部结构框图2.2 cd4046构成频率调制与解调电路的工作原理当从9脚输入音频信号时,从4端可输出受输入信号调制的调频信号。

电路如图2所示,由于调频时要求vco有一定的频率范围(频偏),所以不用r2收缩频带,即r2为无穷大(12脚空置)仅用r 1和c1确定vco的中心频率f0即可。

设计参数时,只需由f0查图4(电源电压vdd为9v时的曲线,横坐标为c1取值)求出c1与r1即可。

图2 cd4046构成的频率调制电路当从14脚输入一被音频信号调制的(中心频率与cd4046的vco的中心频率相同)调频信号,则相位比较器输出端将输出一个与音频信号具有相同变化频率的包络信号,经低通滤波器滤去载波后,即剩下调频信号解调后的音频信号了。

一般使用pci,这时仅由r1和c1确定vco的中心频率f0,而不用r2来收缩频率范围(其为无穷大)。

(完整版)锁相环工作原理

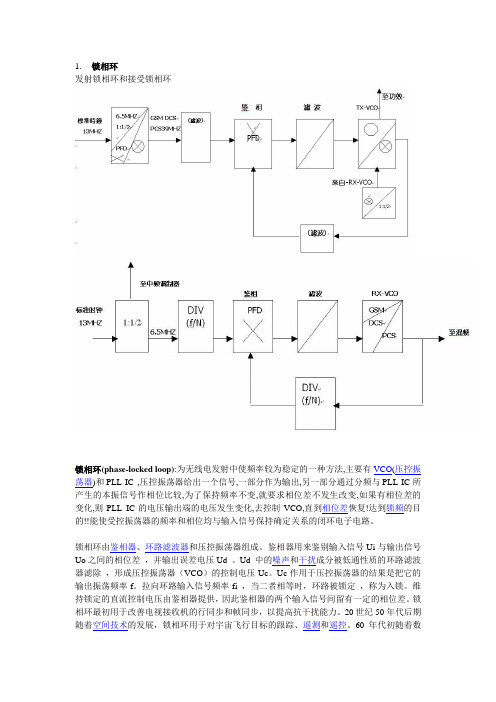

基本组成和锁相环电路1、频率合成器电路频率合成器组成:频率合成器电路为本机收发电路的频率源,产生接收第一本机信号源和发射电路的发射信号源,发射信号源主要由锁相环和VCO电路直接产生。

如图3-4所示。

在现在的移动通信终端中,用于射频前端上下变频的本振源(LO),在射频电路中起着非常重要的作用。

本振源通常是由锁相环电路(Phase-Locked Loop)来实现。

2.锁相环:它广泛应用于广播通信、频率合成、自动控制及时钟同步等技术领域3.锁相环基本原理:锁相环包含三个主要的部分:⑴鉴相器(或相位比较器,记为PD或PC):是完成相位比较的单元,用来比较输入信号和基准信号的之间的相位.它的输出电压正比于两个输入信号之相位差.⑵低通滤波器(LPF):是个线性电路,其作用是滤除鉴相器输出电压中的高频分量,起平滑滤波的作用.通常由电阻、电容或电感等组成,有时也包含运算放大器。

⑶压控振荡器(VCO):振荡频率受控制电压控制的振荡器,而振荡频率与控制电压之间成线性关系。

在PLL中,压控振荡器实际上是把控制电压转换为相位。

1、压控振荡器的输出经过采集并分频;2、和基准信号同时输入鉴相器;3、鉴相器通过比较上述两个信号的频率差,然后输出一个直流脉冲电压;4、控制VCO,使它的频率改变;5、这样经过一个很短的时间,VCO 的输出就会稳定于某一期望值。

锁相环电路是一种相位负反馈系统。

一个完整的锁相环电路是由晶振、鉴相器、R分频器、N分频器、压控振荡器(VCO)、低通滤波器(LFP)构成,并留有数据控制接口。

锁相环电路的工作原理是:在控制接口对R分频器和N分频器完成参数配置后。

晶振产生的参考频率(Fref)经R分频后输入到鉴相器,同时VCO的输出频率(Fout)也经N分频后输入到鉴相器,鉴相器对这两个信号进行相位比较,将比较的相位差以电压或电流的方式输出,并通过LFP滤波,加到VCO的调制端,从而控制VCO的输出频率,使鉴相器两输入端的输入频率相等。

(高频电子线路)第七章锁相环

测试原理及步骤说明

3. 调整信号发生器的频率和幅度,观察锁相环电 路的输出变化。

4. 使用频率计测量输入信号和输出信号的频率, 记录数据。

5. 使用电压表测量输入信号、输出信号以及误差 信号的电压幅度,记录数据。

数据处理与结果分析

数据处理:根据实验记录的数据,计算 输入信号和输出信号的频率差、相位差 以及误差信号的电压幅度等指标。

VS

组成结构

锁相环主要由鉴相器(PD)、环路滤波器 (LF)和压控振荡器(VCO)三个基本部 分组成。其中,鉴相器用于检测输入信号 与本地振荡器输出信号的相位差;环路滤 波器用于滤除误差信号中的高频噪声,保 证环路稳定性;压控振荡器则根据误差信 号调整本地振荡器的频率和相位。

性能指标及分类方法

性能指标

滤波特性

滤除鉴相器输出电压中的高频成分,保证环路稳定性。

电路设计要点

根据锁相环的带宽和稳定性要求,选择合适的滤波器类型和参数, 优化滤波器的幅频特性和相频特性。

压控振荡器设计

振荡器类型

LC振荡器、晶体振荡器等。

振荡特性

描述振荡器输出频率与输入控制电压之间的关系。

电路设计要点

选择合适的振荡器类型,确定振荡器的频率范围和稳定性要求,优化 振荡器的线性范围和灵敏度,以及减小相位噪声和杂散。

集成化趋势

集成化是锁相环发展的另一个重要趋 势。通过高度集成化设计,可以减小 锁相环的体积和重量,降低成本,提 高可靠性和稳定性。

面临的技术挑战和解决方案

技术挑战

锁相环在发展过程中面临着一些技术挑战,如相位噪声、杂散抑制、快速锁定 等。这些挑战限制了锁相环的性能和应用范围。

锁相环调频及锁相环调频发射与接收实验实验报告

锁相环调频及锁相环调频发射与接收实验实验报告沈凯捷101180101锁相环调频实验一. 实验目的1.加深对锁相环基本工作原理的理解。

2.掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3.掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

1.理解用锁相环实现调频的基本原理。

2.掌握NE564构成调频电路的原理和调试,测试方法。

二、实验使用仪器1.NE564锁相和调频实验板2.100MHz泰克双踪示波器3. FLUKE万用表4. 高频信号源5. 低频信号源三、实验内容1. 压控振荡器的测试。

2 . 同步带和捕捉带的测量。

3. 调频信号的产生和测量。

四、实验步骤1. 压控振荡器的测试(1)在实验箱主板上插上锁相环调频与测试电路实验模块。

接通实验箱上电源开关,电源指标灯点亮。

(2)把跳线S1,S2,S5,S6,S7断开,S3,S4合上。

单独测试压控振荡器的自由振荡频率。

将双排开关S8的4端合上,此时8200pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值,观察振荡频率是否有变化,并思考原因。

然后调节可变电容CW ,观察振荡频率的变化范围,并记录。

将双排开关S8的3端合上,此时820pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值,观察振荡频率是否有变化,并思考原因。

然后调节可变电容CW ,观察振荡频率的变化范围,并记录。

将双排开关S8的2端合上,此时82pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

调节滑动变阻器W1的值,观察振荡频率是否有变化,并思考原因。

然后调节可变电容CW ,观察振荡频率的变化范围,并记录。

将双排开关S8的1端合上,此时22pF 的固定电容接入12,13脚之间,用示波器观察TP2处的波形(压控振荡器的输出端),并测量此时的振荡频率。

用于高频接收器和发射器的锁相环-第二部分

用于高频接收器和发射器的锁相环-第二部分 本系列文章的第一部分介绍了关于锁相环(PLL)的基本概念,说明了PLL架构和工作原理,同时以一个例子说明了PLL在通信系统中的用途。

在第二部分中,我们将侧重于详细考察与PLL相关的两个关键技术规格:相位噪声和参考杂散。

导致相位噪声和参考杂散的原因是什么,如何将其影响降至最低?讨论将涉及测量技术以及这些误差对系统性能的影响。

我们还将考虑输出漏电流,举例说明其在开环调制方案中的重要意义。

振荡器系统中的噪声 在任何振荡器设计中,频率稳定性都至关重要。

我们需要考虑长期和短期稳定性。

长期频率稳定性是关于输出信号在较长时间(几小时、几天或几个月)内的变化情况。

其通常以一定时间内的比率Δf/f来规定,单位为百分比或dB。

短期稳定性则是关于几秒或更短时间内的变化情况。

这些变化可能是随机的,也可能是周期性的。

可以使用频谱分析仪来检查信号的短期稳定性。

信号源中的已知时钟频率、电力线干扰和混频器产品都可能引起离散杂散成分。

随机噪声波动引起的扩张是相位噪声造成的。

其可能是有源和无源器件中的热噪声、散粒噪声和/或闪烁噪声造成的。

电压控制振荡器中的相位噪声 在考察PLL系统中的相位噪声之前,我们先看看电压控制振荡器(VCO)中的相位噪声。

理想的VCO应该没有相位噪声。

在频谱分析仪上看到的输出应是一条谱线。

当然,事实并非如此。

输出上会有抖动,频谱分析仪会显示出相位噪声。

为了便于理解相位噪声,请考虑一种相量表示方式,如 在许多无线电系统中,必须符合总积分相位误差规格的要求。

该总相位误差由PLL相位误差、调制器相位误差和基带元件导致的相位误差构成。

例如,在GSM中,。

锁相环工作原理

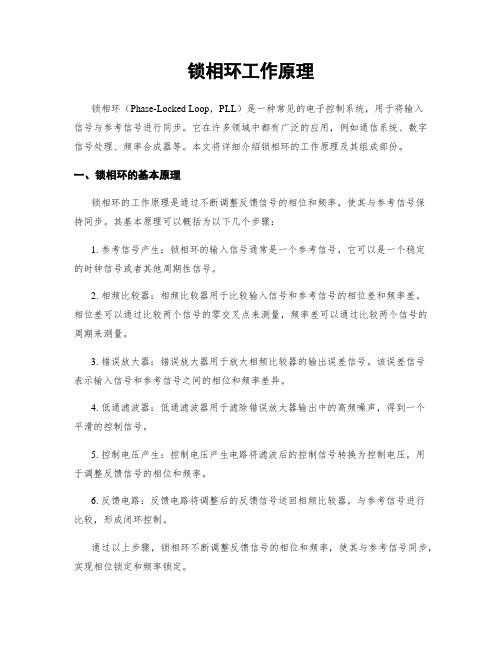

锁相环工作原理锁相环(Phase-Locked Loop,PLL)是一种常见的电子控制系统,用于将输入信号与参考信号进行同步。

它在许多领域中都有广泛的应用,例如通信系统、数字信号处理、频率合成器等。

本文将详细介绍锁相环的工作原理及其组成部份。

一、锁相环的基本原理锁相环的工作原理是通过不断调整反馈信号的相位和频率,使其与参考信号保持同步。

其基本原理可以概括为以下几个步骤:1. 参考信号产生:锁相环的输入信号通常是一个参考信号,它可以是一个稳定的时钟信号或者其他周期性信号。

2. 相频比较器:相频比较器用于比较输入信号和参考信号的相位差和频率差。

相位差可以通过比较两个信号的零交叉点来测量,频率差可以通过比较两个信号的周期来测量。

3. 错误放大器:错误放大器用于放大相频比较器的输出误差信号。

该误差信号表示输入信号和参考信号之间的相位和频率差异。

4. 低通滤波器:低通滤波器用于滤除错误放大器输出中的高频噪声,得到一个平滑的控制信号。

5. 控制电压产生:控制电压产生电路将滤波后的控制信号转换为控制电压,用于调整反馈信号的相位和频率。

6. 反馈电路:反馈电路将调整后的反馈信号送回相频比较器,与参考信号进行比较,形成闭环控制。

通过以上步骤,锁相环不断调整反馈信号的相位和频率,使其与参考信号同步,实现相位锁定和频率锁定。

二、锁相环的组成部份锁相环通常由以下几个主要组成部份构成:1. 相频比较器:相频比较器用于比较输入信号和参考信号的相位差和频率差。

常见的相频比较器有边沿比较器、乘法器、数字式比较器等。

2. 错误放大器:错误放大器是一个放大器,用于放大相频比较器的输出误差信号。

常见的错误放大器有运算放大器、差分放大器等。

3. 低通滤波器:低通滤波器用于滤除错误放大器输出中的高频噪声,得到一个平滑的控制信号。

常见的低通滤波器有RC滤波器、积分器等。

4. 控制电压产生电路:控制电压产生电路将滤波后的控制信号转换为控制电压,用于调整反馈信号的相位和频率。

调频发射与接收系统设计

调频发射与接收系统设计调频(Frequency Modulation,简称FM)是一种在无线通信领域广泛应用的调制方式。

调频发射与接收系统的设计涉及多个方面,包括调频信号产生、调频信号发射、调频信号接收和解调等。

本文将详细介绍调频发射与接收系统的设计。

一、调频信号产生调频信号产生是调频发射与接收系统的第一步。

调频信号可以通过多种方式产生,最常见的方式是使用压控振荡器(Voltage-Controlled Oscillator,简称VCO)和相位锁定环(Phase-Locked Loop,简称PLL)。

VCO是一种根据输入电压变化产生相应频率输出的电路,而PLL则是通过反馈控制,使得VCO输出的频率与输入的基准信号保持同步。

二、调频信号发射调频信号发射是将调频信号送入天线,以无线电波的形式传输到接收端。

调频信号发射需要经过信号放大、功率放大和频率变换等处理。

信号放大是指将调频信号经过放大器放大到一定的幅度,以便后续的处理。

功率放大是指将调频信号的功率经过一定的放大倍数放大,以保证信号能够在传输过程中保持较高的信噪比。

频率变换是指将调频信号的频率转换为合适的无线电波频率。

一般来说,调频信号的频率较低,需要经过混频器和本振电路的处理,将其转换为无线电波的频率。

三、调频信号接收调频信号接收是将接收到的无线电波转换为原始的调频信号。

调频信号接收需要经过频率变换、信号放大和解调等处理。

频率变换是指将接收到的无线电波的频率转变为与原始调频信号相同的频率。

信号放大是为了提高接收到的信号的信噪比,以便后续的解调处理。

解调是指将调频信号中的信息信号还原出来。

常见的调频信号接收解调方法有相干解调和非相干解调。

相干解调是指将接收到的调频信号与本地的参考信号进行相乘或相减,以还原原始的信息信号。

相干解调的优点是还原的信息信号质量好,缺点是要求接收到的调频信号与本地参考信号有严格的相位和频率同步。

非相干解调是指不使用参考信号,直接对接收到的调频信号进行处理,以还原原始的信息信号。

锁相环工作原理

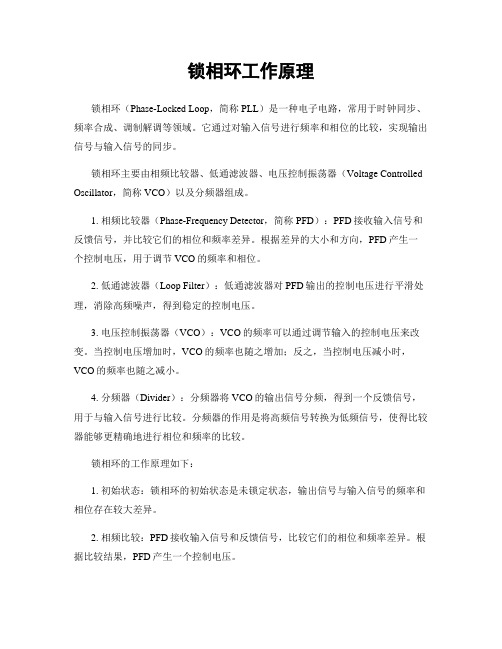

锁相环工作原理锁相环(Phase-Locked Loop,简称PLL)是一种电子电路,常用于时钟同步、频率合成、调制解调等领域。

它通过对输入信号进行频率和相位的比较,实现输出信号与输入信号的同步。

锁相环主要由相频比较器、低通滤波器、电压控制振荡器(Voltage Controlled Oscillator,简称VCO)以及分频器组成。

1. 相频比较器(Phase-Frequency Detector,简称PFD):PFD接收输入信号和反馈信号,并比较它们的相位和频率差异。

根据差异的大小和方向,PFD产生一个控制电压,用于调节VCO的频率和相位。

2. 低通滤波器(Loop Filter):低通滤波器对PFD输出的控制电压进行平滑处理,消除高频噪声,得到稳定的控制电压。

3. 电压控制振荡器(VCO):VCO的频率可以通过调节输入的控制电压来改变。

当控制电压增加时,VCO的频率也随之增加;反之,当控制电压减小时,VCO的频率也随之减小。

4. 分频器(Divider):分频器将VCO的输出信号分频,得到一个反馈信号,用于与输入信号进行比较。

分频器的作用是将高频信号转换为低频信号,使得比较器能够更精确地进行相位和频率的比较。

锁相环的工作原理如下:1. 初始状态:锁相环的初始状态是未锁定状态,输出信号与输入信号的频率和相位存在较大差异。

2. 相频比较:PFD接收输入信号和反馈信号,比较它们的相位和频率差异。

根据比较结果,PFD产生一个控制电压。

3. 控制电压调节:低通滤波器对PFD输出的控制电压进行平滑处理,并将其传递给VCO。

VCO的频率根据控制电压的大小和方向进行调节。

4. 反馈:VCO输出的信号经过分频器分频后,得到一个反馈信号,用于与输入信号进行比较。

如果输入信号的频率和相位与反馈信号相差较大,PFD将产生一个较大的控制电压,继续调节VCO的频率和相位。

5. 锁定状态:随着反复的比较和调节,锁相环逐渐将输出信号的频率和相位与输入信号同步。

用于高频接收器和发射器的锁相环-第三部分

用于高频接收器和发射器的锁相环-第三部分用于高频接收器和发射器的锁相环-第三部分作者:Mark Curtin和Paul O’Brien本系列第一部分介绍了锁相环(PLL),说明了其基本架构和工作原理。

另外举例说明了PLL在通信系统中的用途。

在第二部分中,我们详细考察了相位噪声、参考杂散、输出漏电流等关键性能规格,还考虑了它们对系统性能的影响。

在本部分中,我们将考察PLL频率合成器的主要构建模块。

我们还将比较整数N和小数N架构。

最后将总结市场上现有的VCO,同时列出ADI的现有频率合成器系列。

PLL频率合成器基本构建模块PLL频率合成器可以从多个基本构建模块的角度来考察。

我们在前面已经提到过这个问题,下面将更加详细地进行探讨:鉴频鉴相器(PFD)参考计数器(R)反馈计数器(N)鉴频鉴相器(PFD)频率合成器的核心是鉴相器,也称鉴频鉴相器。

在鉴相器中,将比较参考频率信号与从VCO输出端反馈回来的信号,结果得到的误差信号用于驱动环路滤波器和VCO。

在数字PLL (DPLL)中,鉴相器或鉴频鉴相器是一个逻辑元件。

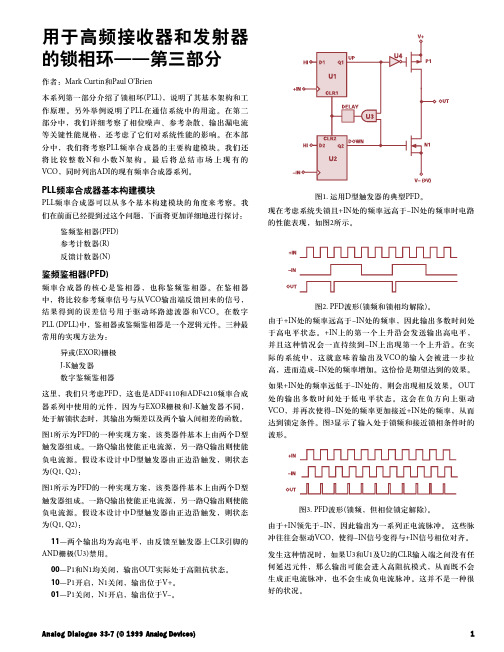

三种最常用的实现方法为:异或(EXOR)栅极J-K触发器数字鉴频鉴相器这里,我们只考虑PFD,这也是ADF4110和ADF4210频率合成器系列中使用的元件,因为与EXOR栅极和J-K触发器不同,处于解锁状态时,其输出为频差以及两个输入间相差的函数。

图1所示为PFD的一种实现方案,该类器件基本上由两个D型触发器组成。

一路Q输出使能正电流源,另一路Q输出则使能负电流源。

假设本设计中D型触发器由正边沿触发,则状态为(Q1, Q2):11—两个输出均为高电平,由反馈至触发器上CLR引脚的AND 栅极(U3)禁用。

00—P1和N1均关闭,输出OUT实际处于高阻抗状态。

10—P1开启,N1关闭,输出位于V+。

01—P1关闭,N1开启,输出位于V–。

图1. 运用D型触发器的典型PFD。

现在考虑系统失锁且+IN处的频率远高于–IN处的频率时电路的性能表现,如图2所示。

高频 锁相环调频

实验十锁相环调频121180166 赵琛一. 实验目的1.加深对锁相环基本工作原理的理解。

2.掌握锁相环同步带、捕捉带的测试方法,增加对锁相环捕捉、跟踪和锁定等概念的理解。

3.掌握集成锁相环芯片NE564的使用方法和典型外部电路设计。

4. 理解用锁相环实现调频的基本原理。

5. 掌握NE564构成调频电路的原理和调试方法。

二、实验使用仪器1.NE564锁相和调频实验板2.100MHz泰克双踪示波器3. FLUKE万用表4. 高频信号源5. 低频信号源三、实验原理锁相环由鉴相器( PD)、环路滤波器( LF)和电压控制振荡器( VCO)三个基本部件组成。

锁相环路是一个相位误差控制系统,它将参考信号与输出信号之间的相位进行比较,产生相位误差电压来调整输出信号的相位,以达到与参考信号同频的目的。

锁相环路由于具有良好的跟踪特性、窄带滤波特性和良好的门限特性等一些特殊的性能,而广泛应用于电子技术的各个领域。

图10-1是锁相环的构成框图。

图10-1锁相环的构成框图u t与压控振荡器输出信号鉴相器是相位比较器,用来比较输入信号()i0()u t 的相位,输出电压对应于这两个信号相位差的函数。

环路滤波器是滤除d ()u t 高频分量及噪声,以保证环路所要求的性能。

压控振荡器受环路滤波器输出电压c ()u t 的控制,使振荡频率向输入信号的频率靠拢,直至两者的频率相同,使得VCO 输出信号的相位和输入信号的相位保持某种特定的关系,达到相位锁定的目的。

设输入信号和本振信号(压控振输出信号)分别是正弦和余弦信号,它们在鉴相器内进行比较,鉴相器的输出是一个与两者的相位差成比例的的电压,一般把它称为误差电压。

(鉴相器的输出电压通常具有正弦鉴相的特点),鉴相器的拉氏变换数学模型可以表示如下:()sin ()d d e V s K s θ= 其中d K 表示鉴相器的灵敏度,()d V s 表示鉴相器的输出信号。

误差信号的相位()e s θ满足,()()()e i V s s s θθθ=-环路低通滤波器的作用是滤除鉴相器中的高频分量,然后把输出电压加到VCO 的输入端。

锁相环

1.锁相环发射锁相环和接受锁相环锁相环(phase-locked loop):为无线电发射中使频率较为稳定的一种方法,主要有VCO(压控振荡器)和PLL IC ,压控振荡器给出一个信号,一部分作为输出,另一部分通过分频与PLL IC所产生的本振信号作相位比较,为了保持频率不变,就要求相位差不发生改变,如果有相位差的变化,则PLL IC的电压输出端的电压发生变化,去控制VCO,直到相位差恢复!达到锁频的目的!!能使受控振荡器的频率和相位均与输入信号保持确定关系的闭环电子电路。

锁相环由鉴相器、环路滤波器和压控振荡器组成。

鉴相器用来鉴别输入信号Ui与输出信号Uo之间的相位差,并输出误差电压Ud 。

Ud 中的噪声和干扰成分被低通性质的环路滤波器滤除,形成压控振荡器(VCO)的控制电压Uc。

Uc作用于压控振荡器的结果是把它的输出振荡频率f。

拉向环路输入信号频率fi ,当二者相等时,环路被锁定,称为入锁。

维持锁定的直流控制电压由鉴相器提供,因此鉴相器的两个输入信号间留有一定的相位差。

锁相环最初用于改善电视接收机的行同步和帧同步,以提高抗干扰能力。

20世纪50年代后期随着空间技术的发展,锁相环用于对宇宙飞行目标的跟踪、遥测和遥控。

60年代初随着数字通信系统的发展,锁相环应用愈广,例如为相干解调提取参考载波、建立位同步等。

具有门限扩展能力的调频信号锁相鉴频器也是在60年代初发展起来的。

在电子仪器方面,锁相环在频率合成器和相位计等仪器中起了重要作用.2.锁相环是指一种电路或者模块,它用于在通信的接收机中,其作用是对接收到的信号进行处理,并从其中提取某个时钟的相位信息。

或者说,对于接收到的信号,仿制一个时钟信号,使得这两个信号从某种角度来看是同步的(或者说,相干的)。

由于锁定情形下(即完成捕捉后),该仿制的时钟信号相对于接收到的信号中的时钟信号具有一定的相差,所以很形象地称其为锁相器。

而一般情形下,这种锁相环的三个组成部分和相应的运作机理是:1 鉴相器:用于判断锁相器所输出的时钟信号和接收信号中的时钟的相差的幅度;2 可调相/调频的时钟发生器器:用于根据鉴相器所输出的信号来适当的调节锁相器, 内部的时钟输出信号的频率或者相位,使得锁相器完成上述的固定相差功能;3 环路滤波器:用于对鉴相器的输出信号进行滤波和平滑,大多数情形下是一个低通滤波器,用于滤除由于数据的变化和其他不稳定因素对整个模块的影响。

高频电路基础第5章-锁相环

vd

2

kViVo[sin

sin(2t

)

1 sin(2t

3

3 ) ......]

2021/3/18

高频电路基础

9

可能还会有两个输入都是方波的情况。 但不管哪种情况,输出信号中的低频分量均为

vd

1 2

kViVo

sin

Kd

sin[i (t) o (t)]

乘积型鉴相器的特点: • 定义两个输入正交时的相位差为0 • 输出电压平均值与两个输入的相位差的正弦成正比(所以

i (t) i (t)

鉴相器 vd (t) 环路滤波器 vc (t) 压控振荡器

PD

LF

VCO

分频电路 (可选)

o (t) o (t)

2021/3/18

高频电路基础

6

锁相环主要部件1——鉴相器

作用:比较输入与反馈两个信号的相位,输出与 相位差相关的电压(或电流)

形式:乘积型鉴相器 异或门鉴相器 边沿触发的RS触发器构成的鉴相器 边沿触发的鉴频-鉴相器

VCO

o (t) o (t)

瞬时相差: e ( t ) i ( t ) o ( t )

瞬时频差: (t) i (t) o (t)

d dt

e

(t

)

2021/3/18

高频电路基础

26

以算子 p 代表微分运算,则乘积型鉴相器(若采

用的其他鉴相器,可以相应的函数关系代替)、

环路滤波器、压控振荡器对于相位的数学运算表

不同环路滤波器情况下PLL的传递函数

简单RC

开环传递函数 H (s) K d K o

s(1 s)

闭环传递函数

(s)

s2

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验十一锁相环调频发射与接收实验

121180166 赵琛

一、实验目的

1. 加深锁相环工作原理和调频波解调原理的理解。

2. 掌握NE564构成的锁相环鉴频电路的原理和调试方法。

3. 锁相环调频发射电路与锁相环鉴频接收电路进行通信实验,加深对通信系统的理解。

二、实验使用仪器

1.NE564锁相和调频实验板

2.100MHz泰克双踪示波器

3. FLUKE万用表

4. 高频信号源

5. 低频信号源

三、实验基本原理与电路

1. 锁相环鉴频电路

用锁相环路可实现调频信号的解调。

如果将环路的频带设计得足够宽,则压控振荡器的振荡频率跟随输入信号的频率而变。

若压控振荡器的电压-频率变换特性是线性的,则加到压控振荡器的电压,即环路滤波器输出电压的变化规律必定与调制信号的规律相同。

故从环路滤波器的输出端,可得到解调信号。

用锁相环进行已调频波解调是利用锁相环的跟踪特性,这种电路称调制解调型PLL。

锁相鉴频原理框图如图11-1所示

图11-1锁相鉴频原理框图

采用NE564锁相环集成芯片来实现鉴频,由于其内部的压控振荡器转换增益不高,为了获得有效的解调输出信号,要求输入调频信号的频偏尽可能的大一些。

下图11-2是NE564构成调频信号解调的典型电路图。

图11-2 NE564构成调频信号解调的典型电路图

2.实验电路

锁相环鉴频实验电路见图11-3:

图11-3 调频信号解调实验电路图

电路原理:

电容C12和C13是5V的直流电源的去耦电容,NE564的1脚和10脚外接5V 正电源,8脚接地。

12脚和13脚之间有一个可变电容,可以微调压控振荡器的中心频率,跳线开关S8可以切换固定电容,决定了载波中心频率的范围。

已调频信号从TP1处输入,电容C1是隔直电容,调频信号从6脚输入鉴相器,电阻R1和电容C2是7脚外接的滤波电路。

9脚是压控振荡器的输出端,电阻R3是上拉电阻。

3脚是鉴相器的另外一个输入端,9脚和3脚相连构成调频解调电路。

调频信号可以从9脚输出,在TP4端可以通过示波器观察调频信号。

芯片的4,5脚分别外接低通滤波器的滤波电容。

TP3是环路低通滤波器的输出端。

滑动变阻器W1可以调节芯片2脚的基准电流,从而调整NE564的频率锁定范围。

16脚是FSK解调的输出端。

在16脚处可以外接示波器观察FSK解调出的TTL电平的数字基带信号。

14脚是普通调频信号的解调输出端,在TP3处可以用示波器观察到解调输出的调制信号,电容C14是解调信号输出端外接的积分电容。

15脚是NE564内部斯密特触发器的迟滞电压控制端。

四、实验内容

1. 锁相环路的调整。

2. 锁相环路调频电路的调整。

3. 锁相环路鉴频电路的调整。

4. 锁相环调频发射电路与接收电路的通信实验。

五、实验步骤

1. 锁相环路调频电路的调整

在实验箱主板上插上锁相环调频与测试电路实验模块和锁相环鉴频实验电路模块,接通实验箱上电源开关,电源指标灯点亮。

根据实验十调整好锁相环调频电路,产生中心频率为10.7MHz的调频信号输出。

2. 锁相环路鉴频电路的调整

将开关S8的1端合上,微调滑动变阻器W1和可变电容CW,使得在TP4处测得的压控振荡器的振荡频率为10.7M。

锁相环路调频电路的调整完毕后,将锁相环调频与测试电路实验板产生的调频信号(FM)由OUT端接入锁相环路鉴频电路模块TP1端。

当锁相环鉴频电路模

块的锁相环在FM信号中心频率上锁定时,压控振荡器将跟踪这个信号的时变频率,VCO的输入电压是来自鉴相器输出经低通滤波后的误差电压,它相当于解调输出,TP2端的输出应为解调后的信号。

用示波器双踪观察原始的调制信号和解调信号,并判断两者的波形和频率是否一致。

逐步增加原始调制信号的频率,当调制信号的幅度增加到一定大小时,锁相环鉴频电路将无法正确解调,记录下此时的调制信号幅度。

逐步增加原始调制信号的频率,当调制信号的频率增加到一定大小时,锁相环鉴频电路将无法正确解调,记录下此时的调制信号的频率。

从图中可以看出,被解调波形和FM波形的包络基本一致,说明锁相环能够正确实现调频波的解调功能。

数据记录:

取载波峰峰值为1V,频率10.7MHz

当频率为1kHz时,频偏大约在1.2MHz时失真。

当频偏为600KHz时,频率大约在15KHz时,输出信号幅度小于50mV,认为失真。

数据分析:从数据来看,基本符合NE564的工作状态。

实验感想:

本次实验是我本学期高频实验的最后一个实验,主要验证了锁相环的另一个用途,那就是作为鉴频器。

通过本次实验,我对于锁相环工作原理和调频博解调原理有了更深的认识。

最后也感谢姜乃卓老师本学期以来辛勤的指导,使我受益万分!。