高等院校DSP(数字信号处理)实验指导书-实验内容

DSP实验指导书(2)

DSP原理及应用实验指导书电气与电子工程学院实验六QDMA 读写实验一、实验目的:1.了解QDMA原理;2.熟悉QDMA的接口的配置;3.掌握QDMA的操作.二、实验内容:1.DSP 初始化;2.QDMA 配置;三、实验背景知识:QDMA 控制器可以在没有CPU参与的情况下完成存储器影射空间中的数据传输. 这些数据的传输可以是在片内存储器、片内外设或是外部器件之间,而且是在CPU操作后台进行的.QDMA 控制器的主要特点:1.后台操作:DMA 控制器可以独立于CPU工作.2.高吞吐率:可以以CPU时钟的速度进行数据吞吐.3.6个通道:DMA 控制器可以控制6 个独立通道的传输.4.辅助通道:该通道允许主机口向CPU的存储器空间进行请求.辅助通道与其他通道间的优先级可以设置.5.通道分割〔即Split-channel〕操作:利用单个通道就可以与一个外设间同时进行数据的读取和写入,与存在两个DMA 通道的效果一样.6.多帧〔Multiframe〕传输:传送的每个数据块可以含有多个数据帧.7.优先级可编程:每一个通道对于CPU的优先级是可编程确定的.8.可编程的地址产生方式:每个通道的源地址寄存器和目标地址寄存器对于每次读和写传输都是可配置的.地址可以是常量、递增、递减,或是设定地址索引值.9.自动初始化:每传送完一块数据,DMA 通道会自动重新为下一个数据块的传送做好准备.10.事件同步:读、写和帧操作都可以由指定的事件触发.11.中断反馈:当一帧或一块数据传送完毕,或是出现错误情况时,每一个通道都可以向CPU发送中断.四、实验要求:通过本实验,了解QDMA接口的配置及应用.五、实验程序功能与结构说明:➢QDMA 实验包含文件本次实验我们使用Test2011里面的0502的QDMA工程文件.1.main.c:实验的主程序,包含了系统初始化,系统时钟设置,QDMA通道CACHE 以及定时器设置,运行DMA 转移函数等;2.C6x.c:对SEED-DEC6713 各项资源操作的函数集,主要包含系统初始化函数,对CPLD 的各个控制函数.3.vecs.asm:包含定时器中断的中断向量表.4.linkd:声明了系统的存储器配置与程序各段的连接关系.➢程序流程图六、实验准备:1.将DSP 仿真器与计算机连接好;2.将DSP 仿真器的JTAG插头与SEED-DEC6713 单元的J2 相连接;3.打开SEED-DEC6713 的电源.观察SEED-DTK_MBoard单元的+5V,+3.3V,+15V, -15V 的电源指示灯以及SEED_DEC6713的电源指示灯D1、D3 是否均亮;若有不亮的,请断开电源,检查电源.七、实验步骤:1.打开CCS,进入CCS 的操作环境.2.装入QDMA.pjt 工程文件.3.打开main.c 程序,运行并下载程序.4. 设置断点,打开0x20000和0x21000开始的存储空间,运行程序.5.观察相关存储单元值的变化,验证QDMA相关原理.大家可以通过设置不同QDMA_S_OPT寄存器的值来观察其他的数据搬移效果实验七定时器控制实验一、实验目的:1.了解TMS320VC6713 的定时器;2.熟悉定时器各寄存器的配置;3.掌握TMS320VC6713 的中断结构和对中断的处理流程;4.学会C 语言中断程序设计,以及运用中断程序控制程序流程二、实验内容:1.系统初始化;2.定时器中断初始化;三、实验背景知识:TMS320C6713 片内集成了2 个32BIT 的通用TIMER,TIMER的原理框如下图.这些时钟有两种信号模式,可以用内部或外部时钟源做为时钟计数.这些时钟有两个PIN 脚:输入和输出PIN脚,可以用做时钟输入和时钟输出;也可以用做GPIO.在SEED-DEC6713 中,2 个TIMER配置为:z TIMER0 配置为外部扩展空间或内部使用;z TIMER1 配置为外部扩展空间或内部使用;本实验采用的定时器是TIMER1.四、实验要求:通过本实验,熟悉中断的结构及用中断程序控制程序流程,掌握定时器的应用.五、实验程序功能与结构说明:➢LED实验包含文件1.DEC6713_Timer.c:实验的主程序,包含了系统初始化,定时器中断初始化,定时器中断程序等.2.DEC6713.c:对SEED-DEC6713 各项资源操作的函数集,主要包含系统初始化函数,对CPLD 的各个控制函数.3.vecs.asm: 包含定时器中断的中断向量表.4.SEED_DEC6713d: 声明了系统的存储器配置与程序各段的连接关系.5.DEC6713.gel:系统初始化程序➢程序流程图Main 程序流程图定时器中断流程图六、实验准备:首先将光盘下03. Examples of Program \ 04. SEED_DTK-EPD实验程序目录下的3.2.7 Timer的文件夹拷贝到D:盘根目录下.1.将DSP 仿真器与计算机连接好;2.将DSP 仿真器的JTAG插头与SEED-DEC6713 单元的J2 相连接;3.打开SEED-DTK6713 的电源.观察SEED-DTK_MBoard 单元的+5V,+3.3V,+15V,-15V 的电源指示灯以及SEED_DEC6713 的电源指示灯D1、D3 是否均亮;若有不亮的,请断开电源,检查电源.七、实验步骤:1.打开CCS,进入CCS 的操作环境.2.装入time.pjt 工程文件, 添加DEC6713.gel 文件.3.装载time.out 文件,进行调试.4.打开DEC6713_Timer.c,在程序的第163行"TimerEventHandler<>;"处设置断点.5.运行程序,程序会停在断点处,表明已进入定时器中断.此时观察CCS 下方的"Stdout"窗口,会看到"Count:1".继续运行程序,程序每次都会停在断点处,连续进入中断60次后,退出主程序.如下图所示:提示:实验者可根据自己的需要改变周期寄存器的值,从而控制每次进中断的时间.实验八PLL锁相环实验一、实验目的:1.了解TMS320VC6713 的PLL锁相环;2.熟悉锁相环各寄存器的配置;3.掌握锁相环初始化的过程操作二、实验内容:1.系统初始化2.锁相环初始化3.改变锁相环的相关寄存器的值观察实验结果的变化情况三、实验背景知识:1.锁相环由锁相环乘法器<PLLM>、分频器<OSCDIV1、D0、D1、D2、D3>和复位控制器等部分组成,可通过软件进行配置,见图8-1.锁相环的输入参考时钟为来自CLKIN引脚的外部晶体振荡器的输入信号<CLKMODE0 = 1>,通过使用可配置的乘法器和分频器,在DSP内部,锁相环可灵活方便地修改输入的时钟信号,最后生成的时钟被传送到DSP内核、外围设备和其它的DSP内部模块2.锁相环模式<PLLEN=1>,当系统要使用分频器D0和乘法器的时候,进行此初始化过程.•在PLLCSR寄存器中,设置PLLEN=0<禁用模式>•等待最慢的PLLOUT信号或者参考时钟源<CLKIN>四个周期•在PLLCSR寄存器中,设置PLLRST=1<PLL被复位>•如果有必要,对PLLDIV0和PLLM编程•如果有必要,对PLLDIV1-n编程,必须执行此操作来使分频器更新比例系数•等待锁相环正确地复位•在PLLCSR寄存器中,设置PLLRST=0,使锁相环退出复位状态•等待锁相环锁定•在PLLCSR寄存器中,设置PLLEN=1来使能锁相环模式四、实验要求:通过本实验,熟悉锁相环的结构和功能及初始化过程中相关寄存器的配置,掌握锁相环的应用.五、实验程序功能与结构说明:实验中通过软件对锁相环和锁相环控制寄存器进行初始化,通过对锁相环和其相关寄存器的正确配置,产生DSP各个模块或者外围设备所需要的时钟信号.六、实验准备:1.将DSP 仿真器与计算机连接好;2.将DSP 仿真器的JTAG插头与SEED-DEC6713 单元的J2 相连接;3.打开SEED-DTK6713 的电源.观察SEED-DTK_MBoard 单元的+5V,+3.3V,+15V,-15V 的电源指示灯以及SEED_DEC6713 的电源指示灯D1、D3 是否均亮;若有不亮的,请断开电源,检查电源.七、实验步骤::1.打开CCS,进入CCS操作环境2.打开Test2001文件里面的SpeedUSB.pjt工程文件3.编译、下载main.c文件4.结合上节定时器实验,修改相关寄存器,观察输出的快慢变化。

DSP实验完整版

实验名称: 熟悉MATLAB 环境快速傅里叶变换(FFT)及其应用 IIR 数字滤波器的设计 FIR 数字滤波器的设计实验报告内容包括:实验一 实验名称(注意:9题选4~5题)一、实验目的(1)熟悉MA TLAB 的主要操作命令。

(2)学会简单的矩阵输入和数据读写。

(3)掌握简单的绘图命令。

(4)用MATLAB 编程并学会创建函数。

(5)观察离散系统的频率响应。

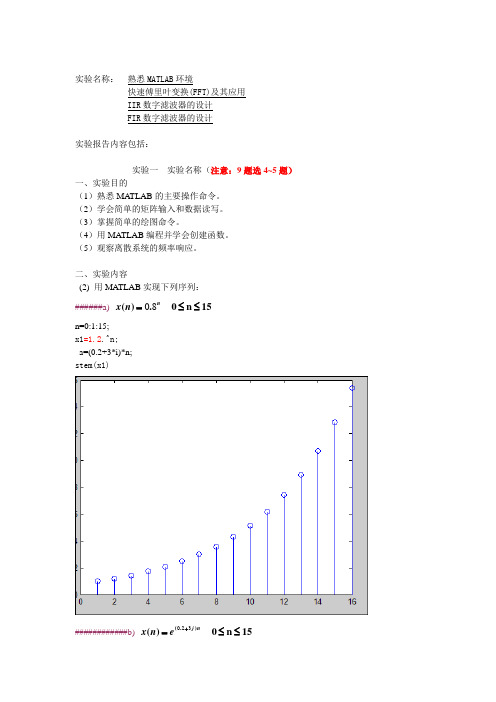

二、实验内容(2) 用MATLAB 实现下列序列:######a) 08(). 0n 15n x n =≤≤n=0:1:15; x1=1.2.^n; a=(0.2+3*i)*n; stem(x1)############b) 023(.)() 0n 15j nx n e+=≤≤n=0:1:15; x2=exp(a); a=(0.3+2*i)*n; stem(x2)################b) 100()cos()sin() 0t 4s x t t t ππ=≤≤ t=0:0.01:4;x=cos(200*pi*t).*sin(pi*t); plot(t,x, 'r-');xlabel('t'),ylabel('x(t)'),title('cos')##################(8) 求以下差分方程所描述系统的单位脉冲响应h (n ), 050n ≤<011006221().().()()()y n y n y n x n x n +---=--实验过程与结果(含实验程序、运行的数据结果和图形); clear all;N=50; a=[2 -1];b=[2 0.3 -0.04]; x1=[1 zeros(1,N-1)]; n=0:1:N-1; h=filter(a,b,x1); stem(n,h)axis([-1 53 -2.5 1.2])实验二实验名称(注:共四个,也可以自己在老师给的“实验二的内容”中自己选做)一、实验目的(1) 在理论学习的基础上,通过本实验,加深对FFT的理解,熟悉MA TLAB中的有关函数。

DSP实验指导书探素

DSP原理及应用实验指导书实验一:熟悉CCS,编写一个以C语言为基础的DSP程序一、实验目的1.认识TMS320LF2407 DSP实验开发系统的硬件结构。

2.了解TMS320LF2407 DSP应用程序的开发调试流程。

3.学习使用CCS3.3调试TMS320LF2407 DSP程序。

4.学习用标准C语言编制程序:了解常用的C语言程序设计方法和组成部分。

二、实验设备PC兼容机一台,操作系统为Windows2000(或Windows98,Windows XP,以下默认为Windows2000),CCS3.3编译软件,TMS320LF2407 DSP实验开发板和仿真器。

三、实验原理1.标准C语言程序:CCS支持使用标准C语言开发DSP应用程序。

当使用标准C语言编制程序时,其源文件名的后缀应为.C(如:volume.c)。

CCS在编译标准C语言程序时,首先将其编译成相应汇编语言程序,再进一步编译成目标DSP的可执行代码。

最后生成的是COFF格式的可下载到DSP 中运行的文件,其文件名后缀为.out。

由于使用C语言编制程序,其中调用的标准C的库函数由专门的库提供,在编译链接时编译系统还负责构建C运行环境。

所以用户工程中需要注明使用C 的支持库。

2.命令文件的作用:命令文件(文件后缀为.cmd)为链接程序提供程序和数据在具体DSP硬件中的位置分配信息。

通过编制命令文件,我们可以将某些特定的数据或程序按照我们的意图放置在DSP所管理的内存中。

命令文件也为链接程序提供了DSP外扩存储器的描述。

在程序中使用CMD文件描述硬件存储区,可以只说明使用部分,但只要是说明的,必须和硬件匹配,也就是只要说明的存储区必须是存在的和可使用的。

3.内存映射(map)文件的作用:一般的,我们设计、开发的DSP程序在调试好后,要固化到系统的ROM 中,为了更精确的使用ROM空间,我们就需要知道程序的大小和位置,通过建立目标程序的map文件可以了解DSP代码的确切信息。

dsp实验指导书

《 D S P 技术及应用》实验指导书吴延海吴冬梅编西安科技大学通信学院2 0 0 6目录第一章DES320PP-U介绍§1.1 功能特点 3 §1.2 XDS510仿真调试器 3 §1.3 对外的扩展接口 3 §1.4 DES5402PP-U结构及功能 4第二章DES320PP-U驱动程序的安装8 §2.1 安装驱动程序setupcc54x 8 §2.2 安装CCS下的硬仿真器驱动程序9第三章DSP实验内容12 §3.1 实验一CCS开发环境练习12 §3.2 实验二基本算术运算—--定点加减法15 §3.3 实验三基本算术运算----定点乘除法18 §3.4 实验四用定时器实现数字振荡器21 §3.5 实验五FFT的实现26 §3.6 实验六BSP串口操作45 §3.7 实验七HPI接口操作实验50 §3.8 实验八FIR滤波器56附录DES320PP-U实验系统资源一览63 附1.1 实验系统跳线说明63 附1.2 实验系统测试点说明64 附1.3 实验系统I/O接口说明65 附1.4 存储器映射一览表65第一章DES320PP-U介绍§1.1 功能特点●集成XDS510仿真调试器,无需外部JTAG仿真器便可完成所有DSP实验;全面支持'C2000,'C5000,'C6000,'VC33各个系列DSP,并全面兼容CCS 2.0,方便您调试自己的目标DSP系统●多类型仿真/教学实验DSP平台,通过更换DSP子卡可满足不同需求,包括C2000系列、C5000系列、C6000系列的DSP子卡●在可换CPU架构上,提供多种扩展模块,包括USB1.1模块、视频模块、EDA实验模块、信号与系统实验模块等等,便于用户选购定制;●可学习深层次信号处理原理,如G.723编解码;定点DSP实现MP3解码;无线基带通信所涉及的卷积编码、Vitebi译码、自适应均衡;AM调制、LMS自适应滤波;●可完成语音频段范围的信号处理实验:使用TLC320AC01作为模拟接口(AIC)电路,提供A/D和D/A各1个通道(14 bit),最高采样率为25K Sa/s。

dsp实验指导书

电气工程学院《DSP技术及应用》实验指导书尉学军编写适用专业:电子信息工程贵州大学二OO 八年八月《数字信号处理》实验是理论教学的深化和补充,具有较强的实践性,是一门重要的专业必修课,可作为通信类、电子类专业学生的选修课。

所开设的实验以具体实例为实验内容,让学生深刻理解DSP芯片的特点,培养学生应用DSP 设计解决实际问题的能力。

通过上机与实验,理解实验原理及实验方案,掌握正确的操作规程,掌握5410USB EVM实验箱的正确使用方法。

掌握CCS软件的使用,熟练掌握DSP的汇编语言的编写和程序调试,掌握DSP的中断技术和定时器的初始化方法以及应用,以及利用串口进行数据采集。

并要求学生利用北京闻亭5410USB EVM实验箱进行数字式信号发生器和滤波器的设计。

作者在此设计了10个实验,其中4个验证性实验,6个设计性实验。

在开设实验过程中,可以根据大纲选作部分实验。

1、实验一:CCS的安装与simulate的使用·····················································32、实验二:汇编语言基本算术运算································································73、实验三:程序的控制和转移······································································104、实验四:数字式正弦信号发生器·······························································145、实验五:FIR数字滤波器·········································································216、实验六:IIR数字滤波器·········································································277、实验七: 图象的伽玛增强········································································358、实验八: 快速傅立叶变换(FFT)的实现······················································429、实验九: 控制XF引脚周期性变化·····························································4910、实验十: 多通道缓冲串口的使用·····························································5411 实验报告基本内容要求···········································································6212、实验报告格式··························································································6313、参考文献·································································································65实验一:CCS的安装与simulate的使用实验学时:2实验类型:验证实验要求:必修一、实验目的学会CCS的安装和设置,熟悉程序的开发流程,初步掌握Simulator的使用方法.二、实验内容安装CCS软件,并利用CCSsetup进行设置对一个简单程序进行调试三、实验原理、方法和手段利用软件对指令进行仿真分析。

DSP实验指导书

实验一常用指令实验一、实验目的1、了解DSP开发系统的组成和结构;2、掌握DSP开发系统连接过程和DSP的开发界面;3,熟悉LF2407系列的寻址系统及常用LF2407系列指令的用法。

二、实验设备计算机,CCS 2.0版软件,DSP仿真器,EXP3实验箱。

三.实验步骤与内容开发TM S 320C2xxx应用系统一般需要以下几个调试工具来完成:(1)软件集成开发环境(CodeComposer):完成系统的软件开发,进行软件和硬件仿真调试。

它也是硬件调试的辅助乎段。

(2)开发系统:实现硬件仿真调试时与硬件系统的通信,控制和读取硬件系统的状态和数据。

(3)评估模块:提供软件运行和调试的平台和用户系统开发的参照。

(4) CodeComposer4.1卞要完成系统的软件开发和调试。

它提供一整套的程序编制、维打…、编译、调试环境,能将汇编语言和C语言程序编译连接生成COFF(公共目标文件)格式的可执行文件,并能将程序下载到目标DSP上运行调试。

(5)用户系统的软件部分可以由CodeComposer建立的工程文件进行管理,工程文件一般包含以下几种文件:源程序文件:C语言或汇编语言文件(*.ASM或*.C)头文件(*H)命令文件(*.CMD)库文件(*.LIB)中断向量交件(*.ASM)★启动CodeComposer双击桌面上“CC C2000 "启动Code Composer 4.1;可以看到显示出的C2XX CodeComposer窗口;★创建工程(1)创建新的工程文件:选择菜单“Project”的“New...”项;输入工程文件名字并保存;这时建立的是一个空的工程文件;.(2)在工程文件中添加程序文件:选择菜单“Project”的“Add Files to Project...”项;在“Add Files to Project”对话框中改变文件类型为“Asm Source Files(.a*;*.s*)",选择文件“*asm";重复上述各步骤,再添加以下文件到工程中;*.cmd, vector.asm.(3)编译连接工程:选择菜单“Project”的“Rebuild All”项;注意编译过程中CCS卞窗日下部的“Build"提示窗中显示编译信息,最后将给出错误和警告的统计数;编辑修改工程中的文件.(4)查看工程文件展开CCS卞窗日左侧工程管理窗中的工程各分支,可以看到“*.mak*工程中包含"*.asm","*.cmd"和"*.h;,其中“*.h”为程序在编译时根据程序中的“include"语句自动加入的;(5).查看源文件双击工程竹理窗中的“`'`as m”文件,可以查看程序内容;双击工程竹理窗中的“`'`.h”文件,打开此文件显示,可以看到其中有卞程序中要用到的一些寄存器等;" *.cmd”文件定义程序所放置的位置,此例中描述了LF2407的片内存储器资源,指定了程序和数据在内存中的位置;(6)基本调试功能:a)执行File-Load Program,在随后打开的对话框中选择刚刚建立的*.out文件;在项日浏览窗日中,双击`'`.rim激活这个文件,移动光标到start 行上,右击鼠标选择Toggle Breakpoint或按F9设置断点;b)使用观察窗口执行View令Watch window打开观察窗日;在`*asm中,选中任意一个变量,右击鼠标,选择”Quickwatch",CCS将打开quickwatch窗口并显示选中的变量;在`*asm中,选中任意一个变量,右击鼠标,选择”Add to watch window",CCS将把变量添加到观察窗日并显示选中的变量值;在观察窗日中双击变量,则弹出修改变量窗日,此时,可以在这个窗日中改变程序变量的值。

DSP实验指导书-图文

DSP实验指导书-图文数字信号处理E某PIV教学实验系统110实验五离散余弦变换(DCT)算法实验一、实验目的学习DCT算法的实现方法。

二、实验设备计算机,CCS2.0版软件,实验箱,DSP仿真器。

三、实验原理离散余弦变换与离散傅立叶变换紧密相关的,属于正弦类正交变换,由于其优良的去冗余性能及高效快速算法的可实现性,被广泛用于语音及图象的有损和无损压缩。

在开始实验之前,应了解以下基本原理。

1.语音或图象的压缩手段;2.DCT变换在数据压缩中的作用与应用。

四、实验步骤1.阅读本实验所提供的样例子程序;2.运行样例程序,分析结果;3.样例程序实验操作说明A.实验前准备1)正确完成计算机、DSP仿真器和实验箱连接后,开关K9拨到右边,即仿真器选择连接右边的CPU:CPU2;系统上电;2)“A/D转换单元”的拨码开关设置:JP3拨码开关:码位123456备注ON:将“模拟信号源”单元的信号输入到AD7822OFF:OFF:OFF:OFF:OFF:SW2拨码开关:SW21ON2ON3ON4备注码位ONAD7822的采样时钟为250KHZ,且中断给CPU2的中断2数字信号处理E某PIV教学实验系统111S23拨码开关:码位1、2B.实验启动CCS2.0,Project/Open打开“Algorithm”目录中“e某p05_cpu2”子目录下“E某p-DCT-AD.pjt”工程文件;双击“E某p-DCT-AD.pjt”及“Source”可查看各源程序;加载“E某p-DCT-AD.out”;在主程序中,在flag=0处设置断点;单击“Run”运备注OFF,不混频行程序,程序将运行至断点处停止;数字信号处理E某PIV教学实验系统112用View/Graph/Time/Frequency打开两个图形观察窗口;采用双踪观察在启始地址分别为某和y,长度为128的单元中数值的变化,数值类型为32位浮点型,这两个数组分别存放的是经A/D转换的输入信号和对该信号进行DCT变换的结果;再打开一个图形观察窗口,设置观察变量为z;变量z为输入信号的DCT变换及逆DCT变换的结果,长度128,32位浮点型,即输入信号的重构信号;调整各图形观察窗口,观察正变换与逆变换结果;单击“Animate”运行程序,调整各图形观察窗口,动态观察变换结果;改变输入信号的波形、频率、幅值,动态观察变换结果;数字信号处理E某PIV教学实验系统113单击“Halt”暂停程序运行,关闭窗口,实验结束;实验结果:在CCS2.0环境,同步观察输入信号及其DCT变换结果。

DSP实验指导书汇总

实验一 DSP教学实验系统与集成开发环境入门一、实验目的1、熟悉CCS集成开发环境,掌握工程的生成方法;2、熟悉SEED-DTK BPD实验环境;3、掌握CCS集成开发环境的调试方法;4、了解数在计算过程中的定标,掌握数的定点、浮点表示方法,定点、浮点基本运算以及定点、浮点间的相互转换。

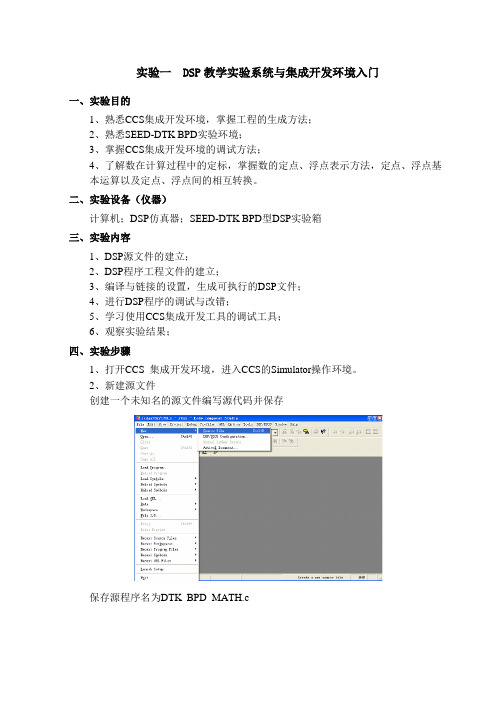

二、实验设备(仪器)计算机;DSP仿真器;SEED-DTK BPD型DSP实验箱三、实验内容1、DSP源文件的建立;2、DSP程序工程文件的建立;3、编译与链接的设置,生成可执行的DSP文件;4、进行DSP程序的调试与改错;5、学习使用CCS集成开发工具的调试工具;6、观察实验结果;四、实验步骤1、打开CCS 集成开发环境,进入CCS的Simulator操作环境。

2、新建源文件创建一个未知名的源文件编写源代码并保存保存源程序名为DTK_BPD_MATH.c创建其他源程序(如.cmd)可重复上述步骤3、建立新工程,打开CCS,点击Project-->New,创建一个新工程工程名及路径可任意指定。

这里新建一个名为DTK_BPD_MATH.pjt的工程,路径为C:\tic2000\myprojects\DTK_BPD_MATH。

点击Project,选择add files to project,添加DTK_BPD_MATH.c、math.cmd、rts2800_ml.lib 文件到工程中。

在下面窗口中可以看到DTK_BPD_MATH.c、math.cmd、rts2800_ml.lib文件已经加到工程文件中。

4、设置编译与连接选项设置相应的编译参数,一般情况下,按默认值就可以。

设置连接顺序,注:当使用rts2800_ml.lib 时将其放在最后。

点击Project-->Build all,对工程进行编译,如正确则生成DTK_BPD_MATH.out;若是修改程序,可以使用Project->Build命令,进行编译连接,它只对修改部分做编译连接工作,可节省编译与连接的时间。

DSP实验指导书学生版

实验一 DSP集成开发环境一、实验目的1.熟悉CCS软件运行环境设置及基本操作。

2.掌握CCS工程项目的创建、调试和分析。

3.通过实例初步掌握在CCS环境下设计DSP程序。

二、实验工具电脑Code Composer Studio三、实验内容乘法累加运算设计DSP汇编语言程序,实现, 其中[a1 a2 a3 a4]=[1,2,3,4]; [x1 x2 x3 x4]=[8 6 4 2];1、程序:(1)dp1.asm.mmregsSTACK .usect "STACK",10h.bss a,4.bss x,4.bss y,1.def aa.datatable: .word 1,2,3,4.word 8,6,4,2.textaa: STM #STACK+10h,SPSTM #a,AR1RPT #7MVPD table,*AR1+CALL SUMend: B endSUM: STM #a,AR3STM #x,AR4RPTZ A,#3MAC *AR3+,*AR4+,ASTL A,@yRET.end(2)dp1.cmd/*dp1.cmd*/-e aa-m map.mapMEMORY{PAGE 0:EPROM :org=04000H len=0100HVECS :org=05000H len=0004HPAGE 1:SPRAM :org=0060H len=0020HDARAM :org=0080H len=0100H}SECTIONS{.data :>EPROM PAGE 0.bss :>SPRAM PAGE 1STACK :>DARAM PAGE 1.vectors :>VECS PAGE 0}2、设置CCS环境双击CCS Sdudio,添加add ,仿真器为C54 simulater,再单击“Save and Quit”按钮后退出3、工程项目的创建和调试(1)新建一个工程:dp1.pjt。

DSP实验指导书

实验1 CCS 开发环境的使用方法一、实验目的:1、熟悉DSP 集成开发环境;2、掌握TMS320C54小DSP 程序空间的分配;3、掌握TMS320C54xDSP 数据空间的分配;4、掌握操作TMS320C54xDSP 存储器的相关命令。

二、实验设备硬件:计算机软件:CCS 集成开发环境三、实验内容编写在四个(1,2,3,4)i i a x i =乘积中找出最大值,并把最大值保存在累加器A 中的程序,其中a 1=1,a 2=2,a 3=3,a 4=4,x 1=5,x 2=6,x 3=7,x 4=8。

通过该程序的编写,使学生掌握CCS 的使用方法、寄存器内容的查看方法及存储空间的查看方法。

四、实验步骤1. 用CCS 软件新建一个工程。

2、打开一个空白的文档编写源程序。

3、把编写的源程序添加到工程中。

3、编译、连接工程中所有文件,生成.out 文件。

4、装载上述.out 文件,并运行。

五、实验报告1、简述实验目的及实验步骤;2、给出实验中编得的源程序;3、并对源程序中的每一句给出注释。

实验2 小数乘法运算实验一、实验目的:1、熟悉DSP 集成开发环境;2、掌握TMS320C54小DSP 程序空间的分配;3、掌握TMS320C54xDSP 数据空间的分配;4、掌握操作TMS320C54xDSP 存储器的相关命令;5、掌握基本算数运算指令的使用方法。

二、实验设备硬件:计算机软件:CCS 集成开发环境三、实验内容编写乘累加运算的程序,41(1,2,3,4)i ii y a x i ===∑, a 1=0.1,a 2=0.2,a 3=-0.3,a 4=0.4,x 1=0.8,x 2=0.6,x 3=-0.4,x 4=-0.2。

四、实验步骤1. 用CCS 软件新建一个工程。

2、打开一个空白的文档编写源程序。

3、把编写的源程序添加到工程中。

3、编译、连接工程中所有文件,生成.out 文件。

4、装载上述.out 文件,并运行。

dsp实验报告

dsp实验报告DSP实验报告一、引言数字信号处理(Digital Signal Processing,DSP)是一种对数字信号进行处理和分析的技术。

它在许多领域中被广泛应用,如通信、音频处理、图像处理等。

本实验旨在通过实际操作,探索和理解DSP的基本原理和应用。

二、实验目的1. 理解数字信号处理的基本概念和原理;2. 掌握DSP实验平台的使用方法;3. 进行一系列DSP实验,加深对DSP技术的理解。

三、实验器材和软件1. DSP开发板;2. 电脑;3. DSP开发软件。

四、实验内容1. 实验一:信号采集与重构在此实验中,我们将通过DSP开发板采集模拟信号,并将其转换为数字信号进行处理。

首先,我们需要连接信号源和开发板,然后设置采样频率和采样时间。

接下来,我们将对采集到的信号进行重构,还原出原始模拟信号,并进行观察和分析。

2. 实验二:滤波器设计与实现滤波器是DSP中常用的模块,用于去除或增强信号中的特定频率成分。

在此实验中,我们将学习滤波器的设计和实现方法。

首先,我们将选择合适的滤波器类型和参数,然后使用DSP开发软件进行滤波器设计。

最后,我们将将设计好的滤波器加载到DSP开发板上,并进行实时滤波处理。

3. 实验三:频谱分析与频域处理频谱分析是DSP中常用的方法,用于分析信号的频率成分和能量分布。

在此实验中,我们将学习频谱分析的基本原理和方法,并进行实际操作。

我们将采集一个包含多个频率成分的信号,并使用FFT算法进行频谱分析。

然后,我们将对频谱进行处理,如频率选择、频率域滤波等,并观察处理后的效果。

4. 实验四:音频处理与效果实现音频处理是DSP中的重要应用之一。

在此实验中,我们将学习音频信号的处理方法,并实现一些常见的音频效果。

例如,均衡器、混响、合唱等。

我们将使用DSP开发软件进行算法设计,并将设计好的算法加载到DSP开发板上进行实时处理。

五、实验结果与分析通过以上实验,我们成功完成了信号采集与重构、滤波器设计与实现、频谱分析与频域处理以及音频处理与效果实现等一系列实验。

《数字信号处理》实验指导书

数字信号处理实验指导书电子与信息工程学院二○一二年前言数字信号处理(DSP)研究数字序列信号的表示方法,并对信号进行运算,以提取包含在其中的特殊信息。

数字信号处理是一门技术基础课程,实验是该课程教学的重要内容,是理论联系实际的重要手段。

学生通过实验,可以验证和巩固所学的理论知识,掌握数字信号处理实验的基本技能,提高分析和解决实际问题的能力,培养认真、严谨、实事求是的工作作风。

我们根据当前通信类新课程体系的流行趋势,充分考虑通信工程类专业的特殊要求,编写了这门实验课程指导书。

在内容安排上,我们在自身的教学基础上,吸收了兄弟院校的先进经验。

我们把重点放在对学生理论联系实际、分析和解决问题能力的训练上,力求丰富实验内容,简化实验方法与步骤,化抽象为具体,让学生通过实验能够举一反三,融会贯通,提高信息处理和信息加工的能力,为以后在信息领域的发明和创造打下牢固的基础。

在实验的具体编排上,我们按照循序渐进的原则,逐步加深实验内容,注意前后实验之间的连贯性,强化基本实验技能的培养,保证实验内容的丰富性、生动性,增强学生对数字信号处理实验课程的兴趣。

目录实验一信号的谱分析 (1)实验二基-2FFT算法的软件实现 (6)实验三 IIR数字滤波器的设计 (12)实验四 FIR数字滤波器的设计 (16)实验一 信号的谱分析一、实验目的1、熟练掌握快速离散傅里叶变换(FFT )的原理及用FFT 进行频谱分析的基本方法;2、熟悉连续信号经理想采样前后的频谱变化关系,加深对时域采样定理的理解;3、进一步了解离散傅里叶变换的主要性质及FFT 在数字信号处理中的重要作用。

二、基本原理1、离散傅里叶变换(DFT )及其主要性质DFT 表示离散信号的离散频谱,DFT 的主要性质中有奇偶对称特性,虚实特性等。

通过实验可以加深理解。

例如:实序列的DFT 具有偶对称的实部和奇对称的虚部,这可以证明如下: 由定义∑-==10)()(N n knNW n x k X∑∑-=-=-=1010)2sin()()2cos()(N n N n kn N n x j kn N n x ππ ∑-=-=-10)()()(N n nk N NW n x k N X∑-=-=1)(N n kn NNnW Wn x∑-=-=10)(N n knN W n x∑∑-=-=+=1010)2sin()()2cos()(N n N n kn N n x j kn N n x ππ)(*)(k N X k X -=∴对于单一频率的三角序列来说它的DFT 谱线也是单一的,这个物理意义我们可以从实验中得到验证,在理论上可以推导如下: 设:)()2sin()(n R n N n x N π=其DFT 为:∑-=-=102)()(N n kn Njen x k X πkn Nj N n e n N ππ210)2sin(--=∑=kn N j N n n Nj nN j e e e j πππ21022)(21--=-∑-=∑-=+----=10)1(2)1(2)(21N n k n Nj k n N j e e j ππ从而∑-=-=-=10220)(21)0(N n n Nj nN j e e j X ππ∑-=--==-=10422)1(21)1(N n n Nj N j j N e j X π0)2(=X0)2(=-N X22)(21)1(102)2(2N j j N e e j N X N n n j n N N j =-=-=-∑-=--ππ以上这串式中)0(X 反映了)(n x 的直流分量,)1(X 是)(n x 的一次谐波,又根据虚实特性)1()1(X N X -=-,而其它分量均为零。

【2018最新】dsp实验指导书-word范文 (15页)

本文部分内容来自网络整理,本司不为其真实性负责,如有异议或侵权请及时联系,本司将立即删除!== 本文为word格式,下载后可方便编辑和修改! ==dsp实验指导书篇一:DSP实验指导书实验一 CCS软件的认识实验目的1.熟悉 CCS 集成开发环境,掌握工程的生成方法;2.掌握 CCS 集成开发环境的调试方法;实验内容:1. DSP 源文件的建立;2. DSP 程序工程文件的建立;3.学习使用 CCS 集成开发工具的调试工具;实验知识背景:CCS 提供了配置、建立、调试、跟踪和分析程序的工具,它便于实时、嵌入式信号处理程序的编制和测试,它能够加速开发进程,提高工作效率。

CCS 提供了基本的代码生成工具,它们具有一系列的调试、分析能力。

(1)CCS3.3的安装与配置和CCS3.1类似,先安装CCS3.3,路径可选择为C:\CCStudio_v3.3,桌面上会出现和两个图标,然后安装硬件仿真器usb驱动SEED-XDSUSB_CCS3.3,路径仍为C:\CCStudio_v3.3,C:\CCStudio_v3.3\drivers出现Seedusb2.cfg文件,安装完毕后,先双击图标进入Code Composer Studio Setup,在Family下拉列表中选择C28xx。

软件仿真模式:如果进行软件仿真,则双击选择F2812 Device Simulator,F2812 Device Simulator即出现在MySystem中,然后单击左下角的Save&Quit,在弹出的Start Code Composer Studio on exit?对话框中选择“是”,即可打开Code Composer Studio进行软件仿真。

硬件仿真模式:如果连接硬件仿真器,进行硬件调试,则双击选择F2812XDS510 Emulator,F2812 XDS510 Emulator即出现在MySystem中,然后在MySystem中,在F2812 XDS510 Emulator上单击右键选择Properties,在弹出的窗口中将Auto-generate board data file 改为Auto-generate board data file with extra configuration,点击Browse选择Seedusb2.cfg,接着点击Next,Finish,最后单击左下角的Save&Quit,在弹出的Start Code Composer Studio on exit?对话框中选择“是”,即可打开Code Composer Studio进行硬件仿真。

DSP实验指导书(2812)

目录目录 (1)第一章实验平台说明 (2)§基本参数 (3)§使用方法 (4)第二章算法实验 (5)§基础实验 (5)§卷积计算 (7)§相关运算 (9)§快速傅里叶变换(FFT) 实现 (11)§有限冲击响应滤波器(FIR) 实现 (15)§无限冲击响应滤波器(IIR) 实现 (21)§自适应滤波器(LMS) 实现 (23)第三章外设接口实验 (26)§数码管控制实验 (26)§交通灯控制实验 (28)§液晶显示屏(LCD)实验 (30)§矩阵键盘扫描实验 (31)§通用异步串行接口(UART) 实验 (32)§通用串行总线(USB) 接口实验 (33)§内置A/D转换实验 (36)§高速A/D转换实验 (38)§高速D/A转换实验 (40)§直流电机控制实验 (42)§步进电机控制实验 (43)§以太网卡与TCP/IP协议实验 (45)§CAN总线实验 (49)第一章实验平台说明随着科学技术的飞速发展,人们对控制模型、控制算法要求越来越高,传统意义上的处理器很难满足发展的需求,而数字信号处理器DSP 经历了20 多年的发展与普及,应用领域几乎涵盖了所有的行业:通信、信息处理、自动控制、雷达、航空航天、医疗、日常消费品等。

德州仪器(TI)占据了整个DSP 市场的50%左右,很多高校、研究所、公司大量采用TI 的方案与芯片进行开发与研究。

DSP 是一门理论与实践并重的技术,在成功掌握了理论知识的同时再配合做一些经典的DSP 实验,从而加深对DSP 软、硬件的理解与掌握,为今后从事独立的开发打下扎实的基础。

目前很多高校都已经开设了数字信号处理的课程,对普及与推广DSP 做出了巨大的贡献。

DSP技术实验指导书

DSP技术实验指导书陈军波刘海华编电子信息工程学院信号处理教研室2005年10月目 录第一部分DSP实验教学平台功能介绍 (3)☆结构简介: (3)☆数据流程图 (17)第二部分基础实验 (20)实验一CCS操作与DSP综合外设控制实验 (20)实验二DSP存储器及基本指令实验 (33)实验三快速傅里叶变换(FFT)实现 (38)实验四有限冲击响应滤波器(FIR)实现 (43)实验五无限冲击响应滤波器(IIR)实现 (51)实验六实时语音FIR滤波设计实验 (57)第三部分创新性实验 (60)实验一温度测量实验 (60)实验二YUV彩色图像处理之增强对比度 (62)实验三脉冲幅度相干(PAM)解调实验 (66)实验四MP3音频解码实验 (70)提示:请不要带电拔插仿真器和板卡!第一部分DSP实验教学平台功能介绍☆结构简介:一、主要功能模块:1、主CPU(SZ-5416D)模块:采用TI公司TMS320C5416DSP(以下简称5416)芯片,该模块上的资源有:4mbit flash、256k*16bit SRAM、2500 gate CPLD、电平转换芯片,模块上留有JTAG 插口,用户可以通过仿真器和CCS下载程序和进行实验;2、主CPU(SZ-2407E)模块:采用TI公司TMS320LF2407DSP(以下简称2407)芯片,该模块上的资源有:256k*16bit SRAM、2500 gate CPLD、电平转换芯片,模块上留有JTAG插口,用户可以通过仿真器和CCS下载程序和进行实验;以上两个模块可以通过5416的HPI接口实现双DSP的高速并行数据交换。

在实现对其他对象操作时,在平台的主板采用了CPLD(XC95216)来实现两DSP之间的软切换。

3、图象、语音模块(SZ-DSPFVV板):图象采用高速AD(TLC5510)和高速的DA(TLC5602),同时TLC5510和TLC5602又可做普通的AD、DA实验;语音模块采用专用语音处理芯片TLC320AD50C,最高采样率为22.05KHz,16位串行接口。

DSP实验指导书

节 1.01 §1.2 使用方法1. 电源本实验箱内部自带变压器,使用时不需另配低压电源,可直接用普通三相插头接入220V电源。

接上电源后,由电源模块输出±12V,±5V,3.3V,分别送至实验箱的各个模块。

另外为方便单独使用,两个主控板上都设有独立的电源输入端口,可以接入5V的直流电源。

2. 仿真器接口在做实验时,需要一个DSP仿真器,把在计算机上编译并生成的执行代码下载到5509或2812芯片上。

仿真器有两端接口,其中一端与计算机的并行口或USB口相连,这取决于仿真器的类型;另一端与DSP芯片的JTAG 接口相连,这是一个14针的接口,在两块主控板上都可以找到。

仿真器连接好后才能对主控板上的DSP芯片进行读写控制。

4. 计算机的配置DSP实验中的代码编写,下载仿真和程序调试都必须在计算机上完成。

计算机上需要安装DSP集成开发环境软件CCS(使用2.2或3.1版本)。

计算机应具备最少32M内存,100M硬盘空间和奔腾处理器,显示器分辨率不能低于800*600。

另外,部分模块的实验还要求计算机配有标准的USB接口,DB9串行接口以及RJ-45网卡接口。

5. 其它配件包括USB连接线,串行口连接线,网线,排线等。

节 1.02 §2.1 基础实验一、实验目的1. 掌握CCS实验环境的使用;2. 掌握用C语言编写DSP程序的方法。

二、实验设备1. 一台装有CCS软件的计算机;2. DSP实验箱的TMS320F2812主控板;3. DSP硬件仿真器。

三、实验原理浮点数的表达和计算是进行数字信号处理的基本知识;产生正弦信号是数字信号处理中经常用到的运算;C语言是现代数字信号处理表达的基础语言和通用语言。

写实现程序时需要注意两点:(1)浮点数的范围及存储格式;(2)DSP的C语言与ANSI C语言的区别。

四、实验步骤1.打开CCS 并熟悉其界面;2.在CCS环境中打开本实验的工程(Example_base.pjt),编译并重建.out 输出文件,然后通过仿真器把执行代码下载到DSP芯片中;3.把X0 , Y0 和Z0添加到Watch窗口中作为观察对象(选中变量名,单击鼠标右键,在弹出菜单中选择“Add Watch Window”命令);4.选择view->graph->time/frequency…。

DSP实验指导书

DSP实验指导书目录实验一正弦信号发生器 (1)实验二AM系统 (8)实验三DDS (16)实验四FSK调制系统 (25)实验五快速傅里叶变换 (32)实验六16阶FIR滤波器 (51)实验七IIR滤波器 (62)实验一正弦信号发生器一、实验仪器:PC机一台,JQ-SOPC-2C35实验箱一台及辅助软件(DSP Builder、Matlab/Simulink、Quartus II、Modelsim)。

二、实验目的:1. 初步了解JQ-NIOS-2C35实验箱的基本结构;2。

学习和熟悉基于DSP Builder开发数字信号处理实验的流程。

三、实验原理:正弦波是一种基本信号,任何复杂信号都可由许多频率、幅度各不相同的正弦波复合而成。

已知正弦波存在如下的关系:αsinαπ+sin(=2)由以上公式可知,正弦波存在周期性,本实验就是根据正弦波的这一特性进行正弦波发生。

在Altera DSP Builder库中,有一名为Increment Decrement的模块,根据参数设置的不同,Increment Decrement会不断从0计数到设定值,然后清0,接着又从0开始计数。

图3-1显示的是Increment Decrement的参数设置界面,以图中参数为例,number of bits设置为6,即从0开始计数到2^6,然后清0,接着又从0开始计数。

在LUT(Look Up Table)查找表模块中事先存入一个周期的正弦波的抽样值,利用Increment Decrement模块不断计数,根据计数值找到查找表的地址取出里面的值进行输出,因为Increment Decrement模块的输出具有周期性,则从LUT的输出也具有了周期性,这样,就产生了正弦波。

四、实验步骤:本实验的操作步骤如下:1.点击桌面上的Matlab图标,进入Matlab主界面,并将工作目录设为Matlab安装目录下的work文件夹,如图1所示:图1 Matlab启动界面2.点击菜单栏中的File->New->Model,新建一个模型,在Matlab命令窗口中输入simulink命令,调出simulink工具栏,如图2所示:图2 新建模型3.双击simulink工具栏中的Altera DSP Builder中的Arithmetic库,找到Increment Decrement模块,选中它并按住鼠标左键将其拖到新建的模型文件中,如图3所示:图3 添加模块4.双击模型文件中的Increment Decrement模块,打开模块参数对话框,将Bus Type设为Signed Integer,number of bits设为6,保持其他参数不变,点击【OK】按钮确认。

DSP实验指导书

实验要求1.在进入实验室前,按要求仔细阅实验内容和相关的资料,并编写上机程序。

2.凡调试成功的程序必须由实验辅导教师检查认可后方可离开实验室。

3.实验报告要求:1)实验目的。

2)实验程序的功能。

3)实现各种功能的算法。

4)程序结构图。

5)思考题、对实验的改进意见和想法。

6)实验报告以书面形式提交。

7)每次实验报告下一次实验前交给老师。

实验一、CCS开发环境的使用【实验目的】1.熟悉Code Composer Studio开发环境2.熟悉DSP软件开发流程3.熟悉几种主要的调试方法4.熟悉在调试环境下观察指令执行结果的方法【实验原理及简要说明】CCS (Code Composer Studio)是TI公司为其TMS320系列DSP提供的一个高度集成的软件开发和调试环境,它将DSP工程项目管理、源代码的编辑、目标代码的生成、调试和分析都打包在一个环境中,使其可以基本涵盖软件开发的每一个环节。

CCS主要包括以下工具:1. C编译器、汇编优化器和连接器(代码生成工具)2.指令集仿真器(Simulator)3.实时的基础软件(DSP/BIOS)4.主机和目标机之间的实时数据交换(RTDX)5.实时分析和数据可视化利用CCS,用户可以方便地建立一个DSP的工程项目,并对相应的源文件进行管理或编辑修改。

所有源文件的编译、汇编和连接只需要一个按钮就可以一次完成,用户不必再通过输入冗长的命令行来完成这些操作。

经过上面的过程产生的目标代码可以在CCS的环境下通过硬件仿真工具,如XDS510等,下载到用户目标系统中进行调试和运行。

如果没有用户目标系统,还可以将目标代码装载到Simulator中运行。

Simulator利用计算机的资源模拟DSP的运行情况,可以帮助用户熟悉DSP的内部结构和指令,在有的情况下还可以对部分的程序功能进行非实时的验证。

在CCS中,用户可以利用其提供的数据可视化工具按照数据的自然格式来观察数据,如眼图、星座图、FFT瀑布图等,对于图像数据,CCS也提供了多种格式(如YUV格式或RGB格式等)来读取原始数据并加以显示,这些工具使得位于DSP存储器中的数据得以形象的表现,从而可以大大加速分析与测试的速度。

DSP实验指导书

PDF 文件使用 "pdfFactory Pro" 试用版本创建

85 bk2:绝对地址寻址方式-数据存储器地址寻址;数据观察窗口地址为实际程序所编。 bk3:绝对地址寻址方式-程序存储器地址寻址;打开内存窗口的程序观察窗口地址 为,实际程序所编写(如程序中定义 PDAT0 为 1F00,地址就为 1F00)。 bk4:累加器寻址方式;打开寄存器和内存的数据观察窗口。 bk5:直接寻址方式(DP 为基准),打内存的数据观察窗口。 bk6:直接寻址方式(SP 为基准),打内存的数据观察窗口。 bk7:间接寻址方式,打开寄存器和内存的数据观察窗口。 bk8:存储器映射寄存器寻址方式,打开寄存器观察窗口。 bk9:堆栈寻址方式,打开寄存器观察窗口。 Bk10: 程序存储器到数据存储器的复制,打开寄存器观察窗口。 具体实验程序请参考:随机光盘里的 hmem 文件夹。 (六)思考题 1、如何将程序存储器其中某一起始地址的 0x100 个字复制到数据存储器的 0x4000 为起 始地址的空间中? 2、如何实现用 C 语言编写一个对可用数据内存清零程序?

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

表 1 CPU 数据地址总线扩展接口管脚定义表。

P1 管脚序号

对应 54X 管脚

说明

1

GND

地

2

D0

数据线 0

3

D1

数据线 1

4

D2

数据线 2

5

D3

数据线 3

6

D4

数据线 4

7

D5

数据线 5

8

D6

数据线 6

9

D7

数据线 7

10

D8

数据线 8

11

D9

数据线 9

12

D10

数据线 10

13

D11

数据线 11

-1-

二.CPU 板

本实验系统的CPU板由CPU模块,时钟模块,复位模块,存储器模块,CPLD 模块,扩展接口模块,电源模块以及接口组成,其布局图如图2所示。

3

2

1

4 1 1

9 5 6

7

8

1

1—JTAG 接口(J1)

2—电源插口(P4)

5—FLASH 写保护跳线(J3) 6—拨码开关(SW2)

9—扩展接口(P2)

HPI 控制信号 0

34

GND

地

35

HCNTL1

HPI 控制信号 1

36

GND

地

37

HINT

HPI 中断信号

38

+3.3V

电源

39

HRDY

HPI 准备好信号

40

+3.3V

电源

P2:CPU 外设总线扩展接口,其管脚定义如表 4 所示。

表 4 CPU 外设总线扩展接口管脚定义

P2 管脚序号

对应 54X 管脚

实验系统简介

一.系统概述

EL-DSP-EXP III 教学系统是综合的实验教学系统,它采用模块化分离式结 构,使用灵活,方便二次开发。通过“E_LAB”和“TECH_V”扩展总线,可以 扩展声、光、机、电等不同领域的控制对象。其平面布局图如图 1 所示。

仿真器接口

语音 单元

E_LAB接口2 TECH_V接口

本实验系统的 CPU 板可以单独使用,用于实验和开发,也可以通过 CPU 板

接口接在实验箱上。

由于本实验系统的 DSP 采用 3.3V 和 1.8V 供电,其输入输出接口电平为

3.3V,对于数字量输出而言完全可以和 5V TTL 电平兼容。但对于数字量输入而

言,由于其内部是 3.3V,因此不能将中央处理器的输出口直接和外围扩展的 5V

10—HPI 设置(J2)

3—复位按钮(S1) 7—CPLD 下载口(J4) 11—拨码开关(SW1)

4—扩展接口(P1) 8—扩展接口(P3) 12—LED 指示灯

图 2 CPU 板布局图

各接口功能说明如下: J1:DSP JTAG接口,符合IEEE Standard 1149.1(JTAG)标准,引脚分配如图3

37

A15

38

A14

39

+5V

40

+5V

地址线 18 地址线 1 地址线 0 地址线 3 地址线 2 地址线 5 地址线 4 地址线 7 地址线 6 地址线 9 地址线 8 地址线 11 地址线 10 地址线 13 地址线 12 地址线 15 地址线 14

电源 电源

J3:FLASH 写保护跳线。当接 1、2 两端时,不允许擦除 FLASH;当接 2、

五.电机控制接口

电机控制接口是 C2000 系列的 CPU 板用于控制各种类型的电机时使用的, 本实验系统采用 C5000 系列的 CPU 板,因此该接口不使用。

六.语音接口与处理单元。

语音编解码器(Codec)采用扩展板的形式通过语音接口与主板相连。本实 验系统的语音扩展板 Codec 芯片采用 TLV320AIC23(以下简称 AIC23),AIC23 是 TI 推出的一款高性能的立体声音频 Codec 芯片,内置耳机输出放大器,支持 MIC 和 LINE IN 两种输入方式(二选一),且对输入和输出都具有可编程增益 调节。AIC23 的模数转换(ADCs)和数模转换(DACs)部件高度集成在芯片内 部,采用了先进的 Sigma-delta 过采样技术,可以在 8K 到 96K 的频率范围内提 供 16bit、20bit、24bit 和 32bit 的采样,ADC 和 DAC 的输出信噪比分别可以达

3 两端时,允许擦除 FLASH(注:在配置 AM29LV320 FLASH 芯片时有效)。

SW2:拨码开关,SW2 的 1~3 位用于设置 CPLD 的工作状态,第 4 位用于

设置 LED 灯 D5 的工作状态,当第 4 位的状态为 ON 时,灯灭,反之,灯亮。

CPLD 的工作状态的设置功能见表 2。

-10-

图 8 TECH_V 总线接口信号图

TECH_V 接口的资源分配如下: bcs0 分配空间为 IO 空间的:0000h-0fffh 共 4K; bcs1 分配空间为 IO 空间的:1000h-1fffh 共 4K; bcs1 分配空间为 IO 空间的:2000h-2fffh 共 4K; bcs3 分配空间为 DATA 空间的:e000h-ffffh 共 8K; 注意:只有当子板检测信号引脚“cpu_det”为低电平时上述分配才起作用, 否则上述分配无效。

说明

1

GND

地

2

GND

地

3

READY

准备好信号

4

PS

程序空间片选信号

5

DS

数据空间片选信号

6

IS

IO 空间片选信号

7

R/W

读写信号

8

MSTRB

存储器空间选择信号

9

IOSTRB

IO 空间选择信号

10

MSC

微状态完成信号

-6-

11

XF

IO 输出信号

12

HOLDA

总线保持响应信号

13

IAQ

指令地址采集信号

14

HOLD

总线保持信号

15

BIO

IO 输入信号

16

GND

地

17

CLKRO

MCBSP0 输入位时钟

18

CLKR1

MCBSP1 输入位时钟

19

FSR0

MCBSP0 输入侦时钟

20

FSR1

MCBSP1 输入侦时钟

21

DR0

MCBSP0 输入数据

22

DR1

MCBSP1 输入数据

23

CLKXO

MCBSP0 输出位时钟

12

NC

空脚

13

HD6

HPI 数据线 6

14

NC

空脚

15

HD7

HPI 数据线 7

16

CPUCS

CPU 种类指示信号

17

NC

空脚

18

NC

空脚

19

HPIENA

HPI 使能信号

-5-

20

NC

空脚

21

HDS2

HPI 数据选通信号 2

22

DR2

MCBSP2 输入数据

23

HDS1

HPI 数据选通信号 1

24

FSR2

14

D12

数据线 12

15

D13

数据线 13

16

D14

数据线 14

17

D15

数据线 15

18

GND

地

19

A17

地址线 17

20

A16

地址线 16

21

A19

地址线 19

-3-

22

A18

23

A1

24

A0

25

A3

26

A2

27

A5

28

A4

29

A7

30

A6

31

A9

32

A8

33

A11

34

A10

35

A13

36

A12

4

CLKMD1=0

CLKMD1=1

OFF

MP/MC=1

5

MP/MC=0 DSP 工作微计算机方式

DSP 工作微处理器方 式

OFF

CPUCS=0

CPUCS=1

6

CPU 板为 54X 系列

CPU 板为 2X 系列

ON

LED 指示灯。各指示灯的功能为:D1—+5V,D2—+3.3V,D3—DSP 核电

压,D4—复位信号,D5—CPLD 测试。

MCBSP2 输入侦时钟

25

HBIL

HPI 字节指示信号

26

CLKR2

MCBSP2 输入位时钟

27

HAS

HPI 地址选通信号

28

CLKX2

MCBSP2 输出位时钟

29

ቤተ መጻሕፍቲ ባይዱ

HCS

HPI 片选信号

30

FSX2

MCBSP2 输出侦时钟

31

HR/W

HPI 读写信号

32

DX2

MCBSP2 输出数据

33

HCNTL0

24

CLKX1

MCBSP1 输出位时钟

25

FSX0

MCBSP0 输出侦时钟

26

FSX1

MCBSP1 输出侦时钟

27

DX0

MCBSP0 输出数据

28

DX1

MCBSP1 输出数据

29

NMI

不可屏蔽中断信号