tps23754参考设计

tps23754 工作原理

tps23754 工作原理

TPS23754是一款用于PoE(Power over Ethernet)应用的集成

电路。

它是一个嵌入式斩波器(flyback converter),可以从

以太网线缆上的PoE电源端提取直流电能,并将其转换为设

备所需的合适电压和电流。

其工作原理如下:

1. 输入电压检测:TPS23754会检测以太网电缆上的输入电压,以确定PoE供电的可用性。

2. 分离:TPS23754将输入电压与输出电压(设备所需电压)

分离,以保护设备不受输入电压的影响。

3. 驱动器:集成的驱动器会根据输出电压需求来控制电流的开关,从而产生所需输出电压。

4. 斩波变换:TPS23754通过斩波变换(flyback conversion)

将输入电压通过电感储存在输出电容中,并使其达到所需电压。

5. 维持稳定:通过反馈回路,TPS23754会实时监测输出电压,并根据其变化调整开关频率和占空比,以保持输出电压的稳定。

6. 保护功能:TPS23754还具有多种保护功能,如短路保护、

过温保护和过电流保护,以确保设备的安全性和稳定性。

总之,TPS23754通过斩波转换从PoE电源提取电能,并通过

控制开关进行变压和稳定输出电压,具有保护功能以确保设备的稳定供电。

ku11p ddr4设计规则

ku11p ddr4设计规则全文共四篇示例,供读者参考第一篇示例:KU11P DDR4设计规则在当今高性能计算和数据处理领域,需要高速和高密度的内存来支持日益增长的数据需求。

DDR4是目前最先进的内存标准之一,它提供了更高的带宽和更低的能耗,成为众多CPU、服务器和其它计算设备的首选。

KU11P是一种高性能的DDR4内存控制器IP,为设计人员提供了强大的功能和灵活性,以满足各种应用需求。

设计DDR4内存系统需要遵循一系列严格的规则和要求,以确保系统的稳定性和可靠性。

在使用KU11P DDR4 IP时,设计人员需要遵循以下设计规则:1. 时序规则:DDR4内存具有非常严格的时序要求,包括时钟频率、读写时序、预充电和刷新等。

设计人员需要根据DDR4规范中提供的时序要求,正确配置内存控制器的时钟信号和数据线,以确保数据传输的正确性和稳定性。

2. 电气规则:DDR4内存对电气性能要求也非常高,包括信号完整性、电压波动和噪声等。

设计人员需要正确配置信号引脚的阻抗匹配和电压标准,以确保数据传输的可靠性和抗干扰能力。

3. PCB布局规则:DDR4内存系统的PCB布局对其性能和稳定性至关重要。

设计人员需要遵循DDR4规范中提供的布局要求,包括信号走线长度匹配、功率平面设计和信号分组等,以最大限度地减少信号串扰和时钟偏差,提高系统性能。

4. 内存排布规则:DDR4内存的排布对系统性能和信号传输速度也有很大影响。

设计人员需要正确配置内存条的插槽和排列方式,以确保数据传输的平衡和稳定性。

5. 异常处理规则:在DDR4内存系统中,可能会出现各种异常情况,如时序错误、数据错误和通信故障等。

设计人员需要根据DDR4规范提供的异常处理指南,及时识别和解决问题,确保系统的可靠性和稳定性。

KU11P DDR4设计规则涵盖了时序、电气、PCB布局、内存排布和异常处理等多个方面,为设计人员提供了全面的指导和支持。

遵循这些规则,可以帮助设计人员设计出稳定、高性能的DDR4内存系统,满足各类应用需求。

PD控制器设计的LAYOUT注意事项

PD控制器设计的LAYOUT注意事项作者:宋云红王宏亮来源:《中国科技博览》2013年第06期[摘要]德州仪器(TI)宣布针对13W或26W的用电装置(PD)应用,如lP电话、无线AP(Wireless Access Points)或监控摄影机等,推出一款高效率、高功率以太网络供电(POE)控制器TPS23754,该组件符合IEEE 802.3at draft 4.0标准,可支持DC/DC转换器拓朴,转换效率达90%以上。

针对此款芯片进行电源设计。

[关键词]POE供电反馈端控制内部DC/DC转换电流检测串扰隔离中图分类号:TM571.1 文献标识码:A 文章编号:1009-914X(2013)06-0212-021、引言以太网供电,简称POE(Power over Ethemet)指的是在现有的以太网Cat.5布线基础架构不作任何改动的情况下,在为一些基于lP的终端(如lP电话机、无线局域网接入点AP、网络摄像机等)传输数据信号的同时,还能为此类设备提供直流供电的技术。

POE技术能在确保现有结构化布线安全的同时保证现有网络的正常运作,最大限度地降低成本。

一个完整的POE系统包括供电端设备(PSE,Power Sourcing Equilmaent)和受电端设备(PD,Powered Device)两部分。

TI公司的TPS23754是组合了以太网供电(PoE)30W大功率PoE用电装置接口和电流模式DC/DC控制器,非常适合用于隔离的转换器,应用空闲脚供电时,4、5脚连接为正极,7、8脚连接为负极。

2、PD控制器的设计TPS23754集成了POE受电设备PD接口和DC/DC转换器。

本文设计的控制器主要实现以下功能:(1)变压器降压实现(2)cTL反馈控制PwM(3)DC/DC转换电流的的检测(4)DC/Dc转换控制输出(5)整流电路输出(6)PD电源检测3、LAYOUT设计注意事项整体布局布线图(图1)此板为四层板,板面左侧1/3为PD电源部分。

TLV-2374资料

Printed or Pin 1Pin 1PACKAGING INFORMATIONOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)TLV2370ID ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2370IDBVR ACTIVE SOT-23DBV63000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2370IDBVRG4ACTIVE SOT-23DBV63000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2370IDBVT ACTIVE SOT-23DBV6250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2370IDBVTG4ACTIVE SOT-23DBV6250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2370IDG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2370IDR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2370IDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2370IP ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2370IPE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2371ID ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2371IDBVR ACTIVE SOT-23DBV53000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2371IDBVRG4ACTIVE SOT-23DBV53000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2371IDBVT ACTIVE SOT-23DBV5250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2371IDBVTG4ACTIVE SOT-23DBV5250Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2371IDG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2371IDR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2371IDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2371IP ACTIVE PDIP P850Pb-Free(RoHS)Call TI N/A for Pkg TypeTLV2371IPE4ACTIVE PDIP P850Pb-Free(RoHS)Call TI N/A for Pkg TypeTLV2372ID ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2372IDG4ACTIVE SOIC D875Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2372IDGK ACTIVE MSOP DGK880Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2372IDGKG4ACTIVE MSOP DGK880Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2372IDGKR ACTIVE MSOP DGK82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)TLV2372IDGKRG4ACTIVE MSOP DGK82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2372IDR ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2372IDRG4ACTIVE SOIC D82500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2372IP ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2372IPE4ACTIVE PDIP P850Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2373ID ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2373IDG4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2373IDGS ACTIVE MSOP DGS1080Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2373IDGSG4ACTIVE MSOP DGS1080Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2373IDGSR ACTIVE MSOP DGS102500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2373IDGSRG4ACTIVE MSOP DGS102500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2373IDR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2373IDRG4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2373IN ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2373INE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2374ID ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2374IDG4ACTIVE SOIC D1450Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2374IDR ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2374IDRG4ACTIVE SOIC D142500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2374IN ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2374INE4ACTIVE PDIP N1425Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2374IPW ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2374IPWG4ACTIVE TSSOP PW1490Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2374IPWR ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2374IPWRG4ACTIVE TSSOP PW142000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2375D PREVIEW SOIC D16TBD Call TI Call TIOrderable Device Status(1)PackageType PackageDrawingPins PackageQtyEco Plan(2)Lead/Ball Finish MSL Peak Temp(3)TLV2375DR PREVIEW SOIC D16TBD Call TI Call TITLV2375ID ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2375IDG4ACTIVE SOIC D1640Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2375IDR ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2375IDRG4ACTIVE SOIC D162500Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2375IN ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2375INE4ACTIVE PDIP N1625Pb-Free(RoHS)CU NIPDAU N/A for Pkg TypeTLV2375IPW ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2375IPWG4ACTIVE TSSOP PW1690Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2375IPWR ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIMTLV2375IPWRG4ACTIVE TSSOP PW162000Green(RoHS&no Sb/Br)CU NIPDAU Level-1-260C-UNLIM(1)The marketing status values are defined as follows:ACTIVE:Product device recommended for new designs.LIFEBUY:TI has announced that the device will be discontinued,and a lifetime-buy period is in effect.NRND:Not recommended for new designs.Device is in production to support existing customers,but TI does not recommend using this part in a new design.PREVIEW:Device has been announced but is not in production.Samples may or may not be available.OBSOLETE:TI has discontinued the production of the device.(2)Eco Plan-The planned eco-friendly classification:Pb-Free(RoHS),Pb-Free(RoHS Exempt),or Green(RoHS&no Sb/Br)-please check /productcontent for the latest availability information and additional product content details.TBD:The Pb-Free/Green conversion plan has not been defined.Pb-Free(RoHS):TI's terms"Lead-Free"or"Pb-Free"mean semiconductor products that are compatible with the current RoHS requirements for all6substances,including the requirement that lead not exceed0.1%by weight in homogeneous materials.Where designed to be soldered at high temperatures,TI Pb-Free products are suitable for use in specified lead-free processes.Pb-Free(RoHS Exempt):This component has a RoHS exemption for either1)lead-based flip-chip solder bumps used between the die and package,or2)lead-based die adhesive used between the die and leadframe.The component is otherwise considered Pb-Free(RoHS compatible)as defined above.Green(RoHS&no Sb/Br):TI defines"Green"to mean Pb-Free(RoHS compatible),and free of Bromine(Br)and Antimony(Sb)based flame retardants(Br or Sb do not exceed0.1%by weight in homogeneous material)(3)MSL,Peak Temp.--The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications,and peak solder temperature.Important Information and Disclaimer:The information provided on this page represents TI's knowledge and belief as of the date that it is provided.TI bases its knowledge and belief on information provided by third parties,and makes no representation or warranty as to the accuracy of such information.Efforts are underway to better integrate information from third parties.TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals.TI and TI suppliers consider certain information to be proprietary,and thus CAS numbers and other limited information may not be available for release.In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s)at issue in this document sold by TI to Customer on an annual basis.IMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty. T esting and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. T o minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements. Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers Audio /audioData Converters Automotive /automotiveDSP Broadband /broadbandInterface Digital Control /digitalcontrolLogic Military /militaryPower Mgmt Optical Networking /opticalnetwork Microcontrollers Security /securityLow Power Wireless /lpw Telephony /telephonyVideo & Imaging /videoWireless /wirelessMailing Address:Texas InstrumentsPost Office Box 655303 Dallas, Texas 75265Copyright 2006, Texas Instruments Incorporated。

AE-2M-3005 GC2375 CSP 模组设计指南 V1.0_20160520

GENERATION REVISION HISTORYREV. EFFECTIVEDATEDESCRIPTION OF CHANGESPREPARED BY1.0 2016-05-20 Document Release AE Dept.GCC on fi d e n ti al目录1. 外围电路 (4)2. 设计说明 (4)3. GC2375 CSP封装说明 (6)3.1 Optical Center (unit: µm) (6)3.2 GC2375 CSP封装(单位:µm) (7)3.3 CSP封装点阵表 (7)3.4 CSP封装管脚说明 (8)3.5 PCB焊盘设计说明示意图(单位:µm) (9)3.6模组成像方向 (9)3.7 CSP封装尺寸图(单位:μm) (10)3.8 CSP 封装说明 (11)G C C on fi d en ti a l1. 外围电路MIPI 1 lane图1-1 MIPI 接口外围电路图2. 设计说明外围电路设计说明◆ GC2375芯片分三路电源:AVDD28、DVDD18、IOVDD 。

AVDD28为模拟供电电源,2.7~3.0V ;DVDD18为数字电路供电电源,1.7~1.9V ; IOVDD 为I/O 电源,1.7~3.0V ;◆ 靠近电源处,加如图示滤波电容,容值请参照外围电路图;注意:A VDD 上电容(C4)规格为C0402;◆ 电容摆放应尽量靠近电源Pin 脚;◆ 所有电容均不可省去,否则会影响图像质量;◆ AGND 、DGND 需要在FPC 上靠近芯片端接到一起,铺地后引出到连接器端,否则会影响图像质量;◆ GND 走线尽量要粗,至少加粗至0.2mm 以上,尽量多打一些过孔; ◆ 电源线走线宽度至少加粗至0.2mm 以上; ◆ 芯片有RESET pin ,需要引出控制;◆ FPC/PCB 布线时尽量让SBDA/SBCL 线远离高速的信号线;◆ MCP 、MCN 需要尽量平行走线,等长;尽量少打或不打过孔;且要远离高GCC on fi d ti al频信号线(如MCLK),最好是能用地线保护起来,且差分线对走线的背面也尽量是地线走线,并铺地铜作为参考层。

华为服务器设计的艺术之路

华为服务器设计的艺术之路作者:华为来源:《通信产业报》2015年第35期凭借创新、可靠、安全、开放四大原则,华为服务器秉持“持续创新让计算变简单”的理念,连续7个季度出货量排在全球第四,覆盖金融、政府、互联网服务提供商与大企业。

华为服务器拥有稳定可靠、绿色节能、性能领先、持续创新和基于业务优化的特点,为企业关键业务保驾护航。

这是如何做到的呢?设计:精益求精在华为看来,高质量、高可靠性的服务器是设计出来的。

例如获得挑剔的日本客户认可的华为FusionServer RH8100 V3关键业务服务器,凭借创新的高可靠性设计、灵活扩展能力和卓越的计算性能,在Interop展上赢得了“BestofShowAward”大奖。

它采用RAS2.0技术,包括电源、风扇等关键模块的热插拔技术、全冗余的硬件和软件设计架构,以及提升管理维护效率的“黑匣子”等。

同时,使用高可靠硬盘设计,实现服务器内存和硬盘的自动装配,减少内存、硬盘人工装配引发问题的几率。

再如华为刀片服务器E9000采用无源背板设计,进一步提升可靠性,避免单点故障,同时使用独立风道设计,耐40摄氏度高温,有效地保障了企业用户关键业务的连续性。

材料:精挑细选服务器的用材决定着服务器的品质。

这不仅仅是外表的健美结实,也包括强劲的内涵。

华为每一台服务器的材质都采用电信级器件,质量等级高于业界标准。

同时,坚持被集成战略,利用EMS(电子制造服务)厂商实现产品设计、代工生产、后勤管理、产品维修等服务。

为了掌控整个流程,华为实现严密的稽核制度,不定期稽核供应商,并派驻全职驻厂稽核人员。

实时监控EMS厂质量数据,如质量数据异常会及时处理。

特别是在硬盘与内存这种容易出错的领域,华为会将报错较多的问题让供应商进行出厂前测试,逆向推动供应商改进产品质量。

此外,采用器件降频设计。

主要实现高频的配件以较低的频率工作,从而达到稳定工作的目的,解决频率过高带来高发热和系统不稳定的问题。

Tektronix TPS2012 TPS2014 TPS2024 数字存储示波器 说明书

数字存储示波器TPS2012 TPS2014 TPS2024产品技术资料所有型号都标配FFT高级触发,迅速捕获关心的事件传统模拟式旋钮和多语言用户界面,操作简便自动设置菜单、自动量程、波形存储器和设置存储器、内置上下文相关帮助,设置和操作迅速 带背灯的菜单按钮,视觉清楚 11种最关键的自动波形测量功能应用工用电源设计、调试、安装和维护 高级电子设计、调试、安装和维护 汽车设计和测试 教育TPS2000系列示波器,从工作台到现场,提供强大的生产效率TPS2000系列在示波器中提供了广泛的一系列功能,同时提供了用户熟悉、简便易用的控制功能和菜单。

TPS2000系列采用IsolatedChannel TM 技术,分成2通道和4通道版本,与接地及在通道之间实现了隔离,可以让您轻松进行测量,而不用担心损坏电路。

它标配电池电源,成为现场应用的自然之选。

对电源电子器件测试,选配软件把通常需要的电源系统测量功能集成到仪器中,加快了电源分析和调试速度。

主要特点和优点100 MHz 和200 MHz 带宽 高达2 GS/s 的实时采样率2条或4条全面隔离和浮动通道,外加隔离外部触发在安装两块电池时可以连续工作8小时,电池可以热插拔,几乎不受交流电源限制选配电源分析应用软件,以其价位提供了最广泛的电源测量功能OpenChoice ®软件或集成CompactFlash ®海量存储设备,迅速存档和分析测量结果产品技术资料进行浮动测量和差分测量-迅速、准确、经济被测电路以非预计方式接地,是测量结果差和电路损坏的常见原因。

连接两个或多个接地的探头可能会损坏接地环路,如果电流足够高,可能会导致元器件和设备毁坏。

最重要的是,在进行浮动测量时,如果仪器和探头使用不当,可能会给人身安全带来伤害。

2 4个IsolatedChannel TM 输入和隔离外部触发输入,可以迅速、准确、经济地进行浮动测量和差分测量。

输入信号等级参考浮动等级高压示波器探头 TPS2000输入BNC泰克IsolatedChannel技术简化了浮动测量。

复旦大学模拟电路二级运放实例

3.6.1 定义 ........................................................................................................ 16 3.6.2 两级运放的 CMRR .................................................................................. 17 3.7 电源抑制比(PSRR) ................................................................................ 18 3.7.1 定义 ........................................................................................................ 18 3.7.2 两级运放的 PSRR ................................................................................... 19 3.8 转换速率(Slew Rate) ............................................................................. 21 3.8.1 定义 ........................................................................................................ 21 3.8.2 两级放大器的 Slew Rate ......................................................................... 22 3.8.3 单位增益带宽 GBW 和压摆率 SR............................................................ 23 3.9 噪声 ............................................................................................................ 24 3.9.1 低频噪声 ................................................................................................. 24

TI工程师教你设计更小的电源

TI工程师教你设计更小的电源来源:TI在线支持社区作者:Aaron Paxton[导读]假设您几乎已经完成了最新、最重大的应用设计。

所有漏洞都已清除,而且非常好用。

差不多该进入主要阶段了,但还要解决最有一件事:电源。

关键词:TLV71333PTILDO假设您几乎已经完成了最新、最重大的应用设计。

所有漏洞都已清除,而且非常好用。

差不多该进入主要阶段了,但还要解决最有一件事:电源。

毕竟,我们不可能指望所有人都使用实验室电源为其应用供电,对吧?事后考虑电源并不稀奇。

我们很少围绕电源管理来设计系统,而且正好相反。

这样的做事顺序会造成恐慌,尤其是在 PCB 上空间所剩无几的时候。

唯一可用的方法就是找到最小的电源 IC。

LDO 是空间有限应用的热门选择,支持健身腕带、智能手表以及其它可穿戴设备等便携式应用。

然而,即使是机顶盒与路由器等线路供电的应用,空间也不是无限的,在可能的情况下也需要优化。

工程师经常会因芯片尺寸小而选择 LDO。

但这是唯一的考虑因素吗?这肯定是最重要的因素之一。

我们还需要权衡一些其它的因素,例如功耗、噪声特点与精确性等,但芯片首先要能放入应用,才有成为可行的解决方案。

IC 的物理尺寸能说明些问题,但绝对不够全面。

与任何其它 IC 一样,也需要考虑外部组件。

LDO 的外部组件包括电阻器网络、输入电容器与输出电容器。

图 1. 具有各种无源元件的 PCB 实例我们首先来讨论电阻器网络。

固定 LDO 将电阻分压器内部化,与可调 LDO 相比,可提供三大主要优势:空间。

固定 LDO 无需在电路板上布置或连接电阻器。

这可能听起来很微不足道,但即使是 0402 电阻器(1.0 毫米 x 0.5 毫米),也会占据宝贵的基板空间。

成本。

尽管电阻器比硅芯片便宜,但它们也需要成本。

我们也必须要考虑布置的成本问题。

减少组件数量可节省资金,特别是在准备将应用投入量产时。

准确性。

作为电阻器内部化的一部分,制造时可确保它们能够针对特定容差进行调节。

POE介绍

POE 相关介绍POE(power on Ethernet)为一种利用以太网双绞线传输电能的技术。

长期以来,双绞线是局域网的主要传输媒质;作为局域网设备的扩展,POE 设备能够在原有主要硬件的基础上,将受电端的设备电源解放。

其主要应用在IP 电话、无线接入点、PDA 充电站等;这些设备无需额外的AC 布线和外部电源适配器,利用POE 提供的13W(IEEE802.3af)或者30W(IEEE802.3at)功率便可以正常工作。

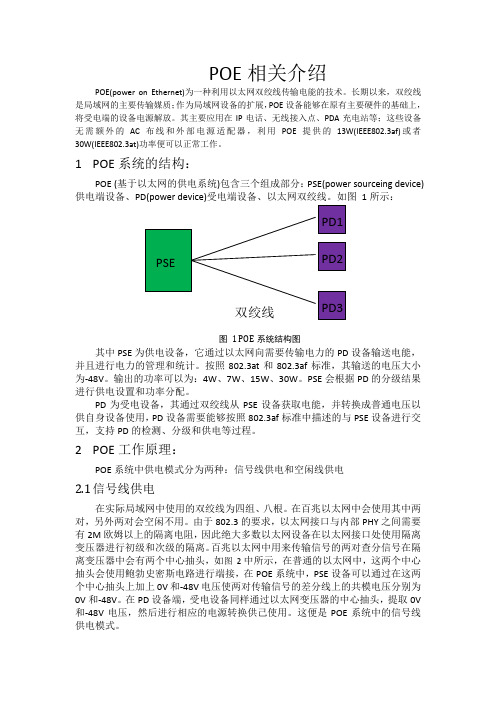

1 POE 系统的结构:POE (基于以太网的供电系统)包含三个组成部分:PSE(power sourceing device)供电端设备、PD(power device)受电端设备、以太网双绞线。

如图 1所示:图 1 POE 系统结构图 其中PSE 为供电设备,它通过以太网向需要传输电力的PD 设备输送电能,并且进行电力的管理和统计。

按照802.3at 和802.3af 标准,其输送的电压大小为-48V 。

输出的功率可以为:4W 、7W 、15W 、30W 。

PSE 会根据PD 的分级结果进行供电设置和功率分配。

PD 为受电设备,其通过双绞线从PSE 设备获取电能,并转换成普通电压以供自身设备使用,PD 设备需要能够按照802.3af 标准中描述的与PSE 设备进行交互,支持PD 的检测、分级和供电等过程。

2 POE 工作原理:POE 系统中供电模式分为两种:信号线供电和空闲线供电2.1 信号线供电在实际局域网中使用的双绞线为四组、八根。

在百兆以太网中会使用其中两对,另外两对会空闲不用。

由于802.3的要求,以太网接口与内部PHY 之间需要有2M 欧姆以上的隔离电阻,因此绝大多数以太网设备在以太网接口处使用隔离变压器进行初级和次级的隔离。

百兆以太网中用来传输信号的两对查分信号在隔离变压器中会有两个中心抽头,如图 2中所示,在普通的以太网中,这两个中心抽头会使用鲍勃史密斯电路进行端接,在POE 系统中,PSE 设备可以通过在这两个中心抽头上加上0V 和-48V 电压使两对传输信号的差分线上的共模电压分别为0V 和-48V 。

TPS2734

3

3.1

Quality Statement...................................................................... 10

Liability Policy ..................................................................................................... 10

2

2.1 2.2 2.3 2.4

Type Characteristics ................................................................... 3

Design Characteristics.......................................................................................... 3 Electrical Characteristics ...................................................................................... 4 Optical Characteristics.......................................................................................... 6 Mechanical Drawing ............................................................................................. 9

TrueSignal微电子TS2123A TS2124A TS2223A TS2224A TS242

TrusignalMicroelectronicsTS2123A/TS2124A TS2223A/TS2224ATS2424A3.3MHz, Rail-to-Rail I/O CMOS Operational AmplifierFeatures• Low Offset Voltage: 1.2mV (typ) • High Gain: 105dB (typ)• High Gain Bandwidth Product: 3.3MHz • Rail-to-rail Input/Output • Low I B : 10pA (typ)• Low supply voltage: +2.7 V to +5.5 V • Low Power Consumption: 260μA at 5 V (per amplifier)•Extended Temperature : -40°C to +125°CApplications• Signal Conditioning• Current Sensor Amplifier• Battery-Powered Applications • Portable Devices • Active Filtering• Weight Scale Sensor•Medical/Industrial Instrumentation •Power Converter/InverterProduct DescriptionThe TS2123A/TS2124A families of products are low noise, low voltage and low power operational amplifiers with a gain-bandwidth product of 3.3MHz and slew rate of 2V/μs . The maximum input offset voltage is only 5mV and the input common mode range extends beyond the supply rails.TS2123A/TS2124A families of operational amplifiers are specified at the full temperature range of −40︒C to +125︒C under single or dual power supplies of 2.7V to 5.5V, however these products will operate under an extended supply range from 2.7V to 5.5V at a reduced temperatures range.The TS2123A and TS2223A have a power-down feature that reduces the supply current to 1μA.SOT23-5TS2124AOUT V-+IN V+-INSOT23-6V-+IN V+-IND +IND V-+INC -INC OUTCV+V+OUT NCNCNCV-Enable SO-8V-V+-INB +INBV- TS2223AV-+INBMicroelectronicsTS2424ADatasheet July 2018 ORDERING INFORMATIONABSOLUTE MAXIMUM RATINGSESD CAUTIONESD (electrostatic discharge) sensitive deviceCharged devices and circuit boards candischarge without detection. Although thisproduct features patented or proprietaryprotection circuitry, damage may occur ondevices subjects to high energy ESD. Therefore,proper ESD precautions should be taken toavoid performance degradation or loss offunctionality.ELECTRICAL CHARACTERISTICS: V S = +2.7V to +5.5V Boldface limits apply over the specified temperature range, T A = −40︒C to +125︒C.At T A = +25︒C, R L = 10kΩ connected to V S/2, and V OUT = V S/2, unless otherwise noted.ELECTRICAL CHARACTERISTICS: V S = +2.7V to +5.5V Boldface limits apply over the specified temperature range, T A= −40︒C to +125︒C.At T A = +25︒C, RL = 10kΩ connected to V S/2, and V OUT = V S/2, unless otherwise noted.TYPICAL CHARACTERISTICSAt T A = +25︒C, R L = 10k Ω connected to V S /2, and V OUT = V S /2, unless otherwise noted.TYPICAL CHARACTERISTICSAt T A = +25︒C, R L = 10k Ω connected to V S /2, and V OUT = V S /2, unless otherwise noted.202530354045505560-50-25255075100125150S h o r t -C i r c u i t C u r r e n t (m A )Temperature (℃)SHORT-CIRCUIT CURRENT vsTEMPERATURE I SC -I SC +0.010.020.030.040.050.060.02.02.53.03.54.04.55.05.5S h o r t -C i r c u i t C u r r e n t (m A )Power-Supply Voltage (V)CONTINUOUS SHORT-CIRCUIT CURRENTvs POWER-SUPPLY VOLTAGEI SC -I SC +20022024026028030022.533.544.555.5Q u i e s c e n t C u r r e n t ( μA )Supply Voltage (V )QUIESCENT CURRENT vs SUPPLY VOLTAGE300400500600700800900-5050100150Q u i e s c e n t C u r r e n t (μA )Temperature (℃)QUIESCENT CURRENT vs EMPERATUREV CC = 5VV CC = 2.5V50m V /d i v400ns/divLARGE-SIGNAL STEP RESPONSEC L =100pF50m V /d i vSMALL-SIGNAL STEP RESPONSE1μs/divC L =200pF-3-2-10123010203040506070O u t p u t V o l t a g e (V )Output Current(mA)OUTPUT VOLTAGE SWING VS OUTPUT CURRENT150℃25℃-55℃0.5u V /d i v0.1 Hz TO 10 Hz NOISE1s/divTYPICAL CHARACTERISTICSAt T A = +25︒C, R L = 10k Ω connected to V S /2, and V OUT = V S /2, unless otherwise noted.-5-4-3-2-1012345Offset Voltage (mV)OFFSET VOLTAGEPRODUCTION DISTRIBUTIONP o p u l a t i o n123456789OFFSET VOLTAGE DRIFT MAGNITUDEPRODUCTION DISTRIBUTIONOffset Voltage Drift (uV/℃)P o p u l a t i o nAPPLICATION NOTESThe TS2123A and TS2124A families of op amps are suitable for a wide range of general-purpose applications. They provide Rail-to-rail input and output. Excellent ac performance makes them well-suited for audio and sensor applications. The input common-mode voltage range includes both rails, allowing the TS2123A and TS2124A families op amps to be used in bipolar and unipolar application. Rail-to-rail input and output swing significantly increases dynamic range, especially in low-supply applications.Power-supply pins should be bypassed with 0.1 F ceramic capacitors.POWER SUPPLYThe TS2123A and TS2124A families operate from a single +2.5V to +5.5V supply or dual ±1.25V to ±2.75V supplies. For single supply operation, bypass the power supply +VS with a 0.1μF capacitor which should be placed close to the +VS pin. For dual-supply operation, both the +VS and the -VS supplies should be bypassed to ground with separate 0.1μF ceramic capacitors. 2.2μF tantalum capacitor can be added for better performance.The TS2123A and TS2124A families are ideal for battery-powered instrumentation and handheld devices because it can operate at the end of discharge voltage of most popular batteries.Figure1. Amplifier with Bypass Capacitors DRIVING CAPACITIVE LOADSThe TS2123A and TS2124A families can directly drive 1000pF in unity-gain without oscillation. The unity-gain follower (buffer) is the most sensitive configuration to capacitive loading. Direct capacitive loading reduces the phase margin of amplifiers and this result in ringing or even oscillation. Applications that require greater capacitive driving capability should use an isolation resistor between the output and the capacitive load like the circuit in Figure2. The isolation resistor R ISO and the load capacitor CL form a zero to increase stability.The bigger the R ISO resistor value, the more stable V OUT will be. Note that this method results in a loss of gain accuracy because R ISO forms a voltage divider with the R LOAD.Figure 2. Indirectly Driving Heavy Capacitive LoadAn improved circuit is shown in Figure 3. It provides DC accuracy as well as AC stability. Rf provides the DC accuracy by connecting the inverting signal with the output. Cf and R ISO serve to counteract the loss of phase margin by feeding the high frequency component of the output signal back to the amplifier’s inverting input, thereby preserving phase margin inthe overall feedback loop.Figure 3. Indirectly Driving Heavy Capacitive Load withDC AccuracyFor non-buffer configuration, there are two other ways to increase the phase margin: (a) by increasing the amplifier’s gain or (b) by placing a capacitor in parallel with the feedback resistor to counteract the parasitic capacitance associated with inverting node.TYPICAL APPLICATIONDifference AmplifierFigure 4. Differential AmplifierThe circuit shown in Figure 4 performs the difference function. If the resistor ratios are equal (R4/R3 = R2/R1) then Vout= (Vin2 –Vin1) × R2/R1 + Vref.Low Pass Active FilterFigure 5. Low Pass Active FilterThe low pass filter shown in Figure 5 has a DC gain of (-R2 / R1) and the –3dB corner frequency is 1/2πR2C. Make sure the filter within the bandwidth of the amplifier. The Large values of feedback resistors can couple with parasitic capacitance and cause undesired effects such as ringing or oscillation in high-speed amplifiers. Keep resistors value as low as possible and consistent with output loading consideration.Instrumentation AmplifierFigure 6. Instrumentation AmplifierThe circuit in Figure 6 performs the same function as that in Figure 4 but with the high input impedance.REV KY.1.0.1A MECHANICAL DIMENSIONSSOT23-5 PACKAGE MECHANICAL DRAWINGSOT23-5 PACKAGE MECHANICAL DATASOT23-6 PACKAGE MECHANICAL DRAWINGSOT23-6 PACKAGE MECHANICAL DATAMSOP-10 PACKAGE MECHANICAL DRAWINGMSOP-10 PACKAGE MECHANICAL DATATSSOP-14 PACKAGE MECHANICAL DRAWINGTSSOP-14 PACKAGE MECHANICAL DATASO-8 PACKAGE MECHANICAL DRAWINGSO-8 PACKAGE MECHANICAL DATASO-14 PACKAGE MECHANICAL DRAWINGSO-14 PACKAGE MECHANICAL DATADFN-10 PACKAGE MECHANICAL DRAWINGDFN-10 PACKAGE MECHANICAL DATACONTACT INFORMATIONTrusignal MicroelectronicsPhone: +86 512-65923982Fax: +86 512-65923995Email: *********************; *******************。

性能测试方案模板

XXXX系统性能测试方案目录1.概述 (1)1.1编写目的 (1)1.2测试容 (1)2.性能测试策略 (1)2.1方法 (1)2.2流程 (1)2.3工具 (1)2.3.1性能测试工具 (1)3.性能测试环境 (2)3.1网络拓扑图 (2)3.2软硬件环境 (2)4.性能测试指标 (2)4.1性能指标关注点 (2)4.2性能指标详解 (3)4.2.1业务性能指标 (3)4.2.2应用服务器性能指标 (3)4.2.3数据库服务器性能指标 (3)4.2.4性能指标参考 (4)5.测试场景 (4)5.1存量数据 (4)5.2测试场景设计 (5)5.2.1单交易基准测试 (5)5.2.2单交易并发测试 (5)5.2.3混合场景并发测试 (6)5.2.4稳定性测试 (7)6.进度计划及人员安排 (7)6.1进度计划 (7)6.2人员安排 (8)7.风险评估 (8)1.概述1.1编写目的本测试方案用于指导XXXX系统的性能测试工作。

本文主要描述了性能测试围、性能参考指标以及使用的测试方法,以便于性能测试实施人员有依据性地对系统展开性能测试,根据实际的性能测试结果数据考察系统的相关指标情况,以便于开发对系统实施相关的调优工作,以及项目相关人员对系统的性能有个客观的评估。

1.2测试容依据XXXX系统的关键业务及功能使用的频繁程度,制定以下功能点为本次性能测试围,以及对应需2.性能测试策略2.1方法使用性能测试工具编写特定的测试脚本,使用多用户并发,模拟对XXXXX系统相关功能进行持续并发访问操作,并记录系统的响应时间等相关信息,以及应用服务器、数据库服务器资源使用情况。

2.2流程系统性能测试围及指标分析->制定测试场景->编写测试脚本->准备测试数据->准备测试环境->执行测试场景->收集测试结果数据->测试结果分析->测试报告输出。

2.3工具2.3.1性能测试工具✧脚本准备:Loadrunner11;✧场景执行:Loadrunner11;✧资源监控:nmon、nmon analyser,适用于应用服务器及数据库服务器。

高级数字IC设计

同步

“同步”:两个触发器简单的组合在一起如图所 示。

如果遇到触发器的setup time和hold time,这将是cell 设计者保证输入能够正确变为输出的时间。亚稳态影 响物理系统的时间分辨率,同样也影响输出值。

在理论上,当取样操作接近被取样事件的时候,时间 分辨率是无限的渐进曲线。

MTBF(平均无故障时间)与可靠性

如果一个设计中包含同步组件,无论是否愿意它都会 出现亚稳态。亚稳态无法彻底消除,因此我们所做的 就是计算错误概率以及在时间上来描述它。

亚稳态

亚稳态:是指触发器无法在某个规定时间段内达到一个可 确认的状态。

当一个触发器进入亚稳态时,既无法预测该单元的输出电平,也 无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期 间,触发器输出一些中间级电平,或者可能处于振荡状态,并且 这种无用的输出电平可以沿信号通道上的各个触发器级联式传播 下去。

亚稳态发生的原因 在 同 步 系 统中 , 如 果触发器 的 setup time / hold time不满足,就可能产生亚稳态,此时触发器输出端 Q在有效时钟沿之后比较长的一段时间处于不确定的状 态,在这段时间里Q端毛刺、振荡、固定的某一电压值, 而不是等于数据输入端D的值。这段之间成为决断时间 (亚稳态到稳定稳态的时间)(resolution time)。 经过resolution time之后Q端将稳定到0或1上,但是 究竟是0还是1,这是随机的,与输入没有必然的关系。

TI推出可优化13W以下设计方案的以

TI推出可优化13W以下设计方案的以

TI推出可优化13W以下设计方案的以太网供电控制器

2008 年7 月25日,北京讯

日前,德州仪器(TI) 宣布推出一款具备板上DC/DC 转换器的13 W 以太网供电型(PoE) 设备控制器,为满足IEEE 802.3af 标准兼容型应用的需求而专门设计,从而进一步壮大了公司的PoE 控制器产品阵营。

高度集成的最新器件可显着简化PoE 应用的系统设计并缩小解决方案尺寸,能够满足IP 电话、IP 监控摄像机、无线接入点设备、安全卡读卡器以及RFID 扫描仪等应用的需求。

更多详情,敬请访问:

focus.TI/cn/docs/prod/folders/print/tps23753.html。

TPS23753 专为隔离式DC/DC 交换拓扑而精心优化,其中包括反向拓扑(flyback topology)。

在以太网供电不可用的情况,TPS23753 也能工作在各种不同的本地电源上。

该器件的工作电压介于12 V~57 V 之间,最低工作电压甚至可达9.5 V,以确保任何12V本地电源电压下降时也能正常工作。

DC/DC 转换器在上述电压范围内工作时的占空比为80% 并支持电流斜坡补偿,从而可降低12V 适配器的输出整流器压力。

为了简化本地电源的设计工作,TPS23753 采用适配器优先级编程技术,使设计人员能在PoE 和本地电源均可用时选择使用的电源。

针对这种优先级的本地供电支持不仅能够显着简化设计工作,而且避免了采用外接组件的麻烦,从而有助于缩小系统尺寸。

TPS23757PW;TPS23757PWR;TPS23757EVM;中文规格书,Datasheet资料

F r o m E t h e r n e t F r o m E t h e r n e t TPS23757SLVS948C –JULY 2009–REVISED JUNE 2012High Efficiency PoE Interface and DC/DC ControllerThe TPS23757supports a number of input voltage FEATURESORing options including highest voltage,external •Powers up to 13W (Input)PDsadapter preference,and PoE preference.•Legacy and IEEE 802.3at Type 1PDsThe TPS23757has an output flag indicating if an •Optimized for Isolated DC/DC Converters external wall adapter is active when used in •Supports High-Efficiency Topologies conjunction with ORing controls.The detection signature pin can also be used to force power from •Complete PoE Interface the PoE source off.Classification can be •Adapter ORing Supportprogrammed to any of the defined types with a single •Programmable Frequency with Synch.resistor.•Robust 100V,0.5ΩHotswap MOSFET The dc/dc controller features two complementary gate •Pin Compatible with TPS23754/6drivers with programmable dead time.This simplifies design of highly-efficient flyback topologies or active-•–40°C to 125°C Junction Temperature Range clamp forward or flyback converters.The second gate •Industry Standard TSSOP-20driver may be disabled if desired for single MOSFET topologies.The controller also features internal APPLICATIONSsoftstart,bootstrap startup source,current-mode compensation,and a 78%maximum duty cycle.A •IEEE 802.3at Type 1Compliant Devices programmable and synchronizable oscillator allows •Video and VoIP Telephones design optimization for efficiency and eases use of •Access Points the controller to upgrade existing power supply designs.Accurate programmable blanking,with a •Security Camerasdefault period,simplifies the usual current-sense filter design trade-offs.DESCRIPTIONThe TPS23757is a combined Power over Ethernet The TPS23757has a 9V converter startup,(PoE)powered device (PD)interface and current-permitting operation with 12V wall adapters.mode dc/dc controller optimized specifically for isolated converters.The PoE interface supports the IEEE 802.3at standard for a type 1PD,which is equivalent to the 13W standard of IEEE 802.3-2008.Figure 1.High Efficiency Converter Using TPS23757Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.TPS23757SLVS948C–JULY2009–REVISED This integrated circuit can be damaged by ESD.Texas Instruments recommends that all integrated circuits be handled with appropriate precautions.Failure to observe proper handling and installation procedures can cause damage.ESD damage can range from subtle performance degradation to complete device failure.Precision integrated circuits may be more susceptible to damage because very small parametric changes could cause the device not to meet its published specifications.PRODUCT INFORMATION(1)POE UVLO CONVERTER UVLO PoE CurrentDUTYSTATUS ON/HYST.ON/HYST.Limit PACKAGE MARKINGCYCLE(V)(V)(mA)TPS23757PW Preview0–78%35/4.59/3.5465TSSOP-20TPS23757 (1)For the most current package and ordering information,see the Package Option Addendum at the end of this document,or see the TIweb site at .ABSOLUTE MAXIMUM RATINGS(1)(2)Voltage with respect to V SS unless otherwise noted.MIN MAX UNITARTN(2),COM(2),DEN,PPD,RTN(3),–0.3100VV DD,V DD1CLS(4)-0.3 6.5V[APD,BLNK(4),CTL,DT(4),FRS(4),–0.3 6.5VVB(4)]to[ARTN,COM]Input voltageCS to[ARTN,COM]–0.3V B V[ARTN,COM]to RTN–22VV C,APb,to[ARTN,COM]–0.319VGATE(4),GAT2(4)to[ARTN,COM]–0.3V C+0.3VSinking current RTN Internally limited mA Sourcing current V B Internally limited mA Average Sourcing or sinking current GATE,GAT225mArmsHuman Body Model(HBM)2kV Electrostatic Discharge Charge Device Model(CDM)500VSystem level(contact/air)at RJ-45(5)8/15kV Operating junction temperature range T J–40Internally limited°C(1)Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.These are stress ratingsonly and functional operation of the device at these or any other conditions beyond those indicated under recommended operating conditions is not implied.Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.(2)ARTN and COM typically tied to RTN.(3)I RTN=0for V RTN>80V.(4)Do not apply voltage to these pins(5)ESD per EN61000-4-2.A power supply containing the TPS23757was subjected to the highest test levels in the standard.See the ESDsection.TPS23757 SLVS948C–JULY2009–REVISED JUNE2012RECOMMENDED OPERATING CONDITIONS(1)Voltage with respect to V SS(unless otherwise noted)MIN NOM MAX UNIT Input voltage range ARTN,COM,PPD,RTN,V DD,V DD1057VInput voltage range APb,V C to[ARTN,COM]018VV IInput voltage range APD,CTL to[ARTN,COM]0V B VInput voltage range CS to[ARTN,COM]02VI Continuous RTN current(T J≤125°C)(2)400mAI S Sourcing current,V B0 2.55mAC V B capacitance0.08μFR BLNK0350kΩSynchronization pulse width input(when used)25nsT J Operating junction temperature range–40125°C(1)ARTN and COM tied to RTN.(2)This is the minimum current-limit value.PDs should be designed for maximum currents below this value to provide for unit power-drawtolerance.IEEE802.3at type1and IEEE802.3-2008compliant devices should not draw average current greater than350mA,or their class power.DISSIPATION RATINGSΨJTθJAθJA PACKAGE°C/W(1)°C/W(2)°C/W(3) PWP(TSSOP-20)0.7/0.4513574(1)Thermal resistance junction to case top,low-k/high-k board,natural convection,T J=T TOP+(ΨJT x P J).UseΨJT to validate T J frommeasurements.(2)JEDEC method with low-k board(1signal layer),natural convection.(3)JEDEC method with high-k board(2signal–2plane layers).ELECTRICAL CHARACTERISTICSUnless otherwise noted:CS=COM=APD=CTL=RTN=ARTN,GATE and GAT2float,R FRS=68.1kΩ,R BLNK=249kΩ,DT=V B, PPD=V SS,APb open,C VB=C VC=0.1μF,R DEN=24.9kΩ,R CLS open,0V≤(V DD,V DD1)≤57V,0V≤V C≤18V,–40°C≤T J≤125°C.Typical specifications are at25°C.CONTROLLER SECTION ONLY[V SS=RTN and V DD=V DD1]or[V SS=RTN=V DD],all voltages referred to[ARTN,COM](unless otherwise noted).PARAMETER TEST CONDITIONS MIN TYP MAX UNIT V CV CUV V C rising8.799.3 UVLO VV CUVH Hysteresis(1) 3.3 3.5 3.7 Operating current V C=12V,CTL=V B,R DT=68.1kΩ0.70.92 1.2mAV DD1=10.2V,V C(0)=0V5085175 Bootstrap startup time,t ST msC VC=22μF V=35V,V C(0)=0V274592DD1V DD1=10.2V,V C=8.6V0.44 1.06 1.80 Startup current source-I VC mAV DD1=48V,V C=0V 2.7 4.8 6.8V BVoltage 6.5V≤V C≤18V,0≤I VB≤5mA 4.8 5.10 5.25V (1)The hysteresis tolerance tracks the rising threshold for a given device.TPS23757SLVS948C–JULY2009–REVISED PARAMETER TEST CONDITIONS MIN TYP MAX UNIT FRSSwitching frequency CTL=V B,measure GATE,R FRS=68.1kΩ227253278kHz D MAX Duty cycle CTL=V B,measure GATE767880%V SYNC Synchronization Input threshold2 2.2 2.4V CTLV ZDC0%duty cycle threshold V CTL↓until GATE stops 1.3 1.5 1.7V Softstart period Interval from switching start to V CSMAX 1.9 3.9 6.2msInput resistance70100145kΩBLNKBLNK=RTN355578 Blanking delayns (In addition to t1)R=49.9kΩ385570BLNKDTCTL=V B,C GATE=1nF,C GAT2=1nF,measure GATE,GAT2t DT1R DT=24.9kΩ,GAT2↑to GATE↑405062.5 Dead timenst DT2See Figure2for t DTx definition R DT=24.9kΩ,GATE↓to GAT2↓405062.5t DT1R DT=75kΩ,GAT2↑to GATE↑120150188t DT2R DT=75kΩ,GATE↓to GAT2↓120150188CSV CSMAX Maximum threshold voltage V CTL=V B,V CS rising until GATE duty cycle drops0.50.550.6Vt1Turnoff delay V CS=0.65V244070nsInternal slope compensationV SLOPE Peak voltage at maximum duty cycle,referenced to CS120155185mV voltagePeak slope compensationI SL_EX V CTL=V B,I CS at maximum duty cycle304254μAcurrentBias current(sourcing)DC component of I CS1 2.5 4.3μA GATESource current V CTL=V B,V C=12V,GATE high,pulsed measurement0.370.60.95ASink current V CTL=V B,V C=12V,GATE low,pulsed measurement0.7 1.0 1.4A GAT2V CTL=V B,V C=12V,GAT2high,R DT=24.9kΩ,pulsedSource current0.370.60.95AmeasurementV CTL=V B,V C=12V,GAT2low,R DT=24.9kΩ,pulsedSink current0.7 1.0 1.4AmeasurementAPD/PPDV APDEN V APD rising 1.43 1.5 1.57 APD threshold voltage VV APDH Hysteresis(2)0.290.310.33V PPDEN V PPD-V VSS rising,UVLO disable 1.45 1.55 1.65VV PPDH Hysteresis(2)0.290.310.33 PPD threshold voltageV PPD2V PPD-V VSS rising,Class enable7.48.39.2VV PPD2H Hysteresis(2)0.50.60.7APD leakage currentV C=12V,V APD=V B1μA (source or sink)I PPD PPD sink current V PPD-V VSS=1.5V 2.557.5μA THERMAL SHUTDOWNTurnoff temperature T J rising135145155°CHysteresis(3)20°C(2)The hysteresis tolerance tracks the rising threshold for a given device.(3)These parameters are provided for reference only,and do not constitute part of TI's published specifications for purposes of TI's productwarranty.DT1G A T EG A T 2DT2TPS23757SLVS948C –JULY 2009–REVISED JUNE 2012ELECTRICAL CHARACTERISTICS –PoE AND CONTROL[V DD =V DD1]or [V DD1=RTN],V C =RTN,COM =RTN =ARTN,all voltages referred to V SS unless otherwise notedPARAMETERTEST CONDITIONSMINTYP MAXUNITDETECTION (DEN)(V DD =V DD1=RTN =V SUPPLY positive)Measure I SUPPLY Detection current V DD =1.6V 6264.366.5μA V DD =10V399406414Detection bias currentV DD =10V,float DEN,measure I SUPPLY5.610μA V PD_DISHotswap disable threshold 345V DEN leakage currentV DEN =V DD =57V,float V DD1and RTN,measure I DEN 0.15μACLASSIFICATION (CLS)(V DD =V DD1=RTN =V SUPPLY positive)13V ≤V DD ≤21V,Measure I SUPPLY R CLS =1270Ω1.82.1 2.4R CLS =243Ω9.910.410.9Classification current,I CLSmAapplies to both cyclesR CLS =137Ω17.618.519.4R CLS =90.9Ω26.527.729.3R CLS =63.4Ω38.039.742V CL_ON Regulator turns on,V DD rising 11.211.912.6Classification regulator lower V thresholdV CL_H Hysteresis (1)1.55 1.65 1.75V CU_OFF Regulator turns off,V DD rising 212223Classification regulator upper V threshold V CU_HHysteresis (1)0.50.751.0Leakage currentV DD =57V,V CLS =0V,DEN =V SS ,measure I CLS 1μA PASS DEVICE (RTN)(V DD1=RTN)On resistance 0.250.430.8ΩCurrent limit V RTN =1.5V,V DD =48V,pulsed measurement 400465535mA Inrush limitV RTN =2V,V DD :0V →48V,pulsed measurement 100140180mA Foldback voltage thresholdV DD rising1112.313.6VUVLO UVLO_R V DD rising 33.93536.1UVLO thresholdVUVLO_H Hysteresis (1)4.44.554.76APbV C =12V,float V DD1,V DD =48V,ARTN =V SS ON characteristic V APD =2V,CTL =ARTN,(V APb -V ARTN )=0.6V 2mA Leakage currentV APb =18V,(V APD -V ARTN )=0V,(V PPD -V VSS )=0V 10μA t APbDelayFrom start of switching to APb active5915msTHERMAL SHUTDOWNTurnoff temperature T J rising135145155°C Hysteresis (2)20°C(1)The hysteresis tolerance tracks the rising threshold for a given device.(2)These parameters are provided for reference only,and do not constitute part of TI's published specifications for purposes of TI's product warranty.Figure 2.GATE and GAT2Timing and PhasingDD GATERTN V C CS V SSV B CTL GAT2ARTN COM DD1GATE V DD1V CV BCTLFRS V DDV SSRTNAPDDENPPDGAT 2DT COM ARTN BLNK CSTPS23757SLVS948C –JULY 2009–REVISED JUNE 2012DEVICE INFORMATIONFUNCTIONAL BLOCK DIAGRAMPWP PACKAGE (TOP VIEW)()()APD1APD2ADPTR_ONAPDENAPDENAPD1APD2ADPTR_OFF APDENAPDH APD2R =R V V V R +R V =V V R ´-´-TPS23757SLVS948C –JULY 2009–REVISED JUNE 2012PIN FUNCTIONSNAME NO.TYPE DESCRIPTIONCTL 1I The control loop input to the PWM (pulse width modulator),typically driven by output regulation feedback (e.g.optocoupler).Use V B as a pullup for CTL.V B 2O 5.1V bias rail for dc/dc control circuits and the feedback optocoupler.Typically bypass with a 0.1μF to ARTN.CS 3I/ODC/DC converter switching MOSFET current sense input.See R CS in Figure 4Gate driver return,connect to ARTN,and RTN for most applications.GATE 5O Gate drive output for the main dc/dc converter switching MOSFET.V C 6I/O DC/DC converter bias voltage.Connect a 0.47μF (minimum)ceramic capacitor to ARTN at the pin,and a larger capacitor to power startup.GAT27O Gate drive output for a second dc/dc converter switching MOSFET (see Figure 1).ARTN 8ARTN is the dc/dc converter analog return.Tie to COM,and RTN for most applications.RTN 9RTN is the output of the PoE hotswap MOSFET.V SS 10Connect to the negative power rail derived from the PoE source.V DD111I Source of dc/dc converter startup current.Connect to V DD for many applications.V DD 12I Connect to the positive PoE input power rail.V DD powers the PoE interface circuits.Bypass with a 0.1μF capacitor and protect with a TVS.DEN 13I/O Connect a 24.9k Ωresistor from DEN to V DD to provide the PoE detection signature.Pulling this pin to V SS during powered operation causes the internal hotswap MOSFET to turn off.PPD 14I Raising V PPD -V VSS above 1.55V enables the hotswap MOSFET and activates APb.Connecting PPD to V DD enables classification when APD is active.Tie PPD to V SS or float when not used.CLS 15I Connect a resistor from CLS to V SS to program classification current per Table 1.DT 16I Connect a resistor from DT to ARTN to set the GATE to GAT2dead time.Tie DT to V B to disable GAT2operation.APD 17I Raising V APD -V ARTN above 1.5V disables the internal hotswap MOSFET,turns class off,and forces APb active.This forces power to come from a external V DD1-V RTN adapter.Tie APD to ARTN when not used.BLNK 18I Connect to ARTN to utilize the internally set current-sense blanking period,or connect a resistor from BLNK to ARTN to program a more accurate period.FRS 19I Connect a resistor from FRS to ARTN to program the converter switching frequency.FRS may be used to synchronize the converter to an external timing source.APb20O Active low output that indicates PPD (first level)or APD are active.PIN DESCRIPTIONSee Figure 1for component reference designators (R CS for example),and the Electrical Characteristics table for values denoted by reference (V CSMAX for example).Electrical Characteristic values take precedence over any numerical values used in the following sections.APDAPD (adapter priority detect)forces power to come from an external adapter connected from V DD1to RTN by opening the hotswap switch,disabling the CLS output (see PPD pin description),and enabling the APb output.A resistor divider is recommended on APD when it is connected to an external adapter.The divider provides ESD protection,leakage discharge for the adapter ORing diode,and input voltage qualification.Voltage qualification assures the adapter output voltage is high enough that it can support the PD before the PoE current is cut off.Select the APD divider resistors per Equation 1where V ADPTR-ON is the desired adapter voltage that enables the APD function as adapter voltage rises.(1)Place the APD pull-down resistor adjacent to the APD pin.APD should be tied to ARTN when not used.()()BLNK BLNK R k =t ns W TPS23757SLVS948C –JULY 2009–REVISED JUNE 2012BLNKBlanking provides an interval between GATE going high and the current-control comparators on CS actively monitoring the input.This delay allows the normal turn-on current transient (spike)to subside before the comparators are active,preventing undesired short duty cycles and premature current limiting.Connect BLNK to ARTN to obtain the internally set blanking period.Connect a resistor from BLNK to ARTN for a more accurate,programmable blanking period.The relationship between the desired blanking period and the programming resistor is defined by Equation 2.(2)Place the resistor adjacent to the BLNK pin when it is used.CLSA resistor from CLS (class)to V SS programs the classification current per the IEEE standard.The PD power ranges and corresponding resistor values are listed in Table 1.The power assigned should correspond to the maximum average power drawn by the PD during operation.Table 1.Class Resistor SelectionPOWER AT PDRESISTORCLASS NOTESMINIMUM MAXIMUM(Ω)(W)(W)00.4412.951270Minimum may be reduced by pulsed loading.Serves as a catch-all default class.10.44 3.842432 3.84 6.491373 6.4912.9590.9412.9525.563.4Not allowed prior to IEEE 802.3at.Maximum type 2hardware class current levels not supported by TPS23757.CSThe CS (current sense)input for the dc/dc converter should be connected to the high side of the switching MOSFET’s current sense resistor (R CS ).The current-limit threshold,V CSMAX ,defines the voltage on CS above which the GATE ON time will be terminated regardless of the voltage on CTL.The TPS23757provides internal slope compensation (155mV,V SLOPE ),an output current for additional slope compensation,a peak current limiter,and an off-time pull-down to this pin.Routing between the current-sense resistor and the CS pin should be short to minimize cross-talk from noisy traces such as the gate drive signal.CTLCTL (control)is the voltage-control loop input to the PWM (pulse width modulator).Pulling V CTL below V ZDC (zero duty cycle voltage)causes GATE to stop switching.Increasing V CTL above V ZDC raises the switching MOSFET programmed peak current.The maximum (peak)current is requested at approximately V ZDC +(2×V CSMAX ).The ac gain from CTL to the PWM comparator is 0.5.The internal divider from CTL to ARTN is approximately 100k Ω.Use V B as a pull up source for CTL.DENDEN (detection and enable)is a multifunction pin for PoE detection and inhibiting operation from PoE power.Connect a 24.9k Ωresistor from DEN to V DD to provide the PoE detection signature.DEN goes to a high-impedance state when V VDD -V VSS is outside of the detection range.Pulling DEN to V SS during powered operation causes the internal hotswap MOSFET and class regulator to turn OFF,while the reduced detection resistance prevents the PD from properly re-detecting.See Using DEN to Disable PoE .()()ADPTR_ON PPDEN PPD1PPDENPPDPPD2PP DEN PPDH ADP TR_OFF PPDEN PPDH P PD1PP D PPD2V V R =V I R V V V =V V +R I R æöç÷-ç÷ç÷-ç÷èøéùæö-êú-´-ç÷ç÷êúèøëûFRS SW 17250R (k )=f (kHz)W ()()DT DT t ns R k =2W TPS23757SLVS948C –JULY 2009–REVISED JUNE 2012DTDead-time programming sets the delay between GATE and GAT2to prevent overlap of MOSFET ON times as shown in Figure 2.GAT2turns the second MOSFET OFF when it transitions high.Both MOSFETs should be OFF between GAT2going high to GATE going high,and GATE going low to GAT2going low.The maximum GATE ON time is reduced by the programmed dead-time period.The dead time period is specified with 1nF of capacitance on GATE and GAT2.Different loading on these pins will change the effective dead time.A resistor connected from DT to ARTN sets the delay between GATE and GAT2per Equation 3.(3)Connect DT to V B to set the dead time to 0and turn GAT2OFF.FRSConnect a resistor from FRS (frequency and synchronization)to ARTN to program the converter switching frequency.Select the resistor per the following relationship.(4)The converter may be synchronized to a frequency above its maximum free-running frequency by applying short ac-coupled pulses into the FRS pin per Figure 25.The FRS pin is high impedance.Keep the connections short and apart from potential noise sources.Special care should be taken to avoid crosstalk when synchronizing circuits are used.GATEGate drive output for the dc/dc converter’s main switching MOSFET.GATE’s phase turns the main switch ON when it transitions high,and OFF when it transitions low.GATE is held low when the converter is disabled.GAT2GAT2is the second gate drive output for the dc/dc converter.GAT2’s phase turns the second switch OFF when it transitions high,and ON when it transitions low.This drives flyback synchronous rectifiers per Figure 1.See the DT Pin Description for GATE to GAT2timing.Connecting DT to V B disables GAT2in a high-impedance condition.GAT2is low when the converter is disabled.PPDPPD is a multifunction pin that has two voltage thresholds,PPD1and PPD2.PPD1permits power to come from an external low voltage adapter,e.g.,24V,connected from V DD to V SS by over-riding the normal hotswap UVLO.Voltage on PPD above 1.55V (V PPDEN )enables the hotswap MOSFET,inhibits class current,and enables APb.A resistor divider per Figure 30provides ESD protection,leakage discharge for the adapter ORing diode,reverse adapter protection,and input voltage qualification.Voltage qualification assures the adapter output voltage is high enough that it can support the PD before it begins to draw current.(5)PPD2enables normal class regulator operation when V PPD is above 8.3V to permit normal classification whenAPD is used in conjunction with diode D VDD (see Figure 29).Tie PPD to V DD when PPD2operation is desired.TPS23757SLVS948C–JULY2009–REVISED The PPD pin has a5μA internal pull-down current.Locate the PPD pull-down resistor adjacent to the pin when used.PPD may be tied to V SS or left open when not used.RTN,ARTN,COMRTN is internally connected to the drain of the PoE hotswap MOSFET,while ARTN is the quiet analog return for the dc/dc serves as the return path for the gate drivers and should be tied to ARTN on the circuit board.The ARTN/COM/RTN net should be treated as a local reference plane(ground plane)for the dc/dc control and converter primary.RTN and(ARTN/COM)may be separated by several volts for special applications. APbAPb is an active low output that indicates[(V APD>1.5V)OR(1.55V≤V PPD≤8.3V)].APb is valid after both a delay of t APb from the start of converter switching,and[V CTL≤(V B–1V)].Once APb is valid,V CTL will not effect it.APb will become invalid if the converter goes back into softstart,overtemperature,or is held off by the PD during C IN recharge(inrush).APb is referenced to ARTN and is intended to drive the diode side of an optocoupler.APb should be left open or tied to ARTN if not used.V BV B is an internal5.1V regulated dc/dc controller supply rail that is typically bypassed by a0.1μF capacitor to ARTN.V B should be used to bias the feedback optocoupler.V CV C is the bias supply for the dc/dc controller.The MOSFET gate drivers run directly from V C.V B is regulated down from V C,and is the bias voltage for the rest of the converter control.A startup current source from V DD1to V C is controlled by a comparator with hysteresis to implement the converter bootstrap startup.V C must be connected to a bias source,such as a converter auxiliary output,during normal operation.A minimum0.47μF capacitor,located adjacent to the V C pin,should be connected from V C to COM to bypass the gate driver.A larger total capacitance is required for startup to provide control power between the time the converter starts switching and the availability of the converter auxiliary output voltage.V DDV DD is the positive input power rail that is derived from the PoE source(PSE).V DD should be bypassed to V SS with a0.1μF capacitor as required by the IEEE standard.A transient suppressor diode(TVS),such as SMAJ58A should be connected from V DD to V SS to protect against overvoltage transients.V DD1V DD1is the dc/dc converter startup supply.Connect to V DD for many applications.V DD1may be isolated by a diode from V DD to support PoE priority operation.V SSV SS is the PoE input-power return side.It is the reference for the PoE interface circuits,and has a current-limited hotswap switch that connects it to RTN.V SS is clamped to a diode drop above RTN by the hotswap switch.A local V SS reference plane should be used to connect the input bypass capacitor,TVS,and R CLS.分销商库存信息:TITPS23757PW TPS23757PWR TPS23757EVM。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

User's GuideSLVU304–April2009This User’s Guide describes the TPS23754EVM(TPS23754EVM-383).TPS23754EVM-383contains evaluation and reference circuitry for the TPS23754.The TPS23754is an IEEE802.3at compliant powered device(PD)controller and power supply controller optimized for isolated converter topologies.TPS23754EVM-383is targeted at25W,active clamp,forward converter applications.Contents1Description (2)1.1Features (2)1.2Applications (2)2Electrical Specifications (2)3Schematic (3)4General Configuration and Description (4)4.1Physcial Access (4)5Test Setup (5)6TPS23754EVM-383Typical Performance Data (5)6.112V DC/DC Efficiency (5)7EVM Assembly Drawings and Layout Guidelines (6)7.1PCB Drawings (6)7.2Layout Guidelines (7)7.3EMI Containment (8)8Bill of Materials (9)List of Figures1TPS23754EVM-383Schematic (3)2Typical TPS23754EVM-383Test Setup (5)3TPS23754EVM-383Efficiency With12V Output (5)4Top Side Layout/Routing (6)5Layer Two Routing (6)6Layer Three Routing (7)7Bottom SIde Placement/Routing (7)List of Tables1TPS23754EVM-383Electrical and Performance Specifications (2)2Connector Functionality (4)3Test Points (4)4TPS23754EVM-383Bill of Materials (9)SLVU304–April2009TPS23754EVM-383EVM:Evaluation Module for TPS237541 Submit Documentation Feedback1Description1.1Features1.2Applications2Electrical SpecificationsDescription TPS23754EVM-383will allow reference circuitry evaluation of the TPS23754.It contains input and output power connectors and an arraytest points for circuit evaluation.A synchronous flyback,5V,25W EVM is also available,see •Efficient,general market design–Self driven,synchronous rectified secondary–25w output power from power over ethernet (POE),30W output power from a 48V adapter –Operates from either POE or external adaptors (48V)–12V output voltage•Voice over Internet Protocol –IP telephones •Wireless LAN –Wireless Access Points •Security –Wired IP camerasTable 1.TPS23754EVM-383Electrical and Performance SpecificationsParameterConditionMinTypMaxUnitsPower Interface Input voltage Applied to the power pins of connectors J1or J3057V Operating Voltage After start up 3057V Rising input voltage 36Input UVLO V Falling input voltage 30Detection voltage At device terminals 1.610V Classification voltage At device terminals 1023V Classification current Rclass =63.4Ω3644mA Inrush current-limit 100180mA Operating current-limit 8501100mADC/DC Converter Output voltage 33V ≤Vin ≤57V,ILOAD ≤ILOAD (max)12V output V Output current 33V ≤Vin ≤57V 12V output 2.5Amps Output ripple voltage,peak-to-peak Vin =44V,ILOAD =2.5A12V output 100mVEfficiency,end-to-end Vin =44V,ILOAD =2.5A12V output87%Switching frequency225275kHz2TPS23754EVM-383EVM:Evaluation Module for TPS23754SLVU304–April 2009Submit Documentation FeedbackGeneral Configuration and Description 4General Configuration and Description4.1Physcial AccessTable2lists the TPS23754EVM-383connector functionality and Table3describes the test pointTable2.Connector FunctionalityConnector Label DescriptionJ1ADAPTER External adapter input.J7(low side)and J8(high side)can select weather the adapter is atthe PD controller input(VDD to VSS)or at the converter input(VDD1to RTN).J6is usedto select PPD or APD function.J2VOUT Output voltage connectorJ3DATA+PoE POWER Ethernet power input connector.Contains Ethernet transformer and cable terminationsJ4DATA PORT Ethernet data port connectorJ5EGND Earth GND connectionTable3.Test PointsTest Point Color Label DescriptionTP3,TP17,TP18BLK GND Secondary side(output)grounds(GND)TP5RED VC DC/DC converter bias supplyTP6ORG DRAIN Drain terminal of the primary side switching MOSFETTP10BLK VSS POE input,low sideTP12,TP16BLK RTN DC/DC converter returnTP14ORG LOOP Can be used with TP13for overall feedback loop measurements.TP13RED VOUT DC/DC converter output voltage.TP15WHT CTL Control loop input to the pulse width modulatorTP9WHT RCS DC/DC converter primary side switching MOSFET current sense(resistor side).TP11RED VB Bias voltage regulatorTP8WHT GATE Gate drive for the primary side switching MOSFETTP7WHT GAT2Gate drive for the primary side active clamp MOSFETTP4RED PVDD1Transformer primary high side.TP23WHT T2P Type2PSE output from TPS23754TP1WHT PPD Connected to PPD pin of TPS23754TP2WHT APD Connected to APD pin of TPS23754TP20RED P78Pair7,8TP21ORG P12Pair1,2TP19ORG P45Pair4,5TP22RED P36Pair3,6D21GRN T2P Type2PSE indicator.Remove the shunt on J9to inhibit the T2P indicator.D12RED POWER ON Output power indicator.Remove the shunt on J10to inhibit the output powerindicator.Provides a connection between VDD and VDD1shorting out D3.Removing the short CL1N/A CL1at CL1allows certain power source priority schemes to be tested.4TPS23754EVM-383EVM:Evaluation Module for TPS23754SLVU304–April2009Submit Documentation Feedback5Test SetupAUX 6TPS23754EVM-383Typical Performance Data 6.112V DC/DCEfficiency50556065707580859095I - Output Current -AO E f f i c i e n c y - % Test SetupFigure 2shows a typical test setup for TPS23754EVM-383.Input voltage can be applied as described in Table 2.Figure 2.Typical TPS23754EVM-383Test SetupFigure 3illustrates three different 48VDC input efficiency plots:1.PoE,48V from J32.Converter only 48V 3.Adapter 48V from J1Figure 3.TPS23754EVM-383Efficiency With 12V OutputSLVU304–April 2009TPS23754EVM-383EVM:Evaluation Module for TPS237545Submit Documentation Feedback7EVM Assembly Drawings and Layout Guidelines 7.1PCBDrawingsEVM Assembly Drawings and Layout Guidelines The following figure shows component placement and layout.Figure 4.Top Side Layout/RoutingFigure yer Two Routing6TPS23754EVM-383EVM:Evaluation Module for TPS23754SLVU304–April 2009Submit Documentation Feedback7.2Layout Guidelines EVM Assembly Drawings and Layout GuidelinesFigure yer Three RoutingFigure 7.Bottom SIde Placement/RoutingThe layout of the PoE front end should follow power and EMI/ESD best practice guidelines.A basic set of recommendations include:•Parts placement must be driven by power flow in a point-to-point manner;RJ-45,Ethernet transformer,diode bridges,TVS and 0.1-µF capacitor,and TPS23754converter input bulk capacitor.•All leads should be as short as possible with wide power traces and paired signal and return.•There should not be any crossovers of signals from one part of the flow to another.•Spacing consistent with safety standards like IEC60950must be observed between the 48-V input voltage rails and between the input and an isolated converter output.SLVU304–April 2009TPS23754EVM-383EVM:Evaluation Module for TPS237547Submit Documentation Feedback7.3EMI ContainmentEVM Assembly Drawings and Layout Guidelines •The TPS23754should be located over split,local ground planes referenced to VSS for the PoE input and to RTN for the converter.Whereas the PoE side may operate without a ground plane,the converter side must have one.Logic ground and power layers should not be present under the Ethernet input or the converter primary side.•Large copper fills and traces should be used on SMT power-dissipating devices,and wide traces or overlay copper fills should be used in the power path.The DC/DC Converter layout can benefit from basic rules such as:•Pair signals to reduce emissions and noise,especially the paths that carry high-current pulses which include the power semiconductors and magnetics.•Minimize trace length of high current,power semiconductors,and magnetic components.•Where possible,use vertical pairing.•Use the ground plane for the switching currents carefully.•Keep the high-current and high-voltage switching away from low-level sensing circuits including those outside the power supply.•Pay special attention to spacing around the high-voltage sections of the converter.•Use compact loops for dv/dt and di/dt circuit paths (power loops and gate drives)•Use minimal,yet thermally adequate,copper areas for heat sinking of components tied to switching nodes (minimize exposed radiating surface).•Use copper ground planes (possible stitching)and top layer copper floods (surround circuitry with ground floods)•Use 4layer PCB if economically feasible (for better grounding)•Minimize the amount of copper area associated with input traces (to minimize radiated pickup)•Hide copper associated with switching nodes under shielded magnetics where possible•Heat sink the “quiet side”of components instead of the “switching side”where possible (like the output side of inductor)•Use Bob Smith terminations,Bob Smith EFT capacitor,and Bob Smith plane•Use Bob Smith plane as ground shield on input side of PCB (creating a phantom or literal earth ground)•Use LC filter at DC/DC input•Dampen high frequency ringing on all switching nodes if present (allow for possible snubbers)•Control rise times with gate drive resistors and possibly snubbers •Switching frequency considerations•Use of EMI bridge capacitor across isolation boundary (isolated topologies)•Observe the polarity dot on inductors (embed noisy end)•Use of ferrite beads on input (allow for possible use of beads or 0ohm resistors)•Maintain physical separation between input-related circuitry and power circuitry (use ferrite beads as boundary line)•Balance efficiency vs.Acceptable noise margin •Possible use of common-mode inductors•Possible use of integrated RJ-45jacks (shielded with internal transformer and Bob Smith terminations)•End-product enclosure considerations (shielding)TPS23754EVM-383EVM:Evaluation Module for TPS237548SLVU304–April 2009Submit Documentation FeedbackEVALUATION BOARD/KIT IMPORTANT NOTICETexas Instruments(TI)provides the enclosed product(s)under the following conditions:This evaluation board/kit is intended for use for ENGINEERING DEVELOPMENT,DEMONSTRATION,OR EVALUATION PURPOSES ONLY and is not considered by TI to be a finished end-product fit for general consumer use.Persons handling the product(s)must have electronics training and observe good engineering practice standards.As such,the goods being provided are not intended to be complete in terms of required design-,marketing-,and/or manufacturing-related protective considerations,including product safety and environmental measures typically found in end products that incorporate such semiconductor components or circuit boards.This evaluation board/kit does not fall within the scope of the European Union directives regarding electromagnetic compatibility,restricted substances(RoHS),recycling (WEEE),FCC,CE or UL,and therefore may not meet the technical requirements of these directives or other related directives.Should this evaluation board/kit not meet the specifications indicated in the User’s Guide,the board/kit may be returned within30days from the date of delivery for a full refund.THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES,EXPRESSED,IMPLIED,OR STATUTORY,INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE.The user assumes all responsibility and liability for proper and safe handling of the goods.Further,the user indemnifies TI from all claims arising from the handling or use of the goods.Due to the open construction of the product,it is the user’s responsibility to take any and all appropriate precautions with regard to electrostatic discharge.EXCEPT TO THE EXTENT OF THE INDEMNITY SET FORTH ABOVE,NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT,SPECIAL,INCIDENTAL,OR CONSEQUENTIAL DAMAGES.TI currently deals with a variety of customers for products,and therefore our arrangement with the user is not exclusive.TI assumes no liability for applications assistance,customer product design,software performance,or infringement of patents or services described herein.Please read the User’s Guide and,specifically,the Warnings and Restrictions notice in the User’s Guide prior to handling the product.This notice contains important safety information about temperatures information on TI’s environmental and/or safety programs,please contact the TI application engineer or visitNo license is granted under any patent right or other intellectual property right of TI covering or relating to any machine,process,or combination in which such TI products or services might be or are used.FCC WarningThis evaluation board/kit is intended for use for ENGINEERING DEVELOPMENT,DEMONSTRATION,OR EVALUATION PURPOSES ONLY and is not considered by TI to be a finished end-product fit for general consumer use.It generates,uses,and can radiate radio frequency energy and has not been tested for compliance with the limits of computing devices pursuant to part15of FCC rules,which are designed to provide reasonable protection against radio frequency interference.Operation of this equipment in other environments may cause interference with radio communications,in which case the user at his own expense will be required to take whatever measures may be required to correct this interference.Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2009,Texas Instruments IncorporatedEVM WARNINGS AND RESTRICTIONSIt is important to operate this EVM within the input voltage range of0V to57V and the output voltage range of10V to15V.Exceeding the specified input range may cause unexpected operation and/or irreversible damage to the EVM.If there are questions concerning the input range,please contact a TI field representative prior to connecting the input power.Applying loads outside of the specified output range may result in unintended operation and/or possible permanent damage to the EVM. Please consult the EVM User's Guide prior to connecting any load to the EVM output.If there is uncertainty as to the load specification, please contact a TI field representative.During normal operation,some circuit components may have case temperatures greater than80°C.The EVM is designed to operate properly with certain components above80°C as long as the input and output ranges are maintained.These components include but are not limited to linear regulators,switching transistors,pass transistors,and current sense resistors.These types of devices can be identified using the EVM schematic located in the EVM User's Guide.When placing measurement probes near these devices during operation, please be aware that these devices may be very warm to the touch.Mailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2009,Texas Instruments IncorporatedIMPORTANT NOTICETexas Instruments Incorporated and its subsidiaries(TI)reserve the right to make corrections,modifications,enhancements,improvements, and other changes to its products and services at any time and to discontinue any product or service without notice.Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete.All products are sold subject to TI’s terms and conditions of sale supplied at the time of order acknowledgment.TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI’s standard warranty.Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty.Except where mandated by government requirements,testing of all parameters of each product is not necessarily performed.TI assumes no liability for applications assistance or customer product design.Customers are responsible for their products and applications using TI components.To minimize the risks associated with customer products and applications,customers should provide adequate design and operating safeguards.TI does not warrant or represent that any license,either express or implied,is granted under any TI patent right,copyright,mask work right, or other TI intellectual property right relating to any combination,machine,or process in which TI products or services are rmation published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement e of such information may require a license from a third party under the patents or other intellectual property of the third party,or a license from TI under the patents or other intellectual property of TI.Reproduction of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties,conditions,limitations,and notices.Reproduction of this information with alteration is an unfair and deceptive business practice.TI is not responsible or liable for such altered rmation of third parties may be subject to additional restrictions.Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice.TI is not responsible or liable for any such statements.TI products are not authorized for use in safety-critical applications(such as life support)where a failure of the TI product would reasonably be expected to cause severe personal injury or death,unless officers of the parties have executed an agreement specifically governing such use.Buyers represent that they have all necessary expertise in the safety and regulatory ramifications of their applications,and acknowledge and agree that they are solely responsible for all legal,regulatory and safety-related requirements concerning their products and any use of TI products in such safety-critical applications,notwithstanding any applications-related information or support that may be provided by TI.Further,Buyers must fully indemnify TI and its representatives against any damages arising out of the use of TI products in such safety-critical applications.TI products are neither designed nor intended for use in military/aerospace applications or environments unless the TI products are specifically designated by TI as military-grade or"enhanced plastic."Only products designated by TI as military-grade meet military specifications.Buyers acknowledge and agree that any such use of TI products which TI has not designated as military-grade is solely at the Buyer's risk,and that they are solely responsible for compliance with all legal and regulatory requirements in connection with such use. TI products are neither designed nor intended for use in automotive applications or environments unless the specific TI products are designated by TI as compliant with ISO/TS16949requirements.Buyers acknowledge and agree that,if they use any non-designated products in automotive applications,TI will not be responsible for any failure to meet such requirements.Following are URLs where you can obtain information on other Texas Instruments products and application solutions:Products ApplicationsAmplifiers AudioData Converters AutomotiveDLP®Products BroadbandDSP Digital ControlClocks and Timers MedicalInterface MilitaryLogic Optical NetworkingPower Mgmt SecurityMicrocontrollers TelephonyRFID Video&ImagingRF/IF and ZigBee®Solutions WirelessMailing Address:Texas Instruments,Post Office Box655303,Dallas,Texas75265Copyright©2009,Texas Instruments Incorporated。