POWER_MOSFET驱动技术

PowerMOS&IGBT&SCR器件结构、原理、参数介绍

CE结反向击穿电压V(br)ces

PNP管的集电极结的反偏耐压即为IGBT的CE结反向击穿电压V(br)ces 测试条件为Vge=0V,Vce大于0V,PNP管的集电结击穿时,取一定大小下的漏电流对 应的CE结所加电压即为V(br)ces。 通VDMOS一样,IGBT耐压也是主要通过增加N-漂移区的厚度和降低电阻率来提高的。

Cgd也称为密勒电容,给电路的输入和输出之间提 供了一个反馈路径,与电压有关,在器件开关过程 中起主导作用。

VDMOS 单元元胞电容示意

Cgd由两部分电容串联组成:Cgdox(栅氧电容)和 Cgdbulk(体电容)

VDMOS源漏CV曲线

VDMOS 寄生电容模型

10

VDMOS开关特性简述

Turn-on

6

导通电阻Ron(一)

导通电阻Ron是影响VDMOS器件特性的的 重要参数。除工艺参数外,它主要由元胞 排列、元胞个数和几何形状及其芯片面积 等因数决定。VDMOS器件的单个元胞导通 电阻Ron(cell)主要由六个部分组成,如图所 示:

导通电阻R

硅极限(silicon limit)

PT、NPT、FS关系示意

16

CE结饱和压降Vce(sat)

不同于VDMOS,当沟道开启时,在漏端施加正电压即有漏极电流,IGBT由于背面正偏 PN结的存在,如果Vce小于0.7V,即使栅极信号使得MOS沟道形成,集电极电流Ic也无 法流通。 一般取栅极电压Vge=15V,给定集电极电流Ic的值,此时的CE结压降即为CE结饱和压 降Vce(sat)。

IGBT元胞结构

IGBT等效电路

12

IGBT发展

MOSFET的驱动保护电路设计

摘要:率场效应晶体管由于具有诸多优点而得到广泛的应用;但它承受短时过载的能力较弱,使其应用受到一定的限制。

分析了二极管器件驱动与保护电路的设计要求;计算了MOSFET驱动器的功耗及MOSFET驱动器与MOSFET的匹配;设计了基于IR2130驱动模块的MOSFET驱动保护电路。

该电路具有结构简单,实用性强,响应速度快等特点。

在驱动无刷直流电机的应用中证明,该电路驱动能力及保护功能效果良好。

功率场效应晶体管(Power MOSFET)是一种多数载流子导电的单极型电压控制器件,具有开关速度快、高频性能好、输入阻抗高、噪声小、驱动功率小、动态范围大、无二次击穿现象和安全工作区域(SOA)宽等优点,因此,在高性能的开关电源、斩波电源及电机控制的各种交流变频电源中获得越来越多的应用。

但相比于绝缘栅双极型晶体管IGBT或大功率双极型晶体管GTR等,MOSFET管具有较弱的承受短时过载能力,因而其实际使用受到一定的限制。

如何设计出可靠和合理的驱动与保护电路,对于充分发挥MOSFET 功率管的优点,起着至关重要的作用,也是有效利用MOSFET管的前提和关键。

文中用IR2130驱动模块为核心,设计了功率MOSFET驱动保护电路应用与无刷直流电机控制系统中,同时也阐述了本电路各个部分的设计要求。

该设计使系统功率驱动部分的可靠性大大的提高。

1 功率MOSFET保护电路设计功率场效应管自身拥有众多优点,但是MOSFET管具有较脆弱的承受短时过载能力,特别是在高频的应用场合,所以在应用功率MOSFET对必须为其设计合理的保护电路来提高器件的可靠性。

功率MOSFET保护电路主要有以下几个方面:1)防止栅极 di/dt过高:由于采用驱动芯片,其输出阻抗较低,直接驱动功率管会引起驱动的功率管快速的开通和关断,有可能造成功率管漏源极间的电压震荡,或者有可能造成功率管遭受过高的di/dt 而引起误导通。

为避免上述现象的发生,通常在MOS驱动器的输出与MOS管的栅极之间串联一个电阻,电阻的大小一般选取几十欧姆。

PowerMOSFET基础知识

针对PowerMOSFET的常见问 题,如热管理、开关时间和电 压击穿等,进行了深入探讨, 并提出了相应的解决方案。

结合实际案例,展示了 PowerMOSFET在电机驱动、 电源供应和逆变器等领域的应 用,突出了其高效、可靠和灵 活的特点。

对未来研究的建议

01

深入研究PowerMOSFET的材料、工艺和结构设计,以提高其性能和 可靠性。

最大允许工作电压是指PowerMOSFET在正 常工作条件下所承受的最大电压,超过此 电压可能导致器件损坏。

03

CATALOGUE

PowerMOSFET的应用领域

电源管理

电源转换

电源保护

PowerMOSFET在电源管理领域中常 用于实现高效的直流电压转换,如将 高压直流电转换为低压直流电,以满 足不同设备的供电需求。

电力系统

无功补偿

PowerMOSFET可以用于构建无功补 偿装置,通过控制MOSFET的开关状 态来调节电容器的投切,从而实现无 功补偿和滤波功能,提高电力系统的 功率因数和稳定性。

智能电网

在智能电网中,PowerMOSFET可以 作为智能电表中的重要元件,用于实 现远程控制和智能管理电力系统的功 能。

PowerMOSFET的工作原理

开关状态

在开关状态下,PowerMOSFET可以 通过控制栅极电压来开启或关闭电流 的导通。当栅极电压足够高时,导电 沟道形成,电流从源极流向漏极。

导通状态

在导通状态下,PowerMOSFET的导 电沟道内存在大量的自由电子和空穴 ,形成很强的电导率,允许大电流通 过。

02

探索新型的PowerMOSFET驱动和控制技术,以适应不断发展的电力 电子系统需求。

详细讲解MOSFET管驱动电路

详细讲解M O S F E T管驱动电路在使用MOS管设计开关电源或者马达驱动电路的时候,大部分人都会考虑MOS的导通电阻,最大电压等,最大电流等,也有很多人仅仅考虑这些因素;这样的电路也许是可以工作的,但并不是优秀的,作为正式的产品设计也是不允许的;下面是我对MOSFET及MOSFET驱动电路基础的一点总结,其中参考了一些资料,非全部原创;包括MOS管的介绍,特性,驱动以及应用电路;1,MOS管种类和结构MOSFET管是FET的一种另一种是JFET,可以被制造成增强型或耗尽型,P沟道或N沟道共4种类型,但实际应用的只有增强型的N沟道MOS管和增强型的P沟道MOS管,所以通常提到NMOS,或者PMOS指的就是这两种;至于为什么不使用耗尽型的MOS管,不建议刨根问底;对于这两种增强型MOS管,比较常用的是NMOS;原因是导通电阻小,且容易制造;所以开关电源和马达驱动的应用中,一般都用NMOS;下面的介绍中,也多以NMOS 为主;MOS管的三个管脚之间有寄生电容存在,这不是我们需要的,而是由于制造工艺限制产生的;寄生电容的存在使得在设计或选择驱动电路的时候要麻烦一些,但没有办法避免,后边再详细介绍;在MOS管原理图上可以看到,漏极和源极之间有一个寄生二极管;这个叫体二极管,在驱动感性负载如马达,这个二极管很重要;顺便说一句,体二极管只在单个的MOS管中存在,在集成电路芯片内部通常是没有的;2,MOS管导通特性导通的意思是作为开关,相当于开关闭合;NMOS的特性,Vgs大于一定的值就会导通,适合用于源极接地时的情况低端驱动,只要栅极电压达到4V或10V就可以了;PMOS的特性,Vgs小于一定的值就会导通,适合用于源极接VCC时的情况高端驱动;但是,虽然PMOS可以很方便地用作高端驱动,但由于导通电阻大,价格贵,替换种类少等原因,在高端驱动中,通常还是使用NMOS;3,MOS开关管损失不管是NMOS还是PMOS,导通后都有导通电阻存在,这样电流就会在这个电阻上消耗能量,这部分消耗的能量叫做导通损耗;选择导通电阻小的MOS管会减小导通损耗;现在的小功率MOS管导通电阻一般在几十毫欧左右,几毫欧的也有;MOS在导通和截止的时候,一定不是在瞬间完成的;MOS两端的电压有一个下降的过程,流过的电流有一个上升的过程,在这段时间内,MOS管的损失是电压和电流的乘积,叫做开关损失;通常开关损失比导通损失大得多,而且开关频率越快,损失也越大;导通瞬间电压和电流的乘积很大,造成的损失也就很大;缩短开关时间,可以减小每次导通时的损失;降低开关频率,可以减小单位时间内的开关次数;这两种办法都可以减小开关损失;4,MOS管驱动跟双极性晶体管相比,一般认为使MOS管导通不需要电流,只要GS电压高于一定的值,就可以了;这个很容易做到,但是,我们还需要速度;在MOS管的结构中可以看到,在GS,GD之间存在寄生电容,而MOS管的驱动,实际上就是对电容的充放电;对电容的充电需要一个电流,因为对电容充电瞬间可以把电容看成短路,所以瞬间电流会比较大;选择/设计MOS管驱动时第一要注意的是可提供瞬间短路电流的大小;第二注意的是,普遍用于高端驱动的NMOS,导通时需要是栅极电压大于源极电压;而高端驱动的MOS管导通时源极电压与漏极电压VCC相同,所以这时栅极电压要比VCC大4V或10V;如果在同一个系统里,要得到比VCC大的电压,就要专门的升压电路了;很多马达驱动器都集成了电荷泵,要注意的是应该选择合适的外接电容,以得到足够的短路电流去驱动MOS管;上边说的4V或10V是常用的MOS管的导通电压,设计时当然需要有一定的余量;而且电压越高,导通速度越快,导通电阻也越小;现在也有导通电压更小的MOS管用在不同的领域里,但在12V汽车电子系统里,一般4V导通就够用了;MOS管的驱动电路及其损失,可以参考Microchip公司的AN799 Matching MOSFET Drivers to MOSFETs;讲述得很详细,所以不打算多写了;5,MOS管应用电路MOS管最显着的特性是开关特性好,所以被广泛应用在需要电子开关的电路中,常见的如开关电源和马达驱动,也有照明调光;现在的MOS驱动,有几个特别的需求,1,低压应用当使用5V电源,这时候如果使用传统的图腾柱结构,由于三极管的be有左右的压降,导致实际最终加在gate上的电压只有;这时候,我们选用标称gate电压的MOS管就存在一定的风险;同样的问题也发生在使用3V或者其他低压电源的场合;2,宽电压应用输入电压并不是一个固定值,它会随着时间或者其他因素而变动;这个变动导致PWM电路提供给MOS管的驱动电压是不稳定的;为了让MOS管在高gate电压下安全,很多MOS管内置了稳压管强行限制gate电压的幅值;在这种情况下,当提供的驱动电压超过稳压管的电压,就会引起较大的静态功耗;同时,如果简单的用电阻分压的原理降低gate电压,就会出现输入电压比较高的时候,MOS管工作良好,而输入电压降低的时候gate电压不足,引起导通不够彻底,从而增加功耗;3,双电压应用在一些控制电路中,逻辑部分使用典型的5V或者数字电压,而功率部分使用12V甚至更高的电压;两个电压采用共地方式连接;这就提出一个要求,需要使用一个电路,让低压侧能够有效的控制高压侧的MOS管,同时高压侧的MOS管也同样会面对1和2中提到的问题;在这三种情况下,图腾柱结构无法满足输出要求,而很多现成的MOS驱动IC,似乎也没有包含gate电压限制的结构;于是我设计了一个相对通用的电路来满足这三种需求;电路图如下:图1 用于NMOS的驱动电路图2 用于PMOS的驱动电路这里我只针对NMOS驱动电路做一个简单分析:Vl和Vh分别是低端和高端的电源,两个电压可以是相同的,但是Vl不应该超过Vh;Q1和Q2组成了一个反置的图腾柱,用来实现隔离,同时确保两只驱动管Q3和Q4不会同时导通;R2和R3提供了aPWM电压基准,通过改变这个基准,可以让电路工作在PWM信号波形比较陡直的位置;Q3和Q4用来提供驱动电流,由于导通的时候,Q3和Q4相对Vh和GND最低都只有一个Vce的压降,这个压降通常只有左右,大大低于的Vce;R5和R6是反馈电阻,用于对gate电压进行采样,采样后的电压通过Q5对Q1和Q2的基极产生一个强烈的负反馈,从而把gate电压限制在一个有限的数值;这个数值可以通过R5和R6来调节;最后,R1提供了对Q3和Q4的基极电流限制,R4提供了对MOS管的gate电流限制,也就是Q3和Q4的Ice的限制;必要的时候可以在R4上面并联加速电容;这个电路提供了如下的特性:1,用低端电压和PWM驱动高端MOS管;2,用小幅度的PWM信号驱动高gate电压需求的MOS管;3,gate电压的峰值限制4,输入和输出的电流限制5,通过使用合适的电阻,可以达到很低的功耗;6,PWM信号反相;NMOS并不需要这个特性,可以通过前置一个反相器来解决;在设计便携式设备和无线产品时,提高产品性能、延长电池工作时间是设计人员需要面对的两个问题;DC-DC转换器具有效率高、输出电流大、静态电流小等优点,非常适用于为便携式设备供电;目前DC-DC转换器设计技术发展主要趋势有:1高频化技术:随着开关频率的提高,开关变换器的体积也随之减小,功率密度也得到大幅提升,动态响应得到改善;小功率DC-DC转换器的开关频率将上升到兆赫级;2低输出电压技术:随着半导体制造技术的不断发展,微处理器和便携式电子设备的工作电压越来越低,这就要求未来的DC-DC变换器能够提供低输出电压以适应微处理器和便携式电子设备的要求;这些技术的发展对电源芯片电路的设计提出了更高的要求;首先,随着开关频率的不断提高,对于开关元件的性能提出了很高的要求,同时必须具有相应的开关元件驱动电路以保证开关元件在高达兆赫级的开关频率下正常工作;其次,对于电池供电的便携式电子设备来说,电路的工作电压低以锂电池为例,工作电压~,因此,电源芯片的工作电压较低;MOS管具有很低的导通电阻,消耗能量较低,在目前流行的高效DC-DC芯片中多采用MOS管作为功率开关;但是由于MOS管的寄生电容大,一般情况下NMOS开关管的栅极电容高达几十皮法;这对于设计高工作频率DC-DC转换器开关管驱动电路的设计提出了更高的要求;在低电压ULSI设计中有多种CMOS、BiCMOS采用自举升压结构的逻辑电路和作为大容性负载的驱动电路;这些电路能够在低于1V电压供电条件下正常工作,并且能够在负载电容1~2pF的条件下工作频率能够达到几十兆甚至上百兆赫兹;本文正是采用了自举升压电路,设计了一种具有大负载电容驱动能力的,适合于低电压、高开关频率升压型DC-DC转换器的驱动电路;电路基于Samsung AHP615 BiCMOS工艺设计并经过Hspice仿真验证,在供电电压,负载电容为60pF时,工作频率能够达到5MHz以上;自举升压电路自举升压电路的原理图如图1所示;所谓的自举升压原理就是,在输入端IN 输入一个方波信号,利用电容Cboot将A点电压抬升至高于VDD的电平,这样就可以在B端输出一个与输入信号反相,且高电平高于VDD的方波信号;具体工作原理如下;当VIN为高电平时,NMOS管N1导通,PMOS管P1截止,C点电位为低电平;同时N2导通,P2的栅极电位为低电平,则P2导通;这就使得此时A点电位约为VDD,电容Cboot两端电压UC≈VDD;由于N3导通,P4截止,所以B点的电位为低电平;这段时间称为预充电周期;当VIN变为低电平时,NMOS管N1截止,PMOS管P1导通,C点电位为高电平,约为VDD;同时N2、N3截止,P3导通;这使得P2的栅极电位升高,P2截止;此时A 点电位等于C点电位加上电容Cboot两端电压,约为2VDD;而且P4导通,因此B点输出高电平,且高于VDD;这段时间称为自举升压周期;实际上,B点电位与负载电容和电容Cboot的大小有关,可以根据设计需要调整;具体关系将在介绍电路具体设计时详细讨论;在图2中给出了输入端IN电位与A、B两点电位关系的示意图;驱动电路结构图3中给出了驱动电路的电路图;驱动电路采用Totem输出结构设计,上拉驱动管为NMOS管N4、晶体管Q1和PMOS管P5;下拉驱动管为NMOS管N5;图中CL为负载电容,Cpar为B点的寄生电容;虚线框内的电路为自举升压电路;本驱动电路的设计思想是,利用自举升压结构将上拉驱动管N4的栅极B点电位抬升,使得UB>VDD+VTH ,则NMOS管N4工作在线性区,使得VDSN4 大大减小,最终可以实现驱动输出高电平达到VDD;而在输出低电平时,下拉驱动管本身就工作在线性区,可以保证输出低电平位GND;因此无需增加自举电路也能达到设计要求;考虑到此驱动电路应用于升压型DC-DC转换器的开关管驱动,负载电容CL很大,一般能达到几十皮法,还需要进一步增加输出电流能力,因此增加了晶体管Q1作为上拉驱动管;这样在输入端由高电平变为低电平时,Q1导通,由N4、Q1同时提供电流,OUT端电位迅速上升,当OUT端电位上升到VDD-VBE时,Q1截止,N4继续提供电流对负载电容充电,直到OUT端电压达到VDD;在OUT端为高电平期间,A点电位会由于电容Cboot 上的电荷泄漏等原因而下降;这会使得B点电位下降,N4的导通性下降;同时由于同样的原因,OUT端电位也会有所下降,使输出高电平不能保持在VDD;为了防止这种现象的出现,又增加了PMOS管P5作为上拉驱动管,用来补充OUT端CL的泄漏电荷,维持OUT端在整个导通周期内为高电平;驱动电路的传输特性瞬态响应在图4中给出;其中a为上升沿瞬态响应,b为下降沿瞬态响应;从图4中可以看出,驱动电路上升沿明显分为了三个部分,分别对应三个上拉驱动管起主导作用的时期;1阶段为Q1、N4共同作用,输出电压迅速抬升,2阶段为N4起主导作,使输出电平达到VDD,3阶段为P5起主导作用,维持输出高电平为VDD;而且还可以缩短上升时间,下降时间满足工作频率在兆赫兹级以上的要求;需要注意的问题及仿真结果电容Cboot的大小的确定Cboot的最小值可以按照以下方法确定;在预充电周期内,电容Cboot 上的电荷为VDDCboot ;在A点的寄生电容计为CA上的电荷为VDDCA;因此在预充电周期内,A点的总电荷为Q_{A1}=V_{DD}C_{boot}+V_{DD}C_{A} 1B点电位为GND,因此在B点的寄生电容Cpar上的电荷为0;在自举升压周期,为了使OUT端电压达到VDD,B点电位最低为VB=VDD+Vthn;因此在B点的寄生电容Cpar上的电荷为Q_{B}=V_{DD}+V_{thn}Cpar 2忽略MOS管P4源漏两端压降,此时Cboot上的电荷为VthnCboot ,A点寄生电容CA的电荷为VDD+VthnCA;A点的总电荷为QA2=V_{thn}C_{BOOT}+V_{DD}+V_{thn}C_{A} 3同时根据电荷守恒又有Q_{B}=Q_{A}-Q_{A2} 4综合式1~4可得C_{boot}=\frac{V_{DD}+V_{thn}}{v_{DD}-v_{thn}}Cpar+\frac{v_{thn}}{v_{DD}-v_{ thn}}C_{A}=\frac{V_{B}}{v_{DD}-v_{thn}}Cpar+\frac{V_{thn}}{v_{DD}-v_{thn}}C_{ A} 5从式5中可以看出,Cboot随输入电压变小而变大,并且随B点电压VB变大而变大;而B点电压直接影响N4的导通电阻,也就影响驱动电路的上升时间;因此在实际设计时,Cboot的取值要大于式5的计算结果,这样可以提高B点电压,降低N4导通电阻,减小驱动电路的上升时间;P2、P4的尺寸问题将公式5重新整理后得:V_{B}={V_{DD}-V_{thn}\frac{C_{boot}}{Cpar}-V_{thn}\frac{C_{A}}{Cpar} 6 从式6中可以看出在自举升压周期内, A、B两点的寄生电容使得B点电位降低;在实际设计时为了得到合适的B点电位,除了增加Cboot大小外,要尽量减小A、B两点的寄生电容; 在设计时,预充电PMOS管P2的尺寸尽可能的取小,以减小寄生电容CA;而对于B点的寄生电容Cpar来说,主要是上拉驱动管N4的栅极寄生电容,MOS管P4、N3的源漏极寄生电容只占一小部分;我们在前面的分析中忽略了P4的源漏电压,因此设计时就要尽量的加大P4的宽长比,使其在自举升压周期内的源漏电压很小可以忽略;但是P4的尺寸以不能太大,要保证P4的源极寄生电容远远小于上拉驱动管N4的栅极寄生电容;阱电位问题如图3所示,PMOS器件P2、P3、P4的N-well连接到了自举升压节点A上;这样做的目的是,在自举升压周期内,防止他们的源/漏--阱结导通;而且这还可以防止在源/漏--阱正偏时产生由寄生SRC引起的闩锁现象;上拉驱动管N4的阱偏置电位要接到它的源极,最好不要直接接地;这样做的目的是消除衬底偏置效应对N4的影响;Hspice仿真验证结果驱动电路基于Samsung AHP615 BiCMOS工艺设计并经过Hspice仿真验证;在表1中给出了电路在不同工作电压、不同负载条件下的上升时间tr和下降时间tf 的仿真结果;在图5中给了电路工作在输入电压、工作频率为5MHz、负载电容60pF条件下的输出波形;结合表1和图5可以看出,此驱动电路能够在工作电压为,工作频率为5MHz,并且负载电容高达60pF的条件下正常工作;它可以应用于低电压、高工作频率的DC-DC转换器中作为开关管的驱动电路;结论本文采用自举升压电路,设计了一种BiCMOS Totem结构的驱动电路;该电路基于Samsung AHP615 BiCMOS工艺设计,可在电压供电条件下正常工作,而且在负载电容为60pF的条件下,工作频率可达5MHz以上;。

mosfet电压隔离驱动方案

mosfet电压隔离驱动方案MOSFET电压隔离驱动方案随着现代电子技术的快速发展,电路的稳定性和可靠性要求也越来越高。

在一些特殊的应用场景中,如高频电路、高压电路、噪声环境下的电路等,需要对电路进行电压隔离来提高系统的稳定性和安全性。

MOSFET电压隔离驱动方案因其高速、低功耗和可靠性等优势,成为了一种常用的解决方案。

MOSFET(金属氧化物半导体场效应晶体管)是一种常见的半导体器件,具有高速开关和低功耗的特点。

通过控制MOSFET的栅极电压,可以实现对电路的开关控制。

而MOSFET电压隔离驱动方案则是利用MOSFET的特性来实现电路之间的电压隔离。

在MOSFET电压隔离驱动方案中,一般会使用光耦来实现电路间的隔离。

光耦是一种能够将电路间的信号通过光信号进行转换的器件。

它由发光二极管(LED)和光敏二极管(光电晶体管)组成。

当输入信号施加在发光二极管上时,发光二极管会发出光信号,光信号经过隔离区域后,被光敏二极管接收并转换为与输入信号相同的电信号。

通过光耦将输入信号与MOSFET的栅极连接起来,当输入信号施加在光耦上时,光敏二极管会产生相应的电信号,通过MOSFET的栅极电压来控制MOSFET的导通和关断。

由于光耦实现了输入信号和MOSFET之间的电气隔离,可以有效地提高系统的稳定性和安全性。

MOSFET电压隔离驱动方案具有以下几个优势:1. 高速开关:MOSFET具有快速的开关速度,可以实现高频电路的要求。

通过光耦隔离驱动MOSFET,可以实现输入信号的快速响应,提高系统的响应速度。

2. 低功耗:MOSFET的工作电流较小,具有较低的功耗。

通过光耦隔离驱动MOSFET,可以进一步降低功耗,提高系统的能效。

3. 可靠性高:MOSFET具有较高的可靠性,长时间工作不易出现故障。

通过光耦隔离驱动MOSFET,可以避免外部电源的电压干扰和噪声对系统的影响,提高系统的稳定性和可靠性。

4. 成本低:MOSFET电压隔离驱动方案相对于其他电压隔离方案来说,成本较低。

功率场效应晶体管MOSFET原理及其驱动

功率场效应晶体管(MOSFET)原理功率场效应管(Power MOSFET)也叫电力场效应晶体管,是一种单极型的电压控制器件,不但有自关断能力,而且有驱动功率小,开关速度高、无二次击穿、安全工作区宽等特点。

由于其易于驱动和开关频率可高达500kHz,特别适于高频化电力电子装置,如应用于DC/DC变换、开关电源、便携式电子设备、航空航天以及汽车等电子电器设备中。

但因为其电流、热容量小,耐压低,一般只适用于小功率电力电子装置。

一、电力场效应管的结构和工作原理电力场效应晶体管种类和结构有许多种,按导电沟道可分为P沟道和N沟道,同时又有耗尽型和增强型之分。

在电力电子装置中,主要应用N沟道增强型。

电力场效应晶体管导电机理与小功率绝缘栅MOS管相同,但结构有很大区别。

小功率绝缘栅MOS管是一次扩散形成的器件,导电沟道平行于芯片表面,横向导电。

电力场效应晶体管大多采用垂直导电结构,提高了器件的耐电压和耐电流的能力。

按垂直导电结构的不同,又可分为2种:V形槽VVMOSFET和双扩散VDMOSFET。

电力场效应晶体管采用多单元集成结构,一个器件由成千上万个小的MOSFET组成。

N沟道增强型双扩散电力场效应晶体管一个单元的部面图,如图1(a)所示。

电气符号,如图1(b)所示。

电力场效应晶体管有3个端子:漏极D、源极S和栅极G。

当漏极接电源正,源极接电源负时,栅极和源极之间电压为0,沟道不导电,管子处于截止。

如果在栅极和源极之间加一正向电压U GS,并且使U GS大于或等于管子的开启电压U T,则管子开通,在漏、源极间流过电流I D。

U GS超过U T越大,导电能力越强,漏极电流越大。

二、电力场效应管的静态特性和主要参数Power MOSFET静态特性主要指输出特性和转移特性,与静态特性对应的主要参数有漏极击穿电压、漏极额定电压、漏极额定电流和栅极开启电压等。

{{分页}}1、静态特性(1)输出特性输出特性即是漏极的伏安特性。

功率MOSFET(PowerMOSFET)的基本知识

功率MOSFET(Power MOSFET)的基本知识自1976年开发出功率MOSFET以来,由于半导体工艺技术的发展,它的性能不断提高:如高压功率MOSFET其工作电压可达1000V;低导通电阻MOSFET其阻值仅lOmΩ;工作频率范围从直流到达数兆赫;保护措施越来越完善;并开发出各种贴片式功率MOSFET(如Siliconix最近开发的厚度为1.5mm“Little Foot系列)。

另外,价格也不断降低,使应用越来越广泛,不少地方取代双极型晶体管。

功率MOSFET主要用于计算机外设(软、硬驱动器、打印机、绘图机)、电源(AC/DC变换器、DC/DC变换器)、汽车电子、音响电路及仪器、仪表等领域。

本文将介绍功率MOSFET的结构、工作原理及基本工作电路。

什么是MOSFET“MOSFET”是英文MetalOxide Semicoductor Field Effect Transistor的缩写,译成中文是“金属氧化物半导体场效应管”。

它是由金属、氧化物(SiO2或SiN)及半导体三种材料制成的器件。

所谓功率MOSFET(Power MOSFET)是指它能输出较大的工作电流(几安到几十安),用于功率输出级的器件。

MOSFET的结构图1是典型平面N沟道增强型MOSFET的剖面图。

它用一块P型硅半导体材料作衬底(图la),在其面上扩散了两个N型区(图lb),再在上面覆盖一层二氧化硅(SiQ2)绝缘层(图lc),最后在N区上方用腐蚀的方法做成两个孔,用金属化的方法分别在绝缘层上及两个孔内做成三个电极:G(栅极)、S(源极)及D(漏极),如图1d所示。

从图1中可以看出栅极G与漏极D及源极S是绝缘的,D与S之间有两个PN结。

一般情况下,衬底与源极在内部连接在一起。

图1是N沟道增强型MOSFET的基本结构图。

为了改善某些参数的特性,如提高工作电流、提高工作电压、降低导通电阻、提高开关特性等有不同的结构及工艺,构成所谓VMOS、DMOS、TMOS 等结构。

MOSFET电流源驱动原理及实现

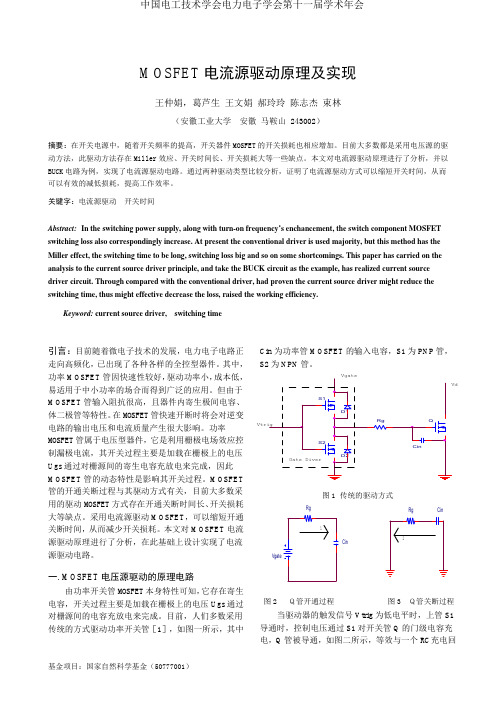

MOSFET电流源驱动原理及实现王仲娟,葛芦生王文娟郝玲玲陈志杰束林(安徽工业大学安徽马鞍山243002)摘要:在开关电源中,随着开关频率的提高,开关器件MOSFET的开关损耗也相应增加。

目前大多数都是采用电压源的驱动方法,此驱动方法存在Miller效应、开关时间长、开关损耗大等一些缺点。

本文对电流源驱动原理进行了分析,并以BUCK电路为例,实现了电流源驱动电路。

通过两种驱动类型比较分析,证明了电流源驱动方式可以缩短开关时间,从而可以有效的减低损耗,提高工作效率。

关键字:电流源驱动开关时间Abstract:In the switching power supply,along with turn-on frequency’s enchancement,the switch component MOSFET switching loss also correspondingly increase.At present the conventional driver is used majority,but this method has the Miller effect,the switching time to be long,switching loss big and so on some shortcomings.This paper has carried on the analysis to the current source driver principle,and take the BUCK circuit as the example,has realized current source driver circuit.Through compared with the conventional driver,had proven the current source driver might reduce the switching time,thus might effective decrease the loss,raised the working efficiency.Keyword:current source driver,switching time引言:目前随着微电子技术的发展,电力电子电路正走向高频化,已出现了各种各样的全控型器件。

MOS管工作原理及其驱动电路

功率场效应晶体管MOSFET1.概述MOSFET的原意是:MOS(Metal Oxide Semiconductor金属氧化物半导体),FET(Field Effect Transistor场效应晶体管),即以金属层(M)的栅极隔着氧化层(O)利用电场的效应来控制半导体(S)的场效应晶体管。

功率场效应晶体管也分为结型和绝缘栅型,但通常主要指绝缘栅型中的MOS型(Metal Oxide Semiconductor FET),简称功率MOSFET(Power MOSFET)。

结型功率场效应晶体管一般称作静电感应晶体管(Static Induction Transistor——SIT)。

其特点是用栅极电压来控制漏极电流,驱动电路简单,需要的驱动功率小,开关速度快,工作频率高,热稳定性优于GTR,但其电流容量小,耐压低,一般只适用于功率不超过10kW的电力电子装置。

2.功率MOSFET的结构和工作原理功率MOSFET的种类:按导电沟道可分为P沟道和N沟道。

按栅极电压幅值可分为;耗尽型;当栅极电压为零时漏源极之间就存在导电沟道,增强型;对于N(P)沟道器件,栅极电压大于(小于)零时才存在导电沟道,功率MOSFET 主要是N沟道增强型。

2.1功率MOSFET的结构功率MOSFET的内部结构和电气符号如图1所示;其导通时只有一种极性的载流子(多子)参与导电,是单极型晶体管。

导电机理与小功率mos管相同,但结构上有较大区别,小功率MOS管是横向导电器件,功率MOSFET大都采用垂直导电结构,又称为VMOSFET(Vertical MOSFET),大大提高了MOSFET 器件的耐压和耐电流能力。

按垂直导电结构的差异,又分为利用V型槽实现垂直导电的VVMOSFET和具有垂直导电双扩散MOS结构的VDMOSFET(Vertical Double-diffused MOSFET),本文主要以VDMOS器件为例进行讨论。

电力场效应晶体管(MOSFET)

图1-42 电力电子器件分类“树”

分类:DATASHEET

(4) 极间电容

——极间电容CGS、CGD和CDS

本章小结

主要内容

全面介绍各种主要电 力电子器件的基本结 构、工作原理、基本 特性和主要参数等。

集中讨论电力电子器 件的驱动、保护

电力电子器件类型归纳

单极型:电力MOSFET和 SIT

双极型:电力二极管、晶闸 管、GTO、GTR和SITH

复合型:IGBT和MCT

1 电力场效应晶体管

电力MOSFET的结构

小功率MOS管是横向导电器件。 电 力 MOSFET 大 都 采 用 垂 直 导 电 结 构 , 又 称 为 VMOSFET(Vertical MOSFET)。 按垂直导电结构的差异,分为利用V型槽实现垂直导电 的 VVMOSFET 和 具 有 垂 直 导 电 双 扩 散 MOS 结 构 的 VDMOSFET(Vertical Double-diffused MOSFET)。 这里主要以VDMOS器件为例进行讨论。

非饱和区之间来回转换。

10

漏源极之间有寄生二极管,漏源 0 极间加反向电压时器件导通。

2

UT

46 UGS/V

8

a)

20

UGS=6V

10

UGS=5V

UGS=4V

功率晶体管

功率晶体管功率晶体管是一种高压、高电流、高功率的电子元件。

它是一种半导体器件,能够将小信号控制大电流,被广泛应用于各种电力电子设备中,如变频器、电源、电机驱动器等。

本文将从功率晶体管的原理、结构、工作特性以及应用领域等方面进行介绍。

一、功率晶体管的原理功率晶体管(Power MOSFET)是一种基于金属氧化物半导体场效应晶体管(MOSFET)的半导体器件。

与普通MOSFET相比,功率晶体管主要区别在于其耐压、耐电流、导通损耗等方面更为优越。

功率晶体管的核心部件是PN结,其结构如图1所示。

图1:功率晶体管结构示意图PN结是由P型半导体和N型半导体组成的结构,它是功率晶体管的主要控制部件。

PN结的导通与截止是通过场效应晶体管的栅电压来控制的。

栅极上的正向偏置电压会使得栅源之间形成一个电场,这个电场会影响PN结的导通与截止。

当栅极电压为零或负电压时,PN结截止,功率晶体管处于关闭状态,不导电;当栅极电压为正电压时,PN结导通,功率晶体管处于导通状态,可以通过电流。

二、功率晶体管的结构功率晶体管的结构主要包括栅极、漏极、源极、衬底等部分。

其中,源极和漏极是功率晶体管的输出端和输入端,栅极则是功率晶体管的控制端。

衬底则是功率晶体管的基底,通常与源极相连,用于固定源极电位。

功率晶体管的结构示意图如图2所示。

图2:功率晶体管结构示意图三、功率晶体管的工作特性功率晶体管的工作特性主要包括导通电阻、开关速度、漏电流等。

其中,导通电阻是功率晶体管的重要指标,它决定了功率晶体管的导通损耗。

开关速度则决定了功率晶体管的开关频率,漏电流则影响功率晶体管的工作温度和可靠性。

1.导通电阻功率晶体管的导通电阻主要由PN结的电阻、漏极电阻和接触电阻等组成。

其中,PN结的电阻和漏极电阻是功率晶体管的主要导通电阻。

为了降低功率晶体管的导通电阻,可以采用优化材料、优化结构和优化工艺等措施。

2.开关速度功率晶体管的开关速度主要由栅电容、栅电阻、栅驱动电路等因素决定。

Power MOSFET IC的结构与电气特性1

Power MOSFET IC的结构与电气特性Power MOSFET IC(以下简称为MOSFET)广泛应用在各种电源电路与汽车等领域,虽然最近几年MOSFET在高速切换(switching)与低ON阻抗化有相当的进展,不过一般认为未来MOSFET势必会朝高性能方向发展,因此本文要介绍MOSFET IC的构造、电气特性,以及今后技术发展动向。

MOSFET IC的构造图1是N channel Power MOSFET IC的断面构造,本MOSFET的gate与source之间,亦即gate pad的周围设有可以防止静电破坏的保护二极管,因此它又称为body diode。

马达驱动电路与断电电源供应器(UPS)等DC-AC转换inverter等应用的场合,保护二极管可以充分发挥它的特性。

图1 Power MOSFET IC的构造图2是MOSFET的结构分类,由图可知MOSFET结构上可以分成纵型与横型两种type;纵型type还分成平板(planer)结构与沟槽(trench)结构两种。

表1是上述结构特征与主要用途一览。

因此从应用面观之纵型与沟槽结构的MOSFET,两者的低容量化特性已经没有太大差异。

如上所述纵型结构的MOSFET具备高耐压、低ON阻抗、大电流等特征,所以适合当作switching组件使用。

‧横型构造横型构造最大缺点是不易符合高耐压/低ON阻抗等要求,不过它低容量特性尤其是逆传达容量(归返容量)C rss非常小。

如图2(b)所示,gate与source之间的容量被field plate遮蔽(shield),因此结构上非常有利。

不过横型构造的cell面积很大,单位面积的ON阻抗比纵型构造大,因此一般认为不适合switching组件使用,只能当作要求高速/高频等高频增幅器常用的输出控制组件(device)。

‧今后发展动向横型构造比较适用于低耐压switching组件,主要应用例如驱逐CPU core的VR(Voltage Regulator)等等。

MOSFET基本原理

Principle of MOSFET功率场效应管(Power MOSFET)也叫电力场效应晶体管,是一种单极型的电压控制器件,不但有自关断能力,而且有驱动功率小,开关速度高、无二次击穿、安全工作区宽等特点。

由于其易于驱动和开关频率可高达500kHz,特别适于高频化电力电子装置,如应用于DC/DC变换、开关电源、便携式电子设备、航空航天以及汽车等电子电器设备中。

但因为其电流、热容量小,耐压低,一般只适用于小功率电力电子装置。

一、电力场效应管的结构和工作原理电力场效应晶体管种类和结构有许多种,按导电沟道可分为P沟道和N沟道,同时又有耗尽型和增强型之分。

在电力电子装置中,主要应用N沟道增强型。

电力场效应晶体管导电机理与小功率绝缘栅MOS管相同,但结构有很大区别。

小功率绝缘栅MOS管是一次扩散形成的器件,导电沟道平行于芯片表面,横向导电。

电力场效应晶体管大多采用垂直导电结构,提高了器件的耐电压和耐电流的能力。

按垂直导电结构的不同,又可分为2种:V形槽VVMOSFET和双扩散VDMOSFET。

电力场效应晶体管采用多单元集成结构,一个器件由成千上万个小的MOSFET组成。

N沟道增强型双扩散电力场效应晶体管一个单元的部面图,如图1(a)所示。

电气符号,如图1(b)所示。

电力场效应晶体管有3个端子:漏极D、源极S和栅极G。

当漏极接电源正,源极接电源负时,栅极和源极之间电压为0,沟道不导电,管子处于截止。

如果在栅极和源极之间加一正向电压U GS,并且使U GS大于或等于管子的开启电压U T,则管子开通,在漏、源极间流过电流I D。

U GS超过U T越大,导电能力越强,漏极电流越大。

二、电力场效应管的静态特性和主要参数Power MOSFET静态特性主要指输出特性和转移特性,与静态特性对应的主要参数有漏极击穿电压、漏极额定电压、漏极额定电流和栅极开启电压等。

{{分页}}1、静态特性(1)输出特性输出特性即是漏极的伏安特性。

功率变换器中PowerMOSFET功率损耗的数学分析及计算

功率变换器中PowerMOSFET功率损耗的数学分析及计算摘要本文旨在通过数学分析和计算来探讨功率变换器中PowerMOSFET的功率损耗. 我们首先回顾了PowerMOSFET的一般原理,重点介绍了PowerMOSFET的功率损耗计算. 在对PowerMOSFET的工作原理的理解的基础上,我们介绍了基于单MOSFET模型的功率损耗计算模型,并用实例来说明. 接着介绍了基于多MOSFET模型的功率损耗计算模型,并用实例来说明. 最后,我们介绍了基于有源过滤器模型的功率损耗计算模型,并用实例来说明.关键词PowerMOSFET, 功率变换器, 功率损耗, 单MOSFET模型, 多MOSFET模型, 有源过滤器模型正文本文旨在探讨功率变换器中PowerMOSFET的功率损耗的数学分析及计算,首先介绍了PowerMOSFET的工作原理,然后介绍了三种不同的功率损耗计算模型,即单MOSFET模型、多MOSFET模型和有源过滤器模型。

首先,我们介绍单MOSFET模型,它是基于PowerMOSFET的基本工作原理来计算功率损耗的。

根据单MOSFET模型,功率损耗可以表示为P=V^2*Rds和k(uS/V)^2*W/L*Vgs^2(Vds-Vgs),其中V为MOSFET的工作电压,Rds为MOSFET的直流电阻,单位为正常单位;k为MOSFET的负载参数,单位为uS/V;W/L为MOSFET的尺寸,W为栅极宽度,L为栅极长度;Vgs为栅极与源极之间的电压,Vds为漏极与源极之间的电压。

然后,我们介绍了多MOSFET模型,它是基于PowerMOSFET的多MOSFET连接来计算功率损耗的。

根据多MOSFET模型,功率损耗可以表示为PMOS=nPMOS*V^2*Rds+(uS/V)^2*W/L*(Vds-Vgs)^2,PMOS表示PMOS连接中消耗的功率, nPMOS表示PMOS片的数量,其他量的单位和含义与单MOSFET模型中的相同。

电力mos场效应晶体管

电力MOS场效应晶体管介绍电力MOS场效应晶体管(Power MOSFET)是一种常用的功率开关器件,能够在高电压、高电流下实现快速、精确的开关操作。

它具有低导通电阻、高开关速度和低驱动功率等优点,被广泛应用于电力电子领域。

结构与工作原理结构电力MOS场效应晶体管由N型MOSFET和P型补偿二极管组成。

晶体管的主要部分包括衬底(Substrate)、栅氧化物(Gate Oxide)、金属栅(Metal Gate)、漏极(Drain)和源极(Source)等。

工作原理1.导通状态:当栅电压高于阈值电压时,MOSFET导通,形成从漏极到源极的通路,电流流经通道正常导通。

2.截止状态:当栅电压低于阈值电压时,MOSFET截止,导电通道被关闭,电流无法流通。

特性参数静态参数电力MOS场效应晶体管的静态参数包括阈值电压(Vth)、漏极电流(ID)和漏极-源极电阻(RDS(on))等。

动态参数电力MOS场效应晶体管的动态参数包括输出电容(Coss)、输入电容(Ciss)和反馈电容(Crss)等。

应用领域电力MOS场效应晶体管在电力电子领域有广泛的应用,包括以下几个方面:开关电源电力MOS场效应晶体管可以用于开关电源的开关器件,实现高效率和高稳定性的能量转换。

电机驱动电力MOS场效应晶体管可以控制电机的启动、停止和速度调节,广泛应用于电动车、空调、洗衣机等家电产品。

电力变换电力MOS场效应晶体管可以实现电力的变换和调节,用于直流变交流、逆变、电源管理等领域。

选型和应用注意事项选型考虑因素在选择电力MOS场效应晶体管时,需考虑以下因素:1.额定电压和电流:根据实际应用需求选择适合的额定电压和电流。

2.开关速度:根据应用要求选择快速开关或低开关损耗的晶体管。

3.热阻:选择低热阻的晶体管可以提高散热效果,提高器件寿命。

4.可靠性:考虑晶体管的可靠性和长期稳定性,在应用环境中要进行可靠性评估。

注意事项在使用电力MOS场效应晶体管时,需要注意以下几点:1.正确的驱动电压和电流:要根据晶体管的数据手册选择合适的驱动电压和电流,避免超过额定值。

POWER MOSFET与IGBT之基础知识

POWER MOSFET与IGBT之基础知识今天,POWER MOSFET(POWER METAL OXIDE SEMICONDUCTOR FIELD EFFECT TRANSISTOR:大功率金属氧化物半导体场效晶体管)已成为大功率元件(POWER DEVICE)的主流,在市场上居于主导地位。

以计算机为首之电子装置对轻薄短小化以及高机能化的要求带动POWER MOSFET的发展,此一趋势方兴未艾,技术之进步永无止境。

在庞大计算机市场支撑之下,IC 开发技术人员在「大功率元件采用单晶IC(MONOLITHIC)技术」方面促成了MOS系大功率元件的突破。

尤其是低耐压大功率MOSFET,随者其母体“MOS IC”之集积度的提高而性能大增(双极晶体管﹝BIPOLAR TRANSISTOR﹞无法达到)。

大功率MOSFET的动作原理十分容易了解,适合于驱动电路及保护电路等制成IC。

大功率元件(POWER DEVICE)不可避免地会发热,在此情况下,POWER MOSFET的MOS(METAL OXIDE SEMICONDUCTOR)系闸极(GATE)四周围绕的绝缘膜(材质通常为SiO2)的质量决定其特性及可靠度。

在元件技术及应用技术确立之时期,开发完成“AVALANCHE FET”并付诸生产,此种元件即使是在崩溃(AVALANCHE)之情况下也不会发生破坏。

之后,大功率MOSFET(POWER MOSFET)剩下的未解决课题是高耐压化,1998年在市场崭露头角的“COOL MOS”将业界水平一举提高至相当高的层次。

AVALANCHE FET 及COOL MOS可以说是确定MOS系大功率元件之评价的两大支柱。

在当初,IGBT(INSULATED GATE BIPOLAR TRANSISTOR)期待只将NCH POWER MOSFET 的基片(SUBSTRATE)的极性从n型变更成p型就能够实现高耐压、大电流元件,但是,IGBT 在本质上为双及元件(BIPOLAR DEVICE),对于单及元件(UNIPOLAR DEVICE)POWER MOSFET 世代的技术人员而言较为难以了解。

电力电子半导体器件(MOSFET)解读

2.隔离驱动电路:电磁隔离,光电隔离;

3.实用驱动电路及保护电路

种类很多:正反馈型,窄脉冲自保护型,高速关断型; 常用,如双PNP管驱动电路;

保护电路:采样漏极电压,与控制脉冲比较,实现保护。 SBD

过流检测

双绞线

三、MOSFET并联: 具有正温度系数沟道电阻,并联时可利用这一特性均流。 一般,静态电流均衡问题不大,关键是动态电流均衡分配,

3.影响开关时间的因素:

①极间电容;

②寄生电感; ③VDS电压; ④ID电流; ⑤ 驱动源参数(内阻)

4.dv/dt对MOSFET动态性能影响 ①静态dv/dt:会引起MOSFET栅极电压变 化,导致错误开通。在栅源间并联电阻, 可防止误开通。 ②动态dv/dt:回路中电感在MOSFET关 断时,引起动态dv/dt;工作频率越高, 负载等效电感越大,器件同时承受大的 漏极电流和高漏极电压,将导致器件损 坏。 加吸收回路,减小引线长度,采用谐 振型电路,可抑制dv/dt

如:开通、关断、窄脉冲下的峰值电流。

解决方法: ①选择器件,参数尽量一致;gm VT Ron

②并联MOSFET各栅极用电阻分开;串入电阻大于栅极电阻。 ③栅极引线设置磁珠,形成阻尼环节。

④漏极间接入几百PF电容,改变耦合相位关系

⑤源极引入适当电感 ⑥ 精心布局,器件对称,连线长度相同,驱动线双绞、等长。

六、MOSFET与GTR比较

§5.3 栅极驱动和保护

一、栅极驱动特性 与GTR相比,驱动功率小,电路简单。

1.理想栅极驱动电路:要求电路简单,快速,具有保护功能。

栅极为容性网络,驱动源输出电阻直接影响开关速度。

Ron,Roff输出电阻 正电压开通 负电压关断

2.驱动特性

四种典型全控型器件比较

四种典型全控型器件的比较四种典型全控型器件的比较一、 对四种典型全控型器件的介绍1、门极可关断晶闸管(GTO ) 1)GTO 的结构与工作原理芯片的实际图形 GTO 结构的纵断面 GTO 结构的纵断面 图形符号GTO 的内部结构和电气图形符号2)工作原理:设计α2较大,使晶体管V2控 制灵敏。

导通时α1+α 2= 1.05更接近1,导通时接近临界饱和,有利门极控制关断,但导通时管压降增大。

多元集成结构,使得P2基区横向电阻很小,能从门极抽出较大电流。

下图为工作原理图。

22222、电力晶体管(GTR) 1)电力晶体管的结构:R NPNPNPA G SK E GI G E AI K I c2I c1I A V 1V 2b)内部结构电气图形符号NPN型电力晶体管的内部结构及电气图形符号2)工作原理:在电力电子技术中,GTR主要工作在开关状态。

晶体管通常连接成共发射极电路,GTR通常工作在正偏(I b>0)时大电流导通;反偏(I b<0)时处于截止状态。

因此,给GTR的基吸施加幅度足够大的脉冲驱动信号,它将工作于导通和截止的开关状态。

3、电力场效应晶体管(Power MOSFET)1)电力MOSFET的结构MOSFET元组成剖面图图形符号电力MOSFET采取两次扩散工艺,并将漏极D移到芯片的另一侧表面上,使从漏极到源极的电流垂直于芯片表面流过,这样有利于减小芯片面积和提高电流密度。

2)电力MOSFET的工作原理:当漏极接电源正极,源极接电源负极,栅源极之间电压为零或为负时,P型区和N-型漂移区之间的PN结反向,漏源极之间无电流流过。

如果在栅极和源极间加正向电压U GS,由于栅极是绝缘的,不会有电流。

但栅极的正电压所形成的电场的感应作用却会将其下面的P 型区中的少数载流子电子吸引到栅极下面的P型区表面。

当u GS大于某一电压值U GS(th)时,栅极下面的P型区表面的电子浓度将超过空穴浓度,使P型反型成N型,沟通了漏极和源极。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

POWER MOSFET 隔离驱动

对于上下管占空比相等的隔离驱动,可以不需要隔直电 容,但必须保证在任何情况下,驱动变压器不饱和。

POWER MOSFET 隔离驱动

10 8 6

R12 10u R1 TX1 C1 P1 S1 Q1 10k R2

4

Vg / V

Vg V1

V2

2 0 -2 -4 -6 -8 -10 0 0.2 0.4 0.6 0.8 1 1.2

寄生参数对并联驱动的影响

25 20

A

15 10 5 -0 10 8

I(Q3-D)

I(Q4-D)

Q4-G

Q3-G

V

6 4 2 -0 270 Time/uSecs

270.1

270.2

270.3

270.4

270.5 100nSecs/div

10n L3

10n L4

R8

25 20 15 10 5 -0

I(Q4-D) I(Q3-D)

常用的加速关断电路

IC

U1 Ref v Vp Osc Vf b Vout Comp Sense Gnd D1 Q1

Comp Sense Gnd Ref v Vp Osc Vf b Vout D2 U2 R2 Q2 Q3

R1

• 电路简单 • 关断电流将流过芯片

• 关断电流通过Q3构成回 路,关断电流环路小 • 开关G极电位不能到0

CBOOT

QTOTAL QG ( I LK ,D IQ,LS IQ,DRV IGS ) toff max VBOOT VBOOT

其中:QG ----------栅极电荷 ILK,D -------自举二极管漏电流 IQ,LS ------- 内部电平转换静态电流 IQ,DRV ------自举电路静态电流 IGS ---------- G-S间漏电流

POWER MOSFET 开通过程

to-t1: 驱动通过Rgate 对Cgs充电, Vgs 电压以指数形式上升

POWER MOSFET 开通过程

I d (VGS Vth ) g fs

t1-t2: Vgs 达到MOSFET开启门槛电压, MOSFET 进入线性区,Id缓慢上升

POWER MOSFET 开通过程

A

620 Time/uSecs

625

630

635

640

645

650 5uSecs/div

POWER MOSFET 并联驱动

MOSFET 并联驱动的注意事项

• 并联MOSFET的特性应完全一致。 • 并联MOSFET的驱动布线应尽量对称。 • 并联MOSFET应有独立的驱动电阻或图腾柱,并尽量靠近 MOSFET栅极 • 如果并联MOSFET驱动发生震荡,可在MOSFET的栅极套磁 珠,并适当增大驱动电阻。

POWER MOSFET 隔离驱动

隔离驱动变压器的要求

• 信号延迟小,寄生电容小 • 漏感小,波形失真小 • 高低压侧可靠绝缘

POWER MOSFET 隔离驱动

隔离驱动变压器的设计

1. 选择合适的磁芯 2. 计算原边匝数

3. 选择线径,通常情况下,最好是能一层绕完一个绕组。

4. 确定绕组排布

POWER MOSFET 并联驱动

2)由于自举二极管工作在高频开关状态,因此需选用高压快恢复二极管

POWER MOSFET 自举驱动

占空比对自举电压的影响

POWER MOSFET 自举驱动

源极负压对于电路的影响

POWER MOSFET 自举驱动

减小源极负压对电路影响的方法

能一定程度缓解源极负压对电路 的影响,但是会使得自举电容充电时 间常数变长

A

2.2 V3 R10

100m R3 100m R4

10n L1 100n L2 10kQ3 R7 Q4 10k R6

Q4-G

V5

8 4 0 -4 655 655.02 655.04 655.06 655.08 655.1 655.12 655.14

V

Q3-G

Time/uSecs

20nSecs/div

MOSFET的关断过程是开通过程的反过程。

POWER MOSFET 驱动电流

Qg Qgs Qgd Qod

Qg Qg ig dt Qg I g ts I g t s

0

V R C ig dr e g eff Rg t

ts

V dr i gpk Rg

等效电路中的 Ceff 为等效输入电容,并 不等于 Ciss

500.1

500.15

500.2

500.25

500.3

500.35

Time/uSecs 30 25

20 15 10 5 -0 8

50nSecs/div

V

并联MOSFET使用单独的驱动 电阻可以改善并联均流问题

A

4 0 -4 605 Time/uSecs 605.05 605.1 605.15 605.2 605.25 605.3 605.35

MOSFET的驱动电压与占空比有关, 应确保在最大ห้องสมุดไป่ตู้空比时有足够的驱 动电压。

VGS

VDRV VC VDRV D VDRV 1 D VDRV n n n

POWER MOSFET 隔离驱动

变压器匝比为1,MOSFET的G-S间电 压与占空比无关。

VGS

VDRV VC n 1 VC VD VGS VDRV VD n

开关模型: 描述了MOSFET的重要寄生参数

POWER MOSFET 寄生参数

CRSS ,ave 2 CRSS ,spec VDS , spec VDS ,off VDS ,spec VDS ,off

COSS ,ave 2 COSS ,spec

CGD CRSS ,ave CGS CISS CRSS CDS COSS ,ave C RSS ,ave

POWER MOSFET 并联驱动

Vth对并联驱动的影响 如果Vth1<Vth2

10n L8 10n L11 R11

12 10

S1-CP / V

8 6 4 2 0 40 30 20 10 0 -10 -20

10 V4 R10 10 R16

S1

S2 V6

MOSFET并联驱动时,应尽可 能保证MOSFET的Vth一致: • MOSFET 特性完全一致 • MOSFET的温度一致

V5

V

310

310.05

310.1

310.15

310.2

310.25

310.3

310.35

310.4

Time/uSecs

20 16

50nSecs/div

A

12 8 4

在MOSFET的栅极串联一个磁 珠并增大驱动电阻可以很好 的改善MOSFET的并联效果。

-0 8 4

V

0 -4 -8 615 Time/uSecs 615.1 615.2 615.3 615.4 615.5 100nSecs/div

ZVS 电路中POWER MOSFET 开通过程

在ZVS电路或同步整流电路中,MOSFET驱 动没有米勒平台。

POWER MOSFET 驱动电阻的影响

增大驱动电阻的影响

12

10

8

D1

V2 Q1-G V1 R1 Q1 I1

Q1-G / V

Rgate 增大

6 4

2

-0 240 Time/uSecs 240.1 240.2 240.3 240.4 100nSecs/div

POWER MOSFET 驱动技术

1

2 3

POWER MOSFET 直接驱动

POWER MOSFET自举驱动

POWER MOSFET隔离驱动

4

POWER MOSFET 并联驱动

POWER MOSFET 的结构

N-MOSFET 结构示意图

POWER MOSFET 等效模型

动态模型: 描述了dV/dt的影响

能有效减小源极负压的影响, 但是同样使得自举电容充电时间变 长

POWER MOSFET 自举驱动

减小寄生电感的方法 • 开关之间的走线不形成回路

• 减小开关管的走线长度 • 自举二极管应尽可能靠近自举电容 • 去耦电容和栅极驱动电阻应尽可能靠近栅极驱动集成电 路。

POWER MOSFET 隔离驱动

10

2MHertz/div

Spectrum(Q1-G (tran19)) / V

1 100m 10m 1m 100u 10u

Rgate 增大

2 -0 450

0 0.5 1 1.5 2 2.5 3 3.5 4

450.02 450.04 450.06 450.08

450.1

450.12 450.14 450.16 20nSecs/div

驱动上升变慢,开关过程延长,开关损耗增大。

POWER MOSFET 驱动电阻的影响

减小驱动电阻的影响

10 1 100m

Spectrum(Q1-G) / V

10m 1m 100u 10u 1u 100n 0 2 4 6 8 10 12 14 16

16 14 12

Q1-G / V

10 8 6 4

Frequency/MHertz

t2-t3: Id达到稳定值,Vgs固定不变,Vds 电压开 始下降,VDD给Cgd提供放电电流。(米勒效应)

POWER MOSFET 开通过程

t3-t4: Vds下降到0V,MOSFET完全导通,VDD继续给Cgs充 电,直至Vgs=Vdd,MOSFET完成开通过程。