李玉山信号完整性分析PPT

04第四讲阻抗测试原理

17

射频电路测试原理 清华大学电子工程系 李国林 雷有华 2012年春季学期

复数阻抗与导纳

施加正弦信号---幅度、相位

Z V Z R jX

I

阻抗 impedance

Y I Y G jB

V

导纳 admittance

G

电导

conductance

R

jX

电阻

电抗

resistance reactance

阻抗测试

电阻+电抗:阻抗幅度+相位 电导+电纳:导纳幅度+相位

电感+Q值 电容+D值

21

射频电路测试原理 清华大学电子工程系 李国林 雷有华 2012年春季学期

为何测试不能保持一致性?

三、阻抗测试中的不确定性

Q : 165

Z Analyzer

Q : 165

? Q = 120

Q : 120

电磁干扰

EMI

电磁干扰问题包含三个方面:噪声源、辐射传 播路径和天线

前面的三个信号完整性问题的根源也是电磁辐射的 根源

即wk.baidu.com噪声远远低于完整性噪声预算,它仍有可能引 发严重的辐射

产生辐射的大多数电压源来自于电源和地分配 网络,减小轨道塌陷噪声也能降低辐射

IO接头的阻抗,特别是返回路径的插件连接头 的阻抗,会严重影响噪声电压,并引发辐射电 流

李玉山_信号完整性(SI)分析1-2

同层屏蔽线

Gnd

Hale Waihona Puke Baidu

VDD

屏蔽层

Gnd

衬底层(Gnd) 图0-11 对抗线间串扰的屏蔽措施剖面说明

图0-12 为了减小电感,实际去耦电容过孔的安装情况

VDD

板线 键合线

芯片内 核

去耦电容

Gnd

图0-13 去耦电容消除地弹,仍不如芯片内去耦

图0-14

电缆外加装扼流圈防止EMI

0.5 信号完整性分析技术

信号完整性(SI)可以泛指由互连线引起的所有信

号电压电平和电流不正常现象,包括:噪声、干扰

和时序等。

狭义的信号完整性,是指信号电压(电流)波形的

形状及质量,包括反射和串扰。由于物理互连造成的

干扰和噪声,使得连线上信号的波形外观变差,出

现了非正常形状的变形,称为信号完整性被破坏。

信号完整性问题是物理互连在高速情况下的直接

0.7 用于分析的传输线模型

传输线(transmission line)是一个网络(导线), 它的返回路 径可能是地、电源等。 设计高速 PCB,用一半精力关注互连。采用传输线模型,考 察传输线效应。 设计师从传输线的角度设计互连已经到 90% PCB 以上。在设计中引入特性阻抗及匹配、反射、驻波等概念分析。 互连线本质上就是传输线。一条为信号线(Signal path),另 一条为返回线(Return path),返回线不能理解成地线。设计信 号线,也要设计返回线物理尺寸,让返回线靠近信号线等。 按传输线的概念看待互连,才容易用阻抗观点理解反射;用 回路互感理解串扰;用净电感理解地弹等等。

信号完整性分析PPT课件

Olica

4

SI简介

• 学习SI的目的 a.什么是典型的信号完整性问题? b.这些问题来自哪里? c.为什么有必要去理解SI问题? d.如何去分析和解决SI问题? e.如何去做SI测试?

30.11.2020

Olica

5

• SI的内容 SI简介

信号完整性它包含两方面的内容,一是 独立信号的质量,另一个是时序。我们 在电子设计的过程中不得不考虑两个问 题:信号有没有按时到达目的地?信号 达到目的地后它的质量如何?所以我们 做信号完整性分析的目的就是确认高频 数字传输的可靠性。

30.11.2020

Olica

19

石英晶体振荡器的类型特点

• 国际电工委员会(IEC)将石英晶体振荡器分为4类: 普通晶体振荡(TCXO),电压控制式晶体振荡器 (VCXO),温度补偿式晶体振荡(TCXO),恒温控 制式晶体振荡(OCXO)。目前发展中的还有数字补 偿式晶体损振荡(DCXO)等。

30.11.2020

联想蓝

黑色

中灰

绿色

Think红

30.11.2020

Olica

14

方波的组成

联想蓝

黑色

中灰

绿色

Think红

30.11.2020

Olica

15

晶振原理

• 石英振荡器结构

30.11.2020

信号完整性分析 ppt课件

SI对国内是既生疏又熟悉。原先对付干扰、噪声的 “三大法宝”是:接地、滤波、屏蔽,显得非常感性 和粗放,已经严重落后。现在对SI量化和细化的研究 逐渐呈现出浓厚的热情,已经有了一定的基础。

电子设计师需要普及SI知识,了解高速电路互连的 SI机理,掌握SI分析与互连设计。

●高速条件下的不当互连设计破坏了信号完整 性。

正是信号完整性引出了发生在我们身边的深刻 变化。面对下列事实,需要想一想:

●为什么计算机配置中用USB2.0接口取代了打印 机并口?

●为什么新的FPGA芯片中增加了RSDS(降低摆幅 差分信令)、LVDS(低压差分信令)模块及接口设计?

●什么样的接口更适合严酷的实时图像信号采集 与传输? 是USB还是IEEE1394?是1394a还是b?

图0-7 互连线的远端和近端串扰情况

电源噪声主要指同步开关噪声(SSN)。 地弹是返回路径中两点之间的电压,它是由于 回路中电流突然变化而产生的。当流经接地回路 电感上的电流变化时,在接地回路导线上产生的

电压称之为地弹。

电源分布系统(PDS)中轨道塌陷,是指由于地/电 源网络中阻抗上的压降引起末端受供电器件端的 净电压不足或过高。

• Ansoft: HFSS(高频结构仿真器)、SI2D

信号完整性分析

李玉山信号完整性分析

《信号完整性培训》课件

目录

• 信号完整性的基本概念 • 信号完整性的问题及解决方法 • 信号完整性分析工具及方法 • 信号完整性设计原则与技巧 • 总结与展望

01

信号完整性的基本概念

信号完整性的定义

01

信号完整性是指在电子系统中的 信号在传输过程中保持其应有的 特性、质量和幅度的能力。

高速数字信号传输设计

01

介绍如何运用信号完整性原则和技巧,设计高速数字信号传输

系统。

模拟信号处理中的信号完整性

02

探讨在模拟信号处理中如何保持信号完整性,提高信号质量。

实际项目中的信号完整性问题解决案例

03

分享在实际项目中遇到的问题及解决方法,总结经验教训。

05

总结与展望

信号完整性问题的挑战与机遇

合理选择传输线

根据信号类型和传输速率,选择合适的传输 线类型和规格。

使用适当的端接方式

根据传输线的类型和长度,选择合适的端接 方式,如串联端接、并联端接等。

优化布线策略

通过合理的布线,减少信号延迟和反射,提 高信号质量。

抑制电磁干扰

通过增加屏蔽、使用滤波器等手段,降低电 磁干扰对信号的影响。

设计实例分享

电源和地平面

电源和地平面上的噪声和不连 续性也会对信号完整性产生影

响。

02

信号完整性的问题及解决方法

信号与电源完整性分拆与设计-李玉山第7讲

信号及电源完整性分析与设计[Chapter7]第七讲传输线设计及接地、过孔分析西安电子科技大学电路CAD研究所 李玉山1

7.0引言美国90%工程师按传输线设计互连。说到底,传输线 是一种场的简化概念!关注的是互连的阻抗、时延和信号 的波形! 准确分析高速互连的SI,要从认识传输线开始! 传输线三种阻抗万变不离其宗,仍是阻抗的基本定义 。只不过将传输线始端的输入阻抗简称为阻抗;将信号随 时遇到的及时阻抗称为瞬时阻抗。如果在信号前进过程中 ,传输线的横截面,包括信号路径与返回路径几何结构都 不变的均匀传输线,则称其为特性阻抗。2

一般的传输线都是由两条有一定长度的导线组成。图7.1给出传输线概念的本质特点,把一条称为信号 路径,另一条称为返回路径。图7.1 传输线由任意两条有一定长度的导线组成。其中一条标记为 信号路径,另一个为返回路径3

一种糊涂认识:线电阻怎么是50Ω?是并联还是串联? 注意,这里应是阻抗而非电阻! 传输线的两个重要特征:特性阻抗和时延(低速场合均被忽略而已),说的都是:传输线对信号的作用。理想传输线模型 (彻底的分布式)性能与实际互连实测性 能更加吻合;模型带宽相当高。理想传输线也可以用R-LG-C集总参数组合近似。 理想传输线是仿真工具箱中的一种新的电路元件,用于 仿真效果较好,但电路概念不够简明易懂。4

7.1返回路径不同于“接地”以往我们简单地将“地”当作传输线返回路径。 信号完整性设计中,最忌讳的就是滥用“地”这一名词。 应习惯于把其他导体看作是返回路径。事实上,中央 “ 地 ” 已经难觅,更多的是本地“地”。 电源布线主要考虑SSN,不要让多个返回路径形成“大 合唱”。理想情况下每个信号都有单独的返回地路径。即 使一般情况下信号与地引脚比率为8:1(认为电源引脚数=地引脚数);超高速互连则要求这一比率为2:1。5

mjt-信号完整性分析课件01-Signal+Integrity

1.Silicon chip

Wafer 代工厂

2. Packaging

What is package? What does it use for?

Advance in package

Wire bond interconnect

TSV interconnect

3. PCB--provide interconnect for package-to-package/component-to-

Signal integrity, SI

All the effects listed above, associated with signal-integrity noise problems, are related to one of the following four unique families of noise sources:

weeks) • 3. Physical basis of transmission line. (2 weeks) • 4.Reflection of a transmission line. (2 weeks) • 5. Lossy lines, Rise time degradation, and eye diagram

Ironically, this is an era when not only are clock frequencies increasing and signal integrity problems getting more severe, but the time design teams have available to solve these problems and design new products is getting shorter. Product design teams have one chance to get a product to market; the product must work successfully the first time. If identifying and eliminating signal integrity problems isn’t an active priority as early in the product design cycle as possible, chances are the product will not work.

李玉山信号完整性分析34 83页PPT文档

图 2.4 1GHz 时钟信号时域中一个周期 (上);DFT 后频域表示(下)

快速傅里叶变换(FFT)和离散傅里叶变换(DFT)本质上 是一回事。快速傅里叶变换的计算速度比普通的离散傅里 叶变换可以快 100~10,000 倍。

傅里叶级数(FS)将周期性波形变换到频域中。其中基本 的假设就是原始的时域波形,每隔 T 秒重复一次。不采用 积分运算,此处使用的是求和,用简单的数学方法就可以 将任意一组数据变换到频域。

2.7 理想方波的傅里叶级数

从理想方波的频谱中可以得到有用的信息,运用这些信 息可以估计实际波形。

理想方波是对称的,其占空比是 50%,并且峰值为 1v, 如图 2.6 所示。

Time domain ──时域

Period──周期

Amplitude

──幅度

Harmonic Number──谐波次数 Frequency Domian──频域

记

2 T2

2nπt

an = T

−T

f

2

t cos

T

dt

2 T2

2nπt

bn = T

−T

f

2

t sin

T

dt

(n = 0,1,2,3, … … ) (n = 1,2,3, … … )

则 f(t)的 FS 展开式为:

∞

������ ������

信号完整性分析实验报告_西电李玉山,路建民老师剖析

实验一反弹图像的仿真

一、实验原理

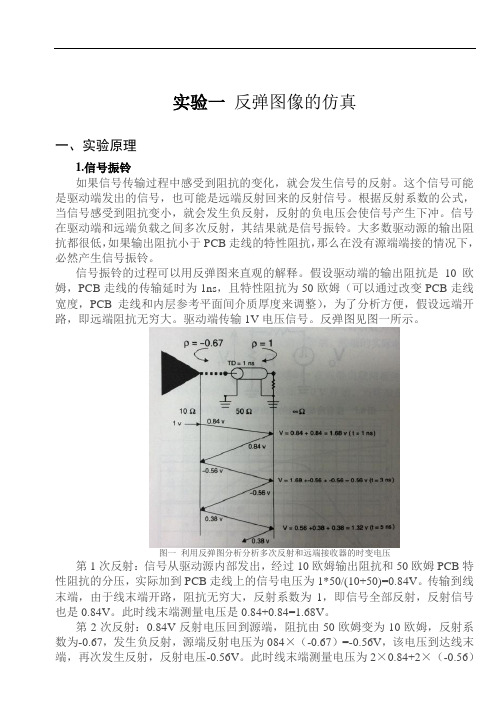

1.信号振铃

如果信号传输过程中感受到阻抗的变化,就会发生信号的反射。这个信号可能是驱动端发出的信号,也可能是远端反射回来的反射信号。根据反射系数的公式,当信号感受到阻抗变小,就会发生负反射,反射的负电压会使信号产生下冲。信号在驱动端和远端负载之间多次反射,其结果就是信号振铃。大多数驱动源的输出阻抗都很低,如果输出阻抗小于PCB走线的特性阻抗,那么在没有源端端接的情况下,必然产生信号振铃。

信号振铃的过程可以用反弹图来直观的解释。假设驱动端的输出阻抗是10欧姆,PCB走线的传输延时为1ns,且特性阻抗为50欧姆(可以通过改变PCB走线宽度,PCB走线和内层参考平面间介质厚度来调整),为了分析方便,假设远端开路,即远端阻抗无穷大。驱动端传输1V电压信号。反弹图见图一所示。

图一利用反弹图分析分析多次反射和远端接收器的时变电压

第1次反射:信号从驱动源内部发出,经过10欧姆输出阻抗和50欧姆PCB特性阻抗的分压,实际加到PCB走线上的信号电压为1*50/(10+50)=0.84V。传输到线末端,由于线末端开路,阻抗无穷大,反射系数为1,即信号全部反射,反射信号也是0.84V。此时线末端测量电压是0.84+0.84=1.68V。

第2次反射:0.84V反射电压回到源端,阻抗由50欧姆变为10欧姆,反射系数为-0.67,发生负反射,源端反射电压为084×(-0.67)=-0.56V,该电压到达线末端,再次发生反射,反射电压-0.56V。此时线末端测量电压为2×0.84+2×(-0.56)

李玉山信号完整性分析PPT课件

信号与电源完整性分拆与设计-李玉山第9讲

信号及电源完整性分析与设计[Chapter9]第九讲有损线带宽、抖动与数据完整性西安电子科技大学电路CAD研究所李玉山1

9.0高频损耗引起数据误码单纯传输,数据信号经过长线后,上升边退化。图9.1 是上升边 RT=50ps 信号在 FR4 上经过 36in 、 50Ω线后的波 形。除延迟外,上升边几乎拉长到2ns。这种退化将引起 数据 0/1 符号间干扰 (Intersymbol Interference , ISI) 和误码 。图9.1RT=50ps的信号入经50Ω、36in长线后为RT=1ns的信号出2

当时钟频率高于1GHz、传输长度超过10in时,例 如高速链路(Serial Link)和千兆以太网,数据误码 主要是传输线损耗引起(机载、星载设备中同类问题很多)。误码的主要原因是:数据信号幅度的塌陷退化直 接影响0/1的阈值判决;时序上的交叠抖动妨碍0/1的 判决时刻(其实,前一讲的时延ΔTD不仅有时延,也有上升边的退化含义,只是未单独讨论)。3

一般,频域中分析高频损耗比较简单。例如:频域 中上升边退化变长等价于:信号高频分量的衰减比低 频分量衰减大得多。 下面分析传输线损耗的思路是:首先,在频域中理 解损耗机理;然后,再到时域中估计它对信号完整性 的影响 (本讲主要考察两种损耗:导线损、介质损及其对退化的影响分析)。4

9.1有损线的退化作用若信号损耗与频率无关,即低频、高频时相同。整个信 号的幅度会统一降低,波形形状则继续保真。图9.2指出: 这种常量型衰减不会造成信号上升边退化和时序抖动。图9.2当损耗与频率无关时,上升边为100ps的信号传播后波形形状不变5

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。