MOS结构准静态C-V特性测量

MOS结构C-V特性测量及BT实验

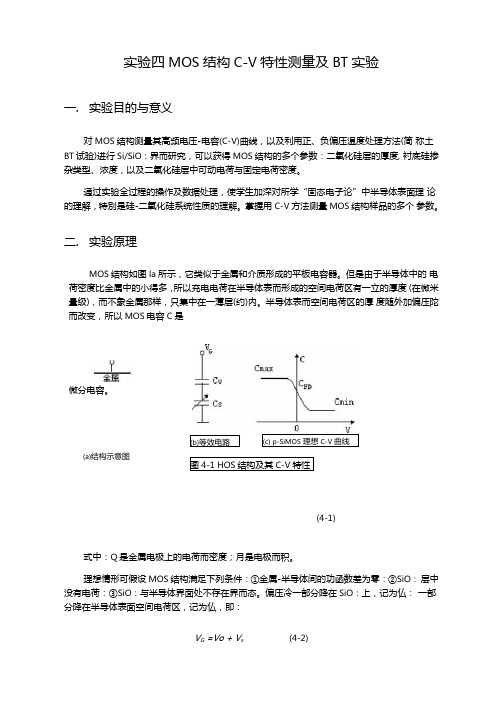

实验四 MOS 结构C-V 特性测量及BT 实验一. 实验目的与意义对MOS 结构测量其高频电压-电容(C-V )曲线,以及利用正、负偏压温度处理方法(简称±BT 试验)进行Si/SiO 2界面研究,可以获得MOS 结构的多个参数:二氧化硅层的厚度,衬底硅掺杂类型、浓度,以及二氧化硅层中可动电荷与固定电荷密度。

通过实验全过程的操作及数据处理,使学生加深对所学“固态电子论”中半导体表面理论的理解,特别是硅-二氧化硅系统性质的理解。

掌握用C-V 方法测量MOS 结构样品的多个参数。

二. 实验原理MOS 结构如图1a 所示,它类似于金属和介质形成的平板电容器。

但是由于半导体中的电荷密度比金属中的小得多,所以充电电荷在半导体表面形成的空间电荷区有一定的厚度(在微米量级),而不象金属那样,只集中在一薄层(约)内。

半导体表面空间电荷区的厚度随外加偏压V G 而改变,所以MOS 电容C 是微分电容。

(a) 结构示意图 (b) 等效电路 (c) p-SiMOS 理想C-V 曲线图4-1 MOS 结构及其C-V 特性G G dv dQ A C = (4-1)式中: Q G 是金属电极上的电荷面密度;A 是电极面积。

理想情形可假设MOS 结构满足下列条件:① 金属-半导体间的功函数差为零;② SiO 2层中没有电荷;③ SiO 2与半导体界面处不存在界面态。

偏压V G 一部分降在SiO 2上,记为Vo ;一部分降在半导体表面空间电荷区,记为Vs ,即:S G V Vo V += (4-2)Vs 又称为表面势。

考虑到半导体空间电荷区电荷和金属电极上的电荷数量相等、符号+相反,有:G s Q Q = (4-3)式中:Qs 为半导体表面空间电荷区电荷面密度。

将(4-2)、(4-3)代入(4-1)式,有:S O G G G dV dV dQ A dV dQ A C +==SO S O C C C C += (4-4) 式(4-4)表明MOS 电容是C 0和Cs 串联而成,其等效电路为图4-1 的b 所示。

MOS结构C-V特性测量及BT实验

实验四 MOS 结构C-V 特性测量及BT 实验一. 实验目的与意义对MOS 结构测量其高频电压-电容(C-V )曲线,以及利用正、负偏压温度处理方法(简称±BT 试验)进行Si/SiO 2界面研究,可以获得MOS 结构的多个参数:二氧化硅层的厚度,衬底硅掺杂类型、浓度,以及二氧化硅层中可动电荷与固定电荷密度。

通过实验全过程的操作及数据处理,使学生加深对所学“固态电子论”中半导体表面理论的理解,特别是硅-二氧化硅系统性质的理解。

掌握用C-V 方法测量MOS 结构样品的多个参数。

二. 实验原理MOS 结构如图1a 所示,它类似于金属和介质形成的平板电容器。

但是由于半导体中的电荷密度比金属中的小得多,所以充电电荷在半导体表面形成的空间电荷区有一定的厚度(在微米量级),而不象金属那样,只集中在一薄层(约0.1nm )内。

半导体表面空间电荷区的厚度随外加偏压V G 而改变,所以MOS 电容C 是微分电容。

(a) 结构示意图 (b) 等效电路 (c) p-SiMOS 理想C-V 曲线图4-1 MOS 结构及其C-V 特性G G dv dQ A C = (4-1) 式中: Q G 是金属电极上的电荷面密度;A 是电极面积。

理想情形可假设MOS 结构满足下列条件:① 金属-半导体间的功函数差为零;② SiO 2层中没有电荷;③ SiO 2与半导体界面处不存在界面态。

偏压V G 一部分降在SiO 2上,记为Vo ;一部分降在半导体表面空间电荷区,记为Vs ,即:S G V Vo V += (4-2)Vs 又称为表面势。

考虑到半导体空间电荷区电荷和金属电极上的电荷数量相等、符号相反,有:G s Q Q = (4-3)式中:Qs 为半导体表面空间电荷区电荷面密度。

将(4-2)、(4-3)代入(4-1)式,有:+3 1 2 0 S O G G G dV dV dQ A dV dQ A C +==SO S O C C C C += (4-4) 式(4-4)表明MOS 电容是C 0和Cs 串联而成,其等效电路为图4-1 的b 所示。

详解半导体器件C-V特性测试

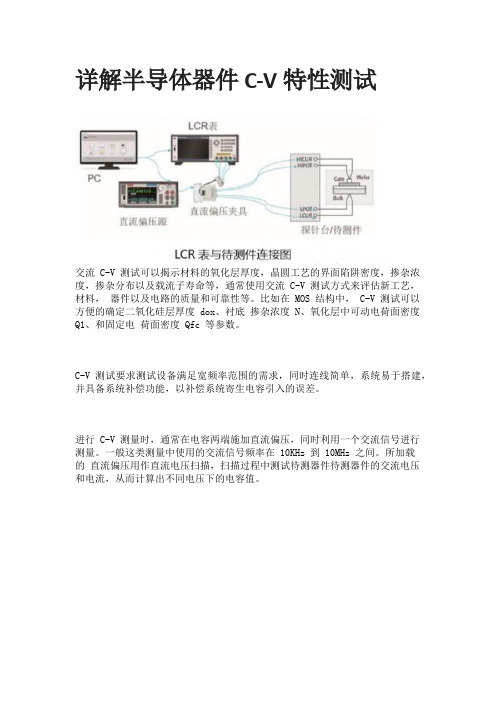

详解半导体器件C-V特性测试交流 C-V 测试可以揭示材料的氧化层厚度,晶圆工艺的界面陷阱密度,掺杂浓度,掺杂分布以及载流子寿命等,通常使用交流 C-V 测试方式来评估新工艺,材料,器件以及电路的质量和可靠性等。

比如在 MOS 结构中, C-V 测试可以方便的确定二氧化硅层厚度 dox、衬底掺杂浓度 N、氧化层中可动电荷面密度Q1、和固定电荷面密度 Qfc 等参数。

C-V 测试要求测试设备满足宽频率范围的需求,同时连线简单,系统易于搭建,并具备系统补偿功能,以补偿系统寄生电容引入的误差。

进行 C-V 测量时,通常在电容两端施加直流偏压,同时利用一个交流信号进行测量。

一般这类测量中使用的交流信号频率在 10KHz 到 10MHz 之间。

所加载的直流偏压用作直流电压扫描,扫描过程中测试待测器件待测器件的交流电压和电流,从而计算出不同电压下的电容值。

在 CV 特性测试方案中,同时集成了美国吉时利公司源表(SMU)和合作伙伴针对 CV 测试设计的专用精密 LCR 分析仪。

源表 SMU 可以输出正负电压,电压输出分辨率高达 500nV。

同时配备的多款 LCR 表和 CT8001 直流偏置夹具,可以覆盖 100Hz~ 1MHz 频率和正负 200V 电压范围内的测试范围。

方案特点:★包含 C-V(电容–电压),C-T(电容–时间),C-F (电容–频率)等多项测试测试功能,C-V 测试最多同时支持测试四条不同频率下的曲线★测试和计算过程由软件自动执行,能够显示数据和曲线,节省时间★提供外置直流偏压盒,最高偏压支持到正负 200V,频率范围 100Hz –1MHz。

★支持使用吉时利 24XX/26XX 系列源表提供偏压测试功能:电压–电容扫描测试频率–电容扫描测试电容–时间扫描测试MOS 器件二氧化硅层厚度、衬底掺杂浓度等参数的计算原始数据图形化显示和保存MOS 电容的 C-V 特性测试方案系统结构:系统主要由源表、LCR 表、探针台和上位机软件组成。

C-V特性-MOS管原理半导体物理与器件

2019/12/7

相当于金属电容与半导体电容串联 电阻越串越大,电容越串越小

1.2 C-V特性

电容-电压特性测试曲线

理想MOS电容C-V特性

测量电源:MOS外加栅压,在直流电压上叠加一交流小信号电压。

直流电压:决定器件工作点,调整大小使MOS先后处于堆积、平带、 耗尽、本征、反型几种状态

2019/12/7

禁带中央:CV曲线实虚线重和

2019/12/7

1.2 C-V特性

例图:需要额外牺牲三个负电荷 来中和界面态的正电

界面陷阱的影响:本征前

+++ ------

---

201199//1122/7/7

本征态

本征之前:EFi>EF,总有施主态在EFS之 上,施主态失去电子界面陷阱带正电。 正施主态数量是栅压的函数。 C-V曲线左移,左移量随栅压不等

黑(灰)色部分可以 理解为两种材料界面 或空间电荷区,一般 书中不画。

1.3MOSFET原理

MOSFET结构

绝缘栅场效应晶体管(Insulated Gate, IGFET): 栅极与其它电极之间是相互绝缘的。

例图:因为Qss均为正电荷, 需要额外牺牲负电荷来中和 界面的正电

++ -----

C'FB

tox

ox ox kT

tox e

s

eN a

2019/12/7

Qss ' VFB C V曲线左移,反之右移

1.2 C-V特性

界面陷阱的分类

被电子占据(在EFS之下)带负电,不被电子占据(在EFS之上)为中 性

CV特性概念和CV特性测试原理 MOS电容在不同半导体表面状态下的特点和公式 频率特性 高低频情况图形及解释 思考:若直流电压变化快,CV曲线如何?

实验报告2

实验一MOS电容的C-V特性测量及氧化层厚度、界面态密度等参数的提取微电子系00848067 曹宇一、实验目的1、测量MOS电容高频和低频时的C-V曲线2、利用C-V曲线进行栅氧化层厚度t ox、氧化层电荷和界面态密度D it、平带电压V fb、硅衬底掺杂浓度等参数的提取。

二、实验原理MOS电容如图1所示,它类似于金属和介质形成的平板电容器。

但是,由于半导体中的电荷密度比金属中的小得多,所以充电电荷在半导体表面形式的空间电荷区有一定的厚度(~微米量级),而不像金属中那样,只集中在一薄层中(~0.1nm)内。

半导体表面空间电荷区的厚度随偏压VG而变化,所以MOS电容是微分电容。

随着栅压的不同,MOS电容将处于不同的工作区:积累区、耗尽区和反型区。

三、实验内容1.掌握MOS电容的C-V特性测试原理和测试方法。

2.学习KeithleyModel 82-WIN 同步C-V测量仪的使用方法。

3.学习Model 82-WIN 同步C-V库的使用,并利用它提取界面陷阱电荷密度、可动离子浓度、掺杂浓度分布、平带电容、电压等。

四、实验仪器1.手动探针台2.KeithleyModel 82-WIN 同步C-V测试仪Keithley595QuasistaticCV Meter (595准静态CV仪)Keithley590 CV Analyzer (590 CV分析仪)Keithley230 Programmable Voltage Source (230可编程电压源)3.Metrics ICS五、典型C-V特性测量的步骤第一步漏电流和杂散电容修正第二步导线效应修正第三步配置测量系统第四步进行C-V测量第五步分析C-V数据配置测量系统:先连接测量元件。

一个好的探针台是不可少的。

把耦合器的同轴输入(Input)端与探针相连,输出(Output)端与底座相连。

进入Metrics ICS界面。

A.点击菜单行的Instruments按钮,出来一个下拉式菜单。

MOS C-V测试技术

一 理想 MOS c-v 特性

我们要了解为何通过测量 MOS 电容的 C-V 曲线,能确定 MOS 结构参数和电学性质,得首先了解理想 的 MOS 电容的 C-V 特性。 理想的 MOS 结构(见图 1b),即氧化物电荷 Qox = 0,金属功函数差Фms = 0。MOS 结构的电容 C 是氧 化层电容 Cox 和半导体空间电荷电容 Csc 的串联,见图 1b 的等效电路。 于是有:

1.40E-10

Ev V=0 时,n MOS 结构能带示意图

(6) (6')

1.20E-10

Cox

Ψs>0

1.00E-10

8.00E-11 C(pF)

CFB(ψS=0)

Ψs<0

高频 低频

6.00E-11

4.00E-11

ψS=2φF

ψ S= φ F Cmin

2.00E-11

0.00E+00 -5 -4 -3 -2 -1 0 V 1 2 3 4 电容的 C-V 特性

由 MOS 电容的最大值确定介质膜厚度

1) 由 Cmax 确定介质膜厚度 由理论 MOS 特性知道,在强积累区,MOS 的电容达到最大值并等于氧化层电容,即 C = Cmax = Cox = A・ε0・εox /tox 于是氧化层厚度 tox 由测试的最大电容确定: tox = A・ε0・εox/Cmax (15) 式中 A 为电容栅面积,ε0 为真空电容率,εox 为 SiO2 介电常数。对于重掺杂衬底的 MOS 电容或 Poly-Si 之间, Al—Poly-Si 之间及 Al—Al 之间的介质结构,它们相当于平行板电容器,只要测出其电容值(与偏压无关), 便可计算出介质膜的厚度: ti = A・ε0・εi / C (15') 这里εi 是该介质膜的介电常数。 2)Cmax 测试误差 实际测试中,由于样品制备不当或测试原因,可能引入串联电阻 R ,它使测试的电容 Cm 小于待测样品的电 容 C 。Cm 与 C 和 R 的关系如下: 2 2 2 Cm = C/(1+R ・ω ・C ) (16)

高频 MOS C-V 电容―电压特性测试

(16)

而单位面积SiO2中的可动电荷数目为:

Qm = Cox( VFB2 - VFB3 ) = C ox . ΔVFB

(17)

由于可动电荷是正一价的Na+离子,则可动电荷密度为:

Mm

=

QM q

= COX q

(VFB2-VFB3)

(18)

X-Y 函数 记录仪

CTG-1 型 高频 C-V 仪

测试盒

UJ106 测温电位差计

1017

1018

图10-5 Al-Si系统功函数差Φms 和NA的关系

电荷和Φms的共同作用,使平带电压

为

C/COX 1.0

VFB2

=Φms–

Qf COX

(12)

③

1019

①②

理想曲线 CFB/COX

从(12)式可求得单位面积SiO2中固定

表面电荷Qf: Qf = COX(Φms–VFB2) 库仑/厘米2

2.求硅片掺杂浓度NA:由实验曲线①测得的

Cmin COX

值,又知dox,由

Cmin COX

~dox,NA查图4

中曲线求得NA值。

3.求平带电容CFB:由已知dox、NA、,Cox可由图10—3查

Cmin COX

~dox,NA求出CFB/Cox从而得

到CFB。 4.求VFB2和VFB3:由所求CFB/Cox点(纵座标)作平行于VG轴的直线,直线与曲线②、③

之交点所对应的VG即为VFB2和VFB3。 5.求固定表面正电荷密度Nf:

Nf

=

COX q

(φms-VFB)

6.求可动离子电荷密度Nm:

Nm

=

COX q

(VFB2-VFB3)

实验指导书3-MOS结构高频C-V特性测试分析(精)

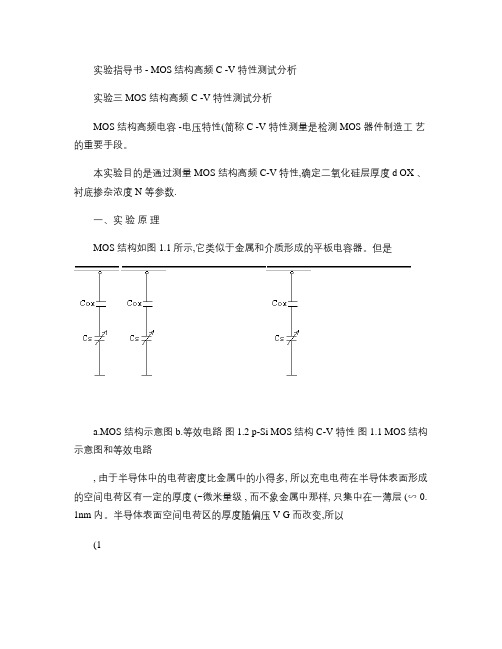

实验三MOS结构高频C -V特性测试分析

MOS结构高频电容-电压特性(简称C -V特性测量是检测MOS器件制造工艺的重要手段。

本实验目的是通过测量MOS结构高频C-V特性,确定二氧化硅层厚度d OX、衬底掺杂浓度N等参数.

一、实验原理

MOS结构如图1.1所示,它类似于金属和介质形成的平板电容器。但是

s

sc

OX

0r 0G

G

OX dV dQ

A

Cs d A

dV dQ

A

C =εε==2

1

i rs

0OX

rs 0r max

min n N ln N

q kT d 11

C C 2

⎥⎦⎤⎢⎣⎡⎪⎭⎫ ⎝⎛εεεε+

=21

B N q kT d 11

C C 2

⎪

⎭

⎫ ⎝⎛εεεε+

=ms

✧图表分析、文件存档和打印

以下将给出包括直观性较强的界面在内的详细操作步骤: ◆人、机安全注意事项:

A、操作之前,请注意将机器正确接地;

B、检修之前,请注意按操作手册将C-V测试仪与电源线及其它设备断开;

C、在测试仪器工作时,禁止触摸仪器的端口。

(6

VS =0时,半导体表面能带平直,称为平带。平带时的MOS电容称为平带电容,记为C FB。对于给定的MOS结构,归一化平带电容由下式给出:

(7

显然,对于理想MOS结构, V FB =0。

考虑实际的MOS结构。由于SiO 2中总是存在电荷(通常是正电荷,且金属的功函数W m和半导体的功函数W s通常并不相等,所以VFB一般不为零。若不考虑界面态的影响,有

MOS C V测试技术

1、当 V = 0 时,Ψs = 0,(能带平出,见下图),Qsc = 0

Байду номын сангаас

Ec

M

SiO2 n-Si

EF

V

Ei

M SiO2 n-Si

Ev

MOS 结构示意图

V=0 时,n MOS 结构能带示意图

但 Csc = Cs0 = dQsc / dΨs≠ 0 由(4)式可导出 Cs0 = [q2·ε0·εs·N /( K·T)]1/2

ωC 容抗大,干扰大)。为此,广泛采用准静态技术以实现甚低频 C-V 测试。

2、准静态甚低频 C-V 曲线

在极慢的斜坡电压下,MOS 电容的位移电流 iC 为:

ic = dQ/dt=(dQ / dV)·(dV / dt)

若 V 是线性斜坡电压,即 V = V0+α·t,则 dv/dt =α为常数。只要α足够低,Si 表面的多子和少子均能响应斜

(二) 理论低频 c-v 曲线

1 理论低频 C-V 曲线

MOS 电容不仅是偏压的函数,也是测试信号频率的函数。以上讨论中,因少子(空穴)不能响应高频信号,

对电容无贡献。但当信号频率足够低时,少子能响应测试信号,对 MOS 电容有贡献,其等效电路如下图。图中,

CD 是耗尽层电容,Cp 是少子空穴对电容的贡献。于是,空间电荷电容 Csc=CD +Cp,MOS 低频电容 CL 可以表 示为

(18)

和最大的耗尽层宽度:

Wmax=εs·tox/εox·[1/(Cmin/Cox)—1]

(19)

式中,tox,εox,和 Cox 分别为 SiO2 膜厚度,介电常数和氧化层电容;N,ni 和εs 分别为 Si 的掺杂密度,本征

C-V测试基本原理

近似求得平带电容为

Cfb=εox/〔xo+( εox/ εs)*√KT εs/Naq2 〕

V>0时,能带下弯,表面空穴耗尽

Cd= εs/W随栅压增加而下降,因而总电容C也 下降。继续增大栅压时,P型表面开始反型 (硅表面处于一个弱的N型状态)。当V>>0 时,半导体表面开始产生强反型,耗尽层宽度 达到最大值,C=Cmin

根据等效电路,单位面积总的MOS电容C可以写成 1/C=1/Cox+1/Cd

Cox是单位氧化层电容:Cox=εox/dox与栅压无关

Cd是单位面积半导体空间电荷电容,与栅压有关

对于确定的衬底浓度和氧化层厚度,总电

容C是空间电荷层亦即是栅压的函数

理想MOS二极管定义: (1)金属半导体功函数差为零; (2) SIO2中不存在电荷,也不存在界面陷

VFB’=φms=φm-φs

AL的公函数为4.1eV N+多晶的功函数为4.05eV

接触后表面能带弯曲,为达到理想平带状态,需外加一个 相当与功函数差的电压,在此需在金属侧加一个负电压,此 电压为平带电压VFB’

2.氧化层电荷对CV特性的影响

在实际的MOS结构中,SIO2中存在四种电 荷:它们的净电荷将在硅表面感应出空间 电荷导致表面能带弯曲。要抵消这种电荷 的影响使能带恢复平直必须在栅上加符号 相反的等量电荷Qm。设氧化层中净电荷为 Qox,则栅上所加的电压必须要满足:

固定电荷导致CV曲线向-平移

氧化层内陷阱电荷:常伴随SIO2的缺陷 产生,存在于SIO2内部的被馅住的电子 和空穴,与氧化工艺有关。

以上四种电荷最终在SI表面感应出负电 荷,为了达到平带状态,必须在金属上 施加一负电压,导致VFB向负偏移。

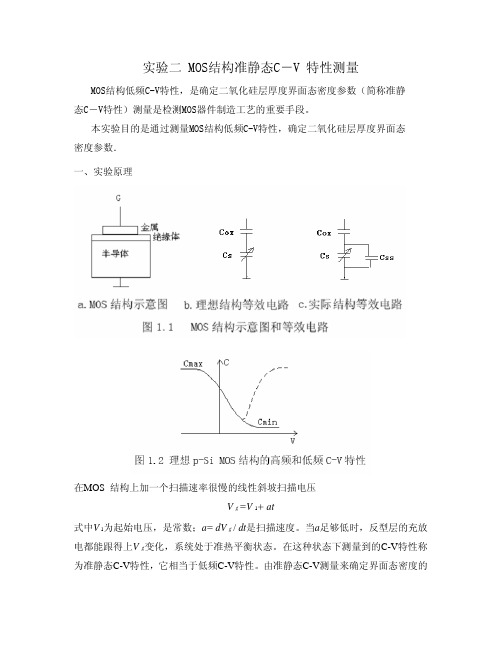

实验二 MOS结构准静态C-V 特性测量

ቤተ መጻሕፍቲ ባይዱ

由 VF =

Ei − EF q

体内

,可得到

EF − Ei = −qVF EF − Ei = qVF

代入(6)式,就得到

( p型) (n型)

NA ⎧ ⎪ E = qVS − qVF = qVS − K BT ln n → ( p型) ⎪ i ⎨ N ⎪ E = qV + qV = qV + K T ln D → (n型) S F S B ⎪ ni ⎩

1 1 1 = + CC Ci CS

(2)

(3)

对于同一个VS,(2)和(3)式中的CS是相同的,将(3)式得到的 CS = CC Ci Ci −CC 代入(2)式,即得到

CSS =

代入(1)式,即得到

1−

CL CL

− Ci

1−

CC CC

(4) Ci

N SS

⎛ CC 1 ⎜ CL = 2⎜ − C q ⎜ 1 − CL 1− C C Ci i ⎝

人、机安全注意事项:

A、操作之前,请注意将机器正确接地; B、检修之前,请注意按操作手册将C-V 测试仪与电源线及其它 设备断开; C、在测试仪器工作时,禁止触摸仪器的端口。 (详细安全信息请详细阅读操作手册) 五、实验数据处理 已知:汞电极面积A=4.206×10-3cm2 1、由初始C-V曲线,可获得Cmax ,利用式 COX = A ⎛ CC 1 ⎜ CL = 2⎜ − C q ⎜ 1 − CL 1− C Ci Ci ⎝ ⎞ ⎟ ⎟ ⎟ ⎠

ε 0ε r 0

dOX

可求出氧化层厚度dox

2、求界面态密度 N SS

半导体物理实验指导书 C-V特性测量

C min = C max

1 ε r0 1+ ε rs d OX ⎡ kTε 0 ε rs ⎛ N ⎞⎤ 2 ln⎜ ⎟⎥ ⎢ 2 ⎝ n i ⎠⎦ ⎣ q N

(13)

1

VS=0 时,半导体表面能带平直,称为平带。平带时的 MOS 电容称为平带电容,

C FB = C ox 1 ε r 0 ⎛ kTε 0 ε rs ⎞ 2 ⎟ ⎜ 1+ ε rs d OX ⎝ q 2 N ⎠

b.理想结构等效电路 结构等效电路 图 1.1 MOS 结构示意图和等效电路

c. b.实际

图 1.2 理想 p-Si MOS 结构的高频和低频 C-V 特性

在 MOS 结构上加一个扫描速率很慢的线性斜坡扫描电压

V g = V1 + at

式中 V1 为起始电压,是常数; a = dV g / dt 是扫描速度。当 a 足够低时,反型层的 充放电都能跟的上 V g 变化,系统处于准热平衡状态。在这种状态下测量到的 C-V 特性称为准静态 C-V 特性,它相当于低频 C-V 特性。由准静态 C-V 测量来确定 界面态密度的基本原理,就是通过低频(准静态)C-V 测量得到的 MOS 电容值, 和理论计算得到的相同表面势下无界面态的 MOS 电容值进行比较,提取出界面 态电容值 CSS,再根据

CL C SS =

代入(1)式,即得到

Ci Ci

CC − 1−

Ci Ci

1−

CL

CC

(4)

CC ⎛ CL ⎞ ⎟ 1 ⎜ Ci Ci N SS (VS ) = 2 ⎜ − ⎟ C q ⎜ 1 − CL 1− C ⎟ Ci Ci ⎠ ⎝

(5)

(5)式就是 NSS~Vg 关系式,式中 CL 和 CC 应当对应相同的 VS。实际测量得到 的是 CL~Vg 关系。 通常,界面态分布用 NSS 和禁带中的能量位置 E 的关系来表示;而(5)式给 出的是 NSS 和表面势 VS 的关系,因此还需要将 VS 转换成 E。如图 3 所示,以 Eis 作为能量零点,则禁带上半部,E>0;禁带下半部,E<0。显然,NSS(E)是表面能

MOS结构C-V特性测量及BT试验

实验四MOS 结构C-V 特性测量及BT 实验一. 实验目的与意义对MOS 结构测量其高频电压-电容(C-V)曲线,以及利用正、负偏压温度处理方法(简 称土BT 试验)进行Si/SiO :界而研究,可以获得MOS 结构的多个参数:二氧化硅层的厚度, 衬底硅掺杂类型、浓度,以及二氧化硅层中可动电荷与固定电荷密度。

通过实验全过程的操作及数据处理,使学生加深对所学“固态电子论”中半导体表面理 论的理解,特別是硅-二氧化硅系统性质的理解。

掌握用C-V 方法测量MOS 结构样品的多个 参数。

二. 实验原理MOS 结构如图la 所示,它类似于金属和介质形成的平板电容器。

但是由于半导体中的 电荷密度比金属中的小得多,所以充电电荷在半导体表而形成的空间电荷区有一立的厚度 (在微米量级),而不象金属那样,只集中在一薄层(约)内。

半导体表而空间电荷区的厚 度随外加偏压陀而改变,所以MOS 电容C 是微分电容。

(a)结构示意图 (4-1)式中:Q 是金属电极上的电荷而密度;月是电极而积。

理想情形可假设MOS 结构满足下列条件:①金属-半导体间的功函数差为零:②SiO : 层中没有电荷:③SiO :与半导体界面处不存在界而态。

偏压冷一部分降在SiO :上,记为仏: 一部分降在半导体表面空间电荷区,记为仏,即:V G =Vo + V s (4-2)(b)等效电路(c) p-SiMOS 理想 C-V 曲线 图4-1 HOS 结构及其C-V 特性%又称为表面势。

考虑到半导体空间电荷区电荷和金属电极上的电荷数量相等、符号相反,有:|e.J=|e G | (4-3)式中:0S 为半导体表面空间电荷区电荷面密度。

将(4-2)、(4-3)代入(4-1)式,有:式(4-4)表明MOS 电容是©和Cs 串联而成,其等效电路为图4-1的b 所示。

其中8 是以SiO :为介质的氧化层电容,它的数值不随%改变,Cs 是半导体表而空间电荷区电容, 其数值随%改变。

半导体C-V测量基础

图1中的金属/多晶层是电容的

一极,二氧化硅是绝缘层。由于绝缘 层下面的衬底是一种半导体材料,因 此它本身并不是电容的另一极。实际 上,其中的多数载流子是电容的另一 极。物理上而言,电容C可以通过下 列公式中的变量计算出来:

C = A (κ/d), 其中 A是电容的面积, κ是绝缘体的介电常数 d是两极的间距 因此,A 和 κ越大,绝缘体厚 度越薄,电容值就越高。通常而言, 半导体电容的大小范围从几纳法到几 皮法,甚至更小。 进行C-V测量时要在电容的两极 加载直流偏压同时利用一个交流信号 进行测量(如图1所示)。通常情况 下,这类测量使用的交流频率范围从 10kHz到10MHz。所加载的偏压作为直 流电压扫描驱动MOSCAP结构从累积区 进入耗尽区,然后进入反型区(如图 2所示)。 强大的直流偏压导致衬底中的 多数载流子在绝缘层界面附近累积。 由于它们无法穿透绝缘层,因此当电 荷积累在界面附近(即d为最小值) 时电容在累积区达到最大值。如图 1所示。从C-V累积测量可以得到的 一个基本参数就是二氧化硅的厚度 tox。 当偏压降低时,多数载流子从 氧化层界面被排斥开,耗尽区形成。 当偏压反相时,电荷载流子远离氧化 层达到最大距离,电容达到最小值 (即d为最大值)。根据这时的反型 区电容,可以推算出多数载流子的数 量。这一基本原理同样适用于MOSFET 晶体管,只是它们的物理结构和掺杂 更加复杂。 在偏压扫过这三个区的过程中 还可以得到多种其他参数,如图2所 示。利用不同的交流信号频率可以得

这类测量的基本特征非常适用 于各种应用和培训。大学的研究实验 室和半导体厂商利用这类测量评测新 材料、新工艺、新器件和新电路。 C-V测量对于产品和良率增强工程师 也是极其重要的,他们负责提高工艺 和器件的性能。可靠性工程师利用这 类测量评估材料供货,监测工艺参 数,分析失效机制。

MOS结构准静态C-V特性测量

MOS结构准静态C-V特性测量一.实验目的1. MOS结构低频C-V特性,是确定二氧化硅层厚度界面态密度参数(简称准静态C-V特性)测量是检测MOS器件制造工艺的重要手段。

掌握并了解MOS结构及C-V方法测量原理。

2.学会X-Y记录仪的使用方法,并测出高频下的C-V特性曲线。

通过测量MOS结构低频C-V 特性,确定二氧化硅层厚度界面态。

二实验原理1.MOS结构及其C-V特性式中是金属电极上的电荷面密度,A是电极面积。

GQ通过对该电容的C-V 特性的测量分析,就可以了解半导体表面的各种状态,如SiO2-Si界面的各种电荷的性质,测定Si的许多重要表面参量和体参量(如杂质浓度,少子寿命等)。

本实验是通过对C-V特性的测量分析计算出氧化层中固定的电荷密度。

2.理想MOS的C-V特性所谓理想情形,是假设MOS结构满足以下条件:(1)金属与半导体间功函数差为零;(2)SiO2绝缘层内没有电荷;(3)SiO2与半导体界面处不存在界面态。

偏压VG一部分在降在SiO2上,记作Vox;一部分降在半导体表面空间电荷区,记作,即Vs,即:Vs=0时,半导体表面能带平直,称为平带。

平带时的MOS电容称为平带电容,记作CFB。

对于给定的MOS结构,归一化平带电容由下式给出[1]:3.实际的MOS的C-V特性由于SiO2中总是存在电荷(通常是正电荷),且金属的功函数Wm和半导体的功函数Ws通常并不相等,所以VFB一般不为零。

若不考虑界面态的影响,有4.氧化层中正电荷的计算通过以上分析,我们看到氧化层中正电荷的影响(在这里我们只笼统的讲是正电荷)。

实际上它包括氧化层中固定电荷,Si-SiO2界面的界面态以及靠近Si-SiO2界面的可动离子正电荷,后者的密度可通过BT实验-正、负偏压温度处理方法来进行测量,这不在本实验的内容。

关于计算氧化层中正电荷密度的方法,在这里我们介绍二种。

第一种方法是根据高频CTG-1型高频测试仪测出的C-V特性曲线。

MOS结构电容-电压特性

MOS 结构高频C-V 特性测试MOS 结构电容-电压特性(简称C-V 特性)测量是检测MOS 器件制造工艺的重要手段。

它可以方便地确定二氧化硅层厚度ox d 、衬底掺杂浓度N 、氧化层中可动电荷面密度I Q 、和固定电荷面密度fc Q 等参数。

本实验目的是通过测量MOS 结构高频C-V 特性及偏压温度处理(简称BT 处理),确定ox d 、N 、I Q 和fc Q 等参数。

一、 实验原理MOS 结构如图1(a )所示,它类似于金属和介质形成的平板电容器。

但是,由于半导体中的电荷密度比金属中的小得多,所以充电电荷在半导体表面形成的空间电荷区有一定的厚度(—微米量级),而不像金属中那样,只集中在一薄层(—0.1nm )内。

半导体表面空间电荷区的厚度随偏压G V 而改变,所以MOS 电容是微分电容 GG dV dQ A C = (1) 式中G Q 是金属电极上的电荷面密度,A 是电极面积。

现在考虑理想MOS 结构。

所谓理想情形,是假设MOS 结构满足以下条件:(1)金属与半导体间功函数差为零;(2)2O S i 绝缘层内没有电荷;(3)2O S i 与半导体界面处不存在界面态。

偏压V G 一部分在降在2O S i 上,记作ox V ;一部分降在半导体表面空间电荷区,记作S V ,即S OX G V V V += (2)S V 又叫表面势。

考虑到半导体表面空间电荷区电荷和金属电极上的电荷数量相等、符号相反,有G SC Q Q = (3)式中SC Q 是半导体表面空间电荷区电荷面密度。

将式(2)、(3)代入式(1),S ox S ox Sox S ox G G G C C C C C C dV dV dQ A dV dQ A C +=+=+==111 (4) 式(4)表明MOS 电容由ox C 和S C 串联构成,其等效电路如图1(b )所示。

其中ox C 是以2O S i 为介质的氧化层电容,它的数值不随改变G V ;S C 是半导体表面空间区电容,其数值随G V 改变,因此oxro ox G ox d A dV dQ A C εε0== (5) S SC S dV dQ AC = (6) 式中ro ε是2O S i 相对介电常数。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

MOS结构准静态C-V特性测量一.实验目的1. MOS结构低频C-V特性,是确定二氧化硅层厚度界面态密度参数(简称准静态C-V特性)测量是检测MOS器件制造工艺的重要手段。

掌握并了解MOS结构及C-V方法测量原理。

2.学会X-Y记录仪的使用方法,并测出高频下的C-V特性曲线。

通过测量MOS结构低频C-V 特性,确定二氧化硅层厚度界面态。

二实验原理1.MOS结构及其C-V特性式中是金属电极上的电荷面密度,A是电极面积。

GQ通过对该电容的C-V 特性的测量分析,就可以了解半导体表面的各种状态,如SiO2-Si界面的各种电荷的性质,测定Si的许多重要表面参量和体参量(如杂质浓度,少子寿命等)。

本实验是通过对C-V特性的测量分析计算出氧化层中固定的电荷密度。

2.理想MOS的C-V特性所谓理想情形,是假设MOS结构满足以下条件:(1)金属与半导体间功函数差为零;(2)SiO2绝缘层内没有电荷;(3)SiO2与半导体界面处不存在界面态。

偏压VG一部分在降在SiO2上,记作Vox;一部分降在半导体表面空间电荷区,记作,即Vs,即:Vs=0时,半导体表面能带平直,称为平带。

平带时的MOS电容称为平带电容,记作CFB。

对于给定的MOS结构,归一化平带电容由下式给出[1]:3.实际的MOS的C-V特性由于SiO2中总是存在电荷(通常是正电荷),且金属的功函数Wm和半导体的功函数Ws通常并不相等,所以VFB一般不为零。

若不考虑界面态的影响,有4.氧化层中正电荷的计算通过以上分析,我们看到氧化层中正电荷的影响(在这里我们只笼统的讲是正电荷)。

实际上它包括氧化层中固定电荷,Si-SiO2界面的界面态以及靠近Si-SiO2界面的可动离子正电荷,后者的密度可通过BT实验-正、负偏压温度处理方法来进行测量,这不在本实验的内容。

关于计算氧化层中正电荷密度的方法,在这里我们介绍二种。

第一种方法是根据高频CTG-1型高频测试仪测出的C-V特性曲线。

然后查表得出平带电容,这样在C-V曲线上就能找出平带电压VFB,再代入(9)式,就可以计算出Qfc来了。

具体方法如下:1. 计算功函数差2. 查表求C FB3.在C-V曲线上求出V FB4.计算三测量步骤本实验采用E4980A c-v测试仪进行测量。

安装NetFx_IOLibSuite_16_1_14931.exe,安装driver_ivicom_e4980a_1_0_11_0_7_3_07.msi,用USB线将电脑与E4980A连接,打开E4980A按图1中1处的Refresh All,确认图中2处的2个?变为√1. 确认图1中3处的Firmware为Rev.2.20。

否则按e4980a_firmware_update.pdf内说明升级固件。

2. 打开E4980_DataTransfer_0100.xls,将1处改为USB,在2处输入图1中4处的那串字母与数字。

点击Handshake,在3处应该是出现OK。

3. 设置E4980A,按Meas Setup键出现如图2的设置界面(在数字键的左下,方向键的正下,如果操作无反应,观察图2右下是否出现RXX的3个英文,试着按屏幕下方最右边的Local/lock键,如果不行就重启E4980A)。

将FUNC改为Cp-D,将FREQ改为1MHz,将LEVEL改为100mV,TRIG改为MAN,按屏幕左边的DC Bias,确认仪器右边DC Bias下的灯是亮的。

4. 按Display Format(在Meas Setup左边),再按Meas Setup,按屏幕中右边显示LIST SETUP对应的按钮,出现如图3的设置界面。

将FREQ[Hz]改为BIAS[V](右边一排没有,按下MORE对应的键)在1后面,BIAS[V]下面输入-5,然后按10下NEXT PAGE对应按钮,在101后面,BIAS[V]下面输入5,按一下PREV PAGE 的对应按钮,再按下FILL LINEAR对应的按钮。

5. 按Display Format按钮,按右边LIST SWEEP对应的按钮,按下屏幕左边的Trigger键,E4980A就开始自动测量,从-5V测到5V。

测量结束后回到电脑上的E4980_DataTransfer_0100.xls,在图5中的1处设置测试数据表名(注意不能重复命名),点Load Data,会多出一个选项卡,测试数据就存在里面。

6.根据测得的数据画出C-V测量曲线,并根据曲线求Cox出值,VFB值。

oxCFBV7.将Cox值,VFB值与Vms值代入Nfc公式,便可求出固定电荷Nfc密度了。

四数据处理Point# BIAS[V] Cp D1 -5 4.19392E-09 0.05417212 -4.9 4.19205E-09 0.05415883 -4.8 4.19028E-09 0.0541534 -4.7 4.18842E-09 0.05415455 -4.6 4.18652E-09 0.05414596 -4.5 4.18449E-09 0.05415027 -4.4 4.18244E-09 0.05415058 -4.3 4.18032E-09 0.05414569 -4.2 4.17808E-09 0.054155710 -4.1 4.17567E-09 0.054162811 -4 4.17326E-09 0.054168612 -3.9 4.17064E-09 0.054195413 -3.8 4.16801E-09 0.054205114 -3.7 4.16524E-09 0.054234215 -3.6 4.16233E-09 0.054275216 -3.5 4.15929E-09 0.054320817 -3.4 4.15607E-09 0.054373718 -3.3 4.1527E-09 0.054442619 -3.2 4.1491E-09 0.054537320 -3.1 4.14528E-09 0.054662521 -3 4.14122E-09 0.054818522 -2.9 4.1368E-09 0.055008323 -2.8 4.13191E-09 0.055237124 -2.7 4.12651E-09 0.055512725 -2.6 4.12033E-09 0.055822426 -2.5 4.11331E-09 0.05610127 -2.4 4.10538E-09 0.056291828 -2.3 4.09681E-09 0.056306229 -2.2 4.08799E-09 0.056088130 -2.1 4.07948E-09 0.055686931 -2 4.07136E-09 0.055225732 -1.9 4.06355E-09 0.054788433 -1.8 4.05581E-09 0.054434234 -1.7 4.04775E-09 0.054184435 -1.6 4.0393E-09 0.05401136 -1.5 4.03016E-09 0.053883337 -1.4 4.02048E-09 0.053803938 -1.3 4.01005E-09 0.053729639 -1.2 3.99898E-09 0.053688140 -1.1 3.98706E-09 0.053653341 -1 3.97434E-09 0.05364342 -0.9 3.96084E-09 0.053674543 -0.8 3.94629E-09 0.053740244 -0.7 3.93079E-09 0.053862545 -0.6 3.91419E-09 0.054076646 -0.5 3.89643E-09 0.054407447 -0.4 3.87744E-09 0.05492648 -0.3 3.85717E-09 0.055696749 -0.2 3.83531E-09 0.056827650 -0.1 3.8118E-09 0.058450351 0 3.7864E-09 0.060700952 0.1 3.75824E-09 0.063772853 0.2 3.72662E-09 0.067851254 0.3 3.68973E-09 0.073156455 0.4 3.64626E-09 0.079760556 0.5 3.59339E-09 0.087891157 0.6 3.52948E-09 0.097413958 0.7 3.45169E-09 0.10829559 0.8 3.35911E-09 0.12003760 0.9 3.25047E-09 0.1319961 1 3.1279E-09 0.14289962 1.1 2.99461E-09 0.15135463 1.2 2.85854E-09 0.15578864 1.3 2.72501E-09 0.15526765 1.4 2.60442E-09 0.14972666 1.5 2.49817E-09 0.14001967 1.6 2.41021E-09 0.12776568 1.7 2.33883E-09 0.11449769 1.8 2.28168E-09 0.10138470 1.9 2.23646E-09 0.089305371 2 2.20045E-09 0.078603172 2.1 2.17176E-09 0.069458973 2.2 2.1487E-09 0.061838774 2.3 2.12932E-09 0.055379875 2.4 2.11358E-09 0.050259276 2.5 2.09993E-09 0.046030877 2.6 2.08849E-09 0.042734178 2.7 2.07863E-09 0.040174179 2.8 2.07015E-09 0.038236780 2.9 2.063E-09 0.036849681 3 2.05703E-09 0.035913682 3.1 2.05231E-09 0.035387183 3.2 2.04874E-09 0.035213184 3.3 2.0461E-09 0.035372485 3.4 2.04445E-09 0.035866186 3.5 2.04359E-09 0.036755887 3.6 2.0436E-09 0.038062388 3.7 2.04453E-09 0.039926889 3.8 2.04665E-09 0.0424735 90 3.9 2.05044E-09 0.0459089 91 4 2.05651E-09 0.050427 92 4.1 2.06584E-09 0.0563333 93 4.2 2.07949E-09 0.0639545 94 4.3 2.09909E-09 0.0737595 95 4.4 2.1265E-09 0.0863148 96 4.5 2.16473E-09 0.102703 97 4.6 2.21803E-09 0.124271 98 4.7 2.2968E-09 0.15254 99 4.8 2.42039E-09 0.18498 100 4.9 2.61476E-09 0.209382 101 5 2.8757E-09 0.208674由以上数据得:电容最大值c1=4.2137nf ,最小值c2=2.1255nf. 所以,Cfb=(c1+c2)/2=3.1696nf ,C=√(Cfb ×c1) =3.6546nf , 在数据表中找到C=3.6546nf 时, Vfb = - 0.2v ,Vm=4.25v , Vms=Vm+Vs= -0.57v ,带入相关数据得,正电荷密度=2.6×10^10 .。