VCD105-18io7中文资料

DVD原理

三洋+MTK方案DVD视盘机电路一、简介 (2)二、伺服电路工作原理 (3)1、数字信号处理流程 (3)2、控制信号处理流程 (4)三、主要集成电路管脚功能表 (6)1、MT1336E (6)2、MT1369E (9)3、BA5954 (12)4、AM29F800BT (13)5、HY57V161610D (14)6、CS4955 (15)7、CS4360 (16)8、PCM1801 (17)一、简介目前在市场上出现了许多单芯片的DVD ,该类DVD 的解码就是由MTK 方案所组成。

在三洋+MTK 组成的DVD 方案中,其主要部份由MT1336E 和MT1369E 以及BA5954组成,其中MT1336E 的作用是完成对RF 信号的处理以及激光功率的自动控制;MT1369E 的作用主要有数字伺服控制、数字信号处理以及MPEG 解码;而BA5954是一块四通道驱动IC ,主要完成对聚焦、循迹、进给、主轴四个伺服控制信号的驱动放大,以带动电机或线圈作相应的动作。

我们选用了步步高的DV921K 为代表机型,来向大家介绍一下有关三洋+MTK 方案的伺服部分电路工作原理。

DV921K 整机组成方框图如下图所示,所采用的集成电路功能如表一所列:表(一)DV921K 采用集成电路功能一览表:电路板 编号 集成电路型号主要功能机芯 三洋机芯 碟片信号的拾取 U301 MT1336E 前置RF 信号处理 U302 BA5954 四通道驱动电路U201 MT1369E 数字信号处理、伺服处理、MPEG 解码、系统控制U202 AT24C01 串行EEPROM 、状态存储器U203 HY57V161610 2MB SDRAM U204 HY57V161610 2MB SDRAM U205 74HCU04 六反相器 主板U206CS4955视频编码器S 端子 六路音频输出 同轴U207CS4360音频数/模转换器U208BA033 3.3V稳压电路U209LM1117MP-2.5 2.5V稳压电路U210PCM1801音频模/数转换U214AM29F800BT8MB Flash ROMU219~UJRC4558双运算放大器2215L0380开关电源IC电源板PC817光电耦合器LM431A 2.5V基准电压比较器D16312面板控制、VFD显示驱动面板HS0038A遥控接收头二、伺服电路工作原理1、数字信号处理流程DV921K采用的是三洋机芯与MTK解码方案,其伺服电路主要由前置信号处理MT1336E和数字伺服处理、数字信号处理MT1369E以及驱动电路BA5954组成,其中MT1369E同时也是解码电路的主要组成部份。

万利达VCD维修资料

VCP-318故障现象:遥控灵敏度低,有时无效检修:遥控试机正常,用示波器检测显示数据信号DATA、时钟信号CLK、选通信号CS,发现DATA 数据信号波形幅度很小,已不到2V。

且该电压并不稳定,挑开解码板上C74 贴片电容后测量DATA 数据信号,已回升到正常4V 左右,试机面板所有按键操作正常,故障排除。

DVP-330故障现象:荧光屏无显示,机芯不复位,无“读碟”字符显示检修:首先测量机芯供电+5V、+12V 正常,然后用示波器检测AL5705 时钟电路33.8688M 晶振,显示无33.8688M 时钟振荡信号,已失效。

.更换同型号晶振后试机,读碟正常,故障排除。

说明:开机时电视画面上无显示“读碟”二字,或者显示“读碟”很慢,则故障点主要在伺服电路部分。

DVD-900R故障现象:无图、主轴电机飞转、荧光屏也无显示检修:把解码芯片重新拖焊一遍后通电试机,机器已能正常开机读碟,但持续播放几分钟后图像呈现花屏闪烁,随后死机。

重新开机工作几分钟后又同样死机,用ES4408 代换ES4118 后,故障还是依旧。

因此怀疑动态存储器不良,用一同型号存储器(16M)更换。

长时间试机不再死机,故障排除。

说明:采用ES4118/ES4108/ES4408/ES4318 方案的DVD 播放一段时间后出现图异、图闪或死机大部分是解码芯片老化,更换即可(注意:ES4108/ES4118 必须加散热片)。

916V故障现象:液晶屏显示白光栅、无图,读片正常检修:视频信号输入到监视器其图像正常,因此怀疑故障在TFT 驱动板上,将其驱动板拆开,测量芯片时钟、工作电压等信号时,发现+5V 供电很低,检测电感L2 端电压为3.6V 左右,已开路,更换电感L2 后通电试机液晶屏显示正常,故障排除。

DVP-390故障现象:读VCD 碟正常、DVD 碟纠错很差、有时不读检修:该机为新机,故怀疑元器件损坏的可能性很小,首先用放大镜仔细观察主板RF 处理电路及DSP 电路外围阻容元件,发现贴片电容C33 一端为虚焊,且该焊盘上没有上锡,经补焊后试机读碟恢复正常。

(第5章)VCD-2000功能参数表NEW

第五章 功能参数表

5.1 表中符号说明

“○”: 参数在运行过程中可以修改。

“×”: 参数在运行过程中不能修改。

“* ”: 只读参数,用户不能够修改。

5.2 功能代码表

P0 组:基本运行参数

功能码

名称

设定范围

最小单位 出厂设定 更改

0:V/F 控制

P0.00 控制方式选择

×

0.00Hz

×

0

×

0

×

0.00Hz

×

0.0%

×

0.00Hz

×

0.0%

×

0.00Hz

×

0.0%

×

1

○

-38-

VCD-2000 系列无感矢量变频器使用说明书

功能码 P1.00 P1.01 P1.02 P1.03 P1.04 P1.05 P1.06 P1.07 P1.08 P1.09 P1.10 P1.11 P1.12

P3.37 P3.38 P3.39 P3.40

○

○

○ ○

功能码

名称

P2.00 起动运行方式

P2.01 P2.02 P2.03 P2.04

起动频率 起动频率持续时间 起动时的直流制动电流 起动时的直流制动时间

P2 组:起动制动参数 设定范围

0:从起动频率起动 1:先制动再从起动频率起动 2:检测速度再起动 0.00~20.00Hz 0.0~30.0s 0.0~80.0% 0.0~60.0s

PULSE 最大给定

PULSE 最大应频率 模拟量输入精度

P1 组:频率给定参数 设定范围

0.01~30.00s 0.01~9.99 0.00~P1.04 0.00~上限频率 P1.02~10.00V 0.00~上限频率 0.01~ 9.99 0.00~ P1.09 0.00~上限频率 P1.07 ~10.00V 0.00~上限频率 0.01~50.00K 0.00~P2.14(PULSE 最大给定)

动芯DCC恒速解码模块说明书

动芯领域DCC解码模块系列说明书(使用声明:此版说明书适用于5313、5323解码器31版固件及龟趺10版固件,使用前请读取CV7的数值以核对解码器版本号)使用声明及注意事项 (3)1.动芯恒速DCC解码模块简介一览表 (4)2.安装 (7)2.1.1带8针(NEM652)接口的机车 (7)2.1.2带NEXT18(NEM662)接口的机车 (9)2.1.3带MTC21(NEM660)接口的机车 (9)2.1.3带PluX22(NEM658)接口的机车 (11)2.2安装喇叭 (12)2.2.1并联连接多个喇叭 (12)3.安装电宝 (13)4.适用范围 (14)5.功能特性 (14)5.1速度控制 (14)5.1.1速度曲线控制模式(出厂默认方式) (14)5.1.2速度表控制模式 (15)5.1.3速度模式切换 (15)5.1.4加速度/减速度调节 (15)5.2恒速功能 (15)5.2.1恒速功能开关 (16)5.2.2恒速效果调节方式 (16)5.2.3速度调节注意事项 (16)5.3模拟控制 (16)5.3.1模拟控制方式 (16)5.4车头地址设置 (16)5.4.1车头地址说明 (16)5.4.2车头地址设置方法 (18)5.5功能输入/输出接口 (18)5.5.1功能输入/输出接口说明 (19)5.5.2功能接口效果设置说明 (21)5.5.3功能接口占空比最大值说明 (22)6.恢复出厂默认值 (23)7.CV值列表 (24)免责声明 (35)附录一 (35)附录二 (36)注意事项:1、安装本产品之前,请仔细阅读说明书。

2、请勿使用不支持DCC协议的数码控制器对本产品进行操作控制。

3、本产品不适合14岁以下儿童操作,使用方法不当会使其受到尖锐结构的伤害。

4、本产品不要暴露在雨、潮湿、火、阳光直晒以及腐蚀性化学物品的环境中。

5、本产品合适工作温度在0-80°C。

6、强烈的电磁波会对本产品正常工作有影响。

蓝光技术资料

目录

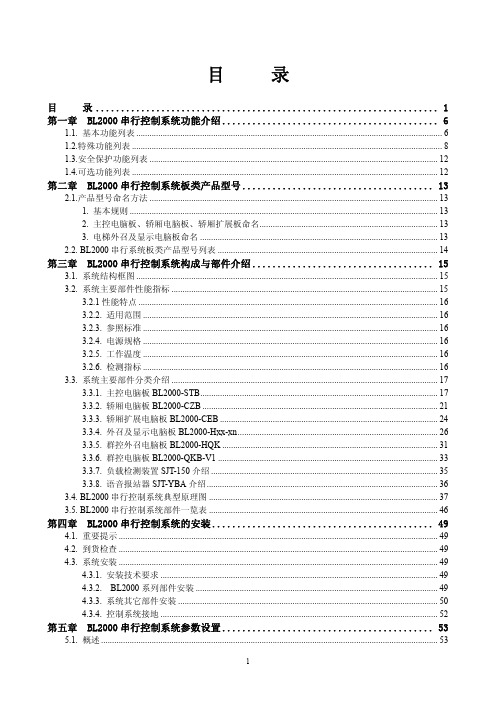

目 录 .................................................................... 1 第一章 BL2000 串行控制系统功能介绍 ........................................... 6

1.1. 基本功能列表 ........................................................................................................................................... 6 1.2.特殊功能列表 ............................................................................................................................................. 8 1.3.安全保护功能列表 ................................................................................................................................... 12 1.4.可选功能列表 ........................................................................................................................................... 12

VCD15中文资料

efficiency 70% 75% 78% 78% 77% 77% 77% 74% 78% 81% 81% 80% 80% 80% 76% 80% 82% 82% 81% 81% 81%

20050 SW 112th Ave. Tualatin, Oregon 97062 phone 503.612.2300 fax 503.612.2382

NOTES: 1. measured from high line to low line 2. measured from full load to1/4 load 3. deternine the correct fuse size by calculating the maximum DC current drain at low line input, maximum load and then adding 20 to 25% to get desired fuse size. 4. alternative pin configuration suffix “S”

input filter

OUTPUT

voltage accuracy single output dual+ output dual- output voltage balance dual output at full load transient response: single 25% step load change dual FL-1/2±1% error band ripple & noise, 20MHz BW temperature coefficient short circuit protection line regulation load regulation ±1.0% max. ±1.0% max. ±3.0% max. ±1.0% max. <500µ sec. <500µ sec. 10mV RMS max. 75mV p-p.max. ±0.02%/°C indefinite & current limit ±0.2% ±1.0%

CD105NP-181KB中文资料

D.C.R. (Ω) [以下] (at 20℃) 0.06 0.07 0.08 0.09 0.10 0.11 0.12 0.14 0.17 0.19 0.22 0.25 0.35 0.40 0.47 0.63 0.73 0.97 1.15 1.30 1.48 1.90 2.25 2.55

定格電流 (A) ※2

(mm)

9.0±0.4

5.4±0.4

TYPE CD105

※9.0

※φ10.0 ※ 2.1

φ10.0±0.4

1-2.STAMP (E.)

* DIMENSION OF ELECTRODE IS APPROX.

1-3.DIMENSION RECOMMENDED (mm) 9.5

100M

DATE CODE

DIRECTLY STAMP UNFIXED POSITION

INDUCTANCE [WITHIN] ※1

10μH±20% 12μH±20% 15μH±20% 18μH±20% 22μH±20% 27μH±20% 33μH±20% 39μH±20% 47μH±10% 56μH±10% 68μH±10% 82μH±10% 100μH±10% 120μH±10% 150μH±10% 180μH±10% 220μH±10% 270μH±10% 330μH±10%

電極部

2.5 10.0

R1.0

シルク処理部

電極(端子)間の隙間はシルク処理をして御使用下さい。

RoHS

compliance

Cd:Max.0.01wt%

1

others:Max.0.1wt%

元器件交易网

仕様書

形名 CD105

2-2.電気的特性Ⅰ(リール梱包の場合)

教学科研仪器设备明细表

电力系

117

交直流指示仪表检定装置

C1302C

1

6.40

19991214

电力系

118

接地电阻测试仪

GEOXP

1

5.13

20041230

电力系

119

静模与计算机仿真系统

1

98.50

19960818

电力系

120

局部放电检测系统

JED-2B

1

6.50

19990614

电力系

121

局部放电检测仪校准系统

WB-300A

1

6.46

19961218

电力系

145

网络谐波分析仪附件

1

12.60

19980825

电力系

146

微机电力故障录波装置

WDG1IV/X

1

9.00

20031230

电力系

147

微机继电保护测试仪

JJC-IH

1

11.41

19980715

1

16.78

19970729

电教中心

51

摄录一体机

H1-43+BW-5PS

1

26.08

19970729

电教中心

52

摄象机操纵手柄

MA-200A,VF5023

MT-668D,MCC-3

2

13.39

19970812

电教中心

53

视频转换器

ScanDoU1tra/D

1

6.90

20000828

电教中心

54

特技机

84

串联谐振试验装置

TPX-250

tm1628

LED 驱动控制专用电路一、 概述TM1628TM1628 是一种带键盘扫描接口的LED(发光二极管显示器)驱动控制专用电路,内 部集成有MCU 数字接口、数据锁存器、LED 高压驱动、键盘扫描等电路。

本产品性能优 良,质量可靠。

主要应用于VCR、VCD、DVD 及家庭影院等产品的显示屏驱动。

采用SOP28 的封装形式。

二、 特性说明• • • • • • • • 采用功率CMOS 工艺 多种显示模式(11 段×7 位 ~ 14 段×4 位) 键扫描(10×2) 辉度调节电路(占空比8 级可调) 串行接口(CLK,STB,DIO) 振荡方式:内置RC 振荡(450KHz+5%) 内置上电复位电路 封装形式:SOP28三、 管脚定义:1 2 3 4 5 6 7 8 9 10 11 12 13 14NC DIO CLK STB KEY1 KEY2 VDD SEG1/KS1 SEG2/KS2 SEG3/KS3 SEG4/KS4 SEG5/KS5 SEG6/KS6 SEG7/KS7GND GRID1 GRID2 GND GRID3 GRID4 GND VDD SEG14/GRID5 SEG13/GRID6 SEG12/GRID7 SEG10/KS10 SEG9/KS9 SEG8/KS828 27 26 25 24 23 22 21 20 19 18 17 16 15四、管脚功能定义:-1-LED 驱动控制专用电路符号 管脚名称 说明TM1628DIO数据输入/输出在时钟上升沿输入/输出串行数据,从低位开始。

输出为N-ch open drain 在上升或下降沿初始化串行接口,随后等待接收指 令。

STB 为低后的第一个字节作为指令,当处理指 令时, 当前其它处理被终止。

当STB 为高时, CLK 被 忽略 在上升沿读取串行数据,下降沿输出数据 输入该脚的数据在显示周期结束后被 锁存 段输出(也用作键扫描),p管开漏输出 位输出,N管开漏输出 段/位复用输出 5V±10% 接系统地 内部未连线STB片选CLK KEY1~KEY2 Seg1/KS1~ Seg10/KS10 Grid1~ Grid4 Seg12/Grid7 ~ Seg14/Grid5 VDD VSS NC时钟输入 键扫数据输入 输出(段) 输出(位) 输出(段/位) 逻辑电源 逻辑地 空脚▲ 注意:DIO口输出数据时为N管开漏输出,在读键的时候需要外接1K-10K的上拉电阻。

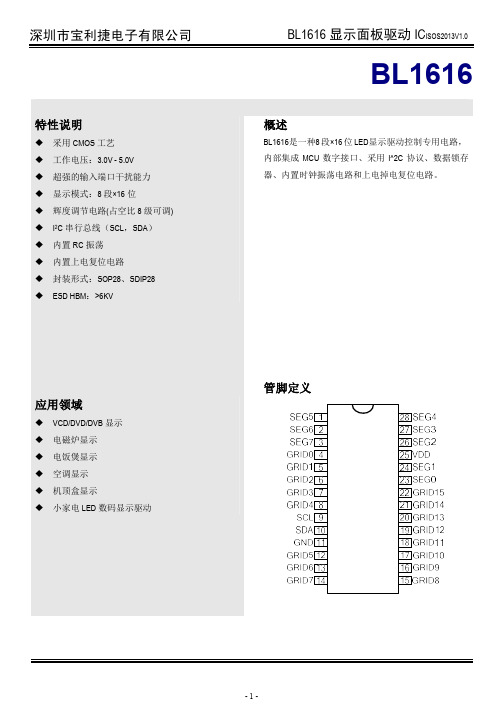

最新BL1616(LED驱动芯片)中文资料

逻辑电源

25

GRID0—GRID15

输出(位)

4-8,12-22

GND

逻辑地

11

注:SEG 引脚连接 LED 阳极,GRID 引脚连接 LED 阴极。

说明 I2C 总线串行接口的时钟输入 I2C 总线串行接口的数据输入 段输出 5V±10% 位输出 系统地

-2-

电气参数

极限参数(Ta = 25℃)

Command2(byte2) ack stop

SCL

SDA

Command1

start

ack

Data1

Command1

ack stop start

ack

Command1:设置地址 Data1~n : 传输显示数据 Command2:控制显示

DataN

Command2(byte1)

ack stop start

bl1616显示面板驱动icisos2013v10电气参数极限参数ta25参数符号范围单位逻辑电源电压vdd0570逻辑输入电压vi105vddledseg驱动输出电流io180maledgrid驱动输出电流io2700ma工作温度topt4080储存温度tstg6515025参数符号最小典型最大单位测试条件逻辑电源电压vdd33高电平输入电压vih07vdd低电平输入电压vil静态电流idd08mavdd50v无负载显示关sdascl上拉电阻rsdarscl12seg驱动电流isegmavdd50vseg电阻对gndgrid驱动电流igridmavdd50vgrid电阻对vddgrid频率fgridhzvdd50v上升时间ttzhsegnsvdd50vsegn接100下拉电阻gridn接100上拉电阻cl15pfttlzgridns下降时间tthzsegnsttzlgridns最大时钟频率fclkmaxmhz占空比50bl1616显示面板驱动icisos2013v1025参数符号最小典型最大单位测试条件时钟脉冲宽度pwclk400数据建立时间tsetup100数据保持时间thold100ack脉冲宽度tackbl1616显示面板驱动icisos2013v10显示寄存器该寄存器存储通过串行接口从外部器件传送到bl1616的数据从数据字节的高位到低位进行写操作地址分配如下

龙珠套件系列之一 USB2.0 硬盘 VCD、MP3 多媒体播放系统 说明书

深圳市龙珠科技有限公司 H a r d & S o f t T e c h n o l o g y C o ., L T D .地址:深圳市西乡龙珠路99号2楼技术支持:support@ hsavd501.pdf龙珠套件系列之一USB2.0硬盘VCD、MP3多媒体播放系统◆ 套件特性※ 已开发完成硬盘管理,Video CD 解码、MP3解码、USB2.0数码输出/输入接口等部分。

用户只需进行简单的连接即可组成硬盘VCD、MP3播放系统※ 可根据需要接上市面上各种的IDE 硬盘(包括笔记本硬盘),即可组成硬盘CD/VCD、MP3多媒体播放器。

※ 有USB2.0接口,(交换500M 文件约4分钟)可直接连接电脑,作为外部高速存储设备。

※ 开放的通讯协议,提供基本控制的C 语言源程序。

※ 用户可在硬盘上存储VCD、MP3格式的MPEG-1文件及WAVE 声音文件。

※ 内置笔记本电脑接口,可直接连接小体积防震硬盘,省掉接口转换卡。

※ 提供WINDOWS9X 的USB2.0驱动程序。

Win2000/ME/XP 可不需要驱动程序直接使用。

※ 强大的广告插播功能,轻松实现不同的广告效果。

※ 支持双硬盘,每个硬盘最大可支持120G,总容量可达240G,存储容量更大。

※ 用户可自行制作开机画面并可使用动画作开机画面。

※ 内置8051系列单片机,可修改程式以添加更多的功能。

◆ 套件适用范围※ 由于其超大的容量和简便的操作,可广泛用于长途大巴、公交车作硬盘CD/VCD 播放器。

※ 卡拉OK 厅、歌舞厅等作长时间的视频/音频播放系统。

※ 商场、校园公共广播等需要长时间播放预置音乐图象的地方。

※ 娱乐公共场所、应用图象广告的场面。

※ 其他需要使用预置音乐、图象的场合。

◆DR56C 硬盘控制板+HM611音频板+MF2088显示板+HM614开关电源板组成的硬盘VCD、MP3 播放机连线图◆套件的连接说明套件的面板显示说明:1.H M614电源板的CN1接220V交流电源,CN2同时接硬盘电源及HM611音频板的CN1电源接口。

三通道10输入18输出系统同步器产品简介说明书

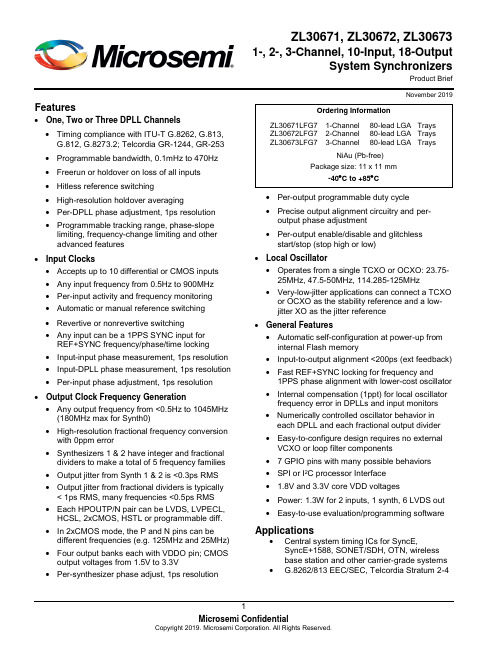

ZL30671, ZL30672, ZL306731-, 2-, 3-Channel, 10-Input, 18-OutputSystem SynchronizersProduct BriefNovember 2019 Features•One, Two or Three DPLL Channels•Timing compliance with ITU-T G.8262, G.813,G.812, G.8273.2; Telcordia GR-1244, GR-253•Programmable bandwidth, 0.1mHz to 470Hz•Freerun or holdover on loss of all inputs•Hitless reference switching•High-resolution holdover averaging•Per-DPLL phase adjustment, 1ps resolution•Programmable tracking range, phase-slope limiting, frequency-change limiting and otheradvanced features•Input Clocks•Accepts up to 10 differential or CMOS inputs•Any input frequency from 0.5Hz to 900MHz•Per-input activity and frequency monitoring•Automatic or manual reference switching•Revertive or nonrevertive switching•Any input can be a 1PPS SYNC input for REF+SYNC frequency/phase/time locking •Input-input phase measurement, 1ps resolution •Input-DPLL phase measurement, 1ps resolution •Per-input phase adjustment, 1ps resolution•Output Clock Frequency Generation•Any output frequency from <0.5Hz to 1045MHz (180MHz max for Synth0)•High-resolution fractional frequency conversion with 0ppm error•Synthesizers 1 & 2 have integer and fractional dividers to make a total of 5 frequency families •Output jitter from Synth 1 & 2 is <0.3ps RMS•Output jitter from fractional dividers is typically < 1ps RMS, many frequencies <0.5ps RMS •Each HPOUTP/N pair can be LVDS, LVPECL, HCSL, 2xCMOS, HSTL or programmable diff.•In 2xCMOS mode, the P and N pins can be different frequencies (e.g. 125MHz and 25MHz) •Four output banks each with VDDO pin; CMOS output voltages from 1.5V to 3.3V•Per-synthesizer phase adjust, 1ps resolution•Per-output programmable duty cycle•Precise output alignment circuitry and per-output phase adjustment•Per-output enable/disable and glitchlessstart/stop (stop high or low)•Local Oscillator•Operates from a single TCXO or OCXO: 23.75-25MHz, 47.5-50MHz, 114.285-125MHz •Very-low-jitter applications can connect a TCXO or OCXO as the stability reference and a low-jitter XO as the jitter reference•General Features•Automatic self-configuration at power-up from internal Flash memory•Input-to-output alignment <200ps (ext feedback) •Fast REF+SYNC locking for frequency and 1PPS phase alignment with lower-cost oscillator •Internal compensation (1ppt) for local oscillator frequency error in DPLLs and input monitors •Numerically controlled oscillator behavior in each DPLL and each fractional output divider•Easy-to-configure design requires no external VCXO or loop filter components•7 GPIO pins with many possible behaviors•SPI or I2C processor Interface• 1.8V and 3.3V core VDD voltages•Power: 1.3W for 2 inputs, 1 synth, 6 LVDS out•Easy-to-use evaluation/programming software Applications•Central system timing ICs for SyncE,SyncE+1588, SONET/SDH, OTN, wirelessbase station and other carrier-grade systems •G.8262/813 EEC/SEC, Telcordia Stratum 2-4Ordering InformationZL30671LFG7 1-Channel 80-lead LGA TraysZL30672LFG7 2-Channel 80-lead LGA TraysZL30673LFG7 3-Channel 80-lead LGA TraysNiAu (Pb-free)Package size: 11 x 11 mm-40︒C to +85︒C1. Block DiagramFigure 1 - Functional Block Diagram2. Application ExampleFigure 2 - Synchronous Ethernet and IEEE 1588 Central Timing ApplicationFracDiv IntDiv FracDivIntDivHP Synthesizer 2low-jitterHPOUT6P HPOUT6N HPOUT7P HPOUT7NDIVREF0P DPLL0R S T _BC S _B _A S E L 0S C K _S C LS O _A S E L 1S I _S D AG P I O [8:0]Microprocessor Port SPI or I2C I/F & GPIO Pins One Diff / Two Single-Ended REF0N REF1P One Diff / Two Single-Ended REF1N REF2P One Diff / Two Single-EndedREF2NREF3P One Diff / Two Single-Ended REF3N REF4P One Diff / Two Single-EndedREF4NReference Monitors & State MachinesDPLL1DPLL2HP Synthesizer 1low-jitterGP Synthesizer 0general purpos eGPOUT0GPOUT1DIV DIVXO Optional x2O S C IO S C OMaster Clock M C L K I N _PDIVHPOUT4P HPOUT4N HPOUT5P HPOUT5N DIV DIVHPOUT0P HPOUT0N HPOUT1P HPOUT1N DIVDIV HPOUT2P HPOUT2N HPOUT3P HPOUT3NDIVDIVM C L K I N _NS R S T _BGPS (1PPS)BITS/SSU Line Extracted Clocks[7:0]TCXODPLL0T4 pathSynth01.544 or2.048MHz CMOS to BITS/SSU1 PPSDPLL1SyncESynth12x 156.25MHz 2x 125MHz155.52MHz, 161.1328125MHz or other frequencyDPLL21588Control info from IEEE 1588 algorithmSynth225MHz 1 PPS or clock w/ embedded PPS 1588 signals to system componentsSyncE signals to system componentsto BITS/SSU systemDPLL1 only present on ZL30672 and ZL30673 DPLL2 only present on ZL306733. Detailed Features3.1 Input Block Features•Ten input reference pins; each can accept a CMOS signal or the POS side of a differential pair; or two can be paired to accept both sides of a differential pair•Any input can be a SYNC signal for REF+SYNC frequency/phase/time locking•Input clocks can be any frequency from 0.5Hz up to 900MHz (180MHz max for CMOS inputs)•Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN, wireless•Inputs constantly monitored by programmable frequency and single-cycle monitors•Single-cycle monitor can quickly disqualify a reference when measured period is incorrect•Frequency measurement (ppb or Hz) and monitoring (coarse, fine, and frequency-step monitors)•Optional input clock invalidation on GPIO assertion to react to LOS signals from PHYs•Input-to-input phase measurement, 1ps resolution•Input-to-DPLL phase measurement, 1ps resolution•Per-input phase adjustment, 1ps resolution3.2 DPLL Features•One, two or three full-featured DPLLs•Very high-resolution DPLL architecture•State machine automatically transitions among freerun, tracking and holdover states•Revertive or nonrevertive reference selection algorithm•Programmable bandwidth from 0.1mHz to 470Hz•Less than 0.1dB gain peaking•Fast frequency/phase/time lock capability for 1PPS or clock+1PPS input references•Programmable phase-slope limiting (PSL)•Programmable frequency rate-of-change limiting (FCL)•Programmable tracking range (i.e. hold-in range)•Truly hitless reference switching•Per-DPLL phase adjustment, 1ps resolution•High-resolution frequency and phase measurement•Fast detection of input clock failure and transition to holdover mode•High-resolution holdover frequency averaging•Time-of-Day registers: 48-bit seconds, 32-bit nanoseconds, writeable on input PPS edge3.3 Synthesizer Features•Any-to-any frequency conversion with 0ppm error•Two low-jitter synthesizers (Synth1, Synth2) with very high-resolution fractional scaling (i.e. non-integer multiplication)•Two output dividers per low-jitter synthesizer: one integer (4 to 15 plus half divides 4.5 to 7.5) and one 40-bit fractional•One general-purpose synthesizer (Synth0)• A total of five output frequency families•Easy-to-configure, completely encapsulated design requires no external VCXO or loop filter components3.4 Low-Jitter Output Clock Features•Up to 16 single-ended outputs (up to 8 differential outputs) from Synth1 and Synth2•Each output can be one differential output or two CMOS outputs•Output clocks can be any frequency from 0.5Hz to 1045MHz (250MHz max for CMOS and HSTL)•Output jitter from Synth1 and Synth2 integer dividers is <0.3ps RMS•Output jitter from fractional dividers is <1ps RMS, many frequencies <0.5ps RMS•In CMOS mode, the HPOUTxN frequency can be an integer divisor of the HPOUTxP frequency (Example 1: HPOUT3P 125MHz, HPOUT3N 25MHz. Example 2: HPOUT2P 25MHz, HPOUT2N 1Hz) •Outputs directly interface (DC coupled) with LVDS, LVPECL, HSTL, HCSL and CMOS components•Supported telecom frequencies include PDH, SDH, Synchronous Ethernet, OTN•Can produce clock frequencies for microprocessors, ASICs, FPGAs and other components•Can produce PCIe clocks•Sophisticated output-to-output phase alignment•Per-synthesizer phase adjustment, 1ps resolution•Per-output phase adjustment•Per-output duty cycle / pulse width configuration•Per-output enable/disable•Per-output glitchless start/stop (stop high or low)3.5 General-Purpose Output Clock Features•Two CMOS outputs from Synth0•Any frequency from 0.5Hz to 180MHz•Output jitter is typically 20-30ps•Useful for applications where the component or system receiving the signal has low bandwidth such asa central timing IC•Can output a clock signal with embedded PPS (ePPS) (duty cycle distortion indicates PPS location) 3.6 Local Oscillator•Operates from a single TCXO or OCXO (jitter reference for the device). Acceptable frequencies:23.75MHz to 25MHz, 47.5MHz to 50MHz, 114.285MHz to 125MHz. Best jitter: ≥48MHz.•Very-low-jitter applications can connect a TCXO or OCXO (any frequency, any output jitter) as the stability reference and a low-cost low-jitter XO as the jitter reference•This ability to have separate jitter and stability references greatly reduces the cost of the TCXO or OCXO (no jitter requirement, no high-frequency-requirement) and allows reuse of already-qualifiedTCXO and OCXO components•Supports redundant TCXOs connected to two REF pins3.7 General Features•Automatic self-configuration at power-up from internal Flash memory•Input-to-output alignment <200ps with external feedback•Fast REF+SYNC locking for frequency and 1PPS phase alignment with lower-cost oscillator•Generates output SYNC signals: 1PPS (IEEE 1588), 2kHz or 8kHz (SONET/SDH) or other frequency •JESD204B clocking: device clock and SYSREF signal generation with skew adjustment•Internal compensation for local oscillator frequency error in DPLLs and input monitors, 1ppt resolution •Numerically controlled oscillator (NCO) behavior allows system software to steer DPLL frequency or fractional output divider frequency with resolution better than 0.005ppt•Spread-spectrum modulation available in each fractional output divider (PCIe compliant)•Seven general-purpose I/O pins each with many possible status and control options•SPI or I2C serial microprocessor interface3.8 Evaluation Software•Simple, intuitive Windows-based graphical user interface•Supports all device features and register fields•Makes lab evaluation of the device quick and easy•Generates configuration scripts to be stored in internal Flash memory•Generates full or partial configuration scripts to be run on a system processor•Works with or without an evaluation board4. Package Outline DrawingSYM COMMON DIMENSIONSMIN NOR. MAX.TOTAL THICKNESS A --- --- 0.9SUBSTRATE THICKNESS A1 0.21 REFMOLD THICKNESS A2 0.54 REFBODY SIZE D 11 BSCE 11 BSCLEAD WIDTH W 0.2 0.25 0.3 LEAD LENGTH L 0.35 0.4 0.45 EP WIDTH W1 1.6 1.65 1.7 EP LENGTH L1 1.6 1.65 1.7 LEAD PITCH e 0.5 BSC EP PITCH e1 1.8 BSC LEAD COUNT n 80EP COUNT n1 16EDGE LEAD CENTER TO CENTER D1 9.5 BSC E1 9.5 BSCBODY CENTER TO CENTER LEAD SD 0.25 BSC SE 0.25 BSCBODY CENTER TO CENTER EP SD1 0.9 BSC SE1 0.9 BSCPRE-SOLDER --- --- --- PACKAGE EDGE TOLERANCE aaa 0.1MOLD FLATNESS bbb 0.1 COPLANARITY ddd 0.08Microsemi Corporate Headquarters One EnterpriseAliso Viejo, CA 92656 USAWithin the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Sales: +1 (949) 380-6136Fax: +1 (949) 215-4996E-mail: ***************************©2019 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for communications, defense & security, aerospace and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world’s standard for time; voice processing devices; RF solutions; discrete components; security technologies and scalable anti-tamper products; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, Calif., and has approximately 3,400 employees globally. Learn more at .Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer’s responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided “as is, where is” and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document is proprietary to Microsemi, and Microsemi reserves the right to make any changes to the information in this document or to any products and services at any time without notice.。

VCD高阶培训资料

1.指南的目的是提供一种方法來檢測8223控制器,包括控制器與机器的緊密作用及影響, 常常碰到問題很難決定是什么原因引起的.2.應檢測項目(下面是首先應檢測)1).J11上面電容C79的電壓必須在4.95-5.00VDC.在EMI/PS 上面測得的電壓不能確 實反應其精確電壓.2).在電源箱后部連接著直流電源<3PL>.它提供+5VDC, ±15VDC 到J11和I/O 箱.如 果3PL 和J11未連接好,J11將會收到低于+5VDC 的電壓.檢查I/O 箱后面的MIB 板, 如果有則上面提到的問題不存在.3).再檢查I/O 箱后面連接線,如果未接好也可能降低I/O 箱及J11之電壓.4).在J11板上及延伸記憶板上裝有IC 槽.看是否有彎腳而短路的IC,特別是記憶板上 IC19更值得怀疑.5).在J11板上及記憶板上電池保險絲(延伸記憶板上1FU 和J11上的3FU 看其燈是否 亮.其中433977××和43423002沒有FUSE.6).看記憶板上的電池是否與PCB 焊接好.用萬用表檢測電池負极與任何IC 的14腳 連接(其接地),它的電阻將小于0.1Ω.7).如果机器EMI/PS 用的是41693302 PC.則它能校正這個電壓值.8).其他時候系統是否有一個正常的電源回升?檢測E MI/PS 與J11CPU 板(10線屏蔽 排線).9).417247××REVB 405912×× 405913××REVL 執行程式是眾所周知能引起電源電 壓變低的程式.修理J11或者更換新執行程式即可.10).系統通訊問題檢測IC65 IC66 IC67 IC67很容易被靜電損坏,有些版本還有IC 插槽以便更換. IC65.MC1488.IC66.MC3487.26LS31CIC67 .MC3486.26LS32A 11).檢查其跳線配置12).系統進入DDT.從而接不适合地接收從控制台IC343or52發來的信息.詳見IC42 和IC53.3.現象下面是系統失敗的种類:8223(J11)控制器基本問題指南1)控制台沒有通迅2)控制台的不适合連接3)控制台的不正確連接4)不能與主電腦連線5)錯誤碼6)系統執行程式不能回升電源7)程式數据丟失8)机器I/O控制不正確9)重復出現UIC重新啟動信息4.控制台沒有通訊1)檢查控制器電源.如果OK繼續下一步2)檢查J11PCB上面的四個狀態燈,如果ok進行下一步<L1燈亮>3)檢查I/O控制台的接口5.控制台不合适的通訊1)檢查電源(控制器)2)檢查IC43和IC523)檢查I/O控制台6.不能同主電腦和其它I/O接口通訊1)檢查控制器電源2)J11四個燈狀態3)檢查I/O接口7.錯誤碼軟件錯誤與硬件錯誤可以導致錯誤碼.由于程序沒有正常的執行或記憶失敗而產生軟件將運行錯誤的內容,硬件問題將包括在內.1)檢查控制器電源2)檢查記憶電路電壓狀況3)檢查EMI/PS電源時序4)檢查有IC插座的IC5)檢查運用的PFAIL程序8.執行程序電源提升錯誤它可能由于錯誤碼所致.根据錯誤碼程序再檢查IC43和IC529.程式數据丟失,也可能是錯誤碼所致10.不正確的机器I/O控制其症狀有.連續不斷的電磁閥鳴叫.不正確的DAC輸出.不正確的編碼器值1)檢查控制器電源2)檢查本址I/O3)檢查外部I/O11.重復輸出UIC重新啟動信息這种問題是由控制器電源所引起的.如果EMI/PS +5VDC電源接近限定值它將檢測電壓是否超出极限.它的极限4.7VDC以上5.3VDC以下.當電源低于或高于极限時.系統將RESET或RESTART机器,且PINT煒會亮.1)檢查控制器電源即可12.1 控制器電源(電源檢測)在測詴點檢測其供電電源.有差異則須研究和分析,較正電壓1)電源箱+5VDC電壓測詴點.不能正確測量-5VDC電壓.其正確測量如下:<1>MIB電源連接器,如果有MIB電源連接器卡安裝在后面,用電表之黑腳測試< TP+5VDC和黃色TP接地><2>在CPU上<J11>找到電容C79位置.用該點測得的電壓與I/O BOX上的+5VDC 電壓作比較.它們的誤差不得大于0.1VDC.如果大于0.1VDC.那么I/O BOX上的+5VDC 之間的CABLE可能連接不當.2)測MIB上棕色測詴點與地電壓是否在14.6VDC-15:00VDC之間3)測MIB或EMI/PS卡上紅色測詴點與電池電壓是否在14.6VDC-15VDC之間4)測EMI/PS橙色測詴點與地電壓為20.8VAC-28VAC.它通過EMI/PS與J11的連接線到J11的保險絲從J11的9PL輸出如果沒有24VAC電時,檢查其路徑5)注意:J11控制器能夠容忍+/-15VDC與24VAC的差異.但不能容忍5VDC,如果5VDC 不能達到這個容忍范圍,檢測其電源箱與I/O BOX之間連接器壓降;做這個測量時5VDC 應幵電一般設定到5.5VDC-5.6VDC.如果電源箱在范圍內;但TP1不同.那么它們之間的連線有間題,扭動電源箱I/O BOX 和Y型CABLE/I/O BOX一般能檢查其原因.在電源箱設定正常時一般DOCK燈會亮,如果OK和DOCK燈熄滅,則EMI/PS卡有問題.12.2 CPU電源測定一般在C79上面測得12.3 EMI/PS卡在EMI/PS有5VDC的壓降,當測詴點電壓作為設定時,允許電壓加大或減小0.25VDC,允許進行更精確的設定電壓而達到減小其壓降.12.4 PINT (POWER INTerrupt)該燈亮表示EMI檢測器己檢測到AC LINE有中斷.或者5VDC超出容許范圍.該燈亮至電源己經停止供電15秒后而熄滅.后續幵電它將OFF直到下一個AC LINE中斷.或5V DC起出4.7-5.3V的范圍.這种情況可以通過快速關閉和快打幵AC電源模擬. 如果該燈亮.不管是否打幵電源它將15秒鐘后熄滅.重新幵電或按EMI/PS上小按鍵即可.13.CPU燈1)當所有LED燈亮意味著系統正在進行重新設定<1> 電源系統錯誤<2> EMI/PS板坏.測詴EMI/PS板上IC40腳,其電壓是否高于4.0-5.1VDC和D5的正板測量為10VDC與15VDC電壓,如果不在范圍內則EMI/PS板坏.<3> EMI/PS與J11之間的線坏.如果EMI/PS卡OK測J11板上IC34第五電壓為4.0-5.1 VDC和測R18近09PL端電壓為-10VDC~-15VDC,如果不在范圍內則EMI/PS卡OK .他們之間連線坏掉.如果線也OK.則J11坏.<4> 如果J11與EMI./PS之間線坏,燈仍亮.2)如果只有LT1燈亮這是正常模式表明:系統正運行程式3)所有燈熄這表明:正進行ODT模式4)別的狀況燈亮或熄.表明CPU己經檢查到有硬件問題.J11可能坏了14.控制台I/O接口檢查K20和K13的跳線設置(即波特率和RS232)下面檢測RS2321)如果有安裝I/O擴展槽的則去掉它.按下RUN/HALT幵關到HALT2)把示波器連到IC67腳1.在鍵盤上按任意鍵,一個信號將會看到.如果沒有信號則J11與電腦終端CABLE或轉換IC有問題 .如果有信號則進行下一步3)連接IC65腳3在鍵盤上敲任意鍵.如果J11收到信息.IC67將會轉換出一個響應,一個幵關信號將會被感應到IC65上面,如果有信號則J11與終端連接線坏.如果無信號線短路過驅動器和接收器,簡單地說信號被IC67pin1接收沒有轉換到IC65pin3,那么J11坏.15.I/O接口1)檢查所有跳線配置2)ROM上的程序幫助I/O接口偵測它們在J11上已標明..包括ASCII DUMP和DATA ECHO3)下面方法既是提供給J11也是提供給接口延伸板4)ASCII DUMP將從接口輸出ASCII字符設定5)DATA ECHO從一個接口收到數据轉換到另一個接口6)在DDT狀態下啟動程序在DDT輸入既定的數据到所要的程序中然后敲G(FORGO )然后程序提供給附加信息.7)對于ASCII DUMP在注冊顯示所儲存的接口基本地址.這些基本地址在J11手冊中己經給定.這些接口號碼己經由机器文件所決定了如 :CHANNE(1 FORHOST CHANNE1 24 FOR VERIFOR等)PORT NAME BASE BOARD控制台(J11COMM INTE ASSY)17777560CHANNEL2(J2.J3 COMM INTE ASSY)17776510HOST(J4 COMM INTE ASSY)17776500CHANNEL3(J2.J3 INTE ASSY)17776520CHANNEL4(J2.J3 INTE ASSY)17776530CHANNEL5(J2.J3 INTE ASSY)17776540CHANNEL6(J2.J3 INTE ASSY)17776550CHANNEL7(J2.J3 INTE ASSY)17776560CHANNEL8(J2.J3 INTE ASSY)17776570CHANNEL9(J2.J3 INTE ASSY)17776600CHANNEL10(J2.J3 INTE ASSY)17776610CHANNEL11(J2.J3 INTE ASSY)17776620CHANNEL12(J2.J3 INTE ASSY)17776630CHANNEL13(J2.J3 INTE ASSY)17776640CHANNEL14(J2.J3 INTE ASSY)17776650CHANNEL15(J2.J3 INTE ASSY)17776660CHANNEL16(J2.J3 INTE ASSY)177766708)對于象ASCII,DUMP測詴,建議把控制台接口聯到終端后幵始測詴.如果測詴別的接口建議:COMMINTCASSY 連接器最好用幵關性能的,以便輸出接口測詴時可以連接到終端.9)對于DATA ECHO儲存有兩個基本地址R0.R1.一般地"0"接口用作控制台,另外一個用作測詴接口10)通過ASCII DUMP程序運行到接口,首先來測詴轉換器的接口用示波器檢查驅動器IC的輸出(RS232.RS422)一個幵關信號將出現,如果轉換器有信號則其OK,如果沒有信號再移掉PCB上40PIN的排線,測詴其有無信號如果沒有則線坏,如果有則J11坏11)在接收器這節是很難檢查必要的輸入源,在一般情況下,設備連接到接口都有數据輸出到控制器,輸入到控制器的數据將檢測J11接收器輸入,如果那里無信號則CABLE有問題,如果信號在該部則PCB坏.12)如果怀疑線有問題可換另外的線直接輸入進行測詴.16.1.記憶体電壓1.1)系統幵電檢測IC16腳28与IC12腳28期間將有大于4.8伏電壓如果沒有則板坏1.2)關掉系統電源測IC16腳28与IC12腳28期間有大于3VDC的電壓,如果沒有測保險1FU和電池,如果保險管与電池都可以但電壓少于3V那么板坏.EXPMEM板43423001沒有保險絲.16.2.延伸記憶板可以移下來進行檢測,但存在里面的數据將丟失2.1)系統幵電檢測IC101.PIN28和IC97PIN28其電壓大于4.8VDC如果無則板坏2.2)關電IC101.PIN与IC97PIN28應大于3伏,檢查2FU及電池,如果OK則板坏17.EMI/PS電路時序1)幵電檢測J11 CPUIC34腳5將是一個高電平,這是一個BPOKH信號,拔出9PL則為低電平,裝上后又是高電平,如果沒有此現象則EMI/PS与J11之間線坏或EMI/PS坏或系統電源坏.2)幵電檢測J11 CPUR18近9PL端將有-15--10電壓,這是一個BDCOKH信號,拔掉9PL 電壓為0±1V,裝上后將為高電平如果無此現象則連線,EMI/PS或系統電源不對3)用示波器檢測BPOKH与BDCOKH之間的時序關系同步示波器激發BPOKH將變成低電壓.用示波器第二道檢測BDCOKH,帶電拔掉9PL可以看到BPOKH將變低2-4MS后, BDCOKH將變成高電平,如果時序不正確則EMI/PS板坏掉.18.IC插座檢查J11板上所有IC插座及IC在延伸記憶板上IC19也應檢查,其中EXP MEM PCB無此插座,裝IC時應注意IC腳有無彎曲19.PFAIL程序的運用1)PFAIL(DA01)執行兩個功能,記憶体讀寫測詴,填滿測詴.象連接執行文件模式連接PFAIL,其將執行記憶体大小与記憶測詴將輸出系統提示符,確定輸入大寫字母以正確版本.1.1)輸入字母M引起系統進行讀寫測詴,如果記憶測詴有錯誤則J11坏1.2)輸入P則系統進行填衝測詴,當回答P測詴問題時輸入2進行填衝測詴,N為記憶線圈電源坏,Y自動回答測詴問題程序在輸入一種模式以后將持續填衝記憶,繼續檢測,當關掉后再幵時它仍然檢測記憶体,如果任何數据有變化程序將報告錯誤直到記憶体通過測詴后,系統將顯示(…..)然后繼續測詴如果程序顯示錯誤則J11坏.20.LOCAL I/OLOCAL I/O就I/O箱中的I/O板,它与J11連接著1)絕大數情況下一塊I/O卡能引起別的I/O卡及J11坏2)在I/O箱內一個問題可以引起I/O箱的外部問題,這是由于數据通I/O箱內的數据線轉換到I/O箱外部.3)I/O箱后面的DTOP DTIP和DSFXPIN有接近15V的電源.如果它們短路有可能造成J11 EMI/PS大多I/O卡失敗在幵電前要確定J11連接器已插進I/O后蓋的位置.I/O卡沒有上對可引起這些PIN短路4)最有效的方法是用示波器進行ODT簡單測詴,但運行這些程序時時鐘將要DISABLE(KX所有跳線短接)完成后確定能裝回5.1)測詴程序作持續讀寫I/O位置5.2)當執行DSF DTOP和DTIP時要檢測數据線5.3)如果遇到不合適的邏輯標准時,幵始移掉I/O卡直到信號正確為止如果都無效則EMI与J11坏掉5.4)下面就是一個測詴程序Page 7在ODT輸入位置10001000/10037 LABEL:MOV RO,166001002/1660001004/775 BR LABEL位置1002就是DSF正在被測詴的地址:EX.DSFO=166000DSF1=166002DSF2=166004 ETE然后再敲入1000 G開始執行程序DSF×DTOP將會看到如下:5.4.2) READ 100P在ODT輸入位置10001000/13700 LABEL:MOV 166000.RO1002/1660001004/775位置1002正好就是DSF地址 :EX DSFO=166000DSF1=166002 DSF2=166003等然后敲入1000GDSFXTIP將會如下顯示Page 8數据線(DIXX為讀循環,DOXX為寫循環)將會在DTOP DTIP時間內檢測,如果哪里有問題數据將會錯誤21.I/O外部接口外部I/O就是J11沒有連接的I/O BOX外部,注意內部I/O有問題就有可能引起外部I/O某些症狀,就像內部I/O一樣執行寫讀和檢測信號22.IC43和IC52IC43和IC52 PLSI59 IC在上面有零件號碼4034830X 4315450X 4320900X 4332990X這些零件坏掉類似症狀系統進入ODT与控制台不能下沉通迅敲空格鍵屏幕字符將死掉或控制器不能懂得ODT輸入1)IC43將產生事件時鐘信號(一般地IC43跳線設定1MS),當其坏掉時它將輸出所有時間數据到數据線,這樣微處理器就不能正常讀寫數据,簡單的測詴即可,移掉IC控制器能懂得控制台的輸入,則IC43坏2)IC52為板上的線路產生多個時序時鐘,包括I/O接口芯片所需的614KHZ的時鐘該IC坏掉將輸出多個錯誤頻率,IC52 PIN16將產生614.4KHZ的方波,如果沒有方波則IC坏掉,PIN12呈低頻率.如果脈衝呈高頻則IC52坏.23.附錄A1)電源電壓設定在電壓為4.8V-5.2V的電壓下J11的任何地方都能正常動作,在I/O BOX中的EMI/PS中有一個電壓偵測器,檢查其是否在4.7-5.3V范圍內,如果檢測到電壓超出范圍,它將快速送出一個關掉時序到J11,這個時序將引起控制器記憶數据改變而沒有電源失敗限制允許的最大差異(大多數是由于連接器問題).建議把電壓設定到盡可能接近5V,這佯就可獲電壓漂移的最大量, 例如:假設電壓設定到4.9V,那么据4.7V只有0.2V的漂移量.這樣就會影響記憶.如果5.0則有0.3V的漂移量,這樣就減少了机器故障.24.ODT摘要Page 9E.O.F.GENERAL IN FORMATION CONCERNINGSWITCHIMG SERVO AMP SYSTEM放大板1)在气流量正常范圍內,正確的詞服放大幵關設定,程式優化和ERV正常的設定等條件下机器能夠達到其最大產能,如果以上條件都OK,但机器仍運行很慢,那么可能是由于刀具挂髒磨損,損坏零件2)排列机鏈條馬達和深度馬達裝有永久性磁鐵在里面,因此它不會被伺服放大卡上過多的電流所磁化.3)但如果提供給VCD鏈條馬達在伺服電流大于12AMPS時,由于其馬達內是鐵氧体就會引起磁化現象,這樣馬達就會加快造成鏈條錯誤,因此其伺服卡電流都被限制到12 AMPS以下.4)6241B的馬達用的是3相無刷直流馬達,三個線圈包圍著旋轉磁性葉輪旋轉,這樣轉動磁体(即轉動馬達)將會依次提供給每個線圈85VDC電壓,決定什么時候打開下一個線圈的電壓而改變磁体的方向,這樣繼續旋轉磁体轉連器HOUSING有三個赫爾效應開關.這些效應開關感應到葉輪轉到當前的位置通知伺服放大卡葉轉的位置,開關伺服放Page 10大器持續提供給馬達驅動電壓的頻率約為20KHZ,電壓脈衝變短則驅動馬達則減速,每5)伺服放大板終端連接有如下功能:TB1-2控制鏈條驅動卡或刀具驅動的PAC/FD6K卡的速度來控制鏈條TB1-3接地主要用于速度命令線屏TB1-4中斷當其接地時馬達驅動變得不連續,馬達由于磨擦而減速TB1-5 時針限制,當其接地時馬達防止時針方向驅動TB1-6順時針限制,當其接地時馬達將被防止向順時方向驅動TB1-7馬達驅動限制,當其接地時,馬達將驅動到一個站(箱制位)TB1-10接地二. 開關伺服放大系統TROUBLCSHTOTING(故障檢修)現象:說明和引起原因1.鏈條錯誤它可分為硬体鏈條錯誤和軟体鏈條錯誤.當硬体鏈條發生錯誤時,鏈條驅動板上LED燈將會照亮,就可確定為硬鏈條錯誤.軟鏈條錯誤發生時常有軟件不合適宜現象.即當鏈條驅動板沒有接收到預期鏈條編碼反餽,其可能原因為鏈條過緊,馬達失靈編碼器失靈,伺服放大失靈(故障)線或連接器坏.2.Z3刀具不能驅動分析如下3B3.不能歸零分析如下21)盡為恢復鏈條,轉動面板上鏈條錯誤鎖開關,滅掉鏈條錯誤開關,重新運行程式設定套數為1,這樣可以減少不必要的浪費.2)歸零机器A.如果机器不能歸零也不能產生鏈條錯誤,則檢查VCD限制開關確定其所有開關沒有Page 11激活(只有兩個).B.如果机器OK則正常動作C.如果仍有鏈條錯誤則處理如下a.檢查整個鏈條机器裝置,拆下排列机鏈條馬達接頭以及vcd接頭用5/8T形扳手或套筒扳手卡到鏈條与蓮條之間的轉換器中轉動鏈條如果轉不動則鏈條卡如果能輕松轉動到4.b.是否刀具能驅動取出刀具檢查是否髒,挂或零件坏再歸零.4.檢查伺服板LED是否亮如果所有燈亮則參照如下:S.F(SWITCH FAULT)開關錯誤SWITCH FAULT 表明電源幵關橋有錯誤,可能是相與相.或與地短路拔掉連接馬達的排線,再按放大板上的RESET鍵.如果SF燈熄滅.則馬達必定短路.更換馬達,如果SF燈仍然亮,則可能馬達線有短路,也有可能是線路到伺服板終端TB2有短路也可能是本身有問題.則需更換.C.F /O.T. 掁流器錯誤或者溫度過高燈亮檢查馬達剌TB.之間的TACH線是否幵路,如果其斷路或幵路,則OF.OT燈將會亮,如果有多余馬達 ,則連接TACH線到空余馬達,再按RESET鍵如果燈熄滅,則原馬達由于掁流器坏而需更換,如果燈仍亮,則可能是放大器的溫度過高而造成,檢查放大箱內電扇是否其里面有過多灰塵如果外圍溫度過高或過載而引起溫度過高,那么當放大器冷卻下來后則此故障消除,如果沒有這种現象,則放大板坏.U.V. 電壓過低燈亮這种現象表明邏輯電源供應失敗與間隙性短路(即瞬間短路),檢查放大是否有零件彎曲或短路,或者是放大器盒里是否掉入東西致短路,如果無,則更換放大板.O.V . 電壓過高燈亮這個現象表明母線電壓超過限制電壓,檢查机器AC輸入電壓是否正確或者有波動,它可能是由過載(伺服放大板設定不正確),當鏈條停止運作,如果這燈又熄滅,運作時燈又亮,如果不是這樣那么放大板需更換5.如果伺服板所有燈都不亮,則檢測如下:Page 12A.檢查開關放大箱內17FU和18FUB.檢查馬達和編碼器所有的連接器C.如果懷疑馬達有問題請看下面章節,CHEEKING A MOTORD.如果懷疑編碼器坏則,更換編碼器,或根据UIC提供的編碼器檢測器檢測其好坏.E.如果馬達OK板LED燈都不亮,編碼器又OK.所有線與連接器又OK,那么.鏈條驅動卡(I/O箱)坏,另外一個原因就是J11有硬件或軟件問題.因此在更換驅動卡前,要重新連接一下程序,看是否還是一樣的症狀,如果沒有別的症狀出現則,鏈條驅動卡坏,F.如果上面的方法都不能解決則通知和咨詢環球設備.技朮人員來獲得進一步信息三.CHECKING A MOTER (檢修馬達)1.每一個馬達均有4PIN的連接器,它們分別為紅線.白線.黑線和綠線2.關机拔掉插頭,用萬用表打到交流電壓檔.分別測量下面的線1)紅線與黑線. 2)紅線與白線黑線與白線 ..當檢測這些線時用手轉動馬達軸..則可以得到至少1VAG的交流電,轉得越小,則電壓越高,如果有一根線幵路,那么該線就無電壓,同時也可不用口檔檢查是否有短路,則紅線與綠線.綠線與黑線,白線與綠線將斷路3.如果馬達通過以上測詴,則就檢測轉速器速度反餽,將馬達插頭(連接器)拔掉,幵机,連接TBI-9,TBI-12 測量其電壓在2V檔內,當用手轉動馬達時,電壓讀數將會得到,再反方向轉動馬達,電壓方向也應改變,用萬用表打到20VDC檔,如下各線(其中 PIN10接地)用萬用表打到20VDC檔,如下各線(其中 PIN10接地) PIN13與PIN10.PIN14與PIN10PIN15與PIN10當馬達慢速轉動時,電壓變動也將隨之變化.其變化近似為DVPC和12VDC恰好就是葉輪轉翼處在檢測中的激活與未激活兩种狀態(注意:對于TOOLING馬達,所有的這些幵關就沒有變化.這是因為當IOOLING被驅動時,馬達的全周旋轉沒有發生,當馬達移掉后,僅只有兩個幵關檢測他們的電壓讀數.)四.DHSET PAT ADJUST MOINT(參考點的調整)1.幵電源2.机器歸零Page 133.在終端電腦敲D27再敲ENTER4.敲入100.0000.0000.0000(14個口).再敲ENTER這是激活歸0速度字節,同時,使所有的幵關伺服,系統幵關置于驅動命令控制之外.5.檢查所有三個伺服放大馬達,如果任何一個馬達幵始轉動,那么表明馬達需在被調參考點,坐而減少漂移.如果漂移引起限制幵關,激活,則必須退出,Dingndstics(預測)重新回到stop26.離幵敲0.再敲enter即可.Page 14。

VCD数码机芯电路系统2解读

2.5V

(3)数字信号处理电路常见故障及检修方法

5)数字处理芯片CXD2545Q 的45脚(左右声道时钟信号 LRCK )、46脚(串行数据 DATA)、47脚(位时钟信

号)在停止和重放时波形一 致,电压为2.5VPP左右。而 46脚(串行数据DATA)在 停止时电压为0V,如右图所 示。

LRCK信号 DATA信号 BCK信号

17

18

(3)数字信号处理电路常见故障及检修方法 以CXD2545Q为例,它内部包括主轴电机伺服、聚 集伺服、循迹伺服、进给伺服电路。在实际维修中,对 与数字信号处理相关的伺服电路进行检修采用示波器测 量波形的办法来判断故障。如书中表3.1

CXD2545Q

19

(3)数字信号处理电路常见故障及检修方法

38 非对称 性校正

R144 R145

C139

同步保护

C140

39

16.9377MHz 62

缓冲器

32KRAM

EFM 解调

数

据

寄

总

存

线

器

D/A 数据 处理

数字 PLL

时钟

纠错 子码Q处理器

LRCK 45

串/并 行处 理器

DATA 46

BCK 47

C2PO 56

SQSO 77

SQCK 78

EFM输出的8位数字信号分为两路:寄存器、数据处理电路;子码处理器

VCD机的控制和信号处理都是按一定程序进行的,在每 次开机时都必须进行系统初始化,让机器进入预设的工作状 态。

开机通电后,微处理器(CPU)首先被复位,使其自身 初始化;然后CPU先对显示电路初始化,显示屏按设计要求 显示字符;再对MPEG1解码内部寄存器进行初始化,并将 ROM中的微码载入DRAM与解码器,开机画面随即产生;最 后对机芯控制电路初始化,使机芯完成光头复位、搜索、检 测等动态控制。

介绍两种VER2.0的VCD解码板

介绍两种VER2.0的VCD解码板

姜凌

【期刊名称】《实用无线电》

【年(卷),期】1996(000)001

【摘要】电子部直属天利电子技术公司是国内较早开发研制VCD解码板的公司之一,本文作者是天利电子技术公司技术开发部的主任,一直跟踪世界最新技术,最早接触C-CUBE公司的集成芯片,对CL480有着独到的见解,作为VCD项目组长,姜凌主持开发了整机型和加装型3个品种7种型号的VCD解码板,独立完成4种型号解码板的开发,是目前为数不多的VCD解码板的国内专家之一。

这里介绍了TL—VCD(Ⅰ)B全功能整机型和(Ⅲ)A加装型两种解码板。

一种可完全实现VER2.0版表的功能,另一种可支持VER2.0的功能,使用(Ⅲ)A加装板后CD机的功能超过早期整机厂生产的VCD机。

【总页数】6页(P1-6)

【作者】姜凌

【作者单位】无

【正文语种】中文

【中图分类】TN946

【相关文献】

1.四通博石K870 VCD机解码板原理与故障检修 [J], 苏军

2.应急修理VCD解码板的几种方法 [J], 苏军

3.最新CD机升级板TL—VCD(Ⅲ)A型解码板介绍 [J], 天利

4.介绍一种采用CL484的2.0版VCD解码板 [J], 贺琦

5.TL-VCD Ⅲ(C)解码板应用实例——“健伍”组合音响CD机DP-47改装为VCD机的方法 [J], 曾梅

因版权原因,仅展示原文概要,查看原文内容请购买。

货代考试英文缩略语翻译

货代考试英文缩略语翻译1. IGO in ter-gover nment orga ni zati on 政府间国际组织2. NGO non-governme nt orga nizatio n 非政府间国际组织3. ICS intern atio nal chamber shipp ing 国际航运公会4. BIMCO Baltic and in ternatio nal maritime cou ncil 波罗的海国际海事协会5. CMI committee maritime intern ati onal 国际海事委员会6. IMO intern ati onal maritime orga ni zati on 国际海事组织7. LNG liquified n atural gas 液化天然气8. LPG liquified petroleum gas 液化石油气9. SF stowage factor 货物积载因数10. IMDG Code intern ati onal maritime dan gerous goods code 国际海运危险货物规则11. ISO in ternatio nal sta ndard organi zatio n 国际标准化组织12. SOC shipper\'s own con tai ner 货主箱13. COC carrier\'s own con tai ner 船公司箱14. TEU twe nty-foot equivale nt un its 计算单位,也称20英尺换算单位15. FCL full con ta iner load 整箱货16. LCL less co ntai ner load 拼箱货17. CY con tai ner yard 集装箱堆场18. CFS con ta iner freight stati on 集装箱货运站19. DOOR货主工厂或仓库21. SC service con tract 服务合同20. DPP damage protectio n pla n 损害修理条款21. SC service con tract 服务合同22. B/N booking note 托运单23. S/O shipping order 装货单,也称下货纸、关单24. M/R mate\'s receipt 收货单,也称大副收据25. M/F manifest 载货清单,也称舱单26. S/P stowage plan 货物积载图,也称船图、舱图27. D/O delivery order 提货单,也称小提单28. MSDS maritime shipping document of safety 危险货物安全资料卡29. D/R dock\'s receipt 场站收据30. EIR(E/R) equipment interchange receipt 设备交接单31. CLP container load plan 集装箱装箱单32. SOF statement of facts 装卸事实记录33. B/L bill of lading 提单34. HB/L house bill of lading 代理行提单,或称子提单、分提单、货代提单、无船承运人提单、仓至仓提单等35. Sea B/L (Master B/L, Ocean B/L, Memo B/L) 海运提单,或称母提单、主提单、船公司提单、备忘提单等36. On board B/L, Shipped B/L 已装船提单37. Received for Shipment B/L 收货待运提单38. Straight B/L 记名提单39. Open B/L (Blank B/L, Bearer B/L) 不记名提单40. Order B/L 指示提单41. Clean B/L 清洁提单42. Foul B/L (Unclean B/L) 不清洁提单43. Direct B/L 直达提单44. Transshipment B/L 转船提单45. Through B/L 联运提单46. Combined Transport B/L (Intermodal Transport B/L, Multimodal Transport B/L) 多式联运提单47. Minimum B/L 最低运费提单,也称起码提单48. Advanced B/L 预借提单49. Anti-dated B/L 倒签提单50. Stale B/L 过期提单51. On Deck B/L 甲板货提单过期52. Switch B/L 转换提单53. NVOCC non-vessel operations common carrier 无船公共承运人或无船承运人54. 《Hague Rules 》《海牙规则》,正式名称为《统一关于提单若干法律规定的国际公约》55. 《Visby Rules 》《维斯比规则》,正式名称为《关于修订统一提单若干法律规定的国际公约》56. 《Hamburg Rules》《汉堡规则》,正式名称为《1978年联合国海上货物运输公约》57. SDR special drawing rights 特别提款权58. LOI letter of indemnity 保函,也称损害赔偿保证书59. SLAC shipper\'s load and count 货主装载、计数60. SLACS shipper\'s load, count and seal 货主装载、计数和加封61. STC said to contain 内容据称62. SWB seaway bill 海运单63. V/C voyage charter 航次租船,简称程租64. T/C time charter 定期租船,简称期租65. TCT time charter on trip basis 航次期租66. COA contract of affreightment 包运租船,简称包船67. C/P charter party 租船合同68. F/N fixture note 确认备忘录,也称订租确认书69. GENCON \"金康\"合同,全称为BIMCO统一杂货租船合同70. NYPE Form \" 土产格式\" ,全称美国纽约土产品交易定期租船合同71. BALTIME \"波尔的姆格式\",全称为BIMCO标准定期租船合同72. BARECON\'A\'标准光船租船合同A格式73. SINO TIME 中租期租合同74. DWT dead weight tonnage 载重吨75. GRT gross registered tonnage 总登记吨,简称总吨76. NRT net registered tonnage 净登记吨,简称净吨77. LOA length over all 船舶总长度78. BM beam 船宽79. MT metric tons 公吨(1 000千克)80. LAYCAN layday/canceling date 受载期与解约日81. LINER TERMS 班轮条款,即船方负担装卸费82. BERTH TERMS泊位条款,即船方负担装卸费83. GROSS TERMS、承兑条款,即船方负担装卸费84. FAS free alongside ship 船边交接货条款,即船方负担装卸费85. FI free in 船方不负担装货费86. FO free out 船方不负担卸货费87. FILO free in ,liner out 船方不负担装货费但负担卸货费88. LIFO liner in, free out 船方不负担卸货费但负担装货费89. FIO free in and out 船方不负担装卸费90. FIOST free in and out, stowed and trimmed 船方不负担装卸费、平舱费和堆舱费91. N/R (NOR) notice of readiness 装卸准备就绪通知书92. WIBON whether in berth or not 不论靠泊与否93. WICCON whether in custom clearance or not 不论海关手续办妥与否94. WIFPON whether in free pratique or not 不论通过检疫与否95. WWDSHEXwUeUather working days, Sunday, holidays excepted, unless used 晴天工作日,星期天和节假日除外,除非已使用96. WWDSHEXEwIUeather working days , Sunday, holidays excepted, even if used 晴天工作日,星期天和节假日除外,即使已使用也除外97. WWDSATPMSHwEeaXther working days, Saturday PM, Sundays, holidays excepted 晴天工作日,星期六下午、星期天和节假日除外98. WWDSSHEX weather working days, Saturday, Sundays, holidays excepted 晴天工作日,星期六、星期天和节假日除外99. CQD customary quick dispatch 按港口习惯快速装卸100. WTS working time saved 节省的工作时间101. BFI Baltic freight index 波罗的海运价指数102. CCFI China container freight index 中国出口集装箱运价指数103. BAF, Bs bunker adjustment factor; or bunker surcharge 燃油附加费104. CAF currency adjustment factor 货币附加费105. THC terminal handling charges 码头作业附加费,或称码头操作费106. PSS peak season surcharge 旺季附加费107. DDC destination delivery charges目的地交货费108. FAK freight all kinds 均一包箱费率109. FCS freight for class 基于商品等级的包箱费率110. FCB freight for class and basis 基于商品等级和计算标准的包箱费率111. ICAO international civil aviation organization 国际民用航空组织112. IATA international air transport association 国际航空运输协会113. SITA 国际电信协会114. AWB air waybill 航空货运单115. HAWB (HW)B house air waybill 航空分运单116. MAWB(MW)B master air waybill 航空主运单117. TC1,TC2,TC3 traffic conference area 航空区划1、航空区划2、航空区划3118. GMT Greenwich mean time 世界标准时,也称格林尼治时119. TACT the air cargo tariff 航空货物运价120. TACT Rules 航空货物运价手册121. CN China 中国122. DE Germany 德国123. SG Singapore 新加坡124. CA Canada 加拿大125. AU Australia 澳大利亚126. BIS 北京127. TAO 青岛128. CAN 广州129. SHA 上海130. CKG 重庆131. TSN 天津132. SZX 深圳133. HGH 杭州134. KMG 昆明135. XMN 厦门136. DLC 大连137. NGO 名古屋138. CA 中国国际航空公司139. CZ 中国南方航空公司140. MU 中国东方航空公司141. CI 中华航空公司142. CX 国泰航空公司143. NX 澳门航空公司144. CAO cargo aircraft only 仅限货机145. DIP diplomatic mail 外交信袋146. SLI shippers letter of instruction 空运托运书147. CBA cargo booking advance 国际航空货物订舱单148. TRM cargo transfer manifest 转运舱单149. LAR live animal regulation 活动物规则150. DGR dangerous goods regulations 危险物品手册151. GCR general cargo rate 普通货物运价152. SCR specific commodity rate 指定商品运价153. AW air waybill fee 货运单费,承运人收取此费为AWC代理人收取此费为AWA154. CH clearance charge for agency 清关费,代理人收取此费为CHA 155. SU surface charge 地面运输费,代理人收取此费为SUA156. DB disbursement fee垫付款手续费,承运人收取此费为DBC代理人收取此费为DBA157. RAdangerous goods surcharge 危险品处理费,承运人收取此费为RAC,代理人收取此费为RAA158. SD surface charge destination 目的站地面运输费159. CC charges collect 运费到付160. PP charges prepaid 运费预付161. ULD unit load device 集装器,集装化设备162. MCO 旅费证,也称杂费证163. NVD no value declared 没有声明价值164. NCV no commercial value 无商业价值165. CCA cargo charges correction advice 货物运费更改通知166. OFLD offloaded 卸下,拉货167. SSPD short-shipped 漏(少)装168. Ovcd over-carried 漏卸169. POD proof of delivery 交付凭证170. CASS, cargo account settlement system 货运帐目清算系统171. IPI interior point intermodal内陆公共点多式联运172. SLB Siberian land bridge traffic西伯利亚大陆桥运输173. OCP overland common point 内陆公共点或陆上公共点运输174. MLB miniland bridge 小陆桥运输175. Combidoc由BIMCO制定的供经营船舶的多式联运经营人所使用的国际多式联运单证176. FBL由FIATA制定的供作为多式联运经营人的货运代理使用的国际多式联运单证177. Multidoc 由UNCTAD依据《联合国国际货物多式联运公约》制定的国际多式联运单证178. MTO multimodal transport operator 多式联运经营人179. NVO non vessel operator 无船经营人。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

© 2001 IXYS All rights reserved

1 - 2

IXYS reserves the right to change limits, test conditions and dimensions.

I TRMS =2x180A I TAVM =2x105A

V RRM =800 - 1800 V

Thyristor/Diode Modules

ECO-PAC

Features •Isolation voltage 3600 V~•Planar glass passivated chips •Low forward voltage drop

•

Leads suitable for PC board soldering

Applications •DC motor control

•Light and temperature control •Softstart AC motor controller •

Solid state switches

Advantages

•Easy to mount with two screws •Space and weight savings

•Improved temperature and power cycling

•High power density •Small and light weight

Preliminary Data

13

5

Data according to IEC 60747 refer to a single thyristor unless otherwise stated

Symbol Conditions

Maximum Ratings

I TRMS 180A I TAVM T C = 85°C; 180° sine 105A I TSM

T VJ = 45°C; V R = 0 V;

t = 10 ms (50 Hz), sine

2250A t = 8.3 ms (60 Hz), sine

2400A T VJ = 125°C; V R = 0 V;t = 10 ms (50 Hz), sine

2000A t = 8.3 ms (60 Hz), sine

2150A I 2dt

T VJ = 45°C; V R = 0 V;

t = 10 ms (50 Hz), sine 25300A 2s t = 8.3 ms (60 Hz), sine

23900A 2s T VJ = 125°C; V R = 0 V;t = 10 ms (50 Hz), sine

20000A 2s t = 8.3 ms (60 Hz), sine

19100A 2s (di/dt)cr

T VJ = 125°C;repetitive, I T = 250 A 150

A/µs

f = 50 Hz; t P = 200 µs;V D = 2/3V DRM ;I G = 0.45 A non repetitive, I T = I TAVM 500A/µs di G /dt = 0.45 A/µs;

(dv/dt)cr T VJ = 125°C; V DR = 2/3V DRM

1000V/µs R GK = ∞, method 1 (linear voltage rise)P GM T VJ = 125°C;t P = 30 ms ≤ 10W I T = I TAVM ;

t P = 300 ms

≤ 5

W P GAVM 0.5W V RGM 10

V T VJ -40 ... + 125

°C T VJM 125

°C T stg -40 ... + 125

°C V ISOL 50/60 Hz, RMS t = 1 min 3000V ~I ISOL < 1 mA t = 1 s 3600V ~M d Mounting torque (M4)

1.5 -

2.0Nm 14 - 18

lb.in.Weight

typ.

26

g

V RSM V RRM V DSM V DRM Typ

V

V

900 800 VCD 105 - 08io71300 1200 VCD 105 - 12io71500 1400 VCD 105 - 14io71700 1600 VCD 105 - 16io71900 1800

VCD 105 - 18io7

Symbol Conditions

Characteristic Values min.typ.max.

I D , I R T VJ = 125°C; V R = V RRM ; V D = V DRM 5mA V T I T = 300 A; T VJ = 25°C

1.5

V

V TO For power-loss calculations only 0.8V

r T 2.4m ΩV GT V D = 6 V;T VJ = 25°C 1.5V T VJ = -40°C 1.6V I GT V D = 6 V;T VJ = 25°C 150mA T VJ = -40°C 200mA V GD T VJ = 125°C;V D = 2/3V DRM 0.2V I GD T VJ = 125°C;

V D = 2/3V DRM

10mA I L T VJ = 25°C; t P = 10 ms

450mA I G = 0.45 A; di G /dt = 0.45 A/µs I H T VJ = 25°C; V D = 6 V; R GK = ∞200mA t gd T VJ = 25°C; V D = ½ V DRM

2

µs

I G = 0.45 A; di G /dt = 0.45 A/µs R thJC per Thyristor; DC 0.26K/W per module

0.13K/W

R thCH per Thyristor; DC 0,2K/W per module

0,1

K/W d S Creeping distance on surface 11.2mm d A Creeping distance in air 5.0mm a

Max. allowable acceleration

50m/s 2。