modelsim编译LPM文件解决方法

Modelsim仿真库的编译

在使用Mode lSim软件对Xilin x ISE进行后仿真时,需要先编译Xi linx的仿真库,否则就会产生无法加载sim prim,unisim等库文件的错误。

在许多论坛上都提到了使用c ompxli b命令来编译Xilinx的仿真库,如使用comp xlib -s mti_se–arch all -l all -dir D:\Modelte ch_6.0\xilinx_lib -w.但是对于如此复杂,而又不经常使用的命令有谁会愿意记忆呢。

还好我们可以使用一个具有图形化界面的编译向导工具来方便的产生仿真库。

今天无意中在X ilinxise软件的安装目录下发现了一个名为c ompxli bgui.exe的程序,根据其名字可以推测这是一个用于编译仿真库的图形化程序。

打开一看,确实很好用,提供向导式的编译过程,只需一路nex t就可以搞定。

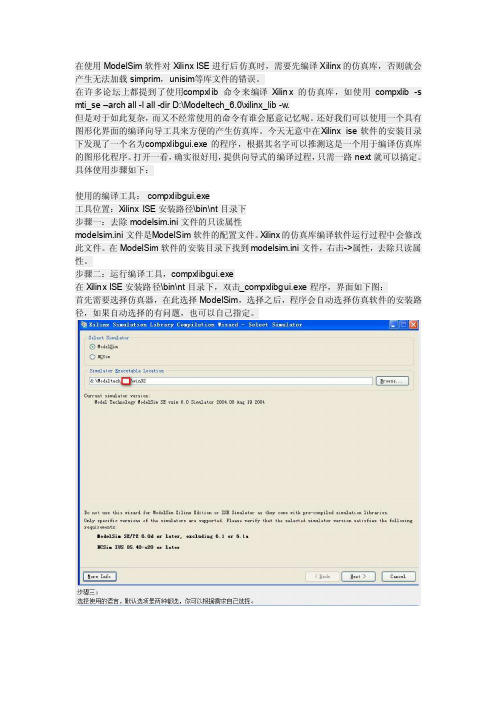

具体使用步骤如下:使用的编译工具: compxli bgui.exe工具位置:XilinxISE安装路径\bin\nt目录下步骤一:去除model sim.ini文件的只读属性modelsi m.ini文件是M odelSi m软件的配置文件。

Xilinx的仿真库编译软件运行过程中会修改此文件。

在ModelS im软件的安装目录下找到models im.ini文件,右击->属性,去除只读属性。

步骤二:运行编译工具,compxli bgui.exe在Xilinx ISE安装路径\bin\nt目录下,双击_comp xlibgu i.exe程序,界面如下图:首先需要选择仿真器,在此选择Mod elSim,选择之后,程序会自动选择仿真软件的安装路径,如果自动选择的有问题,也可以自己指定。

如何用ModelSim se完全编译Xilinx库文件2010-12-28 15:07:29| 分类:默认分类|字号订阅什么是之前的老办法呢?Modlesi m 仿真库的建立:将Models im根目录下的model sim.ini的属性由只读改为可写。

安装modelsim6.5可能出现的问题以及解决办法

有时安装系统时不能填用户名和组织名,或是随便填一个,后来要更改用户名,该怎么办呢电脑用户名为中文造成Modelsim SE读取注册文件错误今天安装Modelsim SE6.5的时候,使用网上的破解软件破解;发现使用Modelsim ?License Wizard导入破解文件生成的license.dat时候报错;错误信息如下:Fatal License Error:Unable to check out alicense.RuntheModelsimLicensing wizard from the start->Programs menu to diagnose the problem仔细阅读发现是license.dat文件里面含有非法字符;因此打开license.dat发现应该是装机的时候用户名和组织是默认中文造成的。

找了改正用户名和组织名的方法,给大家分享;如何修改XP安装时的用户名和公司名?在java程序开发中,每个类开头加入javadoc注释时,生成的作者名总要修改,不方便,在网上找到了可行的方法下面是彻底修改安装操作系统时的用户名和公司名(1)打开“注册表编辑器”。

(2)选择HKEY_LOCAL_MACHINE/Software/Microsoft/Windows NT/Current Vers-ion ? ? ? ? 注册表项。

(3)在其右边的值项窗格中,双击RegisteredOwner 值项,打开“编辑字符串”对话框。

(4)在“数值数据”文本框中更改个人的信息,单击“确定”按钮即可。

(5)双击RegisteredOrganization 值项,打开“编辑字符串”对话框。

下面是修改系统中显示的用户名??右键“我的电脑”---“管理”---“本地用户和组”---“用户”,右键点击你要修改的用户名,选择“重命 ? 名”,改成你要的名字就可以了?这两个方法都做后,系统启动时的名字也会改变。

想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀

想很多人跟我一样,被ModelSim的后仿真搞的头晕脑胀。

为了这个问题,我在网上找了很多的资料,但发现这些资料往往说的不明白。

一些步骤被作者有意无意地省略掉,这常常给读者造成不必要的麻烦,所以我决定写下这一篇文章,把这3天我努力的结果拿出来,与大家分享。

首先,我把我用到的软件说明一下。

如果你发现根据我的操作,你还是解决不了ModelSim后仿真的问题,那就可能是软件版本的问题。

1, ModelSim Se 6.1b2, Synplify Pro 7.5.13, ISE 5.2i (这个是老了点)4, WindowsXP(这个应该没有多大的关系)还有就是我使用的是verilog,我想VHDL的方法与verilog是差不多的,最多也就是在建库方面有点差别而已。

下面的这些方法,是我这3天搞出来的。

当然也参考了一些文章。

如果谁有更方便的方法,欢迎指出来。

我的邮箱是****************。

有空大家多交流。

一、为modelsim生成3个库。

首先,介绍一下这三个库。

Simprim_ver:用于布局布线后的仿真。

Unisim_ver :如果要做综合后的仿真,还要编译这个库。

Xilinxcorelib_ver:如果设计中调用了CoreGen产生的核,则还需要编译这个库。

我们要为modelsim生成的是标准库。

所谓的标准库就是modelsim运行后,会自动加载的库。

不过这方面我还不是很肯定。

因为我在后仿真时,还是要为仿真指定库的路径,不然modelsim找不到。

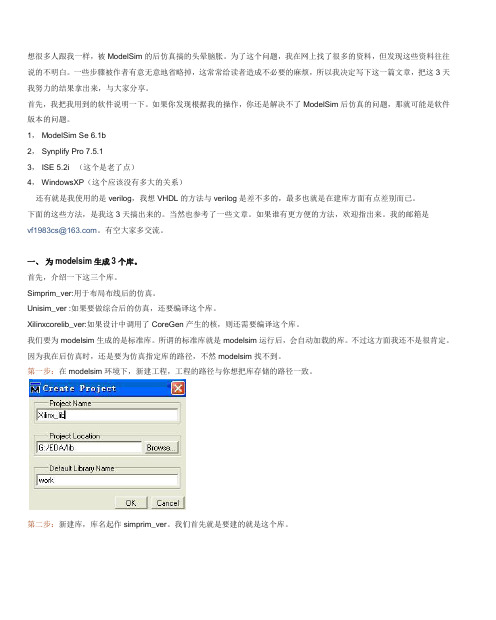

第一步:在modelsim环境下,新建工程,工程的路径与你想把库存储的路径一致。

第二步:新建库,库名起作simprim_ver。

我们首先就是要建的就是这个库。

第三步:在modelsim的命令栏上,打下如下命令:vlog -work simprim_ver d:/Xilinx/verilog/src/simprims/*.v其中的d:/Xilinx是我的Xilinx的安装路径,你把这个改成你的就行了。

modelsim 编译 顺序

modelsim 编译顺序Modelsim编译顺序Modelsim是一款功能强大的仿真工具,常用于数字电路的设计和验证。

在进行数字电路仿真时,编译顺序是一个非常重要的环节,它决定了仿真的准确性和效率。

本文将详细介绍Modelsim的编译顺序,以帮助读者更好地理解和运用这一工具。

一、源代码编译在进行数字电路仿真之前,首先需要将设计的源代码编译成可执行的仿真文件。

Modelsom支持多种源代码语言,如VHDL和Verilog 等。

编译时,Modelsom会解析源代码,并将其转换成仿真器可识别的形式。

该步骤确保了源代码的正确性,为后续的仿真做好准备。

二、库文件编译在进行数字电路仿真时,通常会使用一些标准的库文件,如IEEE库等。

这些库文件中包含了一些常用的模块和函数,可以加快仿真的速度和准确性。

Modelsom需要先将这些库文件编译成可执行的库文件,以供后续的仿真使用。

三、综合综合是数字电路设计中的一个重要环节,它将高级的RTL (Register Transfer Level)描述转换成低级的门级电路描述。

在Modelsom中,综合是将源代码中的逻辑门和触发器等元件实例化,并将其连接起来形成一个完整的电路模型。

综合的结果是一个网表文件,其中包含了电路的结构和元件之间的连接关系。

四、优化优化是在综合之后进行的一个步骤,它的目标是提高电路的性能和效率。

Modelsom会对综合得到的网表文件进行优化,去除一些冗余的逻辑和优化电路的延迟。

优化是一个复杂的过程,需要考虑到多个因素,如功耗、面积和时序等。

Modelsom提供了多种优化选项,可以根据设计需求进行调整。

五、仿真仿真是数字电路设计中的最后一个环节,通过对电路进行仿真,可以验证其功能和性能是否符合设计要求。

在Modelsom中,仿真分为逻辑仿真和时序仿真两种模式。

逻辑仿真主要验证电路的功能是否正确,时序仿真则验证电路的时序性能是否满足要求。

Modelsom提供了丰富的仿真工具和功能,可以对电路进行全面的测试和验证。

实验调试中出现的问题

一.Modelsim实验调试的问题1.编译过程中的问题1)新建工程后:如果这里选择是creat new file ,一定记得这里把这里的Add file as type 改为verilog因为这里默认是VHDL.2)如果是add existing file :要把所有的工程文件,包括仿真文件放在 project location 里面。

或者在下面的选项卡中:选择copy to project directory !!注意了:由于我们用的软件都是自己破解的,所有,有时候即便选择了 copy to project directory 有时候编译还是会出错,所有我们还是自己把工程文件,v 拷贝到我们的工程目录中吧。

2.仿真中出现的问题:当编译成功之后我们就可以进行仿真了1)在仿真的时候有些版本的modelsim 仿真出来的波形是直线原因是我们要注意把Optimization 中的enable optimization 的选项取消了:2)当我们编译成功之后在仿真的过程中,还会经常碰到这样的错误:“#Error loading design”解答:loading design的问题就是你对每个模块编译后的内容,也就是你在work库里出现的东西提示你加载设计错误,就是说明你加载的东西在work 库里没有,这的问题的原因有两个:(1)testbench 没有写好(2)在modelsim编译的时候相关的文件没有添加到modelsim中。

所以我们的对应的解决办法也有两个:A.虽然我们编译通过了,但是可能有些字符拼写错误。

B.我们可以关掉软件,再重新打开重新编译,重新仿真。

3)仿真时遇到如图所示的情况:不能看到全局时,可以通过工具栏里这两个符号进行调节,结果如图:上面问题虽然解决了,但是result结果却让人头疼,根本看不清是多少,此时,可以通过如下步骤把他修改成十进制数字,效果如下图所示:是不是可以看得很清楚了。

modelsim的详细使用方法

一、简介ModelSim是一款由美国Mentor Graphics公司推出的集成电路仿真软件,广泛应用于数字电路和系统设计领域。

它提供了强大的仿真和验证功能,能够帮助工程师快速高效地进行电路设计与验证工作。

本文将详细介绍ModelSim的使用方法,以帮助读者更好地掌握这一工具的操作技巧。

二、安装与配置1. 下载ModelSim安装包,并解压到指定目录2. 打开终端,进入ModelSim安装目录,执行安装命令3. 安装完成后,配置环境变量,以便在任何目录下都能够调用ModelSim程序4. 打开ModelSim,进行软件注册和授权,确保软件可以正常运行三、工程创建与管理1. 新建工程:在ModelSim主界面点击“File” -> “New” -> “Project”,输入工程名称和存储路径,选择工程类型和目标设备,点击“OK”完成工程创建2. 添加文件:在工程目录下右键点击“Add Existing”,选择要添加的源文件,点击“OK”完成文件添加3. 管理工程:在ModelSim中可以方便地对工程进行管理,包括文件的增删改查以及工程参数的设置等四、代码编写与编辑1. 在ModelSim中支持Verilog、VHDL等多种硬件描述语言的编写和编辑2. 在ModelSim主界面点击“File” -> “New” -> “File”,选择要新建的文件类型和存储位置,输入文件名称,点击“OK”完成文件创建3. 在编辑器中进行代码编写,支持代码高亮、自动缩进、语法检查等功能4. 保存代码并进行语法检查,确保代码符合规范,没有错误五、仿真与调试1. 编译工程:在ModelSim中进行代码编译,生成仿真所需的可执行文件2. 设置仿真参数:在“Simulation”菜单下选择“S tart Simulation”,设置仿真时钟周期、输入信号等参数3. 运行仿真:点击“Run”按钮,ModelSim将开始对设计进行仿真,同时显示波形图和仿真结果4. 调试设计:在仿真过程中,可以通过波形图和仿真控制面板对设计进行调试,查找并解决可能存在的逻辑错误六、波形查看与分析1. 查看波形:在仿真过程中,ModelSim会生成相应的波形文件,用户可以通过“Wave”菜单查看波形并进行波形分析2. 波形操作:支持波形的放大、缩小、平移、选中等操作,方便用户对波形进行分析和观察3. 波形保存:用户可以将波形结果保存为图片或文本文件,以便日后查阅和分析七、性能优化与验证1. 时序优化:在设计仿真过程中,可以通过观察波形和性能分析结果,对设计进行优化,提高设计的时序性能2. 逻辑验证:通过对仿真的结果进行逻辑验证,确保设计符合预期的逻辑功能3. 时序验证:对设计的时序性能进行验证,确保信号传输和时钟同步的正确性八、项目输出与文档整理1. 输出结果:在仿真和验证完成后,可以将仿真结果、波形图和性能分析结果输出为文本文件或图片,方便后续的文档整理和报告撰写2. 结果分析:对仿真结果和验证结果进行详细的分析,确定设计的性能和功能是否符合设计要求3. 文档整理:根据仿真和验证结果,进行文档整理和报告撰写,为后续的设计和优化工作提供参考九、总结与展望ModelSim作为一款专业的集成电路仿真软件,具有着强大的功能和丰富的特性,可以帮助工程师进行电路设计与验证工作。

MODESLsim仿真使用说明

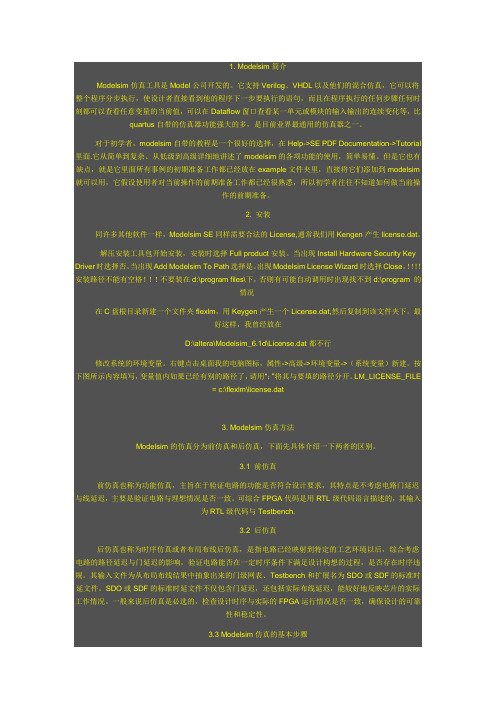

1. Modelsim简介Modelsim仿真工具是Model公司开发的。

它支持Verilog、VHDL以及他们的混合仿真,它可以将整个程序分步执行,使设计者直接看到他的程序下一步要执行的语句,而且在程序执行的任何步骤任何时刻都可以查看任意变量的当前值,可以在Dataflow窗口查看某一单元或模块的输入输出的连续变化等,比quartus自带的仿真器功能强大的多,是目前业界最通用的仿真器之一。

对于初学者,modelsim自带的教程是一个很好的选择,在Help->SE PDF Documentation->Tutorial 里面.它从简单到复杂、从低级到高级详细地讲述了modelsim的各项功能的使用,简单易懂。

但是它也有缺点,就是它里面所有事例的初期准备工作都已经放在example文件夹里,直接将它们添加到modelsim 就可以用,它假设使用者对当前操作的前期准备工作都已经很熟悉,所以初学者往往不知道如何做当前操作的前期准备。

2. 安装同许多其他软件一样,Modelsim SE同样需要合法的License,通常我们用Kengen产生license.dat。

解压安装工具包开始安装,安装时选择Full product安装。

当出现Install Hardware Security Key Driver时选择否。

当出现Add Modelsim To Path选择是。

出现Modelsim License Wizard时选择Close。

!!!!安装路径不能有空格!!!不要装在d:\program files\下,否则有可能自动调用时出现找不到d:\program 的情况在C盘根目录新建一个文件夹flexlm,用Keygen产生一个License.dat,然后复制到该文件夹下。

最好这样,我曾经放在D:\altera\Modelsim_6.1d\License.dat都不行修改系统的环境变量。

右键点击桌面我的电脑图标,属性->高级->环境变量->(系统变量)新建。

modelsim 错误及解决方法

modelsim 错误及解决方法modelsim错误及解决方法这几天学习了下modelsim6.5se,做些总结以便复习。

不一定正确,请浏览者不吝纠正指教。

软件:modelsim6.5se代码来源:王金明:《veriloghdl程序设计教程》1、文件夹adder4中,adder_tb.v的$monitor($time,,,\+%d+%b={%b,%d}\没有现象,出现警告:warning:(vsim-pli-3003)e:/modelsim65se/wangjinming/adder4/adder_tb.v(30):[tofd]-systemtaskorfunction'$minitor'isnotdefined.2、调用顶层文件的例化语句出现错误:adder4adder(.cout(cout),.sum(sum),.a(ina),.b(inb),.cin(cin));错误原因:没分清调用和被调用模块的端口放置位置,正确的写法如下:adder4adder(.cout(cout),.sum(sum),.ina(a),.inb(b),.cin(cin));3、在搞counter4的时候,刚开始没有信号,例如图:原来以为是sourceinsight的问题,删掉sourceinsight的文件只保留counter4.v 和counter4_tb.v之后,仍然是这个问题。

经排查是因为在点击startsimulation后没有去掉enableoptimization。

废止方法:回去点红圈处的钩。

或者如下图,右击必须仿真的文件,选上simulaitonwithoutoptimization.改正之后,objects中出现了信号:2021.7.44、辨认出了initial$monitor($time,,,\reset=%dout=%d\的作用,仿真运行后,在transcript中显示:0clk=0reset=0out=x#50clk=1reset=0out=x#100clk=0reset=1out=x#150clk=1reset=1out=0#200clk=0reset=0out=0#250clk=1reset=0out=1#300clk=0reset=0out=1#350clk=1reset=0out=2#400clk=0r eset=0out=2#450clk=1reset=0out=3#500clk=0reset=0out=35、在做好一个工程后,想要对另一个文件夹内的文件进行仿真,必须选择changedirectory。

modelsim使用常见问题及解决办法集锦③

modelsim使⽤常见问题及解决办法集锦③四、You selected Modelsim-Altera as Simulation Software in EDA ToolSettings,however……You selected ModelSim-Altera as Simulation Software in EDA Tool Settings,however NativeLink found ModelSim in the pata – correct path or change EDA Tool Settings and try again.问题原因该⼯程设置的仿真⼯具名称与在Quartus II软件中指定的该软件路径不匹配。

例如,本来设置的仿真⼯具是modelsim–altera,结果在Quartus II软件的modelsim-altera路径下设定的是Tools下设置的是modelsim-se的路径,导致软件版本不匹配⽽报错。

设置的仿真⼯具为modelsim-alteraModelsim-altera路径却指向了modelsim-se版本。

解决⽅法1、如果你电脑装的是modelsim-se版本,请按照如下图所⽰的设置进⾏⼯程和⼯具路径设置:2、如果你的电脑装的是modelsim-altera版本,请按照如下图所⽰的设置进⾏⼯程和⼯具路径设置:五、Unable to checkout a license问题原因使⽤了⾮免费版本的Modelsim软件,却没有获得软件使⽤许可证解决⽅法⽅法1:使⽤免费版本的modelsim软件,如modelsim altera stater edition。

⽅法2:购买软件许可证。

⽅法3:破解modelsim软件,破解⽅法见如下链接(altera收费版和se版本破解思路相同,破解⼯具通⽤):modelsim-win64-10.1c 下载、安装、破解全攻略(出处: 中国电⼦技术论坛)获得许可后最好重启Quartus II软件六、Error loading design问题原因提⽰信息中提⽰没有Verilog的仿真许可证,表明是没有获得软件使⽤许可。

如何用ModelsimSE仿真IP核-以PLL为例

如何⽤ModelsimSE仿真IP核-以PLL为例我们之前介绍了如何使⽤Modelsim SE进⾏仿真和利⽤do⽂件的仿真⽅法,但是其中待仿真的模块是我们⾃⼰编写的Verilog模块,但是在实际⼯作中,我们的设计中会经常⽤到FPGA ⼚商给我们提供的现成模块—IP核,这些模块我们看到不到源代码,只知道IP核的端⼝信息,当我们要仿真的时候,同样要向Modelsim提供这些IP核的信息,⽽FPGA⼚商也会给我们提供相应的IP核的编译库⽂件,我们如果设计中包含这些IP核,就必须在仿真之前,将这些库⽂件编译到Moldelsim 的库中去。

其实IP核只是我们要添加的其中⼀种库(MegaFunction),除此之外,我们还需要添加lpm库(设计中如果调⽤了lpm原件,需要添加此库),还有原语库(primitive),器件库(我们⽤的是cyclone),当然同⼀种库,还会分Verilog版和VHDL版。

这⾥只介绍Verilog版相关库⽂件的添加,VHDL版的,⽅法类似,⼤家只需更换相应的VHDL编译⽂件即可。

1.1.1.建⽴仿真库我们将IP核等相关库⽂件编译到Modelsim中后,以后凡是设计中调⽤到IP核时,我们就不⽤再重复添加了。

我们看⼀下如何在Modelsim中查看我们已经编译好的库,打开modelsim,如下图,会默认弹出名为library的窗⼝,窗⼝中的内容就有我们已经添加的库,⼀部分是Modelsim⾃带的库。

下⾯我们开始准备添加相关库⽂件。

第⼀步,⾸先在新建⼀个⽂件夹,⽤来存放我们编译后的库⽂件,这⾥命名为altera_lib,我们这⾥存放到了“C:\modeltech64_10.2c\”路径下,然后在altera_lib下新建四个⽂件夹lpm、altera_mf、altera_primitive、cyclone,如下图,后⾯我们会建⽴四个对应且相同名称的库。

第⼆步,建⽴库,我们以添加IP核库⽂件(altera_mf)为例进⾏介绍。

modelsim错误及解决方法

以下操作在ModelSim SE PLUS 6.2b中完成1.新建一个工程file -> new -> project... 此时会弹出一个Creat Project对话框,输入一个工程名,选择保存路径(不要包含中文),其他默认就行了;2.点OK后会弹出一个Add items to the Project,里面有几个可选项,应该很容易明白;3.添加好文件后,点close把Add items to the Project对话框关闭,这时在左侧的workspace的project窗口里可以看到刚才添加的文件,双击可以打开这些文件进行编辑,编辑好后保存;4.右击刚才编辑好的文件compile -> compile select(或根据自己需要选其他项),如果没有错误,则在底部的命令窗口可以看到编译成功的消息(呈绿色),否则会出现出错的消息(呈红色),双击它会弹出一个更具体的窗口提示你出错的地方.5.修改所有错误直到编译成功.这时可以在菜单栏选择Simulation -> Start simulatio... 这时会弹出一个Start simulatio的对话框,在Design的标签下你会看到有很多库,展开work库会看到刚才编译成功的文件(如果有多个文件的话选择一个你想仿真的,比如测试程序,这时底部的OK会由刚才的不可用变成可用的),然后把Opitimization选项下的Enable opitimization前复选取消(这样可以保证过会儿所有的输入输出都可以看到,你可以试试不取消这项有何区别),然后点OK就行了.6.选择view -> Objects就可以看到你想仿真的各个量,选中它们并右击Add to wave -> Selected signals,这时就会弹出一个波形仿真窗口.如果你的测试文件写得没问题的话就可以看到仿真波形,你也可以观察底部的命令窗口察看相关信息.7.如果没写测试文件的话,在波形仿真窗口右击相关信号,选择force...设置想仿真的值或clock...把该量设置为时钟,然后点工具栏上的Run或Simulation菜单下的Run。

modelsim仿真ip核总结报告

说明:如果modelsim要能够仿真ise中的ip核,则首先需要将ip核的描述文件编译到指定的库中,下面就具体步骤进行说明。

1.首先你可以打开modelsim,选择File->Change Diriectory查看你当前的路径,也可以修改路径。

2.在moselsim的wordspace窗口中右击选择new-library,选择create-a new library。

输入library name(如xilinx_lib),其他默认即可,如下图:点击ok确认,那么在你的diriectory路径的目标文件夹下回出现文件夹xilinx_lib,里面有个文件_info.3.选择moselsim-compile-compile。

这里的library选择我们建的library(即xilinx_lib),查找范围找到ip核文件的描述文件所在文件夹($Xilinx->verilog->src 下有三个库“simprims”,“unisims”和“xilinxcorelib”),选中这些ip核描述文件,点击compile。

如下图至此ise中的ip核已加载到modelsim的库中,这里说明一下,并非所有编译的库文件我们都用到,但是都编译了放在那是没有关系的。

4.接下来用ise生成一个ip核,把它的行为级(如fifo.v或.vhdl)描述文件(或者称ip核调用文件)放到diriectory路径的目标文件夹下,在diriectory路径的目标文件夹下新建一个工程,不过注意,新建的工程library必须选择xilinx_lib,即我们所新建的那个library,因为这个library里才有ip核描述文件compile的结果。

5.编写testbench(可以用ise生成,这样很快,当然自己写也可以),编译fifo.v和test.v,之后选择编译后的test,在添加波形即可。

Modelsim仿真PLL遇到的问题

Modelsim仿真PLL遇到的问题Modelsim仿真PLL遇到的问题今天在用Modelsim做一个后仿真的时候,发现PLL的没有输出,在设定不同的测试时钟频率的时候,出现一下三种情况:(1)当输入时钟周期小于在例化PLL时选择的输入时钟周期时,在运行仿真时,会出现以下警告信息:Warning : Input clock freq. is under VCO range. Cyclone III PLL may lose lock(2)当输入时钟周期大于在例化PLL时选择的输入时钟周期时,在运行仿真时,会出现以下警告信息:Warning : Input clock freq. is over VCO range. Cyclone III PLL may lose lock这上面这两种情况下,PLL都不会正常工作。

如果出现上面第一种情况,可以将输入测试时钟的周期设置大一些。

如果出现第二种情况,可以将输入测试时钟的周期设置小一些。

(3)当输入时钟周期等于在例化PLL时选择的输入时钟周期时,在运行仿真时,会出现以下信息:Note : Cyclone III PLL locked to incoming clock这有这种情况下PLL才能正常工作根据以上这三种情况,我判断应该是在编译后生成的.vo文件中,包含了PLL的设置信息,如PLL的输入频率。

但是我也发现比较困惑的一点就是输入测试时钟的频率和例化PLL时设置的输入时钟频率也不一定非要相等,PLL才能工作。

不知道这是什么原因。

但是也并不是只要将测试时钟的频率设定为与PLL的输入时钟完全相同时就一定可以正常工作,例如我例化的PLL 的输入时钟频率为400MHz(从器件手册上看,Cyclone III 的PLL输入是支持这么高的频率的),在测试时我把输入测试时钟的频率设置为2.5ns,但是PLL没有输出。

当我改为5ns的时候就有输出了。

另外,在进行前仿真是,也发现了同样的问题,即如果PLL的输入时钟频率不合适那么PLL将不能够工作,只不过在PLL不能正常工作的时候,Modelsim没有任何提醒,只有在正常工作时,才出现Note : Cyclone III PLL locked to incoming clock。

Modelsim使用常见问题及解决办法

Modelsim使用常见问题及解决办法在ISE启动modelsim时遇到问题1。

我在ISE中启动modelsim时出现了下面的错误Loading work.tb_ic1_func# ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".# No such file or directory. (errno = ENOENT)# ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver". # No such file or directory. (errno = ENOENT)# Loading work.fifoctlr_ic_v2# ** Error: (vsim-19) Failed to access library 'xilinxcorelib_ver' at "xilinxcorelib_ver".# No such file or directory. (errno = ENOENT)# ** Error: (vsim-19) Failed to access library 'unisims_ver' at "unisims_ver". # No such file or directory. (errno = ENOENT)# ** Error: (vsim-3033) fifoctlr_ic_v2.v(126): Instantiation of 'BUFGP' failed. The design unit was not found.是什么原因?“点到仿真模式,在source里面选中你建立工程选择的芯片,然后看Processes,点开,有个compile HDL simulation library,运行一下就OK了”2.ISE用modelsim仿真提示:# ** Error: (vish-4014) No objects found matching '*'.结果仿真时老是报错:# ** Error: (vish-4014) No objects found matching '*'.# Error in macro ./test_top_tb.fdo line 10# (vish-4014) No objects found matching '*'.# while executing# "add wave *"解决办法,改modelsim.ini文件中的一个参数:VoptFlow = 0# ** Error: (vish-4014) No objects found matching 'XXXX'.在之前的设计里有一个信号XX, 并且保持在wave.do文件里现在这个信号在你的设计你被去掉了,modelsim仍然调用旧的wave.do,找不到对应的信号XX,就报错误这个错误可以忽略3.当对IP核修改后,用Modelsim仿真显示:No entity is bound for inst 或CE is not in the entity。

重要】详细介绍使用modelsim对lpm作仿真的步骤操作

如何使用ModelSim對Megafunction或LPM作仿真? (SOC) (MegaCore) (ModelSim)Abstract在FPGA開發中,常會用到Altera所提供的Megafunction與LPM加速開發,這要如何使用ModelSim作仿真呢?Introduction使用環境:Quartus II 8.1 + ModelSim-Altera 6.3g_p1 + ModelSim SE 6.3e在(筆記) 如何使用ModelSim作前仿真與後仿真? (SOC) (Quartus II) (ModelSim)中,提到如何使用ModelSim對Verilog作仿真,包含前仿真與後仿真,若使用了Altera的Megafunction 與LPM,則仿真的方法稍有不同,本文分別使用ModelSim-Altera與ModelSim SE,並對Megafunction:dcfifo作仿真。

my_dcfifo.v / Verilog使用MegaWizard產生的dcfifo。

1// megafunction wizard: %FIFO%2// GENERATION: STANDARD3// VERSION: WM1.04// MODULE: dcfifo56// ============================================================7// File Name: my_dcfifo.v8// Megafunction Name(s):9// dcfifo10//11// Simulation Library Files(s):12// altera_mf13// ============================================================ 14// ************************************************************ 15// THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!16//17// 8.1 Build 163 10/28/2008 SJ Full Version18// ************************************************************ 192021//Copyright (C) 1991-2008 Altera Corporation22//Your use of Altera Corporation's design tools, logic functions 23//and other software and tools, and its AMPP partner logic24//functions, and any output files from any of the foregoing25//(including device programming or simulation files), and any26//associated documentation or information are expressly subject 27//to the terms and conditions of the Altera Program License28//Subscription Agreement, Altera MegaCore Function License29//Agreement, or other applicable license agreement, including, 30//without limitation, that your use is for the sole purpose of31//programming logic devices manufactured by Altera and sold by 32//Altera or its authorized distributors. Please refer to the33//applicable agreement for further details.343536// synopsys translate_off37 `timescale 1 ps / 1 ps38// synopsys translate_on39module my_dcfifo (40 aclr,41 data,42 rdclk,43 rdreq,44 wrclk,45 wrreq,46 q,47 rdempty,48 rdusedw,49 wrfull);5051input aclr;52input [7:0] data;53input rdclk;54input rdreq;55input wrclk;56input wrreq;57output [7:0] q;58output rdempty;59output [4:0] rdusedw; 60output wrfull;6162wire sub_wire0;63wire sub_wire1;64wire [7:0] sub_wire2;65wire [4:0] sub_wire3;66wire rdempty = sub_wire0;67wire wrfull = sub_wire1;68wire [7:0] q = sub_wire2[7:0];69wire [4:0] rdusedw = sub_wire3[4:0];7071 dcfifo dcfifo_component (72 .wrclk (wrclk),73 .rdreq (rdreq),74 .aclr (aclr),75 .rdclk (rdclk),76 .wrreq (wrreq),77 .data (data),78 .rdempty (sub_wire0),79 .wrfull (sub_wire1),80 .q (sub_wire2),81 .rdusedw (sub_wire3)82// synopsys translate_off83 ,84 .rdfull (),85 .wrempty (),86 .wrusedw ()87// synopsys translate_on88 );89defparam90 dcfifo_component.intended_device_family = "Cyclone II",91 dcfifo_component.lpm_hint = "MAXIMIZE_SPEED=5,",92 dcfifo_component.lpm_numwords = 32,93 dcfifo_component.lpm_showahead = "OFF",94 dcfifo_component.lpm_type = "dcfifo",95 dcfifo_component.lpm_width = 8,96 dcfifo_component.lpm_widthu = 5,97 dcfifo_component.overflow_checking = "ON",98 dcfifo_component.rdsync_delaypipe = 4,99 dcfifo_component.underflow_checking = "ON",100 dcfifo_e_eab = "ON",101 dcfifo_component.write_aclr_synch = "OFF",102 dcfifo_component.wrsync_delaypipe = 4;103104105endmodule106107// ============================================================ 108// CNX file retrieval info109// ============================================================ 110// Retrieval info: PRIVATE: AlmostEmpty NUMERIC "0"111// Retrieval info: PRIVATE: AlmostEmptyThr NUMERIC "-1"112// Retrieval info: PRIVATE: AlmostFull NUMERIC "0"113// Retrieval info: PRIVATE: AlmostFullThr NUMERIC "-1"114// Retrieval info: PRIVATE: CLOCKS_ARE_SYNCHRONIZED NUMERIC "0"115// Retrieval info: PRIVATE: Clock NUMERIC "4"116// Retrieval info: PRIVATE: Depth NUMERIC "32"117// Retrieval info: PRIVATE: Empty NUMERIC "1"118// Retrieval info: PRIVATE: Full NUMERIC "1"119// Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone I I"120// Retrieval info: PRIVATE: LE_BasedFIFO NUMERIC "0"121// Retrieval info: PRIVATE: LegacyRREQ NUMERIC "1"122// Retrieval info: PRIVATE: MAX_DEPTH_BY_9 NUMERIC "0"123// Retrieval info: PRIVATE: OVERFLOW_CHECKING NUMERIC "0"124// Retrieval info: PRIVATE: Optimize NUMERIC "2"125// Retrieval info: PRIVATE: RAM_BLOCK_TYPE NUMERIC "0"126// Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0" 127// Retrieval info: PRIVATE: UNDERFLOW_CHECKING NUMERIC "0"128// Retrieval info: PRIVATE: UsedW NUMERIC "1"129// Retrieval info: PRIVATE: Width NUMERIC "8"130// Retrieval info: PRIVATE: dc_aclr NUMERIC "1"131// Retrieval info: PRIVATE: diff_widths NUMERIC "0"132// Retrieval info: PRIVATE: msb_usedw NUMERIC "0"133// Retrieval info: PRIVATE: output_width NUMERIC "8"134// Retrieval info: PRIVATE: rsEmpty NUMERIC "1"135// Retrieval info: PRIVATE: rsFull NUMERIC "0"136// Retrieval info: PRIVATE: rsUsedW NUMERIC "1"137// Retrieval info: PRIVATE: sc_aclr NUMERIC "0"138// Retrieval info: PRIVATE: sc_sclr NUMERIC "0"139// Retrieval info: PRIVATE: wsEmpty NUMERIC "0"140// Retrieval info: PRIVATE: wsFull NUMERIC "1"141// Retrieval info: PRIVATE: wsUsedW NUMERIC "0"142// Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone II"143// Retrieval info: CONSTANT: LPM_HINT STRING "MAXIMIZE_SPEED=5," 144// Retrieval info: CONSTANT: LPM_NUMWORDS NUMERIC "32"145// Retrieval info: CONSTANT: LPM_SHOWAHEAD STRING "OFF"146// Retrieval info: CONSTANT: LPM_TYPE STRING "dcfifo"147// Retrieval info: CONSTANT: LPM_WIDTH NUMERIC "8"148// Retrieval info: CONSTANT: LPM_WIDTHU NUMERIC "5"149// Retrieval info: CONSTANT: OVERFLOW_CHECKING STRING "ON"150// Retrieval info: CONSTANT: RDSYNC_DELAYPIPE NUMERIC "4"151// Retrieval info: CONSTANT: UNDERFLOW_CHECKING STRING "ON"152// Retrieval info: CONSTANT: USE_EAB STRING "ON"153// Retrieval info: CONSTANT: WRITE_ACLR_SYNCH STRING "OFF"154// Retrieval info: CONSTANT: WRSYNC_DELAYPIPE NUMERIC "4"155// Retrieval info: USED_PORT: aclr 0 0 0 0 INPUT GND aclr156// Retrieval info: USED_PORT: data 0 0 8 0 INPUT NODEFVAL data[7..0] 157// Retrieval info: USED_PORT: q 0 0 8 0 OUTPUT NODEFVAL q[7..0]158// Retrieval info: USED_PORT: rdclk 0 0 0 0 INPUT NODEFVAL rdclk159// Retrieval info: USED_PORT: rdempty 0 0 0 0 OUTPUT NODEFVAL rdempty 160// Retrieval info: USED_PORT: rdreq 0 0 0 0 INPUT NODEFVAL rdreq161// Retrieval info: USED_PORT: rdusedw 0 0 5 0 OUTPUT NODEFVAL rdusedw [4..0]162// Retrieval info: USED_PORT: wrclk 0 0 0 0 INPUT NODEFVAL wrclk163// Retrieval info: USED_PORT: wrfull 0 0 0 0 OUTPUT NODEFVAL wrfull 164// Retrieval info: USED_PORT: wrreq 0 0 0 0 INPUT NODEFVAL wrreq165// Retrieval info: CONNECT: @data 0 0 8 0 data 0 0 8 0166// Retrieval info: CONNECT: q 0 0 8 0 @q 0 0 8 0167// Retrieval info: CONNECT: @wrreq 0 0 0 0 wrreq 0 0 0 0168// Retrieval info: CONNECT: @rdreq 0 0 0 0 rdreq 0 0 0 0169// Retrieval info: CONNECT: @rdclk 0 0 0 0 rdclk 0 0 0 0170// Retrieval info: CONNECT: @wrclk 0 0 0 0 wrclk 0 0 0 0171// Retrieval info: CONNECT: rdempty 0 0 0 0 @rdempty 0 0 0 0172// Retrieval info: CONNECT: rdusedw 0 0 5 0 @rdusedw 0 0 5 0173// Retrieval info: CONNECT: wrfull 0 0 0 0 @wrfull 0 0 0 0174// Retrieval info: CONNECT: @aclr 0 0 0 0 aclr 0 0 0 0175// Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components. all176// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.v TRUE177// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.inc FALSE178// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo p FALSE179// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.bsf FALSE180// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_inst.v FALSE181// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_bb.v TRUE182// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_waveforms.html TR UE183// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_wave*.jpg TRUE184// Retrieval info: LIB_FILE: altera_mfmy_dcfifo_tb.v / Verilogdcfifo的testbench。

ModelSim常见错误原因及解决

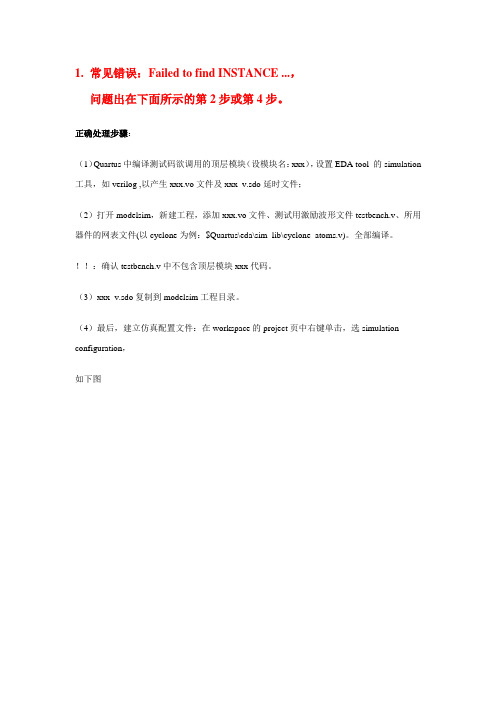

1.常见错误:Failed to find INSTANCE ...,问题出在下面所示的第2步或第4步。

正确处理步骤:(1)Quartus中编译测试码欲调用的顶层模块(设模块名:xxx),设置EDA tool 的simulation 工具,如verilog ,以产生xxx.vo文件及xxx_v.sdo延时文件;(2)打开modelsim,新建工程,添加xxx.vo文件、测试用激励波形文件testbench.v、所用器件的网表文件(以cyclone为例:$Quartus\eda\sim_lib\cyclone_atoms.v)。

全部编译。

!!:确认testbench.v中不包含顶层模块xxx代码。

(3)xxx_v.sdo复制到modelsim工程目录。

(4)最后,建立仿真配置文件:在workspace的project页中右键单击,选simulation configuration,如下图于是,workspace中得到simulation 1。

按下图设置:注意,上面的框中添加xxx_v.sdo,下面的文本框中设置作用域,格式为:\testbench模块名\xxx的实例名。

(5)`timescale 影响仿真结果显示效果。

=================例===================[1]//文件count4.vmodule count4(out,reset,clk);output[3:0] out;input reset, clk;reg[3:0] out;always @(posedge clk)beginif (reset)out <= 0;elseout <= out + 1;endendmodule[2]//测试文件count_tp.v`timescale 1ns/1nsmodule count_tp;reg clk,reset;wire[3:0] out;parameter DELY = 100;count4 mycount(out,reset,clk);always #(DELY/2) clk = ~clk;initialbeginclk = 0; reset = 0;#DELY reset = 1;#DELY reset = 0;#(DELY*20) $finish;endinitial $monitor($time,,,"clk=%d reset=%d out=%d",clk,reset,out); endmodule[3]所用器件:cyclone[4]结果:明显产生了时延p.s.-----------------------网上有朋友指出勾选SDF中的两个选项,将原来的警告禁止,将原来的错误变为警告, 可以成功地进行反标注并运行仿真,但这样做并没有解决实际问题,只能产生功能仿真,没有得到带时延的时序仿真2.** Error: D:/ModelSim_6.5/ModelSimnear "'t": Illegal base specifier in numeric constant.syntax error, unexpected "BASE", expecting "class"错误原因:不是’timescale 而是`timescale,那个是键盘左上角的点,不是一撇。

使用Modelsim仿真FPGA工程步骤以及一些问题

使用Modelsim仿真Altera FPGA工程(包括IP核)步骤以及问题汇总前提:计算机上已经安装QuartusII和Modelsim通用版,并且均已破解。

环境说明:所用的软件版本,QuartusII为9.0,Modelsim为6.5c。

本测试仅在WIN XP SP3上测试,对于VISTA/WIN7/LIN或者其他平台没做过测试。

但其他平台或者其他版本的过程应该都差不多。

其他:感谢teamo版主的破解和编译教程,以及后期对我的热心指导。

如果各位对整个步骤还有什么问题的华可以直接和我联系,我的论坛ID是lanphon,邮箱是lanphon@。

一、Altera库的编译(本部分基本上全部抄袭teamo版主的教程,懒得写了)1) 先到C:\modeltech_6.5目录下找到文件"modelsim.ini",将其属性改为可写(右键‐>属性)。

2) 启动modelsim se,选择【file】‐>【new】‐>【library】命令,在弹出的【create a newlibrary】窗口中将选项【create】设置为【a new library and a logical mapping to it】,在【libryr name】和【library library】窗口中将选项【create】设置为【a new library and a logical mapping to it】,在【libryr name】和【library physical name】中键入所要创建库名字,如Altera ,此时在主窗口中已多了一个Altera 项。

注:这个过程实质上想当于在modelsim 主窗口中的脚本区域中输入了vlib和vmap命令。

3) 在workspace中的library中选中你健入的库名Altera,在主菜单中选【compile】→【compile…】命令。

modelsim编译库步骤-详细

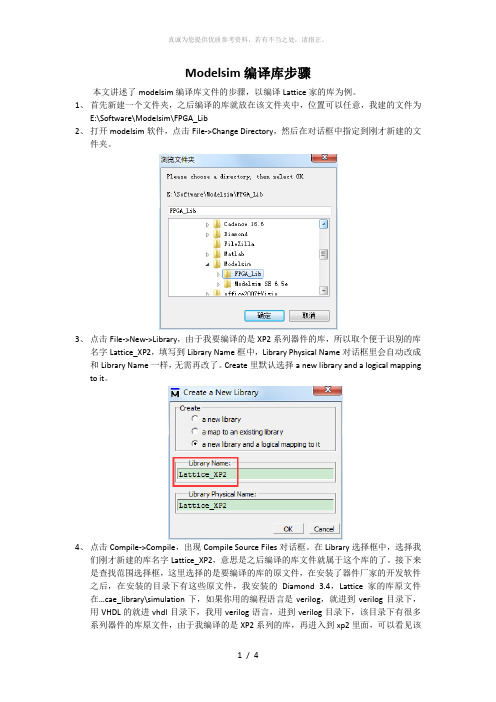

Modelsim编译库步骤本文讲述了modelsim编译库文件的步骤,以编译Lattice家的库为例。

1、首先新建一个文件夹,之后编译的库就放在该文件夹中,位置可以任意,我建的文件为E:\Software\Modelsim\FPGA_Lib2、打开modelsim软件,点击File->Change Directory,然后在对话框中指定到刚才新建的文件夹。

3、点击File->New->Library,由于我要编译的是XP2系列器件的库,所以取个便于识别的库名字Lattice_XP2,填写到Library Name框中,Library Physical Name对话框里会自动改成和Library Name一样,无需再改了。

Create里默认选择a new library and a logical mapping to it。

4、点击Compile->Compile,出现Compile Source Files对话框。

在Library选择框中,选择我们刚才新建的库名字Lattice_XP2,意思是之后编译的库文件就属于这个库的了。

接下来是查找范围选择框,这里选择的是要编译的库的原文件,在安装了器件厂家的开发软件之后,在安装的目录下有这些原文件,我安装的Diamond 3.4,Lattice家的库原文件在…cae_library\simulation下,如果你用的编程语言是verilog,就进到verilog目录下,用VHDL的就进vhdl目录下,我用verilog语言,进到verilog目录下,该目录下有很多系列器件的库原文件,由于我编译的是XP2系列的库,再进入到xp2里面,可以看见该目录下有很多的.v文件,随便点击一个.v文件,然后Ctrl+A把所有.v文件选上,点击Compile就开始编译了。

.v文件比较多的话时间会稍微比较长,编译结束后,在Compile Source Files对话框点击Done就OK了。

(原创)在ModelSim里仿真Altera的lpm_rom文件的实践 (已经阅读)

在前面转载的《在ModelSim里仿真Altera的lpm_rom文件》一文广泛流传于网络。

经过本人最近时间的实践,对其中一些不正确或者说已经落伍了的地方进行修正。

1. 在QuartusII中生成rom的初始化文件,可以是hex,也可以是mif。

MIF 文件的格式很简单明了,所以我一向都是用MIF。

2.下载convert_hex2ver.dll文件,convert_hex2ver.dll就是把hex文件转换成ModelSim 能认出来的ver文件的动态链接库文件。

新版本的QuartusII中已经不带此文件了。

需要在网上找一份。

(老版本的软件里带了此文件(路径:quartusXX/eda/mentor/modelsim/),应当可以用。

)

3.将convert_hex2ver.dll文件放在modelsim安装路径的win32目录下;

4. 在ModelSim安装的目录下找到 modelsim.ini文件,将其只读属性去掉,在“; List of dynamically loaded objects for Verilog PLI applications,”后填入一行“Veriuser = convert_hex2ver.dll”。

保存文件,将只读属性改回来。

Over!祝你好运!

补丁:看到楼下网友留言不能仿真ROM,在这里再增加一条

5.需要将MIF文件复制到ModelSim仿真工程的文件夹下!你运行一次编译和仿真后,会看到自动生成的.ver文件,该文件名同你的MIF文件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Abstract在FPGA開發中,常會用到Altera所提供的Megafunction與LPM加速開發,這要如何使用ModelSim作仿真呢? Introduction使用環境:Quartus II 8.1 + ModelSim-Altera 6.3g_p1 + ModelSim SE 6.3e在(筆記) 如何使用ModelSim作前仿真與後仿真? (SOC) (Quartus II) (ModelSim)中,提到如何使用ModelSim 對Verilog作仿真,包含前仿真與後仿真,若使用了Altera的Megafunction與LPM,則仿真的方法稍有不同,本文分別使用ModelSim-Altera與ModelSim SE,並對Megafunction:dcfifo作仿真。

my_dcfifo.v / Verilog使用MegaWizard產生的dcfifo。

1// megafunction wizard: %FIFO%2// GENERATION: STANDARD3// VERSION: WM1.04// MODULE: dcfifo56// ============================================================7// File Name: my_dcfifo.v8// Megafunction Name(s):9// dcfifo10//11// Simulation Library Files(s):12// altera_mf13// ============================================================14// ************************************************************15// THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE!16//17// 8.1 Build 163 10/28/2008 SJ Full Version18// ************************************************************192021//Copyright (C) 1991-2008 Altera Corporation22//Your use of Altera Corporation's design tools, logic functions23//and other software and tools, and its AMPP partner logic24//functions, and any output files from any of the foregoing25//(including device programming or simulation files), and any26//associated documentation or information are expressly subject27//to the terms and conditions of the Altera Program License28//Subscription Agreement, Altera MegaCore Function License29//Agreement, or other applicable license agreement, including,30//without limitation, that your use is for the sole purpose of31//programming logic devices manufactured by Altera and sold by32//Altera or its authorized distributors. Please refer to the33//applicable agreement for further details.343536// synopsys translate_off37 `timescale 1 ps / 1 ps38// synopsys translate_on39module my_dcfifo (40 aclr,41 data,42 rdclk,43 rdreq,44 wrclk,45 wrreq,46 q,47 rdempty,48 rdusedw,49 wrfull);5051input aclr;52input [7:0] data;53input rdclk;54input rdreq;55input wrclk;56input wrreq;57output [7:0] q;58output rdempty;59output [4:0] rdusedw;60output wrfull;6162wire sub_wire0;63wire sub_wire1;64wire [7:0] sub_wire2;65wire [4:0] sub_wire3;66wire rdempty = sub_wire0;67wire wrfull = sub_wire1;68wire [7:0] q = sub_wire2[7:0];69wire [4:0] rdusedw = sub_wire3[4:0]; 7071 dcfifo dcfifo_component (72 .wrclk (wrclk),73 .rdreq (rdreq),74 .aclr (aclr),75 .rdclk (rdclk),76 .wrreq (wrreq),77 .data (data),78 .rdempty (sub_wire0),79 .wrfull (sub_wire1),80 .q (sub_wire2),81 .rdusedw (sub_wire3)82// synopsys translate_off83 ,84 .rdfull (),85 .wrempty (),86 .wrusedw ()87// synopsys translate_on88 );89defparam90 dcfifo_component.intended_device_family = "Cyclone II",91 dcfifo_component.lpm_hint = "MAXIMIZE_SPEED=5,",92 dcfifo_component.lpm_numwords = 32,93 dcfifo_component.lpm_showahead = "OFF",94 dcfifo_component.lpm_type = "dcfifo",95 dcfifo_component.lpm_width = 8,96 dcfifo_component.lpm_widthu = 5,97 dcfifo_component.overflow_checking = "ON",98 dcfifo_component.rdsync_delaypipe = 4,99 dcfifo_component.underflow_checking = "ON",100 dcfifo_e_eab = "ON",101 dcfifo_component.write_aclr_synch = "OFF",102 dcfifo_component.wrsync_delaypipe = 4;103104105endmodule106107// ============================================================108// CNX file retrieval info109// ============================================================110// Retrieval info: PRIVATE: AlmostEmpty NUMERIC "0"111// Retrieval info: PRIVATE: AlmostEmptyThr NUMERIC "-1"112// Retrieval info: PRIVATE: AlmostFull NUMERIC "0"113// Retrieval info: PRIVATE: AlmostFullThr NUMERIC "-1"114// Retrieval info: PRIVATE: CLOCKS_ARE_SYNCHRONIZED NUMERIC "0"115// Retrieval info: PRIVATE: Clock NUMERIC "4"116// Retrieval info: PRIVATE: Depth NUMERIC "32"117// Retrieval info: PRIVATE: Empty NUMERIC "1"118// Retrieval info: PRIVATE: Full NUMERIC "1"119// Retrieval info: PRIVATE: INTENDED_DEVICE_FAMILY STRING "Cyclone II" 120// Retrieval info: PRIVATE: LE_BasedFIFO NUMERIC "0"121// Retrieval info: PRIVATE: LegacyRREQ NUMERIC "1"122// Retrieval info: PRIVATE: MAX_DEPTH_BY_9 NUMERIC "0"123// Retrieval info: PRIVATE: OVERFLOW_CHECKING NUMERIC "0"124// Retrieval info: PRIVATE: Optimize NUMERIC "2"125// Retrieval info: PRIVATE: RAM_BLOCK_TYPE NUMERIC "0"126// Retrieval info: PRIVATE: SYNTH_WRAPPER_GEN_POSTFIX STRING "0"127// Retrieval info: PRIVATE: UNDERFLOW_CHECKING NUMERIC "0"128// Retrieval info: PRIVATE: UsedW NUMERIC "1"129// Retrieval info: PRIVATE: Width NUMERIC "8"130// Retrieval info: PRIVATE: dc_aclr NUMERIC "1"131// Retrieval info: PRIVATE: diff_widths NUMERIC "0"132// Retrieval info: PRIVATE: msb_usedw NUMERIC "0"133// Retrieval info: PRIVATE: output_width NUMERIC "8"134// Retrieval info: PRIVATE: rsEmpty NUMERIC "1"135// Retrieval info: PRIVATE: rsFull NUMERIC "0"136// Retrieval info: PRIVATE: rsUsedW NUMERIC "1"137// Retrieval info: PRIVATE: sc_aclr NUMERIC "0"138// Retrieval info: PRIVATE: sc_sclr NUMERIC "0"139// Retrieval info: PRIVATE: wsEmpty NUMERIC "0"140// Retrieval info: PRIVATE: wsFull NUMERIC "1"141// Retrieval info: PRIVATE: wsUsedW NUMERIC "0"142// Retrieval info: CONSTANT: INTENDED_DEVICE_FAMILY STRING "Cyclone II"143// Retrieval info: CONSTANT: LPM_HINT STRING "MAXIMIZE_SPEED=5,"144// Retrieval info: CONSTANT: LPM_NUMWORDS NUMERIC "32"145// Retrieval info: CONSTANT: LPM_SHOWAHEAD STRING "OFF"146// Retrieval info: CONSTANT: LPM_TYPE STRING "dcfifo"147// Retrieval info: CONSTANT: LPM_WIDTH NUMERIC "8"148// Retrieval info: CONSTANT: LPM_WIDTHU NUMERIC "5"149// Retrieval info: CONSTANT: OVERFLOW_CHECKING STRING "ON"150// Retrieval info: CONSTANT: RDSYNC_DELAYPIPE NUMERIC "4"151// Retrieval info: CONSTANT: UNDERFLOW_CHECKING STRING "ON"152// Retrieval info: CONSTANT: USE_EAB STRING "ON"153// Retrieval info: CONSTANT: WRITE_ACLR_SYNCH STRING "OFF"154// Retrieval info: CONSTANT: WRSYNC_DELAYPIPE NUMERIC "4"155// Retrieval info: USED_PORT: aclr 0 0 0 0 INPUT GND aclr156// Retrieval info: USED_PORT: data 0 0 8 0 INPUT NODEFVAL data[7..0]157// Retrieval info: USED_PORT: q 0 0 8 0 OUTPUT NODEFVAL q[7..0]158// Retrieval info: USED_PORT: rdclk 0 0 0 0 INPUT NODEFVAL rdclk159// Retrieval info: USED_PORT: rdempty 0 0 0 0 OUTPUT NODEFVAL rdempty160// Retrieval info: USED_PORT: rdreq 0 0 0 0 INPUT NODEFVAL rdreq161// Retrieval info: USED_PORT: rdusedw 0 0 5 0 OUTPUT NODEFVAL rdusedw[4..0] 162// Retrieval info: USED_PORT: wrclk 0 0 0 0 INPUT NODEFVAL wrclk163// Retrieval info: USED_PORT: wrfull 0 0 0 0 OUTPUT NODEFVAL wrfull164// Retrieval info: USED_PORT: wrreq 0 0 0 0 INPUT NODEFVAL wrreq165// Retrieval info: CONNECT: @data 0 0 8 0 data 0 0 8 0166// Retrieval info: CONNECT: q 0 0 8 0 @q 0 0 8 0167// Retrieval info: CONNECT: @wrreq 0 0 0 0 wrreq 0 0 0 0168// Retrieval info: CONNECT: @rdreq 0 0 0 0 rdreq 0 0 0 0169// Retrieval info: CONNECT: @rdclk 0 0 0 0 rdclk 0 0 0 0170// Retrieval info: CONNECT: @wrclk 0 0 0 0 wrclk 0 0 0 0171// Retrieval info: CONNECT: rdempty 0 0 0 0 @rdempty 0 0 0 0172// Retrieval info: CONNECT: rdusedw 0 0 5 0 @rdusedw 0 0 5 0173// Retrieval info: CONNECT: wrfull 0 0 0 0 @wrfull 0 0 0 0174// Retrieval info: CONNECT: @aclr 0 0 0 0 aclr 0 0 0 0175// Retrieval info: LIBRARY: altera_mf altera_mf.altera_mf_components.all 176// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.v TRUE177// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.inc FALSE178// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.cmp FALSE179// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo.bsf FALSE180// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_inst.v FALSE181// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_bb.v TRUE182// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_waveforms.html TRUE 183// Retrieval info: GEN_FILE: TYPE_NORMAL my_dcfifo_wave*.jpg TRUE184// Retrieval info: LIB_FILE: altera_mfmy_dcfifo_tb.v / Verilogdcfifo的testbench。