SYS82000RKXC-85中文资料

ks0108中文资料

电子发烧友 电子技术论坛点阵图形液晶显示模块HD61202控制器使用手册目录注意事项----------------------------------------------------------------------------------------------------------------------------2第一章、关于HD61202 及其兼容控制驱动器的一般介绍----------------------------------4一、HD61202 及其兼容控制驱动器的特点-------------------------------------------------------------------------4二、HD61202 及其兼容控制驱动器的引脚功能-------------------------------------------------------------------4三、HD61202 及其兼容控制驱动器的时序-------------------------------------------------------------------------6四、HD61202 及其兼容控制驱动器显示RAM 的地址结构-----------------------------------------------------7五、HD61202 及其兼容控制驱动器的指令系统-------------------------------------------------------------------7第二章:内藏HD61202 及其兼容控制驱动器图形液晶显示模块的电路结构特点-------------------------------------------------------------------------------------9第三章:内藏HD61202 及其兼容控制驱动器图形液晶显示模块的应用用----------------------------------------------------------------11注意事项十分感谢您购买我公司的产品。

ICP DAS WinCon8000 Series 硬件用户手册说明书

• WinCon 8000 Series

The WinCon 8000 is the flagship compact embedded controller manufactured by ICP DAS. Its leading technology gives you all of the best features of both traditional PLCs and Windows capable PCs. The WinCon 8000 system is powered by Windows and brings Windows programming style and skill into the world of PC-based PLCs. Application developers can directly develop their own programs in Microsoft’s Visual Studio .NET and Embedded Visual tools with the WinCon SDK, and then download them into WinCon 8000 for use. Or, they can port their favorite SCADA software onto WinCon 8000 for even easier application development. For SCADA applications, we also provide a product model embedded with InduSoft Web Studio run-time version to meet this need.

M80C85资料

GENRAL DESCRIPTIONThe MSM80C85AH is a complete 8-bit parallel; central processor implemented in silicon gate C-MOS technology and compatible with MSM80C85A.It is designed with higher processing speed (max.5 MHz) and lower power consumption compared with MSM80C85A and power down mode is provided, thereby offering a high level of system integration.The MSM80C85AH uses a multiplexed address/data bus. The address is split between the 8-bit address bus and the 8-bit data bus. The on-chip address latch : of a MSM81C55-5 memory product allows a direct interface with the MSM80C85AH.FEATURES•Power down mode (HALT-HOLD)•Low Power Dissipation: 50mW(Typ)•Single + 3 to + 6 V Power Supply•–40 to + 85°C, Operating Temperature •Compatible with MSM80C85A •0.8 m s instruction Cycle (V CC = 5V)•On-Chip Clock Generator (with External Crystal)•On-Chip System Controller; Advanced Cycle Status Information Available for Large System Control•Bug operation in MSM80C85AH is fixed•Four Vectored interrupt (One is non-maskable) Plus the 8080A-compatible interrupt.•Serial, In/Serial Out Port•Decimal, Binary and Double Precision Arithmetic •Addressing Capability to 64K Bytes of Memory •TTL Compatible•40-pin Plastic DIP(DIP40-P-600-2.54): (Product name: MSM80C85AHRS)•44-pin Plastic QFJ(QFJ44-P-S650-1.27): (Product name: MSM80C85AHJS)•44-pin Plastic QFP(QFP44-P-910-0.80-2K): (Product name: MSM80C85AHGS-2K)MSM80C85AHRS/GS/JS8-Bit CMOS MICROPROCESSORE2O0009-27-X2元器件交易网FUNCTIONAL BLOCK DIAGRAMINTR INTA 5.5 6.57.5TRAP SID SODRSTX1X2CLK OUT READY RD WR ALE S0S1IO / M HOLD HLDA RESET IN RESET OUT A15 - A8Address BusAD7- ADAddress/Data BusPIN CONFIGURATION (TOP VIEW)40 pin Plastic DIPA 8HOLD HLDA CLK(OUT)RESET IN READY IO/M S 1RD WR ALE S 0A 15A 14A 13A 12A 11A 10A 9V CC 39383736353433READY IO/M S 1RD WR NC ALE TRAP RST7.5RST6.5RST5.5INTR NC INTA 18192021222324A D 4N C A D 5A D 6A D 7G N D A 865432144S I DS O DR E S E T X 2X 1N C7891011121332313029S 0A 15A 14AD 0AD 1AD 2AD 314151617A 13V C C25262728A 9A 10A 11A 1243424140H O L D H L D AC L K (O R E S E T I NTRAP RST7.5RST6.5RST5.5INTR INTA AD 0A D 4A D 5A D 6A D 7G N D V C C A 8AD 1AD 2AD 3NC A 9A 10A 11N CMSM80C85AH FUNCTIONAL PIN DEFINITIONThe following describes the function of each pin:A 0 - A 7(Input/Output)3-state A 8 - A 15(Output, 3-state)Multiplexed Address/Data Bus: Lower 8-bits of the memory address (or I/O address) appear on the bus during the first clock cycle (T state) of a machine cycle. It then becomes the data bus during the second and third clock cycles.Address Bus: The most significant 8-bits of the memory address or the 8-bits of the I/O address, 3-stated during Hold and Halt modes and during RESET.Symbol FunctionALE (Output)Address Latch Enable: It occurs during the first clock state of a machine cycle and enables address to get latched into the on-chip latch peripherals. The falling edge of ALE is set to guarantee setup and hold times for the address information. The falling edge ALE can also be used to strobe the status information ALE is never 3-state.S 0 , S 1 , IO/M (Output)Machine cycle status:IO/M S 1 S 0 States S 1 can be used as an advanced R/W status. IO/M , S 0 and S 1 become valid at the beginning ofa machine cycle and remain stable throughout the cycle. The falling edge of ALE may be used to latch the state of these lines.RD(Output, 3-state)READ control: A low level on RD indicates the selected memory or I/O device is to be read thatthe Data Bus is available for the data transfer, 3-stated during Hold and Halt modes and during RESET.WR(Output, 3-state)WRITE control: A low level on WR indicates the data on the Data Bus is to be written into the selected memory or I/O location. Data is set up at the trailing edge of WR , 3-stated during Hold and Halt modes and during RESET.READY (Input)If READY is high during a read or write cycle, it indicates that the memory or peripheral is ready to send or receive data. If READY is low, the cpu will wait an integral number of clock cycles for READY to go high before completing the read or write cycle READY must conform to specified setup and hold times.HOLD (Input)HLDA (Output)HOLD ACKNOWLEDGE: Indicates that the cpu has received the HOLD request and that it will relinquish the bus in the next clock cycle. HLDA goes low after the Hold request is removed. The cpu takes the bus one half clock cycle after HLDA goes low.HOLD indicates that another master is requesting the use of the address and data buses.The cpu, upon receiving the hold request, will relinquish the use of the bus as soon as the completion of the current bus transfer. Internal processing can continue. The processor can regain the bus only after the HOLD is removed. When the HOLD is acknowledged, the Address, Data, RD , WR , and IO/M lines are 3-stated. And status of power down is controlled by HOLD.INTR (Output)INTERRUPT REQUEST: Is used as a general purpose interrupt. It is sampled on during the next to the last clock cycle of an instruction and during Hold and Halt states. If it is active, the Program Counter (PC) will be inhibited from incrementing and an INTA will be issued. During this cycle a RESTART or CALL instruction can be inserted to jump to the interrupt service routine. The INTR is enabled and disabled by software. It is disabled by Reset and immediately after an interrupt is accepted. Power down mode is reset by INTR.INTA (Output)INTERRUPT ACKNOWLEDGE: Is used instead of (and has the same timing as) RD during the instruction cycle after an INTR is accepted.RST 5.5RST 6.5RST 7.5(Input)RESTART INTERRUPTS: These three inputs have the same timing as INTR except they cause an internal RESTART to be automatically inserted.The priority of these interrupts is ordered as shown in Table 1. These interrupts have a higher priority than INTR. In addition, they may be individually masked out using the SIM instruction. Power down mode is reset by these interrupts.TRAP (Input)Trap interrupt is a nonmaskable RESTART interrupt. It is recognized at the same timing as INTR or RST 5.5 - 7.5. It is unaffected by any mask or Interrupt Disable. It has the highest priority of any interrupt. (See Table 1.) Power down mode is reset by input of TRAP.001100101110101Memory write Memory read I/O write I/O readOpcode fetchIO/M S 1 S 0 States 1...10¥¥10¥¥Interrupt Acknowledge Halt = 3-stateHold (high impedance)Reset ¥ = unspecifiedName Address Branched To (1)When Interrupt OccursType TriggerRST 7.53CH 34H Rising edge (latched).High level unitl sampled.RST 6.5RST 5.52CH (2)High level until sampled.High level until sampled.INTRTRAP Priority 2345124H Rising edge and high level unit sampled.Table 1 Interrupt Priority, Restart Address, and SensitivityNotes:(1)The processor pushes the PC on the stack before branching to the indicatedaddress.(2)The address branched to depends on the instruction provided to the cpuwhen the interrupt is acknowledged.RESET IN (Input)Sets the Program Counter to zero and resets the Interrupt Enable and HLDA flip-flops and release power down mode. The data and address buses and the control lines are 3-stated during RESET and because of the asynchronous nature of RESET IN, the processor's internal registers and flags may be altered by RESET with unpredictable results. RESET IN is a Schmitt-triggered input, allowing connection to an R-C network for power-on RESET delay. The cpu is held in the reset condition as long as RESET IN is applied.Symbol FunctionRESET OUT (Output)Indicated cpu is being reset. Can be used as a system reset. The signal is synchronized to the processor clock and lasts an integral number of clock periods.X 1, X 2(Input)X 1 and X 2 are connected to a crystal to drive the internal clock generator. X 1 can also be an external clock input from a logic gate. The input frequency is divided by 2 to give the processor's internal operating frequency.SID (Input)Serial input data line. The data on this line is loaded into accumulator bit 7 whenever a RIM instruction is executed.SOD (Output)Serial output data line. The output SOD is set or reset as specified by the SIM instruction.V CC + 5 Volt supply GNDGround Reference.CLK (Output)Clock Output for use as a system clock. The period of CLK is twice the X 1, X 2 input period.FUNCTIONAL DESCRIPTIONThe MSM80C85AH is a complete 8-bit parallel central processor. It is designed with silicon gate C-MOS technology and requires a single +5 volt supply. Its basic clock speed is 5 MHz, thus improving on the present MSM80C85A's performance with higher system speed and power down mode. Also it is designed to fit into a minimum system of two IC's: The CPU (MSM80C85AH), and a RAM/IO (MSM81C55-5)The MSM80C85AH has twelve addressable 8-bit register pairs. Six others can be used interchangeably as 8-bit registers or 16-bit register pairs. The MSM80C85AH register set is as follows:PC 16-bit address 8-bit ¥ 6 or 16-bits ¥ 3BC, DE, HL SP 16-bit address 5 flags (8-bit space)Flags or FProgram CounterACC or A 8-bits Accumulator Mnemonic ContentsRegisterGeneral-Purpose Registers; data pointer (HL)Stack Pointer Flag RegisterThe MSM80C85AH uses a multiplexed Data Bus. The address is spilt between the higher 8-bit Address Bus and the lower 8-bit Address/Data Bus. During the first T state (clock cycle) of a machine cycle the low order address is sent out on the Address/Data Bus. These lower 8-bits may be latched externally by the Address Latch Enable signal (ALE). During the rest of the machine cycle the data bus is used for mamory or I/O data.The MSM80C85AH provides RD , WR , S 0, S 1, and IO/M signals for bus control. An Interrupt Acknowledge signal (INTA ) is also provided. Hold and all Interrupts are synchronized with the processor's internal clock. The MSM80C85AH also provides Serial Input Data (SID) and Serial Output Data (SOD) lines for a simple serial interface.In addition to these features, the MSM80C85AH has three maskable, vector interrupt pins, one nonmaskable TRAP interrupt and power down mode with HALT and HOLD.INTERRUPT AND SERIAL I/OThe MSM80C85AH has 5 interrupt inputs: INTR, RST 5.5 RST 6.5, RST 7.5, and TRAP. INTR is identical in function to the 8080A INT. Each of the three RESTART inputs, 5.5, 6.5, and 7.5, has a programmable mask. TRAP is also a RESTART interrupt but it is nonmaskable.The three maskable interrupts cause the internal execution of RESTART ( saving the program counter in the stack branching to the RESTART address) it the interrupts are enable and if the interrupt mask is not set. The nonmaskable TRAP causes the internal execution of a RESTART vector independent of the state of the interrupt enable or masks. (See Table 1.)There are two different types of inputs in the restart interrupt. RST 5.5 and RST 6.5 are high level-sensitive like INTR (and INT on the 8080A) and are recognized with the same timing as INTR. RST 7.5 is rising edge-sensitive.For RST 7.5, only a pulse is required to set an internal flip-flop which generates the internal interrupt request. The RST 7.5 request flip-flop remains set until the request is serviced. Then it is reset automatically, This flip-flop may also be reset by using the SIM instruction or by issuing a RESET␣IN to the MSM80C85AH. The RST 7.5 internal flip-flop will be set by a pulse on the RST 7.5 pin even when the RST 7.5 interrupt is masked out.The interrupts are arranged in a flixed priority that determines which interrupt is to be recognized if more than one is pending, as follows: TRAP-highest priority, RST 7.5, RST 6.5, RST 5.5, INTR-lowest priority. This priority scheme does not take into account the priority of a routine that was started by a higher priority interrupt. RST 5.5 can interrupt an RST 7.5 routine if the interrupt are re-enabled before the end of the RST 7.5 routine.The TRAP interrupt is useful for catastrophic evens such as power failure or bus error. The TRAP input is recognized just as any other interrupt but has the highest priority. It is not affected by any flag or mask. The TRAP input is both edge and level sensitive. The TRAP input must go high and remain high until it is acknowledged. It will not be recognized again until it goes low, then high again. This avoids any false triggering due to noise or logic glitches. Figure 3 illustrates the TRAP interrupt request circuitry within the MSM80C85AH. Note that the servicing of any interrupt (TRAP, RST 7.5, RST 6.5, RST 5.5,INTR) disables all future interrupts (except TRAPs) until an El instruction is executed.The TRAP interrupt is special in that it disables interrupts, but preserves the previous interrupt enable status. Performing the first RIM instruction following a TRAP interrupt allows you to determine whether interrupts were enabled or disabled prior to the TRAP. All subsequent RIM instructions provide current interrupt enable status. Performing a RIM instruction following INTR or RST 5.5-7.5 will provide current interrupt Enable status, revealing that Interrupts are disabled.The serial I/O system is also controlled by the RIM and SIM instructions. SID is read by RIM, and SIM sets the SOD data.AcknowledgeFigure 3 Trap and RESET IN CircuitDRIVING THE X 1 AND X 2 INPUTSYou may drive the clock inputs of the MSM80C85AH with a crystal, or an external clock source.The driving frequency must be at least 1 MHz, and must be twice the desired internal clock frequency; hence, the MSM80C85AH is operated with a 6 MHz crystal (for 3 MHz clock). If a crystal is used, it must have the following characteristics:Parallel resonance at twice the clock frequency desired C L (load capacitance) £ 30 pF C S (shunt capacitance) £ 7 pFR S (equivalent shunt resistance) £ 75 ohms Drive level: 10 mWFrequency tolerance: ±0.05% (suggested)Note the use of the capacitors between X 1, X 2 and ground. These capacitors are required to assure oscillator startup at the correct frequency.Figure 4 shows the recommended clock driver circuits. Note in B that a pull-up resistor is required to assure that the high level voltage of the input is at least 4 V.For driving frequencies up to and including 6 MHz you may supply the driving signal to X, and leave X 2 open-circuited (Figure 4B). To prevent self-oscillation of the MSM80C85AH, be sure that X 2 is not coupled back to X 1 through the driving circuit.Note:Since the constant values may vary depending on oscillator, consult the manufacturer of the oscillator used when designing a circuit.Figure 4 Clock Driver Circuits* X 2 Left Floating33 pF Capacitor required for crystal frequency 10 to 6.25 MHz 50 pF Capacitor required for crystal frequency 6.25 to 4 MHz 100 pF Capacitor required for crystal frequency <4 MHzA. Quartz Crystal Clock DriverB. 1 - 10 MHz Input Frequency External Clock Drive CircuitBASIC SYSTEM TIMINGThe MSM80C85AH has a multiplexed Data Bus. ALE is used as a strobe to sample the lower 8-bits of address on the Data Bus. Figure 5 shows an instruction fetch, memory read and I/O write cycle (as would occur during processing of the OUT instruction). Note that during the I/ O write and read cycle that the I/O port address is copied on both the upper and lower half of the address.There are seven possible types of machine cycles. Which of these seven takes place is defined by the status of the three status lines (IO/M, S1, S0) and the three control signals (RD, WR,and INTA). (See Table 2.) The status line can be used as advanced controls (for device selection, for example), since they become active at the T1 state, at the outset of each machine cycle. Control lines RD and WR become active later, at the time when the transfer of data is to take place, so are used as command lines.A machine cycle normally consists of three T states, with the exception of OPCODE FETCH, which normally has either four or six T states (unless WAIT or HOLD states are forced by the receipt of READY or HOLD inputs). Any T state must be one of ten possible states, shown in Table 3.Table 2 MSM80C85AH Machine Cycle ChartTable 3 MSM80C85AH Machine State Chart0= Logic "0"1= Logic "1"TS = High Impedance ¥= UnspecifiedNotes:(1) ALE not generated during 2nd and 3rd machine cycles of DAD instruction.(2) IO/M = 1 during T 4 - T 6 of INA machine cycle.A AD IO/Figure 5 MSM80C85AH Basic System TimingPOWER DOWN ModeThe MSM80C85AH is compatible with the MSM80C85A in function and POWER DOWN mode. This reduces power consumption further.There are two methods available for starting this POWER DOWN mode. One is through software control by using the HALT command and the other is under hardware control by using the pin HOLD. This mode is released by the HOLD, RESET, and interrupt pins (TRAP, RST7.5, RST6.5 RST5.5, or INTR). (See Table 4.)Since the sequence of HALT, HOLD, RESET, and INTERRUPT is compatible with MSM80C85A, every the POWER DOWN mode can be used with no special attention.Start by means of Halt command Start by means of HOLD pin Released by using pins RESET and INTERRUPT (not by pin HOLD) Released by using RESET and HOLD pins (not by interrupt pins)Table 4 POWER DOWN Mode Releasing Method(1) Start by means of HALT command (See Figures 6 and 7.)The POWER DOWN mode can be started by executing the HALT command.At this time, the system is put into the HOLD status and therefore the POWER DOWN mode cannot be released even when the HOLD is released later.In this case, the POWER DOWN mode can be released by means of the RESET or interrupt.(2) Start by means of HOLD pin (See Figure 8.)During the execution of commands other than the HALT, the POWER DOWN mode is started when the system is put into HOLD status by means of the HOLD pin.Since no interrupt works during the execution of the HOLD, the POWER DOWN mode cannot be released by means of interrupt pins. In this case, the POWER DOWN mode can be released either by means of the RESET pin or by releasing the HOLD status by means of HOLD pin.CLK (OUT)ALEAD 0-7CPU MODE RESET INFigure 6 Started by HALT and Released by RESET INCLK (OUT)ALEHOLD CPU MODEHLDAFigure 8 Started and Released by HOLDCLK (OUT)ALECPU MODERST5.5Figure 7 Started by HALT and Released by RST5.5ABSOLUTE MAXIMUM RATINGS–55 - +150MSM80C85AHRS Power Supply Voltage V CC –0.5 - 7V Input Voltage V IN –0.5 - V CC +0.5V Output Voltage V OUT –0.5 - V CC +0.5V Storage Temperature T STG °CPower DissipationP D0.7WParameter Units Symbol With respect to GND—Ta = 25°CCondition LimitsMSM80C85AHGS MSM80C85AHJS1.01.0OPERATING RANGELimits Power Supply Voltage V CC 3 - 6V Operating TemperatureT OP–40 - +85°CParameterUnit Symbol RECOMMENDED OPERATING CONDITIONSDC CHARACTERISTICS"L"V ILR —–0.3+0.8Typ.Power Supply Voltage V CC 5V T OP +25"L" Input Voltage V IL —"H" Output Voltage V IH —Min.4.5–40–0.32.2Max.5.5+85+0.8V CC +0.3ParameterUnit Symbol °C V V Operating Temperature V V IHR—3.0V CC +0.3VRESET IN Input Voltage "H"RESET IN Input VoltageTyp.Max."L" Output Voltage V OL —0.4V "H" Output Voltage V OH ——V ——V Parameter Unit Symbol Min.—3.0V CC - 0.4I OL = 2.5 mA I OH = –2.5 mA I OH = –100 m A ConditionsV CC = 4.5 V - 5.5 V Ta = –40°C - +85°C Input Leak Current I LI —10m A Output Leak CurrentI LO—10m A –10–100 £ V IN £ V CC 0 £ V OUT £ V CC T cyc = 200 ns C L = 0 pF at reset Operating SupplyCurrentI CC1020mA 510mA——T cyc = 200 nsC L = 0 pF at power down modeAC CHARACTERISTICSParameter Symbol Condition Min.Max.UnitCLY Cycle Period t CYCt CYC=200 nsCL=150 pF 2002000nsCLY Low Time t140—ns CLY High Time t270—ns CLY Rise and Fall Time t r, t f—30nsX1 Rising to CLK Rising t XKR25120nsX1 Rising to CKK Falling t XKF30150nsA8~15 Valid to Leading Edge of Control (1)t AC115—ns AD0~7 Valid to Leading Edge of Control t ACL115—ns AD0~15 Valid Data in t AD—350ns Address Float After Leading Edge of RD INTA t AFR—0nsA8~15 Valid Before Trailing Edge of ALE (1)t AL50—ns AD0~7 Valid Before Trailing Edge of ALE t ALL50—ns READY Valid from Address Valid t ARY—100ns Address (A8~15) Valid After Control t CA60—ns Width of Control Law (RD, WR, INTA)t CC230—ns Trailing Edge of Control to Leading Edges of ALE t CL25—ns Data Valid to Trailing Edge of WR t DW230—ns HLDA to Bus Enable t HABE—150ns Bus Float After HLDA t HABF—150ns HLDA Valid to Trailing Edge of CLK t HACK40—ns HOLD Hold Time t HDH0—ns HOLD Step Up Time to Trailing Edge of CLK t HDS120—ns INTR Hold Time t INH0—ns INTR, RST and TRAP Setup Time to Falling Edge of CLK t INS150—ns Address Hold Time After ALE t LA50—ns Trailing Edge of ALE to Leading Edge of Control t LC60—ns ALE Low During CLK High t LCK50—ns ALE to Valid Data During Read t LDR—270ns ALE to Valid Data During Write t LDW—140ns ALE Width t LL80—ns ALE to READY Stable t LRY—30ns Trailing Edge of RD to Re-enabling of Address t RAE90—ns RD (or INTA) to Valid Data t RD—150ns Control Trailing Edge to Leading Edge of Next Control t RV220—ns Data Hold Time After RD INTA (7)t RDH0—ns READY Hold Time t RYH0—ns READY Setup Time to Leading Edge of CLK t RYS100—ns Data Valid After Trailing Edge of WR t WD60—ns LEADING Edge of WR to Data Vaild t WDL—20ns(Ta = –40°C ~ 85°C, V CC = 4.5 V ~ 5.5 V)Notes:(1)A 8 - A 15 address Specs apply to IO/M , S 0 and S 1.(2)Test condition: t CYC =200 ns C L =150 pF(3)For all output timing where C L =150 pF use the following correction factors:25 pF £ C L < 150 pF : –0.10ns/pF 150 pF < C L £ 200 pF : +0.30ns/pF(4)Output timings are measured with purely capacitive load.(5)All timings are measured to output voltage V L =0.8 V, V H =2.2 V, and 1.5 Vwith 10 ns rise and fall time on inputs.(6)To calculate timing specifications at other values of t CYC use Table 7.(7)Data hold time is guaranteed under all loading conditions.2.40.45Input Waveform for A.C. Tests:(1/2)T - 50t AL Min (Ta = -40°C - +85°C, V CC = 4.5 V - 5.5 V, C L = 150 pF)(1/2)T - 50t LA Min (1/2)T - 20t LL Min (1/2)T - 50t LCK Min (1/2)T - 40t LC Min (5/2+N)T - 150t AD Max (3/2+N)T - 150t RD Max (1/2)T - 10t RAE Min (1/2)T - 40t CA Min (3/2+N)T -70t DW Min (1/2)T - 40t WD Min (3/2+N)T - 70t CC Min (1/2)T - 75t CL Min (3/2)T - 200t ARY Max (1/2)T - 60t HACK Min (1/2)T + 50t HABF Max (1/2)T + 50(2/2)T - 85t HABE Max t AC Min (1/2)T - 60t 1Min (1/2)T - 30t 2Min (3/2)T - 80t RV Min t LDRMax——————————————————————MSM80C85AH Table 7 Bus Timing Specification as a T CYC DependentNote:N is equal to the total WAIT states.T = t CYC(2+N)T -130X1 INPUTCLKOUTPUTFigure 6 Clock Timing Waveform READ OPERATIONCLKA8-A15 AD0-AD7ALE RD / INTA T1T2T3T1WRITE OPERATIONCLK T1A8-A15AD0-AD7ALEWRT2T3T1CLKA 8~A 15AD 0~AD 7ALERD / INTAREADYT 1T 2T WAIT T 3T 1Note: READY must remain stable during setup and hold times.Figure 7 MSM80C85AH Bus Timing, With and Without WaitRead operation with Wait Cycle (Typical)–same READY timing applies to WRITE operationCLK HOLDHLDA BUSFigure 8 MSM80C85AH Hold TimingHOLD OPERATIONNOTE: (1) IO/M is also floating during this time.Figure 9 MSM80C85AH Interrupt and Hold TimingMOVE, LOAD, AND STORE MOVr1 r2MOV M r MOV r M MVI r MVI M LXI B LXI D LXI H LXI SP STAX B STAX D LDAX B LDAX D STA LDA SHLD LHLD XCHG MnemonicDescriptionInstruction Code (1)Clock (2)Cycles000000000000000001111000000000000001D 1D D 10011000011111D 1D D 10101010111000D 0D D 00000001101011S S 1110000000000000S S 1110000111111111S S 0001111000000001D 7D 6D 5D 4D 3D 2D 1D 0477710101010107777131316164Move register to register Move register to memory Move memory to register Move immediate register Move immediate memory Load immediate register Pair B & C Load immediate register Pair D & E Load immediate register Pair H & L Load immediate stack pointer Store A indirect Store A indirect Load A indirect Load A indirect Store A direct Load A direct Store H & L direct Load H & L direct Exchange D & E H & L registers STACK OPS PUSH B PUSH D PUSH H PUSH PSW POP B POP D POP H POP PSW XTHL SPHL 111111111111111111110011001111010101010100000000011111000000000000001011111111111212121210101010166Push register Pair B & C on stack Push register Pair D & E on stack Push register Pair H & L on stack Push A and Flags on stackPop register Pair B & C off stack Pop register Pair D & E off stack Pop register Pair H & L off stack Pop A and Flags off stack Exchange top of stack H & L H & L to stack pointer JUMP JMP JC JNC JZ JNZ JP JM JPE JPO PCHL 11111111111111111111000001111101100110000101001101000000000011111111101000000001107/107/107/107/107/107/107/107/106Jump unconditional Jump on carry Jump on no carry Jump on zero Jump on no zero Jump on positive Jump on minus Jump on parity even Jump on parity oddH & L to program counter CALL CALL CC CNC CZ CNZ CP CM CPE CPO111111111111111111000001111011001100110100110111111111000000000100000000189/189/189/189/189/189/189/189/18Call unconditional Call on carry Call on no carry Call on zero Call on no zero Call on positive Call on minus Call on parity even Call on parity oddTable 8 Instruction Set SummaryRETURN RET RC RNC RZ RNZ RP RM RPE RPO Mnemonic DescriptionInstruction Code (1)Clock (2)Cycles 111111111111111111000001111011001100110100110000000000000000000100000000D 7D 6D 5D 4D 3D 2D 1D 0106/126/126/126/126/126/126/126/12ReturnReturn on carry Return on no carry Return on zero Return on no zero Return on positive Return on minus Return on parity even Return on parity odd RESTART RST11A A A 11112Restart INPUT/OUTPUT IN OUT11110011100011111010Input OutputINCREMENT AND DECREMENT INR r DCR r INR M DCR M INX B INX D INX H INX SP DCX B DCX D DCX H DCX SP 000000000000000000000000D D 1100110011D D 1101010101D D 000000111111110000000000001111111101011111111144101066666666Increment register Decrement register Increment memory Decrement memory Increment B & C registers Increment D & E registers Increment H & L registers Increment stack pointer Decrement B & C Decrement D & E Decrement H & L Decrement stack pointer ADD ADD r ADC r ADD M ADC M ADI ACI DAD B DAD D DAD H DAD SP 11111100000000110000000000001100000001010101011111S S 11110000S S 11110000S S 0000111144777710101010Add register to AAdd register to A with carry Add memory to AAdd memory to A with carry Add immediate to AAdd immediate to A with carry Add B & C to H & L Add D & E to H & L Add H & L to H & LAdd stack pointer to H & LSUBTRACT SUB r SBB r SUB M SBB M SUI SBI111111000011000000111111010101S S 1111S S 1111S S 0000447777Subtract register from ASubtract register from A with borrow Subtract memory from ASubtract memory from A with borrow Subtract immediate from ASubtract immediate from A with borrowTable 8 Instruction Set Summary cont'd。

8M86维修资料

警告本手册仅供有经验的维修人员使用,不使用于一般消费者,手册中没有对非技术人员企图维修本产品而存在的潜在危害提出警告或者提醒。

电器产品应由有经验的专业技术人员进行维护和修理,任何其它人企图对本手册涉及的产品进行维护和修理将有可能受到严重伤害甚至生命危险。

1 产品标准1.1 机芯概述本机芯使用MSTAR的高集成芯片MSD389I,内置32bit RISC CPU,是单芯片数模一体化,内置DEMOdulation的DVB-C和一路串行或并行TS流,可支持DMB-T。

多媒体部分设有两路USB接口,一路网络接口可实现下载和在线收看功能,支持酷K和网络酷开功能。

功放采用的是STA335BW,支持2.1声道。

本机芯的软件架构用的是 Linux的操作系统,Kenel版本是2.6.8.9,用到的Uboot版本是1.1.6。

1.2 主要功能8M86机芯的接口功能配置如下:A.2路AV输入,1组分量,3路HDMI,1路VGA。

B.3路音频输入,其中1组AV,1组AV2和分量共用,1路VGA。

C.1组AV输出,1路重低音输出,1路数字音频输出。

D.2路 USB输入(其中1路可以用于软件升级),2路MIC麦克风输入,1路RJ45网络输入。

本机芯具有网络酷开功能,除具备酷K功能外,还具备本地酷开功能和网络酷开功能,本地酷开支持USB播放酷影、音乐相册(音乐、图片、文本),网络酷开功能支持“在线酷影”可以通过网络实时点播电影:“下载搜索”可以在网上搜索视频节目并下载到本地USB设备;“网上邻居”酷影播放局域网中电脑上共享的媒体文本。

本机芯为数模一体机,支持 DMB-T标准,可接收并解调DVB-C数字信号,通过插入CAM卡可以支持各个CA厂商的CA系统。

1.3 主要技术规格1、支持ISP(在系统可编程)功能,同时支持USB升级功能。

2、内置32-bit RISC CPU。

3、TS流既可从文件读取,也可从TS输入口输入,其最大速率为108M/S。

北京科瑞兴业 K85-CAN 模块 硬件说明书

K85-CAN模块硬件使用说明书(Ver 2.0 2009.02)北京科瑞兴业科技有限公司北京科瑞兴业科技有限公司地址:北京市海淀区知春里28号开源商务写字楼212、213室邮政编码:100086 电话:************************传真:************Sales E-mail: *************Tech Support E-mail: ********************第一章概述注:和本说明书配套使用的还有K85-CAN模块软件说明书,在同一光盘中。

1、K-85系列模块(CAN总线)概述:K-85系列是为现场工业测量控制设计的独立模块系列。

分别有模拟量输入、热电偶输入、热电阻输入、开关量输入、模拟量输出、开关量输出、测频、计数等功能模块。

模块内有微处理芯片和固化好的程序,可以完成上述功能。

每个模块都设有CAN总线接口,通过总线型网络把这些独立模块与计算机联网进行双向通讯,就构成一个完整的数据采集控制系统。

模块供电为宽电压输入,7-30VDC 均可。

可以将模块分散安排在整个现场的工作区域,而传感器或检测控制点就近连接到各自的模块,再用双绞的网络线连接各模块构成网络,因此,可大量节省电缆并减少施工安装的工作量。

系统布局灵活,测点增减方便,是用户构建自己的测控系统时值得选择的方案之一。

2、使用CAN方式的系统构成:图2 CAN总线连接示意图注:由于K-85系列模块使用CAN总线方式,而大部分用户采用主从方式通过PC(计算机)作为主机来进行数据采集或控制。

但是因为计算机一般不具备CAN总线接口,所以要通过图中所示的转换模块进行转换。

转换模块的种类和使用在下面的软件应用中将会提及。

用户在工程组网时除了要选择适用的应用模块外,要考虑到转换模块的选择。

第二章主要技术参数模块通用参数:1.通讯1.1通讯方式:CAN总线, 命令响应式通讯(主从方式)和主动上传模式(DAQ)。

Solaris 8 (SPARC 平台版) 发行说明说明书

Solaris8(SP ARC平台版)10/00发行说明更新Sun Microsystems,Inc.901San Antonio RoadPalo Alto,CA94303-4900U.S.A.部件号码806-6267–102000年10月Copyright2000Sun Microsystems,Inc.901San Antonio Road,Palo Alto,California94303-4900U.S.A.版权所有。

本产品或文档受版权保护,其使用、复制、发行和反编译均受许可证限制。

未经Sun及其授权者事先的书面许可,不得以任何形式、任何手段复制本产品及其文档的任何部分。

包括字体技术在内的第三方软件受Sun供应商的版权保护和许可证限制。

本产品的某些部分可能是从Berkeley BSD系统衍生出来的,并获得了加利福尼亚大学的许可。

UNIX是通过X/Open Company,Ltd.在美国和其他国家独家获准注册的商标。

Sun、Sun Microsystems、Sun标志、、AnswerBook、AnswerBook2、Java,JDK,DiskSuite,JumpStart,HotJava,Solstice AdminSuite,Solstice AutoClient,SunOS,OpenWindows,XView,和Solaris是Sun Microsystems,Inc.在美国和其他国家的商标、注册商标或服务标记。

所有SPARC商标均按许可证使用,它们是SPARC International,Inc.在美国和其他国家的商标或注册商标。

带有SPARC商标的产品均以Sun Microsystems,Inc.开发的体系结构为基础。

PostScript是Adobe Systems,Incorporated的商标或注册商标,它们可能在某些管辖区域注册。

Netscape Navigator(TM)是Netscape Communications Corporation的商标或注册商标。

SUN产品技术讲座

OBP

OpenBoot PROM (OBP) 固件在系统加电时就立刻运行。 OBP固件的主要任务包括: 测试并初始化系统硬件 从存储设备或者网络启动操作系统

提供了对软件和硬件的交互调试工具

OBP 3.X的新特性—通过Patch升级,支持第三方硬件 SUN企业级服务器在系统加电时或者系统重启时执行POST 。POST在OBP开始引导操作系统之前完成对所有硬件设 备的初始化。同时POST还会标识新的设备,并使这些新 设备能够被OBP及系统使用

系统引导过程

系统引导分为四个阶段: • Boot PROM 阶段 • 引导程序阶段 • 操作系统内核初始化阶段 • /sbin/init 阶段 注意: 尽管大型的企业服务器,如M800,比一般的单系统板 服务器,如E250,具有更多的系统板和磁盘,但是 Solaris在它们上面的启动过程几乎都是一样的。

系统配置文件

/etc/nodename 主机名配置文件 /etc/hosts 主机名和IP配置文件 /etc/hostname.hme0 网卡配置文件 /etc/netmasks 系统netmask 配置文件 /etc/defaultrouter 系统网关配置文件 /etc/vfstab 系统文件系统配置文件 /etc/system 系统内核配置文件

Solaris系统的用户管理命令

பைடு நூலகம் 添加用户

useradd –u uid –g gid –d home_dir –m –s shell username

添加用户组 删除用户

groupadd –g gid groupname

userdel –r username userdel username groupdel groupname

中微半导体CMS8S78xx增强型闪存8位1T 8051微控制器数据手册说明书

CMS80F251x数据手册ArrayCMS8S78xx数据手册增强型闪存8位1T 8051微控制器Rev. 1.01请注意以下有关CMS知识产权政策*中微半导体(深圳)股份有限公司(以下简称本公司)已申请了专利,享有绝对的合法权益。

与本公司MCU或其他产品有关的专利权并未被同意授权使用,任何经由不当手段侵害本公司专利权的公司、组织或个人,本公司将采取一切可能的法律行动,遏止侵权者不当的侵权行为,并追讨本公司因侵权行为所受的损失、或侵权者所得的不法利益。

*中微半导体(深圳)股份有限公司的名称和标识都是本公司的注册商标。

*本公司保留对规格书中产品在可靠性、功能和设计方面的改进作进一步说明的权利。

然而本公司对于规格内容的使用不负责任。

文中提到的应用其目的仅仅是用来做说明,本公司不保证和不表示这些应用没有更深入的修改就能适用,也不推荐它的产品使用在会由于故障或其它原因可能会对人身造成危害的地方。

本公司的产品不授权适用于救生、维生器件或系统中作为关键器件。

本公司拥有不事先通知而修改产品的权利,对于最新的信息,请参考官方网站。

1. 产品特性1.1 功能特性◆兼容MCS-51的1T指令系统- 系统时钟频率最高支持48MHz- 机器周期最快支持1T SYS @ F SYS≤24MHz - 机器周期最快支持2T SYS @ F SYS=48MHz ◆内存- 程序FLASH:16K×8Bit- Data FLASH:1K×8Bit- 通用RAM:256×8Bit- 通用XRAM:1K×8Bit- 支持BOOT功能区,1K/2K/4K可选- 程序FLASH支持分区保护◆4种振荡方式- HSI-内部高速振荡:48MHz- HSE-外部高速振荡:8MHz/16MHz- LSE-外部低速振荡:32.768KHz- LSI-内部低速振荡:125KHz◆GPIO- 最多可达26个GPIO- 均支持上/下拉电阻功能- 均支持边沿(上升沿/下降沿/双沿)中断- 均支持唤醒功能◆中断源- 支持所有的外部端口中断- 7个定时器中断- 其它外设中断◆定时器- WDT定时器(看门狗定时器)- Timer0/1,Timer2,Timer3/4- LSE_Timer(支持休眠唤醒功能)- WUT(唤醒定时器)- BRT(串口波特率时钟发生器)◆蜂鸣器驱动- 50%占空比,频率可自由设置◆增强型PWM- 4通道增强型PWM- 4个相互独立周期计数器- 支持独立/互补/同步/成组模式- 支持边沿对齐/中心对齐方式- 支持互补模式死区延时功能- 支持刹车功能以及刹车恢复功能◆通信模块- 1xSPI(通讯速率最高可达6Mb/s)- 1xI2C(通讯速率最高可达400Kb/s)- 1xUART(波特率最高可达1Mb/s)◆工作电压范围- 2.1V~5.5V◆工作温度范围- -40℃~105℃◆低压复位功能(LVR)- 1.8V/2.0V/2.5V/3.5V◆低压检测功能(LVD)- 2.0V~4.6V 16级可选◆内置温度传感器(TS)◆高精度12位ADC- 最多可达26个AD外部通道- 参考电压可选(1.2V/2.0V/2.4V/3.0V/VDD)- 可检测内部1.2V基准电压- 支持硬件触发启动转换功能- 支持一组结果数字比较功能◆支持软件LCD驱动- 软件驱动1/3偏置- 最多支持24COM或24SEG◆支持软件LED驱动- COM SEG驱动电流可选- 最多支持26COM或26SEG◆两路模拟比较器(ACMP0/1)- 正端最多可达4种选择,负端可选内部1.2V/VDD分压- 比较器支持单边/双边迟滞- 负端内部1.2V/VDD分压可接内部ADC通道◆低功耗模式- 空闲模式(IDLE)- 休眠模式(STOP)◆支持96位唯一ID号(UID)- 每颗芯片有独立的ID号◆支持两线串行编程与调试1.2 产品对比注:(1)通过系统配置寄存器设置APROM和BOOT空间大小,APROM与BOOT空间总共最大为16K。

MB85RC64中文

铁电存储器MB85RC64(8K×8)1.概述MB85RC64了FRAM(铁电随机存取记忆体)独立芯片配置了8192×8位,形成铁电工艺和硅栅CMOS工艺技术非易失性内存中的细胞。

MB85RC64采用两线串行接口(与世界标准的I2C总线兼容)。

与SRAM不同的MB85RC64是无需使用数据备份电池,能够保留数据。

MB85RC64的读写次数10亿次,与EPROM和FLASH相比,有显著的改善。

而且不在向写完存储器后,不需要查询序列。

2.特性●位操作:8192×8位●工作电压:2.7V—3.3V●工作频率:400KHz●两串行总线:I2C总线2.1标准版,支持标准模式和快速模式,由SCL和SDA控制。

●工作温度范围:-40℃—85℃●数据保持:10年(55℃)●读写寿命:至少每位10亿次●封装:Plastic / SOP, 8-pin (FPT-8P-M02)●低电压消耗:工作电流0.15mA,待机电流5uA3.管脚分配3.管脚功能描述管教编号管脚名功能描述1—3 A0/A1/A2 器件地址一个I2C总线可以连接8个和MB85RC64类似的器件。

通过将A0/A1/A2与VDD和VSS连接,确定每个器件的地址。

如果A0/A1/A2未连接,默认为0。

CPU通过SDA线输出一个地址与器件进行匹配。

4 VSS 数字地5 SDA 数据IO串口这是双向通信的数据IO口,用来读写铁电存储器的阵列数据,这是开漏极输出,可能是与其它漏极开路(或者集电极开路信号总线)进行线或运算,因此需要一个上拉电阻连接到外部电路。

6 SCL 时钟串口这是时钟输入口,时钟上升沿进行数据采样,下降沿进行数据输出。

7 WP 写保护WP是H电平,禁止写入。

WP是L电平,可进行写数据,如果WP没有置位,默认为L电平。

而读数据操作,不受WP 管脚的限制。

8 VDD 电源电压4.模块框图5.I2C电路MB85RC64有两线串行接口,支持I2C总线,并作为从器件工作。

FUJITSU SPARC ENTERPRISE M4000 服务器数据手册说明书

数据手册FUJITSU SPARC ENTERPRISE M4000服务器经济高效的UNIX®服务器集聚大型机优势,为您提供虚拟化、集成和自动化功能。

FUJITSU SPARC ENTERPRISE服务器永远是您的最佳选择FUJITSU SPARC Enterprise服务器基于可靠的SPARC架构,运行世界领先的Oracle Solaris 10操作系统,可通过虚拟化提高系统利用率和性能,是需要高可扩展性、高可靠性服务器的客户的理想选择。

结合Fujitsu(富士通)在关键业务计算技术和高性能处理器设计方面的丰富经验以及Oracle在开放式、可扩展、基于分区的网络计算方面的资深优势,此款服务器带来了能满足所有任务需求的整体灵活性。

秉承SPARC的优良传统FUJITSU SPARC Enterprise M4000服务器是一款中端系统,与其较大型的企业级兄弟产品一样,拥有强大的RAS功能。

不仅如此,其紧凑的机架安装设计还大大降低了用户的拥有成本。

该服务器具备不间断自我修复机制和坚如磐石的可靠性,能满足部门数据库和ERP应用程序的运行需求,还可跨两个物理分区集群设置这些应用程序,以确保高可靠性。

全面的二进制兼容性充分地保护您的应用程序投资,而且Oracle Solaris 容器也为您实现了进一步的无成本资源细分。

对于大多数业务应用程序而言,FUJITSU SPARC Enterprise M4000服务器的性能在同类产品中遥遥领先。

性能和优势灵活的投资保护可以在服务器中,甚至是分区中混用SPARC64TM VII/VII+双核处理器与SPARC64™VII四核处理器。

通过动态重新配置和可选的FUJITSU PRIMECLUSTER分区间集群,最多可支持2个物理分区和数以千计的Oracle Solaris容器。

满足用户的投资保护需求,更小的风险,更低的拥有成本。

在CPU路数、空间需求、能耗需求不变的情况下,性能可扩展近两倍。

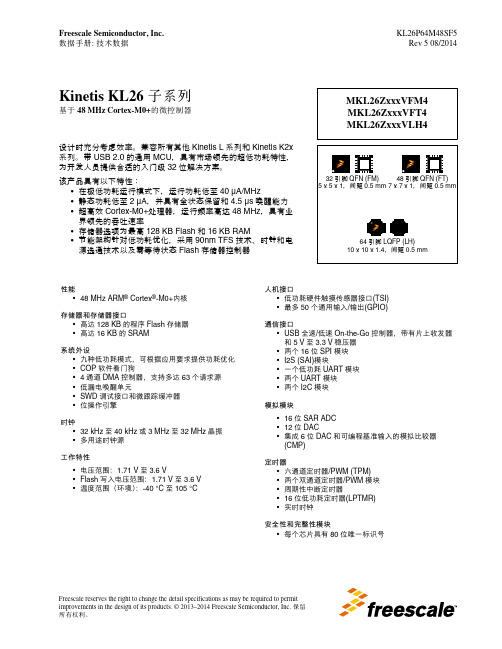

KL26P64M48SF5 中文资料

定时器 • 六通道定时器/PWM (TPM) • 两个双通道定时器/PWM 模块 • 周期性中断定时器 • 16 位低功耗定时器(LPTMR) • 实时时钟

安全性和完整性模块 • 每个芯片具有 80 位唯一标识号

Freescale reserves the right to change the detail specifications as may be required to permit improvements in the design of its products. © 2013–2014 Freescale Semiconductor, Inc. 保留

所有权利。

器件型号

MKL26Z32VFM4 MKL26Z64VFM4 MKL26Z128VFM4 MKL26Z32VFT4 MKL26Z64VFT4 MKL26Z128VFT4 MKL26Z32VLH4 MKL26Z64VLH4 MKL26Z128VLH4

Flash (KB) 32 64 128 32 64 128 32 64 128

• 在极低功耗运行模式下,运行功耗低至 40 μA/MHz • 静态功耗低至 2 μA,并具有全状态保留和 4.5 μs 唤醒能力 • 超高效 Cortex-M0+处理器,运行频率高达 48 MHz,具有业

界领先的吞吐速率 • 存储器选项为最高 128 KB Flash 和 16 KB RAM • 节能架构针对低功耗优化,采用 90nm TFS 技术、时钟和电

3 外设工作要求与特性......................................................................17 3.1 内核模块................................................................................. 17 3.1.1 SWD 电气特性 ......................................................... 17 3.2 系统模块................................................................................. 18 3.3 时钟模块................................................................................. 18 3.3.1 MCG 特性.................................................................. 18 3.3.2 振荡器电气规格........................................................ 20 3.4 存储器和存储器接口............................................................. 22 3.4.1 Flash 电气规格...........................................................22 3.5 安全性和完整性模块............................................................. 23 3.6 模拟......................................................................................... 24 3.6.1 ADC 电气规格...........................................................24 3.6.2 CMP 和 6 位 DAC 的电气规格................................ 28

科立信KS-858G防盗报警控制器说明书

防盗专家科立信KS-858防盗报警控制器GSM/PSTN&GPRS使用说明书泉州市科立信智能科技有限公司一、产品概述-------------------------------------------------二、主要功能及特点-------------------------------------------(1)三、系统工作示意图-------------------------------------------(2)四、系统安装-------------------------------------------------(2)五、键盘编程操作说明---------------------------------------(6)六、日常操作指南-------------------------------------------(17)七、APP 添加与使用-----------------------------------------(21)八、主要技术指标-------------------------------------------(24)九、注意事项-----------------------------------------------(24)十、简易故障检修-------------------------------------------(25)(1)目 录标准配置清单1、用户报警主机 1台 3、KS -13B 遥控器 2只 5、电源线 1条 7、2.2K Ω线尾电阻 8只 9、自攻螺丝 3支11、塑料栓 3支13、GSM (或4G )吸盘天线 1支2、机箱钥匙 2把4、橡胶天线 1根6、电话连接线 1条8、螺母 2个10、产品保修卡 1份12、KS -858使用说明书 1本KS-858是一款自带键盘和液晶显示的电话联网型语音智能报警主机,并可选配2G 或4G 通讯模块,构成双网报警控制器。

C8000设备介绍

第5章 机箱告警管理板介绍

C8000设备简介

C8000产品简介

OpticalLink® C8000

SCU:主控交换盘 LPU:光线路处理盘 SLU:上联盘 SMU:机架管理盘 FAN:风扇盘 PWR:电源盘(背侧)

ATCA架构;高密度;高 可靠性;模块式设计; 19英寸宽,12U高

黄色

慢闪 灭 常亮 快闪 慢闪 灭 常亮 灭

BLUE

蓝色

PON 端口 LINK PON 端口 ACT

SCU-A板外观示意图

交换控制板的相关指标

项目

交换容量

包交换率

VLAN数量

MAC地址表

路由表

SCU-A

96Gbit/s

72Mpps

4K

16K

8K

SCU-Bຫໍສະໝຸດ 136Gbit/s102Mpps

4K

16K

8K

SCU-A板简介

属性 CPU BOOTROM Flash Memory SDRAM 单板尺寸(H×W×D) 净重 最大功耗 对外接口 SCU-A MPC8245 400MHz 512KB 24MB 256MB 30.48mm×322.25mm×280mm 1.7Kg 60W 1个Console口

SCU-B MPC8245 400MHz 512KB 24MB 256MB 30.48mm×322.25mm×280mm

净重

最大功耗 对外接口 符合标准

1.7Kg

60W 1个10GBASE-R(XFP)万兆以太网端口,2个10GBASE-CX4 万兆以太 网端口和1个Console口 IEEE 802.3-2005 IEEE 802.1Q-2003 IEEE 802.1D-2004 IEEE 802.1X-2004

SYS82000RKXDL-85中文资料

Package DetailsSYS82000RKXD - 85/10/12DescriptionFeaturesIssue 1.4 : April 2001•Access Times of 85/100/120ns.•36 Pin Industry Standard Single-In-Line package.• 5 Volt Supply ± 10% .•Power Dissipation :Operating (min cycle)610 mW (max).Standby -L Version (CMOS) 2.2 mW (max).•Completely Static Operation.•Equal Access and Cycle Times.•Low Voltage V CC Data Retention.•Directly TTL Compatible.•On-board Decoding & Capacitors.•Compatible with the SYS8512RKX, SYS81000RKXB and SYS82000RKX modules.The SYS82000RKXD is a plastic 16Mbit Static RAM Module housed in a standard 36 pin Single-In-Line package organised as 2M x 8. This offers an extremely high PCB packing density.The module is constructed using four 512Kx8SRAMs in TSOPII packages mounted on a FR4epoxy substrate. Access times are 85, 100 and 120ns.The SYS82000RKXD is offered in standard and low power versions, with the -L module having a low voltage data retention mode for battery backed applications.Plastic 36 Pin Single-In-Line (SIP)ParameterSymbol Test ConditionMin Typmax UnitI/P Leakage CurrentAddress,OE,WEILI 0V < V IN < V CC-4-4µA Output Leakage Current I LO CS = V IH, V I/O = GND to V CC -4-4µA Average Supply Current I CC1Min. Cycle, CS = V IL ,V IL <V IN <V IH --110mA Standby Supply CurrentTTL levels I SB1CS = V IH--12mA CMOS levelsI SB2CS > V CC -0.2V, 0.2<V IN <V CC -0.2V --8mA -L Version (CMOS)I SB3CS > V CC -0.2V, 0.2<V IN <V CC -0.2V --400µA Output VoltageV OL I OL = 2.1mA --0.4V V OHI OH = -1.0mA2.4--VTypical values are at V CC =5.0V,T A =25o C and specified loading.Voltage on any pin relative to V SS V T (2)-0.3-7.0V Power Dissipation P T - 4.0-W Storage TemperatureT STG-55-125o CNotes :(1)Stresses above those listed may cause permanent damage to the device. This is a stress rating onlyand functional operation of the device at those or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.DC OPERATING CONDITIONS ParameterSymbolMinTypMaxUnitParameterSymbolMinTypMaxUnitSupply Voltage V CC 4.5 5.0 5.5V Input High Voltage V IH 2.2- V CC +0.3V Input Low VoltageV IL -0.3- 0.8V Operating Temperature(Commercial)T A 0-70o C (Industrial)T AI-40-85o CParameterSymbol Test ConditionmaxUnitInput Capacitance (Address,OE,WE)C IN1V IN = 0V 32pF I/P Capacitance (other)C IN2V IN = 0V 8pF I/O CapacitanceC I/OV I/O = 0V40pF* Input pulse levels: 0V to 3.0V * Input rise and fall times: 5ns* Input and Output timing reference levels: 1.5V * Output load: see diagram * V CC=5V±10%CC = 3.0V, CS > V CC I CCDR1 (2)T OP = 0°C to 40°C--220µA Chip Deselect to Data Retention Time t CDR See Retention Waveform 0--ns Operation Recovery Time t R See Retention Waveform5--msNotes(1)Typical figures are measured at 25°C.(2)This parameter is guaranteed not tested.-85 - 10 -12ParameterSymbol min max min max min maxUnitWrite Cycle Timet WC85-100-120-ns Chip Selection to End of Write t CW 75-80-100-ns Address Valid to End of Write t AW 75-80-100-ns Address Setup Time t AS 0-0-0-ns Write Pulse Width t WP 55-60-70-ns Write Recovery Time t WR 3-3-3-ns Write to Output in High Z t WHZ 030035040ns Data to Write Time Overlap t DW 35-40-45-ns Data Hold from Write Time t DH 0-0-0-ns Output active from end of writet OW5-5-5-ns-85 -10 -12ParameterSymbol min max min max min maxUnitRead Cycle Timet RC85-100-120-ns Address Access Time t AA -85-100-120ns Chip Select Access Time t ACS -85-100-120ns Output Enable to Output Valid t OE -45-50-60ns Output Hold from Address Change t OH 10-10-10-ns Chip Selection to Output in Low Z t CLZ 10-10-10-ns Output Enable to Output in Low Z t OLZ 5-5-5-ns Chip Deselection to O/P in High Z t CHZ 030035045ns Output Disable to Output in High Zt OHZ303545nsAC OPERATING CONDITIONSAddressDoutAC Read Characteristics Notes(1)WE is High for Read Cycle.(2)All read cycle timing is referenced from the last valid address to the first transition address.(3)t CHZ and t OHZ are defined as the time at which the outputs achieve open circuit conditions and are notreferenced to output voltage levels.(4)At any given temperature and voltage condition, t CHZ (max) is less than t CLZ (min) both for a given moduleand from module to module.(5)These parameters are sampled and not 100% tested.0VVccCSAC Write Characteristics Notes(1)All write cycle timing is referenced from the last valid address to the first transition address.(2)All writes occur during the overlap of CS and WE low.(3)If OE, CS, and WE are in the Read mode during this period, the I/O pins are low impedance state.Inputs of opposite phase to the output must not be applied because bus contention can occur.(4)Dout is the Read data of the new address.(5)OE is continuously low.(6)Address is valid prior to or coincident with CS and WE low, too avoid inadvertant writes.(7)CS or WE must be high during address transitions.(8)When CS is low : I/O pins are in the output state. Input signals of opposite phase leading to theoutput should not be applied.(9)Defined as the time at which the outputs achieve open circuit conditions and are not referenced tooutput voltage levels. These parameters are sampled and not 100% tested.Plastic 36 Pin Single-In-Line (SIP)SYS82000RKXDLI-85Speed85=85 ns10=100 ns12=120 nsTemperature Range Blank=Commercial TemperatureI=Industrial TemperaturePower Consumption Blank=Standard PartL=Low Power PartPackage RKXD=Plastic 36 Pin Single-In-Line(SIP)Organization82000=2M x 8Memory Type SYS=Static RAMNote :Although this data is believed to be accurate the information contained herein is not intended to and does not create any warranty of merchantibility or fitness for aparticular purpose.Our products are subject to a constant process of development. Data may be changed without notice.Products are not authorised for use as critical components in life support devices without the express written approval of a company director.。

PD80F01x系列_中文资料_数据手册

Rev1.20

第1页

2020-7-27

Pdmicro Technology Ltd

PD80F01X

目录

特性..................................................................................................................................................................................1

2.1. 地址映射................................................................................................................................................................. 9 2.1.1. SFR,BANK0................................................................................................................................................. 9 2.1.2. SFR,BANK1............................................................................................................................................... 10 2.1.3. TMR0,地址 0x01........

富士通sparc企业m8000服务器数据表说明书

DatasheetFujitsu SPARC Enterprise M8000 serverProvides the enterprise start point for large database. ERP and OLTP applications plus total stability, flexibility and asset protection.A SPARC of steelOnly the best with Fujitsu SPARC Enterprise As you would expect in a server aimed at your most important tasks, Fujitsu SPARC Enterprise M8000 has all the qualities of a mainframe. Absolutely rock solid, dependable andsophisticated, it has the total Solaris binary compatibility necessary to both protect your investments and enhance your business. Based on robust SPARC architecture andrunning the leading Oracle Solaris 11, Fujitsu SPARC Enterprise servers are ideal forcustomers needing highly scalable, reliable servers that increase their system utilization and performance through virtualization.The combined leverage of Fujitsu’s expertise in mission-critical computing technologies and high-performance processor design, with Oracle’s expertise in open, scalable,partition-based network computing, provides the overall flexibility to meet any task.Its rich virtualization eco-system of extended partitioning and Solaris Containers coupled with dynamic reconfiguration, means non-stop operation and total resource utilization at no extra cost. Benchmark leading performance with the world’s best applications and outstanding processor scalability just add to the capabilities of this attractive open system platform.Features and benefits Flexible investment protectionAll SPARC64 VI dual-core processor and SPARC64 VII/VII+ quad-core processor can be mixed and matched in the servers and even partitions. Investment protection for years to come, less risk and lower cost of ownership.Scales to nearly twice the performance with the same number of sockets and similar space and power requirements.Supports up to 16 physical partitions and thousands of SolarisContainers with dynamic reconfiguration and optional Fujitsu PRIMECLUSTER inter-partition clustering. Fast deployment of new applications with total availability for business critical processes.Reliability that makes you forgetEngineered like a mainframe with outstanding self-healing capability.All circuits, processors and memory are constantly monitored to ensure correct and continuous operation. Best suited to the needs of large databases, financial and high volume applications.Manages itself so you don’t have to.Self-managing hardware also maximizes the opportunity for applications to work at peak performance.World’s most advanced OS, Oracle Solaris 11Whole network can be virtualized by mapping physical network entities onto virtualization entitiesSolaris 10 Containers can help applications run on Solaris 11Boot Environment greatly reduces downtime for server updatesHighest security including delegated administration can minimize risks of attacks Minimizes costs of server administration and maintenanceApplication asset protection by non-disruptive upgradesMaximum system operations time due to online systems update abilityProtects business credibility by eliminating information exposure and business disruption risksTopicsReliability that makes you forgetFlexible investment protectionWhen Fujitsu designed Fujitsu SPARC Enterprise M8000 they looked to their long mainframe heritage to provide the quality and robustness needed in a major UNIX business-critical platform. The result is a most reliable, and highly scalable, self-sustaining system. That works well with the world’s most popular business application systems anddatabases. By placing the widest range of error checking and correction systems directly into the hardware, the platform manages itself. This relieves system administrators from most of the difficult diagnostic and recovery tasks required with many other systems. Once you own Fujitsu SPARC Enterprise system you will soon forget the operational problems of the past. Like the engine management systems in the finest cars, everything is monitored and self-managed to ensure all applications work non-stop at the peak of their capability.World’s most advanced OS, Oracle SolarisFujitsu has invested in your future by ensuring that new processors can be installed in existing systems. Even better they can be mixed, on the same system boards and in the same physical partitions, with previous processors. This provides unrivalled investment protection and - as you don’t need to replace servers so often - it can also reduce your overall IT spends.As advances in processor technology have continued, Fujitsu SPARC Enterprise and SPARC 64 processors provide the ability to significantly increase performance over time. You can either add more processors (up to 64 cores with Fujitsu SPARC Enterprise M8000) or employ new processors with almost twice the performance. In the latter case the increased performance comes with almost no increase in data center power consumption or additional heat management.To ensure that all that performance is fully used, support for up to 16 physical partitions and thousands of Solaris Containers lets you quickly and dynamically reconfigure the system for both existing and new business processes. Plus, in conjunction with Fujitsu PRIMECLUSTER middleware you can also implement fully mission-critical clustered solutions, between physical partitions, inside your M8000. Solaris is the only OS that has the scalability, security, and diagnostic features, to fully and quickly comprehend the situation, if a major application problem occurs. That is one of the reasons Solaris has the largest application portfolio and why it is the development platform of choice for many of the world’s major business applications.Technical detailsProcessorProcessor quantity and type 2–16x SPARC64 VII+, SPARC64 VII, SPARC64 VIProcessor options SPARC64 VII+ quad-core processor (3.0GHz, 128KB L1 cache on core, 12MB L2cache per chip)SPARC64 VII quad-core processor (2.88GHz, 128KB L1 cache on core, 6MB L2cache per chip)SPARC64 VI dual-core processor (2.4GHz, 256KB L1 cache on core, 6MB L2 cacheper chip)MemoryMemory slots 128 slotsMemory slot type DDR2 SDRAMMemory capacity (min. – max.) 16GB–1TBMemory protection ECCExtended ECCMemory Mirroring supportMemory PatrollingMemory modules 32GB Memory Expansion (16x 2GB DIMM)64GB Memory Expansion (16x 4GB DIMM)128GB Memory Expansion (16x 8GB DIMM)Drive baysHard disk bay configuration 16x 2.5-inch hot-swap SASHard disk drives 146GB 2.5-inch 10,000rpm300GB 2.5-inch 10,000rpmTape drive bay configuration 1x 3.5-inch hot-swap bayTape drives DAT72 (option)Optical drive bay configuration 1x 128mm bayOptical drives CD-RW/DVD-RW (8xDVD-ROM, 6xDVD-RW, 24xCD/CD-R, 10xCD-RW) InterfacesRemote Cabinet Interface (RCI) 2 portService LAN for XSCF 2 ports (10/100Mbit/s, RJ45)Service serial for XSCF 1 port (RS232C, RJ45)SlotsPCI Express 32x PCI Express (x8, full-height, short)Note Expandable to 112 slots (PCI Express, PCI-X) when using 20x External I/OExpansion UnitsSupported operating systemsSupported operating systems SPARC64 VII+ Oracle Solaris 10 8/07 or laterOracle Solaris 11Oracle Solaris 10 8/07 or laterVIISPARC64Oracle Solaris 11Oracle Solaris 10 11/06 or laterSPARC64VIOracle Solaris 11Operating system release link /sparcenterprise/manual/notes/Server managementService processor eXtended System Control Facility (XSCF) Supported software Enhanced Support FacilityServer System ManagerVirtualization Virtualization features Hardware partitioningDynamic ReconfigurationCapacity on demandSolaris ContainerRAS features Integer register protected by ECCProcessor RAS L1 cache protected by parity and redundancy and L2 cache protected by ECCDynamic way degradation in L1, L2 cache and TLBHardware Instruction RetryDynamic chip/core degradationOperation of processor is recorded automaticallyMemory (mirror configuration)Redundant components Hard disk drive (software RAID)PCI card (multi-path configuration)FanPower supply unitPower systemService processor (XSCF)CPU memory unit (CMU)Hot-swap components I/O unit (IOU)Hard disk drive (software RAID)PCI cardTape drive (DAT)Optical drive (CD-RW/DVD-RW)External I/O expansion unitsFanPower supply unitService processor (XSCF)Degradation features Dynamic degradation MemoryHard disk drive (software RAID)FanPower supply unitService processor (XSCF)CPU memory unit (CMU)degradationStaticProcessor (chip, core, cache)MemoryI/O unit (IOU)Hard disk drivePCI cardsCrossbarFanPower supply unitDimensions / WeightFloor-stand (W x D x H) 750 x 1,260 x 1,800 mm29.5 x 49.6 x 70.9 inchesWeight 700 kg1,543 lb.EnvironmentSound pressure (LpAm) 67 dB (A)Operating ambient temperature 5–32°C (depending on altitude)41–89.6°F (depending on altitude)Operating relative humidity 20–80%Operating altitude 0–3,000 m0–10,000 ftElectrical valuesRated voltage range Single-phase AC 200–240 V(delta)AC 200–240 V3-phaseAC 380–415 V(star)3-phaseRated frequency range 50/60 HzActive power max. 10.50 kWApparent power max. 10.98 kVAHeat emission 37,800 kJ/hComplianceEurope CERoHSUSA/Canada FCCUL/CSAJapan VCCIChina Chinese RoHSKorea MICTaiwan BSMICompliance note There is general compliance with the safety requirements of major countries.National approvals required in order to satisfy statutory regulations or for otherreasons can be applied for on request.Warranty and support servicesService link /supportMore informationIn addition to Fujitsu SPARC EnterpriseM8000, Fujitsu provides a range of platform solutions. They combine reliable Fujitsu products with the best in services,know-how and worldwide partnerships.Dynamic InfrastructuresWith the Fujitsu Dynamic Infrastructures approach, Fujitsu offers a full portfolio of ITproducts, solutions and services, ranging from clients to datacenter solutions, Managed Infrastructure andInfrastructure-as-a-Service. How much you benefit from Fujitsu technologies and services depends on the level ofcooperation you choose. This takes IT flexibility and efficiency to the next level.Computing Products/global/services/computing/ - PRIMERGY: Industrial standard server - SPARC Enterprise: UNIX server- PRIMEQUEST: Mission-critical IA server - ETERNUS: Storage system - BS2000/OSD: Mainframe - GS21: Mainframe - ESPRIMO: Desktop PC - LIFEBOOK: Notebook PC - CELSIUS: WorkstationSoftware/software/- Interstage: Application infrastructure software- Systemwalker: System management software- Symfoware: Database software - PRIMECLUSTER: Clustering softwareLearn more about Fujitsu SPARC Enterprise M8000, please contact your Fujitsu sales representative, Fujitsu business partner, or visit our website.©Copyright 2010 Fujitsu Limited. Fujitsu, the Fujitsu logo, PRIMERGY,PRIMEQUEST, ETERNUS, BS2000/OSD, GS21, ESPRIMO, LIFEBOOK, CELSIUS, Interstage, Systemwalker, Symfoware, PRIMECLUSTER are trademarks or registered trademarks of Fujitsu Limited in Japan and other countries. /sparcenterprise/GLOVIA is a trademark of GLOVIAInternational LLC in the United States and other countries.Fujitsu Green Policy Innovation is ourworldwide project for reducing burdens on the environment. Using our global know-how, we aim to resolve issues ofenvironmental energy efficiency through IT. Please find further information at:UNIX is a registered trademark of The Open Group in the United States and other countries.All SPARC trademarks are trademarks or registered trademarks of SPARCInternational, Inc. in the United States and other countries./global/about/environment/Oracle and Java are registered trademarks of Oracle and/or its affiliates.Other company, product and service names may be trademarks or registeredtrademarks of their respective owners.DisclaimerTechnical data subject to modification and delivery subject to availability. Any liability that the data and illustrations are complete, actual or correct is excluded. Designations may be trademarks and/or copyrights of the respective manufacturer, the use of which by third parties for their own purposes may infringe the rights of such owner.ContactFUJITSU LIMITEDWebsite: 2011-11-11 WW-EN。

生物技术工程实验室建设

(2)必要性

重庆市正在着力发展以生物工程、信息工程、环保工程为代表的高新技术产业,抓住中央直辖、三峡工程建设、西部大开发、城乡统筹发展四大历史性机遇,重庆“十一五”发展规划把生物技术作为未来高技术迎头赶上的重点。

2、学科专业现状

生物系现有副教授1名,博士5人,博士后2名,硕士4名,兼职教授3名,团队具有较强的科研和创新能力,近三年,在三大检索系统中共发表论文10多篇。学校特别为生物系制订了人才引进计划,近两年准备引进在生物技术方面有突出贡献的专家、教授2名,985重点院校毕业的博士或在211院校工作过的副教授5名,有计划安排现有的青年教师进入国内外著名的实验室或研究机构进修或学习,以此为基础,构建学院的核心创新团队,组建1个具有一定研究实力的生物制药研究中心,并以此为载体,大力发展本科教育,培养生物工程(以能源生物技术为主要研究方向)和制药工程(以医药生物技术为主要研究方向)本科专业的学生。

2007-2010年中央与地方共建高等学校共建专项资金项目

生物技术工程实验室建设

可行性论证报告

重庆科技学院

生物系

二○○七年六月二十日

一、总论

1、学科基本情况

原化学与生物工程学院是一个多学科及交叉学科并存的综合性学院,有化学与化学工程、生物技术、环境科学三个一级学科,以及交叉学科覆盖了全院八个专业:化学工程与工艺、应用化学、精细化工、工业分析、商品质量检测、生物制药、制药工程、环境工程,其中已有化学工程与工艺、应用化学两个本科专业。07年3月学校完成了学科专业结构布局调整,进行资源重组,由原来的化学与生物工程学院,新组建成立了化学化工学院和生物系。生物系现有15人,副教授1人,讲师7人,助教4人,全部பைடு நூலகம்有硕士学位,其中博士5人。现有生物制药、制药工程两个专业,2001年以来形成了以能力培养为主线,以基础知识的传授和学习能力的培养、工程观念和创新能力的培养为两个教学重心。全面体现“厚基础、宽口径、重实践、高素质、创造性”整体思路,突出本专业在新药研究与开发方面所形成的特色。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Package DetailsDescriptionFeaturesIssue 1.3 : April 2001SYS82000RKXC - 70/85/10/12•Access Times of 85/100/120 ns.•Low Power Disapation:Operating 600 mW (Max.)Standby-L Version 1.1 mW (Max.)• 5 Volt Supply ± 10%.•Completely Static Operation.•Low Voltage V CC Data Retention.•On-board Decoding & Decoupling Capacitors.•38 Pin Single-In-Line package (SIP).•Upgrade path to SYS84000RKXC (32Mbits).The SYS82000RKXC is a plastic 16Mbit Static RAM Module housed in a standard 38 pin Single In-Line package organised as 2M x 8 with access times of 85,100, or 120 ns.The module is constructed using four 512Kx8SRAMs in TSOPII packages mounted onto an FR4epoxy substrate. This offers an extremely high PCB packing density.The device is offered in standard and low power versions, with the -L module having a low voltage data retention mode for battery backed applications.Plastic 38 pin Single-In-Line (SIP)元器件交易网ISSUE 1.3 : April 2001SYS82000RKXC - 85/10/122DC OPERATING CONDITIONS ParameterSymbol min typ max unit Voltage on any pin relative to V SSV T -0.3-+7V Power Dissipation P T -- 4.0W Storage TemperatureT STG-55-+125o CNotes :(1) Stresses above those listed may cause permanent damage to the device. This is a stress rating only and functionaloperation of the device at those or any other conditions above those indicated in the operational sections of thisspecification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect devicereliability.ParameterSymbol Test Condition typ max Unit Input Capacitance (CS,A19,A20)CIN1V IN = 0V -8pF Input Capacitance (A0-18,OE,WE)C IN2V IN = 0V -32pF I/O CapacitanceC I/OV I/O = 0V-10pFParameterSymbol min typ maxunit Supply Voltage V CC 4.5 5.0 5.5V Input High Voltage V IH 2.2 - Vcc+0.3V Input Low VoltageV IL -0.3 - 0.8V Operating TemperatureT A 0-70o C T AI-40- 85o C (I)Parameter Symbol Test Condition min typ max Unit I/P Leakage Current I LI VIN = GND to V CC -4-4µA Output Leakage Current I LO CS = V IH , V I/O = GND to V CC -4-4µA Operating Supply Current I CC CS = V IL , min cycle, Duty = 100%-- 109mA Standby Supply Current TTL levels I SB1CS = V IH -- 12mA -L Version I SB2CS = V CC -0.2V, 0.2 > V IN > V CC -0.2V --200µA Output Low Voltage V OL I OL = 2.1mA --0.4V Output High Voltage V OH I OH = -1.0mA 2.4-- V元器件交易网SYS82000RKXC - 85/10/12ISSUE 1.3 April 20013CCDR CC CC -0.2V,0.2V>V in >V cc Chip Deselect to Data Ret. Time t CDR See Retention Waveform 0--ns Operation Recovery Time t RSee Retention Waveform5--ms元器件交易网ISSUE 1.3 : April 2001SYS82000RKXC - 85/10/124-85 -10 -12Parameter Symbol min max min max min max Unit Read Cycle Time t RC 85-100-120-ns Address Access Time t AA -85-100-120ns Chip Select Access Time t ACS -85-100-120ns Output Enable to Output Valid t OE -45-50-55ns Output Hold from Address Change t OH 10-10-10-ns Chip Selection to Output in Low Z t CLZ 10-10-10-ns Output Enable to Output in Low Z t OLZ 5-5-5-ns Chip Deselection to O/P in High Z t CHZ 030035040ns Output Disable to Output in High Zt OHZ303540nsAC OPERATING CONDITIONS-85 -10 -12Parameter Symbol min max min max min max Unit Write Cycle Timet WC 85-100-120-ns Chip Selection to End of Write t CW 75-80-100-ns Address Setup Timet AS 0-0-0-ns Address Valid to End of Write t AW 75-80-100-ns Write Pulse Width t WP 65-70-80-ns Write Recovery Time t WR 5-5-5-ns Write to Output in High Z t WHZ 030035040ns Data to Write Time Overlap t DW 35-40-45-ns Data Hold from Write Time t DH 0-0-0-ns Output active from end of writet OW5-5-5-ns元器件交易网SYS82000RKXC - 85/10/12ISSUE 1.3 April 20015AC Read Characteristics Notes(1)WE is High for Read Cycle.(2)All read cycle timing is referenced from the last valid address to the first transition address.(3)t CHZ and t OHZ are defined as the time at which the outputs achieve open circuit conditions and arenot referenced to output voltage levels.(4)At any given temperature and voltage condition, t CHZ (max) is less than t CLZ (min) both for a given moduleand from module to module.(5)These parameters are sampled and not 100% tested.元器件交易网ISSUE 1.3 : April 2001SYS82000RKXC - 85/10/1260VVccCSAC Write Characteristics Notes(1)All write cycle timing is referenced from the last valid address to the first transition address.(2)All writes occur during the overlap of CS and WE low.(3)If OE, CS, and WE are in the Read mode during this period, the I/O pins are low impedance state.Inputs of opposite phase to the output must not be applied because bus contention can occur.(4)Dout is the Read data of the new address.(5)OE is continuously low.(6)Address is valid prior to or coincident with CS and WE low, too avoid inadvertant writes.(7)CS or WE must be high during address transitions.(8)When CS is low : I/O pins are in the output state. Input signals of opposite phase leading to theoutput should not be applied.(9)Defined as the time at which the outputs achieve open circuit conditions and are not referenced tooutput voltage levels. These parameters are sampled and not 100% tested.Don'tCare元器件交易网SYS82000RKXC - 85/10/12ISSUE 1.3 April 20017Plastic 38 Pin Single-In-Line (SIP)SYS82000RKXCLI - 85Speed85= 85 ns 10= 100 ns 12= 120 nsTemperature RangeBlank = Commercial Temperature I = Industrial Temperature Power ConsumptionBlank = Standard Part L = Low Power Part Package RKXC = Plastic 38 pin SIP Organization 82000= 2M x 8Memory TypeSYS = Static RAMNote :Although this data is believed to be accurate, the information contained herein, is not intended to and does not create any warranty of merchantibility or fitness for a particular purpose.Our products are subject to a constant process of development. Data may be changed at any time without notice. Products are not authorised for use as critical components in life support devices without the express written approval of a company director.元器件交易网。