基于Verilog_HDL语言的整点智能响铃系统设计

数字闹钟的FPGA实现(Verilog)

闹钟的FPGA实现一.设计目的及总述:本次实验选择用FPGA实现一个闹钟。

它的功能有:1.时钟2.可以用按键快慢调整时钟时间3.可以设定闹钟并在时间到达设定闹钟时间时响起卡农音乐一分钟4.整点报时,响一声来报时系统一共有五个按键,分别命名为switch_mode,switch_enter,switch_pick,switch_down,switch_up。

时钟,调时,设定闹钟通过LCD1602进行显示,整点报时声和闹钟声通过蜂鸣器发出。

其中:本次实验的闹钟用Verilog语言进行设计,由于实验在Xilinx开发板上LCD1602显示模块几经调试显示都有问题,而实验的截止日期又极其接近了故最后选择在我购买的Altera 开发板上进行实现。

由于Altera公司FPGA使用Quartus II软件进行编译下载,所以把原来在ISE软件上以schematic方式实现的顶层原理图对应自动生成的verilog代码更改后添加进Quartus工程中使用。

所需要的修改仅为将顶层原理图中的OR2例化语句改为or(输出,输入1,输入2),并把系统时钟设为50MHZ,其他各模块代码不需进行更改。

二.仿真过程在几经更改之下,更由于在两种系统下的调试,使得仿真变得难以进行,此次试验针对各模块(不包括分频模块:fre_divider)的仿真结果难以找到了而且ISE9.1i十分难用,经常报各种错,因此在这里只选择其中比较重要的控制模块(controller)和时钟模块(timer),调时(快慢)模块(time_adjust)的仿真结果以说明本实验的仿真过程。

Controller:Timer:Time_adjust:三.系统总图即各模块Verilog代码和说明(参考对代码的详细注释):1.各模块之间连线图和对应的Verilog代码:Clock.v:module clock(clk_50m, //在本次实验所用的Altera开发版上,系统时钟为50MHZ rst, //复位键switch_down, //向下调整,设定switch_enter, //确认完成调整,设定switch_mode, //选择系统出于何种模式:时钟,调时,设定闹钟switch_pick, //选择调整,设定的对象:时,分,秒// switch_up, //向上调整,设定beep, //蜂鸣器lcd_d, //lcd1602 d7-d0管脚lcd_e, //lcd1602 en管脚lcd_rs, //lcd1602 rs管脚lcd_rw); //lcd1602 rw管脚input clk_50m;input rst;input switch_down;input switch_enter;input switch_mode;input switch_pick;//input switch_up;output beep;output [7:0] lcd_d;output lcd_e;output lcd_rs;output lcd_rw;//以下声明的线型量用于连接系统各模块 wire [7:0] XLXN_4;wire [7:0] XLXN_5;wire [7:0] XLXN_6;wire [7:0] XLXN_7;wire [7:0] XLXN_8;wire [7:0] XLXN_9;wire [7:0] XLXN_10;wire [7:0] XLXN_11;wire [2:0] XLXN_14;wire XLXN_15;wire XLXN_16;wire XLXN_17;wire XLXN_19;wire [5:0] XLXN_20;wire [5:0] XLXN_21;wire [5:0] XLXN_22;wire XLXN_24;wire [5:0] XLXN_33;wire [5:0] XLXN_34;wire XLXN_36;wire [5:0] XLXN_37;wire [5:0] XLXN_39;wire [5:0] XLXN_40;wire XLXN_50;wire XLXN_51;reg clk_25m;wire switch_up;assign switch_up=1;//由于系统本身是设计在实验室的板子上(25MHZ)上,所以现在把50MHZ系统时钟//二分频得到25MHZ时钟,这样就不用更改各子模块always@(posedge clk_50m)beginif(!rst)clk_25m<=0;elseclk_25m<=~clk_25m;end//控制模块,控制系统出于三种状态之一:时钟,调时,设定闹钟。

VerilogHDL语言数字时钟

VerilogHDL语言数字时钟EDA与数字系统设计报告实验名称:带有设臵时间功能和闹钟功能的数字钟一、设计内容和要求实验要求使用Verilog HDL进行多功能时钟的设计具体要求如下:1.能将基本的小时、分钟、及秒钟显示在数码管上2.能利用拨码开关进行时间的校正3.具有整点报时和闹钟的功能二、设计原理1.工作原理多功能数字钟系统共包括三个模块,即分频器模块、计数器模块和显示译码模块。

多功能数字钟的功能可以从整体上分为三类,分别是正常计时、时钟校对和闹钟设臵,所以考虑在系统中设臵一个模式控制信号mode。

模式控制信号对应一个按键,每按一次按键相当于工作模式进行一次变换,多次按下则数字钟将在正常计时、时间校对和闹钟设臵三个工作模式下依次循环。

在设计中,时钟校对和闹钟设臵工作模式都需要对时间进行设臵,通常是对小时和分钟进行设臵,所以需要在系统中设臵一个时间设臵信号set,对应一个按键,每按一次相当于在小时设臵和分钟设臵之间进行转换。

时间设臵时,分钟和小时计时单位之间互相独立,不存在进位关系。

同时设臵一个时间调整信号accum,每按一次与accum对应的按键,相当于对需要调整的分钟或小时的数字进行加1操作。

数字钟的计时输出信号时必不可少的,用hour,min和sec信号分别表示需要显示的小时、分钟和秒钟的计时结果,上述计时结果将通过译码显示模块进行译码后,连接到外部的七段数码显示器。

在带有闹钟设臵功能的数字钟中,闹钟输出信号也是必不可少的,到达到闹钟设臵的时间后,要向外部扬声器发送一个闹铃信号,设臵alert。

另外,我们还提供了闹钟铃声信号voice,当voice为0的时候,闹钟处于静音状态下,即使时间达到闹钟设定的时间也不会发声,当voice为1的时候,可以正常闹铃,voice信号对应一个拨码开关。

本设计中的小时、分钟和秒钟的计时结果采用BCD码表示方法。

采用这种表示方法便于对数结果的高位和低位分别进行译码。

用Verilog语言编写的多功能数字钟

这次的闹钟电路设计和多功能数字钟有一些相似的地方,不同在于整体构思和细

节上要求的差异。

构思根据要求采用的是状态机设计方法。从一个状态进入另一个状态最适合这个

设计了。细节上和数字钟也有很大的差异。中间的控制逻辑有时候需要反馈。前

后都是有联系的,并不是独立存在的。

本次设计基本上完成的所以的要求,但是由于时间紧急,一些细节并不是很完美,

分频器的作用是对 50Mhz 的系统时钟信号进行分频,得到频率为 1hz 的信号,

作为时钟的输入信号。

2

2.控制器和计数器 控制器的作用是,调整小时和分钟的值,并能实现清零功能。计数器的

作用是实现分钟和秒钟满 60 进 1,小时则由 23 跳到 00。当到达 59 分 55 秒的时 候,LED 灯会闪烁来进行报时。

end 2:

begin state<=2; s=1;

end 3:

begin s=0; if(k1==0) //时调整

7

begin

if(nz_h_l==3)

begin

nz_h_l=0;

if(nz_h_h==2)nz_h_h=0;

else nz_h_h=nz_h_h+1;

end

else nz_h_l=nz_h_l+1;

end

else if(k3==0) finish=1;

//设置完成

else if(k4==0) spker_en=1; //停止声响

end

8

4: begin s=0; if(k4==0) begin on_off<=!on_off;state=0;end end

endcase end end endmodule 3.显示器 显示器的作用是将时:分的值在数码管上依次显示出来。从分频器输出的 1Khz 的信号作为数码管的扫描信号。SEL 表示 6 个数码管选择位,它的取值表示八个 数码管,从左至右依次是 111~000。seg 表示七段数码管,它的取值决定特定位 数上显示的数字。

用verilog_HDL多功能数字钟剖析

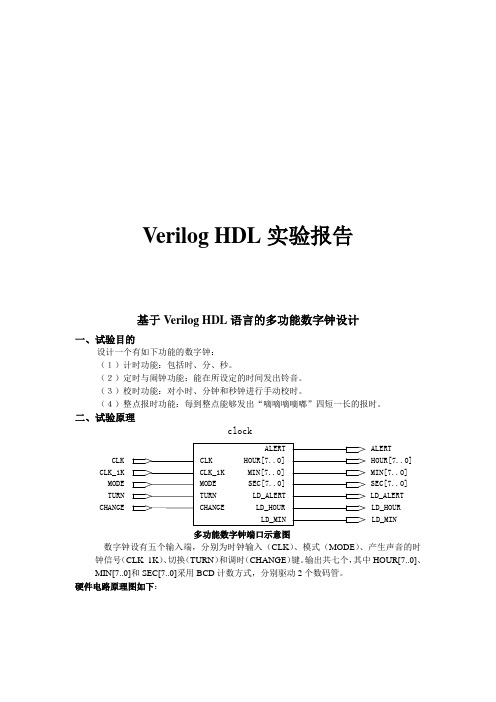

Verilog HDL实验报告基于Verilog HDL语言的多功能数字钟设计一、试验目的设计一个有如下功能的数字钟:(1)计时功能:包括时、分、秒。

(2)定时与闹钟功能:能在所设定的时间发出铃音。

(3)校时功能:对小时、分钟和秒钟进行手动校时。

(4)整点报时功能:每到整点能够发出“嘀嘀嘀嘀嘟”四短一长的报时。

二、试验原理多功能数字钟端口示意图数字钟设有五个输入端,分别为时钟输入(CLK)、模式(MODE)、产生声音的时钟信号(CLK_1K)、切换(TURN)和调时(CHANGE)键。

输出共七个,其中HOUR[7..0]、MIN[7..0]和SEC[7..0]采用BCD计数方式,分别驱动2个数码管。

硬件电路原理图如下:三、试验内容1. 代码/*信号定义:clk: 标准时钟信号,其频率为4Hz;clk_1k:产生闹铃声、报时音的时钟信号,其频率为1024Hz;mode:功能控制信号;为0:计时功能;为1:闹钟功能;为2:手动校时功能;turn:接按键,在手动校时功能时,选择是调整小时还是分钟;若长时间按住改建,还可使秒信号清零,用于精确调时;change: 接按键,手动调整时,每按一次,计数器加1;如果长按,则连续快速加1,用于快速调时和定时;hour,min,sec:此三信号分别输出并显示时、分、秒信号,皆采用BCD码计数,分别驱动6个数码管显示时间;alert:输出到扬声器的信号,用于产生闹铃音和报时音;闹铃音为持续20秒的急促的“嘀嘀嘀”音,若按住“change”键,则可屏蔽该音;整点报时音为“嘀嘀嘀嘀嘟”四短一长音;LD_alert:接发光二极管,指示是否设置了闹钟功能;LD_hour:接发光二极管,指示当前调整的是小时信号;LD_min:接发光二极管,指示当前调整的是分钟信号*/moduleclock(clk,clk_1k,mode,change,turn,alert,hour,min,sec,LD_alert,LD_hour,LD_min); input clk,clk_1k,mode,change,turn;output alert,LD_alert,LD_hour,LD_min;output[7:0] hour,min,sec;reg[7:0] hour,min,sec,hour1,min1,sec1,ahour,amin;reg[1:0] m,fm,num1,num2,num3,num4;reg[1:0] loop1,loop2,loop3,loop4,sound;reg LD_hour,LD_min;reg clk_1Hz,clk_2Hz,minclk,hclk;reg alert1,alert2,ear;reg count1,count2,counta,countb;wire ct1,ct2,cta,ctb,m_clk,h_clk;always @(posedge clk)beginclk_2Hz<=~clk_2Hz;if(sound==3) begin sound<=0; ear<=1; end //ear信号用于产生或屏蔽声音else begin sound<=sound+1; ear<=0; endendalways @(posedge clk_2Hz) //由4Hz的输入时钟产生1Hz的时基信号clk_1Hz<=~clk_1Hz;always @(posedge mode) //mode信号控制系统在三种功能间转换begin if(m==2) m<=0; else m<=m+1; endalways @(posedge turn)fm<=~fm;always //产生count1,count2,counta,countb四个信号begincase(m)2:begin if(fm)begin count1<=change; {LD_min,LD_hour}<=2; endelsebegin counta<=change; {LD_min,LD_hour}<=1; end{count2,countb}<=0;end1:begin if(fm)begin count2<=change; {LD_min,LD_hour}<=2; endelsebegin countb<=change; {LD_min,LD_hour}<=1; end{count1,counta}<=2'b00;enddefault:{count1,count2,counta,countb,LD_min,LD_hour}<=0;endcaseendalways @(negedge clk) //如果长时间按下“change”键,则生成“num1”信号用于连续快速加1if(count2) beginif(loop2==3) num2<=1;elsebegin loop2<=loop2+1; num2<=0;endendelse begin loop2<=0; num2<=0; endalways @(negedge clk) //产生num2信号if(count1) beginif(loop3==3) num3<=1;elsebegin loop3<=loop3+1; num3<=0; endendelse begin loop3<=0; num3<=0; endalways @(negedge clk)if(counta) beginif(loop4==3) num4<=1;elsebegin loop4<=loop4+1; num4<=0; endendelse begin loop4<=0; num4<=0; endassign ct1=(num3&clk)|(!num3&m_clk); //ct1用于计时、校时中的分钟计数assign ct2=(num1&clk)|(!num1&count2); //ct2用于在定时状态下调整分钟信号assign cta=(num4&clk)|(!num4&h_clk); //cta用于计时、校时中的小时计数assign ctb=(num2&clk)|(!num2&countb); //ctb用于在定时状态下调整小时信号always @(posedge clk_1Hz) //秒计时和秒调整进程if(!(sec1^8'h59)|turn&(!m))beginsec1<=0;if(!(turn&(!m))) minclk<=1;end//按住“turn”按键一段时间,秒信号可清零,该功能用于手动精确调时else beginif(sec1[3:0]==4'b1001)begin sec1[3:0]<=4'b0000; sec1[7:4]<=sec1[7:4]+1; endelse sec1[3:0]<=sec1[3:0]+1; minclk<=0;endassign m_clk=minclk||count1;always @(posedge ct1) //分计时和分调整进程beginif(min1==8'h59) begin min1<=0; hclk<=1; endelse beginif(min1[3:0]==9)begin min1[3:0]<=0; min1[7:4]<=min1[7:4]+1; endelse min1[3:0]<=min1[3:0]+1; hclk<=0;endendassign h_clk=hclk||counta;always @(posedge cta) //小时计时和小时调整进程if(hour1==8'h23) hour1<=0;else if(hour1[3:0]==9)begin hour1[7:0]<=hour1[7:4]+1; hour1[3:0]<=0; endelse hour1[3:0]<=hour1[3:0]+1;always @(posedge ct2) //闹钟定时功能中的分钟调节进程if(amin==8'h59) amin<=0;else if(amin[3:0]==9)begin amin[3:0]<=0; amin[7:4]<=amin[7:4]+1; endelse amin[3:0]<=amin[3:0]+1;always @(posedge ctb) //闹钟定时功能中的小时调节进程if(ahour==8'h23) ahour<=0;else if(ahour[3:0]==9)begin ahour[3:0]<=0; ahour[7:4]<=ahour[7:4]+1; endelse ahour[3:0]<=ahour[3:0]+1;always //闹铃功能if((min1==amin)&&(hour1==ahour)&&(amin|ahour)&&(!change))//若按住“change”键不放,可屏蔽闹铃音if(sec1<8'h20) alert1<=1; //控制闹铃的时间长短else alert1<=0;else alert1<=0;always //时、分、秒的现实控制case(m)3'b00: begin hour<=hour1; min<=min1; sec<=sec1; end//计时状态下的时、分、秒显示3'b01: begin hour<=ahour; min<=amin; sec<=8'hzz; end//定时状态下的时、分、秒显示3'b10: begin hour<=hour1; min<=min1; sec<=8'hzz; end//校时状态下的时、分、秒显示endcaseassign LD_alert=(ahour|amin)?1:0; //指示是否进行了闹铃定时assign alert=((alert1)?clk_1k&clk:0)|alert2; //产生闹铃音或整点报时音always //产生整点报时信号alert2 beginif((min1==8'h59)&&(sec1>8'h54)||(!(min1|sec1)))if(sec1>8'h54) alert2<=ear&clk_1k; //产生短音else alert2<=!ear&clk_1k; //产生长音else alert2<=0;endendmodule2. 仿真图四、小结及体会为了做多功能数字钟,我借了多本关于Verilog HDL的程序设计书。

基于VerilogHDL语言多功能数字钟设计毕业设计论文

多功能数字钟NJUST多功能数字钟设计基于VerilogHDL语言学院:电子工程与光电技术学院学号:************姓名:指导教师:2014年11月21日星期五摘要:基于FPGA平台,运用Verilog语言编写设计一多功能数字钟,包括基本的时钟,校时校分,整点报时功能。

扩展闹钟,秒表,万年历,键盘输入功能。

Abstract:FPGA-based platform, using Verilog language to design amulti-functional digital clock, including basic function of clock, school hours, school minutes,the whole point timekeeping. And extended function of alarm clock, stopwatch, calendar, keyboard input.关键词:多功能数字钟,可编程逻辑器件,EDA设计,VerilogKeywords:multi-functional digital clock, FPGA, EDA disign, Verilog目录1 设计要求 (2)2 设计方案选择及思路分析 (2)3 各子模块设计原理和分析 (3)3.1 分频模块 (3)3.2 时分秒模块 (5)3.3 时分调整模块 (6)3.4 报时模块 (7)3.5 扫描显示模块 (8)3.6 秒表模块 (9)3.7 闹钟模块 (10)3.8 万年历模块 (12)3.9 键盘扫描模块 (13)4 调试仿真 (15)5 编程下载 (16)6 结论 (17)7 参考文献 (17)8 实验感想 (17)9 源代码 (18)11 设计要求基于FPGA可编程逻辑器件,用quatusII软件设计一个多功能数字钟,其基本要求如下:1.有基础的计时显示功能,即时、分、秒显示在6个七段管上2.K0,K1,K2,K3分别为系统使能(暂停),时钟清零,校时,校分开关。

校园智能打铃系统的设计

smg_data[3]=8'h0d;

smg_data[4]=8'h99;

smg_data[5]=8'h49;

smg_data[6]=8'h41;

smg_data[7]=8'h1f;

smg_data[8]=8'h01;

smg_data[9]=8'h09;

end

reg [15:0] count_1ms; //1ms计时 always@(posedge clk or negedge reset) begin if(!reset) count_1ms<=0; else if(is_en&&count_1ms==t1ms) count_1ms<=0; else if(is_en) count_1ms<=count_1ms+1'b1; else if(!is_en) count_1ms<=0; end

四、确定输入和输出变量

• 输入变量 clk ,reset ,is_en

输出变量 ring ,smg_out,smg_en

五、确定输入状态

• 程序开始时内部计时显示在共阳数码管上,

• 初始状态 : 8点开始计时打铃。

•

打铃下课

•

午休

•

17点20放学电源关闭

七、输入和输出变量对应部件说明

输入变量:

always@(posedge clk_qian or negedge reset)

begin

if(!reset)

qian<=0;

else

if(qian==1'b1)

begin

qian<=0; end

用verilog-HDL多功能数字钟

用verilog-HDL多功能数字钟Verilog HDL实验报告基于Verilog HDL语言的多功能数字钟设计一、试验目的设计一个有如下功能的数字钟:(1)计时功能:包括时、分、秒。

(2)定时与闹钟功能:能在所设定的时间发出铃音。

(3)校时功能:对小时、分钟和秒钟进行手动校时。

(4)整点报时功能:每到整点能够发出“嘀嘀嘀嘀嘟”四短一长的报时。

二、试验原理ALERT HOUR[7..0]MIN[7..0]SEC[7..0]LD_ALERT LD_HOUR LD_MINCLK CLK_1K MODE TURN CHANGEclockCLK CLK_1K MODE TURN CHANGEALERTHOUR[7..0]MIN[7..0]SEC[7..0]LD_ALERT LD_HOUR LD_MIN多功能数字钟端口示意图数字钟设有五个输入端,分别为时钟输入(CLK )、模式(MODE )、产生声音的时钟信号(CLK_1K )、切换(TURN )和调时(CHANGE )键。

输出共七个,其中HOUR[7..0]、MIN[7..0]和SEC[7..0]采用BCD 计数方式,分别驱动2个数码管。

硬件电路原理图如下:三、试验内容1. 代码/*信号定义:clk: 标准时钟信号,其频率为4Hz;clk_1k:产生闹铃声、报时音的时钟信号,其频率为1024Hz;mode:功能控制信号;为0:计时功能;为1:闹钟功能;为2:手动校时功能;turn:接按键,在手动校时功能时,选择是调整小时还是分钟;若长时间按住改建,还可使秒信号清零,用于精确调时;change: 接按键,手动调整时,每按一次,计数器加1;如果长按,则连续快速加1,用于快速调时和定时;hour,min,sec:此三信号分别输出并显示时、分、秒信号,皆采用BCD码计数,分别驱动6个数码管显示时间;alert:输出到扬声器的信号,用于产生闹铃音和报时音;闹铃音为持续20秒的急促的“嘀嘀嘀”音,若按住“change”键,则可屏蔽该音;整点报时音为“嘀嘀嘀嘀嘟”四短一长音;LD_alert:接发光二极管,指示是否设置了闹钟功能;LD_hour:接发光二极管,指示当前调整的是小时信号;LD_min:接发光二极管,指示当前调整的是分钟信号*/moduleclock(clk,clk_1k,mode,change,turn,alert,hour,min,sec,LD_alert,LD_hour,LD_mi n);input clk,clk_1k,mode,change,turn;output alert,LD_alert,LD_hour,LD_min;output[7:0] hour,min,sec;reg[7:0] hour,min,sec,hour1,min1,sec1,ahour,amin;reg[1:0] m,fm,num1,num2,num3,num4;reg[1:0] loop1,loop2,loop3,loop4,sound;reg LD_hour,LD_min;reg clk_1Hz,clk_2Hz,minclk,hclk;reg alert1,alert2,ear;reg count1,count2,counta,countb;wire ct1,ct2,cta,ctb,m_clk,h_clk;always @(posedge clk)beginclk_2Hz<=~clk_2Hz;if(sound==3) begin sound<=0; ear<=1; end //ear信号用于产生或屏蔽声音else begin sound<=sound+1; ear<=0; endendalways @(posedge clk_2Hz) //由4Hz的输入时钟产生1Hz的时基信号clk_1Hz<=~clk_1Hz;always @(posedge mode) //mode信号控制系统在三种功能间转换begin if(m==2) m<=0; else m<=m+1; endalways @(posedge turn)fm<=~fm;always //产生count1,count2,counta,countb四个信号begincase(m)2:begin if(fm)begin count1<=change; {LD_min,LD_hour}<=2; endelsebegin counta<=change; {LD_min,LD_hour}<=1; end{count2,countb}<=0;end1:begin if(fm)begin count2<=change; {LD_min,LD_hour}<=2; endelsebegin countb<=change; {LD_min,LD_hour}<=1; end{count1,counta}<=2'b00;enddefault:{count1,count2,counta,countb,LD_min,LD_hour}<=0;endcaseendalways @(negedge clk) //如果长时间按下“change”键,则生成“num1”信号用于连续快速加1if(count2) beginif(loop2==3) num2<=1;elsebegin loop2<=loop2+1; num2<=0;endendelse begin loop2<=0; num2<=0; endalways @(negedge clk) //产生num2信号if(count1) beginif(loop3==3) num3<=1;elsebegin loop3<=loop3+1; num3<=0; endendelse begin loop3<=0; num3<=0; endalways @(negedge clk)if(counta) beginif(loop4==3) num4<=1;elsebegin loop4<=loop4+1; num4<=0; endendelse begin loop4<=0; num4<=0; endassign ct1=(num3&clk)|(!num3&m_clk); //ct1用于计时、校时中的分钟计数assign ct2=(num1&clk)|(!num1&count2); //ct2用于在定时状态下调整分钟信号assign cta=(num4&clk)|(!num4&h_clk); //cta用于计时、校时中的小时计数assign ctb=(num2&clk)|(!num2&countb); //ctb用于在定时状态下调整小时信号always @(posedge clk_1Hz) //秒计时和秒调整进程if(!(sec1^8'h59)|turn&(!m))beginsec1<=0;if(!(turn&(!m))) minclk<=1;end//按住“turn”按键一段时间,秒信号可清零,该功能用于手动精确调时else beginif(sec1[3:0]==4'b1001)begin sec1[3:0]<=4'b0000; sec1[7:4]<=sec1[7:4]+1; endelse sec1[3:0]<=sec1[3:0]+1; minclk<=0;endassign m_clk=minclk||count1;always @(posedge ct1) //分计时和分调整进程beginif(min1==8'h59) begin min1<=0; hclk<=1; endelse beginif(min1[3:0]==9)begin min1[3:0]<=0; min1[7:4]<=min1[7:4]+1; endelse min1[3:0]<=min1[3:0]+1; hclk<=0;endendassign h_clk=hclk||counta;always @(posedge cta) //小时计时和小时调整进程if(hour1==8'h23) hour1<=0;else if(hour1[3:0]==9)begin hour1[7:0]<=hour1[7:4]+1; hour1[3:0]<=0; endelse hour1[3:0]<=hour1[3:0]+1;always @(posedge ct2) //闹钟定时功能中的分钟调节进程if(amin==8'h59) amin<=0;else if(amin[3:0]==9)begin amin[3:0]<=0; amin[7:4]<=amin[7:4]+1; endelse amin[3:0]<=amin[3:0]+1;always @(posedge ctb) //闹钟定时功能中的小时调节进程if(ahour==8'h23) ahour<=0;else if(ahour[3:0]==9)begin ahour[3:0]<=0; ahour[7:4]<=ahour[7:4]+1; endelse ahour[3:0]<=ahour[3:0]+1;always //闹铃功能if((min1==amin)&&(hour1==ahour)&&(amin|ahour)&&(!change))//若按住“change”键不放,可屏蔽闹铃音if(sec1<8'h20) alert1<=1; //控制闹铃的时间长短else alert1<=0;else alert1<=0;always //时、分、秒的现实控制case(m)3'b00: begin hour<=hour1; min<=min1; sec<=sec1; end//计时状态下的时、分、秒显示3'b01: begin hour<=ahour; min<=amin; sec<=8'hzz; end//定时状态下的时、分、秒显示3'b10: begin hour<=hour1; min<=min1; sec<=8'hzz; end//校时状态下的时、分、秒显示endcaseassign LD_alert=(ahour|amin)?1:0; //指示是否进行了闹铃定时assign alert=((alert1)?clk_1k&clk:0)|alert2; //产生闹铃音或整点报时音always //产生整点报时信号alert2beginif((min1==8'h59)&&(sec1>8'h54)||(!(min1|sec1)))if(sec1>8'h54) alert2<=ear&clk_1k; //产生短音else alert2<=!ear&clk_1k; //产生长音else alert2<=0;endendmodule2. 仿真图四、小结及体会为了做多功能数字钟,我借了多本关于Verilog HDL的程序设计书。

fpga自动打铃器课程设计

fpga自动打铃器课程设计一、课程目标知识目标:1. 学生理解FPGA的基本原理和功能,掌握FPGA在数字系统设计中的应用。

2. 学生掌握Verilog HDL硬件描述语言的基本语法和编程技巧,能够编写简单的数字电路模块。

3. 学生掌握自动打铃器系统的设计原理,能够利用FPGA实现一个具有定时功能的自动打铃器。

技能目标:1. 学生能够运用所学知识,进行FPGA开发环境搭建,并完成基本的程序编写与烧录。

2. 学生能够运用Verilog HDL语言设计简单的数字电路,具备一定的硬件编程能力。

3. 学生通过实际操作,提高动手能力,培养解决实际问题的能力。

情感态度价值观目标:1. 学生通过课程学习,培养对电子信息技术领域的兴趣和热情,激发创新意识。

2. 学生在团队协作中,学会沟通与交流,培养合作精神,增强团队意识。

3. 学生在学习过程中,养成严谨、求实的科学态度,提高自主学习能力。

课程性质:本课程为电子信息类课程的实践环节,结合理论知识与实际操作,培养学生运用FPGA技术解决实际问题的能力。

学生特点:学生具备一定的数字电路基础,对硬件编程有一定了解,但实际操作能力有待提高。

教学要求:结合学生特点,注重理论与实践相结合,通过项目驱动的教学方法,引导学生主动参与,提高学生的实际操作能力。

在教学过程中,注重分层教学,关注个体差异,使每位学生都能在原有基础上得到提高。

同时,关注学生的情感态度价值观的培养,全面提高学生的综合素质。

二、教学内容1. 数字电路基础回顾:逻辑门电路、组合逻辑电路及时序逻辑电路的基本原理和设计方法。

2. FPGA基本原理:FPGA的结构、工作原理,以及FPGA在现代数字系统中的应用。

3. Verilog HDL语言:Verilog HDL的基本语法、数据类型、运算符、模块结构,以及常用语句的使用方法。

4. 自动打铃器系统设计:a. 系统需求分析:明确自动打铃器的基本功能,如定时打铃、铃声时长设定等。

课程设计---基于Verilog HDL数字时钟设计与实现

课程设计---基于Verilog HDL数字时钟设

计与实现

简介

本课程设计旨在通过使用Verilog硬件描述语言(HDL)设计和实现数字时钟。

学生将研究如何使用Verilog语言来描述数字电路,并将其应用于设计和实现一个简单的数字时钟电路。

设计目标

- 研究使用Verilog HDL来描述和设计数字电路

- 实现一个简单的数字时钟电路

- 熟悉数字时钟的工作原理和设计流程

实施步骤

1. 了解数字时钟的原理和工作方式

2. 研究Verilog HDL语言的基本语法和使用方法

3. 设计并实现时钟的各个功能模块,如时钟显示模块、时钟计数模块等

4. 使用仿真工具验证设计的正确性

5. 进行实际的硬件验证,将设计烧录到FPGA开发板上并进行测试

实验要求

1. 设计的数字时钟应具备基本的时分秒显示功能

2. 时钟应具备可调节的时间设置功能

3. 需要使用FPGA开发板进行实际硬件验证

4. 实验报告应包含设计原理、设计流程、仿真结果和实际硬件验证结果

参考资料

1. Verilog HDL教程

2. FPGA开发板用户手册

3. 相关学术论文和文献

以上为课程设计---基于Verilog HDL数字时钟设计与实现的文档简介。

本课程设计将帮助学生学习Verilog HDL语言并应用于设计和实现数字时钟电路。

智能闹钟整点报时系统的设计介绍

begin count <= 7"b0000000

end end

else if (count < 8"h60) begin

count <= count + 1 enmin_1 <= #100 1"b0 end

else begin

count <= 7"b0000000 end end end endmodule

always @(posedge clk or negedge reset) end

begin

else

if (reset == 1"b0)

begin

begin count <= 7"b0000000

end end

else if (count < 8"h60) begin

count <= count + 1 enhour_1 <= #100 1"b0 end else

分钟计数器

count <= 7"b0000000

module minute (clk, clk1, reset, sethouern,d

enhour, daout);

else

nput clk;

begin

input clk1;

if (count[3:0] == 4"b1001)

input reset;

题目:智能闹钟整点报时系统的设计

一、大作业摘要

– 普通的闹钟只能用来定时响铃,在快要到 时间的时候不能给人们提醒作用,是人们 心中没有那么强烈的时间观念,经常使人 猝不及防。那么,我想要解决的问题来了, 怎样才能让人们更清楚的确定目前处于的 时间段, 我在普通闹钟定时响铃的基础 上增加了整点报时的功能。

基于VerilogHDL语言的课堂智能响铃系统设计

1 引言20世纪末,电子技术获得了飞速的发展,在其推动下,现代电子产品几乎渗透了社会的各个领域,有力地推动了社会生产力的发展和社会信息化程度的提高,同时也使现代电子产品性能进一步提高,产品更新换代的节奏也越来越快。

课堂智能响铃系统走时精度高,稳定性好,实用方便,不需要经常调教,这种响铃具有时、分、秒计数显示功能,以24小时循环计时,时钟计数显示时有LED灯的花样显示,具有调节小时、分钟及清零的功能以及整点报时功能。

1.1 课程设计目的作为通信专业的学生,通过这次EDA方面的课程设计,可以提高我们对EDA领域及通信电路设计领域的认识,有利于培养我们在通信电路EDA方面的设计能力。

一人一题特别有利于锻炼我们独立分析问题和解决问题的能力。

设计过程的复杂加老师的严格要求有益于培养我们严谨的工作作风。

本次课题是计算机组成原理的课程设计,旨在通过自己对所需功能芯片的设计与实现来巩固以前所学的计算机硬件基础知识,同时也提高动手实践的能力,还有为将来进行更大规模更复杂的开发积累经验。

1.2 课程设计内容本次设计以智能打铃为主,实现时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分——60进制计数,即从0到59循环计数,时钟——24进制计数,即从0到23循环计数,并且在数码管上显示数值。

以及时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字钟真正具有使用功能。

我们可以通过实验板上的键7和键4进行任意的调整,因为我们用的时钟信号均是1HZ的,所以每LED灯变化一次就来一个脉冲,即计数一次。

清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。

可以根据我们自己任意时间的复位蜂鸣器在整点时有报时信号产生,蜂鸣器报警,产生“滴答.滴答”的报警声音。

LED灯在时钟显示时有花样显示信号产生。

即根据进位情况,LED不停的闪烁,从而产生“花样”信号。

2 理论基础2.1 Verilog HDL语言概述Verilog HDL是一种硬件描述语言(HDL:Hardware Discription Language),是一种以文本形式来描述数字系统硬件的结构和行为的语言。

FPGA设计实践课程设计报告打铃系统

上海电力学院课程设计报告课程设计名称:FPGA设计实践课程设计设计课题名称:自动打铃系统班级:2007142 指导老师:赵倩姓名:徐晓敏学号:20072702 成绩:设计时间:设计地点:实验室303计算机信息与工程学院自动打铃系统报告一、设计目的:使用Quartus II完成自动打铃系统的设计二、实验器材和工具软件:Pc机使用Quartus II系统De2平台三、设计内容:1. 基本计时和现实功能(用12小时制显示):包括上下午标志,时、分的数字显示,秒信号显示。

2. 可以自由设置当前时间(包含上、下午,时、分)。

3. 可以实现基本的打铃功能,规定:上午06:00起床铃,打铃5s,停2s,再打铃5s;下午10:30熄灯铃,打铃5s,停2s,再打铃5s。

铃声可以用LED灯光显示,如果实验装置没有LED发光管,那么可以用七段显示管的小数点显示,也可以用显示小时的十位数码管的多余段显示。

凡是用到铃声功能的均可以如此处理。

4. 增加整点报时功能,整点时响铃5s。

要求有控制启动和关闭功能。

5. 增加调整起床铃、熄灯铃时间的功能。

6. 增加调整打铃时间长短和间隙时间长短的功能。

7. 增设上午4节课的上、下课打铃功能,规定:7:30上课,8:20下课8:30上课,9:20下课9:40上课,10:30下课10:40上课,11:30下课。

每次铃响5s。

四、设计具体步骤:1、完成各个模块的设计,其具体代码如下:module clock (clock, en, adjusth, adjustm, adjusts, adjustpm, second, minute, hour);input clock;input en;input adjusth;input adjustm;input adjusts;input adjustpm;output[4:0] hour;reg[4:0] hour;output[5:0] minute;reg[5:0] minute;output[5:0] second;reg[5:0] second;always @(posedge clock)beginif (en == 1'b1)beginif (adjustpm == 1'b0)beginif (hour < 12)beginhour <= hour + 12 ;endelsebeginhour <= hour - 12 ;endendelse if (adjusth == 1'b1)beginif (hour == 23)beginhour <= 0 ;endelsebeginhour <= hour + 1 ;endendelse if (adjustm == 1'b1)beginif (minute == 59)beginminute <= 0 ;endelsebeginminute <= minute + 1 ;endendelse if (adjusts == 1'b1)beginsecond <= 0 ;endendelsebeginif (second == 59)beginsecond <= 0 ;if (minute == 59)beginminute <= 0 ;if (hour == 23)beginhour <= 0 ;endelsebeginhour <= hour + 1 ;endendelsebeginminute <=minute + 1 ;endendelsebeginsecond <= second + 1 ;endendendendmodulemodule statemachine (clock, changemode, adjposition, adjval, command, adjbotton, flash);input clock;input changemode;input adjposition;input adjval;output [4:0] command;reg[4:0] command;output[2:0] adjbotton;reg[2:0] adjbotton;output[2:0] flash;reg[2:0] flash;parameter[2:0] timer = 0;parameter[2:0] adj_timer = 1;parameter[2:0] adj_morningtime = 2;parameter[2:0] adj_eveningtime= 3;parameter[2:0] adj_ringlength = 4;parameter[2:0] adj_12or24 = 5;reg[2:0] state;reg[1:0] pos;always @(posedge clock) //mo kuai 1 gong neng shi tong guo changemode de an xia lai gai bian zhuang taibegincase (state) //case statetimer : //timer 0 shi beginif (changemode == 1'b0) // beginstate <= adj_timer ;endendadj_timer :beginif (changemode == 1'b0) beginstate <= adj_morningtime ; endendadj_morningtime :beginif (changemode == 1'b0) beginstate <= adj_eveningtime ; endendadj_eveningtime :beginif (changemode == 1'b0) beginstate <= adj_ringlength ; endendadj_ringlength :beginif (changemode == 1'b0) beginstate <= adj_12or24 ;endendadj_12or24 :beginif (changemode == 1'b0) beginstate <= timer ;endenddefault :beginstate <= timer ;endendcaseendalways @(posedge clock) //mo kuai 2begincase (state)timer : //zheng chang ji shi shibegin //command <= 5'b00000 ; //shu chu command wei 00000pos <= 0 ; //pos wei 0endadj_timer : //tiao zheng shi jian shibeginif (command == 5'b00000) //ru guo dang qian wei zheng chang ji shi zhuang tai begin//command<=5'b00001;pos <= 1 ; // pos wei 1endelsebegin //ru guo bu shi zheng chang ji shi zhuang taiif (adjposition == 1'b0) //erqie ci shi adiposition wei 1beginif (pos == 3) //erqie pos wei 3beginpos <= 1 ; //pos wei 1endelsebegin //pos bu wei3 de hua pos =pos +1pos <= pos + 1 ;endendendcommand <= 5'b00001 ; //zuo wan shang mian zhi hou command wei 00001 endadj_morningtime : //tiao zheng qi chuang shi jian zhuang taibeginif (command == 5'b00001) //ruguo dang qian wei tiao zheng shi jian zhuang tai beginpos <= 1 ; //pos wei 1endelsebeginif (adjposition == 1'b0) //fou zhe ru guo adjposition wei 1beginif (pos == 1) //erqie pos wei 1beginpos <= 2 ; //pos wei 2endelsebeginpos <= 1 ; //fou ze pos bu wei 1 shi pos wei 1endendendcommand <= 5'b00010 ;// zuo wan zhi hou command shu chu wei 00010 tiao zheng xi deng zhuang taiendadj_eveningtime :beginif (command == 5'b00010) // tiao wan shang shi jian de zhuang tai dang command wei 00010 shibeginpos <= 1 ; //pos wei 1endelsebeginif (adjposition == 1'b0) //command bu wei 00010 shi adjposition wei 1 shi beginif (pos == 1) //ru guo pos wei 1beginpos <= 2 ; //pos wei2endelsebeginpos <= 1 ; //fou ze wei 1endendendcommand <= 5'b00100 ; //zhi hou command shu chu wei 00100endadj_ringlength : //tiao zheng xiang liang zhuang taibeginif (command == 5'b00100) //ru guo command wei 00100beginpos <= 1 ; //pos wei1endelsebeginif (adjposition == 1'b0) //fou ze ru guo command bu shi 00100 qie adjposition wei 1beginif (pos == 1) //qie pos wei 1beginpos <= 3 ; //pos wei 3endelsebeginpos <= 1 ; //fou ze pos wei 1endendendcommand <= 5'b01000 ; //zui hou shu chu wei 01000endadj_12or24 : //ru guo dang qian zhuang tai weibeginpos <= 2 ; //pos wei 2command <= 5'b10000 ; //command shu chu wei 10000enddefault :beginpos <= 0 ; //fou ze zui hou pos wei 0command <= 5'b00000 ; //comman wei 00000endendcasecase (pos) //pos de case0 :begin //pos wei 0 shiflash <= 3'b000 ; //flash wei 000adjbotton <= 3'b000 ; //adjbotton wei 000end1 : //pos wei 1beginflash <= 3'b100 ; //flash wei 100if (adjval == 1'b0) //ru guo adjval wei 1beginadjbotton <= 3'b100 ; //adjbotton wei 100endelsebeginadjbotton <= 3'b000 ; //fou ze wei 000endend2 : //ru guo pos wei 2beginflash <= 3'b010 ; //flash wei 010if (adjval == 1'b0) //ru guo adjval wei 1beginadjbotton <= 3'b010 ; //adjbotton wei 010endelsebeginadjbotton <= 3'b000 ; //fou ze wei 000endend3 :beginflash <= 3'b001 ; //pos wei 3 shi flash wei 001 if (adjval == 1'b0) //ru guo adjvalbeginadjbotton <= 3'b001 ; //adjbotton wei 001endelsebeginadjbotton <= 3'b000 ; //fou ze wei 000endenddefault :beginflash <= 3'b000 ; //fou ze zui hou flash wei 000 adjbotton <= 3'b000 ; //adjbotton wei 000endendcaseendendmodulemodule displaycontroller (clock, enchange, change, enring, command, hour, getuphour, sleephour, minute,enalarm, getupminute, sleepminute, second, ringtime, pausetime, numa, numb, numc, pm, ring);input clock;input enchange;input change;input enring;input[4:0] command;input[4:0] hour;input[3:0] getuphour;input[3:0] sleephour;input[5:0] minute;input[5:0] getupminute;input[5:0] sleepminute;input[5:0] second;input[4:0] ringtime;input[3:0] pausetime;output[5:0] numa;reg[5:0] numa;output[5:0] numb;reg[5:0] numb;output[5:0] numc;reg[5:0] numc;output pm;reg pm;output ring;reg ring;output enalarm;wire enalarm;reg display24;reg enablealarm;wire[5:0] time1;wire[5:0] time2;always @(posedge clock)beginif (enchange == 1'b1) //zong kai shi kong zhibeginif (change == 1'b1) //bian hua wei yibegindisplay24 <= ~display24 ; //endendif (enring == 1'b0 & command == 5'b00000) //command mo shi ling sheng shi neng yu foubeginenablealarm <= ~enablealarm; //endendalways @(negedge clock) //bing xing yun xing mo kuaibegincase (command) //case tiao xuan yu ju5'b00000, 4'b0001 : //dang command deng yu 00000huo zhi 0001 shi beginif (display24 == 1'b0) //display24 wei 0 shi wei am pa xian shibeginif (hour >= 12)beginnuma <= hour - 12 ; //hour >12 pm wei yipm<= 1'b1 ;endelsebeginnuma <= hour ; //fou ze pm wei 0pm<= 1'b0 ;endendelsebeginnuma <= hour ; //display wei1 shipm<= 1'b0 ; //pm bu liang hour wei numaendnumb <=minute ; //fen wei numbnumc <= second ; //miao wei numc5'b00010 : //command wei 00010 shibeginpm<= 1'b0 ; //pm wei 0numa <= getuphour ; //xian shi de shi wei getuphournumb <= getupminute ; //xian shi de fen wei numbnumc <= 0 ;end5'b00100 : //command wei 00100 shi xian shi tiao zheng wan shui shi jian beginif (display24 == 1'b0) //dang display 12 dian shibeginnuma <= sleephour - 12 ; //xian shi ye yao bian cheng 12,qie shipm<= 1'b1 ;endelsebeginnuma <= sleephour ; //dang xian shi 24 xiao shi shi pm 0pm<= 1'b0 ;endnumb <= sleepminute ;numc <= 0 ;end5'b01000 : //command wei 01000 shibeginpm<= 1'b0 ; //24 xiao shi xian shinuma <= ringtime ; //numa xian shi xiang ling shi jian chang dunumb <= 60 ; //numb fu zhi 60numc <= pausetime ; //numb xian shi xiang ling zan ting shi jianend5'b10000 : //command wei 10000 shibeginpm<= 1'b0 ; //24 xiao shi xian shinuma <= 60 ; //numa 60 fu zhiif (display24 == 1'b0) //dang shi 12 xiao shi mo shibeginnumb <= 12 ; //numb xian shi 12endelsebeginnumb <= 24 ;// fou ze xin shi 24endnumc <= 60 ; //numc wei 60endbeginendendcaseendalways @(negedge clock) //xin de bing xing mo kuaibeginif (((hour == getuphour) & (minute == getupminute)) | ((hour == sleephour) & (minute == sleepminute)))begin //dang qi chuang huo zhe wan shui ling sheng shi jian shiif (second < ringtime) //qie dang miao xiao yu xiang ling chang du shibeginring <= 1'b1 ; //ling sheng xiang qiendelse if (second < time1) //huo dang miao xiao yu time1 shi xiang ling guan diaobeginring <= 1'b0 ;endelse if (second < time2) //huo dang miao xiao yu time2 shi xiang ling kai qi beginring <= 1'b1 ;endelsebeginring <= 1'b0 ; //qi ta suo you shi hou xiang ling guan biendendelse if ((hour == 7 & minute == 30) | (hour == 8 & minute == 20) | (hour == 8 & minute == 30) | (hour == 9 & minute == 20) | (hour == 9 & minute == 40) | (hour == 10 & minute == 30) | (hour == 10 & minute == 40) | (hour == 11& minute == 30))beginif (second < 5) //huo dang te dian shi jian shi xiang ling 5 wei nei you xiao beginring <= 1'b1 ;endelsebeginring <= 1'b0 ;endendelse if (enablealarm == 1'b1 & minute == 0 & second < 5)begin //enablealarm wei 1 fen wei 0 miao xiao yu 5 xiangring <= 1'b1 ;endelsebeginring <= 1'b0 ;endendassign time1 = ringtime + pausetime ; //time1 wei yi ge xiang tong jia yi ge ting tongassign time2 = ringtime * 2 + pausetime ; //time2 wei liang ge xiang tong yi ge ting tongassign enalarm = enablealarm ;endmodulemodule fenwei (numin, numa, numb);input[5:0] numin;output[3:0] numa;wire[3:0] numa;output[3:0] numb;wire[3:0] numb;wire[3:0] shi;assign shi = (numin == 60) ? 10 : (numin >= 50) ? 5 : (numin >= 40) ? 4 : (numin >= 30) ? 3 : (numin >= 20) ? 2 : (numin >= 10) ? 1 : 0 ;assign numb = (numin == 60) ? 10 : numin - shi * 10 ;assign numa = shi ;endmodulelibrary ieee;use ieee.std_logic_1164.all;entity num_7seg isport(c:in std_logic_vector(3 downto 0);hex:out std_logic_vector(6 downto 0));end num_7seg;architecture behave_num_7seg of num_7seg isbeginwith c(3 downto 0) select --hex<= "1000000" when "0000" , --"0""1111001" when "0001" , --"1""0100100" when "0010" , --"2""0110000" when "0011" , --"3""0011001" when "0100" , --"4""0010010" when "0101" , --"5""0000010" when "0110" , --"6""1111000" when "0111" , --"7""0000000" when "1000" , --"8""0010000" when "1001" ,--"9"--"0000000" when "1010" ,"1111111" when others; --" "end behave_num_7seg;module setringlength (clock, en, adjusth, adjusts, ringtime, pausetime); input clock;input en;input adjusth;input adjusts;output[4:0] ringtime;reg[4:0] ringtime;output[3:0] pausetime;reg[3:0] pausetime;always @(posedge clock) begin : xhdl_1reg[0:0] firsttime;if (firsttime == 0)beginringtime <= 5 ;pausetime <= 2 ;firsttime = 1;endelsebeginif (en == 1'b1)beginif (adjusth == 1'b1)beginif (ringtime == 20)beginringtime <= 1 ;endelsebeginringtime <= ringtime + 1 ; endendelse if (adjusts == 1'b1) beginif (pausetime == 10)beginpausetime <= 1 ;endelsebeginpausetime <= pausetime + 1 ; endendendendendendmodulemodule setringtime (clock, en1, en2, adjusth, adjustm, getuphour, getupminute, sleephour, sleepminute);input clock;input en1;input en2;input adjusth;input adjustm;output[3:0] getuphour;reg[3:0] getuphour;output[5:0] getupminute;reg[5:0] getupminute;output[3:0] sleephour;reg[3:0] sleephour;output[5:0] sleepminute;reg[5:0] sleepminute;always @(posedge clock)begin : xhdl_1reg[0:0] firsttime;if (firsttime == 0)begingetuphour <= 6 ;getupminute <= 0 ;sleephour <= 22 ;sleepminute <= 30 ;firsttime = 1;endelsebeginif (en1 == 1'b1)beginif (adjusth == 1'b1)beginif (getuphour == 11)begingetuphour <= 0 ;endbegingetuphour <= getuphour + 1; endendelse if (adjustm == 1'b1)beginif (getupminute == 59)begingetupminute <= 0 ;endelsebegingetupminute <= getupminute + 1; endendendif (en2 == 1'b1)beginif (adjusth == 1'b1)beginif (sleephour == 23)beginsleephour <= 12 ;endelsebeginsleephour <= sleephour + 1 ; endendelse if (adjustm == 1'b1)beginif (sleepminute == 59)beginsleepminute <= 0 ;endelsebeginsleepminute <= sleepminute +1 ; endendendendendmodulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clk_1_gen isport(clkin :in std_logic;clkout:out std_logic);end clk_1_gen;architecture behave_clk_div8 of clk_1_gen isconstant N: Integer:=24999999;signal Counter:Integer RANGE 0 TO N;signal Clk: Std_Logic;beginprocess(clkin)beginif rising_edge(clkin) then --每计到4个(0~3)上升沿,输出信号翻转一次if Counter=N thenCounter<=0;Clk<=NOT Clk;elseCounter<= Counter+1;end if;end if;end process;clkout<= Clk;end behave_clk_div8;module fenxian5 (in,out0,out1,out2,out3,out4);input [4:0]in;output out0;output out1;output out2;output out3;output out4;assign out0=in[0];assign out1=in[1];assign out2=in[2];assign out3=in[3];assign out4=in[4];endmodulemodule fenxian3 (in,out0,out1,out2);input [2:0] in;output out0;output out1;output out2;assign out0=in[0];assign out1=in[1];assign out2=in[2];endmodulelibrary ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity clkgen isport(clkin :in std_logic;clkout:out std_logic);end clkgen;architecture behave_clk_div8 of clkgen isconstant N: Integer:=4888888;signal Counter:Integer RANGE 0 TO N;signal Clk: Std_Logic;beginprocess(clkin)beginif rising_edge(clkin) then --每计到4个(0~3)上升沿,输出信号翻转一次if Counter=N thenCounter<=0;Clk<=NOT Clk;elseCounter<= Counter+1;end if;end if;end process;clkout<= Clk;end behave_clk_div8;2、根据各个模块进行连线3、引脚分配4、连接并显示实验结果五、设计收获以及存在的问题:在试验设计的过程中,我与同组的同学先是根据网上已有思路,看懂他们所设计的程序各个模块,再进行程序编写的。

Verilog HDL下简易电子钟设计分析

Verilog HDL下简易电子钟设计分析【摘要】Verilog HDL方法背景下,展开建议电子钟设计,不仅可以显示时间,可以精准的完成时间校对,设置闹铃等功能,并且与传统始终相比,减少设计期间很多不必要麻烦,避免出现线路布局问题。

对此,本文首先对简易电子钟设计要求以及原理进行阐述,其次分析了各个模块功能实现;最后提出了Verilog HDL下简易电子钟设计相关展望,希望通过本文,能够为相关人员的研究工作提供参考资料。

关键词:Verilog HDL;简易电子钟;设计;其实,在简易电子钟设计期间,可以利用编程软件来时间,这样可以使电路自动实现与时间的相关功能,也是Verilog HDL方法中解释电路设计行为的一种语言,并且与是C语言有着一定的相似之处。

同时,在Verilog HDL下简易电子钟设计期间,可以利用多功能接口实现预期的设计功能,并且这样不仅可以满足建简易电子钟设计建模的需求,也促使程序代码具有一定的延展性和兼容性,结合实际情况,对功能进行调整和修改,促使Verilog HDL下简易电子钟设计具有简洁的特点,提升简易电子钟的实用性和功能性。

1、简易电子钟设计要求以及原理1.1设计要求明确和掌握设计要求,可以更好地保证Verilog HDL下简易电子钟设计的效果,具体的设计要求如下【1】。

1.1.1通常情况下,简易电子钟设计以四种模式为主,即为:正常显示、时间调整、闹铃时间调整、秒表。

1.1.2要求简易电子钟具有时、分、秒计数等显示功能,并且需要以24h 循环计时。

同时,需要具有调节小时和分钟等功能。

1.1.3针对整点报时和闹铃时间等方面,需要具有可调整的功能。

另外,秒针计时器应当具有百秒计时模式、暂时、清零、以及开始等功能。

1.2设计原理简易电子钟是利用数字电路所显示时间的一种电子装置,并且与传统机械钟相比,不仅走时精准性较高,在功能调节方面,也相对较为简单,所以得到了广泛的使用。

同时,简易电子钟主要是将“时”“分”显示人的视觉器官的一种计时装置,并且24小时作为后期,显示满刻度为23时59分59秒,根据运行情况自动进行校对,确保显示时间的准确性【2】。

基于Verilog_HDL语言的整点智能响铃系统设计

长沙理工大学《计算机组成原理》课程设计报告学院计算机与通信工程专业网络工程班级 11-01 学号学生姓名指导教师陈沅涛课程成绩完成日期 2014年1月10日课程设计任务书计算机与通信工程学院网络工程专业课程设计成绩评定学院计通学院专业网络工程班级11-01班学号学生姓名指导教师陈沅涛完成日期2014年1月10日指导教师对学生在课程设计中的评价指导教师对课程设计的评定意见基于Verilog_HDL语言的整点智能响铃系统设计学生姓名:指导老师:陈沅涛摘要:本设计主要利用Verilog_HDL语言在EDA平台上设计整点响铃系统。

整点智能响铃系统走时精度高,稳定性好,实用方便,不需要经常调教,这种响铃具有时、分、秒计数显示功能,以24小时循环计时,时钟计数显示时有LED灯的花样显示,具有调节小时、分钟及清零的功能以及整点报时功能。

这次设计以Verilog_HDL语言和MAX+PLUS II为工具,实现整点智能报时。

系统分模块进行分析和设计,并给出相应的设计原理图和Verilog_HDL源程序,通过仿真实现预定功能。

关键词:;整点智能响铃系统;EDA;Verilog_HDL;MAX +plusⅡBased on Verilog_HDL language intelligentalarm system design of the hourStudent Name: Supervisor: Chen YuantaoAbstract: This design mainly use Verilog_HDL language on EDA platform design hourly alarm system. The hour walking intelligent alarm system of highprecision, good stability, convenient and practical, don't need often set-up,this ring has when, minutes and seconds count display function, with24-hour cycle time, counting clock display LED lights of the pattern,according to adjust the hours, minutes and reset function and the hour ofthe function. The design to Verilog_HDL language and MAX + PLUS II is thetool, realize intelligent tell the time of the hour. Points module system foranalysis and design, and gives the corresponding design principle diagramand Verilog_HDL source program, reservation function was achieved by thesimulation.Key words: Intelligent alarm system design of the hour;EDA;Verilog_HDL;MAX +plus Ⅱ目录1 引言 (7)1.1 课题背景及意义 (7)1.2课程设计目的 (8)1.3课程设计内容 (8)2 理论基础 (9)2.1 Verilog HDL语言概述 (9)2.2 MaxplusII简介 (10)3 整点智能响铃系统的设计方案 (12)3.1设计功能及分析 (12)3.2 系统总体框架结构 (12)4 系统模块的设计与仿真 (13)4.1秒计数器模块 (13)4.1.1模块的具体实现及功能介绍: (13)4.1.2秒计数器模块仿真: (13)4.2 分钟计数器模块: (14)4.2.1模块的具体实现及功能介绍: (14)4.2.2分钟计数器模块的仿真图: (14)4.3时钟计数器模块: (15)4.3.1模块的具体实现及功能介绍: (15)4.3.2小时计数器模块的仿真图: (15)4.4整点报时模块 (16)4.4.1模块的具体实现及功能介绍: (16)4.4.2整点报时模块的仿真图: (16)5整点智能响铃系统的仿真与实现 (17)6小结 (20)7.致谢 (21)参考文献 (22)附录:整点智能响铃系统设计源程序清单 (23)1引言现在,人类社会已进入到高度发达的信息化社会。

基于Verilog HDL的闹钟设计

封面删除~你懂的之阿布丰王创作随着微电子技术、计算机技术、半导体技术的发展,很多传统的数字门电路的设计已经被可编程逻辑器件替代.而对传统的模拟控制技术,也被数字控制系统所取代.数字系统在各个领域显示出了无穷的魅力与优势,如今已经被广泛应用于实际工程中.本文利用Verilog HDL 语言自顶向下的设计方法设计多功能数字钟, 实现时、分、秒的计时和校时,以及整点报时和闹钟的功能.突出了其作为硬件描述语言的良好的可读性、可移植性和易理解等优点, 并通过ModelSim SE 6.5完成综合、仿真.通过Verilog HDL语言完成数字钟的条理化设计.关键词:数字电子时钟,有限状态机,功能仿真AbstractAs the microelectronics, computer technology, semiconductor technology, many traditional design of digital gate programmable logic device has been WordStrd. As for the traditional analog control, digital control systems have also been WordStrd. Digital systems in various fields has shown infinite charm and advantages, and now has been widely used in practical projects. In this paper, Verilog HDL, the design of top-down multi-functional digital clock designed to achieve the hours, minutes, seconds, time and school, as well as the whole point timekeeping and alarm functions. Highlighted as a hardware description language, good readability, portability and ease of understanding, etc., and through the ModelSim SE 6.5 complete the comprehensive, simulation. Completed by Verilog HDL, the level of the digital clock design.Key words:Digital electronic clock, finite state machine, functional simulation.第1章绪论.................................................................................................................................... .. 11.1时钟的发展简史 (1)1.2设计目的 (1)1.3V e r i l o g H D L硬件描述语言 (2)1.4M o d e l s i m仿真工具 (5)第2章数字电路设计方法 (7)2.1数字系统设计简介 (7)2.2有限状态机 (9)第3章数字钟的条理化设计 (13)3.1功能要求 (13)3.2数字钟系统的工作原理 (13)3.3模块的设计 (13)3.4法式设计 (14)第4章功能仿真 (19)4.1仿真前准时间:二O二一年七月二十九日备 (19)4.2功能仿真 (20)第5章总结...................................................................................................................................2 3 参考文献.................................................................................................................................... .. (26)第1章绪论1.1时钟的发展简史设计目的公元1300年以前,人类主要是利用天文现象和流植物质的连续运动来计时.例如,日晷是利用日影的方位计时;漏壶和沙漏是利用水流和沙流的流量计时.东汉张衡制造漏水转浑天仪,用齿轮系统把浑象和计时漏壶联结起来,漏壶滴水推动浑象均匀地旋转,一天刚好转一周,这是最早呈现的机械钟.北宋元祜三年(1088)苏颂和韩公廉等创制水运仪象台,已运用了擒纵机构.1350年,意年夜利的丹蒂制造出第一台结构简单的机械打点塔钟,日差为15~30分钟,指示机构只有时针;1500~1510年,德国的亨莱思首先用钢发条取代重锤,缔造了用冕状轮擒纵机构的小型机械钟;1582年前后,意年夜利的伽利略发明了重力摆;1657年,荷兰的惠更斯把重力摆引入机械钟,创建了摆钟.1660年英国的胡克发明游丝,并用后退式擒纵机构取代了冕状轮擒纵机构;1673年,惠更斯又将摆轮游丝组成的调速器应用在可携带的钟表上;1675年,英国的克莱门特用叉瓦装置制成最简单的锚式擒纵机构,这种机构一直沿用在简便摆锤式挂钟中.1695年,英国的汤姆平发明工字轮擒纵机构;1715年,英国的格雷厄姆又发明了静止式擒纵机构,弥补了后退式擒纵机构的缺乏,为发展精密机械钟表打下了基础;1765年,英国的马奇发明自由锚式擒纵机构,即现代叉瓦式擒纵机构的前身;1728~1759年,英国的哈里森制造出高精度的标准航海钟;1775~1780年,英国的阿诺德缔造出精密表用擒纵机构.18~19世纪,钟表制造业已逐步实现工业化生产,并到达相当高的水平.20世纪,随着电子工业的迅速发展,电池驱动钟、交流电钟、机电械表、指针式石英电子钟表、数字式石英电子钟表相继问世,钟表的日差已小于0.5秒,钟表进入了微电子技术与精密机械相结合的石英化新时期.1.2设计目的1. 掌握各类计数器及将他们相连的方法2. 掌握多个数码管静态显示的原理与方法3. 掌握用FPGA技术的条理化设计方法4. 进一步掌握用Verilog硬件描述语言的设计思想5. 了解相关数字系统的设计1.3Verilog HDL硬件描述语言1.3.1Verilog HDL的发展过程与编程特点Verilog HDL是一种硬件描述语言(HDL:Hardware Discription Language),是一种以文本形式来描述数字系统硬件的结构和行为的语言,用它可以暗示逻辑电路图、逻辑表达式,还可以暗示数字逻辑系统所完成的逻辑功能.Verilog HDL就是在用途最广泛的C语言的基础上发展起来的一种件描述语言,它是由GDA(Gateway Design Automation)公司的PhilMoorby在1983年末首创的,最初只设计了一个仿真与验证工具,之后又陆续开发了相关的故障模拟与时序分析工具.1985年Moorby推出它的第三个商用仿真器Verilog-XL,获得了巨年夜的胜利,从而使得Verilog HDL迅速获得推广应用.Verilog HDL充沛保管了C语言简洁、高效的编程风格,其中有许多语句和C语言中的语句十分相似,如if语句、case语句等.1.3.2Verilog HDL的基本结构1)模块的基本结构模块是Verilog DHL语言的基本单位.一个模块可以年夜道代表一个完整的系统,也可以小到仅代表最基本的逻辑单位.模块内部具体行为的描述或实现方式的改变,其实不会影响该模块与外部之间的连接关系.一个Verilog模块可被任意多个其他模块所调用,但由于Verilog HDL所描述的是具体的硬件电路,一个模块代表具有特定功能的一个电路块,每当它被某个其他模块调用一次,则在该模块内部,被调用的模块将原原本本的复制一次.一个完整的Verilog HDL模块由以下五部份组成.(1)模块界说行.这一行以module开头,接着给出所界说模块的模块名,模块名是模块唯一的标识符;之后的括号内给出的是端口名列表,端口名列表是由模块的各个输入、输出和双向端口组成的一张端口列表,这些端口用来与其他模块进行连接;最后以分号结束.当无端口名列表时,括号可省去.(2)端口类型说明接在模块界说行后面的是对端口类型的说明,凡是呈现在端口名列表中的端口,都必需显示说明其端口类型.(3)数据类型说明Verilog HDL支持的数据类型有连线类和寄存器类两个年夜类,每个年夜类有细分为多种具体的数据类型.数据类型界说部份用来指定模块内用到的数据对象为寄存器型或连线型,除1位宽的wire类可缺省外,其他将在后面的描述中呈现的变量都应给出相应的数据类型说明.(4)描述部份本部份具体展开对模块功能的描述.(5)结束行结束行是用关键词endmodule标识表记标帜模块界说的结束.2)模块的描述在模块的功能描述中,可用下述方式描述一个设计:数据流方式;行为方式;结构方式;上述描述方式的混合.下面分别介绍模块的这几种描述方式.(1)数据流描述方式数据流型描述主要用来描述组合功能,具体由“assign”连续赋值语句来实现.(2)行为描述方式行为描述时一种高级语言使用到的方法,Verilog中的行为描述方式具有很强的通用性.行为描述是通过行为语句来实现的,行为功能可使用下述过程语句结构描述.Initial语句:此语句只执行一次.Always语句:此语句循环执行.(3)结构描述方式结构描述方式是通过实例进行描述的方法.它将Verilog中预界说的基本元件实例嵌入到语言中,监控实例的输入,一但其中任何一个发生变动,便重新运算并输出.(4)混合型描述方式在模块中,用户可以混合使用以上几种描述方式,也就是说,模块中可以包括门的实例、模块实例语句、连续赋值语句、always语句和initial语句以及它们的混合语句,而且它们之间可以相互包括.1.3.3Verilog HDL的条理设计实现过程用Verilog HDL进行硬件设计的过程实质上是把构成硬件系统的各功能模块进行Verilog描述,也可以使结构描述,前者偏重刻画模块所具有的行为特征,后者偏重反映模块内部的具体构造.通常一个硬件系统是由多个分歧的功能模块所组成的,因而总会存在这样一个模块,他用结构描述的方法,将构成硬件系统的所有功能模块连接起来,这个模块就是系统的顶层模块.相对顶层模块,其他的模块就是低一条理的模块.在对低一条理的模块进行描述时,如果有需要,可以同样用结构描述的方法,把模块的内部结构进一步具体的刻画出来,相对顶层模块而言,用于构造低一条理模块的结构单位就属于更低一个条理.因而随着设计过程的展开,一个硬件系统的构造逐渐由顶层走向底层,各个功能模块的内部结构逐渐获得深化和细化,整个设计过程因而被称之为一个自顶向下的分级设计过程.在这个自顶向下的设计过程的任何阶段,都可以利用仿真工具对处于设计过程中的系统描述进行性能评估与正确性检测.在自顶向下的设计过程中,对上层模块来说,只需要知道某个模块的名称与端口类型,就可把它作为自己的一个下层模块进行调用.至于下层模块的具体实现方式,或者从一种实现方式转换到另一种实现方式,都不会对上层模块的描述发生任何影响.这是自顶向下设计方法一个突出的优点.在设计过程中,通过仿真测试,如果发现性能不够理想,或者发现任何毛病,只需对存在问题的低层的描述或实现方式进行修改或调整,而不用对上层结构进行任何改变.所谓的顶层和底层都是相对的.在实际设计过程中,总是把以后正在实现的模块作为一个局部的顶层模块,在完成描述后,先独自对他进行仿真测试,在验证其正确性后在加入需要调用它的模块中,而成为整个系统设计中某一个条理的功能模块,一个年夜的电子系统设计就是这样从顶层究竟层,边设计,边仿真,并依据仿真结果,反复调整或优化的过程.1.4 Modelsim仿真工具ModelSim是业界最优秀的HDL语言仿真器.它提供最友好的调试环境,是唯一的单内核支持VHDL和Verilog混合仿真的仿真器.是作FPGA/ASIC 设计的RTL级和门级电路仿真的首选,它采纳直接优化的编译技术、Tcl/Tk 技术、和单一内核仿真技术,编译仿真速度快,编译的代码与平台无关,便于呵护IP核,个性化的图形界面和用户接口,为用户加快调错提供强有力的手段.全面支持VHDL和Verilog语言的IEEE 标准,支持C/C++功能调用和调试.ModelSim专业版,具有快速的仿真性能和最先进的调试能力,全面支持UNIX(包括64位)、Linux和Windows平台.主要特点:RTL和门级优化,本地编译结构,编译仿真速度快;单内核VHDL和Verilog混合仿真;源代码模版和助手,项目管理;集成了性能分析、波形比力、代码覆盖等功能;数据流ChaseX;SignalSpy;C和Tcl/Tk接口,C调试.是业界唯一单一内核支持VHDL、 VerilogHDL和SystemC混合仿真的仿真器同时也支持业界最广泛的标准如Verilog2001、SystemVerilog等,内部集成了用于C/C++,PLI/FLI和SystemC的集成C调试器.支持众多的ASIC和FPGA厂家库,可以用于FPGA 和ASIC设计的RTL级和门级电路仿真.下面图1.1为modelsim的主界面.图1.1modelsim主界面ModelSim最年夜的特点是其强年夜的调试功能:先进的数据流窗口,可以迅速追踪到发生不定或者毛病状态的原因;性能分析工具帮手分析性能瓶颈,加速仿真;代码覆盖率检查确保测试的完备;多种模式的波形比力功能;先进的SignalSpy功能,可以方便地访问VHDL 或者VHDL和Verilog混合设计中的底层信号;支持加密IP;可以实现与Matlab的Simulink的联合仿真.ModelSim分几种分歧的版本:SE、PE、LE和OEM,其中SE是最高级的版本而集成在 Actel、Atmel、Altera、Xilinx以及Lattice等FPGA厂商设计工具中的均是其OEM版本.SE版和OEM版在功能和性能方面有较年夜分歧,比如对年夜家都关心的仿真速度问题,以Xilinx公司提供的OEM版本ModelSimXE为例,对代码少于40000行的设计,ModelSimSE 比ModelSimXE 要快10倍;对代码超越40000行的设计,ModelSimSE要比ModelSimXE快近40倍.以下列表介绍了OEM版本(以Xilinx公司提供的ModelSimXE版本为例)与ModelSimSE版本之间的不同.ModelSimSE支持PC、UNIX和LINUX混合平台;提供全面完善以及高性能的验证功能;全面支持业界广泛的标准;MentorGraphics公司提供业界最好的技术支持与服务.第2章数字电路设计方法2.1数字系统设计简介2.1.1数字系统从概念上讲,凡是利用数字技术处置和传输信息的系统都可以称为数字系统.通常把门电路、触发器等称为逻辑器件.将由逻辑器件构成,能执行某单一功能的电路,如计数器、译码器、加法器等称为逻辑功能部件,把有逻辑功能部件组成的能实现复杂功能的数字电路称为数字系统.复杂的数字系统可以分割称为若干个子系统,例如,计算机就是一个内部结构相当复杂的数字系统.近几年来,IC技术的发展日新月异,而最具有代表性的IC芯片主要包括以下几类:微控制芯片(MCU);可编程逻辑器件(PLD);数字信号处置器(DSP);年夜规模存储芯片(RAM&ROM).这几类器件在最近20年均取得了长足的发展,无论是芯片的规模还是性能都有了巨年夜的提高,构成了现代数字系统的基石.2.1.2数字系统设计方法数字系统一般由控制电路、多个受控电路、输入/输出电路、时基电路等几部分构成,如图2.1所示.图2.1数字系统设计方法构成图一般来说,电子系统的设计有两种思路,一种是自下而上的设计思路,一种自上而下的设计思路.(1)自下而上的设计自下而上的设计,也可称为自底向上的设计,过程从最底层设计开始.设计系统硬件时,首先选择具体的元器件,用这些元器件通过逻辑电路设计,完成系统中各自力功能模块的设计,再把这些功能模块连接起来,总装成完整的硬件系统.(2)自上而下的设计自上而下的设计,也可称为自顶向下的设计.它是目前经常使用的数字系统设计方法,也是基于芯片的系统设计的主要方法.它在功能划分、任务分配及设计管理上有一定的长处.2.1.3数字系统设计流程数字系统的设计可分为四个条理,即系统级设计、电路级设计、芯片级设计和电路板级设计.相应的,从提出设计要求到完成系统制品,数字系统设计可分为以下几个步伐:系统设计、电路设计、芯片设计、PCB设计、结构设计及电路调试和系统调试,如图2.2所示.图2.2数字系统设计流程图2.1.4数字系统设计准则进行数字系统设计时,通常需要考虑多方面的条件和要求.如设计的功能和性能要求,元器件的资源分配和设计工具的可实现性,系统的开发费用和本钱等.虽然具体设计的条件和要求千差万别,实现方法也个各相同,但数字系统设计还是具备一些共同的方法和准则.1)分割准则自顶向下设计方法或其他条理化设计方法需要对系统功能进行分割,然后用逻辑语言进行描述.分割过程中,若分割过粗,则不容易用逻辑语言表达;若分割过细,则会带来不需要的充沛和繁琐.因此,分割合适与否对系统设计是否方便有着至关重要的影响.2)系统的可观测性一个系统除引脚上的信号外,系统内部的状态也是需要测试的内容.因此,在系统设计中,应该同时考虑功能检查和性能的测试,即系统观测性的问题.3)系统的稳定性设计时应注意采用办法防止竞争和增加系统稳定性.4)最优化设计设计中罕见的最优化目标有:(1)器件资源利用率最高;(2)系统工作速度最快,即延时最小;(3)布线最容易.2.2有限状态机2.2.1有限状态机简介有限状态机(FSM)又称为有限状态自念头或简称状态机,是暗示有限个状态以及这些状态之间的转移和举措的数学模型.一般来说,除输入部份和输出部份外,状态机还含有一组具有“记忆”功能的寄存器,这些寄存器的功能是记忆有限状态机的内部状态,他们常被称为状态寄存器.其中,寄存器逻辑的功能是存储有限状态机的内部状态;而组合和逻辑又可分为次态逻辑和输出逻辑两部份,次态逻辑的功能是确定有限状态机的下一个状态,输出逻辑的功能是确定有限状态机的输出.在实际应用中,根据有限状态机的输出信号是否与输入信号有关,将其分为Moore(莫尔)型有限状态机和Mealy(米里)型有限状态机两种类型.Moore型状态机输出信号仅与以后状态有关,如图2.3.即可以把Moore型有限状态的输出看成是以后状态的函数.Mealy型状态机输出信号不单与以后状态有关,而且还与输入信号有关,如图2.4即可以把Mealy型状态机的输出看成是以后状态和输入信号的函数.图2.3Moore 函数图图2.4Mealy 函数图需要注意的是Mealy 型状态机的输出是以后状态和输入信号的函数,它的输出是在输入变动后立即发生的,不依赖时钟的同步.而Moore 型状态机仅为以后状态的函数,这类状态机在输入发生变动后,还必需等候时钟的到来,时钟使状态发生变动才招致输出的变动,所以比Mealy 要多等候一个时钟周期.2.2.2有限状态机的编码方案在状态机的编码方案中,有两种重要的编码方法:二进制编码和一位热码(One —Hot)编码.在二进制编码的状态机中,状态位(B)与状态(S)的数目之间的关系为B=log2S,如两位状态位就有00,01,10,11四个分歧状态,它们在分歧的控制信号下可以进行状态转换,但如果各触发器又没有准确地同时改变其输出值,那么在状态01变到10时则会呈现暂时的11或00状态输出,这类险象可能使整个系统造成不成预测的结果.这时,采纳格雷码二进制编码是特别有益,在该编码方案中,每次仅一个状态位的值发生变动.一位热码编码就是用n 个触发器来实现n 个状态的编码方式,状态机中的每一个状态都由其中一个触发器的状态来暗示.如4个状态的状态机需4个触发器,同一时间仅一个状态位处于逻辑1电平,四个状态分别为:0001、0010、0100、1000.在实际应用中,根据状态机的复杂水平、所使用的器件系列和从非法状态退出所需的条件来选择最适合的编码方案,使之能确保高效的性能和资源的利用.对复杂的状态机,二进制编码需用的触发器的数目比一位热码编码的少.如100个状态的状态机按二进制编码仅用7个触发器就可以实现,而一位热码编码则要求100个触发器.另一方面,虽然一位热码编码要求用较多的触发器,但逻辑下一个逻辑状态 状态 寄存器 输出 逻辑输入 激励 以后状态 输出 时钟信号上通常相对简单些.在二进制编码的状态机中,控制从一个状态转换到另一个状态的逻辑与所有7个状态位以及状态机的输入均有关.这类逻辑通常要求到状态位输入的函数是多输入变量的.然而,在一热恋位编码的状态机中,到状态位的输入经常是其它状态位的简单函数.站在器件结构的角度,分歧结构支持其确定的编码类型.MAX+plus II编译法式对所采纳的器件系列自动地选择最合适的编码方法(除非在设计文件中规定了具体的编码方案).例如,FLEX 7000器件系列是寄存器增强型(Register-intensive),以这类器件为对象的状态机最好选用一位热码编码方案来实现.由于一位热码编码的状态机降低了送到每一个状态位的逻辑电路的复杂水平,因而可提高用FLEX 7000器件实现的状态机的性能.MAX 5000和MAX 7000器件系列最适合二进制状态机编码方案.这两类器件都能够利用共享和并联的扩展乘积项有效地实现复杂的逻辑函数.因此,在这两类器件小,可以容纳复杂的组合逻辑函数而不会浪费资源或损失性能.2.2.3有限状态机的一般设计步伐用Verilog HDL进行有限状态机的设计时,主要是用always和case语句来描述模块的功能,一般来说,它们可以采纳以下几个步伐来进行:(1)通过逻辑笼统,得出状态转换图或状态表首先,通过分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数,通常是把设计给定的条件作为输入变量,把获得的结果作为输出变量;然后,界说输入、输出逻辑状态的含义,并将电路状态顺序编号;最后,依照要求列出电路的状态转换表或画出状态转换图就可以了.(2)状态化简初度确定的状态,通常会呈现重复的状态,即它们在相同的输入下转换到同一状态去,并获得一样的输出.这样的状态可以合并为一个.电路的状态数越少,存储电路也就越简单.状态简化的目的就是要将重复的状态尽可能的合并,以获得最简单的状态装换图.(3)状态分配状态分配又称状态编码.通常有很多编码方法,编码方案选择适当,设计的电路可以很简单;反之,选的欠好,则设计的电路就会复杂很多.实际设计时,需综合考虑电路复杂度与电路性能之间的折中.在触发器资源丰富的FPGA或ASIC设计中,采纳独热编码,既可以使电路性能获得保证,又可充沛利用触发器数量多的优势.(4)根据画好的状态转换图或状态表,用Verilog HDL编写法式.用Verilog HDL来描述有限状态机,通过使用always块语句和case(if)等条件语句及赋值语句即可方便实现,而不用去考虑逻辑化简等问题,那些问题可以通过计算机自动完成.第3章数字钟的条理化的设计3.1功能要求设计一个具有时、分、秒计时功能的电子钟电路.依照条理化的设计方法将数字钟的功能划分为三个功能块:计时电路,显示电路,和扩展电路.要求在准确计时的基础上具有校时、校分的功能,按时闹钟的功能和整点报时的功能.3.2数字钟系统的工作原理向秒计数器提供秒脉冲信号,秒计数器记满60后向分计数器进位,分计数器记满60后向小时计数器进位,小时计数器依照24进制规律计数.计数器的输出经译码器送显示器,即显示时间.计时呈现误差可以用校时电路进行校时、校分.在计时主体电路正确运行的况下,进行功能扩展,实现仿电台报时和闹钟功能.3.3模块的设计数字钟可以划分为三个功能块:1.计时电路;2.显示电路;3.扩展电路.这些模块又可分割为更小的模块.计时电路包括校时电路和计数器两个部份.计数器的功能是完成小时、分钟、秒钟的计时,因此又可继续分割为二十四进制和六十进制计数器;校时电路的作用是对小时和分钟的误差进行调整,可设置两个按键,分别予以控制.显示电路的作用是将计时电路发生的几十只在数码管上进行显示,通过七段译码后,驱动LED数码管,然后在计时电路正确的情况下实现两个扩展功能.设计图如图3.1图3.1模块设计3.4 法式设计3.4.1.计时电路设计(1)六十进制计数器.module cnt60(clk,qs,co);input clk;output[7:0] qs=0;output co=0;reg[7:0] qs;reg co;always @(posedge clk)beginif(qs[7:4]!=4'b0101)beginif (qs[3:0]==4'b1001) beginqs[7:4]<=qs[7:4]+4'b0001;qs[3:0]<=4'b0000;co<=1'b0;endelsebegin qs[7:4]<=qs[7:4];qs[3:0]<= qs[3:0]+4'b0001;co<=1'b0;endendelse。

基于FPGA的自动打铃系统的设计与实现

自动打铃系统设计说明书学生姓名:罗衡学号:14092500060专业班级:电子09—2BF报告提交日期:2011-11—28 湖南理工学院物电学院目录一、题目及要求简介 (1)1.设计题目 (1)2.总体要求简介 (1)二、设计方案说明 (1)三、各部分功能介绍及程序 (2)1.系统框图 (2)2。

选择的FPGA芯片及配置·······································23.各模块(元件)说明 (2)四、仿真结果 (4)1。

计时进位····················································4 2。

手动校时····················································5 3。

VHDL实验报告自动打铃系统曹刚DOC

第二次实验自动打铃系统(14)姓名:曹刚学号:1228401082班级:12电子信息工程一.实验目的1、综合运用EDA技术,完成自动打铃系统的设计与操作;2、进一步熟悉EDA技术的开发流程,掌握文件编辑、编译、仿真、下载验证等环节的实现方法和应用技巧;3、通过本实践环节,培养科学和严谨的工作作风。

二.实验要求1.用6个数码管实现时,分、秒的数字显示;2.能设置当前时间;3.能实现上、下课打铃及起床铃、熄灯铃功能;4.能实现整点报时功能,并能控制启动和关闭;5.能实现调整打铃时间和间歇长短的功能;三.实验设计说明根据设计要求,可以将自动打铃系统的划分为以下几个模块:1.状态机:系统有多种显示模式,设计中将每种模式当成一种状态,采用用状态机来进行模式切换,将其作为系统的中心控制模块;2.计时调时模块:用于完成基本的数字钟功能;3.打铃时间设定模块:系统中要求打铃时间可调,此部分功能相对独立,单独用一个模块实现;4.打铃长度设定模块:用以设定打铃时间的长短;5.显示控制模块:根据当前时间和打铃时间等信息决定当前显示的内容;6.打铃控制模块:用于控制铃声音乐的输出;7.分频模块、分位模块、七段数码管译码模块等;以上各模块可用下图表示其间的联系。

四.实验原理用层次化设计的方法以VHDL语言编程实现以下功能:【1】具有“时”、“分”、“秒”计时功能;时为24进制,分和秒都为60进制。

【2】具有消抖功能:手工按下键盘到是否这个过程大概50ms左右,在按下开始到弹簧片稳,定接触这段时间为5-10ms,从释放到弹片完全分开也是5-10ms,在达到稳定接触和完全分开的微观过程中,电平是时高时低的,因此如果在首次检测到键盘按下时延时10ms再检测就不会检测到抖动的毛刺电平了。

64Hz的信号周期为15.6ms,正适合做消抖信号。

【3】具有校时和清零功能,能够用4Hz脉冲对“小时”和“分”进行调整,并可进行秒清零;【4】具有整点报时功能。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

长沙理工大学《计算机组成原理》课程设计报告学院计算机与通信工程专业网络工程班级 11-01 学号学生姓名指导教师陈沅涛课程成绩完成日期 2014年1月10日课程设计任务书计算机与通信工程学院网络工程专业课程设计成绩评定学院计通学院专业网络工程班级11-01班学号学生姓名指导教师陈沅涛完成日期2014年1月10日指导教师对学生在课程设计中的评价指导教师对课程设计的评定意见基于Verilog_HDL语言的整点智能响铃系统设计学生姓名:指导老师:陈沅涛摘要:本设计主要利用Verilog_HDL语言在EDA平台上设计整点响铃系统。

整点智能响铃系统走时精度高,稳定性好,实用方便,不需要经常调教,这种响铃具有时、分、秒计数显示功能,以24小时循环计时,时钟计数显示时有LED灯的花样显示,具有调节小时、分钟及清零的功能以及整点报时功能。

这次设计以Verilog_HDL语言和MAX+PLUS II为工具,实现整点智能报时。

系统分模块进行分析和设计,并给出相应的设计原理图和Verilog_HDL源程序,通过仿真实现预定功能。

关键词:;整点智能响铃系统;EDA;Verilog_HDL;MAX +plusⅡBased on Verilog_HDL language intelligentalarm system design of the hourStudent Name: Supervisor: Chen YuantaoAbstract: This design mainly use Verilog_HDL language on EDA platform design hourly alarm system. The hour walking intelligent alarm system of highprecision, good stability, convenient and practical, don't need often set-up,this ring has when, minutes and seconds count display function, with24-hour cycle time, counting clock display LED lights of the pattern,according to adjust the hours, minutes and reset function and the hour ofthe function. The design to Verilog_HDL language and MAX + PLUS II is thetool, realize intelligent tell the time of the hour. Points module system foranalysis and design, and gives the corresponding design principle diagramand Verilog_HDL source program, reservation function was achieved by thesimulation.Key words: Intelligent alarm system design of the hour;EDA;Verilog_HDL;MAX +plus Ⅱ目录1 引言 (7)1.1 课题背景及意义 (7)1.2课程设计目的 (8)1.3课程设计内容 (8)2 理论基础 (9)2.1 Verilog HDL语言概述 (9)2.2 MaxplusII简介 (10)3 整点智能响铃系统的设计方案 (12)3.1设计功能及分析 (12)3.2 系统总体框架结构 (12)4 系统模块的设计与仿真 (13)4.1秒计数器模块 (13)4.1.1模块的具体实现及功能介绍: (13)4.1.2秒计数器模块仿真: (13)4.2 分钟计数器模块: (14)4.2.1模块的具体实现及功能介绍: (14)4.2.2分钟计数器模块的仿真图: (14)4.3时钟计数器模块: (15)4.3.1模块的具体实现及功能介绍: (15)4.3.2小时计数器模块的仿真图: (15)4.4整点报时模块 (16)4.4.1模块的具体实现及功能介绍: (16)4.4.2整点报时模块的仿真图: (16)5整点智能响铃系统的仿真与实现 (17)6小结 (20)7.致谢 (21)参考文献 (22)附录:整点智能响铃系统设计源程序清单 (23)1引言现在,人类社会已进入到高度发达的信息化社会。

信息化社会的发展离不开电子信息产品开发技术、产品品质的提高和进步。

电子信息产品随着科学技术的进步,其电子器件和设计方法更新换代的速度日新月异。

实现这种进步的主要原因就是电子设计技术和电子制造技术的发展,其核心就是电子设计自动化(EDA,Electronics Design Automation)技术,EDA技术的发展和推广应用又极大地推动了电子信息产业的发展。

为保证电子系统设计的速度和质量,适应“第一时间推出产品”的设计要求,EDA技术正逐渐成为不可缺少的一项先进技术和重要工具。

本设计主要利用Verilog_HDL语言在EDA平台上设计整点响铃系统。

整点智能响铃系统走时精度高,稳定性好,实用方便,不需要经常调教,这种响铃具有时、分、秒计数显示功能,以24小时循环计时,时钟计数显示时有LED灯的花样显示,具有调节小时、分钟及清零的功能以及整点报时功能。

总的程序由几个各具不同功能的元模块程序拼接而成,其中包括秒计数器模块,分钟计数器模块,小时计数器模块和整点报时模块并且使用MaxplusII软件进行电路波形仿真,下载到EDA实验箱进行验证。

1.1 课题背景及意义随着EDA[1]仿真技术的发展,数字系统的设计技术和设计工具发生了深刻的变化。

利用硬件描述语言(VHDL)[2]对数字系统的硬件电路进行描述是EDA的关键技术之一。

VHDL语言是目前主流的硬件描述语言,它具有很强的电路描述和建模能力,具有与具体电路无关和与设计平台无关的特性,在语言易读性和层次化结构方面表现出强大的生命力和应用潜力。

随着科学的日益进步,我们对数字钟的需求也越来越大。

因为人们也越来越忙,时刻都在受着时间的影响,我们。

我们采用了先进的EDA技术,MAX +plusⅡ工作平台和VHDL语言[3],设计了多功能数字钟系统,并对系统进行了仿真验证。

通过仿真及验证的结果分析,完全适应智能化发展要求。

不但实现的报时定时各种的功能,大大提高了时间的准确度,而且提高了系统的先进性和可靠性。

能实现控制器的系统编程。

采用这种器件开发的数字系统其升级与改进非常方便。

这一控制电路,结构简单、性能稳定、操作方便、抗干扰能力强。

将它应用于校园与各地,稳定性高,准确性强。

1. 2课程设计目的作为网络专业的学生,通过这次EDA方面的课程设计,可以提高我们对EDA领域及通信电路设计领域的认识,有利于培养我们在通信电路EDA方面的设计能力。

同时可以促使我们独立地运用Verilog_HDL语言、EDA相关知识和Maxplus2仿真软件编制一个简单的课程设计。

设计过程的复杂加老师的严格要求有益于培养我们严谨的工作作风。

本次课题是计算机组成原理的课程设计,旨在通过对所需功能芯片的设计与实现来巩固以前所学的计算机硬件基础知识,同时也提高动手实践的能力,还有为将来进行更大规模更复杂的开发积累经验。

1.3课程设计内容本次设计以智能打铃为主,实现时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分——60进制计数,即从0到59循环计数,时钟——24进制计数,即从0到23循环计数,以及时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字钟真正具有使用功能。

我们可以通过实验板上的键7和键4进行任意的调整,因为我们用的时钟信号均是1HZ的,所以每LED灯变化一次就来一个脉冲,即计数一次。

清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。

可以根据我们自己任意时间的复位蜂鸣器在整点时有报时信号产生,蜂鸣器报警,产生“滴答.滴答”的报警声音。

LED灯在时钟显示时有花样显示信号产生。

即根据进位情况,LED不停的闪烁,从而产生“花样”信号。

2 理论基础2.1 Verilog HDL语言概述Verilog HDL是一种硬件描述语言(HDL:Hardware Discription Language),是一种以文本形式来描述数字系统硬件的结构和行为的语言。

Verilog HDL就是在用途最广泛的C语言的基础上发展起来的一种件描述语言。

Verilogs是由Gateway设计自动化公司的工程师于1983年末创立的。

该公司的菲尔·莫比(Phil Moorby)完成了Verilog 的主要设计工作。

1990年,Gateway设计自动化被Cadence公司收购。

1990年代初,开放Verilog国际组织(即现在的Accellera)成立,Verilog面向公有领域开放。

1992年,该组织寻求将Verilog纳入电气电子工程师学会标准。

最终,Verilog成为了电气电子工程师学会1364-1995标准,即通常所说的Verilog-95。

设计人员在使用这个版本的Verilog的过程中发现了一些可改进之处。

促使Verilog进行了修正和扩展,这部分内容后来被提交给电气电子工程师学会。

后来被称为电气电子工程师学1364-2001标准,即通常所说的Verilog-2001。

Verilog-2001是对Verilog-95的一个重大改进版本,它具备一些新的实用功能,例如敏感列表、多维数组、生成语句块、命名端口连接等。

目前,Verilog-2001是Verilog的最主流版本,被大多数商业电子设计自动化软件包支持。

2005年,Verilog再次进行了更新,即电气电子工程师学会1364-2005标准。

该版本只是对上一版本的细微修正。

这个版本还包括了一个相对独立的新部分,即Verilog-AMS。

这个扩展使得传统的Verilog可以对集成的模拟和混合信号系统进行建模。

2009年,IEEE 1364-2005和IEEE 1800-2005两个部分合并为IEEE 1800-2009,成为了一个新的、统一的SystemVerilog硬件描述验证语言(hardware description and verification language, HDVL)。

Verilog HDL的最大特点就是易学易用,如果有C语言的编程经验,可以在一个较短的时间内很快的学习和掌握,因而可以把Verilog HDL内容安排在与ASIC设计等相关课程内部进行讲授,由于HDL语言本身是专门面向硬件与系统设计的,这样的安排可以使学习者同时获得设计实际电路的经验。