cadence psd142入门教程

cadence入门教程

Cadence 系列软件从schematic到layout入门一.客户端软件使用及icfb启动要使用工作站上的软件,我们必须在PC中使用xwinpro等工具连接到工作站上。

从开始菜单中,运行xwinpro的xSettings,按照下图设置:点击上图的Settings在出现的窗口中按如下设置(connect host选择为192.168.1.137):设置完后,从开始菜单中运行xwinpro的xsessions,应该就可以进入登陆界面,用户名为user1,密码为root。

二、SchematicCadence系列软件包含了电路图工具Schematic,晶体管级电路仿真工具Spectre,以及版图工具Virtuoso等。

一般来说,我们先用Schematic画好电路原理图然后进行仿真,最后用Virtuoso手动画版图或者直接进行版图综合,最后对版图进行L VS,DRC等验证。

在登陆进工作站后,点击鼠标右键,选择tools——>terminal,在弹出的terminal窗口中敲入命令icfb&就可以启动cadence了。

图1 icfb的主界面我们以建立一个反相器电路为例子:在icfb中,任何一个电路,不论是已经存在的可以引用的库,还是用户新建立的一个电路,都是一个library. 一个library一般有若干个Cell(单元电路),每个cell有若干个schematic(电路原理)和若干个layout(版图)。

所以,我们要做的第一步,就是先创建一个自己的“库”,File菜单->new->library图2 新建一个库的界面从这个新建一个library的界面,我们必须输入新建立的库的名称,并且选择好这个库应该存放的目录,然后注意看右边的三个选项,关于新建立的库是否需要链接到Technology File 的问题。

首先,这个Technology File一般是指工艺库,由Foundry提供。

cadence入门教程

这里开始介绍版图。 我们是要画这个电路的版图:

其他的原理图都可以关掉。记得保存。 版图要注意文件结果,不要放错了,否则后面比较麻烦,现在文件结构如下:

现在要新建一个版图的 Cell,最好是将版图文件和你要建立版图对应的原理图放在同一 个 Cell 里面,过程如下:

如果没有显示 net 信息,这可以通过下面的方法显示。

点击 results 的 annotate 的 net names。

这里面是些显示的设置,具体这里不介绍了。 下面看波形:将 net18 和 net22 的波形都显示出来:

显示出来的波形如下:

然后观察波形,看是否满足原理图的逻辑, 点击这个 可以有很多的仿真模式,我们使用的瞬态仿真是 tran,其他的我也不介绍了,stop time 填 10n, 因为上面信号源的设置是 2ns 的周期,显示 5 个周期就差不多了。然后选中 conservative, 表明是最高精度的分析,然后选中 enabled,使能 tran 仿真,点击 OK 退出。可以发现仿真 窗口发生了变化如下:

同样的原理放置 gnd。记得使用 i 来添加 instance 的方法。vdc 是直流电压,也在 analogLib 库里面,同样放置,vpulse 是方波发生器,也在 analogLib 库里面,同样放置,放完后如下 图:

然后就是仿真 mos 管了,使用的是 tsmc18rf 的库,元件名是 nmos2v 和 pmos2v

上面显示的是文件管理窗口,可以看到文件存放的结构,其中 Library 就是文件夹,Cell 就 是一个单元,View 就是 Cell 的不同表现形式,比如一个 mos 管是一个 Cell,但是 mos 管有 原理图模型,有版图模型,有 hspice 参数模型,有 spectre 参数模型等,这就列举了 Cell 的 4 个 View。他们之间是树状的关系,即,Library 里面有多个 Cell,一个 Cell 里面有多个 View。 应该保持一个好习惯就是每个工程都应该建立一个 Library,Cell 和 View 之间的管理将在后 面介绍。

cadence软件画版图操作

cadence软件画版图操作cadence软件操作1、原理图设计电路的原理图设计和许多的电路设计软件是类似的,这⾥⼤致介绍⼀下基本的操作。

⾸先是新建⼀个cell的原理图:library manager》file》new》cellview》这⾥设置元件名以及类型。

这⾥也可以选择其他类型。

其中⽐较重要的就是schematic和layout,后⾯也会提到。

这要记住如何新建。

这⾥使⽤的tool是Composer-schematic,⽽后⾯的版图设计采⽤virtuoso即可设计版图。

新建完成后会⾃动打开编辑器。

通过编辑,可以得到所需的电路。

这⾥看⼀下设计的基本界⾯。

和Multisim等电路软件类似,左侧是菜单栏,⽤于执⾏操作。

其中重要的有四个:导⼊元件、连线、标记、输⼊输出。

分别在图中的倒数第7、6、4、3,掌握这⼏个就可以绘制基本的原理图。

其中注意该软件的通⽤快捷键:q,在使⽤esc退掉其他指令后,选中某个⽬标,按q即可得到设计的属性。

对于新⼿⽽⾔,不能修改错误是难受的。

在q内可以修改所有设置的值。

2、前仿真前仿真,⾸先要有原理图。

步骤和前⾯的操作基本⼀致。

只不过加⼊了激励信号。

由于使⽤的是模拟仿真器,所以只能采⽤模拟信号源。

(数模混合仿真有时间再记录)注意,如果想要仿真⾃⼰的原理图,需要封装。

⼀⽅⾯可以将原理图内部的标识隔离,⼀⽅⾯⽅便区分顶层和⼦模块。

封装就是在design》create cellview》from cellview即可。

注意要区分保存和检查。

保存并未导⼊⼯程,在后⾯的操作中如果提⽰某个⽂件不⼀致,很有可能就是只是保存⽽没有检查。

在原理图设计界⾯的菜单栏第⼀项tools》analog environment可以进⼊仿真界⾯。

图中配置在使⽤模拟信号仿真时可以不更改。

分析⽤于选择仿真时间。

观察点就是选择要呈现的波形。

右下⾓的红绿灯可以⽤于开始仿真。

3、板图设计先看⼀下界⾯:常⽤功能:shift+z:缩⼩ctrl+z:放⼤(⼀般采⽤右键框选可以放⼤特定的区域)shift+k:清除尺⼦q:属性o:通孔选择p:路径连接shift+f:版图视图ctrl+f:元件视图其他的功能可以在左侧菜单栏⼀⼀验证,这⾥不再多说。

cadence入门指导

Cadence基本操作--Carfic文介绍C adence软件的入门学习,原理图的创建过程,本教程适合与初学着,讲得尽量的详细和简单,按照给出的步骤可以完全的从头到尾走一遍,本教程以最简单的共源放大器为例。

打开终端,进入文件夹目录,输入icfb &或者virtuoso&启动软件。

1.原理图绘制1.点击Tools的Library Manager,如图1图12.下一步,建立新的库File-New-Library,在name处取新库的名字(图2),并关联相应的工艺库,这次关联的工艺库是tsmc18rf(见图3,4)。

图2图3 图43.接下来在,新建库(CS)下面建立原理图,在manager中点击新建的库,再点击File-New-Cell View,并取名字,此处仍取名cs(图5)。

出现原理图(图6)图5 图6接下来可以进行原理图绘制,首先介绍几个快捷键:F:调节界面至最全最合适模式M:移动器件I:加入器件Q:调整器件参数W:连线C:复制器件R:旋转器件,在移动,复制和加器件的时候可以使用X:保存电路并且检查是否有error和warningL:给线标注名字,名字相同即相连,尽量不要取关键字的名字,如vdd!,gnd!等P:加pin脚,在做symbol的时候使用,pin的名字和线的名字一样的时候,默认相连接。

E:进入symbol下一层电路shift+M:移动器件不会影响线shift+W:粗线shift+R:镜像器件ctrl + E:返回上一层电路图4.第一步,先按I(图7),再选择tsmc18rf库,在cell找nmos2v(在此工艺下的器件名,有些工艺是nch),并在view选择symbol,即可添加(图8)。

图7图8同样,可以加入此工艺库下的pmos,电阻和电容等,在简单仿真的时候,除晶体管外的元件(电压源,电流源)可以使用虚拟模拟元件,都在在analogLib下面。

以添加DC电压源步骤为例,按I,再选择analogLib库,在cell中找到vdc,并在view选择symbol(图9)。

CADENCEPSD142入门教程

以下是几种常用属性的名称: PATH:器件在原理图中的标号,防止元件时系统会自动添加,如I10 SIGNAL_NAME:信号名,添加信号名时系统自动生成,亦可作为属性添加 LOCATION:元件所属的物理器件的名称,如U2 BODY_NAME:器件的物理名称,如74LS00 点击Text>Property出现添加属性对话框,出现属性的名称和值,点击OK,鼠标指针变成 十字,点击想要添加属性的器件、 管脚或网络,完成一次添加。

图3.3 也可直接在命令窗口中输入add命令

图3.4

PPT文档演模板

图3.2 选择器件对话框

CADENCEPSD142入门教程

3.1.3 画线 concept-HDL的画线有两种方式,一种为手动画线(Draw)在连线的同时,点击右键可

输入信号名(网络标号),另一种是自动画线(Route),分别点击线的起点和终点,线将 自动连接。这两种都在wire菜单中,在Draw方式下双击左键或点击右键>next画下一条线, 紧接着右键>done则结束本次画线。

跟踪网络的方法是Tools>Global Navigate,出现对话框后,点击任意wire, 则与该wire相连网络会被加入列表,点击 列表中的任意网络均会被高亮(Highlight) 显示.

项目后,在项目管理器中点击 Design Entry进入Concept-HDL, 界面如图3.1

PPT文档演模板

图3.1

CADENCEPSD142入门教程

在图3.1中的标题栏内显示的是将要编辑的原理图文件信息,即:mydesign.sch.1.1。它的 格式为〈Cell〉. 〈View〉. 〈Version〉. 〈Page〉。该处的Version并不是原理图经过多次 改后每次的版本号,而是将该原理图作为一个单一的逻辑功能元件时,出现在原理图中的 元件符号版本。

cadence入门教程PPT课件

IC设计基础

• 集成电路制造过程示意图:

第2页/共163页

IC设计基础

• 集成电路设计域主要包括三个方面: 行为设计(集成电路的功能设计) 结构设计(逻辑和电路设计) 物理设计(光刻掩模版的几何特性和物 理特性的具体实现)

第3页/共163页

IC设计基础

• 集成电路设计层次主要包括五个层次:

(1)系统级 (2)算法级 (3)寄存器传输级(RTL级) (4)逻辑级 (5)电路级

物理工具主要实现物理布局布线。 逻辑工具基于网表、布尔逻辑、传输时序等概念。 该两部分由不同工具承担,利用标准化的网表文件进行数据交换。

第21页/共163页

EDA概述

• EDA应用于三方面: 印制电路板的设计(PCB) 可编程数字系统设计(CPLD、 FPGA、SOPC) IC设计(ASIC, Soc)

EDA概述

• Synopsys公司简介:

是为全球集成电路设计提供电子设计自动化 (EDA)软件工具的主导企业。为全球电子市场提供技 术先进的IC设计与验证平台,致力于复杂的芯片上系 统(SoCs)的开发。总部设在美国加利福尼亚州 Mountain View,有超过60家分公司分布在北美、 欧洲、日本与亚洲。

合设计,嵌入式系统设计,软硬件系统协同设计,系统芯片设计,可编程逻辑器件和可编程系统芯片设计, 专用集成电路设计等

第13页/共163页

EDA概述 • 高级硬件描述语言的完善和IP(Intellectual Property)芯核被广泛使

用,使得电子系统和设计方式发生了根本性的转变。 • IP是集成电路知识产权模块的简称,定义为:经过预先设计、预先验证,

EDA概述

3、全定制IC设计工具

Virtuos Schematic Composer Analog Design Environment Virtuos Layout Editor Spectra Virtuoso Layout Synthesizer Assura dracula Diva

cadence基本使用学习

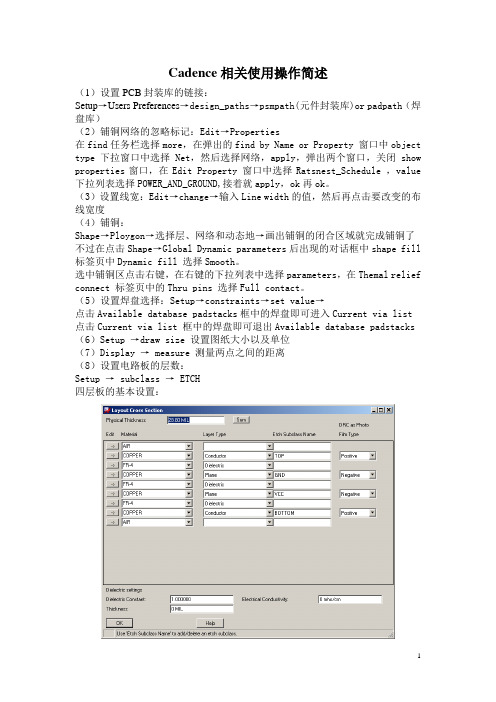

Cadence相关使用操作简述(1)设置PCB封装库的链接:Setup→Users Preferences→design_paths→psmpath(元件封装库)or padpath(焊盘库)(2)铺铜网络的忽略标记:Edit→Properties在find任务栏选择more,在弹出的find by Name or Property 窗口中object type下拉窗口中选择Net,然后选择网络,apply,弹出两个窗口,关闭show properties窗口,在Edit Property 窗口中选择Ratsnest_Schedule ,value 下拉列表选择POWER_AND_GROUND,接着就apply,ok再ok。

(3)设置线宽:Edit→change→输入Line width的值,然后再点击要改变的布线宽度(4)铺铜:Shape→Ploygon→选择层、网络和动态地→画出铺铜的闭合区域就完成铺铜了不过在点击Shape→Global Dynamic parameters后出现的对话框中shape fill 标签页中Dynamic fill 选择Smooth。

选中铺铜区点击右键,在右键的下拉列表中选择parameters,在Themal relief connect 标签页中的Thru pins 选择Full contact。

(5)设置焊盘选择:Setup→constraints→set value→点击Available database padstacks框中的焊盘即可进入Current via list 点击Current via list 框中的焊盘即可退出Available database padstacks (6)Setup →draw size 设置图纸大小以及单位(7)Display → measure 测量两点之间的距离(8)设置电路板的层数:Setup → subclass → ETCH四层板的基本设置:(9)设置好相应的层显示,然后manufacture→artwork→添加相应的层工艺文件详细设置情况见笔记本。

Cadence快速入门教程

Cadence软件不同于Altium Desginer软件,尤其在集成库方面有很大的区别,AD的封装集成库可以包含多个,而Cadence每个元器件的封装是独立的,在绘制封装的过程中,需要先利用Pad Designer添加焊盘,之后利用PCB Editor绘制元件的封装,再在PCB Editor中绘制PCB,过程比较复杂。

其次,AD的一个工程文件即可直接绘制原理图与PCB,而Cadence软件则是独立的,画原理图利用Design Entry CIS,画焊盘利用Pad Designer,画PCB利用PCB Editor。

AD可以直接添加焊盘,而Cadence需要建立封装,再添加,过程较复杂。

但是,Cadence软件的功能十分强大,逻辑性更强,十分值得学习!CONTENTSCONTENTSPARTONE OrCAD Capture原理图设计利用Capture创建原理图工程-以创建一个STM32的最小系统为例:1、点击打开Design Entry CIS (图标如右图1所示),在弹出的Cadence Product Choices 对话框中 选择功能比较强大的OrCAD Capture CIS,单击OK 按钮,启动后的Capture CIS 初始界面如图2所示:2、执行菜单命令File--New--Project,进行新建工程,在弹出的New Project 对话框,在Name 栏输入EXERCISE_SCH ,选中最后一个Schematic 单选按钮,表示绘制原理图,如图3所示:图1软件图标图2OrCAD Capture CIS 的初始界面图3New Project 对话框3、在New Project对话框单击Browse选择文件保存路径,在Drives 处选择工程所在的盘路径,单击Create dir按钮,填入新建文件夹的名称,单击OK按钮,创建文件夹,其中文件夹可提前建好,直接选择路径即可,本例的文件夹名称为EXERCISE。

cadence-PCB-画图(傻瓜教程快速入门)

cadence画PCB板傻瓜教程(转帖)复制于某网站,谢谢。

拿出来分享吧,希望对初学者能有帮助,可以很快了解Cadence的使用,谢谢共享者。

一.原理图1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用Design Entry CIS,点击Ok进入Capture CIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!)3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

cadence使用教程

cadence使用教程Cadence是一种电路设计和仿真软件,非常适合电子工程师用于电路设计和分析。

在本教程中,我们将介绍如何使用Cadence进行基本的电路设计和仿真。

首先,打开Cadence软件,并新建一个新项目。

请确保你已经安装了Cadence软件,并且拥有一个有效的许可证。

在新项目中,你需要定义电路的基本参数,如电源电压、电阻值等。

可以通过绘制原理图的方式来完成这些参数的定义。

在绘图界面中,你可以选择不同的元件,包括电源、电阻、电容、电感等。

你可以使用菜单栏中的工具来放置和连接这些元件。

一旦电路图绘制完成,你可以对电路进行仿真。

首先,需要选择合适的仿真器。

Cadence提供了多种仿真器,如Spectre和HSPICE。

选择一个适合你电路的仿真器,并设置仿真参数,如仿真时间、仿真步长等。

在仿真之前,你首先需要对电路进行布局。

布局涉及将电路中的元件放置在芯片上,并根据布线规则进行连接。

Cadence提供了强大的布局工具,可以帮助你完成这个过程。

完成布局后,你可以进行后仿真。

后仿真涉及将布局好的电路导入到仿真器中,并进行仿真分析。

你可以查看电路的性能指标,如电压、电流和功耗等。

除了基本的电路设计和仿真,Cadence还提供了其他功能,如噪声分析、温度分析和优化设计等。

你可以根据需要选择适合的功能。

总的来说,Cadence是一个功能强大的电路设计和仿真软件。

通过本教程,你可以学会如何使用Cadence进行基本的电路设计和仿真。

希望这对你的电子工程项目有所帮助。

Cadence快速教程

一.原理图(ORCAD工具)1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用Design Entry CIS,点击Ok进入Capture CIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!)3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

完整word版cadence PCB 画图傻瓜教程快速入门

cadence画PCB板傻瓜教程(转帖)复制于某网站,谢谢。

拿出来分享吧,希望对初学者能有帮助,可以很快了解Cadence的使用,谢谢共享者。

一.原理图1.建立工程与其他绘图软件一样,OrCAD以Project来管理各种设计文件。

点击开始菜单,然后依次是所有程序—打开cadence软件—》一般选用Design Entry CIS,点击Ok进入Capture CIS。

接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。

2.绘制原理图新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。

点击上侧工具栏的Project manager(文件夹树图标)或者是在操作界面的右边都能看到进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。

1)修改原理图纸张大小:双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size中可以选择单位、大小等;2)添加原理图库:File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘;(注意:在自己话原理图库或者封装库的时候,在添加引脚的时候,最好是画之前设定好栅格等参数,要不然很可能出现你画的封装,很可能在原理图里面布线的时候通不过,没法对齐,连不上线!)3)添加新元件:常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。

右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。

Cadence PSD14.1 安装说明

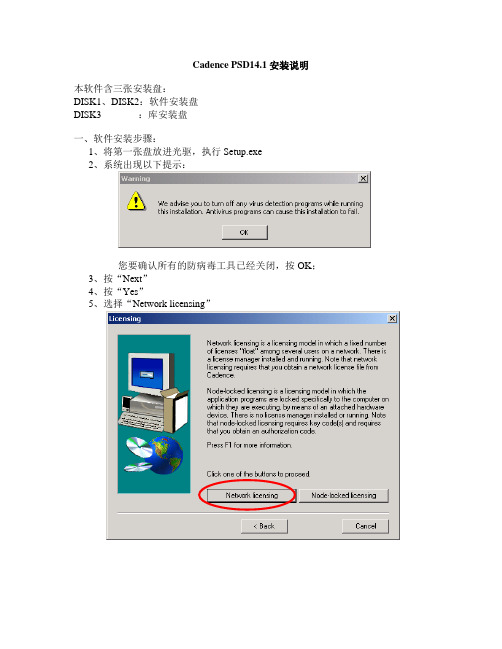

Cadence PSD14.1 安装说明本软件含三张安装盘:DISK1、DISK2:软件安装盘DISK3 :库安装盘一、软件安装步骤:1、将第一张盘放进光驱,执行Setup.exe2、系统出现以下提示:您要确认所有的防病毒工具已经关闭,按OK;3、按“Next”4、按“Yes”5、选择“Network licensing”6、出现下面提示,如需安装License Manager就按“Next”如果不安装License Manager,直接跳到第9 步。

7、这个路径一般不要改变,按“Next”8、如果已经得到License文件,就告诉它你的license.dat在哪里;否则什么也不要填,直接按“Next”,然后按“OK”。

待下个提示出现时,按“Finish”,这时Lisence Manager就安装完毕。

9、紧接着,将进入软件安装,按“Next”10、这时系统会问你,准备把License文件放在哪个目录,如果刚才你安装了License Manager的话,就用Browser把路径指到C:\cadence\license_manager路径下;如果你没安装,就什么也不做,直接按“Next”,然后按“OK”11、按“Next”12、按“Yes”13、按“OK”14、用“Browse”将安装路径改为“D:\cadence\PSD_14.1”;然后在上面的窗口里勾选所需安装的软件:PX3100 SPECCTRAQuest SI ExpertPX3500 PCB Librarian ExpertPX3700 PCB Design Expert with Concept HDL选择完,按“Next”15、选择默认存放数据的目录,一般可改为D:盘,按“Next”16、连续按两个“Next”,软件安装就正式开始了(当然,中间系统会提示您换第二张盘)。

17、安装完就可以按“Finish”结束了。

二、库的安装安装方法可参考上述软件的安装,只是把路径指到D:\Cadence\PSD_14.1就可以了。

Cadence新手简明教程

的孤岛。如果有没删除的孤岛或者没有将 shape更新到smooth,在光绘时就会报错。 3.如果删除过孤岛,在修线后相同区域又出 现孤岛,删除时会报cannot break shape to fragments。

45

制作pad 布线 检查、修改

制作symbol 设置规则Байду номын сангаас铺铜

导入网表 开始摆件

删除孤岛 后处理

46

47

不要忘记这里

48

单层模式

49

50

菜单栏

工具栏

命令窗口

状态栏

标题栏 控制面板 整体视图

51

F3(开始走线) F4(显示属性) F6(完成) F8(oops,取消上一步操作) F9(cancel,取消本次命令) SF3(推挤走线)SF6(移动)SF4(测距) Ctrl+F5(color选项卡)ctrl+d(删除) 滚轮上下(或F11、F12)放大缩小

35

36

37

元器件的坐标 报告复合封装中没有使 用的元件

38

39

40

41

42

勾选了inter tool communication之后,在PCB 布局模式下,选中原理图页的一个元件, PCB中对应的封装就会高亮,并且可以移动

43

44

Allegro是Cadence公司推出的先进 PCB 设计 布线工具。 Allegro 提供了良好且交互的工 作接口和强大完善的功能,和它前端产品 Capture的结合,为当前高速、高密度、多 层的复杂 PCB 设计布线提供了最完美解决方 案。

52

cadence入门教程

cadence入门教程(一)linux常用命令1、cd“cd FileName”是进入FileName文件夹。

“cd..”是进入上一层目录,主要那里是两个点。

2、ls这是最基本的文件命令,用以显示某一个目录中的文件。

可以在ls后加上所要观察的目录名称或文件的名称,如果你在下ls命令后没有接任何的目录名,它将会显示出目前目录中所有文件。

ls可以带一些参数,给予用户更多相关的信息:-a:在UNIX中若一个目录或文件名字的第一个字元为".",该文件为隐藏文件,使用ls将不会显示出这个文件的名字。

如cshell的初始化文件.cshrc,如果我们要察看这类文件,则必须加上参数-a。

-l:这个参数代表使用ls的长(long)格式,可以显示更多的信息,如文件存取权,文件拥有者(owner),文件大小,文件更新日期,或者文件链接到的文件、文件夹。

-F:给目录、可执行文件、符号链接以特殊的标记,在可执行文件后面加“*”、目录后面加“/”、符号连接后面加“@”,以方便用户区别。

3、cpcp命令用于将一个或多个文件复制成另一个文件或者是将其复制到另一个目录去。

cp有三种基本格式如下:cp source target将文件名为source的文件复制一份为文件名为target的文件。

如果target文件不存在,则产生文件名为target的文件,如果target文件存在,缺省时自动覆盖该文件。

cp file1file2…dir将文件file1file2...都以相同的文件名复制一份放到目录dir里面。

cp-r source target拷贝整个目录,将source目录下的所有文件和文件夹复制到target目录下。

cp命令常用的选项参数有:-i:交互(interactive)模式,当文件名为target的文件存在时,缺省情况下该命令会自动将原来target的内容覆盖掉,加上改选项将询问用户是否覆盖。

用户输入y(yes)则执行复制的动作,否则放弃复制。

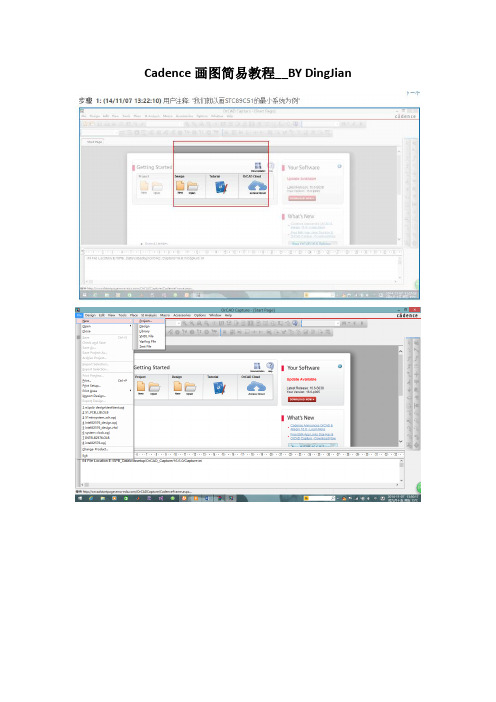

Cadence画图简易教程

Cadence画图简易教程__BY DingJian

如果画元器件,而这些元器件在官方的元器件库中并没有,那么我们就要自己新建一个器件库,即“library”

器件库是新建好了,可新建好的器件库中是没有器件的,接下就讲解一下如何在器件库中添加一个器件

步骤为,右击新建的器件库”library1.olb”,在弹出来的框中选择”New P art“

不同器件的参考符号是不一样的。

比如说主控芯片,CPU,它的参考符号就为”U“;电阻的参考符号就为”R“,电容的参考符号就是”C”

接下来我们就以STC89C51单片机为例

首先先画芯片的边框。

在顶部的菜单栏中选择”Place“下的”Rectangle”,或则在右边的快捷栏中选择

然后它会弹出如下选项框

我们所需要的器件画好了,就需要将它添加到我们的原理图中去

我们就要切换到原理图

点击“51Min.opj”选项卡,再点击“.\51min.dsn”前面的“+”,再点击“SCHEMATIC1”前面的“+”,找到“PAGE1”,双击即可。

接下来放置器件,步骤如下:点击菜单栏中“Place”->”Part”或者在右边的快捷栏中选择

调用时,找到所画的器件名称,双击,并拖到原理图上即可。

PS:在给元器件命名时,它的名字要有意义,这样方便查找。

以上就简单介绍了如何新建工程,器件库,以及从画元器件到添加到原理图上的过程。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

以灵活高效地将原理图输入计算机,并生成后继工具能够处理的数据。

1.13设计转换与修改管理 它实际上是原理图与PCB之间的一个纽带,负责将原理图中所表述的器件

连接关系及元件封装说明翻译成PCB所能接受地格式,并将PCB信息反馈到原 理图中,以保证原理图与PCB同步。这种由前到后和由后到前的设计数据的转换 与传递都是由这一环境完成的。

点击component>add,出现选择器件对话框,如图3.2

点击physical可以进行物理方式添加;如果元 器件不在Library列表中,可以点击search stack进 行库的添加。除了选择菜单命令外,还可以直接从 ADD工具栏中点击添加器件按钮。

图3.3 也可直接在命令窗口中输入add命令

脚。定义了组以后,我们可以对组内的任意元素进行操作。 有三种定义组的方法: *矩形框 *多边形框 * 表达式 这三种方法都可以在Group菜单中找到。创建一个组以前,我们应用一个字母给组命名。

否则下次定义的组会覆盖本次的结果。名称选择可以点击Group>Set Current Group,另外亦 可从工具栏中选择(图3.8)

图3.4

图3.2 选择器件对话框

3.1.3 画线 concept-HDL的画线有两种方式,一种为手动画线(Draw)在连线的同时,点击右键可

输入信号名(网络标号),另一种是自动画线(Route),分别点击线的起点和终点,线将 自动连接。这两种都在wire菜单中,在Draw方式下双击左键或点击右键>next画下一条线, 紧接着右键>done则结束本次画线。

图2.2

5、在图2.3中,左方框内为可供挑选的库,右方框内为项目要用到的库,点选左框内库以 “ADD”方式加入右框内,确认myproj_lib和standard库出现在Project Libraries中。

图2.3 如果缺少任意一个,则可能是输入的项目名或指定的路径不是新的,请点击previous回到 上一级修改。若无错误请点击“NEXT”。

6、输入一个设计名mydesign(一个工程项目可能有许多设计,每个设计又能包含 多原理图),如图2.4所示

图2.4

7、点击NEXT(确保所有的项都应被选中),如图2.5 8 点击Finish结束

图2.5

第三章 原理图设计

在这一章里将介绍原理图的输入工具Concept-HDL的具体使用方法。第一节介绍 Concept-HDL的常用工具;第二节结合一个实例说明工具的具体用法;第三节介绍层次 原理图的设计。

对于数字元件电源和地管脚已在chip.prt文件中进行了说明,为了取代chip.prt中文件 定义的POWER_PIN属性,可以在原理图中给元件添加POWER_GROUP属性。如图3.5

图3.5 3..1.6添加属性

Cadence中属性有四种类型: *system properties-由系统指定,分配给wires(nets)或pin。

在View菜单中有各种命令对图纸进行放大,缩小,局部放大,这些命令都有其对应的 热键,大家可以在下拉菜单中试一试。

3.1.8器件操作 在Component菜单中的命令可以对器件和属性进行编辑操作,这些命令也可以直接从

Edit工具栏中选取,如图3.7

图3.7

3.1.9组操作 组是原理图中某些元素的集合,这些元素可以是器件、网络、属性、注释,但不能是管

3.1.5总线信号名的命名规范 对于总线,命名格式为:信号名<最高位..最低位>。例如8位数据总线可命名为D<7..0>

给一条信号线添加总线信号名后,线会自动加粗以区别于一般信号线。

一个信号名后加后缀_N表示该信号是一个逻辑低有效的信号,在信号名后加上“\G” 或在信号名前加上”/”或“!”都表示该信号是一个全局有效的信号。

3.1.4 添加信号名 点击Wire>Signal Name …出现添加信号名对话框,依次键入要添加的全部信号名的名

称,在信号名所在的信号线上点击左键(使十字光标与信号名重合)则完成一次添加,添加 后的信号名会自动从对话框中消失。

如果用户不添加信号名,存盘时系统会自动给没有信号名的网络添加信号名,建议大家 自己对每个网络添加信号名以利于以后的PCB设计及仿真。

如果要添加多个器件,选择 Text>Attribute,再点击想要添加属 性的器件、管脚或网络,出现添加 属性列表,如图3.6

图3.6

Hale Waihona Puke 在图3.6的方框内填入想要添加的属性名称和值,然后在Visible中选择显示类型,是名称和 值都显示(Both),还是都不显示(None)或只显示一种(Name或Valuue),在Align中 选择对齐方式,点击OK,完成添加。 3.1.7常用的操作

图3.12

图3.11

在最高位(MSB)中填入3,在最低位(LSB)中填入0,Increment(步进值)中填入1,

用鼠标画一条线,从高位到低位穿过四条线,松开鼠标后,“?”会自动赋予位号。效果如

图3.13和3.14

图3.13

图3.14

*Merge:用来合并或分割总线。输入输出总线的宽度必须一致。(具体用法和规则可以 查看帮助文件(Help>on Line Book>printable version of Concept-HDL)

3.1.2 添加元件 Cadence中的元器件不仅包括一般的物理意义上的元器件实体,还可以包括逻辑上的

一些符号,如总线连接符号、总线拆分符号等,甚至连图纸也是作为元器件来添加的。 一个元器件有不同的版本(即视图),系统默认为1,添加元件时,点击右键选Version

来选择不同的视图符号。一个元器件也可以有多个封装类型,添加时,选择物理方式添加, 可以根据chips文件和part_table文件中定义的封装类型来添加元件。

1.14物理设计与加工数据的生成 这一环境主要完成PCB版图的设计(包括布局、布线)和生成后继制造与

加工PCB板所需的各种数据文件。

1.15高速PCB规划设计环境

在该环境中可以对PCB版图进行电磁兼容性(EMC)和信号完整性分析,并将 分析结果传递到Concept和Allegro,从而不断修改和完善PCB版图。该工具在信 号频率较高的PCB版图设计中尤为有用。

项目管理器 Project Manager

↓

原理图输入 Concept HDL

↓

设计转换(导出逻辑连接) Design Sync

↓

板级设计

Allegro/SPECTRA

↓

设计转换(导入物理封装) Design Sync

反标

↑

∣

高速PCB规划设计

∣

Floor planner

∣

∣

∣

图1.1 板级设计流程

CADENCE PSD14.2

入门教程

应用技术项目组

第一章 系统简介

§1.1 系统组成

1.11库 cadence板级设计系统按调用它的软件工具可分为如下四类: *符号库------ Concept-HDL调用 *信噪库------ SingNoise调用 *逻辑功能库-------VerilogXL调用 *物理库------Allegro调用

错误检查。检查类型包括电连接检查、图符检查、名字检查、其他检查,我们可以在Tools> Option>Check标签下进行设定。也可点击Tools>Check进行实时检查。此外Cadence还提供 了更强大地查错工具----Checkplus,它在Project Manager >Tools下,具体设定和使用,麻烦 大家查阅帮助文件(安装目录\doc\checkplus\checkplus.pdf)。 3.1.11点画命令

点画命令是Cadence独特的一种快捷方 式,可以直接用鼠标在屏幕上写特定的笔划, 不同的笔划表示不同的命令。例:Z表示放大, W表示整体显示。我们可以根据自己的习惯 来定义笔划。方法是在命令窗口中敲入 stroke,出现如图3.9的设定对话框。具体定义 可参看帮助。

图3.9

3.1.12原理图展开 在层次和多页原理图设计中,原理图的展开可以使我们深入到设计的每一层每一页,以

跟踪网络的方法是Tools>Global Navigate,出现对话框后,点击任意wire, 则与该wire相连网络会被加入列表,点击 列表中的任意网络均会被高亮(Highlight) 显示.

图3.10

3.1.13Standard库 我们将在这里熟习Standard库中一些常用符号的用法。 *Bus Tap:用来指明某根单线在总线中的位置。例: 有一条总线D<3..0>,要将四条单线从中分出,选wire 菜单> Bus Tap,分别在总线上引出四根线后,如图 3.11,每条线上均有一个“?”,“?”是用来添加BN( 位号)属性的值。添加方法是wire> Bus Tap Value。 出现如图3.12的对话框

§1.2 设计流程

Cadence板级系统设计的基本思想可用图1.1表示,其中: *Project Manager:管理项目设计所使用的工具及工具所产生的数据 *Design Sync:设计同步,保持原理图与PCB一致性 *Allegro:板图设计工具 *Floor Planner:高速PCB规划设计

*schematic properties-由用户指定,分配给component、wires(nets)或pin。 *symbol properties-是在元件库中指定的。 *occurrence properties-由用户指定,可以对同一属性指定不同的值。

以下是几种常用属性的名称: PATH:器件在原理图中的标号,防止元件时系统会自动添加,如I10 SIGNAL_NAME:信号名,添加信号名时系统自动生成,亦可作为属性添加 LOCATION:元件所属的物理器件的名称,如U2 BODY_NAME:器件的物理名称,如74LS00 点击Text>Property出现添加属性对话框,出现属性的名称和值,点击OK,鼠标指针变成 十字,点击想要添加属性的器件、 管脚或网络,完成一次添加。