基于AMBA总线的SPI协议IP核的设计与验证

基于AMBA总线的SPI可复用模块的设计与验证

b gn ei

ibtct =f ln'P— E D T 】b gn f i n > f e[ IL N_ A A) ei (_ _ S

s iC p S=1’ 0 i c t= 3 b ; b ;b t n 2’ 0

— _

e d le b gn n es e i

图 1 面向旅游者的系统菜单

21 0 2年

第 3 期 1

S INC CE E&T C N L GYI F MA I E H O O OR TON N

0I T论坛0

科技信息

( 上接第 1 7页) 3 当片选信号拉低后 ,C = , S K 0 同时写入 3 2位地址 和 3 位命令 , 2 然后读人 3 位数据 ; 2 当片选托高时 , S 1 C : 。 C = , K 0 代码 S

舔

一 丽

蓊

草 图

4 结束语

WeG S技术在旅游方 面的应用具有非常广阔的前景 . bI 它与 Itr ne. nt e 技术的相互结合 . 必将给人们的生 活带来 巨大的帮助。在 WeG S b I 平台上开发旅游信息系统是未来区域旅 游发展和管理 的必然趋势 . 也 是数字化城市的必然要求 。 b I WeG S技术在旅游方面 的成功应用, 必将 满足人们从 l e t n me上获取更多的旅游信 息、享受到更好 的旅游 服务 l 的要求 . 同时借助旅游信 息系统强大 的分析 功能 . 以一种理性 的思维

rgw[i ct lb ] p— s;btct i c t1b ; e_ bt n+ ’ 1 — =simi o i n =bt n+ ’ l _ _

e d n

_

—

() 1信息查询。 区景点信息是游客最为关心 的信息 , 景 游客通过对 s i s k = 1’ 0 p c p c b ;s i s= 1’ l b ; 景点 景区信 息的查 询可以获得各旅游景点 、 名胜古迹 、 园、 假村 、 公 度 展览馆 的地 理位置、 名称 、 地址 、 电话及介 绍资料和 图片 、 图像 等多媒 3 SP 模块 的仿真和验证 I 体信 息。 同时可查询景点景区所在地及附近的旅馆酒 店、 交通站点 、 邮 完成 S I模块 的设 计 后 ,并 对 其 进 行 了 仿 真 和验 证 。先 用 P 电、 、 银行 医疗机构 、 购物中心等配套 服务设施 。 V r oH L语 言 描 述其 R L电 路 .再 用 Xl x公 司 的 Xin S ei g D l T in i l x IE i () 2 图形操 作功能 提供 图层控 制 , 地图无极放大 、 小 , 图漫 缩 地 D s nS i 2 软件进行综合 , ei u e1. g t 2 然后再用 VS 其仿真 。其 中设置参 C对 游. 对象选择等基本 的地 图操作功能 , 同时还提供鹰眼功能 . 使用户 随 数为 : 命令 寄存 器 1 b , 9i 地址寄存器 1b , t 6 i 数据 寄存器 1b , t 5 i 工作在 t 时了解到当前缩放 的区域在整个地图中的位置 主机模式 , 收发数据 , P L O 高位 C O = 。仿真结果如图 3 所示 。 () 3旅游综合信息预报。 包括近期天气状况 、 出台的旅游法规 和 新 政策 、 最近 的节 庆活动 、 的旅游项 目、 新 城市 客流量 、 景区景点所在 地 政治 、 经济 、 安全信息的预报 。 () 4 空间分析功能。 旅游空间图形具有拓扑关 系, 系统可 以计算景 点 的空 间距 离、 路线 选择、 叠加图形信息 、 建立缓冲区 、 完成景点 透视 等。 通过这些空间分析功能 . 游客可 以完成空间距离查询 、 冲区查找 缓 周边 环境 、 最优路径选择( 包括时 间最短 、 费用最少 、 线路 利用率最高 等)线路查询 ( 、 火车 、 航班 、 公交车时刻表 、 票价等信息 , 公交换乘信息 等) 。 () 5 风景区三维虚拟展示功能。 应用 3 D技术 、 虚拟现实 ( R) V 技术 建立真三维旅游地 理信息 系统 .实现地 理空间在 电脑 中的三维化 , 并 对其加以操作 , 使人如置身于真实的旅游境界 2 面 向管理者的功能 ) 在数据库支持下 . 通过一系列 的开发 和比较 分析 . 将使 系统集 成 旅游资源评价 、 客源市场分 析、 旅游规划设计等功能 , 从而达到科 学性 与合 理性 () 1旅游资源评价 。 根据输入 的数据对旅游资源进行评价 , 包括对 游客密度 、 游客容量 、 旅游节律性等进行评价 。 可以向旅游管理规划部 门提供给一个合理 的开发序位 图 3 仿 真 图 () 2 客源市场分析 。 系统根据游客输入 的景 区、 l 信息进行统计 E 期 分析。 可统计 景区的 E接待人数 。 l 多年同期对 比情况 , 占核定最佳 日期 通过仿真之后 . 还进行了实际的 F G P A验证 。验证 的 F G P A采用 接待量 的百分 比. 占核定最 大 日期接待量 的百分 比 . 日饭店宾馆 出 Xl x 司的 Vie5XC V X 2 . 当 in 公 i r x 5 L 2 0 系统 工作 g MHz t 0 频率 下得到 了正 租率等信息 分析的结果 可以用统计图或表格 的形式展现给用户。 确 的结果。 () 3 旅游规划设计 。 助 G S 借 I 的空间分析 功能 , 进行旅游规划与设 计。 利用 G S I 的拓扑叠加功能 , 通过环境层与旅游资源评价图叠加 , 来 4 总 结 分 析优先发展 区域 , 利用 G S I 的网络分析功能 . 分析旅游线路布局 ; 利 本文提 出的基于 A A总线的 S I MB P 可复用模块的设计方法 , 它吸 用 G S的缓冲区功能可以确定风景 区的保护区域、 I 道路红线等 。 取了传统 S I的优 点 , P 具有 速度快 、 构简单 的特 点 , 已通过 E 结 并 DA

AMBA总线论文:基于AMBA APB总线的音频接口IP核的设计与验证

AMBA总线论文:基于AMBA APB总线的音频接口IP核的设计与验证【中文摘要】随着集成电路设计技术及制造技术的发展,片上系统(SoC)已成为超大规模集成电路领域主流技术之一。

SoC一般集成多个IP核,其中音频IP核是较为常用的一种。

数字音频技术发展较快,并随之产生了很多音频规范。

在众多的数字音频接口规范中,I2S 和S/PDIF音频协议标准具有传输简便、设计灵活等优点,在音频系统中广泛使用。

本文基于AMBA APB总线协议,设计实现了数字音频输出接口IP核,完成音频数据从APB总线到I2S和S/PDIF等音频协议信号的转化。

与其他普通的音频接口相比,本文的设计有如下特点:1.基于AMBA APB总线,由于AMBA总线规范被广泛应用,基于该规范设计的IP核具有较强的通用性和可复用性。

2.本设计支持I2S、左对齐、右对齐格式的I2S协议以及S/PDIF协议等多种音频协议。

3.设计可配置:时钟和帧同步及其极性可配置;数据格式可配置;帧内时间槽长可配置可为七种类型之一;槽内的有效数据的字长可配置;数据开始时刻相对帧同步的延迟可以设置为0,1或2位延迟;发送数据的顺序可以配置成从最低位开始或从最高位开始等。

4.本设计功能丰富:可以对模块内外所有的错误进行静音处理,对时钟进行检测以确保时钟的稳定,以及支持DMA传输和CPU中断传输。

设计完成后,我对设计进行了功能验证、综合优化和FPGA仿真。

根据I2S和S/PDIF等协议要求搭建了模拟验证和FPGA仿真平台,对设计进行了功能和时序验证,验证结果符合设计要求。

在综合阶段,采用TSMC 65nm标准单元工艺库,利用Synopsys相关工具对设计进行了综合、分析和优化,最终的系统时钟(即AMBA APB的时钟)可以达到为400MHz以上,同时符合音频接口的32KHz、44.1kHz、48KHz、96KHz或者192KHz(用户可配置)的采样频率的要求,满足设计要求。

基于AMBA总线的DMA控制器IP核设计与分析

第1 2期

谢

琅等 : 基于 A B M A总线的 D A控制器 I 核设计与分析 M P

.1 23.

基 于 A A总线 的 D MB MA控 制器 I 设计 与 分析 术 P核

谢 琅 ,杨 艳

( 武汉大学 电子信息学院, 湖北 武汉 407 ) 30 9

摘 要 :介绍 了一种 设计 基 于 A A总线的 D MB MA控 制 器 I 的方 法。 用硬 件描 述 语 言 ( HD ) P核 V L 来设 计 实现

挂接 在 A B H M AA B总线上 的 D A控制 器 , M 并通 过可编程 逻辑 器件 ( P A 完成 对设计 的验证 。 FG ) 最终形 成 可复 用

级系统总线( S ) A B 和高级外设总线 ( P ) M A总线架构 A B 。A B

广泛应用于嵌入式微 处理 器中 , D 而 MA控 制器需 要高性 能总

线 A B M s rSae的编程接 口。 H at/ l e v

A B总线 可支持 多个 主模块 和多个 从模 块 , 用 中心多 H 采 路总线而不是三态驱 动 的双 向总线进 行连 接。该总线使 用单

过 D A控制器向处理 器提出接管 总线控 制权的 总线 要求 , M 处 理器在 当前总线周 期结 束后 , 响应 D A请求 , M 并将 总线 控制 权交 给 D MA控 制器 。在 D A控 制器 的管理 下 , 设 与寄存 M 外

器之问就可 以直接进行数据交 换。D A控制 器的结 构如 图 1 M

手段 。在大容量 F G P A设 计乃至 S P O C设计 中采用 I P模块 是 十分必要 的, 这样 可以缩短设计周期和上市时问 , 降低风 险 , 减 少投入 , 提高系统的性 能和可靠性。 在一个 由嵌入式微处理器 为主控 的应 用系统中 , 当有大量 的数据 传输 时 , 尽管 中断驱 动 IO 比简单 的编 程控 制 IO有 / /

用于SoC的SPI接口设计与验证

用于SoC的SPI接口设计与验证匡春雨;马琪;陈科明【摘要】The RTL design and functional simulation of SPI IP core applied to SoC design is presented in this paper. The AMBA 2.0 bus standards is adopted to achieve the communication between the peripheral devices and the internal system through SPI. As fore data transmission section,the traditional design method was abandoned,which needs a specific shift regis-ter for serial/parallel transfer. The shifting transmission register and receive register are put together by the reuse registers to im-prove the speed and save the hardware resources. IP is verified with an SoC verification platform under SoC environment. The re-sults of simulation at the clock frequency of 100 MHZ show that the design can achieve data transmission and meet the require-ments of time-sequence design.%给出了一个可用于SoC设计的SPI接口IP核的RTL设计与功能仿真。

基于AMBA总线的IIC协议IP核设计与验证

文献标 识码 : B

文章 编号 : 1 0 0 2—2 2 7 9 ( 2 0 I 4 】 0 I 一 0 0 0 4— 0 5

De s i g n a n d Ve r i f i c a t i o n o f I P Co r e o f l I C Pr o t o c o I B a s e d o n AMB A Bu s

够在 标 准和 快速模 式 下运 行 , 能够 灵活 配置为 十位 地址 寻址 或 七 位地 址 寻 址模 式。详 细说 明 了该 I P核 的架构 , 各 部分 设计 及状 态 转换过 程。 最后该 模 块通 过 了系统 验 证 , 并在 x i l i n x F P G A上 转 化 为硬 件 电路 实现 了所 有功 能。

1 引 言

现如 今 , 电子类 产 品 向着 小 型 化 、 智能化 、 低 功 耗、 低成 本 、 高 可靠 性 的方 向发 展 。I I C仅有 两 根 线

被广 泛 应 用 于 视/ 音频领域 、 I c卡 行业 、 家 用 电器 、

通讯设 备 及各类 电 子产 品中 , 在智能 仪器 、 仪 表和 工 业测 控领 域也得 到 了广 泛应用 。

关键 词 : A MB A总线; V e r i l o g H D L语 言 ; I I C协议 ; 1 P核

D O I 编码 : 1 0 . 3 9 6 9 / j . i s s n . 1 0 0 2—2 2 7 9 . 2 0 1 4 . 0 1 . 0 0 2

中图分类 号 : T N 4 9 2

l 1 1

微

处

饥

第1 j 9 j

2 0 1 4 2』 J

F e I l _. 2 0l 4

基于APB总线接口的SPI协议IP核的设计与验证

基于APB总线接口的SPI协议IP核的设计与验证作者:郭艾华来源:《无线互联科技》2013年第11期摘要:基于APB总线接口,设计了一种可灵活配置为Master/Slave模式、设置传输速率、支持DMA功能并适用于4种时钟模式的SPI 协议IP核。

首先介绍了SPI协议标准,然后详细说明了该IP核的系统结构、接口信号和子模块设计,并使用了Verilog HDL语言实现硬件设计。

最后通过了FPGA时序仿真,验证了该设计的正确性。

该IP核已成功用于一款通信芯片,证明了该IP核在实际工程中的可行性。

关键词:SPI协议;IP核;Verilog HDL;FPGA1 引言随着集成电路工艺的不断发展,SOC的规模不断扩大,集成的IP模块不断增多,可复用IP核可以大幅减少设计的复杂度,缩短SOC的开发周期和提高流片成功率。

SPI(Serial Peripheral Interface)串行通信总线具有配置灵活,结构简单等特有的优点,被广泛应用于各位处理器和嵌入式系统当中。

因此,SPI协议IP核设计已经成为业界的设计热点之一,但现有的设计功能还不够完善。

文献[1]设计了一种SPI协议总线,只具有Master功能,不具有Slave功能;文献[2]设计了一种基于FPGA的SPI协议总线,但是不支持四线工作模式,并且对总线本身的结构和特性叙述不多,缺乏通用性;文献[3]设计了一种多功能化的SPI协议IP核,但是不支持DMA功能,所设计的IP核 Master模块也没有作流水考虑,数据传输率受到限制。

本文提出了一种基于APB总线的高速可复用的SPI协议IP核,解决了上述设计中存在的问题,并具有更高的可行性,方便灵活,并且已经得到了验证,成功应用于一款基带通信芯片。

2 SPI协议及时序概述SPI是一种高速高效率的串行接口技术,由Motorola公司提出。

通常由1个主模块和1个或多个从模块组成,主模块选择一个从模块进行同步通信,从而完成数据交换。

基于AMBA总线的SPI协议IP核的设计与验证

t eI o e u ig Ve i g HDL n d ti A i uain e a peo PGA i n n lssi r sn e o s o t e h P c r sn rl o i eal s lt x m l fF m o t mig a ay i s p ee td t h w h

中 图 分 类 号 :T 1 N9 9 文献 标 识 码 :A

De i n a d v r fc to fI c r fS r t c lb s d o s g n e i i a i n o P o e o PI p o o o a e n AM BA s Bu

Z a i Ca n Ga g Din io isPh sc p rme tU nv r i fS in ea d Tehn lgyo naHe e 3 0 6 La fM c o lcr nc y isDe at n iest o ce c n c oo fChi fi2 0 2 ) y

Ab t a t No d y h p l a i n o PI si e p g o n sr c : wa a s t e a p i to fS k e r wi g,a d I o e o PIp o o o a e o ea h t p ti C c Bu s n P c r fS r t c l sb c m o o I h s n d sg il . Ho v r h u c i n l y o h e in le d r s n e s n ta l.Us al h y c u d t f n t n e in f d e we e ,t e f n to ai f t e d sg s ar a y p e e t d i o mp e t u l t e o l n’ u c i y o a IS a e r c u d ’ t a s ta d r c ie d t n alf u l c d s B s d o sSP lv ,o o l n t r n mi n e ev a a i l o r co k mo e . a e n AM[ A u ,we d sg e n I B B s e in d a P c r fS Ip o o o ,wh c o l e c n i u e sS a t ro PI lv ,c u d s t i e e tta s iso p e o eo P r tc l ih c u d b o fg r d a PI M se r S a e o l e f r n r n m s i n s e d,a d S d f n c u d wo k i n n ft e f u l c d s o l r n a y o e o h o r co k mo e .Th s a t l n r d c s t e sr cu e n e f c n mp e n a i n o i r i e i to u e h t u t r ,i t r a e a d i lme t t f c o

基于AMBA总线的DMA控制器IP核设计

、、、 .c c i a c r I『I e n h n .o III ,, , n

20 06. ・ 7

_

维普资讯

薷

6 在传输过程 中进 行地址修 改和 .

・ 6 DMA通道 ,其 中 6个为独 确定哪个请求优 先被响应。 1个 ・ B总线接 口模块 : AH 本模块负责

・ MA读数据与写数据独立进行。 D

・

各 通 道 独 立 编程 ,独 立 初 始化 。

作为 D MA控制器有其特殊性 , 主 要 体现在它既是 总线的从设备 ,又是 总线的主设备。因此 ,D MA控制器有 两个主要的状态——空 闲态与工作态。 当DMA控制器处于空闲态时 ,它就相

而作 为专用的D MA控制器又会有 AP B总线读 写协议 , 并通过 A M 配置 R

其特定的功能要求 。比如对于 A B总 D H MA控制器的寄存器。 线而言 ,需要支持 B rt us操作。另一方

・

控制 寄存器模块 :该部 分通过 区别 。A MB A总线控制权是 由总线仲

实 现 AH B总 线读 写协 议 。 工 作 原 理 及 流程

传输量计数。当要求的数据传送完后 , 立的软件通道 ,另 1 0个为软硬件 复用

撤销总线请求 ,交还总线控制权。

的 通道 。

总而言之 ,D MA控制器一方面可 以接管总线 , 直接在 I / 口和存储器 O接

之 间进行读写操作 , 即可以像C u一样 P

§ 声

=D !

0 Z

电路 的发展趋势。在 S OC系统设计中, 计 , 简述 了I核设计的流程和需要重点 接在源地址和 E的地址之 间传送 ,不 P l

为了能够快速、 稳定的形成产品 ,P I 核 注意的地方 。 积 累和复 用技术 逐渐成为各个芯 片厂 商的首选 。 在这样 的背景下 ,P I 复用技 术成为 了集 成电路设计的一 个重要分 支 , 多设计厂商在购买其它公司的I 很 P 需要是 中间媒介。 通用的D MA控制器应具有一下功

基于APB总线的SPI接口的设计与实现

作者简介院许云龙(1988-),男,江西进贤人,分别于2009年、2013年获学士学位和博士学位,工程师,主要从事数字信号处理、数字SoC 设计等方面的研究。

E-mail:****************。

基于APB 总线的SPI 接口的设计与实现Design and Implementation of SPI Interface Based on APB Bus许云龙(中国西南电子技术研究所,四川成都610036)Xu Yun-long (Southwest China Institute of Electronic Technology,Sichuan Chengdu 610036)摘要:该文设计了一种可用于APB 总线的SPI 接口IP 核。

IP 核使用APB 总线来实现SPI 接口模块与MCU 之间进行通信,可适用于4种不同时钟模式、灵活地设置波特率并能配置为Master/Slave 模式,硬件设计采用Verilog HDL 实现。

通过联合仿真测试表明,SPI 接口能正确地传输数据,且满足SPI 时序设计要求,设计能满足实际工程应用。

关键词:SPI 接口;APB 总线;SoC 设计;Verilog HDL 中图分类号:TN47;TN402文献标识码:A文章编号:1003-0107(2020)07-0128-05Abstract:A SPI IP core based on APB bus is presented in this paper.The IP core of SPI interface communicates with MCU by APB bus,which could use in any one of the four different clock modes,set up different baud rate flexibly and be configured as SPI Master or SPI Slave,and implementation of the IP core is using Verilog HDL.The simulation test shows that the IP core of SPI interface could transmit data accurately,and satisfy demand of SPI timing,and could satisfy engineering application.Key words:SPI interface;APB bus;SoC design;Verilog HDL CLC number:TN47;TN402Document code:AArticle ID :1003-0107(2020)07-0128-050引言SPI(Serial Peripheral Interface)[1-4]是一种同步串行总线接口,是SoC 设计[5]中的常用外围IP 模块,并且很多器件及应用中都到了SPI 接口,如A/D 转换器[6]、FLASH [7]、E 2PROM [8]、数据采集系统[9]等。

基于AMBA总线的双协议数字音频接口IP核设计

( s tt o L ID s n h a g U i r t ,Ha g h u 3 0 2 ,C ia I tue fV S ei ,Z  ̄i nv s y ni g n ei n z o 1 0 7 hn )

【 s at w i a ado it fc rtcl F n /D F ae it d cd l mpe e t i ehooy o Abt c】T od t1 ui ne ae po os S ad SP I r nr ue .T1 i l na o tcnlg f r r o o e m tn

【 键 词 】F ;SP I ;A B 关 S /D F M A 【 图分 类 号 】T 1 中 N9 2 【 献 标 识 码 】A 文

De i n o sg f AM BA— a e a — r t c l Di i l Au i n e f c P — s d Du l p o o o g t d o I t r a e I b — a

一

2 I S总 线接 口

21 I . 2 S接 口概 述

维普资讯

器 件 与 电 路

圈 妒 ④

文 章 编 号 :0 2 8 8 2 0 1 — 0 7 0 1 0 — 6 4( 0 7) 0 0 3 — 5

基于 A MB 总线 的双 协议 数字 A 音频接 口 I P核设 计

龙 国 强 .阳 晔 ( 江 大 学 超 大规 模 集 成 电路 设 计 研 究所 ,浙 江 杭 州 3 0 2 浙 1 0 7)

1 引 言

过 去 几 十 年 里 ,数 字音 频 接 口技 术 取 得 了 长 足 的

设计 I P核 应 首 先 考 虑 选 用业 界 流 行 的 互 连 方 式 。

基于AMBA总线的SPI协议IP核的实现与验证的开题报告

基于AMBA总线的SPI协议IP核的实现与验证的开题报告一、研究背景SPI(Serial Peripheral Interface)协议是一种串行通信协议,广泛应用于嵌入式系统中。

它可以实现设备之间的通信,并且可以在减小I/O 口数量的情况下提高通信速度。

因此,在当前嵌入式系统中,SPI协议被广泛使用。

在数字系统设计中,IP(Intellectual Property)核的概念日益受到重视,通过使用IP核可以提高设计的可重用性和可维护性,缩短设计周期,降低设计成本。

因此,设计和实现一个基于AMBA(Advanced Microcontroller Bus Architecture)总线的SPI协议IP核是非常有必要的。

二、研究目的本论文旨在设计和实现一个基于AMBA总线的SPI协议IP核,并进行相应的验证。

具体目的如下:1.熟悉SPI协议的基本原理和AMBA总线规范;2.分析SPI协议在AMBA总线上的实现方法;3.设计和实现一个符合AMBA总线规范的SPI协议IP核;4.使用测试程序对IP核进行验证。

三、研究内容本论文的主要研究内容如下:1. SPI协议的基本原理和AMBA总线规范的学习。

2. SPI协议在AMBA总线上的实现方法的研究和分析。

3. IP核的设计和实现,包括SPI控制器和SPI总线接口。

4. 验证IP核的正确性,包括在FPGA上的仿真验证和实际验证。

四、研究方法本论文的研究方法如下:1.文献研究法。

首先,对SPI协议和AMBA总线规范进行详细的文献研究,明确相关知识点和技术细节。

同时,也要了解目前已有的相关研究成果,以便更好地设计和实现SPI协议IP核。

2.软件仿真法。

在IP核设计和实现的过程中,需要使用相应的EDA (Electronic Design Automation)工具进行仿真验证,以确保IP核的正确性。

同时,也需要对IP核的性能进行评估和优化。

3.硬件实验法。

验证IP核的正确性不仅需要进行软件仿真,还需要在FPGA上进行实际验证。

基于AMBA总线接口的以太网IP核

1 A AAH MB B总线

A A规范 是 A M 公司设计的一种用于高性能嵌入 MB R

式系统 的总线标准。A A规范定义 了 3种可使用的不同类 MB

型 的 总线 :AH , S B A B和 A B。 P

图 1 兵型的基于 A A规萜的 S C系统结构 MB o

2 以太网 I P核徽体系结构

系统集成的以太网 I P核符合 IE 0 . E E8 23协议规 范 。 J 该 I P核通过 A B 总线 与 R S 核通信 ,通过外接一个物理层 H IC P Y 接 口芯片与 以太 网相连 。以太网 I H P核主要技术特征包 括 :() 1完成 I E 0 . MA E E8 23 C层功能 ;() 2半双工、全双工支

LI Hu XI U , AO o gta , HANG u Y n -in Z J n

( stt f mp t gT cn lg, hns ae f c n e, e ig10 8 ) I tueo ni Co ui eh oo yC iee n Acd myo i csB in 00 3 Se j [ src ]1 i p prnrd cs h eino te tPcr t nAMB AHB bsit fc 2bt o 11 I oehspse L Ab tat ’ s ae t ue ed s f h me oewi a h i o t g E I h A u e aei a3一iS C.1 Pc r a asdRT nr n e

A A 规范 中的 A B 总线适用于低速的外部设备 ,它 MB P

捌

一

na mc l

I

PH Y

+ l i xa T t “ t胁  ̄T t xr r T s St Cl u s

基于AMBA的IP核设计

基于AMBA的IP核设计

贾博雄;李锦明

【期刊名称】《测试科学与仪器:英文版》

【年(卷),期】2022(13)2

【摘要】集成电路技术发展迅速,使得可复用的知识产权(IP)核设计受到业界的广泛重视。

本文在深入研究高级微控制器总线架构(AMBA)功能特点的基础上,设计了一种功能相对齐全的IP核,对其划分功能模块并完成其结构设计,理清了IP核内部各模块之间的关系,并采用自顶向下的设计方法搭建出IP核的内部架构。

利用Verilog语言对IP核接口模块、寄存器模块、波特率模块、发送模块、接收模块以及中断模块等进行了详细设计。

仿真验证表明,设计的IP核支持高级外围总线(APB)总线协议,IP核的功能覆盖率达到100%,其最高工作频率达到200 MHz,资源占用率小于15%。

可复用的IP核能够支持多种数据格式、多种时序传输方式以及主机/从机操作模式,减少了硬件电路的资源消耗,具有更强的适用性。

【总页数】8页(P217-224)

【作者】贾博雄;李锦明

【作者单位】中北大学仪器与电子学院

【正文语种】中文

【中图分类】TP3

【相关文献】

1.基于AMBA总线的3DES算法IP核的设计与实现

2.基于AMBA总线的独立CAN控制器的IP核设计与实现

3.基于AMBA总线的IIC协议IP核设计与验证

4.基于AMBA总线的SPI协议IP核的设计与验证

5.基于AMBA总线的SpaceWire 控制模块IP核设计

因版权原因,仅展示原文概要,查看原文内容请购买。

基于amba总线的fast irda ip核的设计与实现

基于amba总线的fast irda ip核

的设计与实现

AMBA总线的FAST IRDA IP核是一种具有实时传输功能的处理器架构,用于在系统中进行快速数据传输。

它利用AMBA总线作为其内部信号传输介质,并由三个子系统组成:芯片上的核心处理器、总线控制器和I/O单元(如IRDA协议模块)。

该架构采用了芯片上的核心处理器来实现信号处理和数据传输,总线控制器用于控制总线的同步和异步传输,而I/O单元则用于实现IRDA协议的实时传输。

在基于AMBA总线的FAST IRDA IP核的设计和实现中,首先要建立一个能够支持实时数据传输的架构,在此架构上可以实现处理器和I/O单元之间的通信。

其次,要设计一套总线控制机制,以实现处理器和I/O单元之间的数据传输。

最后,要实现一个符合IRDA协议的IP核,使得芯片上的处理器和I/O单元能够实现高速实时数据传输。

基于AMBA总线的SOC芯片的设计与验证的开题报告

基于AMBA总线的SOC芯片的设计与验证的开题报告一、选题背景随着嵌入式系统在各个领域的广泛应用,System on Chip (SoC) 芯片的设计逐渐成为了研究热点。

而 AMBA (Advanced Microcontroller Bus Architecture)总线作为一个开放的总线标准,在SoC芯片的设计中广泛应用。

AMBA总线是ARM公司推出的一种开放式总线体系结构,包含了AHB (Advanced High-performance Bus)、APB (Advanced Peripheral Bus)、AXI (Advanced eXtensible Interface)三种总线协议,实现了不同组件之间的高速通信和数据传输,提高了SoC系统的整体性能和可靠性。

本课题旨在通过对基于AMBA总线的SoC芯片的设计与验证研究,深入了解AMBA总线技术的特点及应用,设计实现一个基于AMBA总线的SoC芯片并进行验证,提高SoC芯片设计能力和经验。

二、研究内容1. AMBA总线技术的研究与分析;2. SoC芯片的设计与实现,包括芯片架构、接口和子系统设计;3. AMBA总线的接口设计及实现;4. SoC芯片的验证和测试,包括仿真、验证环境搭建和测试用例设计。

三、研究方法1. 阅读相关文献和技术资料,熟悉AMBA总线技术和SoC芯片设计流程;2. 设计芯片架构和接口,实现SoC芯片;3. 设计AMBA总线接口模块,并将其集成到SoC芯片中;4. 使用仿真工具进行SoC芯片的验证和测试。

四、研究意义本课题的研究可以深入了解AMBA总线技术的特点与应用,提高SoC芯片的设计能力和经验。

通过设计实现一个基于AMBA总线的SoC芯片并进行验证,可以进一步验证SoC芯片的正确性和可靠性,减少后期的调试和维护成本。

此外,本课题的研究成果可以为嵌入式系统的设计和应用提供参考,并有望推动SoC芯片设计技术的发展。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

虚拟仪器技术 电 子 测 量 技 术 EL ECTRON IC M EASU REM EN T TECHNOLO GY第33卷第1期2010年1月 基于AMBA总线的SPI协议IP核的设计与验证赵 杰 曹 凡 冮殿亮(中国科学技术大学物理系微电子实验室 合肥 230026)摘 要:基于AMBA总线接口,设计了一个可灵活配置为Master/Slave模式、可设置传输速率并能适用于4种时钟模式的SPI协议IP核。

详细说明了该IP核的系统构架、接口信号和子模块设计,使用Verilog HDL实现硬件设计,通过FP GA时序仿真,验证了该设计在实际工程应用中的有效性。

关键词:SPI协议;IP核;AMBA总线;Verilog HDL;FP GA中图分类号:TN919 文献标识码:ADesign and verif ication of IP core of SPI protocol based on AMBA BusZhao Jie Cao Fan G ang Dianliang(Lab of Microelectronics Physics Depart ment University of Science and Technology of China Hefei230026)Abstract:Nowadays the application of SPI Bus is keep growing,and IP core of SPI protocol has become a hot spot in IC design field.However,the f unctionality of the designs already presented is not ually they couldnπt f unction as SPI Slave,or couldnπt transmit and receive data in all four clock modes.Based on AMBA Bus,we designed an IP core of SPI protocol,which could be configured as SPI Master or SPI Slave,could set different transmission speed,and could work in any one of the four clock modes.This article introduces the structure,interface and implementation of the IP core using Verilog HDL in detail.A simulation example of FP GA timing analysis is presented to show the validity of this design in engineering applications.K eyw ords:SPI protocol;IP core;AMBA Bus;Verilog HDL;FP GA0 引 言可复用IP核的设计是SOC设计的关键,也是FP GA 开发的重要环节。

而SPI串行通讯总线具有结构简单、通讯速度快等显著优点,在嵌入式系统中应用日趋广泛,例如基于SPI总线的数据采集系统[1],基于SPI接口的DSP 的Flash扩展方案[2],以及利用SPI总线连接DSP和单片机[3]等。

实现SPI协议的IP核已经成为业界的设计热点之一,但现有设计功能不够完善。

文献[425]设计了SPI Master模块,没有实现SPI Slave功能;文献[6]介绍一种基于AMBA总线的SPI协议IP核设计,但其重点说明IP核设计的规范流程和方法,对于SPI模块本身的特性叙述不多。

为了给SOC设计和FP GA开发提供最大的灵活性,有必要设计一种可配置为Master或Slave模式,可设置通信速率并能适用于不同传输模式的SPI模块。

本文设计的基于AMBA总线的SPI协议IP核具备上述优点。

选择AMBA总线作为接口的原因是它方便灵活,且完全免费,在基于ARM,SPARC等处理器系统级芯片设计中已经成为SOC的总线标准[7]。

1 SPI协议简介SPI(serial peripheral interface)是Motorola公司推出的一种同步、高速、全双工的串行通信总线,主要用于嵌入式CPU与各种外围设备的通信。

SPI的信号线为同步串行时钟SPICL K、主机输出从机输入MOSI、主机输入从机输出MISO、从机选择SS。

协议规定了主、从两种工作模式,工作在主模式的器件负责输出通讯时钟SPICL K,并初始化数据传输。

协议规定了4种传输时序,其共同点是每位数据的发送/接收需要1个SPICL K周期,每次可传输若干个8位数据。

4种时序由时钟极性CPOL和时钟相位CP HA的不同取值来区分。

CPOL=0代表空闲状态为低电平,而CPOL=1代表空闲状态为高电平;CP HA=0和CP HA= 1决定了数据在不同的SPICL K边沿有效。

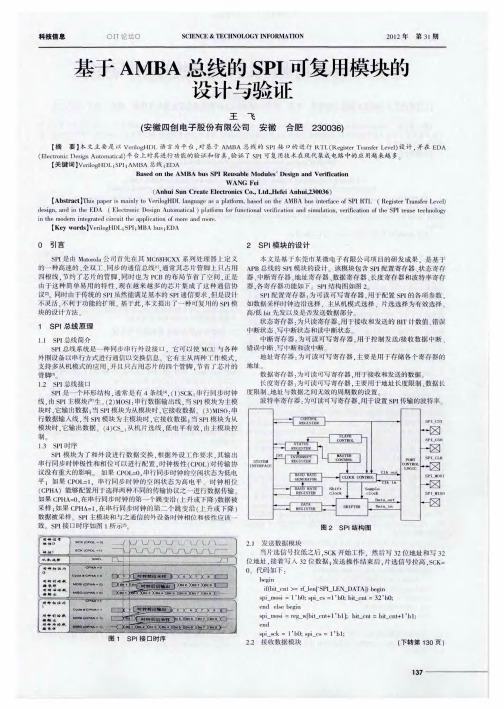

4种传输时序如图1所示。

赵 杰等:基于AMBA 总线的SPI 协议IP 核的设计与验证第1期图1 SPI 协议的4种数据传输时序[8]2 SPI 协议IP 核的设计本IP 核可以通过SPI 总线和其他设备通信,并通过A PB 总线连接A PB Host (例如ARM CPU ,或SPARC等)。

A PB Host 通过APB 总线接口对SPI 模块进行状态控制、数据读写、中断处理等操作。

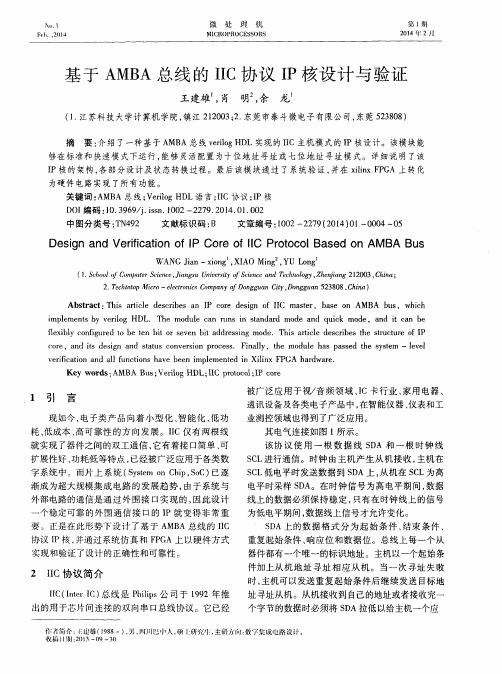

2.1 系统模块结构图系统模块结构图如图2所示。

图2 系统模块结构图2.2 接口说明PRESETn :复位信号,有效时模块回到初始状态。

PSEL :片选信号,有效时选中模块,方可进行操作。

PENABL E :操作使能信号。

读写操作需该信号有效。

PWRITE :写入使能信号。

当PSEL 有效且该信号为高电平,表示写入操作;PSEL 有效且该信号为低电平表示读取操作。

PADDR[5:2]:地址信号。

指定操作的目标寄存器。

PWDA TA[7:0]:写入数据信号。

可写入控制命令或待传输的数据。

PRDA TA[7:0]:读取数据信号。

可读取寄存器的值或接收到的数据。

PCL K:A PB 总线时钟。

以上为A PB 总线接口信号。

下面是和SPI 串行通信相关的信号。

RX :串行数据输入信号。

TX :串行数据输出信号。

CL KOU T :SPI Master 时钟输出信号。

若配置为Slave 则 第33卷电 子 测 量 技 术该信号无用。

CL KIN :SPI Slave 时钟输入信号。

若配置为Master 则该信号无用。

FSSOU T :SPI Master 帧控制信号,当数据传输开始时变为低电平,结束后回复高电平。

若配置为Slave 则该信号无用。

可作为SPI 从机选择信号SS 输出端。

FSSIN :SPI Slave 帧控制输入信号,若配置为Master 则该信号无用。

可作为SPI 从机选择信号SS 输入端。

2.3 各模块设计采用自顶向下的设计方法划分出子模块,主要子模块实现的功能及设计方法如下。

2.3.1 AMBA A PB 接口模块AMBA A PB interface 主要负责地址解码以及读写寄存器。

实现方法是将各寄存器的地址保存为常量数组,当片选信号PSEL 有效时,将地址总线PADDR[5:2]的值和这些地址常量一一对比,如果和某个地址常量相符,则对相应的寄存器进行读写操作。

2.3.2 寄存器模块Register Block 存储控制寄存器、状态寄存器和数据寄存器的数据。

其中控制寄存器SCR0,SCR1可以设置4种SPI 时序,并设定模块为SPI Master/Slave 模式;数据寄存器SDR 保存发送/接收数据。

2.3.3 时钟分频模块当模块被配置为SPI Master 时,时钟分频模块Clock prescaler 将A PB 总线时钟PCL K 分频,产生内部时钟信号CL KDIV 。

分频功能利用倒数计数器实现,计数初值保存在寄存器CPSR 。

CL KDIV 经过收发逻辑模块,产生频率为其一半的CL KOU T 信号,该信号是SPI 通信的主时钟信号。

分频公式为:CL KD IV =PCL K1+CPS R CL KOU T =PCL K2×(1+CPS R )2.3.4 接收缓存和发送缓存由于A PB 总线时钟速度和SPI 的传输速度不匹配,设计了收发缓存模块。

接收缓存RxFIFO 是数据位宽为8,深度为8的先进先出缓存,接收数据从接收移位寄存器被复制到RxFIFO ,直到A PB 总线将其读出。

发送缓存TxFIFO 同样位宽为8,深度为8。

发送数据将缓存在此直到被复制到发送移位寄存器。

2.3.5 中断控制模块本SPI 模块可产生4个独立的可屏蔽中断信号:发送请求、接收请求、接收溢出以及接收超时。

中断控制模块Interrupt generation logic 产生一个综合中断信号,为以上4个信号的或函数。

2.3.6 发送和接收逻辑模块Transmit/Receive Logic 主要负责SPI 协议时序控制,在每个SPI 时钟周期传送一位数据。

为了能配置为Master/Slave 模式,设计两个独立的数据收发模块M TxRxCntl 和STxRxCntl ,分别实现在Master 和Slave 模式下的时序控制功能。

在控制寄存器中设置M/S 选择位作为Master 和Slave 模块的片选信号,同一时刻只选通其中一个模块。

分析SPI 协议时序,将数据传输过程分解为若干阶段,每个阶段用有限状态机的一个状态描述。

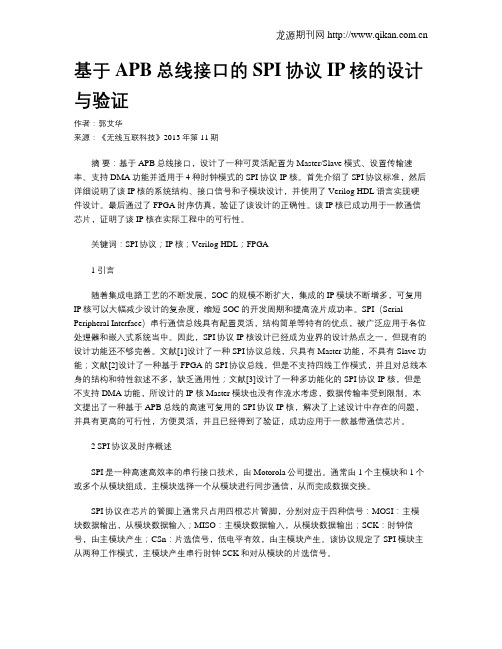

主模式下数据传输有限状态机如图3所示。

图3 主模式下数据传输的有限状态机 初始状态为空闲状态。

Tx 发送数据准备好后,在下个CL KDIV 上升沿进入桢开始状态,并将桢控制输出信号FSSOU T 置为低电平。

之后从发送第一位数据状态开始数据传输,状态转换由CL KDIV 上升沿触发。

发送状态和接收状态相互交替,每个状态发送或接收一位数据,持续一个CL KDIV 周期。

发送和接收状态下将SPI 时钟输出信号CL KOU T 置为相反电平,因此收发一位数据构成一个完整的CL KOU T 周期,CL KOU T 的频率是CL KDIV 的一半。

字节传输完毕后,若Tx 数据未准备好则判定为帧结束,FSSOU T 恢复至高电平,并回到空闲状态;若Tx 准备好则判定为连续字节传输过程,转移到发送第一位状态开始新字节的传输。