HDL实现边缘检测电路

soble边缘检测算法的verilog实现

soble边缘检测算法的verilog实现先来说说soble算子,soble算子是一种离散性差分算子,用来运算图像亮度函数的灰度的近似值,在图像的任何一点使用这个算子,会得到对应的灰度矢量或法矢量。

SOBLE算子的卷积因子为:soble算子包含两组3*3的矩阵,分别为横向和纵向,将Gx 和Gy 与图像做卷积,即可分别得出横向和纵向的亮度差分近似值,如果用A表示原始图像,Gx 和 Gy 分别代表经横向和纵向边缘检测的图像灰度值,公式如下:图像每一个像素的横向和纵向灰度值通过一下公式结合,来计算该点灰度的大小:通常,为了提高效率,使用不开平方的近似值,但是这样做会损失精度,迫不得已的时候可以这样做:就是这个G就是判断条件,如果梯度G大于某一阈值(THRESHOLD),则认为该点(X,Y)为边缘点。

可以使用下面公式计算梯度方向(如果只是边缘检测则不需要计算方向)soble算子的verilog实现,可以划分为4个步骤,解析和实现分别如下:(1)计算Gx, Gy与3*3像素阵列每行的乘积。

以上是例化生成3*3矩阵的模块,下面的代码是计算Gx, Gy。

(2个clk)这个理解起来不难,比较简单,先用一个时钟计算3*3矩阵每行的像素乘积,再求的卷积后的Gx,Gy,因此消耗了两个时钟。

(2)求Gx^2+Gy^2的结果,及Gx与Gy的平方和。

(1个clk)这一步直接通过veilog中的乘法器的描述来实现,综合时会自动布线为片内乘法器,如下。

(3)求Gx^2+Gy^2的平方根。

(1个clk)强大的ALTERA在QII软件中提供了平方根的IP核,如下所示。

下面给出SQRT的例化代码:(4)根据外部输入阈值,判断并实现边缘的检测。

(1个clk)将post_bit_r扩展到8bit, ~{8{post_bit_r}}, 检测到的边缘为黑色。

soble_threshold 是外部输入的一个人为设定的阈值。

(5)前面几步对图像数据的处理总共消耗了5个时钟,因此图像阵列的同步信号需要延迟5个时钟。

图像边缘检测的HDL设计

图像边缘检测的HDL设计赵毅摘要:边缘检测是数字图像处理的重要内容,是基于边界分割方法的基础。

本文首先对边缘检测的原理做了简要的总结和分析并对微分边缘检测方法做了详细的介绍。

硬件描述语言在电子系统设计中有明显的优势。

用硬件描述语言来实现对图像边缘检测的仿真也是最近电子系统仿真的热门研究方向。

本文在分析了图像边缘检测的各种方法和硬件描述语言的特点的基础上应用硬件描述语言简单仿真了边缘检测算法,初步探讨了基于FPGA的图像边缘检测方法。

从结果来看,HDL设计方法可以实现图像边缘的检测。

关键词:边缘检测;微分算子;硬件描述语言;FPGA由于图像物体中的边缘表现为灰度变化,因此,可通过计算灰度的不连续性来增强和检测边缘。

边缘检测的方法很多,目前已经提出了许多种算子,例如Roberts算子、Prewitt算子和Sobel算子等都是比较简单而且常用的边缘检测算子。

小波多尺度边缘检测是20世纪90年代随着小波分析的迅速发展而发展起来的图像检测方法,Mallat 指出,图像可以从其不同尺度下的边缘信息得到近似重建,重建误差在人的视觉感受范围以外[5]。

最新的研究方法是基于数学形态学的边缘检测,将数学形态学用于边缘检测,既能有效地滤除噪声,又可保留图像中的原有细节信息,是边缘检测技术的重大突破。

1 数字图像处理与边缘检测1.1 数字图像与数字图像处理图像是对客观对象的一种相似性的生动的描述或表示。

在其自然的形式下,图像并不能直接由计算机进行分析。

从人眼的视觉特点看,图像可分为可见图像和不可见图像。

其中可见图像又包括生成图(通常称为图形或图片)和光图像两种。

按波段多少,图像可分为单波段、多波段和超波段图像。

单波段图像在每个点只有一个亮度值;多波段图像上每一个点不止一个特性,例如红、绿、蓝三波段光谱图像或彩色图像在每个点具有红、绿、蓝3个亮度值,这3个值表示在不同光波段上的强度,人眼看来就是不同的颜色。

按图像空间坐标和明暗程度的连续性,图像可分为模拟图像和数字图像。

遥感实验——边缘检测

实验二边缘检测一、实验原理两个具有不同灰度值的相邻区域之间总会存在边缘,边缘是灰度值不连续的表现。

由于边缘试图向上灰度变化最剧烈的地方,传统的边缘检测就是利用了这点。

对图像上的个点像素点进行微分或二阶微分来确定边缘像素点。

一阶微分图像的峰值处对应着图像上的边缘点,二阶微分图像的零值处对应着图像上的边缘点。

根据属数字图像的特点,处理图像过程中常采用差分来代替导数运算,对于简单的一阶导数运算,由于具有固定的方向性,只能检测特定方向的边缘,所以不具有普遍性。

为了克服一阶导数的缺点,我们需要定义新的图像梯度算子:1222[(,)][()()F F G F j k j k∂∂=+∂∂ 这是图像处理中最常见的一阶微分算法,式子中F(j,k)表示图像的灰度值,图像梯度的最重要的性质是梯度的方向在图像弧度的最大变化率上,这恰好可以反映出图像的边缘上的灰度变化。

图像边缘提取的常用梯度算子有:Robert 算子、Sobel 算子、Prewitt 算子、拉普拉斯算子等。

二、实验步骤①滤波:边缘检测算法主要是基于图像强度的一阶和二阶导数,但导数的计算对噪声很敏感,因此必须使用滤波器来改善与噪声有关的边缘检测器的性能。

需要指出,大多数滤波器在降低噪声的同时也导致了边缘强度的损失,因此,增强边缘和降低噪声之间需要折中。

②增强:增强边缘的基础是确定图像各点邻域强度的变化值。

增强算法可以将邻域(或局部)强度值有显著变化的点突显出来。

边缘增强一般是通过计算梯度幅值来完成的。

③检测:在图像中有许多点的梯度幅值比较大,而这些点在特定的应用领域中并不都是边缘,所以应该用某种方法来确定哪些点是边缘点。

最简单的边缘检测判据是梯度幅值阈值判据。

④定位:如果某一应用场合要求确定边缘位置,则边缘的位置可在子像素分辨率上来估计,边缘的方位也可以被估计出来。

在边缘检测算法中,前三个步骤用得十分普遍。

这是因为大多数场合下,仅仅需要边缘检测器指出边缘出现在图像某一像素点的附近,而没有必要指出边缘的精确位置或方向。

《基于FPGA的边缘检测系统设计》范文

《基于FPGA的边缘检测系统设计》篇一一、引言随着人工智能和计算机视觉技术的快速发展,边缘检测作为图像处理中的关键技术,被广泛应用于众多领域。

然而,传统的边缘检测方法通常需要大量的计算资源和时间,难以满足实时性和高效性的要求。

因此,基于FPGA(现场可编程门阵列)的边缘检测系统设计成为了研究的热点。

本文旨在探讨基于FPGA的边缘检测系统设计,以提高图像处理的效率和准确性。

二、系统设计概述本系统设计以FPGA为核心,通过硬件加速的方式实现边缘检测算法。

系统主要包括图像输入、预处理、边缘检测、后处理和图像输出等模块。

其中,预处理模块对输入图像进行去噪、平滑等处理,以提高边缘检测的准确性;边缘检测模块采用高效的边缘检测算法,如Sobel、Canny等;后处理模块对检测到的边缘进行平滑、连接等处理,以得到更完整的边缘信息。

三、FPGA硬件加速设计FPGA具有并行计算、高带宽和低功耗等优点,非常适合用于加速图像处理算法。

在边缘检测系统中,我们通过设计专门的硬件电路,将边缘检测算法映射到FPGA上,实现并行计算和高速数据处理。

具体而言,我们采用了流水线设计,将边缘检测算法分解为多个模块,每个模块负责一部分计算任务,并通过数据流水线的方式实现高速数据处理。

此外,我们还优化了算法的硬件实现方式,降低了功耗和硬件资源消耗。

四、边缘检测算法设计在边缘检测算法设计中,我们采用了Canny算法作为主要算法。

Canny算法具有高准确性和鲁棒性,能够有效地检测出图像中的边缘信息。

在FPGA上实现Canny算法时,我们采用了分级处理的思路,将算法分解为多个级联的模块,每个模块负责一部分计算任务。

通过优化算法的硬件实现方式,我们提高了系统的处理速度和准确性。

五、系统实现与测试我们采用Verilog HDL语言编写了FPGA的程序代码,并通过仿真和实际测试验证了系统的可行性和性能。

在测试中,我们使用了多种不同的图像数据,包括自然场景、人像等。

基于可编程逻辑阵列的索贝尔边缘检测算法的两种实现方案

基于可编程逻辑阵列的索贝尔边缘检测算法的两种实现方案张海斌;朱苏磊;徐明亮【摘要】基于可编程逻辑阵列(FPGA)的片上可编程及并行流水线具有处理快、实时性等优点,采用Quartus II自带知识产权(IP)核进行设计的方案耗资源多,处理速度慢,针对于此提出了改进的索贝尔(Sobel)算子方案,使以上缺点得到改善;结合Matlab和Modelsim对这两种方案的仿真和验证结果表明,改进后的Sobel算子方案明显优于Quartus II自带IP核进行设计的方案,并且能很好地实现图像边缘检测,减少了偏差.%In this paper,two kinds of edge detection scheme based on Field Programmable Gate Array(FPGA) are realized and analyzed by using the Sobel operator.In view of the design which utilizes the intellectual property(IP) cores embedded in the Quartus II has some disadvantages such as more resources are consumed、process is relatively slow and so on,an improved scheme which improves the first design′s shortcomings is proposed.Simulation and verification results of these two schemes which are combined with Matlab and Modelsim show that the improved Sobel operator scheme is better than the previous scheme designed by using IP cores embedded in the Quartus II,achieving a good image detection and reducing errors.【期刊名称】《上海师范大学学报(自然科学版)》【年(卷),期】2017(046)002【总页数】7页(P247-253)【关键词】边缘检测;可编程逻辑阵列;数字图像处理【作者】张海斌;朱苏磊;徐明亮【作者单位】上海师范大学信息与机电工程学院,上海 200234;上海师范大学信息与机电工程学院,上海 200234;上海师范大学信息与机电工程学院,上海 200234【正文语种】中文【中图分类】TN911.73数字图像处理就是采用计算机或嵌入式系统对图像进行深度加工,并从中获得有用的信息.伴随着计算机技术、集成电路技术的飞速发展,数字图像处理技术也得到了很大的发展,并且也出现了许多与数字图像处理技术相关的新理论、新技术、新设备.这些新理论、新技术在工业生产、科学研究、医疗卫生等领域得到了广泛应用,对社会的发展及人类生活水平的提高做出了极大的贡献[1].边缘是图像的基本特征,是指图像灰度变化率最大的位置,由图像像素点数据局部的不连续而形成.边缘的表现形式有图像纹理结构的突变及灰度级的突变,彩色变化等等,边缘检测利用物体与背景在某些特征上的差异而实现.由于实时图像边缘检测算法涉及到的数据量大,一般运算器的顺序执行或者传统软件处理实时图像很难满足要求.而采用可编程逻辑阵列(FPGA)的流水线和并行处理技术,不仅可以提高数字图像的处理速度,也可以在一定程度上满足实时系统中的应用需求.边缘检测算子可以分为一阶微分算子和二阶微分算子.常见的一阶微分算子有Prewitt算子,Canny算子、Sobel算子、Roberts Cross算子,Kirsch算子,罗盘算子等等;二阶微分算子包括Laplacian算子以及高斯-拉普拉斯(LOG)算子等等[2].本研究主要介绍了基于FPGA的索贝尔(Sobel)边缘检测算法实现的两种方案,方案一完全采用Quartus II自带的知识产权核(IP)核进行实现,实现简单、工程周期短,但占用逻辑资源多,设计效果不够理想;方案二针对方案一的缺点进行了改进,改善了系统处理速度,减少了逻辑资源的消耗,在一定程度上改善了设计效果,优化了系统性能.1.1 Sobel边缘检测算子索贝尔算子(Sobel operator)是数字图像处理中的常用算子之一,在图像边缘检测和噪声滤波中都有运用,它是离散型差分算子,用来提取图像亮度函数的梯度近似值.在图像的任何像素点上运用这一算子,都可以产生对应像素点的梯度矢量或是其法矢量[2].现在假设图像数据点上有9个像素点:现用一个二次曲面z(x,y)来拟合这9个点的灰度值,即用来近似图像灰度函数f(x,y),并使均方误差最小.令分别对a、b、c、d、e、g的一阶偏导数为0,联立解得各个系数.将二次曲面z(x,y)对x,y求偏导数,得到梯度的幅度值[3]:[f(i+1,j-1)+2f(i+1,j)+f(i+1,j+1)]+[f(i-1,j-1)+2f(i,j-1)+f(i+1,j-1)]-[f(i-1,j+1)+2f(i,j+1)+f(i+1,j+1)].它的两个卷积模块为:1.2 基于FPGA的Sobel算子实现框图Sobel边缘检测算法的实现主要包括三个模块,如图1所示.图1中,前两个模块主要是实现图像像素点的梯度值计算,图像数据输入通过数据缓存模块构成3×3矩阵像素阵列,然后再分别计算水平梯度和垂直梯度,然后把两个方向上的梯度结合起来,接着通过门限处理模块,实现判别输出.假设输入的像素值依次为:p11、p12、p13、p21、p22、p31、p32、p33,那么在垂直方向上的梯度和在水平方向上的梯度分别为:GV=(p11+2p12+p13)-(p31+2p32+p33).梯度结合后的梯度值G为:通常为了提高程序的运行速度都采用如下的公式:门限处理模块之后输出数值P22,当设定的门限值大于G时,输出为0,当G大于设定的门限值时输出为255.综上分析Sobel算子在理论设计上容易实现,并且具有滤除噪声的作用,所以适合用在图像噪声较多的图像处理中.2.1 图像缓存实现由于Sobel算子理论基于3×3像素块计算中心像素梯度,构造3×3像素矩阵特别重要,要实现这个效果,必须使用一个容量足够大的存储单元来缓存串行输入的图像数据流,并把串行数据转化成并行的3行像素值,这样在3个像素时钟后就可以得到3×3图像像素矩阵.过去常使用先入先出(FIFO)作为图像数据的存储方式,但对FIFO 的读写操作较为复杂.而本设计中主要是调用了Quartus II软件自带的altshift_taps移位寄存器宏模块.软件中提供的altshift_taps宏模块是一个可设置参数的并具有多个端口(Taps)输出的移位寄存器,每一个抽头在移位寄存器链的指定位置上输出数据.对于Matlab经常应用的256×256大小图像进行Sobel边缘检测,altshift_taps模块配置为8 bit输入/8 bit输出、3个抽头,相邻两个抽头有256个registor(寄存单元).经过预处理的9个图像灰度像素点进入缓冲区后数据流如,图2所示.2.2 卷积计算和门限比较模块编写的卷积计算模块是为了得到水平的、垂直的两个方向上的梯度值,要达到卷积运算的效果需要做大量的乘法、加法运算.若是采用以往分立的D触发器、加法器和乘法器来完成,可以实现预期的功能,但其结构复杂,设计繁琐.在本方案中先通过调用Quartus II开发工具提供的IP核模块中的可编程乘加法器altmult_add、可编程多路加法器parallel_add以及开方模块(altsqrt)来实现.其原理如图3所示.图3中前面的3个Line就是缓存数据模块,而后面的实现水平梯度和垂直梯度的计算及开方后的结果再与门限比较,输出判别后的结果.考虑到上述方案调用IP时,占用FPGA逻辑资源大,在处理数据乘、开方时,占用大量CPU资源,提出了改进设计方案.3.1 图像缓冲模块设计改进基于图2的图像数据缓冲模块的数据流结构,构想在shift_RAM中存储2行数据,同时与当前的输入行数据组成3行的陈列,具体的实现步奏如下:(1) 首先,将输入的信号用像素使能时钟同步一拍,以保证数据和宏模块altshift_taps输出的数据保持同步,主要实现代码如图4所示.(2) 例化并输入row3_data,经过Modelsim仿真可以观察到3行数据同时存在.(3) row_data读取信号的分析及生成数据在altshift-taps里存储消耗一个时钟,因此3×3阵列阵列读取使能需要一个时钟的偏移.(4) 此时,根据read_image_clken信号直接读取3×3像素阵列,最后得到的matrix_p11、matrix_p12、matrix_p13、matrix_p21、matrix_p22、matrix_p23、matrix_p31、matrix_p32、matrix_p33即为得到的3×3像素阵列,主要代码如图5所示.3.2 卷积模块的实现在1.2节中,可以利用(7),(8)式实现Sobel算子算像素点P22处的水平和垂直梯度值计算,在上面构成的3×3陈列中可以得到图像的每一个像素值,所以只要把(7),(8)式用Verilog语言实现就可以了,水平梯度值计算主要代码如图6所示.这里只分析像素P22在水平上的梯度值,从3×3矩阵模块中出来的像素值matrix_p11,matrix_p12,matrix_p13,matrix_p21,matrix_p22,matrix_p23,matrix_p31,matrix_p32,matrix_p33都是reg无符号数型,即分别为P1、P2、P3、…、P9,在计算机内部数字乘以2就是bit位向左移一位,代码中通过暂存正结果和负结果,通过比较这个数值的大小最终给出水平上的梯度值.垂直上的梯度值同理实现.接着另一个进程中实现平方加的结果,最后再把平方加的结果送入开方模块SQRT中,输出对应像素点的估算梯度值,得到的梯度估算值与阀门值比较得出该像素点是否为边缘像素点.4.1 两种方案在Quartus II下的分析对比两种方案都是基于altera的CycloneIVE EP4CE10F17C8为目标芯片,在Quartus II下编译综合,得出两种方案的硬件资源使用情况综合报告及在约定输入时钟25 mHz时TimeQuest的时序分析报告如表1、2所示.从表1、2可以看出方案二明显比方案一占用资源少,首先,内嵌乘法器只占用了9%,这样数据处理大大减少;其次,专用逻辑寄存器和引脚也明显减少,这样可以在FPGA 上留用更多的资源来处理其他信息;最后在25 mHz时钟约束下,从TimeQuest的分析时钟看,方案一最大工作效率为34.19 mHz,方案二可以达到47.78 mHz,这可以看出优化后的方案二数据处理速度明显提高,满足实时性的要求.4.2 仿真结果分析采用Matlab对灰度图像的各个像素点以16进制存储在image.txt文本文件下,然后将本文文件下的数据通过函数readmemh(image.txt,data_mem)读到存储器类型的data_mem中,再通过always进程通过寻址方式把各个图像数据输给输入端口.在仿真时再通过函数fdisplay(文件句柄,“数据存储格式”,模块输出端口)将两个方案处理后的数据分别存储在ima_process.txt文本里,再采用Matlab软件把ima_process.txt里的数据通过相应函数实现处理后的图像显示,具体代码如图7所示.图8,9分别为输入相同图像数据时在Modelsim下两种方案的Sobel边缘检测仿真结果,门限设定都为200,从图8,9中可以看出在clk时钟的作用下,图像的各个像素值逐个输进输入端口,可以从输出端口(oDATA、post_img_Bits)看到只有两种状态,若该点在边缘上,则通过系统后该点值变为0xff,若不在边缘则变为0x00.两种方案可以实现对图像的边缘检测.图10是设定阈值为200时两种方案对图像边缘提取后的结果对比,从图10中可以看出方案二的处理效果明显比方案一好,进一步说明改进后的方案优于采用IP核的方案;处理后的图片边沿明显出现了误判,这是没有对边沿像素点采取处理的结果,在实际工程中可以对图像边沿采取重叠复制、忽略处理等方法.本文作者基于FPGA采用两种设计方案对Sobel边缘检测进行了实现并仿真分析,首先方案一中完全采用Quartus II自带的IP核设计各个模块,实现图像各个像素值卷积实现图像边缘检测,针对方案一占用FPGA逻辑资源多,处理图像数据慢等特点,设计了另一种设计方案,一方面,针对数据的左移一位(乘2)的思想很好地实现了数据点的水平和垂直梯度的提取,这样大大减少了FPGA内嵌乘法器的使用,也减少了结果误差的舍入;另一方面,为了构建3×3的图像矩阵,就需要构建图像数据缓冲模块,方案一中采用的图像数据缓冲模块完全采用3个taps的数据缓冲模块,每个taps 的深度均为图片行的像素点,这样FPGA的逻辑资源很大程度上就被浪费了,影响FPGA的性能.为了改善这种状况,方案二只调用了2个taps的数据缓冲模块,并结合输入的数据端口利用FIFO的思想构成3×3矩阵,很好地改善了方案一中的占用逻辑资源较大的情况.综合对比两种方案,改善后的方案明显比方案一效果好,消耗资源少,耗时少,并且处理效果较好,完全满足实时图像处理的要求.导师简介: 朱苏磊(1975-),女,副教授,主要从事图像处理及嵌入式方面的研究.E-mail:****************【相关文献】[1] Fang H R.The application of FPGA in image edge detection [J].Information and Communication,2015(1):9-11.[2] Yan L,Lei B,Ding W,et al.Based on local adaptive thresholds edge detection of colorimage color difference [J].Journal of Electronics and Information,2012,34(9):2058-2063. [3] Liao C Z.A Sobel edge-detection algorithm based on FPGA and emulation [J].Journal of Yangtze University,2015,12 (7):37-40.[4] Pan M,Chen Y,Li Q.Design of image sampling system based on FPGA [J].Research and Development,2012,31 (3):58-61.[5] Ruan Q Q,Ruan Y Z.Image processing [M].Beijing:Publishing House of Electronics Industry,2014.[6] Xia Y W.Verilog course in digital systems design [M].Beijing:Beihang University Press,2008.[7] Zhang Z Y.The master of Matlab [M].Beijing:Beihang University Press,2011.[8] Zhang Y J.Design and algorithm realization of FPGA-based image processing systems[D].Chongqing:Chongqing University,2006.[9] Wu Y.Basic algorithms of digital image processing based on FPGA design and implementation [D].Harbin:Harbin Institute of Technology,2008.。

《数字电子技术与接口技术试验教程》课件第5章

第5章 基于HDL的时序逻辑电路实验

图5-2 边沿D触发器的仿真结果

9

第5章 基于HDL的时序逻辑电路实验 (2) 边沿D触发器的VHDL源代码如下:

--Behavioral D Flip-Flop with Clock Enable and Asynchronous Reset

entity Dflipflop is Port (D,clk,rst,ce : in STD_LOGIC; Q : out STD_LOGIC);

architecture Behavioral of DFF is begin

process(clk, rst,D) begin

if (CLK'event and CLK='1') then if rst ='1' then Q <= '0'; else Q<=D; end if;

end if; end process; end Behavioral;

end if; end process; end Behavioral;

13

第5章 基于HDL的时序逻辑电路实验

(3) 带有置位和清零端的边沿D触发器的约束文件规定

如下:

#Basys2约束文件: NET "clk" LOC ="B8"; //时钟

#Basys2约束文件: NET "clk" LOC ="B8"; //时钟

end Dflipflop;

architecture Behavioral of Dflipflop is begin

process(clk, rst,D,ce)

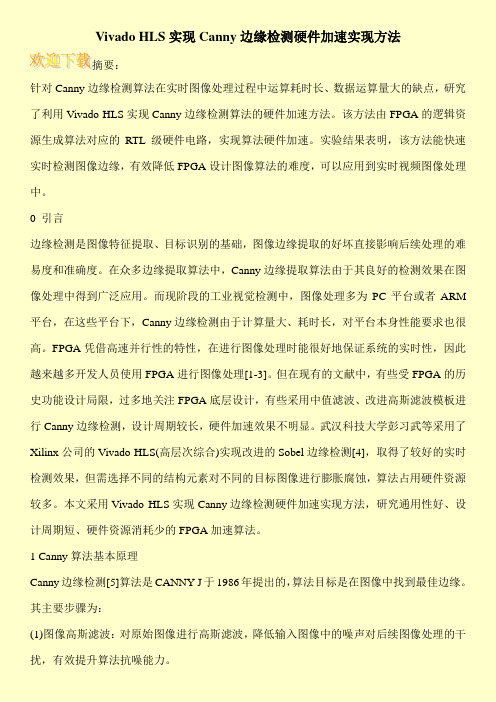

Vivado HLS实现Canny边缘检测硬件加速实现方法

Vivado HLS实现Canny边缘检测硬件加速实现方法摘要:针对Canny边缘检测算法在实时图像处理过程中运算耗时长、数据运算量大的缺点,研究了利用Vivado HLS实现Canny边缘检测算法的硬件加速方法。

该方法由FPGA的逻辑资源生成算法对应的RTL级硬件电路,实现算法硬件加速。

实验结果表明,该方法能快速实时检测图像边缘,有效降低FPGA设计图像算法的难度,可以应用到实时视频图像处理中。

0 引言边缘检测是图像特征提取、目标识别的基础,图像边缘提取的好坏直接影响后续处理的难易度和准确度。

在众多边缘提取算法中,Canny边缘提取算法由于其良好的检测效果在图像处理中得到广泛应用。

而现阶段的工业视觉检测中,图像处理多为PC平台或者ARM 平台,在这些平台下,Canny边缘检测由于计算量大、耗时长,对平台本身性能要求也很高。

FPGA凭借高速并行性的特性,在进行图像处理时能很好地保证系统的实时性,因此越来越多开发人员使用FPGA进行图像处理[1-3]。

但在现有的文献中,有些受FPGA的历史功能设计局限,过多地关注FPGA底层设计,有些采用中值滤波、改进高斯滤波模板进行Canny边缘检测,设计周期较长,硬件加速效果不明显。

武汉科技大学彭习武等采用了Xilinx公司的Vivado HLS(高层次综合)实现改进的Sobel边缘检测[4],取得了较好的实时检测效果,但需选择不同的结构元素对不同的目标图像进行膨胀腐蚀,算法占用硬件资源较多。

本文采用Vivado HLS实现Canny边缘检测硬件加速实现方法,研究通用性好、设计周期短、硬件资源消耗少的FPGA加速算法。

1 Canny算法基本原理Canny边缘检测[5]算法是CANNY J于1986年提出的,算法目标是在图像中找到最佳边缘。

其主要步骤为:(1)图像高斯滤波:对原始图像进行高斯滤波,降低输入图像中的噪声对后续图像处理的干扰,有效提升算法抗噪能力。

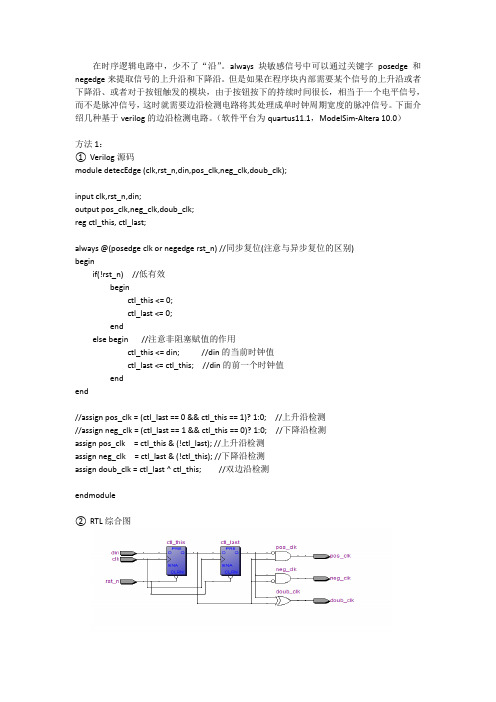

基于verilog的边沿检测电路

在时序逻辑电路中,少不了“沿”。

always块敏感信号中可以通过关键字posedge和negedge来提取信号的上升沿和下降沿。

但是如果在程序块内部需要某个信号的上升沿或者下降沿、或者对于按钮触发的模块,由于按钮按下的持续时间很长,相当于一个电平信号,而不是脉冲信号,这时就需要边沿检测电路将其处理成单时钟周期宽度的脉冲信号。

下面介绍几种基于verilog的边沿检测电路。

(软件平台为quartus11.1,ModelSim-Altera 10.0)方法1:①Verilog源码module detecEdge (clk,rst_n,din,pos_clk,neg_clk,doub_clk);input clk,rst_n,din;output pos_clk,neg_clk,doub_clk;reg ctl_this, ctl_last;always @(posedge clk or negedge rst_n) //同步复位(注意与异步复位的区别)beginif(!rst_n) //低有效beginctl_this <= 0;ctl_last <= 0;endelse begin //注意非阻塞赋值的作用ctl_this <= din; //din的当前时钟值ctl_last <= ctl_this; //din的前一个时钟值endend//assign pos_clk = (ctl_last == 0 && ctl_this == 1)? 1:0; //上升沿检测//assign neg_clk = (ctl_last == 1 && ctl_this == 0)? 1:0; //下降沿检测assign pos_clk = ctl_this & (!ctl_last); //上升沿检测assign neg_clk = ctl_last & (!ctl_this); //下降沿检测assign doub_clk = ctl_last ^ ctl_this; //双边沿检测endmodule②RTL综合图③消耗资源④Modelsim仿真testbench源码:`timescale 1ns/1psmodule testbench;reg clk, rst_n, din;wire pos_clk, neg_clk, doub_clk;//调用detecEdge模块detecEdge inst(.clk(clk),.rst_n(rst_n),.din(din),.pos_clk(pos_clk),.neg_clk(neg_clk),.doub_clk(doub_clk));initial //输入信号初始化beginrst_n = 0;clk = 0;din = 0;#50;rst_n = 1;endalways #100 din = ~din; //输入激励always #5 clk = ~clk; //系统时钟endmodule仿真波形:由仿真结果知,当din上升沿到来时,pos_clk输出一个脉冲信号(宽度为1个clk),同理,当din下降沿到来时,neg_clk输出一个脉冲信号,doub_clk在din的上升沿和下降沿都输出脉冲信号。

边缘检测的原理

边缘检测的原理边缘检测是数字图像处理中的常见任务,它能够识别并提取出图像中物体的边缘信息。

在计算机视觉和模式识别领域,边缘特征对于物体识别、分割以及图像理解非常重要。

本文将介绍边缘检测的原理及其常用的方法。

一、边缘的定义边缘是图像中亮度变化剧烈处的集合。

在图像中,边缘通常表示物体之间的分界线或物体自身的边界轮廓。

边缘通常由亮度或颜色的不连续性引起,可以用于图像分析、特征提取和图像增强等应用中。

二、边缘检测的原理边缘检测的目标是找到图像中的所有边缘,并将其提取出来。

边缘检测的原理基于图像亮度的一阶或二阶变化来进行。

常用的边缘检测原理包括:1. 一阶导数方法一阶导数方法利用图像亮度的一阶导数来检测边缘。

最常见的方法是使用Sobel算子、Prewitt算子或Roberts算子计算图像的梯度,然后通过设置合适的阈值将梯度较大的像素点判定为边缘。

2. 二阶导数方法二阶导数方法通过对图像亮度进行二阶导数运算来检测边缘。

其中,Laplacian算子是最常用的二阶导数算子,它可以通过计算图像的二阶梯度来获取边缘信息。

类似于一阶导数方法,二阶导数方法也需要设定适当的阈值来提取边缘。

3. Canny算子Canny算子是一种广泛使用的边缘检测算法,它综合了一阶和二阶导数方法的优点。

Canny算子首先使用高斯滤波平滑图像,然后计算图像的梯度和梯度方向,并根据梯度方向进行非极大值抑制。

最后,通过双阈值算法检测出真正的边缘。

三、边缘检测的应用边缘检测在计算机视觉和图像处理中具有广泛的应用。

以下是一些常见的应用:1. 物体检测与分割边缘检测可以帮助识别图像中的物体并进行分割。

通过提取物体的边缘,可以实现对图像内容的理解和分析。

2. 图像增强边缘检测可以用于图像增强,通过突出图像中的边缘信息,使图像更加清晰和饱满。

3. 特征提取边缘是图像中最重要的特征之一,可以用于物体识别、图像匹配和目标跟踪等应用中。

通过提取边缘特征,可以实现对图像的自动识别和分析。

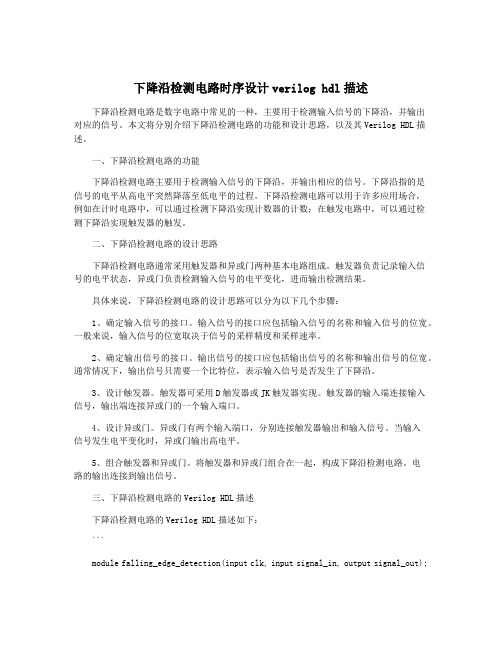

下降沿检测电路时序设计verilog hdl描述

下降沿检测电路时序设计verilog hdl描述下降沿检测电路是数字电路中常见的一种,主要用于检测输入信号的下降沿,并输出对应的信号。

本文将分别介绍下降沿检测电路的功能和设计思路,以及其Verilog HDL描述。

一、下降沿检测电路的功能下降沿检测电路主要用于检测输入信号的下降沿,并输出相应的信号。

下降沿指的是信号的电平从高电平突然降落至低电平的过程。

下降沿检测电路可以用于许多应用场合,例如在计时电路中,可以通过检测下降沿实现计数器的计数;在触发电路中,可以通过检测下降沿实现触发器的触发。

二、下降沿检测电路的设计思路下降沿检测电路通常采用触发器和异或门两种基本电路组成。

触发器负责记录输入信号的电平状态,异或门负责检测输入信号的电平变化,进而输出检测结果。

具体来说,下降沿检测电路的设计思路可以分为以下几个步骤:1、确定输入信号的接口。

输入信号的接口应包括输入信号的名称和输入信号的位宽。

一般来说,输入信号的位宽取决于信号的采样精度和采样速率。

2、确定输出信号的接口。

输出信号的接口应包括输出信号的名称和输出信号的位宽。

通常情况下,输出信号只需要一个比特位,表示输入信号是否发生了下降沿。

3、设计触发器。

触发器可采用D触发器或JK触发器实现。

触发器的输入端连接输入信号,输出端连接异或门的一个输入端口。

4、设计异或门。

异或门有两个输入端口,分别连接触发器输出和输入信号。

当输入信号发生电平变化时,异或门输出高电平。

5、组合触发器和异或门。

将触发器和异或门组合在一起,构成下降沿检测电路。

电路的输出连接到输出信号。

三、下降沿检测电路的Verilog HDL描述下降沿检测电路的Verilog HDL描述如下:```module falling_edge_detection(input clk, input signal_in, output signal_out);wire pre_trigger;DFF pre_trigger_d(signal_in, clk, pre_trigger);assign signal_out = pre_trigger ^ signal_in;endmodule```模块名称为falling_edge_detection。

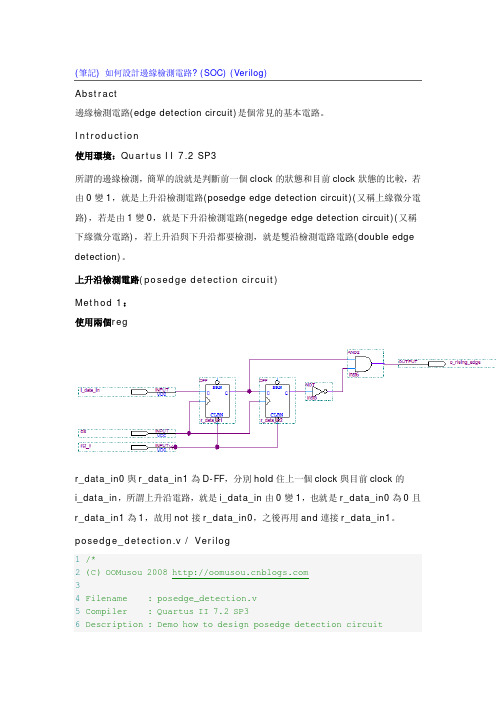

边缘检测电路的(SOC)(Verilog)

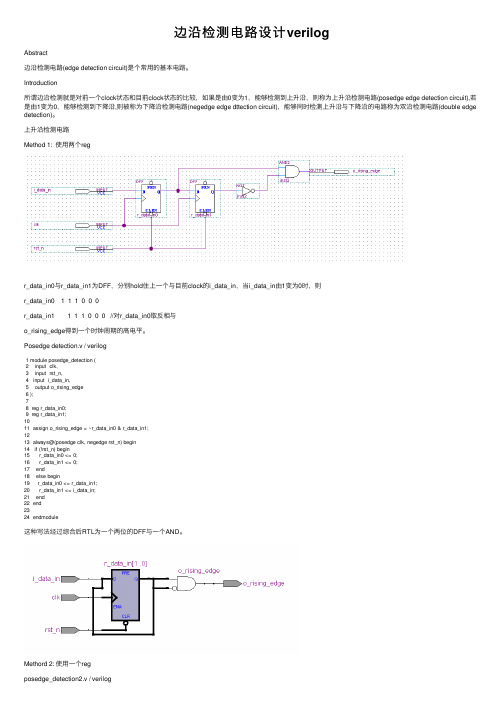

(筆記) 如何設計邊緣檢測電路? (SOC) (Verilog)Abstract邊緣檢測電路(edge detection circuit)是個常見的基本電路。

Introduction所謂的邊緣檢測,簡單的說就是判斷前一個clock 的狀態和目前clock 狀態的比較,若由0變1,就是上升沿檢測電路(posedge edge detection circuit)(又稱上緣微分電路),若是由1變0,就是下升沿檢測電路(negedge edge detection circuit)(又稱下緣微分電路),若上升沿與下升沿都要檢測,就是雙沿檢測電路電路(double edge detection)。

使用環境:Quartus II 7.2 SP3上升沿檢測電路(posedge detection circuit)Method 1:使用兩個regr_data_in0與r_data_in1為D-FF ,分別hold 住上一個clock 與目前clock 的i_data_in ,所謂上升沿電路,就是i_data_in 由0變1,也就是r_data_in0為0且r_data_in1為1,故用not 接r_data_in0,之後再用and 連接r_data_in1。

1 /*2 (C) OOMusou 2008 posedge_detection.v / Verilog34 Filename : posedge_detection.v5 Compiler : Quartus II 7.2 SP36 Description : Demo how to design posedge detection circuit7Release : 07/06/2008 1.08*/910module posedge_detection (11input clk,12input rst_n,13input i_data_in,14output o_rising_edge15 );1617reg r_data_in0;18reg r_data_in1;1920assign o_rising_edge = ~r_data_in0 & r_data_in1;2122always@(posedge clk, negedge rst_n) begin23if (!rst_n) begin24 r_data_in0 <= 0;25 r_data_in1 <= 0;26end27else begin28 r_data_in0 <= r_data_in1;29 r_data_in1 <= i_data_in;30end31end3233endmodule這種寫法經過合成後,會很聰明的只用一個2 bit的D-FF,與一個AND。

《基于FPGA的边缘检测系统设计》

《基于FPGA的边缘检测系统设计》篇一一、引言随着科技的不断进步,边缘检测在图像处理中起着越来越重要的作用。

其目的是突出图像中的对象边缘,增强图像特征信息。

FPGA(Field Programmable Gate Array)作为一种可编程的硬件设备,具有高速度、低功耗和灵活性的特点,使其成为实现边缘检测的理想选择。

本文将详细介绍基于FPGA的边缘检测系统设计,以期在保持系统稳定性的同时提高性能和灵活性。

二、边缘检测系统的总体设计基于FPGA的边缘检测系统设计主要包括硬件设计和软件设计两部分。

硬件设计主要涉及FPGA的选择与配置、电路板的设计等;软件设计则包括算法设计、FPGA编程等。

(一)硬件设计在硬件设计阶段,首先要根据需求选择合适的FPGA芯片。

考虑边缘检测系统的性能需求、功耗、成本等因素,选择合适的FPGA芯片进行设计。

同时,需要设计相应的电路板,包括电源电路、时钟电路、数据传输接口等,以保证系统的稳定性和可靠性。

(二)软件设计在软件设计阶段,首先要对边缘检测算法进行优化,使其能够适应FPGA的并行处理能力。

常用的边缘检测算法包括Sobel算法、Canny算法等。

根据算法特点,将算法进行优化,以便在FPGA上实现高效的处理。

然后,使用硬件描述语言(如VHDL 或Verilog)对优化后的算法进行编程,实现边缘检测系统的软件设计。

三、边缘检测算法的优化与实现(一)算法优化针对FPGA的并行处理能力,对边缘检测算法进行优化。

首先,将算法中的并行部分进行划分,使其能够在FPGA上并行处理。

其次,对算法中的数据进行流水线处理,以提高数据的处理速度。

最后,对算法进行仿真验证,确保其能够在FPGA上正确运行。

(二)算法实现使用硬件描述语言对优化后的边缘检测算法进行编程。

在编程过程中,需要充分考虑FPGA的资源利用率和功耗等因素,合理分配硬件资源。

同时,需要对编程过程中的错误进行调试和修正,确保系统的稳定性和可靠性。

边缘检测原理(内含三种算法)

边缘检测原理的论述摘要数字图像处理技术是信息科学中近几十年来发展最为迅速的学科之一。

图像边缘是图像最基本的一种特征,边缘在图像的分析中起着重要的作用。

边缘作为图像的一种基本特征,在图像识别、图像分割、图像增强以及图像压缩等的领域中有较为广泛的应用,其目的就是精确定位边缘,同时更好地抑制噪声。

目前,数字图像处理技术被广泛应用于航空航天、通信、医学及工业生产等领域中。

图像边缘提取的手段多种多样,本文主要通过MATLAB语言编程分别用不同的算子例如Roberts算子、Prewitt算子、Sobel算子、Kirsch算子、Laplacian算子、Log算子和Canny算子等来实现静态图像的边缘检测,并且和检测加入高斯噪声的图像进行对比。

阐述了不同算子在进行图像边缘提取的特点,并在此基础上提出利用小波变换来实现静态图像的边缘检测。

【关键字】图像边缘数字图像边缘检测小波变换背景图像处理就是对图像信息加工以满足人的视觉心理或应用需求的方法。

图像处理方法有光学方法和电子学方法。

从20世纪60年代起随着电子计算机和计算技术的不断提高和普及,数字图像处理进入了高速发展时期,而数字图像处理就是利用数字计算机或其它的硬件设备对图像信息转换而得到的电信号进行某些数学处理以提高图像的实用性。

计算机进行图像处理一般有两个目的:(1)产生更适合人观察和识别的图像。

(2)希望能由计算机自动识别和理解图像。

数字图像的边缘检测是图像分割、目标区域的识别、区域形状提取等图像分析领域的重要基础,图像处理和分析的第一步往往就是边缘检测。

边缘是图象最基本的特征.边缘检测在计算机视觉、图象分析等应用中起着重要的作用,是图象分析与识别的重要环节,这是因为子图象的边缘包含了用于识别的有用信息.所以边缘检测是图像分析和模式识别的主要特征提取手段。

所谓边缘是指其周围像素灰度后阶变化或屋顶状变化的那些像素的集合,它存在于目标与背景、目标与目标、区域与区域,基元与基元之间。

硬件电路hdl设计模块的网络化测试

1 概述芯片设计不断向超大规模化发展,对应的芯片测试变得越来越复杂[1-3]。

测试工作被分成许多模块,由不同的工作小组完成。

网络化、分布式的测试环境对提高效率、保证知识产权的安全性由重要作用[4-6]。

芯片测试的一个主要是工作是编写测试模块,它们的数量众多,工作量非常大,一些模块可能需要外购。

比如一个TCP/IP 网络芯片的测试模块,其本身也是非常复杂的,也需要进一步的测试。

如何能够充分利用现有的测试模块,是迫切需要解决的问题。

本文提出的网络化测试方法,基于Python 实现,可以使用高级语言编写测试模块,并利用它特别丰富的库。

此外,Python 与其它主流高级语言都有调用接口,相当于由其它高级语言编写的测试模块,都能为我所用。

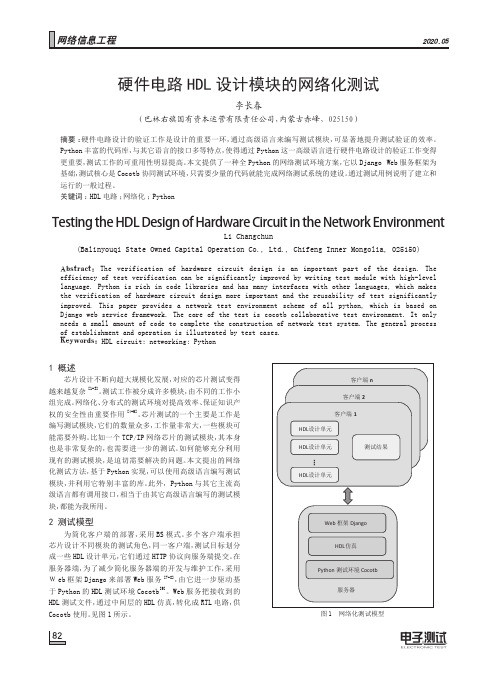

2 测试模型为简化客户端的部署,采用BS 模式。

多个客户端承担芯片设计不同模块的测试角色,同一客户端,测试目标划分成一些HDL 设计单元,它们通过HTTP 协议向服务端提交。

在服务器端,为了减少简化服务器端的开发与维护工作,采用Web 框架Django 来部署Web 服务[7-8],由它进一步驱动基于Python 的HDL 测试环境Cocotb [9]。

Web 服务把接收到的HDL 测试文件,通过中间层的HDL 仿真,转化成RTL 电路,供Cocotb 使用。

见图1所示。

improved. This paper provides a network test environment scheme of all python, which is based on Django web service framework. The core of the test is cocotb collaborative test environment. It only needs a small amount of code to complete the construction of network test system. The general process of establishment and operation is illustrated by test cases.Keywords: HDL circuit; networking; Python了解Python 的工程师比Verilog 或VHDL 多得多,对企业的运作更有利。

多尺度边缘检测算法的硬件电路设计

多尺度边缘检测算法的硬件电路设计1. 多尺度边缘检测算法在图像处理和计算机视觉中的应用多尺度边缘检测算法是图像处理和计算机视觉中的一项研究方向,用来检测和定位图像中的那些特征,以及特征在不同分辨率尺度中的可见特征曲线的位置。

它的应用范围包括图像分割和目标识别、无人驾驶车辆障碍物识别、智能安防系统中的物体检测识别和跟踪、运动检测和行路径恢复、海洋及航天船舶轨迹分析、农作物病害识别等等。

2. 多尺度边缘检测算法原理多尺度边缘检测算法是基于金字塔原理实现的,它利用图像金字塔中不同尺度的模糊图像来实现边缘检测,借助变换函数实现边缘强度的反映。

该算法的实现中,金字塔的构造是本质的,在各级金字塔中依次对不同尺度的模糊图像执行一组通用变换,例如Laplace变换。

之后,通过求和、计算增量变换和梯度分析来构建图像中边缘信息的变换图,完成边缘检测任务。

3.硬件电路设计硬件电路设计中,多尺度边缘检测算法的实现原理大体可以划分为三个步骤:首先是模糊处理,用来对图像进行金字塔处理,在不同的尺度上构建模糊图像。

其次是进行Laplace变换,计算图像的边缘强度。

最后是进行统计梯度分析,建立图像中边缘信息的变换图。

为了实现多尺度边缘检测算法,我们可以使用FPGA(可编程逻辑器件)来完成相应的硬件电路设计,可以实现高效、低成本的电路组装。

FPGA的硬件设计芯片可以采用多种数字信号处理技术,如提取信号、数字滤波器、模数转换等,来实现多尺度边缘检测算法。

同时,FPGA还可以通过数据处理流水线技术,实现多步操作的功能,从而更有效地实现多尺度边缘检测算法。

总之,多尺度边缘检测算法是一项重要的研究方向,在实现它的硬件电路设计中,可以采用FPGA芯片和数据处理流水线技术,为多尺度边缘检测的研究提供了新的思路和可能性。

《基于FPGA的边缘检测系统设计》范文

《基于FPGA的边缘检测系统设计》篇一一、引言随着计算机视觉技术的飞速发展,边缘检测已成为图像处理领域中一个重要的研究方向。

边缘检测可以有效地提取图像中的轮廓信息,为后续的图像处理和分析提供重要的依据。

传统的边缘检测系统通常基于通用处理器(如CPU)实现,但面对复杂的图像处理任务时,其处理速度和效率往往无法满足实时性的要求。

因此,本文提出了一种基于FPGA(现场可编程门阵列)的边缘检测系统设计,旨在提高边缘检测的效率和速度。

二、系统设计概述本系统设计以FPGA为核心,通过硬件加速的方式实现边缘检测算法。

系统主要包括图像输入模块、预处理模块、边缘检测模块、后处理模块和图像输出模块。

其中,FPGA负责协调各模块的工作,实现图像的实时处理和输出。

三、模块设计1. 图像输入模块:负责接收原始图像数据。

该模块可以通过相机、网络等方式获取图像数据,并将其转换为FPGA可以处理的格式。

2. 预处理模块:对原始图像进行预处理,包括去噪、灰度化等操作,为后续的边缘检测提供良好的输入数据。

3. 边缘检测模块:本系统的核心模块,采用硬件加速的方式实现边缘检测算法。

该模块可以根据具体的算法需求,定制硬件逻辑,实现高效的边缘检测。

4. 后处理模块:对检测到的边缘信息进行后处理,包括阈值处理、连通域分析等操作,以提高边缘检测的准确性和鲁棒性。

5. 图像输出模块:将处理后的图像数据输出,可以通过显示器、网络等方式进行展示和传输。

四、FPGA实现在FPGA实现方面,本系统采用硬件描述语言(HDL)进行电路设计。

首先,根据边缘检测算法的需求,设计相应的硬件逻辑电路。

然后,通过FPGA开发工具进行电路编译、综合和布局布线等操作,生成可在FPGA上运行的二进制文件。

最后,将二进制文件烧录到FPGA芯片中,实现边缘检测系统的硬件加速。

五、实验与分析为了验证本系统的性能和效果,我们进行了大量的实验。

实验结果表明,基于FPGA的边缘检测系统具有以下优点:1. 高效率:由于采用硬件加速的方式实现边缘检测算法,本系统的处理速度远高于传统的CPU实现方式。

边沿检测电路设计verilog

边沿检测电路设计verilogAbstract边沿检测电路(edge detection circuit)是个常⽤的基本电路。

Introduction所谓边沿检测就是对前⼀个clock状态和⽬前clock状态的⽐较,如果是由0变为1,能够检测到上升沿,则称为上升沿检测电路(posedge edge detection circuit),若是由1变为0,能够检测到下降沿,则被称为下降沿检测电路(negedge edge dttection circuit),能够同时检测上升沿与下降沿的电路称为双沿检测电路(double edge detection)。

上升沿检测电路Method 1: 使⽤两个regr_data_in0与r_data_in1为DFF,分别hold住上⼀个与⽬前clock的i_data_in,当i_data_in由1变为0时,则r_data_in0 1 1 1 0 0 0r_data_in1 1 1 1 0 0 0 //对r_data_in0取反相与o_rising_edge得到⼀个时钟周期的⾼电平。

Posedge detection.v / verilog1 module posedge_detection (2 input clk,3 input rst_n,4 input i_data_in,5 output o_rising_edge6 );78 reg r_data_in0;9 reg r_data_in1;1011 assign o_rising_edge = ~r_data_in0 & r_data_in1;1213 always@(posedge clk, negedge rst_n) begin14 if (!rst_n) begin15 r_data_in0 <= 0;16 r_data_in1 <= 0;17 end18 else begin19 r_data_in0 <= r_data_in1;20 r_data_in1 <= i_data_in;21 end22 end2324 endmodule这种写法经过综合后RTL为⼀个两位的DFF与⼀个AND。

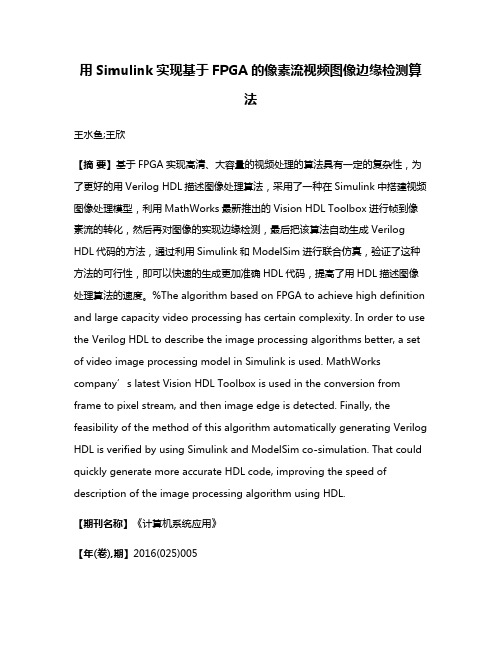

用Simulink实现基于FPGA的像素流视频图像边缘检测算法

用Simulink实现基于FPGA的像素流视频图像边缘检测算法王水鱼;王欣【摘要】基于FPGA实现高清、大容量的视频处理的算法具有一定的复杂性,为了更好的用Verilog HDL描述图像处理算法,采用了一种在Simulink中搭建视频图像处理模型,利用MathWorks最新推出的Vision HDL Toolbox进行帧到像素流的转化,然后再对图像的实现边缘检测,最后把该算法自动生成Verilog HDL代码的方法,通过利用Simulink和ModelSim进行联合仿真,验证了这种方法的可行性,即可以快速的生成更加准确HDL代码,提高了用HDL描述图像处理算法的速度。

%The algorithm based on FPGA to achieve high definition and large capacity video processing has certain complexity. In order to use the Verilog HDL to describe the image processing algorithms better, a set of video image processing model in Simulink is used. MathWorks company’s latest Vision HDL Toolbox is used in the conversion from frame to pixel stream, and then image edge is detected. Finally, the feasibility of the method of this algorithm automatically generating Verilog HDL is verified by using Simulink and ModelSim co-simulation. That could quickly generate more accurate HDL code, improving the speed of description of the image processing algorithm using HDL.【期刊名称】《计算机系统应用》【年(卷),期】2016(025)005【总页数】5页(P89-93)【关键词】FPGA;Simulink;Verilog HDL;ModelSim;HDL【作者】王水鱼;王欣【作者单位】西安理工大学自动化与信息工程学,西安 710048;西安理工大学自动化与信息工程学,西安 710048【正文语种】中文随着微电子技术的发展, 现在的视频越来越高清, 并且视频图像的尺寸也逐渐增大. 因而大多采用大规模的集成电路或者专用的芯片来实现视频图像的处理. 现场可编程门阵列(FPGA)是现在运用非常广泛的可编程逻辑器件,它不同于DSP及其它处理器, 它在设计上可以实现硬件的并行和流水线技术, 并且具很强的灵活性, 可以根据需要实现重新配置, 具有很好地灵活性和适用性[1]. 为了更有效的利用FPGA的并行性, 所以视频图像边缘检测采用像素流的处理方法.对FPGA的设计采用硬件描述语言(HDL)实现, 随着视频数据量的增多即算法实现的复杂性, 所以为了快速实现图像处理算法, 则采用基于Simulink搭建图像处理模块, 并运用Simulink中的HDL Coder工具箱自动产生不同于以往的IP Core的可读、可跟踪的HDL代码, 从而实现视频的快速处理. 由于自动HDL代码生成流程比手工编码快, 工程师得以把节省下来的时间投入到更好地方案设计中. 比起手动的设计, 这种方法使工程师能够以更快的速度生成质量更佳的FPGA原型. 但是, Simulink的中大部分的处理都是对大的阵列进行处理, 即对帧的图像处理, 而FPGA对图像的处理是基于像素流的处理, 所以在进行图像处理之前把帧数据转换成像素流数据需要人为的编写转换代码, 但是这种方法即麻烦又不可靠. 为了更好更快捷实现HDL代码的自生成, 本文先采用Simulink 的Vision HDL Toolbox工具箱把帧数据自动转化成像素流数据作为数据处理的输入量, 然后再在Simulink 中设计一个针对产生HDL代码的子系统,从而在该子系统中设计基于像素流的边缘检测模块, 在子系统搭建好后就可以利用Simulink的HDL Code工具自动产生边缘检测算法的Verilog HDL代码. 最后通过Simulink与ModelSim进行联合仿真以来验证这种方法的可行性及利用QuartusII验证代码的正确性.1.1 图像边缘图像的边缘是指其周围像素灰度急剧变化的那些像素的集合, 它是图像最基本的特征. 边缘主要存在于目标、背景和区域之间, 因此, 它是图像分割所依赖的最重要的依据, 也是目标区域识别和区域形状提取等图像处理技术的基础. 由于边缘检测十分重要, 因此成为机器视觉研究领域最活跃的课题之一[2].边缘检测的基本思想是先检测图像中的边缘点, 在按照某种策略将边缘点连接成轮廓, 从而构成分割区域. 由于边缘是索要提取的目标和背景的分界线, 提取出边缘才能将目标个背景区分开, 因此边缘检测对于数字图像非常重要.1.2 边缘检测算子基于图像像素灰度值的连续性研究, 通常用图像中某个像素邻域内像素梯度来确定图像的边缘, 梯度对应一阶导数, 梯度算子为一阶导数算子. 对于一个灰度图像函数, 其梯度可表示成一个向量., 其中从向量分析可知, 梯度向量坐标指向坐标的灰度值的最大变化率的地方. 向量的幅度和方向角分别为梯度幅值的计算通常采用计算量更小的绝对值来近似:以上各式的偏导数需要对每个像素的位置计算, 在实际中常用小区域模板进行卷积来近似计算. 对和各用一个模板, 将两个模板组合起来就构成一个梯度算子, 根据模板的元素值和大小的不同构造不同的算子, 常见的有Roberts、Sobel、Prewitt、Canny边缘检测算子等[3]. 对比各个算子后, 本文采用Sobel边缘检测, Sobel算子基于图像的梯度值进行边缘检测, 具有一定的降噪能力, 相较于其他边缘检测算子, Sobel算子运算比较简单, 是最常用的边缘检测算法[4]. 由于本设计采用的是Simulink自带的边缘检测模块, 所以不必对Sobel算法做过多的研究.2.1 SimulinkSimulink是MATLAB最重要的组件之一, 是在MATLAB中基于帧的视频图形处理的系统仿真软件, 是实现动态系统建模、仿真和分析的集成环境. 在该环境中, 无需大量编写程序代码, 设计的流程在Simulink中以图形形式描述算法[5]. Simulink已被广泛应用于控制理论和数字信号处理的复杂仿真和设计. 同时各种时变系统, 包括通讯、控制、信号处理、视频处理和图像处理系统, Simulink提供了交互式图形化环境和可定制模块库来对其进行设计、仿真、执行和测试. Simulink 中的Computer Vision System Toolbox(机器视觉工具箱)工具可以非常方便地进行视频图像的帧处理.2.2 ModelSimModelSim是Model Technology(Mentor Graphics的子公司)HDL硬件描述语言的仿真工具, 使用该软件可实现对设计的Verilog HDL、VHDL或者是两种语言混合的程序进行仿真[6]. ModelSim是业界最优秀的HDL语言仿真器, 具有快速的仿真性能和最先进的调试能力, 支持众多的FPGA和ASIC厂家库, 是做FPGA、ASIC设计的RTL级和门级电路仿真的首选. 同是它具有即丰富又易用的图形用户界面, 提供最友好的调试环境, 为加快调试提供强有力的手段[7].3.1 在Simulink中实现Sobel边缘检测数字视频是数字多媒体的重要组成部分, 数字视频是数字图像在时间轴上的扩展, 可以将视频的每一帧视为一幅静止的图像. 由此可见, 视频序列图像由一帧一帧具有相互关联的图像构成, 对视频图像的分析处理可以转化成对每一帧的处理[8]. 随着现在视频处理的分辨率越高及视频图像的尺寸越大, 从而对视频处理的难度也随之变高, 同时在FPGA上用Verilog HDL进行视频图形处理的描述更为复杂.在这里, 我们采用Simulink中的Comupter Vision System Toolbox(机器视觉工具箱)以及MathWorks公司最新推出的Vision HDL Toolbox工具箱来搭建本系统设计模型. Comupter Vision System Toolbox进行图像处理是基于帧的, 但是FPGA用Verilog HDL描述的处理算法是基于像素的, 因此我们采用Vision HDL Toolbox中的Frame to Pixels模块进行帧到像素流的转换, 该模块把全帧的视频格式转换成像素流pixel和控制总线ctrl, 用该模块来产生针对HDL代码产生的子系统的输入, 需要注意的是该模块并不会产生HDL代码. 输出的控制总线ctrl与串行像素数据有关, 该总线包含5个布尔信号来表示像素的有效性和其在一帧中的位置, 即行的起始像素信号hStart、行结束像素信号hEnd、场中第一行的第一个像素信号vStart、场中最后一行的最后一个像素信号vEnd 、任何有效像素信号valid. 这五个信号都是由该模块根据一帧中的像素自行控制, 不需要人为设置, 从而使得自动转换成像素流数据更为方便和准确[9].接下来在一个子系统中建立实现基于像素流的边缘检测, 命名该子系统为HDL Algorithm, 在HDL Algorithm中建立一个边缘检测模块Edge Detector, 并在该模块的参数设置框中选择Method栏为Sobel, 阈值为13. Edge Detector的输入为经Frame to Pixels模块转换后的像素流数据和控制总线信号, 输出则为经边缘检测处理后的像素和控制总线信号. HDL Algorithm子系统内部的Edge Detector模块如图1所示.为了验证基于像素流的边缘检测效果与基于帧的处理效果的一致性, 所以搭建的系统包含基于帧和基于像素流的处理, 以便进行对比. 基于帧的边缘检测的阈值也必须和基于像素流处理的阈值一样, 即13, 最后通过显示模块进行对比. 系统级模型如图2所示[10].3.2 结果分析本设计采用的视频源为RGB格式视频, 所以需把Full Multimedia File模块的输出图像参数设为灰度图像后进行处理. 最终运行的结果分别如图3、图4、图5所示. 图3 灰度化后的视频源图4 基于帧的边缘检测图5 基于像素流的边缘检测由以上的运行结果可知, 图3为待处理的灰度视频图形, 图4为基于帧的边缘检测, 图5为基于像素流的边缘检测. 从图4和图5可以验证把帧转换成像素流进行处理的可行性, 经对比两者的效果完全一致. 从而可以证明在Simulink中基于帧的边缘检测与经帧转换成像素流进行边缘检测的效果相同.3.3 产生Verilog HDL代码根据Simulink的用法只能对子模块产生HDL代码, 所以必须在建立子系统的子系统中搭建边缘检测模块, 即建立子系统HDL Algorithm, 并在其内部添加边缘检测模块. 运行成功后将HDL Algorithm模块通过设置HDL Workflow Advisor从而生成可读的、可追踪的Verilog HDL代码. 如图6所示.图6 HDL Workflow Advisor中设置代码生成4 仿真验证由于之前已经验证基于帧的边沿检测与经过帧转换成像素流的边缘检测效果一样, 所以重新搭建一个基于像素流的边缘检测模型, 然后把边沿检测模块自动产生Verilog HDL代码. 为了验证自动产生Verilog HDL代码与搭建的模型是否一致, 则需要采用Simulink与ModelSim联合仿真进行HDL验证. 在Simulink中搭建系统级测试平台, 用系统级平台作为测试的激励, ModelSim运用Verilog HDL代码, 输入为系统级输入, 输出为从Modelsim拿出与系统级模型作对比, 从而来验证产生的HDL代码与模型的一致性. 系统级测试平台如图7所示.ModelSim的仿真结果如图8所示. 根据ModelSim的仿真波形可以观察到: 当ctrlIn_valid、ctrl_hStart和ctrl_vStart为高电平时, 开始输入经帧转换成像素流的像素, 当ctrl_hEend和ctrl_hVend为高电平是分别表示一行像素输入完毕和一帧像素输入完毕. 同时, 经边缘检测处理后的边沿输出和控制总线ctrl的5个信号也完全符合时序. 从而可以证明自动产生Verilog HDL代码与搭建的模型是完全一致.图7 ModelSim与Simulink联合仿真平台图8 ModelSim仿真波形图最后自动生成的边缘检测模块的Verilog HDL代码在QuartusII上编译成功,编译报告如图9所示. 以及最后生产生成的RTL图如图10所示.图9 QuartusII编译报告从编译报告可已看出自动生成的边缘检测算法的Verilog HDL代码没有错误, 以及从生成的RTL图的输入输出口可以看出在时钟和5个控制信号的作用下输入8位的像素流数据, 经边缘检测处理后输出边缘和5个输出控制信号. 并且可以证明通过Frame to Pixels模块的确将帧数据转换成了像素流数据作为边缘检测的输入. 图10 边缘检测算法的RTL图5 结语本文在Simulink上搭建系统级模型, 通过验证基于帧的边缘检测与通过Vision HDL Toolbox工具箱把帧转换成像素流后进行的边缘检测的效果一样后, 令基于像素流的边缘检测算法自动生成可读的、可追踪的Verilog HDL代码. 最终利用Simulink和ModelSim联合仿真来验证产生的Verilog HDL代码与算法模块的一致性, 以及利用QuartusII验证算法代码的正确性. 采用这种方法可以快速生成视频图像处理算法的HDL, 与传统人为编写图像帧转换成像素流的代码和图像处理代码相比, 这种方法更快、更准确. 在如今的大容量、高清视频处理中更能体现这一方法的价值.1 侯法柱.基于FPGA的图像采集与处理系统设计[硕士学位论文].长沙:湖南大学,2010.2 MATLAB技术联盟张岩. MATLAB图像处理超级学习手册,北京:人民邮电出版社, 2014:269-271.3 熊晓薇.基于FPGA的视频图像处理的研究与实现[硕士学位论文].石家庄:河北大学, 2014.4 杨光耀.基于FPGA的图像采集及处理系统设计[硕士学位论文].呼和浩特:内蒙古大学, 2014.5 GBailey D.原魁,何文浩,肖晗译.基于FPGA的嵌入式图像处理系统设计.北京:电子工业出版社,2013:70-71.6 华清远见嵌入式培训中心.FPGA应用开发入门与典型实例.北京:人民邮电出版社,2008:243-244.7 葛亚明,彭永丰,薛冰等.零基础学FPGA基于Altera FPGA器件&Verilog HDL语言.北京:机械工业出版社,2010:176- 177.8 赵小川,何灏,缪远诚等.MATLAB数字图像处理实战.北京:机械工业出版社,2013:148-149.9 Frame To Pixels User’s Guide. MathWorks Inc, 2015.10 Edge Det ection and Image Overlay User’s Guide. MathWorks Inc, 2015. Realization of Edge Detection Algorithm Based on FPGA by Simulink WANG Shui-Yu, WANG Xin(College of Automatic and Information, Xi’an University of Technology, Xi’an 710048, China )Abstract:The algorithm based on FPGA to achieve high definition and large capacity video processing has certain complexity. In order to use the Verilog HDL to describe the image processing algorithms better, a set of video image processing model in Simulink is used. MathWorks company’s latest Vision HDL Toolbox is used in the conversion from frame to pixel stream, and then image edge is detected. Finally, the feasibility of the method of this algorithm automatically generating Verilog HDL is verified by using Simulink and ModelSim co-simulation. That could quickly generate more accurate HDL code, improving the speed of description of the image processing algorithm using HDL.Key words:FPGA; Simulink; Verilog HDL; ModelSim; HDL①收稿时间:2015-08-18;收到修改稿时间:2015-10-083.2 结果分析本设计采用的视频源为RGB格式视频, 所以需把Full Multimedia File模块的输出图像参数设为灰度图像后进行处理. 最终运行的结果分别如图3、图4、图5所示. 由以上的运行结果可知, 图3为待处理的灰度视频图形, 图4为基于帧的边缘检测, 图5为基于像素流的边缘检测. 从图4和图5可以验证把帧转换成像素流进行处理的可行性, 经对比两者的效果完全一致. 从而可以证明在Simulink中基于帧的边缘检测与经帧转换成像素流进行边缘检测的效果相同.3.3 产生Verilog HDL代码根据Simulink的用法只能对子模块产生HDL代码, 所以必须在建立子系统的子系统中搭建边缘检测模块, 即建立子系统HDL Algorithm, 并在其内部添加边缘检测模块. 运行成功后将HDL Algorithm模块通过设置HDL Workflow Advisor从而生成可读的、可追踪的Verilog HDL代码. 如图6所示.由于之前已经验证基于帧的边沿检测与经过帧转换成像素流的边缘检测效果一样, 所以重新搭建一个基于像素流的边缘检测模型, 然后把边沿检测模块自动产生Verilog HDL代码. 为了验证自动产生Verilog HDL代码与搭建的模型是否一致, 则需要采用Simulink与ModelSim联合仿真进行HDL验证. 在Simulink中搭建系统级测试平台, 用系统级平台作为测试的激励, ModelSim运用Verilog HDL代码, 输入为系统级输入, 输出为从Modelsim拿出与系统级模型作对比, 从而来验证产生的HDL代码与模型的一致性. 系统级测试平台如图7所示.ModelSim的仿真结果如图8所示. 根据ModelSim的仿真波形可以观察到: 当ctrlIn_valid、ctrl_hStart和ctrl_vStart为高电平时, 开始输入经帧转换成像素流的像素, 当ctrl_hEend和ctrl_hVend为高电平是分别表示一行像素输入完毕和一帧像素输入完毕. 同时, 经边缘检测处理后的边沿输出和控制总线ctrl的5个信号也完全符合时序. 从而可以证明自动产生Verilog HDL代码与搭建的模型是完全一致.最后自动生成的边缘检测模块的Verilog HDL代码在QuartusII上编译成功,编译报告如图9所示. 以及最后生产生成的RTL图如图10所示.从编译报告可已看出自动生成的边缘检测算法的Verilog HDL代码没有错误, 以及从生成的RTL图的输入输出口可以看出在时钟和5个控制信号的作用下输入8位的像素流数据, 经边缘检测处理后输出边缘和5个输出控制信号. 并且可以证明通过Frame to Pixels模块的确将帧数据转换成了像素流数据作为边缘检测的输入. 本文在Simulink上搭建系统级模型, 通过验证基于帧的边缘检测与通过Vision HDL Toolbox工具箱把帧转换成像素流后进行的边缘检测的效果一样后, 令基于像素流的边缘检测算法自动生成可读的、可追踪的Verilog HDL代码. 最终利用Simulink和ModelSim联合仿真来验证产生的Verilog HDL代码与算法模块的一致性, 以及利用QuartusII验证算法代码的正确性. 采用这种方法可以快速生成视频图像处理算法的HDL, 与传统人为编写图像帧转换成像素流的代码和图像处理代码相比, 这种方法更快、更准确. 在如今的大容量、高清视频处理中更能体现这一方法的价值.1 侯法柱.基于FPGA的图像采集与处理系统设计[硕士学位论文].长沙:湖南大学,2010.2 MATLAB技术联盟张岩. MATLAB图像处理超级学习手册,北京:人民邮电出版社, 2014:269-271.3 熊晓薇.基于FPGA的视频图像处理的研究与实现[硕士学位论文].石家庄:河北大学, 2014.4 杨光耀.基于FPGA的图像采集及处理系统设计[硕士学位论文].呼和浩特:内蒙古大学, 2014.5 GBailey D.原魁,何文浩,肖晗译.基于FPGA的嵌入式图像处理系统设计.北京:电子工业出版社,2013:70-71.6 华清远见嵌入式培训中心.FPGA应用开发入门与典型实例.北京:人民邮电出版社,2008:243-244.7 葛亚明,彭永丰,薛冰等.零基础学FPGA基于Altera FPGA器件&Verilog HDL语言.北京:机械工业出版社,2010:176- 177.8 赵小川,何灏,缪远诚等.MATLAB数字图像处理实战.北京:机械工业出版社,2013:148-149.9 Frame To Pixels User’s Guide. MathWorks Inc, 2015.10 Edge Detection and Image Overlay User’s Guide. MathWor ks Inc, 2015.。

哈夫变换用于边缘检测的原理

哈夫变换用于边缘检测的原理

哈夫变换是一种强有力的图像处理技术,它可以用来检测图像中的边缘。

它通过将图像中的像素点转换成曲线和曲面来实现边缘检测。

哈夫变换的基本原理是利用梯度曲线来表示图像中像素点的变化。

通过计算梯度曲线在X和Y方向上的斜率,可以获得图像中像素点的变化率,从而检测出图像中的边缘。

哈夫变换的优点是它可以检测出图像中的像素点的变化,而不必考虑其他因素,比如光照、颜色等。

另外,它可以检测出图像中几乎所有类型的边缘,包括水平、垂直和斜率边缘。

哈夫变换还可以用来处理高斯噪声,这是一种常见的图像噪声,它可以对图像产生负面影响,哈夫变换可以有效的去除这种噪声,从而提高图像的质量。

哈夫变换是一种强有力的图像处理技术,可以用来检测图像中的边缘,同时还可以用来处理高斯噪声,从而提高图像的质量。

基于HDL-64E激光雷达道路边界实时检测算法

基于HDL-64E激光雷达道路边界实时检测算法王俊;孔斌;王灿;杨静【期刊名称】《合肥工业大学学报(自然科学版)》【年(卷),期】2018(041)008【摘要】为了使智能车辆在多种道路环境中能够快速有效地提取前方道路,文章提出一种基于HDL-64E激光雷达的道路边界检测算法.该算法首先对激光雷达数据进行空间邻域分析,获取平滑度特征图像;然后利用自适应方向边界搜索算法获取候选道路边界激光雷达数据;为了解决激光雷达数据中存在的干扰及不连续问题,对候选道路边界激光雷达数据进行聚类分析及曲线拟合.实验结果表明,在高速、城区以及乡村道路环境下,该算法能够实时、准确地提取道路边界信息,满足智能车辆道路环境建模及路径规划的需要.【总页数】6页(P1029-1034)【作者】王俊;孔斌;王灿;杨静【作者单位】中国科学院合肥智能机械研究所,安徽合肥 230031;中国科学技术大学信息科学技术学院,安徽合肥 230026;中国科学院合肥智能机械研究所,安徽合肥230031;中国科学技术大学信息科学技术学院,安徽合肥 230026;中国科学院合肥智能机械研究所,安徽合肥 230031;中国科学院合肥智能机械研究所,安徽合肥230031【正文语种】中文【中图分类】TP391.41【相关文献】1.基于3D激光雷达城市道路边界鲁棒检测算法 [J], 孙朋朋;赵祥模;徐志刚;闵海根2.基于激光雷达的道路边界检测的研究 [J], 谭宝成;严征3.基于3D激光雷达道路边缘实时检测算法的研究与实现 [J], 李强;杜煜4.基于3D激光雷达点云的道路边界识别算法 [J], 孔栋;孙亮;王建强;王晓原5.基于三维激光雷达的道路边界提取和障碍物检测算法 [J], 王灿; 孔斌; 杨静; 王智灵; 祝辉因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

(ㄚ㿬) ԩ䀁㿜䙞㎷⁶␀䳏䏃? (SOC) (Verilog)Abstract䙞㎷⁶␀䳏䏃(edge detection circuit) 㽟ⱘ 䳏䏃DŽIntroduction䃖ⱘ䙞㎷⁶␀ˈㇵ ⱘ䁾 ϔ clock ⱘ⢔ Ⳃ clock ⢔ ⱘ↨䓗ˈ㢹⬅0䅞1ˈ Ϟ ⊓⁶␀䳏䏃(posedge edge detection circuit)( 々Ϟ㎷ 䳏䏃)ˈ㢹 ⬅1䅞0ˈ ϟ ⊓⁶␀䳏䏃(negedge edge detection circuit)( 々ϟ㎷ 䳏䏃)ˈ㢹Ϟ ⊓㟛ϟ ⊓䛑㽕⁶␀ˈ 䲭⊓⁶␀䳏䏃䳏䏃(double edge detection)DŽՓ⫼⪄ ˖Quartus II 7.2 SP3Ϟ ⊓⁶␀䳏䏃(posedge detection circuit)Method 1˖Փ⫼ regr_data_in0㟛r_data_in1⚎D-FF ˈ hold ԣϞϔ clock 㟛Ⳃ clock ⱘi_data_in ˈ 䃖Ϟ ⊓䳏䏃ˈ i_data_in ⬅0䅞1ˈг r_data_in0⚎0Ϩr_data_in1⚎1ˈ ⫼not r_data_in0ˈП ⫼and 䗷 r_data_in1DŽ1/*2(C) OOMusou 2008 posedge_detection.v / Verilog 34Filename : posedge_detection.v 5Compiler : Quartus II 7.2 SP36Description : Demo how to design posedge detection circuit7Release: 07/06/2008 1.08*/910module posedge_detection (11input clk,12input rst_n,13input i_data_in,14output o_rising_edge15);1617reg r_data_in0;18reg r_data_in1;1920assign o_rising_edge =~r_data_in0 & r_data_in1;2122always@(posedge clk,negedge rst_n) begin23if(!rst_n) begin24r_data_in0 <=0;25r_data_in1 <=0;26end27else begin28r_data_in0 <= r_data_in1;29r_data_in1 <= i_data_in;30end31end3233endmodule䗭。

⊩㍧䘢 ˈ 㙄 ⱘ ⫼ϔ 2 bitⱘD-FFˈ㟛ϔ ANDDŽMethod 2˖Փ⫼1 reg 1/*2(C) OOMusou 2008 posedge_edgedetection2.v / Verilog㢹Դ㾎 Method 1↨䓗ϡ ⧚㾷ˈ䙷Method 2 䴲 ⱘbehavior ˈ Փ⫼ϔ reg 㿬ԣ ϔ clock ⱘ⢔ ˈϺ 䗭 clock ϔ ⢔ ⚎0ϨⳂ ⢔ ⚎1ˈ䗭ῷ posedge њDŽ34Filename : posedge_detection2.v5Compiler : Quartus II 7.2 SP36Description : Demo how to design posedge detection circuit 7Release : 08/11/2008 1.08*/910module posedge_detection2 (11input clk,12input rst_n,13input i_data_in,14output reg o_rising_edge15);1617reg r_data_in0;1819always @(posedge clk,negedge rst_n) begin20if (!rst_n)21r_data_in0 <=0;22else begin23r_data_in0 <= i_data_in;2425if ({r_data_in0, i_data_in} ==2'b01)26o_rising_edge <=1;27else28o_rising_edge <=0;29end30end3132endmodule䗭。

⊩㍧䘢 П ˈ ϔ D-FF㟛EQUALˈ 䙞ⱘo_rising_edgeⱘD-FF Џ㽕 ⚎ always block ⱘregDŽ䗭 ՟ 㗠㿔ˈMethod 1㟛Method 2Ⳃ Quartus II 7.2 SP3ⱘ ϟresource ˈlogic element ⫼ D-FF㟛㟛ϔ ㌘ 䳏䏃ˈϡ䘢Method 2ⱘcode 䅔 ↨䓗催DŽϟ ⊓⁶␀䳏䏃(negedge detection circuit)r_data_in2㟛r_data_in1⚎regˈ holdԣϞϔ clock㟛Ⳃ clockⱘi_data_inˈ 䃖ϟ ⊓䳏䏃ˈ i_data_in⬅1䅞0ˈг r_data_in2⚎1Ϩr_data_in1⚎0ˈ ⫼not r_data_in1ˈП ⫼and䗷 r_data_in2DŽMethod 1˖Փ⫼ reg 1/*2(C) OOMusou 2008 nededge_detection.v / Verilog34Filename : nededge_detection.v5Compiler : Quartus II 7.2 SP36Description : Demo how to design nededge detection circuit 7Release : 07/06/2008 1.08*/9module negedge_detection (10input clk,11input rst_n,12input i_data_in,13output o_falling_edge14);1516reg r_data_in0;17reg r_data_in1;1819assign o_falling_edge = r_data_in0 &~r_data_in1;2021always @(posedge clk,negedge rst_n) begin22if (!rst_n) begin23r_data_in0 <=0;24r_data_in1 <=0;25end26else begin27r_data_in0 <= r_data_in1;28r_data_in1 <= i_data_in;29end30end3132endmoduleMethod 2˖Փ⫼1 reg1/*nededge_detection2.v2(C) OOMusou 2008 34Filename: nededge_detection2.v5Compiler: Quartus II 7.2 SP36Description : Demo how to design nededge detection circuit 7Release: 07/06/2008 1.08*/9module negedge_detection2 (10input clk,11input rst_n,12input i_data_in,13output reg o_falling_edge14);1516reg r_data_in0;1718always@(posedge clk,negedge rst_n) begin19if(!rst_n)20r_data_in0 <=0;21else begin22r_data_in0 <= i_data_in;2324if({r_data_in0, i_data_in} ==2'b10)25o_falling_edge <=1;26else27o_falling_edge <=0;28end29end3031endmodule䲭⊓⁶␀䳏䏃䳏䏃(double edge detection)r_data_in2㟛r_data_in1⚎regˈ holdԣϞϔ clock㟛Ⳃ clockⱘi_data_inˈ 䃖䲭⊓䳏䏃ˈ i_data_in⬅1䅞0ˈ 㗙⬅0䅞1ˈг r_data_in2⚎1Ϩr_data_in1⚎0ˈ 㗙r_data_in2⚎0Ϩr_data_in1⚎1 ˈ ⫼xor r_data_in1㟛r_data_in2DŽMethod 1˖Փ⫼2 reg 1/*2(C) OOMusou 2008 doubleedge_detection.v / Verilog34Filename : doubleedge_detection.v5Compiler : Quartus II 7.2 SP36Description : Demo how to design double edge detection circuit 7Release : 07/06/2008 1.08*/910module doubleedge_detection (11input clk,12input rst_n,13input i_data_in,14output o_double_edge15);1617reg r_data_in0;18reg r_data_in1;1920assign o_double_edge = r_data_in0 ^ r_data_in1;2122always @(posedge clk,negedge rst_n) begin23if (!rst_n) begin24r_data_in0 <=0;25r_data_in1 <=0;26end27else begin28r_data_in0 <= r_data_in1;29r_data_in1 <= i_data_in;30end31end3233endmoduleMethod 2˖Փ⫼1 regdoubleedge_detection2.v / Verilog1/*2(C) OOMusou 2008 34Filename: doubleedge_detection2.v5Compiler: Quartus II 7.2 SP36Description : Demo how to design double edge detection circuit 7Release: 07/06/2008 1.08*/910module doubleedge_detection2 (11input clk,12input rst_n,13input i_data_in,14output reg o_double_edge15);1617reg r_data_in0;1819always@(posedge clk,negedge rst_n) begin20if(!rst_n)21r_data_in0 <=0;22else begin23r_data_in0<= i_data_in;2425if({r_data_in0, i_data_in} ==2'b10)26o_double_edge <=1;27else if({r_data_in0, i_data_in} ==2'b01)28o_double_edge <=1;29else30o_double_edge <=0;3132// another method33// o_double_edge <= r_data_in0 ^ i_data_in;34end35end3637endmodule ⺐ϟ䓝posedge_detection.7zposedge_detection2.7znegedge_detection.7znegedge_detection2.7zdoubleedge_detection.7zdoubleedge_detection2.7zConclusionҔ咐 Փ⫼䗭。