基于FPGA的电梯控制系统的仿真图(附程序)

基于FPGA的电梯控制器设计.

输出信号

锁定的引脚

door

PIN(78)

Position[3]

PIN(46)

Position[2]

PIN(45)

Position[1]

PIN(44)

Position[0]

PIN(39)

q

PIN(94)

up_down

PIN(95)

输出信号共7个door为门信号,当door=’1’时表示为门开,当door=’0’时表示门关;position[3]、position[2]、position[1]、position[0],为控制数码管显示的输出引脚;q为警告指示信号,当触发警告warm时q=’1’’则超载,当q=’0’时则没事;up_down为上下楼层显示信号,当up_down=’1’时表示电梯正在向上运行,当up_down=’0’时表示电梯正在向下运行。

Button[1]

PIN(70)

Button[0]

PIN(73)

floor[2]

PIN(80)

floor[1]

PIN(81)

floor[0]

PIN(82)

reset

PIN(83)

warm

PIN (57)

输入共10个信号,clk为输入脉冲,提供时钟,信号Button[3]为三楼外下降请求信号,Button[2]为二楼外下降请求信号,Button[1]为二楼外上升请求信号,Button[0]为一楼外上升请求信号;floor[2]为电梯内三层请求信号,floor[1]为电梯内二层请求信号,floor[0]为电梯内一层请求信号;reset为复位信号;warm为警告信号。

指导教师(签名):

教研室主任(签名):

基于FPGA的电梯控制器系统设计

基于FPGA的电梯控制器系统设计本文首先提出了一种基于有限状态机的电梯控制器算法,然后根据该算法设计了一个三层电梯控制器,该电梯控制器的正确性经过了仿真验证和硬件平台的验证。

本文的电梯控制器设计,结合了深圳信息职业技术学院的实际电梯的运行情况,易于学生理解和接受,对于工学结合的教学改革,是一个非常好的实践项目。

另外,本文提出的电梯控制器算法适合于任意楼层,具有很强的适应性和实用性。

电子设计自动化技术是19世纪末21世纪初新兴的技术,其在数字电路设计和日常的控制系统中已经体现了强大的功能和优势。

随着EDA技术的高速发展,电子系统设计技术和工具发生了深刻的变化,大规模可编程逻辑器件FPGA的出现,给设计人员带来了诸多的方便。

HDL(硬件描述语言)是随着可编程逻辑器件(PLD)发展起来的,主要用于描述数字系统的结构、行为、功能和接口,是电子设计自动化(EDA)的关键技术之一。

它通常采用一种自上而下的设计方法,即从系统总体要求出发进行设计。

目前从期刊杂志中看到一些采用FPGA实现电梯控制系统的设计文章,在这些文章中看不到针对任意楼层的控制器算法,而针对任意层数的控制器算法是保证控制器实用性和适用性的关键。

因此,本文尝试采用EDA技术来设计一个N层电梯控制系统,具体思路是:首先给出电梯控制器的算法,然后在硬件平台上实现并验证。

1 电梯控制系统要求电梯控制系统通常包含图1中的功能:电梯升、降、停;电梯门开、关;请求信号显示、楼层显示;超载、故障报警。

其中超载、故障报警需要用到传感器,该控制相对比较简单,因此本文不再展开讨论。

本文着重讨论涉及其他功能的控制器算法。

针对第一教学楼的电梯,其电梯控制器实现了以下功能:(1)电梯内部每层均有相应的STop按钮;电梯外部除顶层外每层都有up按钮,除底层外每层都有down按钮;up按钮被按下表示该层有人要去高层,down按钮被按下表示该层有人要去低层,stop按钮被按下表示该层有人要出电梯。

基于FPGA的电梯控制器

基于FPGA的电梯控制器唐山学院EDA技术课程设计题目基于FPGA的电梯控制器设计系(部) 信息工程系班级姓名学号指导教师2013 年1 月7 日至1 月11 日共 1 周2013年1 月10 日《EDA技术》课程设计任务书课程设计成绩评定表目录1 前言 (1)2 EDA技术介绍 (2)2.1 EDA技术简介 (2)2.2 EDA技术的发展 (2)3 电梯控制器设计 (3)3.1 电梯控制器设计总体框图 (3)3.2 电梯控制器设计思路 (3)3.3 电梯处于各楼层的具体分析 (4)3.4 电梯外部端口具体说明 (6)3.4.1 定义各个端口 (6)3.4.2 引脚锁定 (6)4 仿真结果与说明 (8)5 总结 (10)参考文献 (11)附录程序代码 (12)1 前言当今社会,随着城市建设的不断发展,高层建筑的不断增多,电梯作为高层建筑中垂直运行的交通工具已与人们的日常生活密不可分。

目前电梯控制系统主要有三种控制方式:继电路控制系统(“早期安装的电梯多位继电器控制系统”)、FPGA/CPLD的控制系统、微机控制系统。

继电器控制系统由于故障率高、可靠性差、控制方式不灵活以及消耗功率大等缺点,目前已逐渐被淘汰,微机控制系统虽在智能控制方面有较强的功能,但也存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷。

而FPGA/CPLD控制系统由于运行可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点,倍受人们重视等优点,已经成为目前在电梯控制系统中使用最多的控制方式,目前也广泛用于传统继电器控制系统的技术改造。

随着EDA技术的快速发展,电子设计自动化(EDA)逐渐成为重要的设计手段,已经广泛应用于模拟与数字电路系统等许多领域。

采用EDA设计,拥有电子系统小型化、低功耗、高可靠性、开发过程投资小、周期短等优点,而且还可以通过软件编程对硬件结构和工作方式进行重构,使得硬件设计如软件设计那般方便快捷。

基于FPGA的智能化电梯的设计

基于FPGA的智能化电梯的设计指导教师 : 黄智伟王彦黄松王凤玲余丽( 南华大学电气工程学院湖南衡阳 421001)摘要:介绍了基于FPGA的智能化电梯的电路设计。

该设计采用了可编程逻辑器件FPGA的ASIC 设计,并基于超高速硬件描述语言VHDL在Xilinx公司的SpartanⅡ系列的2sc200PQ208-5芯片上编程实现了整个系统的控制部分,整个自动控制系统由四个模块构成:分频模块、状态控制模块、译码显示模块、模拟门模块。

该设计不仅仅实现了一般电梯的功能,其特别之处是实现了电梯的“智能化”:融入了“智能化”的调度规则、开/关门自动保护功能、超载提示功能等诸多“人性化”的设计。

关键字:可编程逻辑器件超高速硬件描述语言电梯智能化The intelligent design of elevator based onFPGAMentor :Huang Zhiwei Wang YanHuang Song Wang FengLing Yu Li(The College of the Electrical Engineering Nanhua University HuNanHengYang 421001)abstract :The paper will introduce the intelligent design of the elevator based circuit on FPGA. The FPGA of Programmable Logic Devices (PLD) are used the design is the ASIC, it is programming with VHDL in the ICs of 2sc200PQ208-5 to realize the system , the ICs is the series of SpartanⅡ of the Xilinx Company. The auto control system is constituted of…four modules which is 111 a frequency division modes 、a control modes、a piece of translation display modes、and a simulant door modes .This elevator can not only realized the function of normal lift ,the special of the design is “intelligent”,and the idea of ” Humanization” designKeywords :PLD/FPGA VHDL elevator intelligent引言在现代社会和经济活动中,电梯已是城市物质文明的一种标志.在高层建筑中,电梯是不可缺少的垂直运输设备.电梯问世不过100多年,但发展神速.解放前的国产电梯,控制系统复杂,制造技术难度大,而且成本高、功能也少。

基于FPGA的电梯控制系统设计

36魁科■技2021年•第2期基于FPGA的电梯控制系统设计◊武汉轻工大学电气与电子工程学院陶云轩李素芬张祥武杨文卓使用FPGA器件作为主控制芯片,Quartus II作为编程软件,使用DE10-NAN0作为编程后的硬件板子,设计一个基于DE10-NAN0板的电梯控制系统,便于实现更多层电梯控制,有较强的灵活性。

电梯在生活中随处可见,大型的商城中、高档的酒店内都少不了电梯的身影。

现阶段,电梯控制系统硬件由轿厢操纵盘、厅门信号、PLC、变频器、调速系统构成,变频器只完成调速功能,而逻辑控制部分是由PLC完成的。

PLC负责处理各种信号的逻辑关系,从而向变频器发出起停信号,同时变频器也将本身的工作状态输送给PLC,形成双向联络关系已。

FPGA,其实是一种开发者在短时间内利用个人PC就可以在实现多次重写的廉价设备,是高密度可编程逻辑器件的主流产品葺具有运行效率高,操作简易易于实现大规模系统和二次开发的系统。

Quartus II是Altera公司的综合性CPLD/FPGA开发软件,原理图、VHDL、VerilogHDL以及AHDL(Altera Hardware支持DescriptionLanguage)等多种设计输入形式,内嵌自有的综合器以及仿真器,可以完成从设计输入到硬件配置的完整PLD设计流本研究将使用FPGA器件作为主控制芯片,Quartus n作为编程软件,设计〜基于DE10-NANO板五层电梯控制系统。

1电梯的控制要求冋(1)该电梯五层,除第一、五层,每层都设有上下键,一层设有上键,五层设有下键。

(2)电梯内有防超重系统、紧急呼叫按钮、故障指示灯、报警系统和楼MS®等。

(3)电梯到达指定楼层后,过2秒后电梯门打开,开门4s电梯开始关闭,再经过6s电梯开始上下行。

(4)电梯没有接到指令时,在3楼待命。

2系统设计2.1电梯控制器的模块设计电梯控制器主要由指令请求模块、电梯运行状态模块、显示模块、开关门模块、超重报警模块这五个模块组成。

基于FPGA的电梯控制器设计

基于FPGA的电梯控制器设计一、题目要求设计三层电梯控制器,要求能根据用户在电梯内外按下的命令键,实现上升、下降、停止等功能。

电梯内的命令键主要是前往1、2和3楼的按键;电梯外的命令键则主要是分布在电梯三个楼层的入口处,用以呼叫电梯到用户所在的楼层。

二、题目分析本设计主要由电梯控制模块和显示模块两部分组成,其中电梯控制模块又包含状态机、分频、按键扫描、延时等子模块,显示模块主要是通过数码管来完成,可以通过显示“UP”、“DOWN”、“OPEN”、“CLOSE”还有当前楼层数等字样来反映电梯当前状态。

以下是详细介绍。

(一)电梯控制模块电梯控制模块主要部分是一个由14个状态组成的状态机,包括上升、下降、停止、直接打开、等待电梯到来、电梯停稳、等待开门、等待关门、去第几层命令检测等。

电梯控制模块的输入输出端口主动是为该状态机服务的,现介绍模块的输入输出端口如下。

输入端口:up1,up2,up3分别是用户在电梯外部呼叫电梯的信号。

goto_floor1,goto_floor2,goto_floor3分别是用户在电梯内部选择去向的信号。

clk_in为50MHZ时钟信号输入。

rst为复位信号。

输出端口:open_door为开门标志位,当该位置1时为开门状态,当该为置0时为关闭状态。

display_up为上升显示标志位,当该为置1时,表示电梯正处于上升状态。

display_down为下降显示标志位,当该为置1时,表示电梯正处于下降状态。

各状态的定义如表1所示,状态间的切换如图1所示。

表1 状态对照表图1 状态切换图(二)显示模块显示模块主要由6个数目管完成,当电梯处于上升阶段时,会显示“UP”,当电梯处于下降时显示“dn”代表down,当电梯处于开门时显示“OPEN”,当电梯处于关门状态时,由于板载资源有限,显示“CLOE”代表CLOSE ,此外还有当店楼层显示。

整个系统的RTL级结构图如图2所示。

图2 系统RTL图三、程序代码1.电梯控制模块代码/*_______________________电梯控制模块__________________________*/ module Elevator(clk_in,rst,goto_floor1,goto_floor2,goto_floor3, //电梯里面请求去几楼buttonup1,up2,up3, //电梯外面请求去几楼button open_door,display_up,display_down,pos //状态标志作为输出);input clk_in,rst;input up1,up2,up3;input goto_floor1,goto_floor2,goto_floor3;output open_door,display_up,display_down;output pos; //当前楼层数reg open_door,display_up,display_down;reg [1:0] position;reg [3:0] state;reg [1:0] KeyFlag; //外面请求button值reg Cont; //计数标志reg [1:0]goto_floor;reg [27:0] wait_cnt; //计数延时变量reg [24:0] cnt; //分频计数变量wire goto_stop;wire CLK_OUT; //慢时钟扫描button用reg [1:0] pos; //记录当前位置//状态变量parameter[3:0]//wait for elevatorstop=0, //扫描buttonup=1, //电梯向上down=2, //电梯向下opendirect=3, //直接打开wait_evelator_coming=4, //电梯向上或者向下进行中 come_done=5, //电梯停稳wait_door_close=6, //等待电梯门关闭go_to_where=7, //电梯里面选择去哪里//on the elevetorup_d=8, //电梯里面的向上状态down_d=9, //电梯里面的向下状态wait_evelator_coming_d=10, //电梯里面的等待电梯到位 come_done_d=11, //电梯里面的到位完成 wait_door_open=12, //等待开门wait_door_close_d=13; //等待关门/*_______________________状态切换模块_________________________*/ always @ (posedge clk_in or negedge rst)beginif(!rst)beginpos = 1; //默认楼层初始值为1state = stop; //初始状态 stop扫描模式display_up = 0; //显示上升标志位display_down = 0; //显示下降标志位open_door = 0; //开门标志位Cont = 0; //计数标志endelsebegincase(state)/****扫描外部请求button****/stop:beginif(KeyFlag==1) //一楼有请求信号beginif(KeyFlag < pos) //如果电梯当前不是在1楼state = down; //下降elsestate = opendirect; //如在1楼,直接打开门endelse if(KeyFlag==2) //2楼有请求信号beginif(KeyFlag > pos) //如果电梯在1楼state = up; //上升else if(KeyFlag < pos) //如果电梯在3楼state = down; //下降elsestate = opendirect; //在二楼直接打开 endelse if(KeyFlag==3) //如果请求信号在3楼beginif(KeyFlag > pos) //如当期那位置不是在3楼state = up;elsestate = opendirect; //如当前位置在3楼 endelsestate = stop; //如果没有检测到正确值,继续检测 end/******电梯向上******/up:begindisplay_up = 1;state = wait_evelator_coming;end/******等待电梯到来******/wait_evelator_coming:begin Cont = 1;if(wait_cnt[26]==1)beginCont =0;pos = KeyFlag;state = come_done;endelsestate = wait_evelator_coming;end/******电梯已经到来******/come_done:beginopen_door=1;display_up = 0;display_down = 0;state = wait_door_close;end/******等待电梯关门******/wait_door_close:beginCont = 1;if(wait_cnt[26]==1)beginCont =0;pos = KeyFlag;open_door = 0;state = go_to_where;endelsestate = wait_door_close;end/******去哪里—电梯内部button扫描******/go_to_where:beginopen_door = 0;if(((goto_floor ==1) && (goto_floor <pos))|((goto_floor ==2) && (goto_floor < pos)))state = down_d;else if(goto_floor == pos) //elevator at currect pos floor nowstate = opendirect;else if(((goto_floor ==2) && (goto_floor >pos))|((goto_floor ==3) && (goto_floor > pos)))state = up_d;elsestate = go_to_where;end/******直接打开******/opendirect:beginopen_door = 1;state = wait_door_close;end/******检测外部button后,向下运行******/down:begindisplay_down = 1;state = wait_evelator_coming;end/******检测内部button后,向下运行******/down_d:begindisplay_up = 0;display_down = 1;state = wait_evelator_coming_d;end/******检测外部button后,向上运行******/ up_d:begindisplay_up = 1;state = wait_evelator_coming_d;end/******内部状态下,等待电梯到来******/ wait_evelator_coming_d:beginCont = 1;if(wait_cnt[26]==1)beginCont = 0;pos = goto_floor;state = come_done_d;endelsestate = wait_evelator_coming_d;end/******电梯已经到来******/come_done_d:begindisplay_up = 0;display_down = 0;pos = goto_floor;state = wait_door_open;end/******等待开门******/wait_door_open:beginCont = 1;if(wait_cnt[26]==1)beginCont = 0;open_door = 1;state = wait_door_close_d;endelsestate = wait_door_open;end/******等待关门******/wait_door_close_d:beginCont = 1;if(wait_cnt[26]==1)beginCont =0;open_door=0;state = stop;endelsestate = wait_door_close_d;endendcaseendend/*_____________________慢时钟分频模块________________________*/ always @ (posedge clk_in or negedge rst)beginif(!rst)cnt<=0;elsecnt<=cnt+1;endassign CLK_OUT = cnt[8];/*_______________外部button请求扫描模______________________*/ always @ (posedge CLK_OUT or negedge rst)beginif(!rst)KeyFlag<=0;else if(up1)KeyFlag<=1;else if(up2)KeyFlag<=2;else if(up3)KeyFlag<=3;end/*_________________内部button请求扫描模__________________________*/ always @ (posedge CLK_OUT or negedge rst)beginif(!rst)goto_floor<=0;else if(goto_floor1)goto_floor<=1;else if(goto_floor2)goto_floor<=2;else if(goto_floor3)goto_floor<=3;elsegoto_floor<=0;end/*___________________________延时模块______________________________*/ always @ (posedge clk_in or negedge rst)beginif(!rst)wait_cnt<=0;else if(Cont)wait_cnt<=wait_cnt+1;else if(!Cont)wait_cnt<=0;endendmodule2.显示模块代码/*________________________显示模块________________________*/ module display(clk,rst,display_up,display_down,pos,open_door, //标志位信号sm_db0,sm_db1,sm_db2,sm_db3,sm_db4,sm_db5,sm_db6,sm_db60); //数码管input clk,rst;input display_up,display_down;input [1:0]pos,open_door;output[6:0] sm_db0,sm_db1,sm_db2,sm_db3,sm_db4,sm_db5,sm_db6,sm_db60; reg[6:0] sm_db0,sm_db1,sm_db2,sm_db3,sm_db4,sm_db5,sm_db6,sm_db60;//数码管显示编码parameter segC = 7'hC6,segd = 7'hA1,segE = 7'h86,segL = 7'hC7,segN = 7'hC8,segO = 7'hc0,segP = 7'h8C,segU = 7'hC1,seg1 = 7'hf9,seg2 = 7'ha4,seg3 = 7'hb0,segdis = 7'hff;always @ (posedge clk or negedge rst)beginif(!rst)begin //复位显示关闭sm_db0 <= segdis;sm_db1 <= segdis;sm_db2 <= segdis;sm_db3 <= segdis;sm_db4 <= segdis;sm_db5 <= segdis;sm_db6 <= segdis;sm_db60 <= segdis;endelsebeginif(display_up && (!display_down)) //4 5数码管显示UPbeginsm_db5 <= segU;sm_db4 <= segP;endelse if(display_down && (!display_up)) //4 5 数码管显示 DN 代表downbeginsm_db5 <= segd;sm_db4 <= segN;endelsebeginsm_db5 <= segdis;sm_db4 <= segdis;endif(open_door) //0 1 2 3 数码管显示 OPENbeginsm_db3 <= segO;sm_db2 <= segP;sm_db1 <= segE;sm_db0 <= segN;endelse //open_door = 0 数码管显示 CLOEbeginsm_db3 <= segC;sm_db2 <= segL;sm_db1 <= segO;sm_db0 <= segE;endif(pos == 1) sm_db6 <= seg1;else if(pos == 2) sm_db6 <= seg2;else if(pos == 3) sm_db6 <= seg3;endendendmodule四、测试仿真1.测试代码timescale 1ns / 1psmodule test;// Inputsreg clk;reg rst;reg goto_floor1;reg goto_floor2;reg goto_floor3;reg up1;reg up2;reg up3;reg [1:0] seg7_sel;// Outputswire [7:0] seg7;wire led_flag;// Instantiate the Unit Under Test (UUT)top_elevator uut (.clk_in(clk),.rst(rst),.goto_floor1(goto_floor1),.goto_floor2(goto_floor2),.goto_floor3(goto_floor3),.up1(up1),.up2(up2),.up3(up3),.seg7(seg7),.seg7_sel(seg7_sel),.led_flag(led_flag));always # 1 clk =~clk;initialbegin// Initialize Inputsclk = 0;rst = 0;goto_floor1 = 0;goto_floor2 = 0;goto_floor3 = 0;up1 = 0;up2 = 0;up3 = 0;seg7_sel = 0;// Wait 100 ns for global reset to finish#100;rst = 1;up2 = 1;#20000;up2 = 0;//goto_floor3 = 1;//#20000;//goto_floor3 = 0;// Add stimulus hereendendmodule2.仿真结果图3 仿真效果五、实验效果图4 初始状态:楼层为1,电梯关闭图5 当2楼有用户呼叫,电梯状态为up图6 用户选择3楼为目的地并到达3楼,此时电梯门打开六、实验心得本次试验可谓感触颇多,通过题目要求的实现,较为系统的了解了FPGA的编程方法,对状态机也有了更进一步的认识,感谢在程序调试中出现的一系列问题,给了我学习知识的机会,也感谢老师和学长的帮助,最后,对本次作业如此长时间的迟交向老师表示深深的歉意!!。

基于FPGA的电梯控制器设计_毕业设计论文

(3)当电梯处于上升时,只响应比电梯所在位置高的上楼请求信号,直到最后一个上楼请求执行完毕,再进入下降模式。

(4)当电梯处于下降时,只响应比电梯所在位置低的下楼请求信号,直到最后一个下楼请求执行完毕,再进入上升模式。

(5)电梯的初始状态为第一楼层。

(6)设计超载报警功能。

设计要求:

(1)根据任务要求确定电路各功能模块;

(2)写出设计代码;

(3)给出时序仿真结果和硬件调试结果;

(4)最后要有设计总结。

二、设计原始资料

QuartusⅡ软件,EDA实验箱。

三、要求的设计成果(课程设计说明书、设计实物、图纸等)

软件仿真和硬件仿真结果;课程设计说明书。

四、进程安排

周1-周4:查阅资料,上机编写并调试代码;

3 电梯控制器设计

3.1 电梯控制器设计总体框图

电梯控制器的功能模块如图所示,包括主控制器、分控制器、楼层选择器、状态显示器、译码器和楼层显示器。乘客在电梯中选择所要到达的楼层,通过主控制器的处理,电梯开始运行,状态显示器显示电梯的运行状态,电梯所在楼层数通过译码器译码从而在楼层显示器中显示。分控制器把有效的请求传给主控制器进行处理,同时显示电梯的运行状态和电梯所在楼层数。由于分控制器相对简单很多,所以主控制器是核心部分。

2 EDA技术介绍

2.1 EDA技术简介

EDA是电子设计自动化(Electronic Design Automation)的缩写,在20世纪90年代初从计算机辅助设计(CAD)、计算机辅助制造(CAM)、计算机辅助测试(CAT)和计算机辅助工程(CAE)的概念发展而来的。EDA技术就是以计算机为工具,设计者在EDA软件平台上,用硬件描述语言VHDL完成设计文件,然后由计算机自动地完成逻辑编译、化简、分割、综合、优化、布局、布线和仿真,直至对于特定目标芯片的适配编译、逻辑映射和编程下载等工作。

基于FPGA的全自动电梯控制器的研究

基于FPGA的全自动电梯控制器的研究摘要当今社会,有三种关键的电梯控制系统,分别是采用硬件接线来实现操控的继电器操控体系和应用计算机参与获得一定操控目的的计算机操控体系以及可编程逻辑器件FPGA/CPLD的操控体系。

继电器操控体系连线复杂且运行效率逐渐被人们遗弃。

计算机操控体系虽然在继电器控制系统的基础上有所改进,但在某些方面依然存在一定的缺陷,比如:抗干扰性差、一人多机操控不便。

而FPGA操控体系的接口比较多,便于连接外接设备;运算速度快,采用VHDL编程语言,便于更改,设计的灵活性高;同时查错和排错的用时较短;所以FPGA控制系统被许多人所看重,并且成为当前最最流行的电梯控制系统。

关键词:电梯控制系统;FPGA; VHDL一、电梯控制器的工作原理1结构设计思想完成六层电梯的运转操控,是此次设计的紧要目标。

当乘客到达电梯前,想要上升并且准备前往目的楼层时,只需按下厅外呼叫按钮-上升键。

这时,电梯控制器会自动回应此申请,操控电梯抵达呼唤请求层,这时电梯门会主动敞开,乘客走进电梯内部,按下快速关门键和的想要前往的楼层的按键,这时电梯操控器会控制电梯进入上升运转形式,与此同时,在厢内,会在七段数码管上显示上升标志提示和上升到的楼层号。

当电梯运转到想要到达的层数后轿厢门主动敞开,搭乘电梯的人们走出轿厢。

就这样,电梯循环往复的执行着操控作用,运送着一批又一批的乘客。

电梯在运转过程中应遵照以下原则:当电梯处在升上去的时候,如果有想要搭乘电梯的人按下升上去的按钮,电梯只回应比它高的楼层。

从下到上顺次施行任务,直至完成所有的上升请求。

若是电梯在上升的行程中,有乘客按下下降申请按钮,那么,电梯控制器将控制电梯实施完全部的上升申请后,径直抵达有下降需求的顶峰楼层,乘客走进轿厢,电梯投入下降的运行方式。

同理假如电梯在下降的行程中,乘客有下楼申请,那么,电梯只回应比它当前所处位置楼层低的楼层请求,从上到下顺次施行,直至全部的下降申请都施行完毕。

基于FPGA的电梯控制系统的仿真图(附程序)

系统主体模块的设计与仿真本设计是以9层的电梯控制系统为模型。

主要实现电梯运行开关的控制,楼层的请求,电梯运行遵循的方向优先原则,提前、延时开关门等基本的功能。

以下是对不同的状态进行仿真,以验证本设计的可行性。

电梯进入运行状态控制进程,通过判断上升、下降请求寄存器每一位的值,决定电梯运行状态,并通过状态指示信号输出该状态,本设计都是使用高电平触发。

(1)当电梯处于1楼时,上升请求:图4.1 电梯处于第一层时仿真图(2)提前/延时关门功能没有提前/延时关门时的情况下:图4.2 没有提前/延时关门时的仿真图从图4.2知道,运行或停止输出信号“lamp”为高电平时电梯进入运行状态,低电平时停止。

圈内显示电梯在75.36us后从停止状态转入运行状态。

当设置提前关门“close”为高电平时:图4.3 有提前关门时的仿真图图4.3与图4.2对比可知,由于设置了提前关门进程“close”,电梯提前到75.36us 以前从停止状态转入运行状态。

2当设置了延时关门“delay”为高电平时:图4.4 延时关门时的仿真图图4.4与图4.2对比可知,由于设置了延时关门进程“delay”,电梯延时到80.48us 后才从停止状态转入运行状态。

(3)当电梯处于较高层数时图4.5 电梯处于较高层数时的仿真图(5)电梯轿厢内楼层选择开关功能仿真图4.6 轿厢内楼层选择开关仿真图4(4)电梯的次态功能仿真如图4.7所示,当运行或等待时间“run_wait”计数到0110时,电梯运行状态变量“ladd”给出电梯的下一个状态。

如图 4.7圈内显示,“ladd”从0显示模块的设计与仿真图4.8 显示模块仿真图本设计的显示模块一共有3个显示部分,分别是电梯运行/等待时间显示run_wait、楼层选择指示direct以及所在楼层批示st_out。

这3个显示部分的设计结构都是一样的,所以以其中一个仿真作为例子。

从图4.8圈内看到,当电梯处于楼层2时,ledin收到信号‘0010’,经过系统内部自动转化为‘1011011’并通过ledout输出到共阴极LED数码显示。

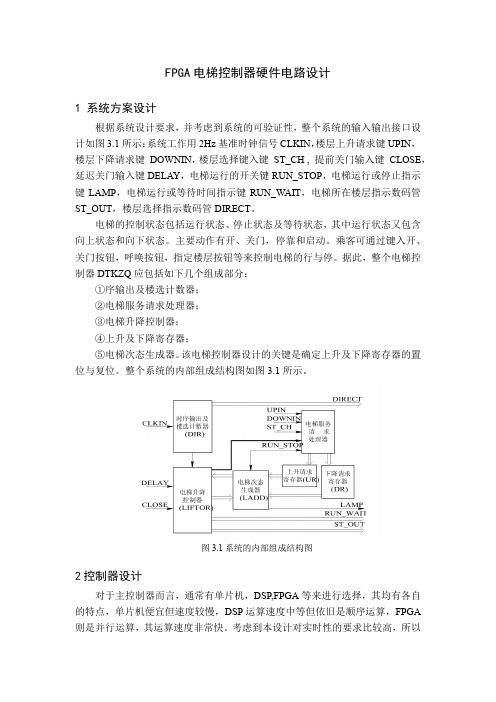

FPGA电梯控制器硬件电路设计

FPGA电梯控制器硬件电路设计1 系统方案设计根据系统设计要求,并考虑到系统的可验证性,整个系统的输入输出接口设计如图3.1所示:系统工作用2Hz基准时钟信号CLKIN,楼层上升请求键UPIN,楼层下降请求键DOWNIN,楼层选择键入键ST_CH , 提前关门输入键CLOSE,延迟关门输入键DELAY,电梯运行的开关键RUN_STOP,电梯运行或停止指示键LAMP,电梯运行或等待时间指示键RUN_WAIT,电梯所在楼层指示数码管ST_OUT,楼层选择指示数码管DIRECT。

电梯的控制状态包括运行状态、停止状态及等待状态,其中运行状态又包含向上状态和向下状态。

主要动作有开、关门,停靠和启动。

乘客可通过键入开、关门按钮,呼唤按钮,指定楼层按钮等来控制电梯的行与停。

据此,整个电梯控制器DTKZQ应包括如下几个组成部分:①序输出及楼选计数器;②电梯服务请求处理器;③电梯升降控制器;④上升及下降寄存器;⑤电梯次态生成器。

该电梯控制器设计的关键是确定上升及下降寄存器的置位与复位。

整个系统的内部组成结构图如图3.1所示。

图3.1系统的内部组成结构图2控制器设计对于主控制器而言,通常有单片机,DSP,FPGA等来进行选择,其均有各自的特点,单片机便宜但速度较慢,DSP运算速度中等但依旧是顺序运算,FPGA 则是并行运算,其运算速度非常快。

考虑到本设计对实时性的要求比较高,所以本次选用的FPGA是EP3C来作为本次设计的主控制器。

其电路图如下3.2所示。

图3.2 主控制器电路对于FPGA芯片来说它是一种由可编程逻辑器件来构成的微处理器。

FPGA 的内部采用其包括数据模块,引脚模块,连线资源等等,根据不同的型号其内部还具有不同的硬件架构其具有专门的硬件乘法器,采用并行操作,提供特殊的指令,可以用来快速的实现各种数字信号处理算法,一些高级的FPGA芯片其内部还加入了ARM等硬核资源,FPGA具有一些主要特点:①由于是并行运算所以在一个指令周期内可完成多次乘法和多次加法;②程序和数据空间可以进行配置,可以同时访问数据空间和程序空间;③片内具有快速RAM,通常可通过独立的数据总线同时访问两块芯片:④具有低开销或零开销循环及跳转的硬件支持;⑤具有在单周期内操作的多个硬件地址产生器;⑥快速的中断处理和硬件I/O支持;⑦可以并行执行多个操作,支持流水线操作,取指、译码和执行等操作可以流水执行。

基于FPGA的智能电梯系统的设计

路传器测 L 控 楼霍传器电 F 嚣控诃 层尔感) (感检 P G A 制速

体就能 自动重新开门。

参 考 文 献

电 它入号J 梯 输信 其

图 2 电梯控制系统硬件结构框 图

楼

[] 1 申彦春等. 于 F G 基 P A的 电梯控制 器的设计 [] I. 科技创新 导报 ,

控制组成 的模块 ,分别控制轿厢 的开关 门和按钮接 过之后需要记忆显

示 的发 光 二 极 管 电路 。 4结 论 .

指示呼叫系统随时显示轿厢 的运动方 向和所 在楼层 位置 。安全装置保

证 审. 运 行安 全 。 梯 3智 能 电梯 的 控 制 部 分 . ( ) 件设计 1硬

为 了改善 电梯 的舒 适感 和运行的可靠性 ,现都改为用 F G P A来控

制 电梯 的运行。F G P A同以往的 P L G L等相 比, P A的规 模较大 , A 、A FG 适合于时序 , 组合等逻辑 电路应用场合 。 但是系统仍有许 多需要改进的

苎皇 =竺兰 =竺 } : }

2智能电梯系统 的原理 . 智能电梯控制 系统原理框 图如 图 l 所示。

( G ) F A 等组 成。F G P P A集信号采集 、 信号输出及逻辑控制于一体 , 电 与 梯电力拖动系统一起实现 电梯控制 的所有功能 。高层 电梯控制 系统 由 呼叫到 响应 形成一次工作循环 , 电梯工作过程又分 为 自检 、 正常工作 、 强制工作等工作状态 。 电梯在三种工作状态之 间来 回切换 , 了完整 构成 的电梯工作 过程。 电梯控制 系统 的硬件结构如图 2 所示 。 为减少 F G P A输人输出点数 , 采用编码 的方式将 3 个呼叫及楼层 1 按钮编码五位二进制码输入 F G 。 P A

FPGA的自动升降电梯控制器的设计

3.方向优先控制方式方案

方向优先控制是指电梯运行到某一楼 层时先考虑这一楼层是否有请求:有 ,则停止; 无,则继续前进。 其效率远大于单向层层停等控制方式 的效率。 而且,方向优先控制方式 下,电梯在维持停止状态的时候可以 进入省电模式,又能节省大量电能。 本设计选择方向优先控制方式。

谢 谢!

控制器功能模块图

电梯控制方式

1.内部请求优先控制方式 2.单向层层停控制方式

3.方向优先控制方式

1.内部请求优先控制方式方案

在内部请求优先控制方式中,当 电梯外部人的请求和电梯内部人 的请求冲突时,外部人的请求信 号可能被长时间忽略,因而它不 能作为通用型电梯的设计方案。

2.单向层层停控制方式方案 这种方案的优点在于“面面俱 到”,然而这样不必要的等待消 耗了大量时间,而且电梯的运作 与用户的请求无关,当无请求时 电梯也照常跑空车,就浪费了大 量电能。 对用户而言,其请求响应时间也 不是很快,因而这不是理想的方 案。

FPGA技术的定义

FPGA是Field Programmable Gate Array的缩写,译为现场可编 程阵列,是一种数字集成电路。 FPGA芯片内部有大量的逻辑块, 这些逻辑块是可以编程的,逻辑块 之间的连接称为互连资源,这些互 连资源 也是可以编程的通过对逻辑块以及互连资源 的编程可以实现各种数字电路、数字系统的 设计。

FPGA的全自动电梯控 制系统的设计

指导老师: 2013-5

一、研究内容

Fpga简介

1.系统组成

基 于 FP GA 的 电 梯 控 制 系 统

二、研究现状

2.国外

2.国外

三、设计要求

2.国外

四、分析比较各个研 究的优点与缺点

基于FPGA的电梯控制器系统设计

基于FPGA 的电梯控制系统设计的电梯控制系统设计摘要摘要: :本设计介绍了基于FPGA 的四层电梯控制系统的设计。

该系统采用Altera 公司的Cyclone CycloneⅡ系列Ⅱ系列FPGA 芯片EP2C5T144作为主控制芯片作为主控制芯片,,采用Verilog-HDL 编程描述编程描述,,实现对电梯的智能控制实现对电梯的智能控制,,经仿真验证经仿真验证,,实现了上升下降请求按键、所在楼层显示、电梯运行状态显示、开门指示、超载报警等功能。

该设计采用模块化编程编程,,升级可实现任意多层电梯系统升级可实现任意多层电梯系统,,具有很强的适应性和实用性。

具有很强的适应性和实用性。

关键词关键词: : 电梯控制电梯控制 、 FPGA 、 Verilog 、 控制模块控制模块The design of control system of elevator based on FPGAAbstract:This design introduced the design of four layer elevator control system based on FPGA. The system adopts the Altera company's Cyclone series FPGA chip EP2C5T144 as the main control chip, using Verilog-HDL programming, toachieve control of the elevator intelligent, simulation results show that, the rise and fall of the request, floor display, key operation state of elevator door display, indicating, overload alarm function. The design uses the modularprogramming, upgrade can be arbitrary multilayer elevator system, has strong adaptability and practicabilityKeywords:elevator control 、 FPGA 、 Verilog 、 control module引言引言随着社会的发展随着社会的发展,,电梯的使用越来越普遍电梯的使用越来越普遍,,对电梯功能的要求也不断提高对电梯功能的要求也不断提高,,其相应控制方式也在不断发生变化。

基于FPGA的四层电梯控制系统设计毕业设计论文

毕业论文声明本人郑重声明:1.此毕业论文是本人在指导教师指导下独立进行研究取得的成果。

除了特别加以标注地方外,本文不包含他人或其它机构已经发表或撰写过的研究成果。

对本文研究做出重要贡献的个人与集体均已在文中作了明确标明。

本人完全意识到本声明的法律结果由本人承担。

2.本人完全了解学校、学院有关保留、使用学位论文的规定,同意学校与学院保留并向国家有关部门或机构送交此论文的复印件和电子版,允许此文被查阅和借阅。

本人授权大学学院可以将此文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本文。

3.若在大学学院毕业论文审查小组复审中,发现本文有抄袭,一切后果均由本人承担,与毕业论文指导老师无关。

4.本人所呈交的毕业论文,是在指导老师的指导下独立进行研究所取得的成果。

论文中凡引用他人已经发布或未发表的成果、数据、观点等,均已明确注明出处。

论文中已经注明引用的内容外,不包含任何其他个人或集体已经发表或撰写过的研究成果。

对本文的研究成果做出重要贡献的个人和集体,均已在论文中已明确的方式标明。

学位论文作者(签名):年月关于毕业论文使用授权的声明本人在指导老师的指导下所完成的论文及相关的资料(包括图纸、实验记录、原始数据、实物照片、图片、录音带、设计手稿等),知识产权归属华北电力大学。

本人完全了解大学有关保存,使用毕业论文的规定。

同意学校保存或向国家有关部门或机构送交论文的纸质版或电子版,允许论文被查阅或借阅。

本人授权大学可以将本毕业论文的全部或部分内容编入有关数据库进行检索,可以采用任何复制手段保存或编汇本毕业论文。

如果发表相关成果,一定征得指导教师同意,且第一署名单位为大学。

本人毕业后使用毕业论文或与该论文直接相关的学术论文或成果时,第一署名单位仍然为大学。

本人完全了解大学关于收集、保存、使用学位论文的规定,同意如下各项内容:按照学校要求提交学位论文的印刷本和电子版本;学校有权保存学位论文的印刷本和电子版,并采用影印、缩印、扫描、数字化或其它手段保存或汇编本学位论文;学校有权提供目录检索以及提供本学位论文全文或者部分的阅览服务;学校有权按有关规定向国家有关部门或者机构送交论文的复印件和电子版,允许论文被查阅和借阅。

基于FPGA电梯控制器设计

目录一、设计要求 (5)二、系统设计 (5)三、单元模块设计 (7)四、仿真与调试 (9)五、优化与约束 (10)六、协同与分工 (10)七、心得体会(总结) (18)参考文献 (18)摘要:系统基于EDA技术的电梯控制器实现,,以现场可编程门阵列(FPGA)为设计核心,集成于一片ALtera公司的ACEX系列EP1K100QC208—3芯片上,采用超高速硬件描述语言(VHDL)模块化编程,实现了电梯的上行、下行、暂停、手动开门和快速关门等功能,并伴有蜂鸣器和指示灯的提示等功能。

本设计的特点在于能够进行真实的电梯模拟,主要采用了状态机,该系统具有集成度高、灵活性强、易于开发和维护等特点。

关键字: FPGA VHDL 电梯控制器状态机Abstract:The system according to the EDA technical achieve the elevator controller,It is base on FPGA(Field Programmable Gate Array), adopting VHDL(VHSIC Hardware Description Language) under the environment of ISE.most of the designs gather in the ACEX seriesEP1K100QC208—3 chip of the ALtera company .The whole design is composedof the up going of the elevator , the down going of the elevator , the pause of the elevator , direct manual control open-door and close the door quickly. It can be carry out the function such as conversion, handle and display .It is a characteristic that the system can simulate the real elevator ,which mainly adopting the state machine . The system has high accuracy and stability,it is proved to reliable and of high value and feasibility after testing.Key –word: FPGA VHDL elevator state machine一、设计要求功能:设计一4层楼电梯控制器,梯外各层显示当前电梯所在楼层及上行、下行状态;1层只有向上按钮,4层只有向下按钮,其余各层均有上下按钮;按钮均带灯。

基于FPGA的三层电梯

基于FPGA(verilog)编写的三层电梯一、需求分析;1、问题描述与要求:用Verilog语言设计一个电梯控制器,通过实验板对设计进行演示;要求楼层的高度大于等于6,并且所设计的电梯调度算法满足提高服务质量、降低运行成本的原则,电梯每2s上升或下降一层,关门需要2s,电梯开门维持4s,电梯超载后蜂鸣器会响,报警。

二、系统描述;1、考虑到板上的资源利用情况,设定电梯控制器适用的楼层为3层.2、在电梯的内部有一个控制面板,它负责按下请求到的楼层,并且显示当前尚未完成的目的地请求,当到达该楼层以后自动撤销本楼层的请求,即将面板灯熄灭.3、除1层和3层分别只有上/下按钮外,每个楼层(电梯门口旁)的召唤面板都有两个按钮,分别指示上楼和下楼请求。

4、电梯的外部面板会显示电梯当前所在的楼层,及上行还是下行(暂停显示刚才运行时的状态).当电梯在运行时,对应的楼层灯间固定显示一段时间进入下一楼层。

5、电梯调度方案:电梯向一个方向运行时,只对本方向前方的请求进行应答,直到本方向前方无请求时,才对反方向的请求进行应答。

当前内部控制面板上有的请求,只要经过所在楼层均会立即响应.在所有内部外部请求都已完成后,电梯转入等待。

电梯模型:(如下附图)三,功能模块划分1,分频模块:50Mhz的系统时钟输入,经过分频后产生1KHZ的时钟和0.5hz的时钟,1KHZ的时钟用于采集按键信号,按键的消抖和显示模块中数码管的动态扫描。

0.5hz的时钟用于主控制模块的的工作时钟,电梯每2s上升或下降一层,电梯开门维持4s,关门需要2s。

2,按键消抖模块:由于按键在按下的过程中有抖动的现象,会影响信号的采集结果,所以有必要对按键进行消抖,消抖模块为:3,报警模块:电梯开门后,如果电梯超载则蜂鸣器响,报警报警模块为:4,寄存器模块:用于对采集的按键信号进行保存,供后面的主控制模块分析,采样频率为1khz,寄存器模块为:5,主控制模块:该模块为整个设计的核心,控制电梯的运行情况;主控制模块为:6,显示模块:该模块用于将主控制的模块的输出数据进行译码显示,显示模块为:7,主控制模块的功能分析:将主控制模块分为5个状态,idle(等待),ceng1(第一层),ceng2(第二层),ceng3(第三层),kai(开门),主要通过这几个状态之间的转变来实现电梯的工作情况8,板上硬件介绍:按键:sw1为一层的上升请求,sw2为二层的上升请求,sw3为二层的下降请求,sw4为三层的下降请求,sw5为超载信号输入,sw6为选择第一层,sw7为选择第二层,sw8为选择第三层.数码管:左边三个数码管分别显示各层电梯所处的状态,为0时表示空闲等待状态,为1时表示下降,为2时表示上升,第4,5,6个数码管为各层显示电梯处于的层数,第7个数码管为电梯内部显示电梯所在层数,第8个数码管为内部显示电梯的工作方式,为0时表示空闲等待状态,为1时表示下降,为2时表示上升。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

系统主体模块的设计与仿真本设计是以9层的电梯控制系统为模型。

主要实现电梯运行开关的控制,楼层的请求,电梯运行遵循的方向优先原则,提前、延时开关门等基本的功能。

以下是对不同的状态进行仿真,以验证本设计的可行性。

电梯进入运行状态控制进程,通过判断上升、下降请求寄存器每一位的值,决定电梯运行状态,并通过状态指示信号输出该状态,本设计都是使用高电平触发。

(1)当电梯处于1楼时,上升请求:图4.1 电梯处于第一层时仿真图(2)提前/延时关门功能没有提前/延时关门时的情况下:图4.2 没有提前/延时关门时的仿真图从图4.2知道,运行或停止输出信号“lamp”为高电平时电梯进入运行状态,低电平时停止。

圈内显示电梯在75.36us后从停止状态转入运行状态。

当设置提前关门“close”为高电平时:图4.3 有提前关门时的仿真图图4.3与图4.2对比可知,由于设置了提前关门进程“close”,电梯提前到75.36us 以前从停止状态转入运行状态。

2当设置了延时关门“delay”为高电平时:图4.4 延时关门时的仿真图图4.4与图4.2对比可知,由于设置了延时关门进程“delay”,电梯延时到80.48us 后才从停止状态转入运行状态。

(3)当电梯处于较高层数时图4.5 电梯处于较高层数时的仿真图(5)电梯轿厢内楼层选择开关功能仿真图4.6 轿厢内楼层选择开关仿真图4(4)电梯的次态功能仿真如图4.7所示,当运行或等待时间“run_wait”计数到0110时,电梯运行状态变量“ladd”给出电梯的下一个状态。

如图 4.7圈内显示,“ladd”从0显示模块的设计与仿真图4.8 显示模块仿真图本设计的显示模块一共有3个显示部分,分别是电梯运行/等待时间显示run_wait、楼层选择指示direct以及所在楼层批示st_out。

这3个显示部分的设计结构都是一样的,所以以其中一个仿真作为例子。

从图4.8圈内看到,当电梯处于楼层2时,ledin收到信号‘0010’,经过系统内部自动转化为‘1011011’并通过ledout输出到共阴极LED数码显示。

根据设计原理,共阴极LED数码显示的管脚a、b、e、d、g有高电平输入,所以发光,显示数字‘2’。

6附录A 电梯控制器总体框图附录B 电梯控制器主体的程序library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;entity lift isport (clk: in STD_LOGIC; --2hz信号upin: in STD_LOGIC; --上升请求键downin: in STD_LOGIC; --下降请求键st_ch: in STD_LOGIC; --楼层选择键close: in STD_LOGIC; --提前关门键delay: in STD_LOGIC; --延时关门键run_stop: in STD_LOGIC; --电梯运行开关lamp: out STD_LOGIC; --运行或停止灯run_wait: out STD_LOGIC_VECTOR (3 downto 0); --运行或等待时间st_out: out STD_LOGIC_VECTOR (3 downto 0); --电梯所在楼层指示direct: out STD_LOGIC_VECTOR (3 downto 0) --楼层选择指示);end lift;architecture rtl of lift iscomponent ledport(ledin:in std_logic_vector(3 downto 0);ledout:out std_logic_vector(6 downto 0));end component;8signal ur,dr:STD_LOGIC_VECTOR (9 downto 1); signal dir,liftor:integer range 0 to 8;signal wai_t:STD_LOGIC_VECTOR (2 downto 0); signal divide,hand,clkin:STD_LOGIC;signal ladd:STD_LOGIC_VECTOR (1 downto 0); signal closex,delayx:STD_LOGIC;--signal run_wait: STD_LOGIC_VECTOR (3 downto 0); --signal st_out: STD_LOGIC_VECTOR (3 downto 0); --signal direct: STD_LOGIC_VECTOR (3 downto 0);begindirect<=conv_std_logic_vector(dir,4)+1;st_out<=conv_std_logic_vector(liftor,4)+1;run_wait<='0'&wai_t;lamp<=ladd(1);hand<=wai_t(2) and (not wai_t(1)) and wai_t(0); closex<=close and (not ladd(1));delayx<=delay and (not ladd(1));--urun_wait:led port map(run_wait,run_waitdis);--ust_out:led port map(st_out,st_outdis);--udirect:led port map(direct,directdis);p0:process(clk)beginif (clk'event and clk='1') thenclkin<=not clkin;--lamp<=ladd(1);end if;end process p0;--hand<=wai_t(2) and (not wai_t(1)) and wai_t(0);--closex<=close and (not ladd(1));--delayx<=delay and (not ladd(1));p1:process(clkin)beginif (clkin'event and clkin='1') thendivide<=not divide;if (dir=8) thendir<=0;elsedir<=dir+1;end if;end if;end process p1;p2:process(ur,dr,dir,upin,downin,st_ch,liftor,wai_t,run_stop,hand) variable num,t:integer range 0 to 9;beginnum:=liftor+1;t:=dir+1;if (run_stop='1') thenif (((t>num) and (st_ch='1')) or (upin='1')) thencase t is10when 1 => ur(1)<='1';when 2 => ur(2)<='1';when 3 => ur(3)<='1';when 4 => ur(4)<='1';when 5 => ur(5)<='1';when 6 => ur(6)<='1';when 7 => ur(7)<='1';when 8 => ur(8)<='1';when 9 => ur(9)<='1';when others =>Null;end case;elsif (hand='1') thencase num iswhen 1=> ur(1)<='0';when 2=> ur(2)<='0';when 3 => ur(3)<='0';when 4 => ur(4)<='0';when 5 => ur(5)<='0';when 6 => ur(6)<='0';when 7 => ur(7)<='0';when 8 => ur(8)<='0';when 9 => ur(9)<='0';when others =>Null;end case;end if;if (((t<num) and (st_ch='1')) or (downin='1')) thencase t is11when 1 => dr(1)<='1'; when 2 => dr(2)<='1'; when 3 => dr(3)<='1'; when 4 => dr(4)<='1'; when 5 => dr(5)<='1'; when 6 => dr(6)<='1'; when 7 => dr(7)<='1'; when 8 => dr(8)<='1'; when 9=> dr(9)<='1'; when others =>Null; end case;elsif (hand='1') then case num iswhen 1 => dr(1)<='0'; when 2 => dr(2)<='0'; when 3 => dr(3)<='0'; when 4 => dr(4)<='0'; when 5 => dr(5)<='0'; when 6 => dr(6)<='0'; when 7 => dr(7)<='0'; when 8 => dr(8)<='0'; when 9 => dr(9)<='0'; when others =>Null; end case;end if;elseur<="000000000";dr<="000000000";12end if;end process p2;p3:process(ur,dr,liftor,ladd,wai_t,run_stop)beginif (run_stop='1') thenif (wai_t="110") thenif ((ur or dr)="000000000") thenladd(1)<='0';elsecase liftor iswhen 0 =>if ((ur(1) or dr(1))>'0') thenladd(1)<='0';elseladd<="11";end if;when 1 =>if ((ur(2) or dr(2))>'0') thenladd(1)<='0';elsif(((ladd(0)='1') and ((ur(9 downto 3) or dr(9 downto 3))>"0000000")) or((ur(1) or dr(1))='0')) thenladd<="11";elseladd<="10";end if;when 2 =>if ((ur(3) or dr(3))>'0') thenladd(1)<='0';elsif(((ladd(0)='1') and ((ur(9 downto 4) or dr(9 downto 4))>"000000")) or((ur(2 downto 1) or dr(2 downto 1))="00")) then13ladd<="11";elseladd<="10";end if;when 3 =>if ((ur(4) or dr(4))>'0') thenladd(1)<='0';elsif(((ladd(0)='1') and ((ur(9 downto 5) or dr(9 downto 5))>"00000")) or((ur(3 downto 1) or dr(3 downto 1))="000")) thenladd<="11";elseladd<="10";end if;when 4 =>if ((ur(5) or dr(5))>'0') thenladd(1)<='0';elsif(((ladd(0)= '1')and((ur(9 downto 6) or dr(9 downto 6))>"0000"))or((ur(4 downto 1) or dr(4 downto 1))="0000")) thenladd<="11";elseladd<="10";end if;when 5 =>if ((ur(6) or dr(6))>'0') thenladd(1)<='0';elsif(((ladd(0)= '1')and14((ur(9 downto 7) or dr(9 downto 7))>"000"))or((ur(5 downto 1) or dr(5 downto 1))="00000")) thenladd<="11";elseladd<="10";end if;when 6 =>if ((ur(7) or dr(7))>'0') thenladd(1)<='0';elsif(((ladd(0)= '1')and((ur(9 downto 8) or dr(9 downto 8))>"00"))or((ur(6 downto 1) or dr(4 downto 1))="000000")) thenladd<="11";elseladd<="10";end if;When 7=>if((ur(8) or dr(8))>'0') thenladd(1)<='0';elsif(((ladd(0)='1') and ((ur(9) or dr(9))>'0')) or((ur(7 downto 1) or dr(7 downto 1))="0000000")) thenladd<="11";elseladd<="10";end if;15when 8 =>if ((ur(9) or dr(9))>'0') thenladd(1)<='0';elseladd<="10";end if;when others=>null;end case;end if;end if;elseladd<="00";end if;end process p3;p4:process(divide,wai_t,ladd,closex,delayx) beginif (divide'event and divide='1') thenif (wai_t="000" or closex='1') thenwai_t<="110";elseif (delayx='0') thenwai_t<=wai_t-1;elsewai_t<="010";end if;if (wai_t="001") thenif (ladd="11") thenliftor<=liftor+1;16elsif (ladd="10") thenliftor<=liftor-1;end if;end if;end if;end if;end process p4;end rtl;17附录C 显示电路的程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity led isport(ledin:in std_logic_vector(3 downto 0);ledout:out std_logic_vector(6 downto 0));end led;architecture rtl of led isbeginprocess(ledin)begincase ledin is --The sequence is "g f e d c b a"when "0000" => ledout<="0111111"; -- " show 0 "when "0001" => ledout<="0000110"; -- " show 1 "when "0010" => ledout<="1011011"; -- " show 2 "when "0011" => ledout<="1001111"; -- " show 3 "when "0100" => ledout<="1100110"; -- " show 4 "when "0101" => ledout<="1101101"; -- " show 5 "when "0110" => ledout<="1111101"; -- " show 6 "when "0111" => ledout<="0000111"; -- " show 7 "when "1000" => ledout<="1111111"; -- " show 8 "when "1001" => ledout<="1101111"; -- " show 9 "when others => ledout<="0000000"; --必须有,Here it is 'X',single quote end case;end process ;18end rtl;顶层模块设计程序:library IEEE;use IEEE.std_logic_1164.all;use IEEE.std_logic_arith.all;use IEEE.std_logic_unsigned.all;entity top isport (clk: in STD_LOGIC; --2hz信号upin: in STD_LOGIC; --上升请求键downin: in STD_LOGIC; --下降请求键st_ch: in STD_LOGIC; --楼层选择键close: in STD_LOGIC; --提前关门键delay: in STD_LOGIC; --延时关门键run_stop: in STD_LOGIC; --电梯运行开关lamp: out STD_LOGIC; --运行或停止灯run_waitdis: out STD_LOGIC_VECTOR (6 downto 0); --运行或等待时间st_outdis: out STD_LOGIC_VECTOR (6 downto 0); --电梯所在楼层指示directdis: out STD_LOGIC_VECTOR (6 downto 0) --楼层选择指示);end top;architecture rtl of top iscomponent led isport(ledin:in std_logic_vector(3 downto 0);ledout:out std_logic_vector(6 downto 0));19end component;component lift isport(clk: in STD_LOGIC; --2hz信号upin: in STD_LOGIC; --上升请求键downin: in STD_LOGIC; --下降请求键st_ch: in STD_LOGIC; --楼层选择键close: in STD_LOGIC; --提前关门键delay: in STD_LOGIC; --延时关门键run_stop: in STD_LOGIC; --电梯运行开关lamp: out STD_LOGIC; --运行或停止灯run_wait: out STD_LOGIC_VECTOR (3 downto 0); --运行或等待时间st_out: out STD_LOGIC_VECTOR (3 downto 0); --电梯所在楼层指示direct: out STD_LOGIC_VECTOR (3 downto 0) --楼层选择指示);end component lift;signal s0,s1,s2:STD_LOGIC_VECTOR(3 downto 0);BEGINU1:lift PORT MAP(clk,upin,downin,st_ch,close,delay,run_stop,lamp,s0,s1,s2);U2:led PORT MAP(s0,run_waitdis);U3:led PORT MAP(s1,st_outdis);U4:led PORT MAP(s2,directdis);END rtl;20。