一种新型的抽取滤波器设计

高频数字抽取滤波器的设计

耗, 第二 级 采用传 统 结构 。 C I C补偿 滤 波器使 信号 通 带平坦 , 半 带滤 波 器满足 了阻 带的衰减要 求 。 为 了验 证 数 字 滤 波 器 的性 能 , 搭 建 了 四 阶 前 馈 一 反 馈 结 构 △ 调 制 器 , 作 为数 字抽 取 滤 波 器 的输入 , 最终在 输 入 信 号频 率 为 0 . 5 MH z

s t r u c t u r e o f t wo s t a g e s f o r o p e r a t i n g i n h i g h ̄ e q u e n c y .1 1 1 e i f st r s t a g e a d o p t s p o l y p h a s e d e c o mp o s i t i o n t o d e c r e a s e t h e o p e r a t i n g f r e ・

q u e n c y S O t h a t t h e p o we r c o n s u mp t i o n c a n b e r e d u c e d s i g n i i f c a n t l y .a n d t h e s e c o n d s t a g e u s e s t r a d i t i o n a l s t uc r t u r e.T h e C I C e o m— p e n s a t i o n p a r t a c h i e v e s a l f a t p a s s b a n d a n d t h e h a l f -b a n d f i l t e r me e t s t h e d e ma n d o f s t o p b a n d a t t e n u a t i o n.I n o r d e r t o v e r i f y t h e

低功耗Delta-Sigma ADC抽取滤波器的设计与实现的开题报告

低功耗Delta-Sigma ADC抽取滤波器的设计与实现的开题报告一、选题背景与意义Delta-Sigma ADC是一种高精度、低功耗的模数转换器,广泛应用于信号采集和处理、电力电子、无线通信等领域。

其中,抽取滤波器是Delta-Sigma ADC的核心部件之一,用于对模数转换器输出的无穷序列进行数字滤波和抽取操作,得到有限序列的数字信号。

因此,对Delta-Sigma ADC抽取滤波器的设计和实现具有重要的理论和应用价值。

二、研究内容和研究方法本文以Delta-Sigma ADC抽取滤波器的设计和实现为研究目标,包括以下内容:1. Delta-Sigma ADC的原理和应用,介绍Delta-Sigma调制器、数字滤波器等基本原理。

2. 抽取滤波器的设计和实现,包括数字信号处理中的抽取和滤波操作、滤波器结构和参数的设计和优化等方面。

3. 模拟电路和数字电路的设计和实现,包括滤波器的模拟电路、数字电路、系统级集成等方面。

4. 系统仿真和测试验证,通过理论分析、MATLAB仿真和硬件实现等方式对抽取滤波器的性能进行分析和测试。

研究方法主要包括文献综合、数学分析、MATLAB仿真、软件编程和电路实现等技术手段。

三、研究进度目前,已经完成Delta-Sigma ADC的理论研究和抽取滤波器的设计方案,初步确定了数字电路和模拟电路的方案设计。

下一步,将进行MATLAB仿真和电路模拟验证,并进行实际系统测试。

四、预期研究成果本研究的预期成果包括:1. 抽取滤波器的设计方案和实现流程,提高Delta-Sigma ADC抽取滤波器的设计和实现水平。

2. 系统仿真和测试验证结果,提高Delta-Sigma ADC抽取滤波器的性能和应用范围。

3. 发表相关论文及优秀学术著作,提高科研水平。

五、研究难点和风险控制Delta-Sigma ADC抽取滤波器的设计和实现具有一定难度,其风险主要体现在以下方面:1. 短时间内难以完成全部设计和实现工作。

一种新型滤波器的设计与实现

3

直接型 FIR 滤波器的 FPG A 实现

FIR 滤波器最吸引人的特点 之一就是使其设

h( 3) = h( 9) = 0. 0545 h( 5) = h( 7 ) = 0 . 1756

计结果具有线性相位。具有线性相位的因果 FIR 数字滤波器的冲激响应具有偶对称特性, 即: h( n) = h( N - 1- n) , 线性相位 F IR 滤波器由于系数对 称, 因此每个滤波周期的乘法器数是直接型 FIR 滤 波器的一半 , 加法器的数目相等。其运算速度和所 消耗的硬件资源具有明显的优势。 设计线性相位数字滤波器的一般方法: 是给出 所要求的理想数字滤波器的频率响应 H d ( e ) , 要 求设计一个 FIR 数字滤波器频率响应 H ( e ) 来逼 近 H d ( e ) , 但设计是在时域进行的 , 因而先有 H d ( ej w ) 的傅 立 叶反 变 换得 出: H d ( n) = 1 2

( N- 1) / 2- 1 [ 1]

H[z]=

n= 0 2K

h[ n] z - n =

k= 1

(

0K

+

1K

z-1+

z

- 2

) 为 H ( z ) 分解成实系数二阶因子的乘积形

式。这种结构所 需要的系数 ( i = 0, 1 , 2; k = 1, 2, , N / 2 ) 比卷积型的系数 h[ n] 要多, 因而需要更多 的储存单元。理论上需要 N 个单元储存系数 , 再 加上 N 个单元储存中间结果, 结果一共需要 5N / 2 个储存单元。由于每一个子系统都是二阶系统, 故 量化误差对整个系统的影响较小, 可以使用较短的 系数量化字长。 2. 3 频率抽样型 H ( z ) 的内插公式为 H ( z ) = ( 1- Z

FPGA的FIR抽取滤波器设计

FPGA的FIR抽取滤波器设计用FPGA实现抽取滤波器比较复杂,主要是因为在FPGA中缺乏实现乘法运算的有效结构,现在,FPGA中集成了硬件乘法器,使FPGA在数字信号处理方面有了长足的进步。

本文介绍了一种采用Xilinx公司的XC2V1000实现FIR抽取滤波器的设计方法。

具体实现结构设计基于抽取滤波器的工作原理,本文采用XC2V1000实现了一个抽取率为2、具有线性相位的3阶FIR抽取滤波器,利用原理图和VHDL共同完成源文件设计。

图1是抽取滤波器的顶层原理图。

其中,clock是工作时钟,reset是复位信号,enable是输入数据有效信号,data_in(17:0)是输入数据,data_out(17:0)是输出数据,valid是输出数据有效信号。

adder18是加法器模块,mult18是乘法器模块,acc36是累加器模块,signal_36to18是数据截位器模块,fir_controller是控制器模块。

控制器定时向加法器、乘法器和累加器发送数据或控制信号,实现流水线操作。

图1 抽取滤波器顶层原理图控制器控制器是抽取滤波器的核心模块,有两个功能:一是接收输入数据,二是向其它模块发送数据和控制信号。

它根据加法器、乘法器和累加器的时序特性,有规律地向加法器发送抽头数据,向乘法器发送系数,向累加器发送控制信号,让加法器、乘法器和累加器在每个时钟周期都完成指定的任务,从而实现流水线操作。

控制器用VHDL语言描述,用寄存器存放抽头和系数。

加法器加法器的输入和输出都是18 bit,用VHDL语言描述实现。

它有两个工作时钟的延迟,在输入数据准备好的情况下,第一个时钟得出相加结果,第二个时钟把相加结果锁存输出。

乘法器乘法器为18 bit输入,36bit输出,用库元件MULT18X18S和36 bit锁存器实现。

MULT18X18S是XC2V1000自带的18×18bit硬件乘法器,单个时钟就可完成乘法运算。

Sigma-Delta ADC中抽取滤波器的设计与实现的开题报告

Sigma-Delta ADC中抽取滤波器的设计与实现的开题报告一、选题背景及研究意义Sigma-Delta ADC抽取滤波器是Sigma-Delta调制器中最为关键的一个组成部分,它对ADC整个系统性能的影响非常大。

抽取滤波器的作用是减小Sigma-Delta ADC的过采样率,缩小ADC转换器的宽带,从而减小数字滤波器的计算量,提高Sigma-Delta ADC抽取率和工作效率。

抽取滤波器设计精度要求高,设计难度大,对滤波器设计者的理论水平有着很高的要求。

因此,设计一种高效、高性能的Sigma-Delta ADC抽取滤波器是当前研究热点之一。

本篇开题报告旨在探索Sigma-Delta ADC抽取滤波器的设计与实现,为其优化提供理论参考和技术支持。

二、研究内容和方法本研究的内容主要包括:1. 研究Sigma-Delta ADC抽取滤波器的主要设计原理和特点,分析其难点和瓶颈;2. 探索Sigma-Delta ADC抽取滤波器设计的各种算法和方法,比较其优缺点,实现对各种算法的评估、验证和对比;3. 设计一种符合IFI6UHPC架构的Sigma-Delta ADC抽取滤波器电路,实现其关键算法和方法功能;4. 对设计的Sigma-Delta ADC抽取滤波器电路进行实验测试,验证其设计的正确性和性能优越性;5. 最后,对设计过程和实验结果进行详细分析和总结,并提出改进和优化方案。

本研究的方法主要包括:1. 文献资料研究法:查阅与Sigma-Delta ADC抽取滤波器相关的文献资料,了解其发展历程、设计思路和实现细节;2. 算法研究法:针对Sigma-Delta ADC抽取滤波器的各种算法和方法,比较其优缺点,实现对各种算法的评估、验证和对比;3. 仿真模拟法:利用计算机软件对设计的Sigma-Delta ADC抽取滤波器电路进行仿真模拟,进行性能分析和优化调试;4. 实验验证法:采用硬件电路搭建方式对设计的Sigma-Delta ADC抽取滤波器电路进行实验验证,验证其设计的正确性和性能优越性。

改进型CIC抽取滤波器设计与FPGA实现

改进型CIC抽取滤波器设计与FPGA实现张杰;戴宇杰;张小兴;吕英杰【摘要】为了改善级联积分梳状(CIC)滤波器通带不平和阻带衰减不足的缺点,给出一种改进型CIC滤波器.该滤波器在采用COSINE滤波器提高阻带特性的基础上,级联了一个SINE滤波器,补偿了其通带衰减.硬件实现时,采用新的多相分解方法结合非递归结构,不仅大大减少了存储单元数量,还使电路结构更加规则.经仿真和FPGA 验证,改进型CIC滤波嚣使用较少硬件,实现了阻带衰减100.3 dB,通带衰减仅为0.000 1 dB.【期刊名称】《现代电子技术》【年(卷),期】2009(032)010【总页数】3页(P22-24)【关键词】CIC抽取滤波器;COSINE滤波器;SINE滤波器;设计优化;FPGA【作者】张杰;戴宇杰;张小兴;吕英杰【作者单位】南开大学,南开大学微电子所,天津,300071;南开大学,南开大学微电子所,天津,300071;南开大学,南开大学微电子所,天津,300071;南开大学,南开大学微电子所,天津,300071【正文语种】中文【中图分类】TP368.1抽取滤波器是Σ-Δ模/数转换器中的重要组成部分,积分梳状滤波器经常作为第一级滤波器,用以实现抽取和低通滤波[1]。

其优点是实现时不需要乘法器电路,且系数为整数,不需要电路来存储系数,同时通过置换抽取可以使部分电路工作在较低频率,与相同滤波性能的其他FIR滤波器相比,节约了硬件开销[2]。

经过仿真,抽取率为32的一阶积分梳状滤波器第一旁瓣相对于主瓣的衰减最大约为15 dB,这样的阻带衰减根本达不到实用滤波器的设计要求。

为了改变滤波性能,一般采用级联积分梳状滤波器(CIC)[3]。

但经过CIC降频滤波系统降频后会产生信号混叠现象,并且主瓣曲线不平,需要用新的算法或新结构来修正改善这些特性。

1 CIC抽取滤波器原理经典的抽取滤波器为Hogenauer [3]CIC滤波器,其传输函数表达式为:(1)式中:参数M为降频因子,决定了CIC的通带大小;K为滤波器的阶数,对阻带衰减起到加深作用。

一种性能良好的高效CIC抽取滤波器的设计

一

种 性 能 良好 的 高 效 C C抽 取 滤 波 器 的 设 计 I

叶 和 忠 ,赵 利 ,彭 小 卫 ,周 胜 源

( 林 电 子 科技 大 学 信 息 与 通 信 学 院 , 西 桂 林 桂 广 510) 4 0 4

摘 要 : 对 传 统 C C 抽 取 滤 波 器 性 能 和 结 构 存 在 的 问 题 , 用 一 个 I O 针 I 利 S P滤 波 器 和 余 弦 滤 波 器 对 C C抽 取 滤 波 器 I

Y e H e hong,Zha ,Pe a z o Li ng Xiow e ,Zho i u She gy n n ua

( c o l f n o ma in a d C m m u ia in E g n e ig,Gul nv ri f e t nc T c n lg ,Gu l 4 0 4, S ho fr t n o o I o nc t n ie rn o in U ie st o c r i e h oo y i y El o i n 5 1 0 Chn ) i ia

表 明 : 设 计 方 法使 得 C C 抽 取 滤 波 器 性 能 得 到 改 善 , 现 结 构 高 效 , 实 际 工 程 中 有 很 大 的应 用 价 值 。 该 I 实 在

一种短波数字化电台CIC抽取滤波器的设计

D

0 罄 害 罄 咨 t 2 罄 ^ ,

图1 00 波 器 幅频 特 性 1滤

Ⅳ

图1 区间 f 丌 中, D 称为CC I滤波器 的主瓣 , 其余区间称 为旁瓣。由图可见 , 随着频率 的增大 , 旁瓣 电平不 断减 小。 阻 但 带抑制 比较小, 一般采 用多级 CC I 滤波器级联 的方 法来增大 阻 带抑制。

字滤波器 , 广泛 应用于数字下变频器前级处理 中, 是数 字下变

根据式 () 4可得单级带内容差:

t { r

≈ 2 5X1 . 0

‘

~

.

:

= := : :

根据式 () 6 可计算无用边带的抑制为:

a 11

.

。

3 .d 35 B

8 h .

^

I矗 . 妻 .

采 用单 级C C I抽取滤 波器 时, 其无 用边带抑制为3 .d , 35 B 无 法满足 系统 9 d 的要求 。 0B 所以, 需求采用3 I抽取滤波器进 级CC

数。 ( z 专是积 分器 , (=— 是梳妆滤波器, ) = z I ) z 所以,

命名为级联积分一 梳状 滤波器。 CC I抽取滤波器 的幅频公式 为:

带内容差。 以, I 滤波器 的级数不宜太长。 所 CC

4 CI C抽取 滤 波器 的设 计

根 据此短 波 电台项 目要求 ,电台数字 化在 中频5 0 H 上 0K z 进行。 收时, 接 首先对 5 0 H 中频信号进 行采样 , 0K z 采样 速率为

抽取速率可编程CIC滤波器设计

C I C抽 取滤 波器 结构 如 下 图所示 :

处理 。采 样 率变 换 可能会 造 成频 谱 的混 叠或 镜像 效 应 ,因此 仅靠 简 单 的改变 系 统采 样 时钟 是难 以实 现 的, 必须 对采 样 的数 据另 行处 理 , 即通 过 特殊 的滤 波 器来 尽 可 能地 减弱 频 谱 的混 叠 或镜 像效 应 。C I C滤 波器是一种极 、 零点相消 的 F I R滤 波 器 , 没 有 乘 法 器, 只有 加 法器 , 性 能较 好 , 所 以被广 泛应 用 。 在 实 际应用 中对多 种 中频带 宽信 号 进行 下变 频 处理时 , 通常要求 C I C的抽 取 速 率 可 变 , 并 且 在 不 同抽取 速 率 下要 求 滤 波 器 的输 入 、 输 出信 号 的动 态 范围 、 精度 等得 到 保证 。 因此 本 文 在传 统 C I C抽 取 滤 波器 的基 础 上 , 提 出 了抽 取 速率 可 编程 的 C I C抽 取 滤 波器 设 计 方案 , 并 对 抽 取 速 率 变 化 时 的截 位 方

编程 的 C I C滤波 器设 计 方案 , 并针对 不 同速率 时 的截位 问题进 行分 析 。验证 表 明 , 本 文提 出的截 位 方案

符合 项 目性 能要 求 。 关键 词 : C I C滤 波器 ; 可 编程 ; 截位

The De s i g n f o r Ra t e Pr o g r a mma bl e CI C Fi l t e r

很难 跟上 。因此 必须 对 A / D后 的数据 流 进行 下变 频

【 l 】 国 集 成 电 路

C hi na I nt egr at ed Ci r cu i t

抽样 率 的级 联理 想积 分器 和低 抽 样率 的级联 梳状 器 组成 ,根 据 抗混 叠 和抗 镜像 的 指标 确定 所需 的级联

一种数字下变频抽取滤波器的设计

第 41 卷第 1 期 2011 年 2 月

图 1 数字下变频器 Fig . 1 Dig ital do wn conver ter

收稿日期: 2010 08 09; 定稿日期: 2010 09 20 基金项目: 国家自然科学基金资助项目( 60906009)

2

兰金保等: 一种数字下变频抽取滤波器的设计

2011 年

2 抽取滤波器总体结构

2. 1 抽取滤波器的三级串联实现 由于 IIR 滤波器不具有线性相频特性, 且在定点

通过对 F IR 滤波器的传输函数进行多相分解, 再利用图 3 所示的抽取滤波器的等价变换性质, 可 得到 F IR 型抽取滤波器的一种高效实现结构, 其处 理过程如图 4 所示。

假设 H ( z 1) 的阶数为 N , 令: H e ( z 1 ) = h0 + h2 z 1 + + hN - 2 z + ( N - 2) / 2 hN z N / 2

3. S cie nce and T ech nol og y on A nal og Int eg rat ed Ci rcu it L aborat or y , Ch ong qi ng 400060, P. R. Chi na)

Abstract: Design of a decimation filter fo r digit al do wn conversion w as presented in detail. T he decimatio n filter,

改进的抽取滤波器设计

H gnu r I oe ae C滤 波器 中的 差分器 , 而减 小 数 字 电路 的 面积 。 一个 采 用这 种 结 构 的 4阶 3 C 从 2倍 降 采样 数 字滤波 器 在 Srt I系 列 2 3 P A 芯 片 中实 现 。 经 过 测 试 , 费 的 硬 件 资 源 比传 统 t iI ax S 0F G 耗

第 1期 21 0 1年 2月

微

处

理

机

Nl l l _

Ml CROP ROCES ORቤተ መጻሕፍቲ ባይዱ S

F b , 0l e 2 1

改 进 的抽 取 滤 波 器 设 计

潘桃莉 , 光忠 , 谢 周 云 , 亚 东 蒋

( 电子科技 大 学 光 电信 息 学院 电子薄膜 与集 成器件 国家重 点实验 室 , 成都 6 0 5 ) 10 4

p a t e,i o t h p r s u c s11 e c ntls ha h tu i g ta iina g n u rsr cu e rci c tc ss c i e o r e p r e e s t n t a sn r d to lHo e a e tu t r . K e o ds: g n u F ]e De i ain Fi e ; yw r Ho e a m’ itr; cm to l r FPGA t

a e u e t ’pa e mul p e o d r s d o l lc ( t l fa dm’ i r d t n lHo e a e C i e’ n o d lt pt z h o i s n ta ii a g n u r CI fl  ̄ o t .i r e’ o o i e t e c mb mi

的模 拟器件 相对 较少 , 字器 件增 多 , 数 更易 与数 字 电

FIR抽取滤波器的工作原理

FIR抽取滤波器的工作原理FIR(有限脉冲响应)滤波器是一种数字滤波器,常用于信号处理和数字通信领域。

它的工作原理基于对输入信号的离散时间样本进行线性加权求和的方式。

FIR滤波器的工作原理可以分为三个主要步骤:采样、加权和求和。

1.采样:输入信号经过模数转换器(A/D转换器)转换为数字形式,以离散时间点的方式进行采样。

这意味着信号在时间上是离散的,并以一定的时间间隔采集样本。

2.加权:每个采样点都乘以一个系数,称为滤波器的冲激响应。

冲激响应是一个数字序列,表示了滤波器的频率响应特性。

它决定了滤波器如何对不同频率的信号进行加权。

冲激响应的长度决定了滤波器的阶数,即影响滤波器频率响应的能力。

3.求和:加权后的采样点按顺序相加,得到输出信号。

输出信号是滤波器对输入信号进行处理后得到的结果。

FIR滤波器的特点是其脉冲响应是有限长度的,因此它不具有反馈回路。

这意味着它的稳定性得到了保证,并且不会引入频率抖动或波动。

此外,FIR滤波器的相应通带和停带特性可以精确设计,其幅频响应在通带内的波动较小,同时对停带内的频率具有较高的抑制能力。

设计FIR滤波器的关键是确定滤波器的冲激响应。

常见的设计方法有窗函数法、频率采样法和最小平方误差法等。

窗函数法通过在理想传递函数和实际传递函数之间引入窗函数来设计滤波器。

频率采样法在设计过程中提前选择一组所需的频率样本点,然后通过这些样本点确定滤波器的冲激响应。

最小平方误差法是基于最小化输入信号和期望响应之间的均方误差来设计滤波器。

FIR滤波器的应用广泛,例如语音处理、图像处理、音频处理和无线通信等领域。

它可以实现低通、高通、带通和带阻等多种滤波器类型,具有较好的抗混叠性能和相位线性特性,能够有效地去除信号中的干扰和噪声。

总结起来,FIR滤波器的工作原理是将输入信号离散采样后,对每个采样点乘以滤波器的冲激响应系数,并将这些加权后的采样点求和,得到输出信号。

滤波器的冲激响应可以通过不同的设计方法获得,以满足特定的频率响应要求。

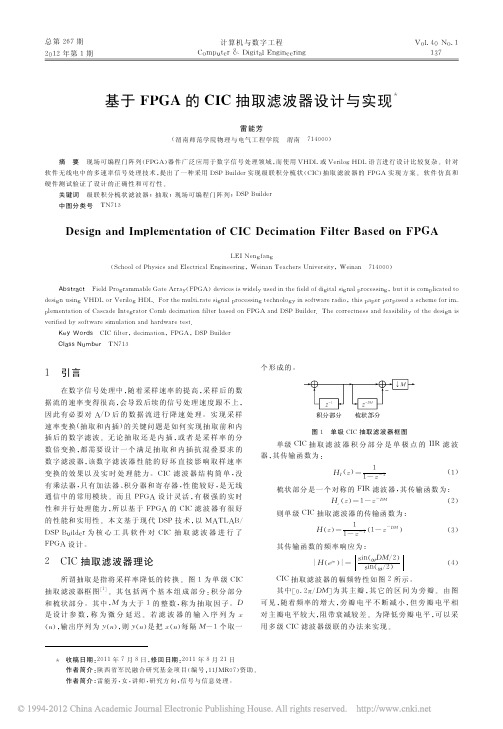

基于FPGA的CIC抽取滤波器设计与实现

( ) 4

C I C 抽取滤波器的幅频特性如图 2 所示 。 / 其中 [ 为其 主 瓣, 其 它 的 区 间 为 旁 瓣。由 图 0. 2 DM ] π 可见 , 随着频率的增 大 , 旁 瓣 电 平 不 断 减 小, 但旁瓣电平相 对主瓣电平较大 , 阻带衰减较差 。 为降低 旁 瓣 电 平 , 可以采 用多级 C I C 滤波器级联的办法来实现 。

总第 2 6 7期 2 0 1 2 年第 1 期

计算机与数字工程 C o m u t e r &D i i t a l E n i n e e r i n p g g g

V o l . 4 0N o . 1 1 3 7

基于 F P G A的C I C 抽取滤波器设计与实现

雷能芳

( ) 渭南师范学院物理与电气工程学院 渭南 7 1 4 0 0 0

[ 2] / 可以由 F P GA C P L D 开发工具 Q u a r t u s Ⅱ来完成 。采用 比直接采用 该方法进行数字信 号 处 理 系 统 的 F P GA 设 计 ,

图 5 测试电路

在Q 对测试电路进行编译 , 下载到 c u a r t u s Ⅱ 环境中 , - y 就可以对硬件进行测 c l o n e系列 E P 1 C 1 2 Q 2 4 0 C 8 器 件 后, / 经D 试 。 调制器 的 输 出 信 号 为 数 字 信 号 , A 转换后可以通 过示波器进行测试 , 也可以直接采用 Q u a r t u s Ⅱ 软件中的 嵌

图 3 3 级 C I C 抽取滤波器模型图

滤波器常结合半带滤波器来完成采样速 率 的 抽 取 功 能 。 滤 波时只做加法运算 , 大大简化了计算量 , 从而降低后续电路 的处理速度 。 本文的创新之 处 在 于 : 应用现代 D S P技术设计 C I C抽 取滤波 器 , 图 形 化 界 面 使 设 计 简 单 易 行, 避免了繁琐的 设计者甚至 不 需 要 了 解 F VHD L 语言编程 ; P GA 和 硬 件 描 述语言 , 真正实现了电子系统设计的黑盒 子 化 、 积木化和简

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 变级数的非递归抽取滤波器

梳状滤波器常用作抽取滤波器 .其单位脉冲响应全部为

基金项 目: 国家部委预研项 目资助

H ( z ) = I I Z 1 - 卜( ‘ “ 一 ‘ ) n ( l + z Z ) " . . . ( I + Z I) n

( 4 )

作者简介: 陈雷( 1 9 7 8 - ) , 男, 汉族, 西北工业大学航空微电子中 心博士生, 主要研究方向: 高精度s i g m a d e l t a A / I 〕 转换器设计, 数模混合设计及计 算机体系结构。 赵元富( 1 9 6 2 一, 男, 汉族, 北京微电子技术研究所研究员, 主要研究方向: V L S I 设计, 片上系统集成技术, S O I 技术等。 高德远( 1 9 4 2 - ) , 男, 汉族, 西北工业大学教授, 博士导师, 主要研究方向: 计算机体系结构, V I S I 设计, S O C 设计技术等。

计算机工程与应用 2 0 0 5 . 3 2 2 5

假设滤波器的输入字长 m位 , 每级字长增加 n 位, 第i 级 的字长为 m + i x n , 采样速率每级降低 2 倍。 信号速率变小。 这种 结构的优点是前级的字长非常短, 功耗较低; 当采样率和滤波 器阶次增加时, 功耗增加的较少。同时这种规则的结构使得电

偶数部分 :

n = o n = O

X ( n ) = x ( 0 ) + x ( I ) : 一 , + x ( 3 ) z ' + . . - + z '

1 _ 一 6吞 1

d e c i ma t i o n f i l t e r s a t s a me c i r c u i t c l o c k .

K e y w o r d s : d e c i m a t i o n f i l t e r , c o m b i f l t e r , p o l y p h a s e t r a n s f o r m a b l e s t a g e n o n - r e c u r s i v e c o m b f i l t e r

C h e n L e i ' Z h a o Y u a n f u 2 G a o D e y u a n ' We n Wu 2 Wa n g Z o n g m i n ' Z h u X i a o f e i 2 P e n g H e p i n g '

' ( A v i a t i o n M i c r o e l e c t r o n i c C e n t e r , N o t r h w e s t e n r P o l y t e c h n i c a l U n i v e r s i t y , X i ' a n 7 1 M7 2 )

1 前言 通信、 过采样s i g m a d e l t a A / I 〕 转换器被广泛地用在音频、 航空航天、 雷达、 测控系统、 地震勘探、 水声等领域。 S i g m a d e l t a

A / 1 ) 成为实现高分辨率 A D C的主流技术。 数字抽取滤波器是过

1 , 其中 M为抽取滤波器抽取因子 , 梳状滤波器的传输函数

一种新型的抽取滤波器设计

陈 雷 ‘ 赵元富 2 高德远 ’ 文 武 2 王宗民2 朱小飞 2 彭和平 ’

权西北工业大学航空微电子中心, 西安 7 1 0 0 7 2 ) 2 ( 北京微电子技术研究所, 北京 1 0 0 0 7 6 )

E - m a i l : c h e n l e i n p u @ y a h o o . c o m

1- 6 , 6 f i ,/ ,

- _ 0 4\6 -

n l z / =L 丁 了万不 ̄二 不- 1=[ 二丽 二 了 节万丙 J 1 i ' Z /

O咔又1 -Z ) UH k 1 -Z )

( 5 )

M( 1 二一 , )

( 3 )

器。 A b o u s h a d Y E ' l 讨论和对比各种抽取滤波器的第一级结构。

C r o c h i e r e r ' l 描述了多速率多级滤波器结构, 减小采样频率来减小

硬件和功耗。 B a r e t t e给出了多相半带滤波器结构来简化滤波器 系数。J o h a n s s o n i 9 - 提出了使用全通 I I R滤波器增加速度减小功 耗。 这些研究大多数从改变滤波器的抽取结构上考虑, 本文从滤 波器的级数和抽取结构上考虑, 在面积和性能上折衷考虑, 提出 了一种小面积低功耗的多相变级数抽取滤波器设计。

器很大程度上决定了s i g m a d e l t a A l l 〕 转换器的 转换速率, 功耗

和面积。 抽取滤波器的功耗直接和滤波器的阶数、 字长和采样频 率相关。 近年来对抽取滤波器有很多研究, 主要是用梳状滤波器 来实现, 结构上大体分为递归结构和非递归结构。 N a v i n e r 等n N 出梳状一 F I R滤波器结构作为一个有效 的低功耗抽取滤波

H ( z ) 及相应的 频率H ( e - ) 如等式( 1 ) 和( 2 ) :

H( z ) =

采样s i g m a - d e l t a A / D 转换器的 重要组成 部分, 用于 滤出 有用信

号带外的噪声和降低采样频率至奈奎斯特频率。数字抽取滤波

e - p - ( 膝I 班 s i n ( ( o M / 2 ) H( e " ' ) = H( z ) I = } - = s i n ( o ) / 2 )

样速率。 同时采用多相结构进一步减小字长, 降低功耗, 提高电 路速率。多速率信号处理理论中一个 N阶 F I R滤波器输 出 Y ( z ) 表示为等式( 8 ) :

N-1 刀e s l

路设计和布线都比 较容易实现, 这样可以降低功耗。

我们对抽取滤波器设计的通用方法进行分析 , 定义整体设 计指标。 假设系统要设计一个抽取 6 4 倍的梳状滤波器, 前面调 制器是 5 阶, 按模字长理论应该用 6 级抽取滤波器。阻带衰减 6 5 d B 。其滤波器传递函数H ( z ) 表达式如等式( 5 ) 和( 6 ) :

11/ \ 「

摘 要 文章基于面积和功耗方面考虑提出了一种低功耗多相变级数非递归梳状滤波器结构,这种滤波器适合高阶过

采样s i g m a d e l t a A / D转换器。 抽取滤波器采用T o p - d o w n 方法设计, 用0 . 6 - W m C M O S 标准单元实 现, 相比同 样速度下的

抽取因子 M和滤波器器级数 n比较大的时候就会带来非常大 的功耗。因为 I I R部分一直工作在非常高的频率下( 过采样频 率) 。 总体电路速度将受到积分器大字长和递归环的制约。 因此 I I R部分限制了递归结构在 M和 n比较大的时候的应用。 非递归结构算法梳状滤波器是另一种实现方法。 使用置换 原则, 非递归结构每级有相同的低阶 F I R滤波器但是有不同的 采样率。将等式( 3 ) 写成非递归结构传递函数如等式( 4 ) , / M - t \ ”

2 ( B e i j i n g M i c r o e l e c t r o n i c s T e c h n o l o g y I n s t i t u t e , B e i j i n g 1 0 0 0 7 6 )

A b s t r a c t : T h e p a p e r p r e s e n t s a n o v e l l o w e r p o w e r p o l y p h a s e t r a n s f o r m a b l e s t a g e n o n - r e c u r s i v e c o m b f i l t e r a r c h i t e c t u r e c o n s i d e r i n g t h e a r e a a n d p o w e r c o n s u m p t i o n , w h i c h i s v e y r s u i t a b l e f o r h i g h - o r d e r o v e r s a m p l i n g s i g m a d e l t a A / D c o n v e t r e r s . T h e f i l t e r i s d e s i g n e d b y T o p - d o w n m e t h o d a n d i m p l e m e n t e d u s i n g 0 . 6 - } t m C M O S s t a n d a r d c e l . T h e p r o p o s e d d e c i m a t i o n f i l t e r h a s 1 / 3 l e s s h a r d w a r e a r e a a n d p o w e r c o n s u m p t i o n c o m p a r e d t o t h a t o f c o n v e n t i o n a l n o n - r e c u r s i v e

们 艺 n=0

z ,二

1 - z ' I - z '

产‘、 了. 、

、 ,矛 、卫 夕

, 1 2

I - Z ' l n - f I I n / , - - M \ n

]- L - W , , , 一 - 1 } J、 , - L )

2 性 k i -a )

标准的非递 归结构抽取 滤波器节省 了约 1 / 3面积和功耗 。

关键词

抽取

0 0 2 - 8 3 3 1 - ( 2 0 0 5 ) 3 2 - 0 0 2 5 - 0 3 文章编号 1

文献标识码 A

中图分类号 T P 3 1 1

D e s i g n o f a N o v e l D e c i m a t i o n F i l t e r