3 8译码器

8-3编码器,3-8译码器的verilog实现

8-3编码器,3-8译码器的verilog实现在数字系统中,由于采⽤⼆进制运算处理数据,因此通常将信息变成若⼲位⼆进制代码。

在逻辑电路中,信号都是以⾼,低电平的形式输出。

编码器:实现编码的数字电路,把输⼊的每个⾼低电平信号编成⼀组对应的⼆进制代码。

设计⼀个输⼊为8个⾼电平有效信号,输出代码为原码输出的3位⼆进制编码器。

化简逻辑表达式:由逻辑表达式可以得出,普通的8-3编码器⽤或门即可实现。

对应的verilog程序如下:module mb_83(x,y);input [7:0]x;output [2:0]y;reg [2:0]y;always@(x)begincase (x)8'b00000001:y=3'b000; //当当 x=8 ’b00000001,则则 y 输出为 3 ’b0008'b00000010:y=3'b001; //当当 x=8 ’b00000010,则则 y 输出为 3 ’b0018'b00000100:y=3'b010; //当当 x=8 ’b00000100,则则 y 输出为 3 ’b0108'b00001000:y=3'b011; //当当 x=8 ’b00001000,则则 y 输出为 3 ’b0118'b00010000:y=3'b100; //当当 x=8 ’b00010000,则则 y 输出为 3 ’b1008'b00100000:y=3'b101; //当当 x=8 ’b00100000,则则 y 输出为 3 ’b1018'b01000000:y=3'b110; //当当 x=8 ’b01000000,则则 y 输出为 3 ’b1108'b10000000:y=3'b111; //当当 x=8 ’b10000000,则则 y 输出为 3 ’b111default: y=3'b000;endcaseendendmodule上述编码器有⼀个缺点,即在某⼀个时刻只允许有⼀个有效的输⼊,⽽同时若⼜有两个或两个以上的输⼊信号要求编码,输出端⼀定会发⽣混乱,出现错误。

实验三 3-8译码器的功能测试及仿真

实验三3-8译码器功能测试及仿真一、实验目的1、掌握中规模集成3-8译码器的逻辑功能和使用方法。

2、进一步掌握VHDL语言的设计。

二、预习要求复习有关译码器的原理。

三、实验仪器和设备1.数字电子技术实验台1台2.数字万用表1块3.导线若干4.MUX PLUSII软件5.74LS138集成块若干四、实验原理译码器是一个多输入、多输出的组合逻辑电路。

它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。

译码器在数字系统中有广泛的用途,不仅用于代码的转换、终端的数字显示,还用于数据分配,存贮器寻址和组合控制信号等。

不同的功能可选用不同种类的译码器。

译码器分为通用译码器和显示译码器两大类。

前者又分为变量译码器和代码变换译码器。

1.变量译码器(又称二进制译码器)用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。

若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。

而每一个输出所代表的函数对应于n个输入变量的最小项。

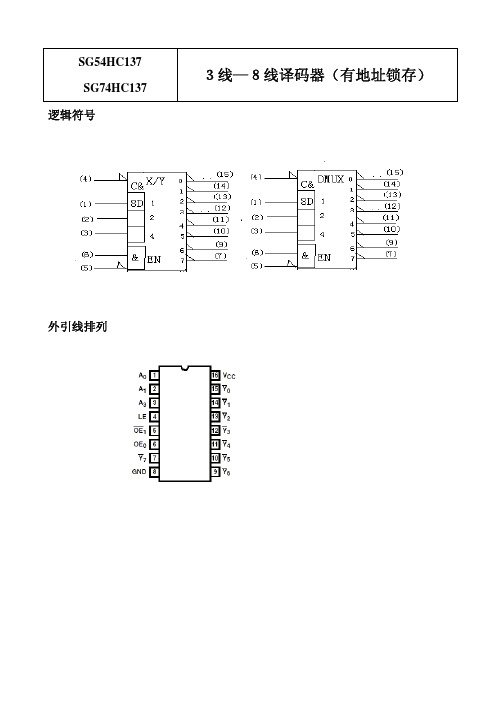

以3线-8线译码器74LS138为例进行分析,下图(a)、(b)分别为其逻辑图及引脚排列。

其中 A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S为使能端。

下表为74LS138功能表,当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其它所有输出端均无信号(全为1)输出。

当S1=0,2S+3S=X时,或 S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。

3-8线译码器74LS138逻辑图及引脚排列图74LS138功能表输入输出S12S+3S A2A1A00Y1Y2Y3Y4Y5Y6Y7Y1 0 0 0 0 0 1 1 1 1 1 1 11 0 0 0 1 1 0 1 1 1 1 1 11 0 0 1 0 1 1 0 1 1 1 1 11 0 0 1 1 1 1 1 0 1 1 1 11 0 1 0 0 1 1 1 1 0 1 1 11 0 1 0 1 1 1 1 1 1 0 1 11 0 1 1 0 1 1 1 1 1 1 0 11 0 1 1 1 1 1 1 1 1 1 1 00 ×××× 1 1 1 1 1 1 1 1× 1 ××× 1 1 1 1 1 1 1 1二进制译码器实际上也是负脉冲输出的脉冲分配器。

三八译码器逻辑表达式

三八译码器逻辑表达式

三八译码器是一种组合逻辑电路,用于将三个二进制输入信号翻译为八个输出信号。

其逻辑表达式可以表示为:L0, L1, L2, L3, L4, L5, L6, L7 = A2'A1'A0', A2'A1A0, A2'A1A0', A2A1'A0', A2A1A0', A2A1A0, A2A1'A0, A2A1A0'

其中,A2、A1、A0是输入信号,L0、L1、L2、L3、L4、L5、L6、L7是输出信号。

这个逻辑表达式包含了输入信号的所有可能组合,对应于每个输入组合,都有一个输出信号为1,其余输出信号为0。

因此,三八译码器可以将三个二进制输入信号翻译为八个输出信号,用于驱动八个不同的电路或设备。

在实际应用中,可以根据需要选择不同数量的输入信号和输出信号,以实现不同的译码功能。

同时,也可以通过添加适当的门电路来扩展三八译码器的功能,例如将输出信号进行反相或与门操作等。

总之,三八译码器是一种非常有用的组合逻辑电路,广泛应用于数字电路设计中。

通过掌握其逻辑表达式和功能特点,可以更好地理解和应用这种电路。

3-8译码器(2)

三八译码器的设计与实现一.实验内容用FPGA设计一个3-8译码器,采用基本门结构化描述二.实验原理3-8译码器的真值表如下所示:根据这个真值表,我们画出卡诺图,化简之后就得到每个输出对应的组合逻辑,即得到如下的电路图根据这个电路图我们就可以写出3-8译码器的门电路的实现。

三.实验过程从上面的电路图我们可以看出需要若干个四输入与非门和三输入的非与门。

四输入与非门源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity and4not isPort ( in1 : in STD_LOGIC;in2 : in STD_LOGIC;in3 : in STD_LOGIC;in4 : in STD_LOGIC;out1 : out STD_LOGIC);end and4not;architecture Behavioral of and4not issignal temp1: STD_LOGIC;signal temp2: STD_LOGIC;signal temp3: STD_LOGIC;begintemp1 <= in1 and in2;temp2 <= in3 and in4;temp3 <= temp1 and temp2;out1 <= not temp3;end Behavioral;三输入的非与门源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity and3not isPort ( in1 : in STD_LOGIC;in2 : in STD_LOGIC;in3 : in STD_LOGIC;out1 : out STD_LOGIC);end and3not;architecture Behavioral of and3not issignal temp1: STD_LOGIC;begintemp1 <= in1 and (not in2);out1 <= temp1 and (not in3);end Behavioral;再在顶层模块里把这些器件按原理图连接起来就行了. 源程序如下:library IEEE;use IEEE.STD_LOGIC_1164.ALL;entity decoder isPort ( A : in STD_LOGIC;B : in STD_LOGIC;C : in STD_LOGIC;S1 : in STD_LOGIC;S2 : in STD_LOGIC;S3 : in STD_LOGIC;Y0 : out STD_LOGIC;Y1 : out STD_LOGIC;Y2 : out STD_LOGIC;Y3 : out STD_LOGIC;Y4 : out STD_LOGIC;Y5 : out STD_LOGIC;Y6 : out STD_LOGIC;Y7 : out STD_LOGIC);end decoder;architecture Behavioral of decoder is COMPONENT and4notPort ( in1 : in STD_LOGIC;in2 : in STD_LOGIC;in3 : in STD_LOGIC;in4 : in STD_LOGIC;out1 : out STD_LOGIC);end COMPONENT;COMPONENT and3notPort ( in1 : in STD_LOGIC;in2 : in STD_LOGIC;in3 : in STD_LOGIC;out1 : out STD_LOGIC);end COMPONENT;signal temp1:STD_LOGIC;beginU0:and3not PORT MAP(S1,S2,S3,temp1);U1:and4not PORT MAP(not A,not B,not C,temp1,y0); U2:and4not PORT MAP(A,not B,not C,temp1,y1);U3:and4not PORT MAP(not A,B,not C,temp1,y2);U4:and4not PORT MAP(A,B,not C,temp1,y3);U5:and4not PORT MAP(not A,not B,C,temp1,y4);U6:and4not PORT MAP(A,not B,C,temp1,y5);U7:and4not PORT MAP(not A,B,C,temp1,y6);U8:and4not PORT MAP(A,B,C,temp1,y7);end Behavioral;由于有5个输入量,因此输入共有32种情况,仿真程序如下: LIBRARY ieee;USE ieee.std_logic_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY decoderwb ISEND decoderwb;ARCHITECTURE behavior OF decoderwb IS-- Component Declaration for the Unit Under Test (UUT)COMPONENT decoderPORT(A : IN std_logic;B : IN std_logic;C : IN std_logic;S1 : IN std_logic;S2 : IN std_logic;S3 : IN std_logic;Y0 : OUT std_logic;Y1 : OUT std_logic;Y2 : OUT std_logic;Y3 : OUT std_logic;Y4 : OUT std_logic;Y5 : OUT std_logic;Y6 : OUT std_logic;Y7 : OUT std_logic);END COMPONENT;--Inputssignal A : std_logic := '0';signal B : std_logic := '0';signal C : std_logic := '0';signal S1 : std_logic := '0';signal S2 : std_logic := '0';signal S3 : std_logic := '0';--Outputssignal Y0 : std_logic;signal Y1 : std_logic;signal Y2 : std_logic;signal Y3 : std_logic;signal Y4 : std_logic;signal Y5 : std_logic;signal Y6 : std_logic;signal Y7 : std_logic;-- No clocks detected in port list. Replace <clock> below with -- appropriate port nameBEGIN-- Instantiate the Unit Under Test (UUT)uut: decoder PORT MAP (A,B,C,S1,S2,S3,Y0,Y1,Y2,Y3,Y4,Y5,Y6,Y7);-- Stimulus processstim_proc: processbegin-- hold reset state for 100 ns.A<='0';B<='0';C<='0';S1<='0';S2<='0';S3<='0';wait for 100 ns;A<='0';B<='0';C<='0';S1<='0';S2<='0';S3<='1';wait for 100 ns;A<='0';B<='0';C<='0';S1<='0';S2<='1';S3<='0';wait for 100 ns;A<='0';B<='0';C<='0';S1<='0';S2<='1';S3<='1';A<='0';B<='0';C<='0';S1<='1';S2<='0';S3<='0'; wait for 100 ns;A<='0';B<='0';C<='0';S1<='1';S2<='0';S3<='1'; wait for 100 ns;A<='0';B<='0';C<='0';S1<='1';S2<='1';S3<='0'; wait for 100 ns;A<='0';B<='0';C<='0';S1<='1';S2<='1';S3<='1'; wait for 100 ns;A<='0';B<='0';C<='1';S1<='0';S2<='0';S3<='0'; wait for 100 ns;A<='0';B<='0';C<='1';S1<='0';S2<='0';S3<='1'; wait for 100 ns;A<='0';B<='0';C<='1';S1<='0';S2<='1';S3<='0'; wait for 100 ns;A<='0';B<='0';C<='1';S1<='0';S2<='1';S3<='1'; wait for 100 ns;A<='0';B<='0';C<='1';S1<='1';S2<='0';S3<='0'; wait for 100 ns;A<='0';B<='0';C<='1';S1<='1';S2<='0';S3<='1'; wait for 100 ns;A<='0';B<='0';C<='1';S1<='1';S2<='1';S3<='0'; wait for 100 ns;A<='0';B<='0';C<='1';S1<='1';S2<='1';S3<='1'; wait for 100 ns;A<='0';B<='1';C<='0';S1<='0';S2<='0';S3<='0'; wait for 100 ns;A<='0';B<='1';C<='0';S1<='0';S2<='0';S3<='1'; wait for 100 ns;A<='0';B<='1';C<='0';S1<='0';S2<='1';S3<='0'; wait for 100 ns;A<='0';B<='1';C<='0';S1<='0';S2<='1';S3<='1'; wait for 100 ns;A<='0';B<='1';C<='0';S1<='1';S2<='0';S3<='0'; wait for 100 ns;A<='0';B<='1';C<='0';S1<='1';S2<='0';S3<='1'; wait for 100 ns;A<='0';B<='1';C<='0';S1<='1';S2<='1';S3<='0'; wait for 100 ns;A<='0';B<='1';C<='0';S1<='1';S2<='1';S3<='1'; wait for 100 ns;A<='0';B<='1';C<='1';S1<='0';S2<='0';S3<='0'; wait for 100 ns;A<='0';B<='1';C<='1';S1<='0';S2<='0';S3<='1';A<='0';B<='1';C<='1';S1<='0';S2<='1';S3<='0'; wait for 100 ns;A<='0';B<='1';C<='1';S1<='0';S2<='1';S3<='1'; wait for 100 ns;A<='0';B<='1';C<='1';S1<='1';S2<='0';S3<='0'; wait for 100 ns;A<='0';B<='1';C<='1';S1<='1';S2<='0';S3<='1'; wait for 100 ns;A<='0';B<='1';C<='1';S1<='1';S2<='1';S3<='0'; wait for 100 ns;A<='0';B<='1';C<='1';S1<='1';S2<='1';S3<='1'; wait for 100 ns;A<='1';B<='0';C<='0';S1<='0';S2<='0';S3<='0'; wait for 100 ns;A<='1';B<='0';C<='0';S1<='0';S2<='0';S3<='1'; wait for 100 ns;A<='1';B<='0';C<='0';S1<='0';S2<='1';S3<='0'; wait for 100 ns;A<='1';B<='0';C<='0';S1<='0';S2<='1';S3<='1'; wait for 100 ns;A<='1';B<='0';C<='0';S1<='1';S2<='0';S3<='0'; wait for 100 ns;A<='1';B<='0';C<='0';S1<='1';S2<='0';S3<='1'; wait for 100 ns;A<='1';B<='0';C<='0';S1<='1';S2<='1';S3<='0'; wait for 100 ns;A<='1';B<='0';C<='0';S1<='1';S2<='1';S3<='1'; wait for 100 ns;A<='1';B<='0';C<='1';S1<='0';S2<='0';S3<='0'; wait for 100 ns;A<='1';B<='0';C<='1';S1<='0';S2<='0';S3<='1'; wait for 100 ns;A<='1';B<='0';C<='1';S1<='0';S2<='1';S3<='0'; wait for 100 ns;A<='1';B<='0';C<='1';S1<='0';S2<='1';S3<='1'; wait for 100 ns;A<='1';B<='0';C<='1';S1<='1';S2<='0';S3<='0'; wait for 100 ns;A<='1';B<='0';C<='1';S1<='1';S2<='0';S3<='1'; wait for 100 ns;A<='1';B<='0';C<='1';S1<='1';S2<='1';S3<='0'; wait for 100 ns;A<='1';B<='0';C<='1';S1<='1';S2<='1';S3<='1';A<='1';B<='1';C<='0';S1<='0';S2<='0';S3<='0';wait for 100 ns;A<='1';B<='1';C<='0';S1<='0';S2<='0';S3<='1';wait for 100 ns;A<='1';B<='1';C<='0';S1<='0';S2<='1';S3<='0';wait for 100 ns;A<='1';B<='1';C<='0';S1<='0';S2<='1';S3<='1';wait for 100 ns;A<='1';B<='1';C<='0';S1<='1';S2<='0';S3<='0';wait for 100 ns;A<='1';B<='1';C<='0';S1<='1';S2<='0';S3<='1';wait for 100 ns;A<='1';B<='1';C<='0';S1<='1';S2<='1';S3<='0';wait for 100 ns;A<='1';B<='1';C<='0';S1<='1';S2<='1';S3<='1';wait for 100 ns;A<='1';B<='1';C<='1';S1<='0';S2<='0';S3<='0';wait for 100 ns;A<='1';B<='1';C<='1';S1<='0';S2<='0';S3<='1';wait for 100 ns;A<='1';B<='1';C<='1';S1<='0';S2<='1';S3<='0';wait for 100 ns;A<='1';B<='1';C<='1';S1<='0';S2<='1';S3<='1';wait for 100 ns;A<='1';B<='1';C<='1';S1<='1';S2<='0';S3<='0';wait for 100 ns;A<='1';B<='1';C<='1';S1<='1';S2<='0';S3<='1';wait for 100 ns;A<='1';B<='1';C<='1';S1<='1';S2<='1';S3<='0';wait for 100 ns;A<='1';B<='1';C<='1';S1<='1';S2<='1';S3<='1';wait for 100 ns;-- insert stimulus hereend process;END;运行仿真程序,即得到如下的仿真结果:四.实验结果与分析此次实验没有要求上板,因此仿真结果就是最终的结果,可以看出这次实验还是很好完成了既定的任务。

38译码器实验报告

38译码器实验报告实验原理:译码器是数字电路中的组合逻辑电路,它的作用是把二进制码组转换为相应的十进制数或BCD码。

由于是多对一的映射关系,故称为译码器。

常用的译码器有十进制译码器、BCD译码器、7段译码器(数码管译码器)等。

本次实验使用的是常用的数字电路集成电路74HC138,它是一个三-八行数码管译码器,能将3位二进制码译成8种不同的输出。

实验内容:1. 搭建实验电路:将74HC138译码器与LED灯和电路板上的电源和接地线连接。

2. 上电测试:将电路板插到插座上,上电后,LED灯按照二进制码的不同组合依次闪烁。

3. 换成7段数码管:将LED灯换成7段数码管,上电后,数码管能够显示不同数字。

实验步骤:1. 准备材料:电路板、74HC138译码器、LED灯、7段数码管、220欧姆电阻、杜邦线、面包板、数字万用表等。

2. 按照示意图,在面包板上连接电路,连接如下:将电源和接地线连接到面包板中。

将74HC138译码器的8个输出引脚连接到面包板的8个LED灯的阳极上,并通过220欧姆电阻连接到接地线上。

同时,将74HC138译码器的3个选择输入引脚连接到面包板的数字端口(1-3号端口)。

74HC138的数据输入引脚不连接。

将7段数码管的A-G引脚连接到面包板的数字端口(4-10号端口),将7段数码管的DP引脚接到接地线上。

3. 检查电路连接:确保每个引脚都连接到正确的端口。

使用数字万用表进行连通性测试。

5. 更换电路元件:将LED灯换成7段数码管。

使用数字万用表确认7段数码管引脚与数字端口的连接关系。

6. 上电测试:再次上电,调整数字端口上的开关,能够让7段数码管显示不同的数字。

实验结果:经过搭建和调试,我们成功实现了74HC138译码器的上电测试和数码管显示的功能。

我们通过手动改变数字端口上的开关状态,成功地改变了LED灯的亮灭顺序和7段数码管的显示数字。

实验结果显示,译码器具有将二进制码组转换为相应十进制数或BCD码的功能,能够广泛应用于数字电路中。

3-8译码器

可编程逻辑实验器件实验报告3-8译码器班级:13电子1班组长:阮灼雄(131201127) 组员:沈平(131201128)石鑫(131201129)宋惠聪(131201130) 制作人:石鑫指导老师:龚兰芳目录一正文:(1)设计要求------(2)设计目的------(3)设计方案------(4)任务要求------(5)设计原理------(6)硬件要求------(7)设计步骤------(8)参考程序------(9)引脚分配------(10)硬件测试报告及数据处理分析结果------二心得:一正文:(1)设计要求用VHDL语言设计一个3-8译码器的程序,输入是三位二进制数,输出是对应的是十进制0-7。

编写完程序之后在开发系统上进行硬件测试。

(2)设计目的掌握3-8译码器的构成、原理与设计方法。

(3)设计方案设计一个程序,用8段数码管和矩阵8*8来做实验现象,三个开关来控制输入,使他能够显示。

(4)任务要求将输入的二值代码转换成对应的高低电平信号,称为译码。

他是编码的反操作。

实现译码操作的电称为译码器。

译码器分为二进制译码器,十进制译码器及数字符显示译码器,各种译码器的工作原理类似,设计方法相同。

设二进制译码器的输入段位N 个,则输出端为2N个,且对于输入代码的每一种态,2N个输出只有一个为1(或为0),其余全为(或为1)。

(5)设计原理输入3位二进制代码,输出8个互斥的信号。

(6)硬件要求1)主芯片Altera EPM240T100C5。

2)8*8矩形点阵。

3)3个拨码开关。

4)电源模板和晶振模块。

(7)设计步骤编写程序,然后仿真,拨打三个开关,然后让数码管进行显示,并且能够在8*8矩阵进行显示,记下实验结果,掌握3-8译码器的功能。

(8)参考程序library ieee;use ieee.std_logic_1164.all;entity yima3_8 isport (a:in std_logic_vector(2 downto 0);y:buffer std_logic_vector(7 downto 0);l:out std_logic_vector(7 downto 0);row1:out std_logic_vector(7 downto 0));end yima3_8;architecture behav of yima3_8 is beginrow1<="11111110";with a selecty<= "00000001"when"000","00000010"when"001","00000100"when"010","00001000"when"011","00010000"when"100","00100000"when"101","01000000"when"110","10000000"when"111","00000000"when others; l<=y;end behav;(9)引脚分配(10)硬件测试报告及数据处理分析结果实验中,数码管和矩阵8*8能够随着开关的拨打而进行显示。

3-8译码器

组合电路——3-8译码器的设计一、实验目的1、通过一个简单的3-8译码器的设计,让学生掌握组合逻辑电路的设计方法。

2、熟悉原理图输入及仿真步骤。

3、掌握组合逻辑电路的静态测试方法。

4、初步了解可编程器件设计的全过程。

5、理解硬件描述语言和具体电路的映射关系。

二、硬件要求主芯片Altera EPM7128SLC84-15,时钟。

三、实验内容描述一个3线-8线译码器,使能端为g1、g2a、g2b,地址选择端为a、b、c,输出端为总线y。

四、实验原理三-八译码器三输入,八输出。

当输入信号按二进制方式的表示值为N时,输入端低电平有效输出端从零到八记,标号为N输出端输出低电平表示有信号产生,而其它则为高电平表示无信号产生。

三个输入端能产生的组合状态有八种。

电路符号:3-8译码器器工作原理框图。

如图1所示。

图1五、实验源程序:decoder3_8.vhdlibrary ieee;use ieee.std_logic_1164.all;entity decoder3_8 isport(a,b,c,g1,g2a,g2b:in std_logic;y:out std_logic_vector(7 downto 0));end ;architecture rtl of decoder3_8 issignal dz:std_logic_vector(2 downto 0);begindz<=c&b&a;process(dz,g1,g2a,g2b )beginif (g1='1' and g2a='0' and g2b='0') thencase dz iswhen "000"=>y<="11111110";when "001"=>y<="11111101";when "010"=>y<="11111011";when "011"=>y<="11110111";when "100"=>y<="11101111";when "101"=>y<="11011111";when "110"=>y<="10111111";when "111"=>y<="01111111";when others=>y<="XXXXXXXX"; end case;elsey<="11111111";end if;end process;end;六、波形仿真结果。

3-8译码器的不同实现的比较

EDA课程作业一个电子系统(例如3-8译码器)可由单片机技术实现,也可由EDA技术实现,比较两种方案各自的特点。

答:关于两种方案各自的优缺点,我们将在如下几方面讨论:(1)处理速度上①数据处理方式单片机的任何运算必须经过累加器,因而可视为一种串行处理;而EDA对输入的处理由其内部的各独立门电路独立完成,可视为一种并行处理。

相比之下,EDA技术在处理输入时没有取指令、输入采样、运算、输出等过程,因而处理速度上远远高于单片机技术。

②硬件结构上单片机的硬件结构是一种通用的结构,是通过执行一些指令来实现3-8译码器的功能的。

而EDA技术用的是一种专门为3-8译码器的电路实现功能的。

因而针对性更强,速度更快。

综上,EDA技术与单片机技术相比较,在处理数据上速度远比后者快。

(2)实现多个3-8译码器时的差别①单片机实现以常见的ATmega16为例。

Mega16有4个IO口,共32脚,一片单片机上最多实现3个3-8译码器。

但由于单片机必须分配给每个译码器一个时间片来实现每一个译码器的功能。

因而在处理高频输入信号时会有很大的误差,甚至不能实现功能。

此外,对于多个译码器的操作,单片机不论是采用轮询方式还是中断驱动方式,都会给编程造成一定难度。

②EDA技术实现因PLD引脚数、集成度等资源限制,在实现数量上并不一定会比单片机多。

但如果是集成度很高的CPLD、FPGA应该可以在单片上实现数量众多的3-8译码器。

而且各3-8译码器由独立的门电路实现,并行处理,互不干扰。

可以实现对高频的、大量的输入的处理。

并且编程简单。

(3)工作频率上①单片机实现(1)、(2)中已经提到,单片机对高频的信号处理能力不足。

原因在于其工作频率不高。

可以通过更换外部晶振提高单片机工作频率,但以51系列单片机为例,晶振大多为8M、12M,工作频率并不高。

②EDA实现有些EDA系统中时钟频率可以高达50M,而且可以通过软件方式分频给不同门电路以不同的时钟信号,让EDA系统可以同时处理频率相差很大的输入信号。

3-8译码器

摘要EDA技术是指以计算机为工作平台,融合了应用电子技术、计算机技术、信息处理及智能化技术的最新成果,进行电子产品的自动设计。

利用EDA工具,电子设计师可以从概念、算法、协议等开始设计电子系统,大量工作可以通过计算机完成,并可以将电子产品从电路设计、性能分析到设计出IC版图或PCB版图的整个过程的计算机上自动处理完成。

现在对EDA的概念或范畴用得很宽。

包括在机械、电子、通信、航空航天、化工、矿产、生物、医学、军事等各个领域,都有EDA的应用。

目前EDA技术已在各大公司、企事业单位和科研教学部门广泛使用。

例如在飞机制造过程中,从设计、性能测试及特性分析直到飞行模拟,都可能涉及到EDA技术。

本文所指的EDA技术,主要针对电子电路设计、PCB设计和IC设计。

EDA设计可分为系统级、电路级和物理实现级。

关键词译码,VHDL语言,MAX+PLUSⅡAbstractEDA technology refers to the computer for working platform, shirt-sleeve application of electronic technology, computer technology and information processing and intelligent technology to the latest achievements of electronic products, the automatic design.Using EDA tools, electronic stylist can be from concept, algorithm, agreement, etc, begin to design your electronic system a lot work can be finished by computer and electronic products can be from circuit design, performance analysis to design the IC territory or PCB layout the whole process of the computer automatically complete the processing.Now on the concept of using EDA or category very wide. Included in machinery, electronics, communication, aerospace, chemical, mineral, biology, medicine, military and other fields, have EDA applications. Current EDA technology has in big companies, enterprises, institutions and teaching research departments extensive use. For example in the aircraft manufacturing process, from design, performance testing and characteristic analysis until a flight simulator, all may involve EDA technology. Globalization-the EDA technology, mainly in electronic circuit design, PCB design and IC design.EDA can be divided into system level and circuit-level and physical implementation level.Keywords cent, the VHDL language, MAX+PLUS II目录摘要 (I)ABSTRACT (II)目录 .............................................................................................................................................. I II 引言 (1)一EDA技术简介 (2)1.1EDA技术的概念 (2)1.2EDA技术的特点 (2)1.3EDA设计技术的主要内容 (2)1.4EDA设计技术的方法 (2)1.5EDA技术的发展趋势 (3)二硬件语言VHDL描述 (5)2.1VHDL概述 (5)2.2VHDL语言的特点 (5)2.3VHDL语言的基本结构 (6)2.4VHDL语言的设计方法 (6)2.5VHDL语言的设计流程 (6)三3-8译码器 (7)3.1M AX+PLUS II软件介绍 (7)3.23-8译码器的工作原理和VHDL语言程序 (7)3.2.1 3-8译码器的工作原理 (7)3.2.2 3-8译码器的VHDL语言程序 (8)3.33-8译码器的仿真和原理分析 (9)3.3.1 3-8译码器的仿真步骤 (9)3.3.2 3-8译码器的仿真波形 (13)3.3.3 3-8译码器的仿真波形分析 (13)3.3.4 3-8译码器的原理框图 (14)结论 (15)致谢 (16)参考文献 (17)附录A (18)附录B (19)附录C (20)引言随着社会的发展,科学技术也在不断的进步。

3线8线译码器(有地址锁存)

3线—8线译码器(有地址锁存)

外引线排列

极

限

值

推荐工作条件

电源电压 输入电压 输出电压 输入电流 输出电流

电源电流

VCC…………….-0.5~+7.0V V1….…..-1.5V~+Vcc+1.5V VO……….-0.5V~Vcc+0.5V I1(每端)…….…..±20mA IO(每端)…………...± 25mA

1.2

1.2

2.0

1.9

1.9

1.9

4.5

4.4

4.4

4.4

V

6.0

5.9

5.9

5.9

VI=VIL或VIH

4.5

|IO| ≤4.0mA

6.0

|IO| ≤5.2mA

VI=VIL或VIH

2.0 4.5

|IO| ≤20µA VOL 输出低电平电压

6.0

(最大)

VI=VIL或VIH

4.5

|IO| ≤4.0mA

2.0

195

4.5

39

6.0

33

2.0

100

4.5

20

6.0

17

2.0

50

4.5

10

6.0

8

2.0

75

4.5

15

6.0

13

2.0

80

4.5

16

6.0

14

75

10

246

291

49

58

ns

42

49

125

150

25

30

ns

3-8译码器设计

摘要EDA技术是以微电子技术为物理层面,现代电子设计技术为灵魂,计算机软件技术为手段,最终形成集成电子系统或专用集成电路ASIC为目的的一门新兴技术。

而VHDL语言是硬件描述语言之一,其广泛应用性和结构的完整性使其成为硬件描述语言的代表。

随着社会经济和科技的发展,越来越多的电子产品涌如我们的日常生活当中,在日常生活中译码器起着不可忽视的作用。

本设计就是运用VHDL语言设计的3-8译码器。

3-8译码器电路的输入变量有三个即D0,D1,D2,输出变量有八个Y0-Y7,对输入变量D0,D1,D2译码,就能确定输出端Y0-Y7的输出端变为有效(低电平),从而达到译码目的。

关键词 EDA 输入,输出,译码器AbstractEDA technology is for the physical plane microelectronics technology, modern electronic design technology for the soul, and computer software technology as the means, and finally form integrated electronic system or application-specific integrated circuit ASIC for the purpose of a new technology. And VHDL language is one of the hardware description language, which are widely applied and theintegrity of the structure to make it a hardware description language representative.Along with the social economy and the development of science and technology, more and more electronic product surged into our daily life in the daily life of decoder plays an important role. This design is theuse of the design of 3-VHDL language 8 decoder. 3-8 decoder circuit, input variables have three namely D0, D1, D2, output variable has eight Y0-Y7, D0 to input variables, D1, D2 decoding, can determine the output, the output terminal of the Y0-Y7 into effective (low level), so as to achieve the purpose decoding.Key word EDA input output decode目录引言EDA(Electronic Design Automation)技术是现代电子工程领域的一门新技术。

74LS138的工作原理

74LS138的工作原理

74LS138是一个3-8线译码器/解码器集成电路。

它有3个输入线A0,A1和A2,以及8个输出线Y0-Y7。

其工作原理如下:

1. 输入选择:根据输入线A2、A1和A0的逻辑电平,选择要

激活的输出线。

2. 译码功能:当输入线的逻辑电平满足特定条件时,将激活相应的输出线。

输出线上的逻辑电平取决于电路连接的方式,可以是高电平、低电平或三态(输出线不连接到任何电路)。

3. 解码功能:74LS138还可以作为解码器使用。

在解码模式下,输入线A2、A1和A0信号负逻辑,将会选择并激活一个输出线,其余输出线处于三态。

4. 输出端:输出线Y0-Y7的状态由输入线A2、A1和A0的逻

辑电平决定。

其中,只有一个输出线为低电平,其余输出线为高电平或三态(解码模式下)。

5. 使能端:除了输入线和输出线之外,74LS138还具有使能端(通常标记为G),通过对使能端进行控制,可以控制

74LS138的工作状态。

综上所述,74LS138通过输入选择和译码功能,根据输入信号

的逻辑电平激活特定的输出线,实现3-8线的译码器/解码器

功能。

3-8译码器 EDA 仿真

项目题目: 3-8译码器的设计姓名:院系:应用技术学院专业:电子信息工程(仪器)学号:指导教师:综合成绩:完成时间: 2011 年5月 3 日一、 项目实验内容摘要(1)实验目的1、 通过一个简单的 3-8译码器的设计,掌握组合逻辑电路的设计方法。

2、 掌握组合逻辑电路的静态测试方法。

3、 初步掌握QUARTUS Ⅱ原理图输入方法设计的全过程。

(2) 实验的硬件要求:1、 输入:DIP 拨码开关3位。

2、输出:LED 灯。

3、主芯片:EP1K1OTC100-3。

(3) 实验原理:三-八译码器为三输入,八输出。

当输入信号按二进制方式的表示值为N 时(输入端低电平有效),输出端从零到八记,标号为N 输出端输出低电平表示有信号产生,而其它则为高电平表示无信号产生。

因为三个输入端能产生的组合状态有八种,所以输出端在每种组合中仅有一位为低电平的情况下,能表示所有的输入组合,因此不需要像编码器实验那样再用一个输出端指示输出是否有效。

但可以在输入中加入一个输出使能端,用来指示是否将当前的输入进行有效的译码,当使能端指示输入信号无效或不用对当前信号进行译码时,输出端全为高电平,表示无任何信号。

本例设计中没有考虑使能端,自己设计时可以考虑加入使能输入端时,程序如何设计。

三-八译码器真值表:三八译码器逻辑函数表达式如下:1270126012501240123012201210120...................................................................A A A Y A A A Y A A A Y A A A Y A A A Y A A A Y A A A Y A A A Y ========二、项目实验项目源代码Library ieee;Use ieee.std_logic_1164.all;Use ieee.std_logic_arith.all;Use ieee.std_logic_unsigned.all;Entity three_eight isPort(a,b,c:in std_logic;D0,d1,d2,d3,d4,d5,d6,d7:out std_logic);End three_eight;Architecture s_b of three_eight isSignal O_11, O_22, O_33:std_logic; --注“O”为字母O,不是数字0。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

试验一组合逻辑3线-8线译码器设计试验

一、试验目的

1、了解并初步掌握ModelSim软件的使用;

2、了解使用ModelSim进行组合数字电路设计的一般步骤;

3、掌握组合逻辑电路的设计方法;

4、掌握组合逻辑电路3线-8线译码器的原理;

5、掌握门级建模的方法;

二、试验原理

译码器(Decoder)的逻辑功能是将每个输入的二进制代码译成对应得输出高、低电平或另外一个代码。

因此,译码是编码的反操作。

常用的译码器电路有二进制译码器、二-十进制译码器和显示译码器等。

二进制译码器的输入是一组二进制代码,输出是一组与输入代码一一对应得高、低电平信号。

例如,典型的3线-8线译码器功能框图图1-1所示。

输入的3位二进制代码共有8种状态,译码器将每个输入代码译成对应的一根输出线上的高、低电平信号。

图1-1 3线-8线译码器框图

74HC138是用CMOS门电路组成的3线-8线译码器,它的逻辑图图1-2所示。

表1-1是74HC138的逻辑功能表。

当门电路G S的输出为高电平时,可以由逻辑图写出。

图1-2 74HC138逻辑功能图

表1-1 74HC138逻辑功能表

由上式可以看出,由''07Y Y -同时又是210,,A A A 这三个变量的全部最小项的译码输出,所以也将这种译码器称为最小项译码器。

74HC138有3个附加的控制端''

123,S S S 和。

当''123

S 1,S S 0=+=时,s G 输出为高电平,译码器处于工作状态。

否则,译码器被禁止,所有的输出端被封锁为高电

平。

这3个控制端也称为“片选”输入端,利用片选的作用可以将多片连接起来以扩展译码器的功能;

三、 预习要求

1、数字电子技术基础组合逻辑电路设计一般设计方法;

2、74HC138的逻辑功能;

3、门级建模的一般方法和基本语句;

4、ModelSim 软件的一般使用方法(ModelSim SE Tutorial);

四、 实验步骤

(一)、熟悉ModelSim 软件环境 1、建立一个新Project

1-1双击左面快捷方式或者电击[程序]/[ModelSim SE 6.1f]/[ModelSim]启动ModelSim 6.1(如图1-3);

注意:必须首先关闭IMPORTANT Information 对话框才能开始其它操作;

图1-3

1-2 [File]/[New]/[Project…]新建一个project,会弹出Create Project对话框(如图1-4);

图1-4

⏹Project Name(项目名称)需要填入你所建立的项目的名称;

⏹指定项目所在路径;如果所指定的目录不存在,会弹出对话框提示是否建立

这个目录;一般选择是;

⏹缺省的工作库名;

注意:1、路径一般不应包含汉字;2、逻辑应在ModelSim的安装目录下指定;3、缺省的工作库的名称一般不需要改动;

2、载入HDL元文件

2-1设定好1-2步骤的每项内容后,点击OK,弹出Add items to the Projects对话框;如图1-5所示。

图1-5

⏹Create New File 产生一个新的文件

⏹Add Existing File 将已存在的文件加入Project

⏹Create Simulation 产生一个模拟

⏹Create New Folder 产生一个文件夹

如果事先已经编辑好源文件可以选择Add Existing File,否则应该选择Create New File;我们选择Add Existing File。

将D:\Modeltech_6.1f\examples \tutorials\verilog\projects目录下的counter.v和tcounter.v加入到这个project,如图1-6,1-7所示

图1-6

通过Browse选择想要加入Project的文件名,同时选择Copy to project directory单选框;

●Reference from current location 文件在当前位置不变

●Copy to project directory 将文件拷贝到project所在目录;

注意:以上操作也可以选择[File]/[Add to Project]/[Existing Files]菜单完成,如图1-8所示。

图1-7

图1-8

3、编译compile

3-1 在project标签页内,选择任意文件,点击鼠标右键选择[Compile]/[Compile

All](如图1-9所示)或者选择菜单[Compile]/[Compile All]

图1-9

如果编译的源文件没有错误,那么project标签页的所有文件的status状态项会显示对号,如图1-10;

图1-10

如果源文件中有语法错误,Verilog会在Transcript窗口提供错误信息,用户需要对错误进行修改直到将文件中的全部错误消除为止。

注意:双击红色的出错信息,会有更详细的出错提示;

图1-11

4、模拟Simulate

4-1源文件正确编译后选择[Simulate]\[Start Simulation],弹出Start Simulation对话框。

如图1-12所示

图1-12

点击工作库前面的加号,选择最顶层模块作为Simulate的模块,这里我们选择test_counter作为仿真模块,点击OK按钮后弹出一系列的调试窗口(Debug Windows)。

4-2 如果没有弹出你希望使用的调试窗口,可以选择[View]/[Debug Windows]。

这里我们选择[View]/[Debug Windows]/[Wave],如图1-13所示。

4-3在Objects窗口选择需要加入到Wave窗口中的信号单击右键,选择[Add to Wave]\[Selected Signals],将输入和输出信号加入到Wave窗口。

4-4选择[Simulate]/[Run]/[Run All]开始模拟;可以在Wave窗口中查看仿真波形同时,可以在Transcript窗口观察仿真输出结果。

如图1-14所示。

图1-13

图1-14

(二)、3线-8线译码器设计

1.按照以上介绍的ModelSim软件的一般使用方法,编写Verilog源程序,设

计3线-8线译码器(门级描述);

module

decode38(s1,s2,s3,a0,a1,a2,y0bar,y1bar,y2bar,y3bar,y4bar,y5bar,y6bar,

y7bar);

input s1,s2,s3;

input a0,a1,a2;

output y0bar,y1bar,y2bar,y3bar,y4bar,y5bar,y6bar,y7bar;

wire s1bar,s2bar,s3bar; //声明中间变量

wire a0bar,a1bar,a2bar;

wire gs;

not(s1bar,s1);//非门引用

not(s2bar,s2);

not(s3bar,s3);

not(a0bar,a0);

not(a1bar,a1);

not(a2bar,a2);

and(gs,s1,s2bar,s3bar);//与门

nand g0(y0bar,a0bar,a1bar,a2bar,gs); //与非门

nand g1(y1bar,a0bar,a1bar,a2bar,gs);

nand g2(y2bar,a0bar,a1,a2bar,gs);

nand g3(y3bar,a0,a1,a2bar,gs);

nand g4(y4bar,a0bar,a1bar,a2,gs);

nand g5(y5bar,a0,a1bar,a2,gs);

nand g6(y6bar,a0bar,a1,a2,gs);

nand g7(y7bar,a0,a1,a2,gs);

endmodule

2.用2个3线-8线译码器设计组成1个4线-16线译码器;

3.设计74HC138逻辑功能并使用ModelSim进行模拟(行为描述);(选做)

五、实验内容

1、完成实验步骤中所要求的实验内容;

2、给出简单测试激励块的设计和3线-8线译码器的仿真输出波形;

3、给出简单测试激励块的设计和4线-16线译码器的仿真输出波形;

4、比较用硬件描述语言Verilog HDL设计组合电路与用传统的方法设计电路的

不同;。