K60核心板原理图

K60-02节

K60系列的存储器空间地址映像(一)

地址范围 0x0000_0000~0x0FFF_FFFF 0x1000_0000~0x13FF_FFFF 大小 实际的物理对象 256MB 可编程flash和只读数据(包括一开始1024字节的异常中 断向量) 64MB 对MK60N256VLQ100芯片:未使用 对MK60X256VLQ100芯片:FlexNVM 对MK60N512VLQ100芯片:未使用 对MK60N256VMD100芯片:未使用 对MK60X256VLQ100芯片:FlexNVM 对MK60N512VMD100芯片:未使用

256

512 512

256

256 512

—

4 —

64

64 128

100

100 100

2.4 K60系列微控制器的存储器映像与编程结构

2.4.2 K60系列存储器映像 ARM Cortex-M4为32位处理器内核。内部的数据是32位 的,寄存器是32位的,存储器接口也是32位的。

CPU频 率 (MHz) 100 100 100 120 150 120 150 闪存 (KB) 256 512 256 512 512 1024 1024 FlexNV M (KB) — — 256 512 512 — — SRAM (KB) 64 128 64 128 128 128 128 FlexRA M (KB) — — 4 16 16 — — 100 LQFP 14× 14 + + + — — — — 104 BGA 8× 8 + + + — — — — 144 LQFP 20× 20 + + + + + + + 144 BGA 13× 13 + + + + + + + 196 BGA 15× 15 — — — + + + + 256 BGA 17× 17 — — — + + + +

K60(Rev6-Ch24-MCG)(中文)

第24章多用途时钟信号生成器(MCG)24.1 介绍多用途多用途时钟信号生成器(MCG)模块为MCU提供多种时钟源选项。

这个模块由一个频率环锁(FLL)和一个相位环锁(PLL)组成。

FLL可由一个内部或外部参考时钟控制,而PLL可由一个外部参考时钟控制。

这个模块要么在FLL或PLL输出时钟之间,要么在内部参考时钟或外部参考时钟之间选择一个时钟源以作为MCU系统时钟。

MCG操作与晶体振荡器有关,其中晶体振荡器允许一个外部晶体、陶瓷共振器或外部时钟源产生外部参考时钟。

24.1.1 特性MCG模块的关键特性:◆频率环锁(FLL)。

●数控石晶(DCO)。

●DCO可设置时钟范围有四个。

●低频率外部参考时钟源的编程选项和最大DCO输出频率。

●内外参考时钟可以作为FLL源。

●可以作为其他片上外设的时钟源。

◆相位环锁(PLL)●电压控制振荡器(VCO)●外部参考时钟作为PLL时钟源。

●VCO频分模块。

●相位/频率检测器。

●集成环过滤器。

●可以作为其他片上外设的时钟源。

◆内参考时钟生成器●9个微调位的精确慢时钟●4个微调位的快时钟●可以被用作FLL的时钟源。

在FEI模式下,只有慢内参考时钟(IRC)可以被用作FLL源。

●无论是快时钟还是慢时钟都不能用作MCU的时钟源●可以作为其他片上外设的时钟源。

◆低功耗的石晶时钟发生器位MCG外部参考提供控制信号:●HGO,RANGE,EREFS◆从晶振获得外部时钟●可被用作FLL或PLL的时钟源●可被用作MCU的时钟源◆从RTC获得外部时钟●只能作为FLL的时钟源●只能选择MCU的时钟源◆带有重置请求能力的外部时钟监视器,可以在FBE,PEE,BLPE或者FEE模式下对外部时钟进行监测◆在PLL中使用的有中断请求能力的锁检测器◆外时钟参考的内参考时钟自动裁切功能(ATM)。

◆FLL和PLL的参考分频。

◆为其他片上设备提供时钟源的MCG PLL 时钟(MCGPLLCLK)◆为其他片上设备提供时钟源的MCG FLL时钟(MCGPLLCLK)◆为其他片上设备提供时钟源的MCG Fixed Frequency时钟(MCGPLLCLK)◆为其他片上设备提供时钟源的MCG 内参考时钟(MCGPLLCLK)图24-1 多用途时钟生成器(MCG)框图24.1.2 运行模式MCG共有九中运行模式:FEI,FEE,FBI,FBE,PEE,BLPI,BLPE,和终止模式。

K60核心板说明与扩展板_SD-Ex-D_对接说明

K60核心板说明与扩展板(SDExD)对接说明 1、核心板引脚说明K60一共有100个GPIO口,还有其他为复用的非GPIO口,如USB、ADC 等引脚。

核心板引出了所有的GPIO和其他非K60最小系统的引脚。

具体的引脚如下。

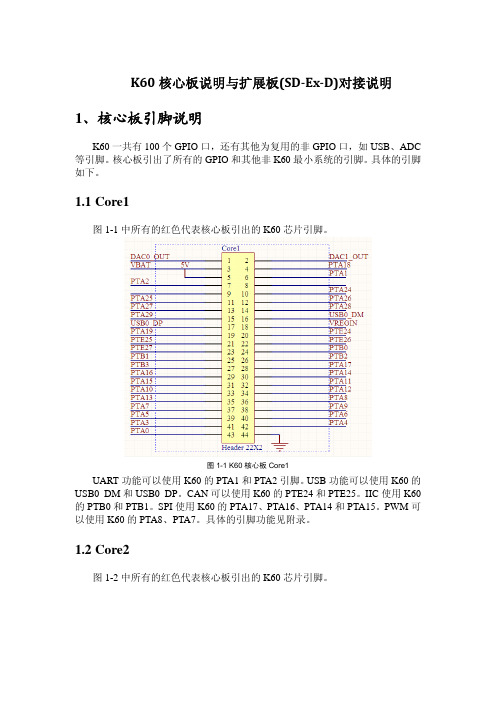

1.1 Core1图1-1中所有的红色代表核心板引出的K60芯片引脚。

图1-1 K60核心板Core1UART功能可以使用K60的PTA1和PTA2引脚。

USB功能可以使用K60的USB0_DM和USB0_DP。

CAN可以使用K60的PTE24和PTE25。

IIC使用K60的PTB0和PTB1。

SPI使用K60的PTA17、PTA16、PTA14和PTA15。

PWM可以使用K60的PTA8、PTA7。

具体的引脚功能见附录。

1.2 Core2图1-2中所有的红色代表核心板引出的K60芯片引脚。

图1-2 K60核心板Core2可以使用K60的ADC1_SE16和ADC0_SE16。

具体的引脚功能见附录。

1.3 Core3图1-3中所有的红色代表核心板引出的K60芯片引脚。

图1-3 K60核心板Core3具体的引脚功能见附录。

2、核心板与大板对接在设计电路时,考虑到与旧的扩展板兼容,做了如下设计,保证K60核心板与扩展板兼容。

以下图片中的蓝色表示大板的功能,红色代表核心板引出引脚。

2.1 Core1图2-1 Core1引脚定义2.2 Core2LCD使用K60的PTE可以实现,具体功能见参考代码。

图2-2 Core2引脚定义AD5和AD9分别接K60的ADC1_SE16和ADC0_SE16。

2.3 Core3可以使用K60的PTC口实现LED功能,具体实现见参考代码。

图2-3 Core3引脚定义3、附录:144引脚资源简明表3.1 硬件最小系统引脚K60N512VM100芯片电源类引脚,BGA封装22个,LQFP封装27个,其中BGA 封装的芯片有五个引脚未使用(A10、B10、C10、M5和L5)。

K60 Nano核心板用户手册

K60 Nano核心板用户手册版本0.1用户手册目录1.K60 Nano板整体介绍 (3)1.1.板载资源 (3)1.2.核心板引脚 (5)2.第一次测试Nano板 (6)2.1.上电测试 (6)2.2.观察LED灯 (7)2.3.观察串口信息 (7)3.快速开发指南 (7)3.1.开发包目录说明 (8)3.2.运行一个示例工程 (9)3.3.更改内核频率 (11)3.4.用模板新建一个工程 (11)4.利用Bootloader给Nano板下载 (13)1.K60 Nano板整体介绍“K60 Nano板”是拉普兰德电子技术独家设计的一款专门应用于飞思卡尔智能车竞赛的最小系统板。

之所以命名为“ Nano板”,是因为他是目前市场上同类产品中尺寸最小的产品,大小仅为5.5cm*3.5cm的PCB板上板载了LQFP-144封装的K60单片机!该核心板不仅在尺寸上占有优势,更集成了其他核心板不具有的功能,如Micro-SD卡座、USB接口等等!K60 Nano核心板整体采用白色PCB板与白色塑胶插针组合,焊盘均为沉金工艺!使得该板不仅在功能上领先同类,更在外观上出类拔萃!该最小系统板的整体照片如图1所示。

该最小系统板的原理图请见文档“K60 Nano核心板原理图”。

图1. K60 Nano板整体概览1.1.板载资源K60 Nano板具有一个JTAG 10Pin仿真/下载接口,引脚数为2x5个,插针距离为标准的100Mil(2.54mm)排针间距。

用户可以使用J-Link V8下载器配合转接板给核心板下载程序。

注意,如果用户需要给Nano板下载程序,必须给板子供电,因为Jlink下载器在默认情况下不能为目标板输出电源。

JTAG接口原理图如图2所示。

小提示:由于采用复合插针,因此该JTAG引脚奇偶对调。

图2. JTAG接口K60 Nano板搭载了4个LED灯,方便开发者调试时指示各种状态,或测试IO口。

这8个LED灯分别与K60芯片的PTA4、PTA6、PTA8和PTA10相连,当IO口为低电平时,对应的LED点亮。

006K60与最小系统-戴敏

K60系列微控制器的存储器映像与编程结构

K60系列微控制器具有: IEEE 1588以太网 全速和高速USB 2.0 硬件加密和防窜改探测能力, 具有丰富的模拟、通信、定时和控制外设 256 KB~ 1MB闪存

第7页,共35页。

K60系列的模 块结构框图

1.内核模块

2.系统模块 3.存储模块

ADC/RTC/UART/SPI/I2S/SDHC/GPIO

第20页,共35页。

3)K60的硬件最小系统原理图

单片机内部虽然集成了很多电路,但仍旧不能独立运行,必须 要外连一些电路,才能使单片机运行起来。这种能使单片机工 作的最简电路,我们叫做单片机最小系统。

一般情况下,MCU的硬件最小系统由电源、晶振及复位等电路组成。 芯片要能工作,必须有电源与工作时钟。 复位电路则提供不掉电情况下MCU重新启动的手段。

第11页,共35页。

K60系列的存储器空间地址映像(二)

地址范围 0x4000_0000~0x4007_FFFF

大小

实际的物理对象

512KB 外设总线0的位寻址区(AIPS-Lite0)

0x4008_0000~0x400F_EFFF 508KB 外设总线1的位寻址区(AIPS-Lite1)

0x400F_F000~0x400F_FFFF 4KB 通用输入输出的位寻址区

L6

42

30

3.3V RTC模块的输入电源(可电池供电)

电源

VDDA、VSSA H5、H6 31、34

22、25

30.V3V、A/D模块的输入电源

VREFH、 VREFL

G5、G6 32、33

23、24

30.V3V、A/D模块的参考电压

Kinetis K60核心板套件用户手册V2.0

通联物网Kinetis K60 Cortex ™-M4 核心板+扩展板用户手册(ARM ® Cortex ™-M4 V2.0)北京通联物网教育咨询有限公司更新说明1、本次更新为2.0版本2、本次更新了K60套板的全部基础案例,共计59个案例。

后续基于KL04的传感器模块基础实验会不断更新到本文档目录更新说明 (2)目录 (3)一、Kinetis K60 Cortex ™-M4 (4)二、产品介绍 (6)1、产品简介 (6)2、开发板硬件资源 (10)2.1、核心开发板硬件资源 (10)2.2、通用扩展开发板硬件资源 (11)2.3 K60 核心板+通用扩展板配套光盘资料 (12)2.4 K60 核心板+扩展板C语言代码实验案例 (13)三、实验案例操作方法 (13)3.1搭建开发环境 (13)3.2安装串口转USB接口驱动 (15)3.3建立实验调试“超级终端”环境 (15)3.4注意事项及建立IAR6.3调试环境 (18)3.5基础案例 (23)一、Kinetis K60 Cortex ™-M4核心板+扩展板及配件照片:图1-1 K60/K10 核心板(正面)图1-2 K60/K10 核心板(反面)图1-3 K60 完全版扩展板(正面)图1-4 K60/K10 核心板+简化扩展板+JLINK 仿真器连接图图1-5 JLINK V8 仿真器二、产品介绍1、产品简介Cortex-M 系列内核是ARM 公司针对低功耗和高性能的嵌入式控制市场而开发的内核。

Cortex-M0 和Cortex-M3 系列芯片广泛的应用于智能仪表、智能卡、智能家电、智能玩具、短距离联网应用(Zigbee 和NFC)、汽车电子和高效电机控制等领域。

ST、TI、NXP、Atmel 和东芝等芯片设计公司都已经推出Cortex-M3 的MCU。

Cortex-M4 是ARM 公司于2009 年下半年推出的内核,其性能比Cortex-M3 提高20%。

野火K60 测试说明书

野火K60核心板和调试板测试说明书欢迎使用野火 K60 核心板,现在让我们走近K60……目录野火K60核心板和调试板测试说明书 (1)1.K60 核心板资源介绍 (2)2.供电方式 (2)排针供电 (2)USB供电 (3)Jlink供电 (4)3.J-Flash下载固件 (7)4.野火鹰眼软排线转接板 (11)5.测试方案 (13)LED测试 (13)USB测试 (14)摄像头无线发送模式 (18)调试板测试模式 (20)1. K60 核心板资源介绍首先,拿到我们的野火K60核心板,先来熟悉我们的板载资源:图 1 野火核心板正面 图 2野火核心板背面2. 供电方式 排针供电野火K60核心板的排针,有专门的5V 电源输入和3.3V 电源输入管脚,两者可任意选择其中一个来进行供电。

如果是采用5V 供电,则通过板载的LDO 芯片转换为3.3V ,供控制器、无线模块、摄像头使用。

建议采用 5V 供电,板载专用的低压差线性LDO 更能保证电源的稳定。

LED 1~4 野火摄像头排线接口复位按钮NRF24L01+无线模块接口Micro USB 接口V5V 转3.3V50MHz晶振 预留给USB 转TTL 接口KEY 1 & 2 电源指示灯KEY 1 & 2 JLink 接口LED 1~43.3V 管脚 3.3V和5V 管脚供电后,此电源灯会亮图 3 核心板排针供电指示注意:不要把5V电源插入 3.3V 的排针座内!!!USB供电用micro USB 数据线(现在绝大部分的智能机都是用这类的数据线),一头接入核心板,另外一头接入电脑的USB口或者5V供电的带USB口充电器的口上。

比mini USB更加扁平的图 4 micro USB数据线图 5野火K60核心板USB 供电方式Jlink 供电野火K60 核心板使用标准的10PIN 插头,Jlink 默认不支持供电,但Jlink 虽然支持使用power on 和 power off 命令来实现供电,但仅仅适用于5V 供电,而且不适用于 10PIN 管脚。

第2章Kinetis微控制器概述与K60硬件最小系统

第2章Kinetis微控制器概述与K60硬件最⼩系统第2章Kinetis微控制器概述与K60硬件最⼩系统本章导读:本章给出Kinetis微控制器概述与K60硬件最⼩系统。

主要知识点有①学习⼀个新MCU芯⽚的基本要素;②Kinetis微控制器与ARM Cortex-M4概述;③K60⼦系列微控制器的存储器映像、编程結构、寻址⽅式与异常向量表;④K60N512VMD100芯⽚的引脚功能与硬件最⼩系统电路。

本章的重点是存储空间的地址分配、中断结构.硬件最⼩系统电路。

2.1学习⼀个新MCU芯⽚的基本要素⼀般來说,学习⼀个新的MCU芯⽚,芯⽤C语⾔进⾏编程,快速⼊门的学习过程如下。

(1)了解性能及内部主要功能模块与存储空间的地址分配。

(2)了解基本的编程结构、编程模式及导址⽅式。

(3)了解中断结构。

(4)了解芯⽚的引脚总体布局情况.掌握硬件最⼩系统电路。

(5)理解第⼀个⼯程的结构,理解⼯程中各个⽂件的基本功能。

—般来说,第⼀个⼯程为⼀个简单的⼩程序,如借助通⽤I/0模块编程控制⼏个发光⼆极管,主要⽬的是给出程序框架和⼯作过程?(6)进⾏实际环境的编译(Compile),链接(Link)以⽣成可以下载到芯⽚内部Flash存储器中的程序(可以运⾏的机器码),基本理解列表⽂件和机器码⽂件。

(7)有硬件评估坏境是学习新型MCU的必需品。

利⽤写⼊调试器将程序下载到⽬标MCU 中:在⽬标板上,观察运⾏情况,随后,可进⼀步利⽤嵌⼊式软件的“打桩调试技术”,即在被测程序代码中插⼊⼀些函数或语句,利⽤这些函数或语句在硬件系统中产⽣可观察的物理现象,以便了解程序的运⾏情况。

(8)从整个⼯程组织、各⽂件功能等⾓度,透彻理解第⼀个⼯程的执⾏过程。

(9)理解第⼀个带有中断过程的C语⾔⼯程结构,理解主循环与中断两条程序执⾏路线各⾃的作⽤。

(10)根据⾃⼰的相关知识基础与项⽬的实际需求,决定是否采⽤嵌⼊式(实时)操作系统。

⾄此,以上学习过程已经覆盖了学习⼀个新型MCU硬件设计与软件编程的基本要素。