Cadence学习笔记(十三)

candence学习笔记

candence学习笔记主要学习以下内容:(1)利用OrCAD Capture CIS 进行原理图设计(2)利用Cadence PCB Editor 进行PCB布局布线(3)光绘文件(Artwork)制作,如何生成Gerber文件。

1. 工具介绍PCB Edtor 绘制PCB的工具PCB Librarian 制作PCB原件库的工具PCB Router自动布线的工具PCB SI 和SigXplorar 电路板信号完整性仿真的工具2 . OrCAD Capture CIS启动改工具后,会打开如下界面,通常选择OrCAD Capture CISOrCAD Capture CIS 与OrCAD Capture相比的优势是,在画原理图时对原理图中所有元件的管理会很方便。

3.DSN文件,是建立工程的数据库文件,包含了工程的所有数据。

Design Cache,每在原理图中放置一个元件,就会在该文件下将该元件保存下来,当下次再放置同一个文件时,就可以很方便的从这里来选取相关元件。

Library,包含元理图用到的库4. OrCAD Capture 的菜单是上下文相关的,对不同的窗口操作,菜单是不同的。

5. 原理图文件的创建(1) 选原理图文件夹,Design---->New Schematic Page----->.........(2) 选原理图文件夹,右键单击------>New Page--------->...........6. 原理图文件的删除(1) 选中要删除的原理图文件,Design---->Delete----->.........(2) 选中要删除的原理图文件,按Delete键7. 原理图文件的重命名(1) 选中要得命名的原理图文件,Design---->Rename----->.........(2) 选中要得命名的原理图文件,右键单击------>Rename--------->...........8. 原理图文件的放大和缩小(1) i:放大o:缩小都是以鼠标所在位置为中心(2) 通过菜单操作(3) Ctrl + 鼠标滚轮选中某元件后,就会以该元件为中心来进行放大或者缩小1. 打开Orcad capture CIS 后,在创建原理图前,需要做一些设置:(1)Options------>Design T emplate2.修改原理图的背景色:Options---->Preferences------>Background3.对单个原理图页面设置Options-------Schematic Page Properties4.元件库的建立在OrCAD Capture CIS中,选择File------New-----Library 。

Cadence_Skill_语法详解(中文)要点

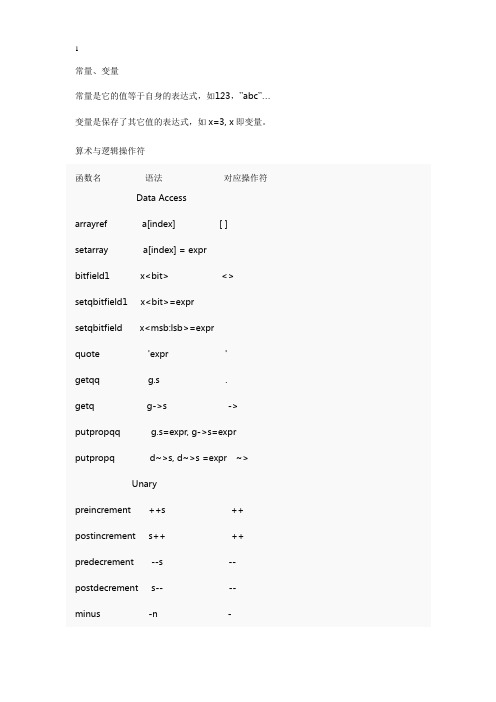

常量、变量常量是它的值等于自身的表达式,如123,”abc”…变量是保存了其它值的表达式,如x=3, x即变量。

算术与逻辑操作符函数名语法对应操作符Data Accessarrayref a[index] [ ] setarray a[index] = exprbitfield1 x<bit> <> setqbitfield1 x<bit>=exprsetqbitfield x<msb:lsb>=exprquote 'expr 'getqq g.s .getq g->s -> putpropqq g.s=expr, g->s=expr putpropq d~>s, d~>s =expr ~>Unarypreincrement ++s ++ postincrement s++ ++ predecrement --s -- postdecrement s-- -- minus -n -not !expr !bnot ~x ~Binaryexpt n1 ** n2 ** times n1 * n2 * quotient n1 / n2 / plus n1 + n2 + difference n1 - n2 - leftshift x1 << x2 << rightshift x1 >> x2 >> lessp n1<n2 < greaterp n1>n2 > leqp n1<=n2 <= geqp n1>=n2 >= equal g1 == g2 == nequal g1 != g2 != band x1 & x2 & bnand x1 ~& x2 ~& bxor x1 ^ x2 ^ bxnor x1 ~^ x2 ~^ bor x1 | x2 | bnor x1 ~| x2 ~|and x1 && x2 &&or x1 || x2 ||range g1 : g2 :setq s = expr =对于既有函数名又有操作符函数,采用函数名调用和采用操作符调用的效果是一样的。

Cadence学习笔记

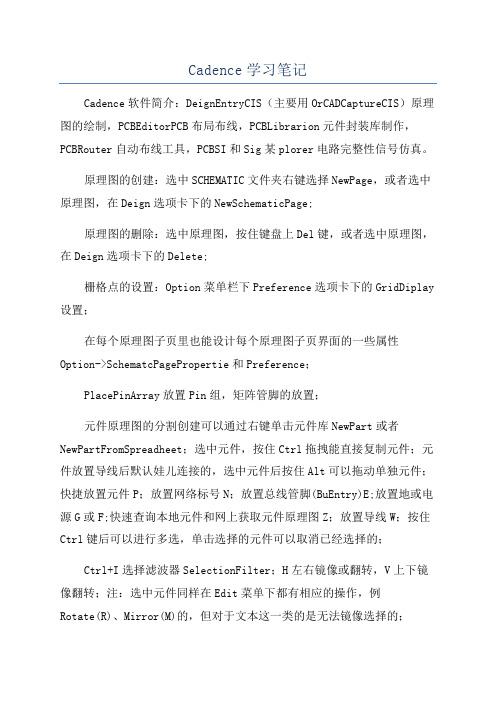

Cadence学习笔记Cadence软件简介:DeignEntryCIS(主要用OrCADCaptureCIS)原理图的绘制,PCBEditorPCB布局布线,PCBLibrarion元件封装库制作,PCBRouter自动布线工具,PCBSI和Sig某plorer电路完整性信号仿真。

原理图的创建:选中SCHEMATIC文件夹右键选择NewPage,或者选中原理图,在Deign选项卡下的NewSchematicPage;原理图的删除:选中原理图,按住键盘上Del键,或者选中原理图,在Deign选项卡下的Delete;栅格点的设置:Option菜单栏下Preference选项卡下的GridDiplay 设置;在每个原理图子页里也能设计每个原理图子页界面的一些属性Option->SchematcPagePropertie和Preference;PlacePinArray放置Pin组,矩阵管脚的放置;元件原理图的分割创建可以通过右键单击元件库NewPart或者NewPartFromSpreadheet;选中元件,按住Ctrl拖拽能直接复制元件;元件放置导线后默认娃儿连接的,选中元件后按住Alt可以拖动单独元件;快捷放置元件P;放置网络标号N;放置总线管脚(BuEntry)E;放置地或电源G或F;快速查询本地元件和网上获取元件原理图Z;放置导线W;按住Ctrl键后可以进行多选,单击选择的元件可以取消已经选择的;Ctrl+I选择滤波器SelectionFilter;H左右镜像或翻转,V上下镜像翻转;注:选中元件同样在Edit菜单下都有相应的操作,例Rotate(R)、Mirror(M)的,但对于文本这一类的是无法镜像选择的;放置文本框输入文字时Ctrl+E换行;总线放置BaeName不能以数字结尾;其中F4可以连续放置BuEntry,总线与导线连接必须要BuEntry,总线与总线可以梯形连接或者Junction;画任意角度的连线在放置连线前按住hift;Junction接头或交叉点;如果想在交叉点上去除一个Junction,只需要重复添加一个就行,电气上也就失去了连接;或者先按住键盘上的S 键,选中Junction然后Del;放置总线时,总线的名字和信号线的标号(BaeName)必须一致,开始和结尾的数字必须与总线的定义一致,并且只能通过Netlab连接;不同页面的电气连接要用off-PageConnecter;按住Alt拖动元件可以实现单个拖动,Cadence中默认的是一起;Cadence在处理电气链接关系时利用的就是Netlab网络标志;对原理图元件属性的编辑,在选中所需修改的元件后右键选择EditPropertie可以统一修改属性,快捷键Ctrl+E;选中Piovt可以更改元件属性表格排列方式;元件封装信息的添加:对于单个元件,在原理图中可以在右键编辑元件属性时在PCBFootprint属性栏添加,也可以在元件库中把元件的PCBFootprint添加上,然后通过ReplaceCache添加;对于批量元件,选中一组所需要修改的元件,单击右键选择EditPropertie出现批量修改属性表格,选中PCBFootprint属性栏,全选,右键单击Edit出现EditPropertyValue对话框,就可以进行对选中元件统一修改,也可以选中某个原理图页面右键选择EditObjectPropertie进行元件封装的修改;在选择Browe选项之后可以选择浏览表格的所有元件信息然后使用EditPropertie来更改元件属性,选中第一个,然后按住hift选中最后一个可以全选;使用Find查找,选中所需更改元件也可以更改元件属性,快捷键ctrl+hift+E;在元件属性中可用于元件属性的修改;DeignCache文件夹选项,左键单击DeignCache的元件名,其中ReplaceCache全局替换元件(可以改变元件库的一种连接关系),会弹出一个替换元件对话框,可以更具自己的需要更改,有Preervechematicpartpropertie(但是选择这种方式无法替换封装)和Replacechematicpartpropertie分别是保留与更新原理图也面下该元件的属性;UpdateCache全局更新元件;右键单击DeignCache文件夹,选择CleanupCache全局清除已经不存在的元件历史文件;这对于全局浏览所用的元件非常有效。

cadence学习笔记

begin layer 正常焊盘regulapadpastemasktop 一样大小加焊层soldermask 阻焊层大0.1Mm通孔焊盘0.7Mm 通孔1mm就好1.先做花焊盘内径外经开口钻孔1mm的话内径比钻孔大6-8mil 1.5mm2.begin layer end 一样3.内层DEFAULT INTERNAL THERMAL 要用Flash焊盘4.sold-- 和pastmask 大点pastmask 和表层一样画好焊盘后,1.place-boud-top add-rectagule courtyad2.silkscreen add-line 和封装一样大3.画角标4. assembly top 直接画5 索引编号标示layout label refdel assembly top 中间qapl963silkscreenshape 矩形etch画圆第一次圆心第二次X半径Y不变错误相容shape merge shapeschret smbortsetup 最后一个设置路径通孔的封装焊盘制作。

通孔比焊盘大10-12mil1.flash 焊盘add-flsh 内圆1.5 外圆1.8 开口0.72做焊盘holetype 圆形plating 孔壁上锡plateddrill diameter 直径drill/slot光会文件时候,形状character 字母with 大小3 geometry-suare 方形圆孔的(第一个脚用的)thermalrelief 一样anti pad 大0.1mm做好后表层拷贝到END layer 表层制作完成4 default internal 花焊盘5pastemask top bottm 和表层一致。

SOLDERMASK 两层和表层大0.1mm之后做外面圆的。

1.添加线创建边框,2.倒角,,manufacture-draft-fillet3.准许布线区域,比边框小点,setup-areas-routekeepin 注意选择shapefill-unfilled不填充4.package-keepin edit-z-kopy 小点5.加固定孔6.setup-cross-section板子层7.铺通,内点层。

cadence学习笔记

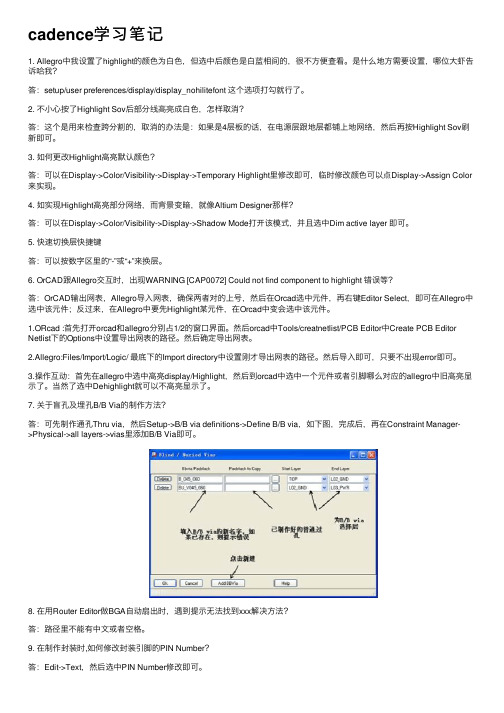

cadence学习笔记1. Allegro中我设置了highlight的颜⾊为⽩⾊,但选中后颜⾊是⽩蓝相间的,很不⽅便查看。

是什么地⽅需要设置,哪位⼤虾告诉哈我?答:setup/user preferences/display/display_nohilitefont 这个选项打勾就⾏了。

2. 不⼩⼼按了Highlight Sov后部分线⾼亮成⽩⾊,怎样取消?答:这个是⽤来检查跨分割的,取消的办法是:如果是4层板的话,在电源层跟地层都铺上地⽹络,然后再按Highlight Sov刷新即可。

3. 如何更改Highlight⾼亮默认颜⾊?答:可以在Display->Color/Visibility->Display->Temporary Highlight⾥修改即可,临时修改颜⾊可以点Display->Assign Color 来实现。

4. 如实现Highlight⾼亮部分⽹络,⽽背景变暗,就像Altium Designer那样?答:可以在Display->Color/Visibility->Display->Shadow Mode打开该模式,并且选中Dim active layer 即可。

5. 快速切换层快捷键答:可以按数字区⾥的“-”或“+”来换层。

6. OrCAD跟Allegro交互时,出现WARNING [CAP0072] Could not find component to highlight 错误等?答:OrCAD输出⽹表,Allegro导⼊⽹表,确保两者对的上号,然后在Orcad选中元件,再右键Editor Select,即可在Allegro中选中该元件;反过来,在Allegro中要先Highlight某元件,在Orcad中变会选中该元件。

1.ORcad :⾸先打开orcad和allegro分别占1/2的窗⼝界⾯。

然后orcad中Tools/creatnetlist/PCB Editor中Create PCB Editor Netlist下的Options中设置导出⽹表的路径。

Cadence视频笔记

Cadence SPB15.7 快速入门视频教程目录Capture CIS 原理图及元件库部分第1-15讲第1讲课程介绍,学习方法,了解CADENCE软件Cadence下几个程序说明Design Entry CIS 系统级原理图设计Design Entry HDL 芯片设计Layout plus orcad 自带的pcb板布局布线工具,功能不是很强大,不推荐使用Pcb Editor Pcb librarian Cadence带的PCB布局布线封装设计PCB Router pcb自动布线Pcb SI SigXplorer Pcb电路板信号完整性仿真OrCAD Capture CIS 对元件管理更方便相对于OrCAD CaptureI 放大O 缩小页面属性设置options Design Templateoptions Schematic Page Propertie s第2讲创建工程,创建元件库原理图元件库,某元件分成几个部分,各部分间浏览ctrl+N ctrl+B元件创建完后修改footprint封装,options Package Properties第3讲分裂元件的制作方法1、homogeneous 和heterogeneous 区别homogeneous,芯片包含几个完全相同的部分选择该模式,画好第一个part后,后面的part会自动生成,因为完全一样。

但是引脚编号留空了,要自己再设置引脚编号。

heterogeneous芯片包含几个功能部分,可按照功能部分分成几个部分。

ctrl+N ctrl+B切换分裂元件的各个部分原理图画完之后,要对各元件自动编号,在项目管理窗口选择项目,点击tools annotate,在Action下面选择相应的动作。

2、创建homogeneous类型元件3、创建heterogeneous类型元件第4讲正确使用heterogeneous类型的元件1、可能出现的错误Cannot perform annotation of heterogeneous part J?A(Value RCA_Octal_stack ) part has not been uniquely group(using a common User Property with differing Values) or the device designation has not been chosen2、出现错误的原因分裂元件分成几个part,并且用了多片这样的分裂元件。

Cadence使用工程笔记

Cadence应用工程软件使用工程笔记1、Allegro PCB Editor用于创建修改设计文件,是最主要的设计工具。

可以单独启动,也可以在工程管理器中启用。

有两种模式:layout mode 和symbol creation mode。

当我们进行手工布局布线时,就工作在layout mode这种模式下。

Symbol creation mode中可以创建及修改Package symbol、mechanical symbol、format symbol、shape symbol、flash symbol。

2、Padstack Designer创建及修改焊盘padstacks,Allegro在创建零件封装时,焊盘需要单独设计,必须使用这个工具先创建焊盘。

3、DSDoctober用于检查设计数据中的错误,在设计的每一个阶段执行,可以部分修复数据错误。

在生成光绘文件前必须进行DBDoctor 检查。

4、Allegro Constraint ManagerAllegro约束管理器,布局布线约束规则的创建、管理、评估、检查等,如各种物理间距,线长,线宽等。

可以与Allegro PCB Editor和Allegro PCB SI等完美集成,非常方便进行交互设计。

5、Allegro PCB Router自动布线工具,对于有复杂设计规则的高密度电路板处理能力很强,可以在Allegro PCB Editor中用自动布线命令调出来。

这个布线工具名气很大,对于简单的电路板,布线很美观。

相比较而言,布通率很高。

6、Allegro PCB SI电路板信号完整性仿真工具,反射、串扰等噪音分析。

布线前后都可以使用,布线前主要进行约束规则的开发。

7、Allegro PCB PI电源完整性仿真工具,不能仿真电源平面分割情况,可以用其他工具替代。

8、Allegro PCB Planner是专门为布局用的,有部分SI的功能,有部分布线功能,是两个的交集。

Cadence学习笔记(十三)

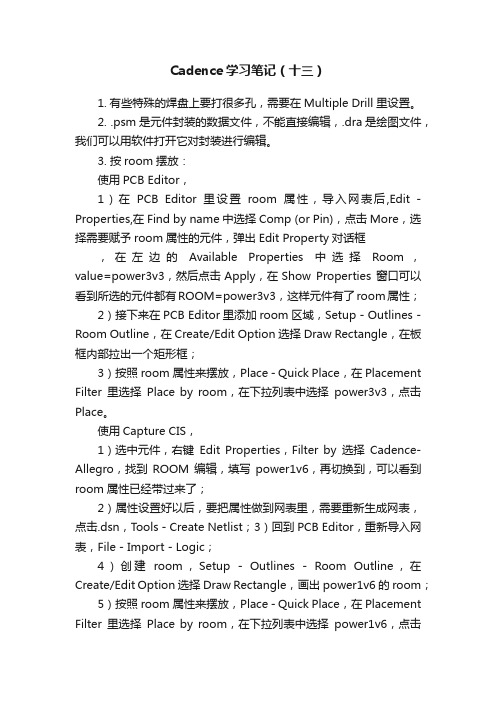

Cadence学习笔记(十三)1. 有些特殊的焊盘上要打很多孔,需要在Multiple Drill里设置。

2. .psm是元件封装的数据文件,不能直接编辑,.dra是绘图文件,我们可以用软件打开它对封装进行编辑。

3. 按room摆放:使用PCB Editor,1)在PCB Editor里设置room属性,导入网表后,Edit - Properties,在Find by name中选择Comp (or Pin),点击More,选择需要赋予room属性的元件,弹出Edit Property对话框,在左边的Available Properties中选择Room,value=power3v3,然后点击Apply,在Show Properties 窗口可以看到所选的元件都有ROOM=power3v3,这样元件有了room属性;2)接下来在PCB Editor里添加room区域,Setup - Outlines - Room Outline,在Create/Edit Option 选择Draw Rectangle,在板框内部拉出一个矩形框;3)按照room属性来摆放,Place - Quick Place,在Placement Filter里选择Place by room,在下拉列表中选择power3v3,点击Place。

使用Capture CIS,1)选中元件,右键Edit Properties,Filter by选择Cadence-Allegro,找到ROOM编辑,填写power1v6,再切换到,可以看到room属性已经带过来了;2)属性设置好以后,要把属性做到网表里,需要重新生成网表,点击.dsn,T ools - Create Netlist;3)回到PCB Editor,重新导入网表,File - Import - Logic;4)创建room,Setup - Outlines - Room Outline,在Create/Edit Option选择Draw Rectangle,画出power1v6的room;5)按照room属性来摆放,Place - Quick Place,在Placement Filter里选择Place by room,在下拉列表中选择power1v6,点击Place。

Cadence学习笔记

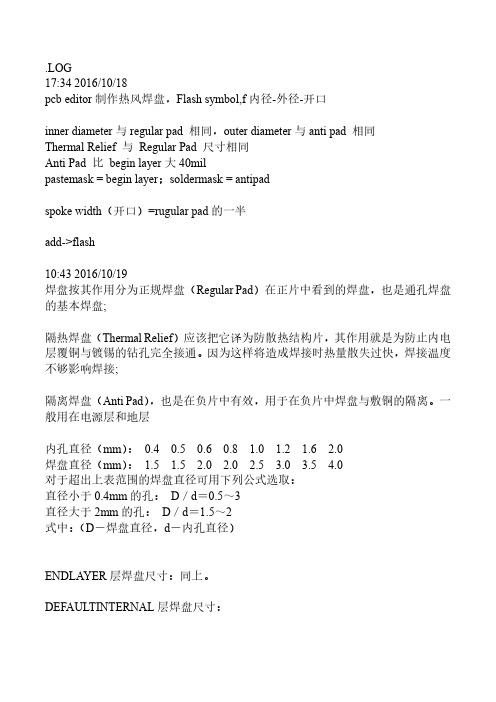

.LOG17:34 2016/10/18pcb editor制作热风焊盘,Flash symbol,f内径-外径-开口inner diameter与regular pad 相同,outer diameter与anti pad 相同Thermal Relief 与Regular Pad 尺寸相同Anti Pad 比begin layer大40milpastemask = begin layer;soldermask = antipadspoke width(开口)=rugular pad的一半add->flash10:43 2016/10/19焊盘按其作用分为正规焊盘(Regular Pad)在正片中看到的焊盘,也是通孔焊盘的基本焊盘;隔热焊盘(Thermal Relief)应该把它译为防散热结构片,其作用就是为防止内电层覆铜与镀锡的钻孔完全接通。

因为这样将造成焊接时热量散失过快,焊接温度不够影响焊接;隔离焊盘(Anti Pad),也是在负片中有效,用于在负片中焊盘与敷铜的隔离。

一般用在电源层和地层内孔直径(mm):0.4 0.5 0.6 0.8 1.0 1.2 1.6 2.0焊盘直径(mm): 1.5 1.5 2.0 2.0 2.5 3.0 3.5 4.0对于超出上表范围的焊盘直径可用下列公式选取:直径小于0.4mm的孔:D/d=0.5~3直径大于2mm的孔:D/d=1.5~2式中:(D-焊盘直径,d-内孔直径)ENDLAYER层焊盘尺寸:同上。

DEFAULTINTERNAL层焊盘尺寸:DRILL_SIZE (钻孔尺寸)>= 实际管脚尺寸+ 10MIL(0.25mm)RegularPad >= DRILL_SIZE + 16MIL(0.4mm)(DRILL_SIZE<50MIL(1.27mm)) Regular Pad >= DRILL_SIZE + 30MIL(0.76mm)(DRILL_SIZE>=50MIL(1.27mm)) Regular Pad >= DRILL_SIZE + 40MIL(1mm)(钻孔为矩形或椭圆形时) Thermal Pad = TRaXbXc-d (其中TRaXbXc-d 为Flash 的名称(后面有介绍))Anti Pad = DRILL_SIZE + 30MIL(0.76mm)Flash Name: TRaXbXc-d其中:a. Inner Diameter(内径): Drill Size + 16MIL(0.4mm)b. Outer Diameter(外径): Drill Size + 30MIL(0.76mm)c. Spoke width:12 ( 当DRILL_SIZE = 10MIL 以下)15 (当DRILL_SIZE = 11~40MIL)20 (当DRILL_SIZE = 41~70MIL)30 (当DRILL_SIZE = 71~170 MIL)40 (当DRILL_SIZE = 171 MIL 以上)保证连接处的宽度不小于10mil 。

cadence 原理图学习笔记

Design Entry CIS :板基设计的原理图设计Design Entry HDL Rules Checker 芯片设计工具Design Entry HDL 芯片设计工具PCB Editor:PCB布局布线的软件PCB Router:自动布线的工具PCB SI:线路板的完整性分析SigXplorer:线路板的完整性分析平时画原理图工具:OrCAD Capture CIS原理图模板设置:创建原理图元件库新建的原理库存储到指定的位置新建元件库元件新建元件的属性,包括名称,索引号,封装,多元件共体,等信息元件库原理图编辑界面单个引脚放置:弹出引脚属性设置阵列引脚放置:单个引脚双击修改属性多个引脚选中后在spreadsheet一起修改。

放置填充多边形按住shift可以画任意角多边形双击调出多边形属性选择实体就好了放置元件方体画方框结束鼠标重复放置命令,右击End Mode 或者Esc元件属性,设置引脚管脚显示等。

元件封装属性修改,原理图与pcb封装的映射就在这里修改。

多元件共体浏览分裂元件浏览。

不规则元件第3讲:分裂元件制作创建Homogereous双运放元件,每个单元件都一摸一样,引脚编号不同,电源脚编号可以重复。

新建元件画好第一个单元件快捷键Ctrl+n 自动生成另一部分单元件。

需要全部重新定义引脚编号。

引脚名称隐藏快捷键Ctrl+b 可以返回查看A部分元件图形。

创建Heterogeneous元件,每部分图形可以不一致。

快捷键Ctrl+n 会完全留空,全部要重新画。

分裂元件整体浏览第4讲分裂元件的自动编号的问题解决。

分裂元件的组定义,在元件库中操作,使同组元件具备同一属性。

第一步:创建元件第二步:给元件创建一个可以区分“分组”的属性完成了单个元件的新属性的创建依次创建同组的其它元件的新属性。

要求同名同参数第三步:在原理图中双击元件使同组的元件都新属性参数相同即可。

配对时不能冲突,比如双运放就只能有两个运放,同一参数有三个运放相同的话就出错了。

Cadence学习笔记

教程实例:DSP最小系统教程内容:1、利用Capture CIS进行原理图设计2、利用Cadence PCB Editor布局布线3、光绘文件(Artwork)制作,生成Gerber文件1mil=0.0254mm一原理图放大I 缩小O图纸右下角标注:Design Template1、创建新工程文件库文件2、参考datasheet在库文件中添加新元件:Place pin(画管脚编辑属性,power型visible)、Place pin array(管脚阵列)全部元件在Spreadsheet表中编辑(全选右键单击edit properties)可以在新建元件时选New Part Creation Spreadsheet通过表格创建多引脚元件常用选项:Option-part properties / package properties画不规则元件:Preference中取消Pointer snap to Grid,随意划线,画完再改回去3、分裂原件:homogeneous(完全相同)、heterogeneous(多个功能模块不同)以NE5532为例Tools-Annotate:给元件编号原理图中多个heterogeneous分裂原件的分组问题:库文件中选中分裂原件,在part properties中新建new property(name如package不可为group,value为组号123等),分裂原件的多个部分都要执行上一操作;打开原理图,双击分裂原件在property editor中将package属性设置为相同则为同一组分裂原件;要给之编号还需在annotate菜单physical packaging栏中将最后一项改为上文中name名大型元件的分割:参考《cadence电路设计案例精析》P184、在工程中添加元件库(自建库、系统库)电容电阻电感变压在discrete库中不知道元件在哪个库可以搜索放置元件place part5、元件的连接:直接连、用网络别名连接(在同一原理图页面中place net alias,名称相同表示电气上连接在一起)引脚悬空(末端连Place no connect)最好不要在放置元件时就把元件连在一起6、总线:功能类似的信号总线连接:Place-Bus 默认直角拐弯按住shift拉任意转方向画总线命名net alias(规则:XX[起始:结束])拖到总线上连接管脚与总线:place bus entry、按F4连续放置总线入口、信号线(与总线名一致)总线之间的连接:T型交叉有电气连接十字无实际电气连接不同页面之间的连接:place off-page connect 实际上与同一页面连接时net alias相似7、浏览BROWSE-元件parts(容易发现元件编号和大小错误)、网络Nets(双击看某一网络与哪些部分连接)、页面之间进行互联的网络:Browse-off page connectors、电气检查中的错误查看DRC 搜索Find元件parts、网络nets、Netlist修改元件库后更新元件:replace/update cache工程已经不在的元件在cache中删掉cleanup cache8、给元件添加封装信息:双击元件打开Property Editor,在PCB Footprint中标注封装批量修改封装:多选……在元件库中添加封装信息:打开库,选择元件-option-Package Property,回到项目中选中更改封装的元件-replace cache-选择replace schematic part property生成网表:先元件重编号Annotate、再DRC(design rules check)检查、选中dsn文件-Tools-create netlist-PCB Editor生成元件清单BOM,两种:1)Reports-CIS Bill of Materials-standard2)Tools- Bill of Materials9、二PCB高速电路设计流程原则:设计即正确1、工具介绍Allegro PCB Editor用于创建修改设计文件,是主要的设计工具,有两种模式:layout mode和symbol creation mode,进行手工布局布线时,工作在layout mode下,symbol creation mode中可以创建和修改package symbol、mechanical symbol、formal symbol、shape symbol、flash symbol Pad Designer创建及修改焊盘PadstackDBdoctor用于检查设计数据中的错误,Allegro Constraint ManagerAllegro约束管理器,布局布线约束规则的创建、管理、评估、检查Allegro PCB Router自动布线工具,对于有复杂涉及规则的高密度电路板处理能力很强Allegro PCB SI/PI信号/电源完整性仿真工具2、PCB设计流程(理论):1)规划出所设计电子设备的各项系统的规格,包括系统功能、系统的大小、运作情况以及成本2)做出系统的功能方块图,同时将每个方块之间的关系表示出来3)根据系统的功能方块图将系统分割成数个PCB,可以缩小系统的尺寸,同时可以使系统具有升级与交换零件的能力4)决定各PCB使用的技术以及电路数量,决定板子的大小。

cadence PCB板学习笔记

第16讲第17讲功能介绍第18讲切换界面工具栏定制命令参数控制窗口的停靠位置设置命令参数控制窗口动态显示当前命令的设置未激活命令时,命令参数控制窗口options控制图层显示关闭未激活命令时,visibility控制线路板按类显示。

激活move命令,命令控制窗口find控制可操作的对象第19讲 class subclass 类子类,PCB板信息分类,(EAGLE以层分类,机械层,丝印层,线路层,元件坐标层,阻焊层,焊锡层。

)查看线路板的类元素。

第20讲零件封装IPC7351标准软件PCB Matrix IPC LP Viewer焊盘制作工具焊盘尺寸设置焊盘建好后 FILE-CHECK 两次后提示没问题后进行 file save as 进行文件存档焊盘建好后,下一步可以创建元件封装了:在allegro PCB Design XL中file new创建一个封装文件封装符号第一步,因为元件比较小,先把图纸尺寸改小。

要先把单位改正并且应用后才能改其它尺寸(尺寸改不动,尺寸改正不过来)栅格大小修改Layout pins 放置引脚通过命令参数窗口选取焊盘设置焊盘个数和距离命令方式定位x0 y0坐标命令方式画线, iy ix,,i表示增量。

画元件几何尺寸标示线框。

画元件外框丝印线标示框放置禁止布局框防止其它元件重叠,放置元件索引别号在assembly top也加上元件索引编号。

用于出位号图在丝印层上也加上元件索引编号,用于线路板显示元件编号。

在丝印层上放置元件参数。

至此元件可以存盘了。

.psm为元件封装文件。

.dra为图形编辑文件(画元件封装和花焊盘都是存为这个格式)。

.ssm为自定义图形保存格式。

.pad 为paddesigner生成的焊盘元件。

.fsm为花焊盘文件。

第21讲建立一个BGA封装。

第22讲建立特殊焊盘元件。

第一步:建立特殊焊盘建立非规则焊盘在allegro平台下建立shape symbol特殊形状的符号并存档,然后用pad designer利用这个符号建立焊盘第二步:同上设定图纸和栅格尺寸第三步top层上画多个图形。

Cadence学习笔记

Cadence学习笔记1__焊盘一、焊盘前期准备在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。

元件封装大体上分两种,表贴和直插。

针对不同的封装,需要制作不同的Padstack。

名词解释不同层的名词解释:Begin Layer:最上面的铜Default Internal:中间层End Layer:最下面的铜Solder Mask:阻焊层、绿油层。

是反显,有就是没有。

等于是开了个小孔不涂绿油,是为了把焊盘或是过孔露出来,不涂绿油就是亮晶晶的铜,也就是在板子上看到的焊盘,或者是一个个的孔,其它的部分都上阻焊剂,也就是绿油,其实不光是绿色的,还有红色的、黑色的、蓝色的等等。

Paste Mask:助焊层、钢网层、锡膏防护层、锡膏层,也叫胶贴、钢网、钢板。

是正显,有就是有。

等于是钢网开了个窗,过波峰焊时机器就在此窗口内喷上焊锡了。

这一层是针对表面贴装(SMD)元件的,其实不光是表贴,通孔也要用到,因为通孔的表面上也有个焊盘,该层用来制作钢板﹐而钢板上的孔就对应着电路板上的SMD器件的焊点。

在表面贴装(SMD)器件焊接时﹐先将钢板盖在电路板上(与实际焊盘对应)﹐然后将锡膏涂上﹐用刮片将多余的锡膏刮去﹐移除钢板﹐这样SMD器件的焊盘就加上了锡膏,之后将SMD器件贴附到锡膏上面去(手工或贴片机)﹐最后通过回流焊机完成SMD器件的焊接。

通常钢板上孔径的大小会比电路板上实际的焊盘小一些。

Film Mask:预留层,用于添加用户自定义信息,根据需要使用。

不同焊盘的名词解释:Regular Pad:实际焊盘、规则焊盘,正片中使用,也是通孔焊盘的基本焊盘。

可以是:Null、Circle 圆型、Square 方型、Oblong 拉长圆型、Rectangle 矩型、Octagon 八边型、Shape形状(可以是任意形状)。

Thermal Relief:热焊盘、热风焊盘、花焊盘、防散热焊盘。

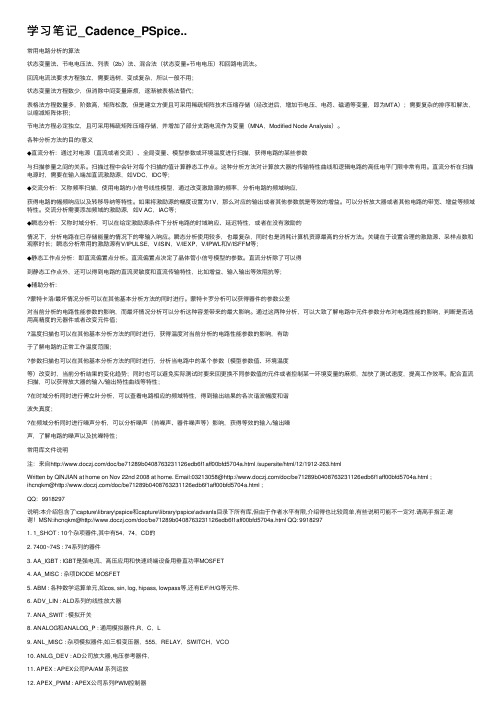

学习笔记_Cadence_PSpice..

学习笔记_Cadence_PSpice..常⽤电路分析的算法状态变量法、节电电压法、列表(2b)法、混合法(状态变量+节电电压)和回路电流法。

回流电流法要求⽅程独⽴,需要选树,变成复杂,所以⼀般不⽤;状态变量法⽅程数少,但消除中间变量⿇烦,逐渐被表格法替代;表格法⽅程数量多,阶数⾼,矩阵松散,但是建⽴⽅便且可采⽤稀疏矩阵技术压缩存储(经改进后,增加节电压、电荷、磁通等变量,即为MTA);需要复杂的排序和解法,以缩减矩阵体积;节电法⽅程必定独⽴,且可采⽤稀疏矩阵压缩存储,并增加了部分⽀路电流作为变量(MNA,Modified Node Analysis)。

各种分析⽅法的⽬的/意义◆直流分析:通过对电源(直流或者交流)、全局变量、模型参数或环境温度进⾏扫描,获得电路的某些参数与扫描参量之间的关系。

扫描过程中会针对每个扫描的值计算静态⼯作点。

这种分析⽅法对计算放⼤器的传输特性曲线和逻辑电路的⾼低电平门限⾮常有⽤。

直流分析在扫描电源时,需要在输⼊端加直流激励源,如VDC,IDC等;◆交流分析:⼜称频率扫描,使⽤电路的⼩信号线性模型,通过改变激励源的频率,分析电路的频域响应,获得电路的幅频响应以及转移导纳等特性。

如果将激励源的幅度设置为1V,那么对应的输出或者其他参数就是等效的增益。

可以分析放⼤器或者其他电路的带宽、增益等频域特性。

交流分析需要添加频域的激励源,如V AC,IAC等;◆瞬态分析:⼜称时域分析,可以在给定激励源条件下分析电路的时域响应、延迟特性,或者在没有激励的情况下,分析电路在已存储能量的情况下的零输⼊响应。

瞬态分析使⽤较多,也最复杂,同时也是消耗计算机资源最⾼的分析⽅法。

关键在于设置合理的激励源、采样点数和观察时长;瞬态分析常⽤的激励源有V/IPULSE,V/ISIN,V/IEXP,V/IPWL和V/ISFFM等;◆静态⼯作点分析:即直流偏置点分析。

直流偏置点决定了晶体管⼩信号模型的参数。

Cadence学习总结

Cadence学习总结Allegro 软件是 Cadence 公司出品的面向中高端企业用户的 PCB 设计软件,主要针对高速、高密度电路板设计,尤其在通讯等领域被广泛应用,目前最新版本号是 16.0。

Allegro 软件导出坐标数据步骤.①Design Entry CIS绘制原理图。

②*HDL:芯片开发时的扳机设计③PCB Editor:PCB板布局布线的工具④PCB Router:自动布线的工具。

⑤PCB SI:电路板完整性仿真。

⑥⑦设置模版Options--Design Template⑧原理图背景设置,设置跳转:options-preferences⑨修改原理图属性:options-Schematic page properties⑩封装的一些设置在:options-user properties11多个部分的元器件显示在一页:view-package12---第一个多个模块功能相同13第二个功能不同14多个部分之间切换:ctrl+n;15同时看多个部分:View--package.16放置期间:place--part17取消所有标注;18自动生成编号:19多个部分冲突,给封装添加一个属性,根据不同修改属性。

20放置的时候,按R按键,可以旋转放置的封装。

21画线快捷键:按W22画线到了终点(终端悬空),双击,如果单击还会继续画。

23画之前,按住shift按键,可以绘制任意角度的线条。

24删除节点,按住S,才能选中焦点。

25放置网络名字,按n26总线的命名:名字一定是英文。

27总线和信号线的要求:2829连接到其他页。

30浏览工程中用到的软件,选中工程中的dns---菜单edit---browse---parts(可以查看有没有忘记编号那些)31电气规则检查:32查看所有网络:dns---edit---browse---nets(双击表格中的网络,可以查看此网络) 33查看页面之间互联的网络:dns---EDIT---browse---off_page(原理图检查非常重要,或者用pans检查也行)。

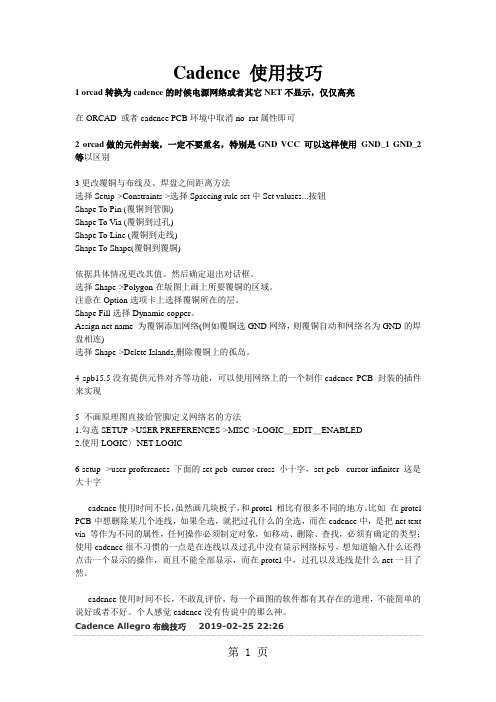

Cadence技巧精品文档13页

Cadence 使用技巧1 orcad转换为cadence的时候电源网络或者其它NET不显示,仅仅高亮在ORCAD 或者cadence PCB环境中取消no_rat属性即可2 orcad做的元件封装,一定不要重名,特别是GND VCC 可以这样使用GND_1 GND_2等以区别3更改覆铜与布线及、焊盘之间距离方法选择Setup->Constraints->选择Spaceing rule set中Set valuses...按钮Shape To Pin (覆铜到管脚)Shape To Via (覆铜到过孔)Shape To Line (覆铜到走线)Shape To Shape(覆铜到覆铜)依据具体情况更改其值。

然后确定退出对话框。

选择Shape->Polygon在版图上画上所要覆铜的区域。

注意在Option选项卡上选择覆铜所在的层。

Shape Fill选择Dynamic copper。

Assign net name 为覆铜添加网络(例如覆铜选GND网络,则覆铜自动和网络名为GND的焊盘相连)选择Shape->Delete Islands,删除覆铜上的孤岛。

4 spb15.5没有提供元件对齐等功能,可以使用网络上的一个制作cadence PCB 封装的插件来实现5 不画原理图直接给管脚定义网络名的方法1.勾选SETUP->USER PREFERENCES->MISC->LOGIC_EDIT_ENABLED2.使用LOGIC〉NET LOGIC6 setup-->user proferences 下面的set pcb_cursor cross 小十字,set pcb _cursor infiniter 这是大十字cadence使用时间不长,虽然画几块板子,和protel 相比有很多不同的地方。

比如在protel PCB中想删除某几个连线,如果全选,就把过孔什么的全选,而在cadence中,是把net text via 等作为不同的属性,任何操作必须制定对象,如移动、删除、查找,必须有确定的类型;使用cadence很不习惯的一点是在连线以及过孔中没有显示网络标号,想知道输入什么还得点击一个显示的操作,而且不能全部显示,而在protel中,过孔以及连线是什么net一目了然。

cadence学习笔记

关键字:1.快捷键2.注意基本了解了一下界面最左面的原理图管理器的基本设置;学会两个快捷键:放大I 缩小O;上下滚动pageup、pagedown;鼠标滚动左右滚动ctrl+ pageup、pagedown;ctrl+鼠标滚动刷新F5今天了解了cadence原理图页面的基本设置:页面大小、title是否显示,网格大小显示的基本设置!这都是在options选项中设置!今天学会了自己画简单元件(只需要一部分就能画出的元器件),了解其常见设置;画一个AT90S8535为例!1、练习了显示隐藏引脚(pin)的设置(Options-part propreties选项中设置,ture表示显示,falth表示隐藏);2、练习对引脚的批量属性改变!选中十字光标右键,eide proprepries…出现下图,一一修改;画原件应注意,body部分应该放在虚线框中;注意:liberiy中用到的快捷键:H,V,RAT90S8535:今天了解了分立元件的画法和理念,例如74系列的一类芯片!芯片中分几路功能相同(这种采用homogeneous(同址形式),另外一形式为heterogeneous);在new part 对话框中;设置项parts per Pkg表示元件需要分几部分画!注意:heterogeneous与homogeneous的区别:1.homogeneous是元件的每部分电气属性、结果相同;画一部分,自动生成下一部分!只需自己改下pin的number!heterogeneous不然,表示每一部分的电气属性、结果都不一样,每部分都需自己画!快捷键:ctrl+N 自动切换到下部分!Ctrl+B 自动切换到上面部分!哎!令人蛋腾+乳酸的大学,好不容易休息了一个双休,一切的一切都是拜自考占用学校所赐!何得何能啊?今天初涉原理图设计,也就是添加库文件,放置元器件(快捷键P),元器件连接方式:连接导线(w)、总线连接(b)、网络标号连接(n)等形式,自动命名(tools-annotate)注意:1. 连接导线时改变走线方向时按键shift;2.当某元器件的端口悬空时,需放置place no connect(快捷键X),表示引脚悬空电气检查时不报错!3.尽量不要使两元器件的端口直接连接,这样后期布板,电气检查,容易出错,而是用线直接连上;4.常用的库文件,也就是电阻电容之内的在discrete库中;5.放过的器件都在Design Cache中记录。

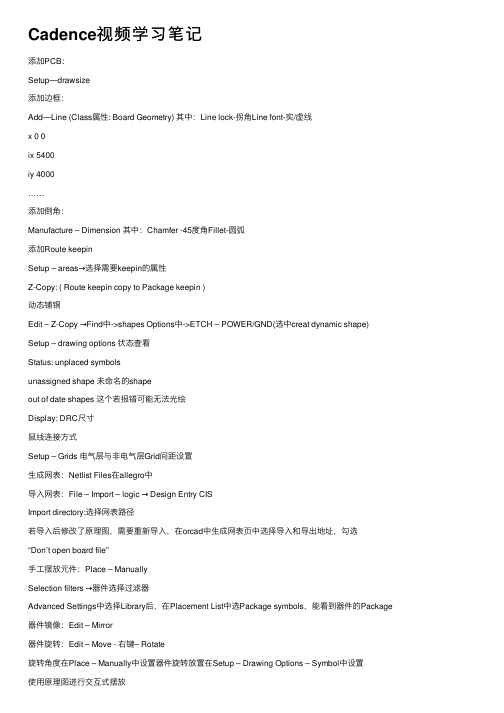

Cadence视频学习笔记

Cadence视频学习笔记添加PCB:Setup—drawsize添加边框:Add—Line (Class属性: Board Geometry) 其中:Line lock-拐⾓Line font-实/虚线x 0 0ix 5400iy 4000……添加倒⾓:Manufacture – Dimension 其中:Chamfer -45度⾓Fillet-圆弧添加Route keepinSetup – areas→选择需要keepin的属性Z-Copy: ( Route keepin copy to Package keepin )动态铺铜Edit – Z-Copy →Find中->shapes Options中->ETCH – POWER/GND(选中creat dynamic shape) Setup – drawing options 状态查看Status: unplaced symbolsunassigned shape 未命名的shapeout of date shapes 这个若报错可能⽆法光绘Display: DRC尺⼨⿏线连接⽅式Setup – Grids 电⽓层与⾮电⽓层Grid间距设置⽣成⽹表:Netlist Files在allegro中导⼊⽹表:File – Import – logic → Design Entry CISImport directory:选择⽹表路径若导⼊后修改了原理图,需要重新导⼊,在orcad中⽣成⽹表页中选择导⼊和导出地址,勾选“Don’t open board file”⼿⼯摆放元件:Place – ManuallySelection filters →器件选择过滤器Advanced Settings中选择Library后,在Placement List中选Package symbols,能看到器件的Package 器件镜像:Edit – Mirror器件旋转:Edit – Move - 右键– Rotate旋转⾓度在Place – Manually中设置器件旋转放置在Setup – Drawing Options – Symbol中设置使⽤原理图进⾏交互式摆放OrCAD中Options-Preferences- Miscellaneous 选中Enable Intertool Communication然后PCB Edit中Place- Placement(cmd处于place manual下)在OrCAD中选中要的元件,右键选择PCB edit selection按原理图页⾯进⾏摆放重新创建⽹表PCB Edit中–点Setup edit 在记事本本件中PAGE = YES(激活了新属性)必须选allow user defined PropertiesPCB Edit中,重新导⼊⽹表,选中create user-defined properties导⼊后选择Place – Quickplace 选Place by property/value 中的新属性,edge和board side都是摆放的位置在PCB Edit中按room摆放:导⼊⽹表后,Edit – Properties后,在Find by name中选择Comp (or Pin)点more,选中要放的元件,点apply,在下拉列表中找到Room,然后给Value赋值。

cadence学习记录-图文

cadence学习记录-图文2022-3-13制版流程:原理图(先做好原理图元件库),2、DRC检查,输出网表3、做好封装,确认每个元件都有封装。

4、画好板子边框,导入网表,布局,设置约束规则,不限铺铜,DRC检查,出丝印,钻孔,出光汇第三讲原理图库上原理图库设计DeignentryCIS-------orcadcaptureci新建库file----new---library(默认保存在系统文件夹下)or新建工程在工程里新建库放置边框放置管脚(右键endmode取消放置)--avea如果修改管脚,选中管脚右键—editpropertieplacepinarray可以同时放置多个管脚(矩阵管脚)一个复合元器件的原理图库设计复合元器件分为很多部分分割为几部分分隔成相同的部分,还是不同的部分以字母来区分还是以数字来区分View—package将整个元件视图展现,更改某PART属性双击该part进行设置,若是相同part,更改一个part,另一个part也会更改。

注:管脚输入有上划线的,管脚name输入w\\r\\,,输出结果为第四讲原理图库下创建分割元件(不同模块)方法一:同上一节创建相同part的方法,创建完模块A,按住end键,模块A消失,点重现,ctrl+n切换到下一部分方法2:通过表格进行创建,Library1.olb单击右键,newpartfrompreadheet,在e某cel表格里可以先填好,再复制到newpartcreationpreadheet画原理图添加元器件库。

(1)单击,或执行菜单命令“place→part”,此时元件库“Librarie”中只有库元件“DeignCache”选项(2)单击(placepart),单击“添加元件库。

第五讲设置环境”添加元件库,或者单击,(1)创建工程,页面:file→new→project→图图纸(2)熟悉菜单界面file→撤销剪切镜像viewplaceoption(3)环境设置option→preferenceoption→图纸无效option→第六讲库管理、放置元件原理图库添加与删除→右键newpage创建原理模板设置,只对下一次创建工程起作用,对本次工程原理图纸设置,只对某page起作用,打开原理图,按键盘上的P键,弹出元器件窗口或点击库,删除原理图库。

cadence使用笔记

(百度和网页/analog/Cadence.html 的作者无关,不对其内容负责。

百度快照谨为网络故障时之索引,不代表被搜索网站的即时页面。

)您查询的关键词是:errpreset 。

如果打开速度慢,可以尝试快速版;如果想保存快照,可以添加到搜藏。

内容目录1 Candence 使用笔记2 1.1波形图的自定义设置 2 1.2波形图的打印 2 1.3ocean 脚本辅助仿真3 1.4用Results Browser 查看相噪 41.5用脚本方便的实现工艺角和温度组合的仿真 5 1.6在服务器端进行远程仿真 5 1.7积分方法和参数设置对仿真的影响 6 1.8改变schematic 和layout 的对应关系 7 1.9Assura 提取电容参数出现误差的问题 7 1.10ADE 中默认精度的设置 7 1.11由服务器向本地传送文件 81.Candence使用笔记2007.11.1, duoyun1.1波形图的自定义设置Candence平台由SKILL脚本写成,因此为其强大的自定义功能提供了基础。

在用户目录(/home/**或~/)下有一个文件.cdsinit(如果没有的话可以自己创建)。

在这个文件中加入SKILL语句,Candence每次启动时自动执行这些语句,因此可以完成定义默认设置,绑定快捷键等多种自定义设置。

以波形图的硬复制为例,如果希望在画出波形图时默认画出网格线,并且默认打印到文件。

则可以在.cdsinit文件中加入以下两句:awvSetOptionValue("displayGrids" t)awvSetOptionValue("hcOutputFile" t)其他一些常见设置如:awvSetOptionValue("dateStamp" t)awvSetOptionValue("hcHeader" nil)awvSetOptionValue("hcMailLogNames" nil)awvSetOptionValue("hcPaperSize" "A")awvSetOptionValue("hcPlotterName" "Tektronix")将这些语句写入.cdsinit或.oceanrc即可。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

1. 有些特殊的焊盘上要打很多孔,需要在Multiple Drill里设置。

2. .psm是元件封装的数据文件,不能直接编辑,.dra是绘图文件,我们可以用软件打开它对封装进行编辑。

3. 按room摆放:

使用PCB Editor,

1)在PCB Editor里设置room属性,导入网表后,Edit - Properties,在Find by name中选择Comp (or Pin),点击More,选择需要赋予room属性的元件,弹出Edit Property对话框

,在左边的Available Properties中选择Room,value=power3v3,然后点击Apply,在Show Properties 窗口可以看到所选的元件都有ROOM=power3v3,这样元件有了room属性;

2)接下来在PCB Editor里添加room区域,Setup - Outlines - Room Outline,在Create/Edit Option 选择Draw Rectangle,在板框内部拉出一个矩形框;

3)按照room属性来摆放,Place - Quick Place,在Placement Filter里选择Place by room,在下拉列表中选择power3v3,点击Place。

使用Capture CIS,

1)选中元件,右键Edit Properties,Filter by选择Cadence-Allegro,找到ROOM编辑,填写power1v6,再切换到<Current Properties>,可以看到room属性已经带过来了;

2)属性设置好以后,要把属性做到网表里,需要重新生成网表,点击.dsn,Tools - Create Netlist;3)回到PCB Editor,重新导入网表,File - Import - Logic;

4)创建room,Setup - Outlines - Room Outline,在Create/Edit Option选择Draw Rectangle,画出power1v6的room;

5)按照room属性来摆放,Place - Quick Place,在Placement Filter里选择Place by room,在下拉列表中选择power1v6,点击Place。

4. 把所有的元件都调进来,Place - Quick Place,在Placement Filter里选择Place all components,查找,Edit - Move,在Find by name中选择Symbol (or Pin),输入想要

查找的元件的参考编号。

1. 手工建立电路板的步骤:

1)设置绘图参数

2)建立板外框

3)放置安装孔

4)设置允许摆放区域,Setup - Areas - Package Keepin

5)设置允许布线区域,Setup - Areas - Route Keepin

6)设置禁止布线区域,Setup - Areas - Route Keepout

2. 建立电路板机械符号:

1)建立机械符号文件

2)设置格点,Non-Etch部分的Spacing x:25mil,Spacing y:25mil,

3)建立板框

4)添加定位孔

5)倾斜拐角,Dimension - Chamfer,First设为50,

6)尺寸标注,Dimension - Parameters,点击Extension lines,将Offset Distance from Element 设为0.25,然后Dimension - Linear Dim,

7)标注斜角,

Dimension - Chamfer Leader,单击45°的斜线,拖动鼠标移动到适当位置,左键确定位置,右键Done,

Add - Text,Text Block设为4,左键确定位置,输入文本(jixie),右键Done,

如果要修改文本内容,Edit - Text,

8)设置允许摆放区域和允许布线区域,Edit - Z-Copy Shape,

Copy to class选择Package Keepin,Copy to subclass选择All,Size选择COntract,Offset设为70,单击板框边界,出现允许摆放区域,

Copy to class选择Route Keepin,Copy to subclass选择All,Size选择COntract,Offset设为50,单击板框边界,出现允许布线区域,右键Done,

9)设置禁止摆放区域和禁止布线区域,

Setup - Areas - Package Keepout,在电路板中间画一个矩形,

显示固定孔,Setup - Areas - Route Keepout,在固定孔附近画一个矩形,右键Done,

10)设置禁止过孔区域,Setup - Areas - Via Keepout。