数电大作业

哈工大数电大作业——学号后三位为模的计数器

数字电子技术应用Verilog HDL设计计数器学院:航天学院班级:学号:姓名:教师:设计要求:利用Verilog HDL设计一个以自己学号后三位为模的计数器。

设计步骤:首先我的学号后三位为114,因此计数器范围是0到113一共114个数。

然后根据此要求编写功能程序以及激励源的相关程序,第三步在modelsim下进行实验调试,看所编程序能否实现预期功能,然后再把相关实验数据截图记录。

程序代码:modulejishuqi(out,reset,clk);output [7:0] out;inputreset,clk;reg [7:0] out;always @(posedgeclk)beginif(!reset)out<=8'h00;else if(out>=113)out=8'h00;else out<=out+1;endendmodule激励源设置程序:`timescale 1 ns/ 1 psmodulejishuqi_test();regclk;reg reset;wire [7:0] out;jishuqi i1 (.clk(clk),.out(out),.reset(reset));initialbegin#1 clk=0;#10 reset=0;#40 reset=1;endalways #20 clk=~clk ;endmoduleModelsim仿真波形图:注二进制数01110001化成十进制数为113,因此得到了正确的波形图。

RTL ViewerTechnology Map Viewer。

电大高等数学基础形考作业~参考答案

【高等数学基础】形考作业4答案第5章不定积分 第6章定积分及其应用(一)单项选择题1 1.若f(x)的一个原函数是—,则f (x)( D )•xlnx 4 — f 下列等式成立的是(D ).x x x-Jf (x)dx f (x) df (x) f (x) d f (x)dx f (x) 一 f (x)dx f (x)若 f (x) dx f (x)dx (B ).2.若函数F(x)与G(x)是同一函数的原函数,则F(x) G(x) c(常数).7•若无穷积分1—p dx 收敛,xsin x c cosx c sin x c d cosx c - dx x 2f (x 3 4)dx(B).1 1 1 _ f (x 3)二 f (x)二 f (x 3)若 f (x)dx F(x) c ,则 一 f( _x)dx (B 1 c -=F ^/x) c 下列无穷限积分收敛的是(D).x 尝(二)填空题 x f (x)dx .3 2 3 1 1〜f(x 3)x 2匚加二 c ,.3 3 F(.x) c2F(..x) cF(2..x) dx —7 .•函数f(x)的不定积分是dx x 1356. 3(sin x2)dx 32. 3. (三)计算题 1 cos- 汁dx x 如 e . ---- dx x -^dx xln x xsin 2xdx cos 1 d(1)x x .1 sin xe x d 、x 2e x c 1 d(ln x)lnx1 xcos2x2In(ln x)1 cos2xdx 21 x cos 2x 1 si n2x c2 4cosx ,贝UF(x)与G(x)之间有关系式9cos(3x)e3 In x e115.dx.(3 In x)d(3In x)(3In x):1 x12212x .1 2x 1 1 1 2x . 12 1 2x 1 1 2 1 6.xe dx-e x—e dx-e -e 0 -e — 0 20 2 02 44 4e2 x e1 e2 e 17.xln xdx——Inxdx12 1 2 1 24eln x . 1 , ee 1 , 1 1 e2 ,& d2 dx — I—dx11 xx 11xe x1e(四)证明题a1.证明:若f(x)在[a, a ]上可积并为奇函数,则f(x)dx 0 .aaaa=0 f( x)dx o f (x)dx J f (x) f ( x)]dx 证毕f (x)dxaaf( t)dt a f( at)dtf(t)dtf(x)dxa f (x)dxaa f (x)dxa0证毕2.证明:若f (x)在[a, a]上可积并为偶函数,0 f (x)dxaaaf(x)dx0 f (x)dxa 证:a3•证明: 证:af(x)dx oa o[f (X )af(x)dx of (x)dxf ( x)]dxf (x)dxf( aaaf(x)dxax)dx o f(x)dxa0 f(x)dx .x x23. d e dx e4. (tan x) dx tan x c5.若f(x)dx cos3x c,贝U f (x)。

电大数学思想与方法形考作业:通关作业答案

电大数学思想与方法形考作业:通关作业答案第一关3题目1巴比伦人是最早将数学应用于()的。

在现有的泥板中有复利问题及指数方程。

选择一项:A. 农业B. 工程C. 商业D. 运输题目2《九章算术》成书于(),它包括了算术、代数、几何的绝大部分初等数学知识。

选择一项:A. 战国时期B. 商朝C. 汉朝D. 西汉末年题目3金字塔的四面都正确地指向东南西北,在没有罗盘的四、五千年的古代,方位能如此精确,无疑是使用了()的方法。

选择一项:A. 几何测量B. 代数计算C. 天文测量D. 占卜题目4在丢番图时代(约250)以前的一切代数学都是用()表示的,甚至在十五世纪以前,西欧的代数学几乎都是用()表示。

选择一项:A. 符号,符号B. 文字,文字C. 符号,文字D. 文字,符号题目5古埃及数学最辉煌的成就可以说是()的发现。

选择一项:A. 四棱锥台体积公式B. 球体积公式C. 进位制的发明D. 圆面积公式题目6《几何原本》中的素材并非是欧几里得所独创,大部分材料来自同他一起学习的()。

选择一项:A. 毕达哥拉斯学派B. 柏拉图学派C. 亚历山大学派D. 爱奥尼亚学派题目7古印度人对时间和空间的看法与现代天文学十分相像,他们认为一劫(“劫”指时间长度)的长度就是(),这个数字和现代人们计算的宇宙年龄十分接近。

选择一项:A. 1亿年B. 10亿年C. 1000亿年D. 100亿年题目8根据亚里士多德的想法,一个完整的理论体系应该是一种演绎体系的结构,知识都是从()中演绎出的结论。

选择一项:A. 自然命题B. 一般原理C. 最终原理D. 初始原理题目9欧几里得的《几何原本》几乎概括了古希腊当时所有理论的(),成为近代西方数学的主要源泉。

选择一项:A. 几何与代数B. 数论及几何学C. 代数与数论D. 几何题目10数学在中国萌芽以后,得到较快的发展,至少在()已经形成了一些几何与数目概念。

选择一项:A. 六七千年前B. 春秋战国时期C. 新石器时代D. 五千年前第二关3题目1欧几里得的《几何原本》是一本极具生命力的经典著作,它的著名的平行公设是( )。

哈工大电大数字电子技术基础大作业

哈工大电大数字电子技术基础大作业

H a r b i n I n s t i t u t e o f T e c h n o l o g y

数字电子技术基础大作业

课程名称:数字电子技术基础

设计题目:血型与状态机

院系:

班级:

设计者:

学号:

哈尔滨工业大学

血型逻辑电路设计

一实验目的

1.掌握采用可编程逻辑器件实现数字电路与系统

的方法。

2.掌握采用Xilinx_ISE软件开发可编程逻辑器件

的过程。

3.学会设计血型能否输血的数字电路。

4.掌握Verilog HDL描述数字逻辑电路与系统的方

法。

二设计要求

1.采用BASYS2开发板开关,LED,数码管等制作验

证能否输血的电路。

2.采用Xilinx_ISE软件进行编程、仿真与下载设

计到BASYS2开发板。

三电路图

1.电路模块图(简化)

应用:

2.内部电路组成(简化)。

数电大作业(交通指示灯+电子琴+智能钟表)

数电大作业(交通指示灯+电子琴+智能钟表)-标准化文件发布号:(9456-EUATWK-MWUB-WUNN-INNUL-DDQTY-KII(交通指示灯是可以实现的电子琴那个是不知道是否正确自己验证吧)(最后还有两个题一个是交通指示灯的有点复杂的另一个是时钟的个人感觉也是有点复杂)一、交通灯电路设计要求:1.设计一个十字路口交通灯控制电路,要求东西方向车道和南北方向车道两条交叉掉路上的车辆交替运行,每次通行的时间设置为24秒。

2.在绿灯转为红灯时,要求黄灯先亮4秒钟,才能变换运行车道。

3.可用LED模拟交通灯。

4.用倒计时显示每个状态的时间。

思路分析:1.电路有四个状态:东西绿南北红→东西黄南北红→东西红南北绿→东西红南北黄一共有四个状态循环,所以可以先用一个模4计数器来转换这四个状态。

设计电路如图所示:这里采用74LS163构成模4计数器,状态由 00 → 01 → 10 → 11 进行循环。

L1(东西绿):当00时亮,其他状态时不亮。

L2(东西黄):当01时亮,其他状态时不亮。

L3(东西红):当10、11时亮,00、01时不亮。

L4(南北绿):当10时亮,其他状态时不亮。

L5(南北黄):当11时亮,其他状态时不亮。

L6(南北红):当00、01时亮,10、11时不亮。

电路可以这样实现:B A Y0 Y1 Y2 Y30 0 0 1 1 10 1 1 0 1 11 0 1 1 0 11 1 1 1 1 0所以,Y0~Y4口接上非门后可以控制L1、L2、L4、L5。

L3=B,L6=B,所以将L3直接连在1B端,将1A端加非门与L6相连。

通过这样的连接便可以实现这四个状态的循环。

接下来要完成电路的计数部分:由于要实现倒计时显示,所以可以采用两片74LS190,该芯片是十进制加减法计数器。

通过网络找出一下功能表。

由于要实现倒计时,所以U/D端输入高电平,此时计数器进行减计数。

用两片74LS190,通过RC端进行异步级联,由于红灯28秒,黄灯4秒,绿灯24秒,所以各状态及持续时间如下:状态1:东西绿南北红(00):24秒状态2:东西黄南北红(01):4秒状态3:东西红南北绿(10):24秒状态4:东西红南北黄(11):4秒当状态转变时,给计数器置数即可。

电大离散数学作业2

离散数学集合论部分形成性考核书面作业本课程形成性考核书面作业共3次,内容主要分别是集合论部分、图论部分、数理逻辑部分的综合练习,基本上是按照考试的题型(除单项选择题外)安排练习题目,目的是通过综合性书面作业,使同学自己检验学习成果,找出掌握的薄弱知识点,重点复习,争取尽快掌握.本次形考书面作业是第一次作业,大家要认真及时地完成集合论部分的综合练习作业.要求:学生提交作业有以下三种方式可供选择:1. 可将此次作业用A4纸打印出来,手工书写答题,字迹工整,解答题要有解答过程,完成作业后交给辅导教师批阅.2. 在线提交word文档3. 自备答题纸张,将答题过程手工书写,并拍照上传.一、填空题1.设集合{1,2,3},{1,2}A B==,则P(A)-P(B )= {{3}, {1,2,3}, {1, 3 }, {2,3}} ,A⨯B= {<1,1>,<1,2>,<2,1>,<2,2>,<3,1>,<3,2>} .2.设集合A有10个元素,那么A的幂集合P(A)的元素个数为1024 .3.设集合A={0, 1, 2, 3},B={2, 3, 4, 5},R是A到B的二元关系,R⋂∈y∈x<且=且>∈x{B,,AAyyBx}则R的有序对集合为{<2, 2>,<2, 3>,<3, 2>},<3, 3> .4.设集合A={1, 2, 3, 4 },B={6, 8, 12},A到B的二元关系R=}x∈y∈><y=2,,,{ByxAx那么R-1={<6,3>,<8,4>} .5.设集合A={a, b, c, d},A上的二元关系R={<a, b>, <b, a>, <b, c>, <c, d>},则R具有的性质是反自反性,反对称性.6.设集合A={a, b, c, d},A上的二元关系R={<a, a >, <b, b>, <b, c>, <c, d>},若在R中再增加两个元素<c, b>, <d, c>,则新得到的关系就具有对称性.7.如果R1和R2是A上的自反关系,则R1∪R2,R1∩R2,R1-R2中自反关系有 2 个.8.设A={1, 2}上的二元关系为R={<x, y>|x∈A,y∈A, x+y =10},则R的自反闭包为{<1, 1>, <2, 2>} .9.设R是集合A上的等价关系,且1 , 2 , 3是A中的元素,则R中至少包含<1, 1>, <2, 2>, <3, 3> 等元素.10.设A={1,2},B={a,b},C={3,4,5},从A到B的函数f ={<1, a>, <2, b>},从B到C的函数g={< a,4>, < b,3>},则Ran(g︒ f)= {3,4} .二、判断说明题(判断下列各题,并说明理由.)1.若集合A = {1,2,3}上的二元关系R={<1, 1>,<2, 2>,<1, 2>},则(1) R是自反的关系;(2) R是对称的关系.解:(1)错误,R不是自反关系,因为没有有序对<3,3>.(2)错误,R不是对称关系,因为没有有序对<2,1>2.设A={1,2,3},R={<1,1>, <2,2>, <1,2> ,<2,1>},则R是等价关系.解:错误, 即R不是等价关系.因为等价关系要求有自反性x R x, 但<3, 3>不在R中.3.若偏序集<A,R>的哈斯图如图一所示,则集合A的最大元为a,最小元不存在.οοοοab cd图一οοοg e fh ο解:错误.集合A的最大元不存在,a是极大元.4.设集合A={1, 2, 3, 4},B={2, 4, 6, 8},,判断下列关系f是否构成函数f:A→,并说明理由.B(1) f={<1, 4>, <2, 2,>, <4, 6>, <1, 8>};(2) f={<1, 6>, <3, 4>, <2, 2>};(3) f={<1, 8>, <2, 6>, <3, 4>, <4, 2,>}.解:(1) f不能构成函数.因为A中的元素3在f中没有出现.(2) f不能构成函数.因为A中的元素4在f中没有出现.(3) f可以构成函数.因为f的定义域就是A,且A中的每一个元素都有B中的唯一一个元素与其对应,满足函数定义的条件.三、计算题1.设}4,2{=CB==E,求:A},5,4,3,2,1{=},5,2,1{4,1{},(1) (A⋂B)⋃~C;(2) (A⋃B)-(B⋂A) (3) P(A)-P(C);(4) A⊕B.解:(1)因为A∩B={1,4}∩{1,2,5}={1},~C={1,2,3,4,5}-{2,4}={1,3,5}所以(A∩B ) ⋃~C={1}⋃{1,3,5}={1,3,5}(2)(A⋃B)-(B⋂A)= {1,2,4,5}-{1}={2,4,5}(3)因为P(A)={φ,{1}, {4}, {1,4}}P(C)={φ,{2},{4},{2,4}}所以P(A)-P(C)={ φ,{ 1},{ 4},{ 1,4}}-{φ,{ 2},{ 4},{2,4 }}(4) 因为A⋃B={ 1,2,4,5}, A⋂B={ 1}所以A⊕B=A⋃B-A⋂B={1,2,4,5}-{1}={2,4,5}2.设A={{1},{2},1,2},B={1,2,{1,2}},试计算(1)(A-B);(2)(A∩B);(3)A×B.解:(1)A-B ={{1},{2}}(2)A∩B ={1,2}(3)A×B={<{1},1>,<{1},2>,<{1},{1,2}>,<{2},1>,<{2},2>,<{2},{1,2}>,<1,1>,<1,2>,<1, {1,2}>,<2,1>,<2,2>,<2, {1,2}>}3.设A={1,2,3,4,5},R={<x,y>|x∈A,y∈A且x+y≤4},S={<x,y>|x∈A,y∈A且x+y<0},试求R,S,R•S,S•R,R-1,S-1,r(S),s(R).解:R={<1,1>,<1,2>,<1,3>,<2,1>,<2,2>,<3,1>}, \R-1={<1,1>,<2,1>,<3,1>,<1,2 >,<2,2>,<1, 3>}S=φ, S-1 =φr(S)={<1,1>,<2,2>,<3,3>,<4,4>,<5,5>}s(R)= {<1,1>,<1,2>,<1,3>,<2,1>,<2,2>,<3,1>}R •S=φS •R=φ4.设A ={1, 2, 3, 4, 5, 6, 7, 8},R 是A 上的整除关系,B ={2, 4, 6}.(1) 写出关系R 的表示式; (2 )画出关系R 的哈斯图;(3) 求出集合B 的最大元、最小元.解:R={<1,1>,<1,2>,<1,3>,<1,4,<1,5>,<1,6>,<1,7>,<1,8>,<2,2>,<2,4>,<2,6>,<2,8>,<3,3>,<3,6>,<4,4>,<4,8>,<5,5>,<6,6>,<7,7>,<8,8>}(2)关系R 的哈斯图如图(3)集合B 没有最大元,最小元是:2四、证明题1.试证明集合等式:A ⋃ (B ⋂C )=(A ⋃B ) ⋂ (A ⋃C ).证明:设,若x ∈A ⋃ (B ⋂C ),则x ∈A 或x ∈B ⋂C , 即 x ∈A 或x ∈B 且 x ∈A 或x ∈C .即x ∈A ⋃B 且 x ∈A ⋃C ,即 x ∈T =(A ⋃B ) ⋂ (A ⋃C ),所以A ⋃ (B ⋂C )⊆ (A ⋃B ) ⋂ (A ⋃C ).反之,若x ∈(A ⋃B ) ⋂ (A ⋃C ),则x ∈A ⋃B 且 x ∈A ⋃C ,即x ∈A 或x ∈B 且 x ∈A 或x ∈C ,即x ∈A 或x ∈B ⋂C ,7即x∈A⋃ (B⋂C),所以(A⋃B) ⋂ (A⋃C)⊆ A⋃ (B⋂C).因此.A⋃ (B⋂C)=(A⋃B) ⋂ (A⋃C).2.试证明集合等式A⋂ (B⋃C)=(A⋂B) ⋃ (A⋂C).证明:设S=A∩(B∪C),T=(A∩B)∪(A∩C),若x∈S,则x∈A且x∈B∪C,即x∈A且x∈B或x∈A且x∈C,也即x∈A∩B或x∈A∩C,即x∈T,所以S⊆T.反之,若x∈T,则x∈A∩B或x∈A∩C,即x∈A且x∈B 或x∈A且x∈C也即x∈A且x∈B∪C,即x∈S,所以T⊆S.因此T=S.3.对任意三个集合A, B和C,试证明:若A B = A C,且A,则B = C.证明:设x∈A,y∈B,则<x,y>∈A⨯B,因为A⨯B = A⨯C,故<x,y>∈ A⨯C,则有y∈C,所以B⊆ C.设x∈A,z∈C,则<x,z>∈ A⨯C,因为A⨯B = A⨯C,故<x,z>∈A⨯B,则有z∈B,所以C⊆B.故得B=C.4.试证明:若R与S是集合A上的自反关系,则R∩S也是集合A上的自反关系.证明:R1和R2是自反的,∀x∈A,<x, x> ∈R1,<x, x> ∈R2,则<x, x> ∈R1∩R2,所以R1∩R2是自反的.。

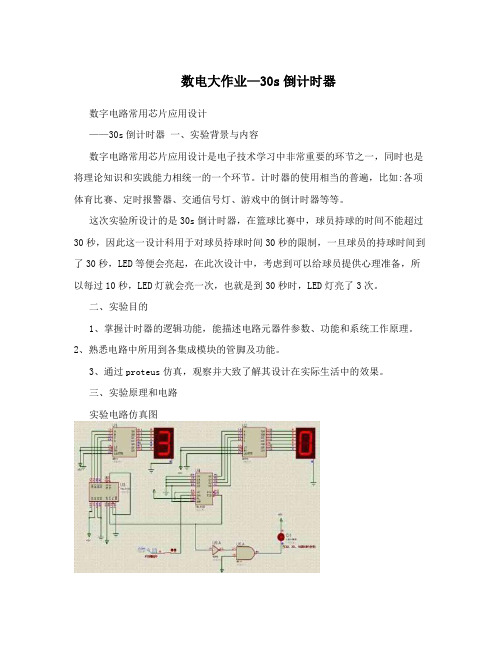

数电大作业—30s倒计时器

1、掌握计时器的逻辑功能,能描述电路元器件参数、功能和系统工作原理。 2、熟悉电路中所用到各集成模块的管脚及功能。

3、通过proteus仿真,观察并大致了解其设计在实际生活中的效果。

三、实验原理和电路

实验电路仿真图

实验元器件及介绍:两个74LS192双时钟方式的十进制可逆计数器、两个4511七段译码器、

1

4011四2输入与非门、4069六反相器、LED灯,开关

, 74LS192

74LS192是十进制可编程同步加锁计数器,它采用8421码二-十进制编码,并具有直接清零、置数、加锁计数功能。其中CP、CP分别是加计数器、减计数器的时钟脉冲输入UD

端(上升沿有效)。PL是异步并行置数控制端(低电平有效),TC、TC分别是进位、UD借位输出端(低电平有效),MR是异步清除端,P0~P3是并行数据输入端,Q3~Q0是输出端。我们将用到的是它的减计数功能。

不过在此次proteus仿真中,就是一个非门,如下图:

4

5

74ls192引脚图:

CPCP:计数芯片时钟脉冲输入 :倒计时时钟脉冲输入 UD

PL:异步并行负载(低电平)输入 Pn:并行数据输入

Qn:触发器输出 MR:异步主复位(清除)输入 TCTC:终端数最多输出 :终端倒计时输出 UD

74ls192功能表:

输入 输出 MR PL CPU CPD P3 P2 P1 P0 Q3 Q2 Q1 Q0 1 X X X X X X X 0 0 0 0 0 1 X X d c b a d c b a 0 0 1 X X X X 加计数

2

0 0 1 X 192的工作原理:

CPCP 当PL=1,MR=0时,若时钟脉冲加入到端,且置数=1,则计数器在预置数的基UD

数电大作业流水灯

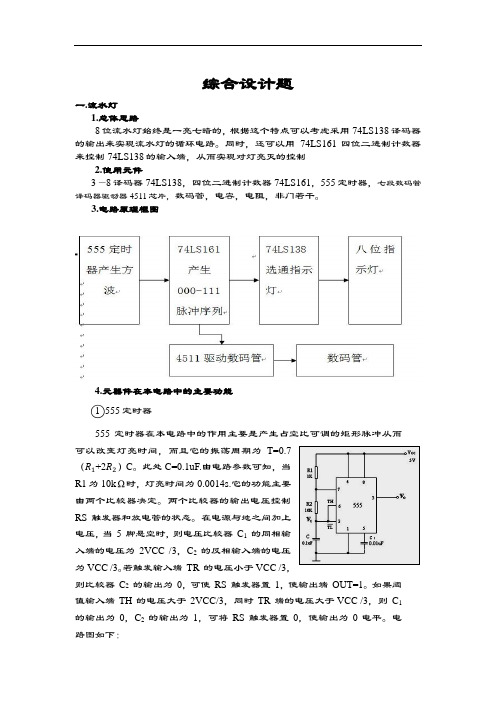

综合设计题一.流水灯1.总体思路8位流水灯始终是一亮七暗的,根据这个特点可以考虑采用74LS138译码器的输出来实现流水灯的循环电路。

同时,还可以用74LS161四位二进制计数器来控制74LS138的输入端,从而实现对灯亮灭的控制2.使用元件3—8译码器74LS138,四位二进制计数器74LS161,555定时器,七段数码管译码器驱动器4511芯片,数码管,电容,电阻,非门若干。

3.电路原理框图4.元器件在本电路中的主要功能○1555定时器555 定时器在本电路中的作用主要是产生占空比可调的矩形脉冲从而可以改变灯亮时间,而且它的振荡周期为T=0.7(R1+2R2)C。

此处C=0.1uF.由电路参数可知,当R1为10kΩ时,灯亮时间为0.0014s.它的功能主要由两个比较器决定。

两个比较器的输出电压控制RS 触发器和放电管的状态。

在电源与地之间加上电压,当5 脚悬空时,则电压比较器C1的同相输入端的电压为2VCC /3,C2的反相输入端的电压为VCC /3。

若触发输入端TR 的电压小于VCC /3,则比较器C2的输出为0,可使RS 触发器置1,使输出端OUT=1。

如果阈值输入端TH 的电压大于2VCC/3,同时TR 端的电压大于VCC /3,则C1的输出为0,C2的输出为1,可将RS 触发器置0,使输出为0 电平。

电路图如下:○274LS161计数器74LS161计数器在本电路中的作用是产生000-111脉冲控制74LS138的A2A1A0,依次选通Y0-Y7。

产生脉冲序列也可以用74LS191是四位二进制同步加/减计数器,与74LS161相比,它能够实现减计数,此处只需要求产生脉冲序列,而且74LS161是常用的计数器,所以选择74LS161产生脉冲序列。

所以采用反馈置数法,产生000-111脉冲序号,时钟脉冲外部接入,原理图如下图所示○374LS138译码器74LS138译码器在本电路中的作用主要是选通指示灯发光。

西电电院数电大作业

数电大作业学院:电子工程学院选题一:交通灯一、设计要求为了确保十字路口的车辆顺利畅通地行驶,往往都采用自动控制的交通信号灯来进行指挥。

其中红灯亮,表示该条道路禁止通行;黄灯亮表示暂时的停车,等待信号;绿灯亮表示可以通行。

1.设计一个十字路口交通信号灯控制器,其要求如下:设南北方向的红、黄、绿灯分别为r,y,g;东西方向的红、黄、绿灯分别为R,Y,G,满足图1 的工作流程并且可以并行工作:g(R)→r(G),黄灯用于提示绿灯变为红灯或者绿灯变为红灯。

2.满足两个方向的工作时序:其中令东西方向为主干道方向,绿灯亮30秒,红灯亮20秒,黄灯5秒;南北方向为支线,绿灯20秒,红灯30秒,黄灯5秒。

3.十字路口要有数字显示装置(数码管),作为时间提示,以便人们更直观地把握时间。

二、方案1、总体设计方案分析系统的逻辑功能需求后,交通灯控制系统将主要由以下几个部分构成:定时脉冲发生器、状态机、控制器、译码器、延时器、彩灯。

定时脉冲发生器发出以1S为单位的定时脉冲,状态机控制交通灯红、绿、黄状态的变化,而控制器将控制数码管的倒计时,并将对状态机进行反馈。

延时器、译码器与交通彩灯将由状态机的输出信号进行相应的信号灯变化。

总体设计框图如下:为实现倒计时功能,可由555芯片设计一个1S为周期,50%占空比的脉冲电路,以控制控制器的时钟。

3、状态机设计将图一的四个状态分别以00、01、11、10表示,则可用双D触发器构成一个简单的状态机21124、控制器设计控制器主要实现倒计时功能,但普通计数器只有正向计数功能,固在计数输经过分析上表,其中每个状态的初始值都可由状态机的输出状态进行置数。

7610321212D5=Q1与非Q2 。

5、延时、译码、及信号灯设计信号灯同样可由状态机的输出信号控制,其中用“1”表示灯亮,“0”表示由译码器的两个输出脚经过或门得到。

但是,为了实现在29、04、19秒变灯还必须在状态机与译码器之间加上一个延时器,当变灯信号到达后,延时一秒,再经由译码器控制信号灯变化,而这同样也可以由一个双D触发器实现。

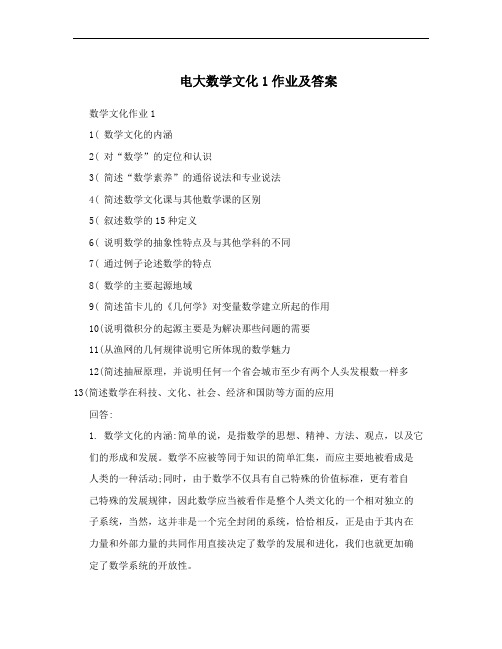

电大数学文化1作业及答案

电大数学文化1作业及答案数学文化作业11( 数学文化的内涵2( 对“数学”的定位和认识3( 简述“数学素养”的通俗说法和专业说法4( 简述数学文化课与其他数学课的区别5( 叙述数学的15种定义6( 说明数学的抽象性特点及与其他学科的不同7( 通过例子论述数学的特点8( 数学的主要起源地域9( 简述笛卡儿的《几何学》对变量数学建立所起的作用10(说明微积分的起源主要是为解决那些问题的需要11(从渔网的几何规律说明它所体现的数学魅力12(简述抽屉原理,并说明任何一个省会城市至少有两个人头发根数一样多13(简述数学在科技、文化、社会、经济和国防等方面的应用回答:1. 数学文化的内涵:简单的说,是指数学的思想、精神、方法、观点,以及它们的形成和发展。

数学不应被等同于知识的简单汇集,而应主要地被看成是人类的一种活动;同时,由于数学不仅具有自己特殊的价值标准,更有着自己特殊的发展规律,因此数学应当被看作是整个人类文化的一个相对独立的子系统,当然,这并非是一个完全封闭的系统,恰恰相反,正是由于其内在力量和外部力量的共同作用直接决定了数学的发展和进化,我们也就更加确定了数学系统的开放性。

2. 对“数学”的定位和认识:有三点认识(1)数学不仅是一种重要的“工具”或“方法”,也是一种思维模式,即“数学方式的理性思维”;(2)数学不仅是一门科学,也是一种文化,即“数学文化”;(3)数学不仅是一些知识,也是一种素质,即“数学素质”。

3. 简述“数学素养”的通俗说法和专业说法:(1)通俗说法是,“把所学的数学知识都排除或忘掉后,剩下的东西”。

例如,从数学的角度看问题的出发点;有条理的思维,严密的思考、求证;简洁、清晰、准确地表达;在解决问题时、总结工作时,逻辑推理的意识和能力;对所从事的工作,合理地量化和简化,周到地运筹帷幄。

(2)专业说法是第一,主动探寻并善于抓住数学问题的背景和本质的素养;第二,熟练地用准确、简明、规范的数学语言表达自己数学思想的素养;第三,具有良好的科学态度和创新精神,合理地提出新思想、新概念、新方法的素养;第四,对各种问题以“数学方法”的理性思维,从多角度探寻解决问题的方法的素养;第五,善于对现实世界中的现象和过程进行合理的简化和量化,建立数学模型的素养。

数电大作业任务流水灯

综合设计题一.流水灯1.总体思路8位流水灯始终是一亮七暗的,根据这个特点可以考虑采用74LS138译码器的输出来实现流水灯的循环电路。

同时,还可以用74LS161四位二进制计数器来控制74LS138的输入端,从而实现对灯亮灭的控制2.使用元件3—8译码器74LS138,四位二进制计数器74LS161,555定时器,七段数码管译码器驱动器4511芯片,数码管,电容,电阻,非门若干。

3.电路原理框图4.元器件在本电路中的主要功能○1555定时器555 定时器在本电路中的作用主要是产生占空比可调的矩形脉冲从而可以改变灯亮时间,而且它的振荡周期为T=0.7(R1+2R2)C。

此处C=0.1uF.由电路参数可知,当R1为10kΩ时,灯亮时间为0.0014s.它的功能主要由两个比较器决定。

两个比较器的输出电压控制RS 触发器和放电管的状态。

在电源与地之间加上电压,当5 脚悬空时,则电压比较器C1的同相输入端的电压为2VCC /3,C2的反相输入端的电压为VCC /3。

若触发输入端TR 的电压小于VCC /3,则比较器C2的输出为0,可使RS 触发器置1,使输出端OUT=1。

如果阈值输入端TH 的电压大于2VCC/3,同时TR 端的电压大于VCC /3,则C1的输出为0,C2的输出为1,可将RS 触发器置0,使输出为0 电平。

电路图如下:○274LS161计数器74LS161计数器在本电路中的作用是产生000-111脉冲控制74LS138的A2A1A0,依次选通Y0-Y7。

产生脉冲序列也可以用74LS191是四位二进制同步加/减计数器,与74LS161相比,它能够实现减计数,此处只需要求产生脉冲序列,而且74LS161是常用的计数器,所以选择74LS161产生脉冲序列。

所以采用反馈置数法,产生000-111脉冲序号,时钟脉冲外部接入,原理图如下图所示○374LS138译码器74LS138译码器在本电路中的作用主要是选通指示灯发光。

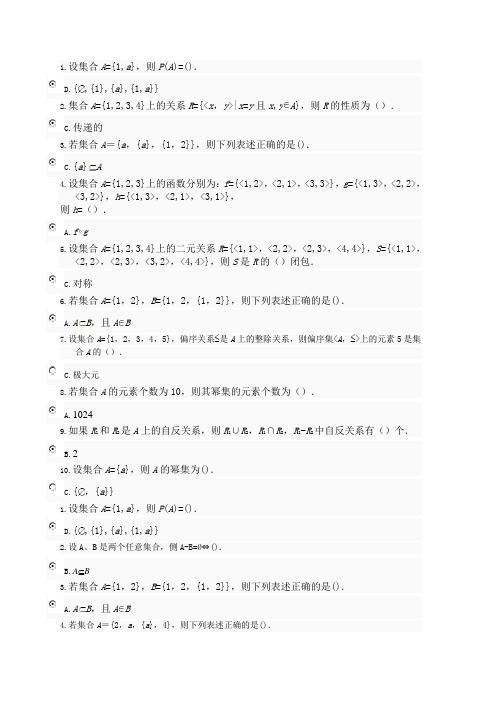

国家开放大学(电大)离散数学作业1集合论部分概念及性质

1.设集合A={1,a},则P(A)=().D.{,{1},{a},{1,a}}2.集合A={1,2,3,4}上的关系R={<x,y>|x=y且x,y A},则R的性质为().C.传递的3.若集合A={a,{a},{1,2}},则下列表述正确的是().C.{a}A4.设集合A={1,2,3}上的函数分别为:f={<1,2>,<2,1>,<3,3>},g={<1,3>,<2,2>,<3,2>},h={<1,3>,<2,1>,<3,1>},则h=().A.f◦g5.设集合A={1,2,3,4}上的二元关系R={<1,1>,<2,2>,<2,3>,<4,4>},S={<1,1>,<2,2>,<2,3>,<3,2>,<4,4>},则S是R的()闭包.C.对称6.若集合A={1,2},B={1,2,{1,2}},则下列表述正确的是().A.A B,且A B7.设集合A={1,2,3,4,5},偏序关系≤是A上的整除关系,则偏序集<A,≤>上的元素5是集合A的().C.极大元8.若集合A的元素个数为10,则其幂集的元素个数为().A.10249.如果R1和R2是A上的自反关系,则R1∪R2,R1∩R2,R1-R2中自反关系有()个.B.210.设集合A={a},则A的幂集为().C.{,{a}}1.设集合A={1,a},则P(A)=().D.{,{1},{a},{1,a}}2.设A、B是两个任意集合,侧A-B=Ø⇔().B.A⊆B3.若集合A={1,2},B={1,2,{1,2}},则下列表述正确的是().A.A B,且A B4.若集合A={2,a,{a},4},则下列表述正确的是().D.{a}⊆A5.集合A={1,2,3,4,5,6,7,8}上的关系R={<x,y>|x+y=10且x,y A},则R的性质为().B.对称的6.如果R1和R2是A上的自反关系,则R1∪R2,R1∩R2,R1-R2中自反关系有()个.B.27.设A={a,b,c},B={1,2},作f:A→B,则不同的函数个数为().D.88.设集合A={1,2,3,4,5},偏序关系≤是A上的整除关系,则偏序集<A,≤>上的元素5是集合A的().C.极大元9.若集合A的元素个数为10,则其幂集的元素个数为().A.102410.设A={a,b},B={1,2},C={4,5},从A到B的函数f={<a,1>,<b,2>},从B到C的函数g={<1,5>,<2,4>},则下列表述正确的是().B.g°f={<a,5>,<b,4>}1.设集合A={a},则A的幂集为().C.{,{a}}2.如果R1和R2是A上的自反关系,则R1∪R2,R1∩R2,R1-R2中自反关系有()个.B.23.设A={1,2,3,4,5,6,7,8},R是A上的整除关系,B={2,4,6},则集合B的最大元、最小元、上界、下界依次为().D.无、2、无、24.若集合A={a,{a},{1,2}},则下列表述正确的是().C.{a}A5.集合A={1,2,3,4}上的关系R={<x,y>|x=y且x,y A},则R的性质为().C.传递的6.设集合A={2,4,6,8},B={1,3,5,7},A到B的关系R={<x,y>|y=x+1},则R=().A.{<2,3>,<4,5>,<6,7>}7.设A、B是两个任意集合,侧A-B=Ø⇔().B.A⊆B8.设集合A={1,2,3,4}上的二元关系R={<1,1>,<2,2>,<2,3>,<4,4>},S={<1,1>,<2,2>,<2,3>,<3,2>,<4,4>},则S是R的()闭包.C.对称9.若集合A的元素个数为10,则其幂集的元素个数为().A.102410.设集合A={1,2,3}上的函数分别为:f={<1,2>,<2,1>,<3,3>},g={<1,3>,<2,2>,<3,2>},h={<1,3>,<2,1>,<3,1>},则h=().A.f◦g1.设函数f:N→N,f(n)=n+1,下列表述正确的是().D.f是单射函数2.设A={a,b,c},B={1,2},作f:A→B,则不同的函数个数为().D.83.设集合A={a},则A的幂集为().C.{,{a}}4.设A、B是两个任意集合,侧A-B=Ø⇔().B.A⊆B5.设集合A={1,2,3,4,5}上的偏序关系的哈斯图如右图所示,若A的子集B={3,4,5},则元素3为B的().B.最小上界6.如果R1和R2是A上的自反关系,则R1∪R2,R1∩R2,R1-R2中自反关系有()个.B.27.设集合A={1,2,3},B={3,4,5},C={5,6,7},则A∪B–C=().A.{1,2,3,4}8.设集合A={1,2,3,4}上的二元关系R={<1,1>,<2,2>,<2,3>,<4,4>},S={<1,1>,<2,2>,<2,3>,<3,2>,<4,4>},则S是R的()闭包.C.对称9.设集合A={1,a},则P(A)=().D.{,{1},{a},{1,a}}10.设A={a,b},B={1,2},C={4,5},从A到B的函数f={<a,1>,<b,2>},从B到C的函数g={<1,5>,<2,4>},则下列表述正确的是().B.g°f={<a,5>,<b,4>}1.设函数f:N→N,f(n)=n+1,下列表述正确的是().D.f是单射函数2.设集合A={a},则A的幂集为().C.{,{a}}3.设A={a,b},B={1,2},C={4,5},从A到B的函数f={<a,1>,<b,2>},从B到C的函数g={<1,5>,<2,4>},则下列表述正确的是().B.g°f={<a,5>,<b,4>}4.集合A={1,2,3,4}上的关系R={<x,y>|x=y且x,y A},则R的性质为().C.传递的5.设集合A={1,a},则P(A)=().D.{,{1},{a},{1,a}}6.设集合A={1,2,3,4,5},偏序关系≤是A上的整除关系,则偏序集<A,≤>上的元素5是集合A的().C.极大元7.若集合A={2,a,{a},4},则下列表述正确的是().D.{a}⊆A8.若集合A={a,{a},{1,2}},则下列表述正确的是().C.{a}A9.设A、B是两个任意集合,侧A-B=Ø⇔().B.A⊆B10.设集合A={2,4,6,8},B={1,3,5,7},A到B的关系R={<x,y>|y=x+1},则R=().A.{<2,3>,<4,5>,<6,7>}1.如果R1和R2是A上的自反关系,则R1∪R2,R1∩R2,R1-R2中自反关系有()个.B.22.设A、B是两个任意集合,侧A-B=Ø⇔().B.A⊆B3.设A={a,b},B={1,2},C={4,5},从A到B的函数f={<a,1>,<b,2>},从B到C的函数g={<1,5>,<2,4>},则下列表述正确的是().B.g°f={<a,5>,<b,4>}4.设集合A={2,4,6,8},B={1,3,5,7},A到B的关系R={<x,y>|y=x+1},则R=().A.{<2,3>,<4,5>,<6,7>}5.设集合A={1,2,3,4,5}上的偏序关系的哈斯图如右图所示,若A的子集B={3,4,5},则元素3为B的().B.最小上界6.设集合A={1,2,3}上的函数分别为:f={<1,2>,<2,1>,<3,3>},g={<1,3>,<2,2>,<3,2>},h={<1,3>,<2,1>,<3,1>},则h=().A.f◦g7.设集合A={1,2,3,4,5},偏序关系≤是A上的整除关系,则偏序集<A,≤>上的元素5是集合A的().C.极大元8.设A={1,2,3,4,5,6,7,8},R是A上的整除关系,B={2,4,6},则集合B的最大元、最小元、上界、下界依次为().D.无、2、无、29.若集合A={2,a,{a},4},则下列表述正确的是().D.{a}⊆A10.设集合A={1,a},则P(A)=().D.{,{1},{a},{1,a}}1.设集合A={1,2,3,4,5}上的偏序关系的哈斯图如右图所示,若A的子集B={3,4,5},则元素3为B的().B.最小上界2.若集合A={1,2},B={1,2,{1,2}},则下列表述正确的是().A.A B,且A B3.设集合A={a},则A的幂集为().C.{,{a}}4.设A={1,2,3,4,5,6,7,8},R是A上的整除关系,B={2,4,6},则集合B的最大元、最小元、上界、下界依次为().D.无、2、无、25.集合A={1,2,3,4,5,6,7,8}上的关系R={<x,y>|x+y=10且x,y A},则R的性质为().B.对称的6.设A、B是两个任意集合,侧A-B=Ø⇔().B.A⊆B7.设函数f:N→N,f(n)=n+1,下列表述正确的是().D.f是单射函数8.设A={a,b,c},B={1,2},作f:A→B,则不同的函数个数为().D.89.若集合A的元素个数为10,则其幂集的元素个数为().A.102410.设集合A={1,2,3}上的函数分别为:f={<1,2>,<2,1>,<3,3>},g={<1,3>,<2,2>,<3,2>},h={<1,3>,<2,1>,<3,1>},则h=().A.f◦g1.集合A={1,2,3,4,5,6,7,8}上的关系R={<x,y>|x+y=10且x,y A},则R的性质为().B.对称的2.设函数f:N→N,f(n)=n+1,下列表述正确的是().D.f是单射函数3.设集合A={1,2,3,4,5}上的偏序关系的哈斯图如右图所示,若A的子集B={3,4,5},则元素3为B的().B.最小上界4.设A={a,b,c},B={1,2},作f:A→B,则不同的函数个数为().D.85.设集合A={1,2,3}上的函数分别为:f={<1,2>,<2,1>,<3,3>},g={<1,3>,<2,2>,<3,2>},h={<1,3>,<2,1>,<3,1>},则h=().A.f◦g6.设A、B是两个任意集合,侧A-B=Ø⇔().B.A B7.若集合A={1,2},B={1,2,{1,2}},则下列表述正确的是().A.A B,且A B8.设集合A={1,2,3,4}上的二元关系R={<1,1>,<2,2>,<2,3>,<4,4>},S={<1,1>,<2,2>,<2,3>,<3,2>,<4,4>},则S是R的()闭包.C.对称9.若集合A={a,{a},{1,2}},则下列表述正确的是().C.{a}A10.若集合A={2,a,{a},4},则下列表述正确的是().1.若集合A={1,2},B={1,2,{1,2}},则下列表述正确的是().A.A B,且A B2.如果R1和R2是A上的自反关系,则R1∪R2,R1∩R2,R1-R2中自反关系有()个.B.23.设集合A={1,2,3,4}上的二元关系R={<1,1>,<2,2>,<2,3>,<4,4>},S={<1,1>,<2,2>,<2,3>,<3,2>,<4,4>},则S是R的()闭包.C.对称4.设A={a,b,c},B={1,2},作f:A→B,则不同的函数个数为().D.85.若集合A={2,a,{a},4},则下列表述正确的是().D.{a}⊆A6.设A={a,b},B={1,2},C={4,5},从A到B的函数f={<a,1>,<b,2>},从B到C的函数g={<1,5>,<2,4>},则下列表述正确的是().B.g°f={<a,5>,<b,4>}7.设A、B是两个任意集合,侧A-B=Ø⇔().B.A⊆B8.设集合A={1,2,3}上的函数分别为:f={<1,2>,<2,1>,<3,3>},g={<1,3>,<2,2>,<3,2>},h={<1,3>,<2,1>,<3,1>},则h=().A.f◦g9.设函数f:N→N,f(n)=n+1,下列表述正确的是().D.f是单射函数10.集合A={1,2,3,4,5,6,7,8}上的关系R={<x,y>|x+y=10且x,y A},则R的性质为().B.对称的1.设集合A={2,4,6,8},B={1,3,5,7},A到B的关系R={<x,y>|y=x+1},则R=().A.{<2,3>,<4,5>,<6,7>}2.设A={a,b},B={1,2},C={4,5},从A到B的函数f={<a,1>,<b,2>},从B到C的函数g={<1,5>,<2,4>},则下列表述正确的是().B.g°f={<a,5>,<b,4>}3.若集合A={2,a,{a},4},则下列表述正确的是().D.{a}⊆A4.设集合A={1,2,3}上的函数分别为:f={<1,2>,<2,1>,<3,3>},g={<1,3>,<2,2>,<3,2>},h={<1,3>,<2,1>,<3,1>},则h=().A.f◦g5.设A、B是两个任意集合,侧A-B=Ø⇔().B.A⊆B6.设集合A={1,2,3,4,5},偏序关系≤是A上的整除关系,则偏序集<A,≤>上的元素5是集合A的().C.极大元7.设集合A={a},则A的幂集为().C.{,{a}}8.如果R1和R2是A上的自反关系,则R1∪R2,R1∩R2,R1-R2中自反关系有()个.B.29.若集合A的元素个数为10,则其幂集的元素个数为().A.102410.集合A={1,2,3,4,5,6,7,8}上的关系R={<x,y>|x+y=10且x,y A},则R的性质为().B.对称的单项选择题题目1设函数f:N→N,f(n)=n+1,下列表述正确的是().正确答案是:f是单射函数题目2设集合A={1,2,3},B={3,4,5},C={5,6,7},则A∪B–C=().正确答案是:{1,2,3,4}题目3若集合A的元素个数为10,则其幂集的元素个数为().正确答案是:1024题目4设集合A={1,a},则P(A)=().正确答案是:{,{1},{a},{1,a}}题目5集合A={1,2,3,4}上的关系R={<x,y>|x=y且x,y A},则R的性质为().正确答案是:传递的题目6设集合A={1,2,3,4,5},偏序关系是A上的整除关系,则偏序集<A,>上的元素5是集合A的().正确答案是:极大元题目7设A={a,b},B={1,2},C={4,5},从A到B的函数f={<a,1>,<b,2>},从B到C的函数g={<1,5>,<2,4>},则下列表述正确的是().正确答案是:g°f={<a,5>,<b,4>}题目8集合A={1,2,3,4,5,6,7,8}上的关系R={<x,y>|x+y=10且x,y A},则R的性质为().正确答案是:对称的题目10正确设集合A={1,2,3,4,5}上的偏序关系的哈斯图如图所示,若A的子集B={3,4,5},则元素3为B的().正确答案是:最小上界题目11设A={1,2,3},R={<1,1>,<1,2>,<2,1>,<3,3>},则R是等价关系.()正确的答案是“错”。

电大数据库运维作业一

数据库运维作业一一、单项选择题(每题2分,共60分)1. 数据库系统的核心是()。

A. 数据库B.数据库管理员C.数据库管理系统D.计算机软硬件系统2. 数据库(DB)、数据库系统(DBS)和数据库管理系统(DBMS)三者之间的关系是()。

A. DBS 包括 DB 和 DBMSB. DBMS 包括 DB 和 DBSC. DB包括DBS和DBMSD. DBS包括DB,也就是DBMS3. 在文件管理方式中,数据处于一种()的状态。

A.集中B.集体化C.分散D.链接4. 以下不属于数据库特点的是()。

A. 数据共享B.数据冗余度高C.数据集中控制D.数据独立性高5. 对数据库特征的描述不准确的是()。

A. 数据具有独立性B.数据结构化C.数据集中控制D,数据没有冗余6. mysqladmin command参数中删除一个库的参数是()。

A. delete [DB_NAME]B. drop [DB_NAME]C. drop database [ DB_NAME ]D. delete database [ DB_NAME ]7. MySQL二进制日志binlog的作用是记录MySQL内部()的内容。

A.增删改B.查询 selectC.显ZK showD.异常 exception8. mysqlbinlog中使用参数()可以打开指定库的binlog文件。

A, —d B. —r C. —h D. —u9. MySQL数据库中使用命令行工具()可以有效地对记录进行归档。

A. mysqldumpB. mysqladminC. mysqlbinlogD. percona toolkit10. 在MySQL可视化管理工具MySQL GUI Tools中,方便数据库迁移的图形化应用程序是()。

A. MySQL AdministratorB. MySQL Migration ToolkitC. MySQL Query BrowserD. MySQL Workbench11. MySQL使用的默认端口是()。

数电大作业--2.5分频

3

• 由于对于所得信号要实现一个半周期的延 时,准备用触发器实现延时功能,而且延时

后的信号是下降沿触发的,所以经思考后, 采用两个D触发器实现两个周期的延时,一 个JK触发器实现下降沿触发。对于JK触发器,

将表达式化成触发器输入的标准表达式, 有 JQ2,KQ2

2021/6/16

4

仿真电路图

2021/6/16

5

仿真结果2021/6/16 Nhomakorabea6

结束语

若有不当之处,请指正,谢谢!

2021/6/16

2

实际采用的方案

• 经老师在课上对2.5分频介绍,并且给出一 种思路后,我接着老师的思路给出了如下 方案。

• 在学习扭环计数器的时候,在理解了其置 数的设计原理后,根据其其中一位输出四 低四高的电平特点,设计置数电路实现了 比较独特的“每五个周期有一个周期高电 平”的电路。

2021/6/16

数电第一次大作业---2.5分频

2021/6/16

1

思考过程

• 最初不知道2.5分频到底是个什么概念,到 网上查了一些资料后发现有先实现倍频再 实现分频的说法,于是最开始 准备先实现

2倍频再实现5分频来实现2.5分频。具体思 路是对时钟信号进行延时,再与时钟信号 异或可实现2倍频,再用扭环计数器实现5 分频。但是延时电路具体的实现令我煞费 脑筋,不得以准备用n个非门来实现基于器 件本身的延时,但本方案被老师否决。

形考作业1答案(高等数学基础电大形考作业一)

0高等数学基础形考作业1答案:第1章 函数 第2章 极限与连续(一)单项选择题⒈下列各函数对中,(C )中的两个函数相等. A. 2)()(x x f =,x x g =)( B. 2)(x x f =,x x g =)(C. 3ln )(x x f =,x x g ln 3)(= D. 1)(+=x x f ,11)(2--=x x x g分析:判断函数相等的两个条件(1)对应法则相同(2)定义域相同 A、2()f x x ==,定义域{}|0x x ≥;x x g =)(,定义域为R 定义域不同,所以函数不相等; B、()f x x ==,x x g =)(对应法则不同,所以函数不相等;C 、3()ln 3ln f x x x ==,定义域为{}|0x x >,x x g ln 3)(=,定义域为{}|0x x > 所以两个函数相等D 、1)(+=x x f ,定义域为R ;21()11x g x x x -==+-,定义域为{}|,1x x R x ∈≠ 定义域不同,所以两函数不等。

故选C⒉设函数)(x f 的定义域为),(+∞-∞,则函数)()(x f x f -+的图形关于(C )对称. A. 坐标原点 B. x 轴 C. y 轴 D. x y = 分析:奇函数,()()f x f x -=-,关于原点对称偶函数,()()f x f x -=,关于y 轴对称()y f x =与它的反函数()1y f x -=关于y x =对称,奇函数与偶函数的前提是定义域关于原点对称设()()()g x f x f x =+-,则()()()()g x f x f x g x -=-+=所以()()()g x f x f x =+-为偶函数,即图形关于y 轴对称故选C⒊下列函数中为奇函数是(B ).A. )1ln(2x y +=B. x x y cos =C. 2x x a a y -+= D. )1ln(x y +=分析:A 、()()()()22ln(1)ln 1y x x x y x -=+-=+=,为偶函数B 、()()()cos cos y x x x x x y x -=--=-=-,为奇函数 或者x 为奇函数,cosx 为偶函数,奇偶函数乘积仍为奇函数C 、()()2x xa a y x y x -+-==,所以为偶函数D 、()ln(1)y x x -=-,非奇非偶函数 故选B⒋下列函数中为基本初等函数是(C ). A. 1+=x y B. x y -=C. 2xy = D. ⎩⎨⎧≥<-=0,10,1x x y分析:六种基本初等函数(1) y c =(常值)———常值函数(2) ,y x αα=为常数——幂函数 (3) ()0,1xy aa a =>≠———指数函数(4) ()log 0,1a y x a a =>≠———对数函数(5) sin ,cos ,tan ,cot y x y x y x y x ====——三角函数(6) [][]sin ,1,1,cos ,1,1,tan ,cot y arc x y arc x y arc x y arc x=-=-==——反三角函数分段函数不是基本初等函数,故D 选项不对 对照比较选C⒌下列极限存计算不正确的是(D ).A. 12lim 22=+∞→x x xB. 0)1ln(lim 0=+→x xC. 0sin lim=∞→x x x D. 01sin lim =∞→xx x分析:A 、已知()1lim 00n x n x→∞=>2222222211lim lim lim 1222101x x x x x x x x x x x→∞→∞→∞====++++B 、0limln(1)ln(10)0x x →+=+=初等函数在期定义域内是连续的C 、sin 1limlim sin 0x x x x xx →∞→∞==x →∞时,1x是无穷小量,sin x 是有界函数,无穷小量×有界函数仍是无穷小量D 、1sin1lim sin lim1x x x x x x→∞→∞=,令10,t x x =→→∞,则原式0sin lim 1t t t →== 故选D⒍当0→x 时,变量(C )是无穷小量.A.x x sin B. x 1C. xx 1sin D. 2)ln(+x分析;()lim 0x af x →=,则称()f x 为x a →时的无穷小量A 、0sin lim1x xx →=,重要极限B 、01lim x x→=∞,无穷大量C 、01lim sin 0x x x →=,无穷小量x ×有界函数1sin x仍为无穷小量D 、()0limln(2)=ln 0+2ln 2x x →+=故选C⒎若函数)(x f 在点0x 满足(A ),则)(x f 在点0x 连续。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

数电作业课程名称:数字电子技术基础课程时间:2015年秋授课教师:康磊学生姓名:XXX学生班级:学生学号:联系电话:哈尔滨工业大学英才学院2015年12月大作业一一、设计目的利用Verilog HDL设计一个电路,使其可以检测输入的一段由二进制数组成的序列,若序列中有连续的三个或者三个以上的1,则电路下一个时钟到来时输出为1,否则为0。

状态转换图如图所示。

二、设计步骤1、安装ISE14.2,并学会如何仿真。

2、根据状态图编写verilog程序。

3、仿真并生成仿真波形图。

4、保存项目并完成报告。

三、程序源代码1、主程序`timescale 1ns / 1psmodule shudian1(clk,rst,din,out);input clk,rst,din;output out;reg[2:1] y, Y;reg out;parameter A=2'b00,B=2'b01,C=2'b10,D=2'b11;always @(posedge clk or negedge rst)beginif(!rst)y <= A;elsey <= Y;endalways@(y or din) begincase(y)A: beginout = 0;if(din) Y=B;else Y=A;endB: beginout = 0;if(din) Y=C;else Y=A;endC: beginout = 0;if(din) Y=D;else Y=A;endD: beginout = 1;if(din) Y=D;else Y=A;enddefault:beginout = 0;Y = A;endendcaseendendmodule2、测试程序`timescale 1ns / 1ps module sudian11;// Inputsreg clk;reg rst;reg [20:0]data;assign din=data[20];// Outputswire out;// Instantiate the Unit Under Test (UUT)shudian1 uut (.clk(clk),.rst(rst),.din(din),.out(out));initialbeginrst = 0;#200 rst = 1;endinitialbeginclk = 0;endalwaysbegin#50 clk=~clk;endinitialbegindata=20'b10110111011110101101;endalways @(posedge clk)#2 data ={data[19:0],data[20]};endmodule四、仿真波形图将仿真时间设为1.5us,我们可以看到如下波形图。

可以看出,当输入信号有连续的三个或者三个以上的1,则电路输出在下一个时钟到来变为1,否则为0,且电路为Moore型,输出是当前状态的函数。

大作业二一、设计目的利用Verilog HDL设计一个电路,使其可以检测输入的一段由二进制数组成的序列,若序列中有连续的三个或者三个以上的1,则电路立刻输出为1,否则为0。

状态转换图如图所示。

二、设计步骤1、根据状态图编写verilog程序。

2、仿真并生成仿真波形图。

3、保存项目并完成报告。

三、程序源代码1、主程序`timescale 1ns / 1psmodule shudian2(clk , w , rst , z);input clk, rst, w;output z;reg z;reg [1:0] y, Y;parameter A=2'b00, B=2'b01,C=2'b10;always @ (posedge clk or negedge rst)beginif(!rst)y = A;elsey <= Y;endalways @(w or y)begincase(y)A: beginif(!w)beginY = A;z = 0;endelsebeginY = B;z = 0;endendB: beginif(!w)beginY = A;z = 0;endelsebeginY = C;z = 0;endendC: beginif(!w)beginY = A;z = 0;endelsebeginY = C;z = 1;endenddefault:beginz = 0;Y = A;endendcaseendendmodule2、测试程序`timescale 1ns / 1psmodule shudian22;reg clk;reg rst;reg [20:0]data;assign w=data[20];wire z;// Instantiate the Unit Under Test (UUT) shudian2 uut (.clk(clk),.w(w),.rst(rst),.z(z));initial beginrst = 0;#200; rst=1;endinitial beginclk=0;endalwaysbegin#50 clk=~clk;endinitialbegindata=20'b10110111011110110101;endalways @(posedge clk)#2 data ={data[19:0],data[20]};endmodule四、仿真波形图将仿真时间设为1.5us,我们可以看到如下波形图。

可以看出,当输入信号有连续的三个或者三个以上的1,电路输出立刻为1,否则为0,电路为Mealy型,输出是当前状态和输入的函数。

大作业三一、设计目的利用Verilog HDL设计一个模为学号后三位(408)的同步加减法计数器,使其当输入X为0时立即执行加计数,当X为1时立即执行减计数。

二、设计步骤1、根据状态图编写verilog程序。

2、仿真并生成仿真波形图。

3、保存项目并完成报告。

三、程序源代码1、主程序`timescale 1ns / 1psmodule shudian3(clk,rst,out,X);input clk,rst;input X;output reg[8:0]out=0;parameter A=0,B=1;always @(posedge clk or X)case(X)A:beginif(!rst) out <= 0;else if(out>=407) out<=0;else out <= out+1;endB:beginif(!rst) out <= 0;else if(!out) out<=407;else out <= out-1;endendcaseendmodule2、测试程序`timescale 1ns / 1psmodule shudian33;reg clk;reg rst;reg X;wire [8:0] out;// Instantiate the Unit Under Test (UUT)shudian3 uut (.clk(clk),.rst(rst),.out(out),.X(X));parameter PERIOD = 2;always beginclk = 1'b0;#(PERIOD/2) clk = 1'b1;#(PERIOD/2);endinitial beginclk = 0;rst = 0;X = 0;#100;rst = 1;begin#1000;X=~X;endendendmodule四、仿真波形图1.当rst为1时,开始计数。

X=0时进行加计数2.当X=0时进行加计数,且模为408。

3. 当X=1时进行减计数。

4.当X=1时进行减计数,且模为408。

可以看出,这个同步加减法计数器完美的完成了加计数和减计数功能。