DDR内存时序设置详解

内存时序的调节

-2T拥有较久的延迟、差很多的系统内存较能。较高的兼容性、稳定性。推荐将内存设定为1T能让内存达到最佳效能。

12.对于BIOS中内存时序部分未提及的几项参数,一般设为AUTO即可。

以上是对参数的解释,在说明调节参数的细节之前,我想声明几点:

1.内存性能最重要的标志就是它的频率,相比之下内存时序显得并不是那么重要,适当调节的确会有提升,但是不会像调节频率来的那么明显。当然作为一个DIY爱好者,榨干系统的每一分性能才是最终目标。这里一个评测大家可以参考下,[ /157/1570442.html此网页不属于本网站,不保证其安全性 继续访问 取消 不再提示我 /157/1570442.html 传送门 ]

上面已经说过,当内存频率提高,特别是过了标称值的时候,就需要以增加内存小参值为代价。

(1)若你内存工作的频率是小于等于你的内存标称值的,那么可以认为你的内存工作时序可以至少跑到标称的水平,比如我选择的内存在1600频率之下,先设定内存时序为7-7-7 1T,其他AUTO,若能成功进入系统并且通过memory test,那说明你的内存时序是OK的,我当时貌似是7-7-7-24-5-89 1T,那接下来继续缩小部分参数值(注意:一个一个调整,一元变量和多元变量的道理),比如设定7-7-7-21(20)1T,看能否稳定,依旧是进系统,测试(重复枯燥的劳动,所以说需要耐心...)若能稳定,那就继续,比如7-7-7-21(20)-5-60 1T,这个我没能成功;若不能稳定就略微的加小参值,比如7-8-7-21(20),以此类推找到稳定的最小值。

内存时序的调节

由于CPU外频锁定在200(倍频20),那么对于我所选用的内存条,根据几种既定的频率比(FSB:RAM)比较合适的频率为:1600(2:8)和2000(2:10)。

发个我自己的图, [ /cache/banner/1027841.png ]

,如图可以看到内存在1600频率下时序为7-7-7-20 1T(7-7-7-20-5-89

1T),个人建议主要调整前6个参数值,其它的参考之前的解释微调,或者直接AUTO。

1.DRAM CAS Latency(tCL):内存CAS

Latency是指“内存读写操作前列地址控制器的潜伏时间”,该参数设置对内存带宽影响较大,数值越小内存性能越高,反之越低,内存运行频率越高该参数通常需要设置越大,根据DDR3内存体质不同,保守设置通常是7-9,也可根据自己内存体质设置不同的Cl值。

上面已经说过,当内存频率提高,特别是过了标称值的时候,就需要以增加内存小参值为代价。

(1)若你内存工作的频率是小于等于你的内存标称值的,那么可以认为你的内存工作时序可以至少跑到标称的水平,比如我选择的内存在1600频率之下,先设定内存时序为7-7-7

1T,其他AUTO,若能成功进入系统并且通过memory test,那说明你的内存时序是OK的,我当时貌似是7-7-7-24-5-89

11.DRAM Timing

Mode:内存首命令延迟设定用选项,对内存性能影响较大,放宽到2N(2T)可适当提升内存超频频率,通常设置为1N(1T)。

-1T拥有较少的延迟,较佳的系统内存效能。却较差的兼容性。

-2T拥有较久的延迟、差很多的系统内存较能。较高的兼容性、稳定性。推荐将内存设定为1T能让内存达到最佳效能。

ddr时序

DDR 内存既然叫做双倍速率SDRAM(Dual date rate SDRSM),就是说是SDRAM的升级换代产品。

从技术上分析,DDR SDRAM最重要的改变是在界面数据传输上,其在时钟信号上升缘与下降缘时各传输一次数据,这使得DDR的数据传输速率为传统SDRAM的两倍。

那么大家就应该知道了,我们所说的DDR400,DDR333,DDR266,他们的工作频率其实仅为那些数值的一半,也就是说DDR400工作频率为200MHz。

FSB与内存频率的关系首先请大家看看表一:FSB(Front Side Bus:前端总线)和内存比率与内存实际运行频率的关系。

FSB/MEM比率实际运行频率1/01200MHz1/02100MHz2/03133MHz3/04150MHz3/05120MHz5/06166MHz7/10140MHz9/10180MHz对于大多数玩家来说,FSB和内存同步,即1:1(DFI 用1/01表示)是使性能最佳的选择。

而其他的设置都是异步的。

同步后,内存的实际运行频率是FSBx2,所以,DDR400的内存和200MHz的FSB正好同步。

如果你的FSB为240MHz,则同步后,内存的实际运行频率为240MHz x 2 = 480MHz。

表2更详尽列出了FSB与不同速度的DDR内存之间正确的设置关系强烈建议采用1:1的FSB与内存同步的设置,这样可以完全发挥内存带宽的优势。

Command Per Clock(CPC)可选的设置:Auto,Enable(1T),Disable(2T)。

Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。

由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。

这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。

DDR工作原理与时序(详细且准确版----以DDR3为例)

DDR工作原理与时序(详细且准确版----以DDR3为例)2015-07-08 by mbmlccking168一、内存工作流程首先,我们先了解一下内存的大体结构工作流程,这样会比较容量理解这些参数在其中所起到的作用。

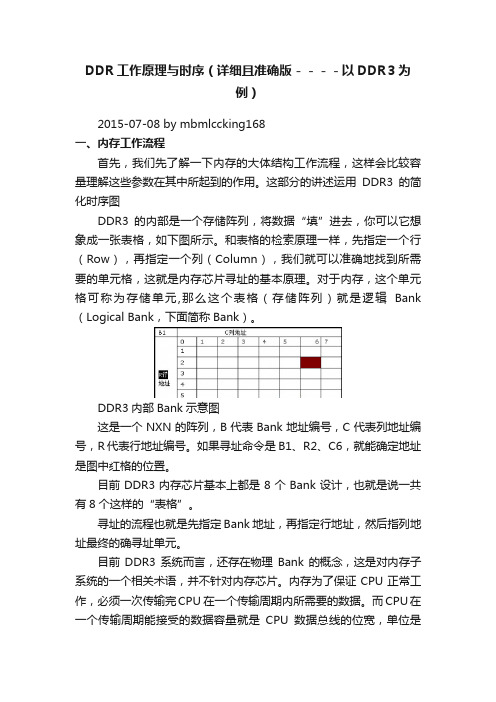

这部分的讲述运用DDR3的简化时序图DDR3的内部是一个存储阵列,将数据“填”进去,你可以它想象成一张表格,如下图所示。

和表格的检索原理一样,先指定一个行(Row),再指定一个列(Column),我们就可以准确地找到所需要的单元格,这就是内存芯片寻址的基本原理。

对于内存,这个单元格可称为存储单元,那么这个表格(存储阵列)就是逻辑Bank (Logical Bank,下面简称Bank)。

DDR3内部Bank示意图这是一个NXN的阵列,B代表Bank地址编号,C代表列地址编号,R代表行地址编号。

如果寻址命令是B1、R2、C6,就能确定地址是图中红格的位置。

目前DDR3内存芯片基本上都是8个Bank设计,也就是说一共有8个这样的“表格”。

寻址的流程也就是先指定Bank地址,再指定行地址,然后指列地址最终的确寻址单元。

目前DDR3系统而言,还存在物理Bank的概念,这是对内存子系统的一个相关术语,并不针对内存芯片。

内存为了保证CPU正常工作,必须一次传输完CPU 在一个传输周期内所需要的数据。

而CPU在一个传输周期能接受的数据容量就是CPU数据总线的位宽,单位是bit(位)。

控制内存与CPU之间数据交换的北桥芯片也因此将内存总线的数据位宽等同于CPU数据总线的位宽,这个位宽就称为物理Bank (Physical Bank,有的资料称之为Rank)的位宽。

目前这个位宽基本为64bit。

在实际工作中,Bank地址与相应的行地址是同时发出的,此时这个命令称之为“行激活”(Row Active)。

在此之后,将发送列地址寻址命令与具体的操作命令(是读还是写),这两个命令也是同时发出的,所以一般都会以“读/写命令”来表示列寻址。

ddr 时序参数

ddr 时序参数DDR(Double Data Rate)时序参数是指DDR存储器的时序特性,包括时钟速度、时钟周期、数据传输速率等。

DDR时序参数的优化是提高DDR存储器性能的关键。

本文将从时钟速度、时钟周期和数据传输速率三个方面介绍DDR时序参数的优化方法。

一、时钟速度时钟速度是DDR存储器工作频率的表征,通常以MHz为单位。

提高时钟速度可以加快DDR存储器的数据传输速率,从而提高系统的整体性能。

然而,时钟速度的提高也会带来一些问题,比如信号完整性的降低和功耗的增加。

为了克服这些问题,可以采取以下优化方法:1. 选择高质量的时钟发生器和时钟信号线,确保时钟信号的稳定性和准确性。

2. 使用低延迟的时钟布线技术,减小时钟信号的传输延迟。

3. 合理设计时钟分配网络,避免时钟偏移和时钟抖动。

二、时钟周期时钟周期是DDR存储器时序参数中的另一个重要指标,它表示数据在一个时钟周期内的传输时间。

时钟周期越短,数据传输速率越高。

为了优化时钟周期,可以采取以下方法:1. 减小时钟延迟:通过优化时钟信号的传输路径和布线方式,减小时钟信号的传输延迟。

2. 优化时钟分配:合理设计时钟分配网络,避免时钟偏移和时钟抖动,确保时钟信号的稳定传输。

3. 优化时钟缓冲:选择合适的时钟缓冲器,减小时钟信号的驱动能力,以提高时钟信号的传输速度。

三、数据传输速率数据传输速率是DDR存储器的重要性能指标,它表示DDR存储器单位时间内能传输的数据量。

提高数据传输速率可以提高系统的数据处理能力。

为了优化数据传输速率,可以采取以下方法:1. 提高总线带宽:通过增加数据总线的宽度,提高数据传输的并行性,从而提高数据传输速率。

2. 优化数据线布局:合理布置数据线,减小数据线的长度和电容负载,降低传输延迟和功耗。

3. 优化数据驱动电路:选择高速、低功耗的数据驱动电路,提高数据传输速率的同时降低功耗。

DDR时序参数的优化是提高DDR存储器性能的关键。

DDR2内存时序调节方法

DDR2内存时序调节方法DDR2内存已经成为目前绝大部分用户的标配产品,而如何合理设置DDR2的参数就成为了不少用户(尤其是菜鸟用户)的最想了解的地方。

当你超频的时候,如何平衡内存频率和参数之间的关系;究竟如何合理选取内存频率,什么参数才是带来最高性能呢?相信这些问题是目前最多用户最想了解。

其实要了解这些东西,首先要明白DDR2内存在BIOS中的参数设置情况。

因为要提高系统整体性能,并不只是简单超频CPU外频,调高内存频率这么简单,将一大堆数字合理地分配和组合才是最为重要的。

目前市场上销售的DDR2内存主要按频率来划分,譬如DDR2 533、DDR2 667、DDR2 800就是消费者最常见的产品(注:部分厂商推出DDR2 1000高频DDR2内存,但这些DDR2内存在市场上并不多见,而价格昂贵,所以我们就暂时不讨论一些超频型DDR2内存)。

在这三款内存产品当中,就数DDR2 667内存最为多人购买,因为它同时具备了性能、价格、兼容性这些特点,而DDR2 533已经逐步被DDR2 667所取代。

如果您的内存为镁光D9颗粒,请直接参考本站《镁光小D9内存超频调教全攻略》,如果您是DDR内存,请参考本站《教你如何调整DDR内存参数》至于目前频率较高DDR2 800也逐渐成为玩家购买的对象,因为Intel双核心平台对高频DDR2内存有着极大需求,要发挥酷睿2最大威力,一条高频率、可运行高参数的DDR2内存是非常重要的。

鉴于AMD AM2处理器内置了DDR2内存控制器,所以AM2平台的DDR2设置方法与Intel平台有着不同。

最稳当的DDR2内存设置方法,就是在主板BIOS当中将DDR2的设置参数设为By SPD,而这个选项也是最安全的DDR2内存设置方法。

不过这个设置最大缺点是,没有将内存的潜力发挥出来,只是用安全换来相对较低的性能。

如果你想超频手中的DDR2,那么By SPD选项将不是你的设置的地方,手动调整才是你的手段。

ddr4时序参数

ddr4时序参数(原创版)目录1.DDR4 时序参数简介2.DDR4 时序参数的组成3.DDR4 时序参数的作用4.DDR4 时序参数的调整5.总结正文一、DDR4 时序参数简介DDR4(Double Data Rate 4)是第四代内存模块的标准,具有更高的数据传输速率和更低的功耗。

在 DDR4 内存模块中,时序参数是一个重要的概念,它直接影响到内存模块的性能。

二、DDR4 时序参数的组成DDR4 时序参数主要包括以下几个部分:1.延迟(Delay):延迟是指内存模块在接收到读写请求后,需要等待的时间。

它包括 tDQ(数据传输延迟)、tRCD(行到列延迟)、tRP(预充电延迟)等。

2.插槽(Row)和列(Column):插槽和列是指内存模块中的存储单元。

插槽是指内存模块的物理排列方式,列是指存储单元的物理位置。

在 DDR4 中,每个插槽可以包含多个列。

3.读写操作(Read and Write Operations):DDR4 时序参数还包括读写操作的相关参数,如 tRD(读取延迟)、tWR(写入延迟)等。

三、DDR4 时序参数的作用DDR4 时序参数对于内存模块的性能至关重要。

它们决定了内存模块在执行读写操作时所需的时间,直接影响到系统的运行速度和效率。

正确的时序参数设置可以提高内存模块的稳定性和性能,而错误的设置可能导致系统崩溃或性能下降。

四、DDR4 时序参数的调整为了获得最佳的性能,需要根据实际硬件和应用需求,合理调整 DDR4 时序参数。

通常,可以通过主板的 BIOS 或内存控制器的软件工具进行调整。

调整时序参数需要一定的专业知识和技巧,不当的调整可能导致系统不稳定或性能下降。

五、总结DDR4 时序参数是内存模块性能的关键因素,它包括延迟、插槽和列、读写操作等参数。

合理的时序参数设置可以提高内存模块的稳定性和性能,而不当的设置可能导致系统崩溃或性能下降。

ddr工作原理与时序

ddr工作原理与时序

DDR(Double Data Rate双倍数据速率)是一种现代的动态随

机存取存储器(DRAM)的接口标准,它具有高带宽、高存

储密度和低功耗等特点。

DDR内部工作原理和时序如下:

工作原理:

1. 内存芯片初始时处于“等待指令”的状态,等待控制器发送读写指令。

2. 控制器向内存芯片发送读或写指令,并同时传输地址信息。

3. 内存芯片接收到指令和地址后,开始进行操作(读取或写入数据),并将结果通过数据线传输给控制器。

时序:

1. 内存芯片上电复位后,需要一定的初始化时间来使其进入正常工作状态。

这个时间称为Power On Reset(POR)时间。

2. 初始化完成后,内存芯片开始从控制器接收和发送数据。

DDR在每个时钟周期内进行一次数据传输,一个时钟周期称

为一个Bus Clock周期。

3. 周期开始时,控制器向内存芯片发送指令,同时传输地址信息。

这个阶段称为命令和地址传输阶段(Command/Address Transfer Phase)。

4. 在下一个时钟周期,内存芯片进行操作(读取或写入数据),并将结果通过数据线传输给控制器。

这个阶段称为数据传输阶段(Data Transfer Phase)。

5. 所有数据传输完成后,内存芯片等待下一次指令。

DDR的主要特点是在一个Bus Clock周期内进行两次数据传输,

即上升沿和下降沿都传输一次数据,从而达到双倍数据速率的效果。

同时,DDR还采用了预取和乱序传输等技术来提高数据传输效率。

ddr3 标准时序

ddr3 标准时序DDR3标准时序。

DDR3是一种电脑内存标准,它采用了高速的时序设计,以实现更快的数据传输速度。

在本文中,我们将深入探讨DDR3标准时序的相关知识,包括时序参数的意义、常见的时序设置以及时序优化的方法。

首先,我们需要了解DDR3时序参数的含义。

时序参数是指内存模块在进行读写操作时,各种信号的时序要求。

这些参数包括CAS延迟(CL)、RAS到CAS延迟(tRCD)、预充电时间(tRP)、行前置时间(tRAS)等。

这些参数的设置直接影响着内存的性能和稳定性。

接下来,我们来看一些常见的DDR3时序设置。

在实际应用中,我们通常会遇到一些常见的时序设置,比如CL9-9-9-24、CL11-11-11-30等。

这些数字分别代表了CAS延迟、RAS到CAS延迟、预充电时间和行前置时间。

一般来说,时序参数越小,内存的性能就越好,但也会增加内存稳定性方面的挑战。

除了常见的时序设置外,我们还可以通过一些方法来优化DDR3的时序。

例如,可以通过提高内存电压来改善内存稳定性,从而允许更加激进的时序设置。

此外,还可以通过超频技术来提高内存时序的性能,不过这需要谨慎操作,以免损坏硬件或降低系统稳定性。

总的来说,DDR3标准时序对于内存的性能和稳定性至关重要。

合理的时序设置可以提高内存的读写速度,从而提升整个系统的性能。

然而,过于激进的时序设置可能会导致内存稳定性问题,甚至损坏硬件。

因此,在设置DDR3时序参数时,需要权衡性能和稳定性,选择合适的时序设置,并且谨慎进行时序优化。

综上所述,DDR3标准时序是内存性能优化中至关重要的一环。

合理的时序设置和优化可以提升系统性能,但需要谨慎操作,以免影响系统稳定性。

希望本文对于DDR3标准时序的理解能够帮助读者更好地应用和优化内存,提升系统性能。

内存时序设置(DRAM Configuration) - 七彩虹 C_P35 X3 Ver2_0 说明书使用手册 - IT168

sdram precharge delay(sdram 内存预充电延迟)

此项控制s d r a m 内存时钟周期数的r a s 最小值。

sdram twr

选择dram 登录最后一笔写入数据后的写入回复时间,即最后一笔写入数据之后的预充电时间。

sdram trfc

该字段用于选择自动刷新周期时间。

sdram twtr

选项为reserved, 1 bus clock, 2 bus clocks 与3 bus clocks

sdram trrd

选择不同b a n k 的列与列间的延迟时间。

clocks, 7 bus clocks

sdram ras# precharge(trp)

指定row 预备时间.预先激活或自动更新相同的bank. 通常为20-24nsec。

选项: 3 bus clocks (默认), 2 bus clocks, 4 bus clocks, 5bus clocks, 6 bus

内存时序设置(DRAM Configuration) - 七彩虹 C.P35 X3 Ver2.0 说明书|使用手册 - IT168

内存时序设置(DRAM Configuration)

非专业人士请不要随意更改选项内的设置!

Hale Waihona Puke dram timing selectable(动态记忆体时序选择)

u,则此字段不会出现。auto 自动侦测内存时钟。

1t 为较佳性能的时钟设定。

2t 为一般性能的时钟设定,提供较佳的系统稳定性。此选项为默认值。

七彩虹 C.P35 X3 Ver2.0 相关内容:报价 | 参数 | 图片 | 论坛 | 评测

内存时序的概念和设置

一:CAS Latency(简称CL值)内存CAS延迟时间,他是内存的重要参数之一,某些牌子的内存会把CL值印在内存条的标签上。

二:RAS-to-CAS Delay(tRCD),内存行地址传输到列地址的延迟时间。

在一些技术文章里介绍内存设置时序参数时,一般数字“A-B-C-D”分别对应的参数是“CL-tRCD-tRP-tRAS”,现在你该明白“2-3-3-6”是什么意思了吧?!^_^下面就这几个参数及BIOS设置中影响内存性能的其它参数逐一给大家作一介绍: 一、内存延迟时序“CL-tRCD-tRP-tRAS”的设置 首先,需要在BIOS中打开手动设置,在BIOS设置中找到“DRAM Timing Selectable”,BIOS设置中可能出现的其他描述有:Automatic Configuration、DRAM Auto、Timing Selectable、Timing Configuring By SPD等,将其值设为“Menual”(视BIOS的不同可能的选项有:On/Off或Enable/Disable),如果要调整内存时序,应该先打开手动设置,之后会自动出现详细的时序参数列表: Command Per Clock(CPC) 可选的设置:Auto,Enable(1T),Disable(2T)。 Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。 显然,也是越短越好。但当随着

ddr4时序参数

ddr4时序参数DDR4(第四代双数据率同步动态随机存取存储器)是一种常见的计算机内存标准,它定义了一系列时序参数,用于控制内存模块的数据传输和存储操作。

以下是一些常见的DDR4时序参数及其中文解释:1. CL(CAS Latency):数据存取延迟时间,表示存储器从接收到读取请求到开始提供数据之间的时间。

CL的值越小,存储器性能越好。

2. tRCD(RAS to CAS Delay):行激活到列激活延迟时间,表示在激活行之后,等待多长时间才能激活列。

tRCD的值越小,性能越好。

3. tRP(Row Precharge Time):行激活到行预充电延迟时间,表示在关闭一行之前,等待多长时间。

tRP的值越小,性能越好。

4. tRAS(Row Active Time):行激活时间,表示行保持激活状态的时间。

tRAS的值越小,性能越好。

5. tRC(Row Cycle Time):行循环时间,表示在执行完一个行激活到下一个行激活之间的时间。

tRC的值越小,性能越好。

6. tWR(Write Recovery Time):写恢复时间,表示在写入数据后,等待多长时间才能进行下一次写入。

tWR的值越小,性能越好。

7. tRRD(Row to Row Delay):行到行延迟时间,表示在激活一行后,再次激活相邻行之间的延迟。

tRRD的值越小,性能越好。

8. tWTR(Write to Read Delay):写入到读取延迟时间,表示在写入数据后,切换到读取操作之间的延迟。

tWTR的值越小,性能越好。

请注意,这些时序参数的具体值取决于内存模块的规格和制造商的设计。

在选择内存时,你可能需要根据系统需求和性能要求来调整这些参数。

内存超频时序设置参数

内存超频时序设置参数

内存超频时序设置是一项比较高级的操作,需要了解一定的电脑硬件知识和技能,因此在进行内存超频时序设置之前,需要先备份重要的数据和系统文件。

以下是内存超频时序设置参数的中文说明:

1. 内存频率:即DDR3、DDR4等内存频率设置,一般情况下选择最高频率即可。

2. CAS时序:CAS时序是指列寻址延迟时间,一般情况下,越小越好,但是太小会影响内存稳定性。

4. 时序1、时序2、时序3:这三个参数是内存超频时序设置中比较重要的参数,需要根据硬件配置和软件环境进行调整。

5. Command Rate:即指写入时序,一般情况下选择较低值即可,但也要考虑内存稳定性。

6. DRAM Voltage:即内存电压,一般情况下,可以适当增加电压提升内存频率和运行稳定性。

但是过高的电压也会损坏内存条和主板等硬件。

7. Termination Voltage:即终端电压,也是一个比较重要的参数,对内存超频和运行稳定性都有较大的影响。

总之,在进行内存超频时序设置之前,需要充分了解自己的硬件配置和软件环境,同时也要不断地进行实验和测试,以确保内存超频设置的稳定性和安全性。

内存参数DDR怎么优化

内存参数DDR怎么优化 电脑内存少导致运⾏变慢,那如何对内存参数进⾏优化设置呢?下⾯是店铺为⼤家介绍内存参数DDR优化的⽅法,欢迎⼤家阅读。

优化内存的延迟参数对PC性能的提⾼有很⼤帮助。

优化内存是通过调节BIOS中⼏个内存时序参数来实现的。

内存参数DDR优化的⽅法 ⼀、内存延迟时序“CL-tRCD-tRP-tRAS”的设置 ⾸先,需要在BIOS中打开⼿动设置,在BIOS设置中找到“DRAM Timing Selectable”,BIOS设置中可能出现的其他描述有:Automatic Configuration、DRAM Auto、Timing Selectable、Timing Configuring By SPD等,将其值设为“Menual”(视BIOS的不同可能的选项有:On/Off或Enable/Disable),如果要调整内存时序,应该先打开⼿动设置,之后会⾃动出现详细的时序参数列表: 1、CL(CAS Latency):“内存读写操作前列地址控制器的潜伏时间”(可能的选项:1.5/2/2.5/3) BIOS中可能的其他描述为:tCL、CAS Latency Time、CAS Timing Delay。

这个参数很重要,内存条上⼀般都有这个参数标记。

在BIOS设置中DDR内存的CAS参数选项通常有“1.5”、“2”、“2.5”、“3”⼏种选择,SDRAM则只有“2”、“3”两个选项。

较低的CAS周期能减少内存的潜伏周期以提⾼内存的⼯作效率。

因此只要能够稳定运⾏操作系统,我们应当尽量把CAS参数调低。

反过来,如果内存运⾏不稳定,可以将此参数设⼤,以提⾼内存稳定性。

2、tRCD(RAS-to-CAS Delay)“⾏寻址⾄列寻址延迟时间”(可能的选项:2/3/4/5) BIOS中的可能其他描述: tRCD、RAS to CAS Delay、Active to CMD等。

数值越⼩,性能越好。

ddr时序原理

ddr时序原理DDR时序原理DDR(Double Data Rate)是一种常见的内存技术,它能够在每个时钟周期中传输两次数据,提高了内存的数据传输速率。

DDR的时序原理是指内存控制器与内存芯片之间的数据传输时序关系。

本文将对DDR时序原理进行详细介绍。

一、时钟信号与时钟周期在DDR中,时钟信号是内存控制器与内存芯片之间进行数据传输的基础。

时钟信号以一定的频率产生,并且规定了内存控制器和内存芯片在每个时钟周期内进行数据传输的时间间隔。

时钟周期是指时钟信号的一个完整周期,可以用来衡量数据传输的速度。

二、时序参数DDR的时序参数是指内存控制器与内存芯片之间进行数据传输时所需要遵守的一系列时间要求。

常见的时序参数包括:tCK、tRCD、tRP、tRAS、tRRD、tWR、tWTR等。

1. tCK(Clock Cycle Time):时钟周期时间,用来衡量内存控制器与内存芯片之间的数据传输速度。

tCK越小,数据传输速度越快。

2. tRCD(Row to Column Delay):行到列延迟时间,指内存芯片从接收到行地址到能够响应列地址的时间。

tRCD越小,内存芯片响应速度越快。

3. tRP(Row Precharge Time):行预充电时间,指内存芯片在进行行地址切换之前需要等待的时间。

tRP越小,内存芯片切换行地址的速度越快。

4. tRAS(Row Active Time):行激活时间,指内存芯片保持在激活状态的时间。

tRAS越小,内存芯片可以更快地响应读写请求。

5. tRRD(Row to Row Delay):行到行延迟时间,指内存芯片在进行行地址切换时,需要等待的时间。

tRRD越小,内存芯片切换行地址的速度越快。

6. tWR(Write Recovery Time):写恢复时间,指内存芯片在写入数据后需要等待的时间,以保证写操作的稳定性。

tWR越小,内存芯片写入数据的速度越快。

7. tWTR(Write to Read Delay):写到读延迟时间,指内存芯片在从写操作切换到读操作时需要等待的时间。

内存时序以及内存时序优化

谈内存时序以及内存时序优化原创作者:不抬杠最近看到一些网友对内存频率的重要性争论不休,认为内存频率不重要的,只能说对电脑运行的工作原理不了解,对超频知识不了解。

内存的实质是随时写入/读取存储器,是一种高速存储器。

CPU不能直接读取硬盘内的数据进行计算,那么硬盘的数据就要通过内存来实现和CPU之间的交换,所有的程序运行时候都要调入到内存里才能进一步交换给CPU计算。

如果内存速度(频率)低,会直接影响到内存与CPU进行数据交换的速度,因此影响到整体的计算速度。

内存频率虽然重要,内存时序优化也很重要。

如果内存时序调校得不好,就算CPU体质再好,频率一样上不去。

在主板BIOS设置中,有以下几个重要的内存时序参数:1. DRAM Command Rate(CMD Rate)这个参数表示“首命令延迟”。

该参数的单位是时钟周期,越小越好。

不过,当内存较多且系统工作不太稳定时,要将此参数调大。

在K8主板上,CMD Rate 的选项有Auto、1T或2T。

品质好一点的内存模组可以使用1T来提高性能,大部分主板为了保证更好的兼容性,默认采用了2T的保守值。

2. CAS# Latency(tCL)CAS表示“列地址选通脉冲”,在内存寻址后,系统必须等待列地址信号CAS 才能开始进行数据传输,CL就是列地址脉冲的反应时间,它是衡量内存品质的重要参数之一。

通常DDR2内存的tCL=4/5/6,在稳定的前提下,数值越低越好。

3. RAS to CAS Delay(tRCD)该参数表示“行寻址至列寻址延迟时间”,这个参数主要影响带宽和稳定性,数值越小越好。

在超频时大部分内存在设定为5以上时会改善不少稳定性。

4. Row Precharge Timing(tRP)该参数表示“行位址预充电时间”,即内存从结束一个行存取操作到重新开始下次操作的间隔时间。

和tRCD类似,tRP也主要影响带宽和稳定性,数值也是越小越好。

5. Minimum RAS Active Timing(tRAS)该参数表示“从行激活到预充电开始程序之间的最小时钟周期”,即从收到一个请求后到初始化RAS并真正接收数据的间隔时间。

ddr4时序参数

ddr4时序参数DDR4时序参数是指DDR4内存模块的时序要求和参数设置,包括CAS 延迟(CL)、RAS到CAS延迟(RCD)、RAS预充电延迟(RP)、行到行延迟(TRCD)、行到列延迟(TRP)、写入延迟(TWR)等。

CAS延迟(CL)是指列地址选择到数据有效的延迟时间。

它是内存模块从接收到读取请求到开始输出数据的延迟时间。

较低的CAS延迟意味着内存能够更快地响应读取请求,提高内存读取性能。

RAS到CAS延迟(RCD)是指行地址选择到列地址选择之间的延迟时间。

它表示内存模块在接收到读取请求后,需要多久才能开始进行列地址选择。

较低的RCD能够减少内存访问的等待时间,提高内存读取性能。

RAS预充电延迟(RP)是指行地址选择到预充电命令之间的延迟时间。

RP参数表示内存模块在进行行地址选择后,需要等待多久才能开始进行预充电操作。

较低的RP能够缩短内存访问的等待时间,提高内存读取性能。

行到行延迟(TRCD)是指在不同行之间进行切换所需的延迟时间。

TRCD参数表示内存模块在进行行地址选择后,需要等待多久才能开始进行下一行的行地址选择。

较低的TRCD能够减少内存访问的等待时间,提高内存读取性能。

行到列延迟(TRP)是指在同一行中进行列地址选择所需的延迟时间。

TRP参数表示内存模块在进行行地址选择后,需要等待多久才能开始进行列地址选择。

较低的TRP能够减少内存访问的等待时间,提高内存读取性能。

写入延迟(TWR)是指内存模块接收到写入请求后,需要等待多久才能开始进行写入操作的延迟时间。

较低的TWR能够缩短内存写入的等待时间,提高内存写入性能。

DDR4时序参数是影响内存读取和写入性能的重要因素。

通过调整这些参数,可以提高内存的响应速度和数据传输效率。

不同的应用场景和需求可能需要不同的时序参数设置,因此在选择和配置内存模块时,需要根据实际情况进行合理的选择和调整。

同时,还需要注意内存模块和主板的兼容性,确保时序参数的稳定性和可靠性。

内存时序怎么设置

内存时序怎么设置虽然店铺从小就对看书感兴趣,可是让我看一本完全不了解的书可是一点都看不下去,学知识也是一样,自己喜欢的不用别人督促,就能把它学的很好很扎实,自己不喜欢的学科呢,就要逼着自己学,而且效果并不好,兴趣是最好的老师,不过正在上学还没高考的可要认真学习每一门功课,考上大学后再选择一个自己喜欢的专业。

内存时序设置店铺是看不懂,相信总有人会明白的。

内存时序设置内存参数的设置正确与否,将极大地影响系统的整体性能。

下面我们将针对内存关于时序设置参数逐一解释,以求能让大家在内存参数设置中能有清晰的思路,提高电脑系统的性能。

涉及到的参数分别为:CPC : Command Per ClocktCL : CAS Latency ControltRCD : RAS to CAS DelaytRAS : Min RAS Active TimingtRP : Row Precharge TimingtRC : Row Cycle TimetRFC : Row Refresh Cycle TimetRRD : Row to Row Delay(RAS to RAS delay)tWR : Write Recovery Time……及其他参数的设置首先,需要在BIOS中打开手动设置,在BIOS设置中找到“DRAM Timing Selectable”,BIOS设置中可能出现的其他描述有:Automatic Configuration、DRAM Auto、Timing Selectable、Timing Configuring By SPD等,将其值设为“Menual”(视BIOS的不同可能的选项有:On/Off或Enable/Disable),如果要调整内存时序,应该先打开手动设置,之后会自动出现详细的时序参数列表:CPC : Command Per Clock可选的设置:Auto,Enable(1T),Disable(2T)。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

内存时序设置详解内容概要关键词:内存时序参数设置导言:是否正确地设置了内存时序参数,在很大程度上决定了系统的基本性能。

本文详细介绍了内存时序相关参数的基本涵义及设置要点。

与传统的SDRAM相比,DDR(Dual date rate SDRSM:双倍速率SDRAM),最重要的改变是在界面数据传输上,其在时钟信号上升缘与下降缘时各传输一次数据,这使得DDR 的数据传输速率为传统SDRAM的两倍。

同样地,对于其标称的如DDR400,DDR333,DDR266数值,代表其工作频率其实仅为那些数值的一半,也就是说DDR400 工作频率为200MHz。

FSB与内存频率的关系首先请大家看看FSB(Front Side Bus:前端总线)和内存比率与内存实际运行频率的关系。

FSB/MEM比率实际运行频率1/1 200MHz1/2 100MHz2/3 133MHz3/4 150MHz3/05 120MHz5/6 166MHz7/10 140MHz9/10 180MHz对于大多数玩家来说,FSB和内存同步,即1:1是使性能最佳的选择。

而其他的设置都是异步的。

同步后,内存的实际运行频率是FSBx2,所以,DDR400的内存和200MHz的FSB正好同步。

如果你的FSB为240MHz,则同步后,内存的实际运行频率为240MHz x 2 = 480MHz。

FSB与不同速度的DDR内存之间正确的设置关系强烈建议采用1:1的FSB与内存同步的设置,这样可以完全发挥内存带宽的优势。

内存时序设置内存参数的设置正确与否,将极大地影响系统的整体性能。

下面我们将针对内存关于时序设置参数逐一解释,以求能让大家在内存参数设置中能有清晰的思路,提高电脑系统的性能。

涉及到的参数分别为:∙CPC : Command Per Clock∙tCL : CAS Latency Control∙tRCD : RAS to CAS Delay∙tRAS : Min RAS Active Timing∙tRP : Row Precharge Timing∙tRC : Row Cycle Time∙tRFC : Row Refresh Cycle Time∙tRRD : Row to Row Delay(RAS to RAS delay)∙tWR : Write Recovery Time∙……及其他参数的设置CPC : Command Per Clock可选的设置:Auto,Enable(1T),Disable(2T)。

Command Per Clock(CPC:指令比率,也有翻译为:首命令延迟),一般还被描述为DRAM Command Rate、CMD Rate等。

由于目前的DDR内存的寻址,先要进行P-Bank的选择(通过DIMM上CS片选信号进行),然后才是L-Bank/行激活与列地址的选择。

这个参数的含义就是指在P-Bank选择完之后多少时间可以发出具体的寻址的L-Bank/行激活命令,单位是时钟周期。

显然,CPC越短越好。

但当随着主板上内存模组的增多,控制芯片组的负载也随之增加,过短的命令间隔可能会影响稳定性。

因此当你的内存插得很多而出现不太稳定的时间,才需要将此参数调长。

目前的大部分主板都会自动设置这个参数。

该参数的默认值为Disable(2T),如果玩家的内存质量很好,则可以将其设置为Enable(1T)。

tCL : CAS Latency Control(tCL)可选的设置:Auto,1,1.5,2,2.5,3,3.5,4,4.5。

一般我们在查阅内存的时序参数时,如“3-4-4-8”这一类的数字序列,上述数字序列分别对应的参数是“CL-tRCD-tRP-tR AS”。

这个3就是第1个参数,即CL参数。

CAS Latency Control(也被描述为tCL、CL、CAS Latency Time、CAS Timing Delay),CAS latency是“内存读写操作前列地址控制器的潜伏时间”。

CAS控制从接受一个指令到执行指令之间的时间。

因为CAS主要控制十六进制的地址,或者说是内存矩阵中的列地址,所以它是最为重要的参数,在稳定的前提下应该尽可能设低。

内存是根据行和列寻址的,当请求触发后,最初是tRAS(Activeto Precharge Delay),预充电后,内存才真正开始初始化RAS。

一旦tRAS激活后,RAS(Row Address Strobe )开始进行需要数据的寻址。

首先是行地址,然后初始化tRCD,周期结束,接着通过CAS 访问所需数据的精确十六进制地址。

期间从CAS开始到CAS结束就是CAS延迟。

所以CAS是找到数据的最后一个步骤,也是内存参数中最重要的。

这个参数控制内存接收到一条数据读取指令后要等待多少个时钟周期才实际执行该指令。

同时该参数也决定了在一次内存突发传送过程中完成第一部分传送所需要的时钟周期数。

这个参数越小,则内存的速度越快。

必须注意部分内存不能运行在较低的延迟,可能会丢失数据,因此在提醒大家把CAS延迟设为2或 2.5的同时,如果不稳定就只有进一步提高它了。

而且提高延迟能使内存运行在更高的频率,所以需要对内存超频时,应该试着提高CAS延迟。

该参数对内存性能的影响最大,在保证系统稳定性的前提下,CAS值越低,则会导致更快的内存读写操作。

CL值为2为会获得最佳的性能,而CL值为3可以提高系统的稳定性。

注意,WinbondBH-5/6芯片可能无法设为3。

tRCD : RAS to CAS Delay可选的设置:Auto,0,1,2,3,4,5,6,7。

该值就是“3-4-4-8”内存时序参数中的第2个参数,即第1个4。

RAS to CAS Delay(也被描述为:tRCD、RAS to CAS Delay、Active to CMD),表示"行寻址到列寻址延迟时间",数值越小,性能越好。

对内存进行读、写或刷新操作时,需要在这两种脉冲信号之间插入延迟时钟周期。

在JEDEC规范中,它是排在第二的参数,降低此延时,可以提高系统性能。

建议该值设置为3或2,但如果该值设置太低,同样会导致系统不稳定。

该值为4时,系统将处于最稳定的状态,而该值为5,则太保守。

如果你的内存的超频性能不佳,则可将此值设为内存的默认值或尝试提高tRCD值。

tRAS : Min RAS Active Timing可选的设置:Auto,00,01,02,03,04,05,06,07,08,09,10,11,12,13,14,15。

该值就是该值就是“3-4-4-8”内存时序参数中的最后一个参数,即8。

Min RAS Active Time (也被描述为:tRAS、Active to Precharge Delay、Row Active Time、Precharge Wait State、Row Active Delay、Row Precharge Delay、RAS Active Time),表示“内存行有效至预充电的最短周期”,调整这个参数需要结合具体情况而定,一般我们最好设在5-10之间。

这个参数要根据实际情况而定,并不是说越大或越小就越好。

如果tRAS的周期太长,系统会因为无谓的等待而降低性能。

降低tRAS周期,则会导致已被激活的行地址会更早的进入非激活状态。

如果tRAS 的周期太短,则可能因缺乏足够的时间而无法完成数据的突发传输,这样会引发丢失数据或损坏数据。

该值一般设定为CAS latency + tRCD + 2个时钟周期。

如果你的CAS latency的值为2,tRCD的值为3,则最佳的tRAS 值应该设置为7个时钟周期。

为提高系统性能,应尽可能降低tRAS的值,但如果发生内存错误或系统死机,则应该增大tRAS的值。

tRP : Row Precharge Timing(tRP)可选的设置:Auto,0,1,2,3,4,5,6,7。

该值就是“3-4-4-8”内存时序参数中的第3个参数,即第2个4。

Row Precharge Timing (也被描述为:tRP、RAS Precharge、Precharge to active),表示"内存行地址控制器预充电时间",预充电参数越小则内存读写速度就越快。

tRP用来设定在另一行能被激活之前,RAS需要的充电时间。

tRP参数设置太长会导致所有的行激活延迟过长,设为2可以减少预充电时间,从而更快地激活下一行。

然而,想要把tRP设为2对大多数内存都是个很高的要求,可能会造成行激活之前的数据丢失,内存控制器不能顺利地完成读写操作。

对于桌面计算机来说,推荐预充电参数的值设定为2个时钟周期,这是最佳的设置。

如果比此值低,则会因为每次激活相邻紧接着的bank将需要1个时钟周期,这将影响DDR内存的读写性能,从而降低性能。

只有在tRP值为2而出现系统不稳定的情况下,将此值设定为3个时钟周期。

一般说来,tRP值建议2-5之间的值。

值为2将获取最高的性能,该值为4将在超频时获取最佳的稳定性,同样的而该值为5,则太保守。

大部分内存都无法使用2的值,需要超频才可以达到该参数。

tRC : Row Cycle Time(tRC)可选的设置:Auto,7-22,步幅值1。

Row Cycle Time(tRC、RC),表示“SDRAM行周期时间”,它是包括行单元预充电到激活在内的整个过程所需要的最小的时钟周期数。

其计算公式是:row cycle time (tRC) = minimum row active time(tRAS) + row precharge time(tRP)。

因此,设置该参数之前,你应该明白你的tRAS值和tRP值是多少。

如果tRC的时间过长,会因在完成整个时钟周期后激活新的地址而等待无谓的延时,而降低性能。

然后一旦该值设置过小,在被激活的行单元被充分充电之前,新的周期就可以被初始化。

在这种情况下,仍会导致数据丢失和损坏。

因此,最好根据tRC = tRAS + tRP进行设置,如果你的内存模块的tRAS值是7个时钟周期,而tRP的值为4个时钟周期,则理想的tRC的值应当设置为11个时钟周期。

tRFC : Row Refresh Cycle Time可选的设置:Auto,9-24,步幅值1。

Row Refresh Cycle Time(tRFC、RFC),表示“SDRAM行刷新周期时间”,它是行单元刷新所需要的时钟周期数。

该值也表示向相同的bank中的另一个行单元两次发送刷新指令(即:REF指令)之间的时间间隔。

tRFC值越小越好,它比tRC的值要稍高一些。

通常tRFC的值不能达到9,而10为最佳设置,17-19是内存超频建议值。