实验 触发器设计

钟控d触 发器设计实验原理

钟控d触发器设计实验原理

钟控D触发器是数字集成电路中的一种重要组成部分,它由六个与非门组成,包括两个基本的RS触发器、时钟控制电路和数据输入电路。

当不向D触发器施加任何时钟输入或在时钟信号的负边沿(下降沿)期间,输出不会发生变化,它将在输出Q处保留其先前的值。

如果时钟信号为高

电平(更准确地说是上升沿/正边沿)并且如果D输入为高电平,则输出也

为高电平,如果D输入为低电平,则输出将变为低的。

因此,在存在时钟

信号的情况下,输出Q跟随输入D。

此外,D触发器也称为维持-阻塞边沿D触发器,由三个SR NAND锁存器构成。

输入级由两个锁存器组成,输出级由一个锁存器组成。

在输入级,数据输入连接到其中的一个NAND锁存器,时钟信号(CLK)并行连接到两

个SR锁存器。

以上内容仅供参考,如需更准确全面的信息,建议查阅相关的专业书籍或咨询专业人士。

实验六JK触发器的VHDL设计

实验六JK触发器的VHDL设计实验六JK触发器的VHDL设计设计JK触发器,其中prn(置1端)、clrn(清零端)均为⾼电平有效,当prn(置1端)、clrn(清零端)均为低电平时,cp上升沿来临输出q、q_not根据J、K的值有不同的输出。

library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity chufa_JK isport(cp,j,k,prn,clrn:in std_logic;q,q_not: out std_logic);end chufa_JK;architecture arch of chufa_JK issignal qn:std_logic;beginprocess(cp,prn,clrn)beginif clrn='1'and prn='0' then ----------异步(强制)置0qn<='0';elsif prn='1'and clrn='0'then ---------异步(强制)置1qn<='1';elsif cp'event and cp='1' then ---------cp上升沿qn<=(j and not qn) or(not k and qn);end if;end process;q<=qn;q_not<=not qn;end arch;1、波形仿真分析注意:此JK触发器设计中prn(置1端)、clrn(清零端)均为⾼电平有效,当prn(置1端)、clrn(清零端)均为低电平时,cp上升沿来临输出q、q_not根据J、K的值有不同的输出。

注意与课本JK触发器功能表的区分。

触发器实验报告

触发器实验报告一、实验目的本次触发器实验的主要目的是深入了解触发器的工作原理、功能特性以及在数字电路中的应用。

通过实际操作和观察,掌握触发器的基本概念,熟悉其逻辑功能和时序特性,为后续更复杂的数字电路设计和分析打下坚实的基础。

二、实验设备与器材1、数字电路实验箱2、示波器3、逻辑分析仪4、若干集成电路芯片,包括 D 触发器、JK 触发器等三、实验原理(一)D 触发器D 触发器是一种在时钟脉冲上升沿或下降沿触发的触发器。

当 D 输入端的数据在时钟脉冲作用下被传输到输出端 Q。

其逻辑表达式为:Q(n+1) = D 。

(二)JK 触发器JK 触发器具有置 0、置 1、保持和翻转四种功能。

当 J = 1,K = 0 时,触发器置 1;当 J = 0,K = 1 时,触发器置 0;当 J = K = 0 时,触发器保持原态;当 J = K = 1 时,触发器翻转。

其逻辑表达式为:Q(n+1) = JQ' + K'Q 。

四、实验内容与步骤(一)D 触发器功能测试1、按照实验电路图在数字电路实验箱上连接好 D 触发器芯片。

2、将 D 输入端分别接高电平和低电平,通过示波器观察时钟脉冲和输出端 Q 的波形,记录实验结果。

(二)JK 触发器功能测试1、依照实验电路图搭建 JK 触发器的实验电路。

2、分别设置 J、K 输入端的不同组合,观察并记录输出端 Q 的状态变化。

(三)触发器的级联1、将多个 D 触发器或 JK 触发器级联,形成移位寄存器。

2、输入串行数据,观察移位寄存器的输出结果。

五、实验数据与结果分析(一)D 触发器实验结果当 D 输入端接高电平时,在时钟脉冲上升沿,输出端 Q 变为高电平;当 D 输入端接低电平时,在时钟脉冲上升沿,输出端 Q 变为低电平。

这与 D 触发器的逻辑功能相符,验证了其正确性。

(二)JK 触发器实验结果在不同的 J、K 输入组合下,JK 触发器的输出端 Q 呈现出置 1、置0、保持和翻转的状态,与理论预期完全一致。

实验二D触发器的设计和仿真

告报验实哈尔滨工程大学教务处制实验二D触发器的设计和仿真一、实验目的1、学习模拟数字电路单元的基本设计方法。

2、学习Cadence工具下电路设计的基本操作和方法。

3、学习Sprectre工具的仿真操作方法。

二、实验内容. . . .本实验通过设计一个异步清零的D触发器电路学习Cadence工具下电路的设计和仿真方法。

实验内容包括:完成反相器、与非门、传输门电路的设计和仿真验证;完成各个单元电路symbol的建立;利用建立的单元电路symbol完成D触发器电路的设计和仿真;分析仿真结果。

该电路设计采用上华CSMC0.5umCMOS工艺设计,工作电压5V。

三、实验步骤、登陆到UNIX系统。

1在登陆界面,输入用户名和密码,用户名和密码都为学生学号。

2、Cadence的启动。

启动Cadence软件的命令有很多,不同的启动命令可以启动不同的工具集,常用的启动命令有icfb,icca等,也可以单独启动单个工具。

3、原理图的输入。

(1)Composer的启动。

在CIW窗口新建一个单元的Schematic视图。

(2)添加器件。

在comparator schematic窗口点击Add-Instance 或者直接点i,就可以选择所需的器件。

(3)添加连线。

执行Add-Wire,将需要连接的部分用线连接起来。

(4)添加管脚。

执行Add-Pin和直接点p,弹出添加管脚界面。

(5)添加线名。

为设计中某些连线添加有意义的名称有助于在 . . . . 波形显示窗口中显出该条线的信号名称,也可以帮助检查电路错误。

点击Add-Wire Name,弹出新窗口,为输入输出线添加名称。

为四端的MOS器件的衬底添加名称vdd!或gnd!,其中!表示全局变量。

(6)添加电源信号。

选择Vdd和Gnd的symbol各一个,在两个symbol 之间连接一个vdc,设置直流电压5V。

(6)保存并检查。

点击schematic窗口上的Check and Save按钮,察看是否有警告或者错误。

D触发器设计

数字逻辑实验报告试验一 D触发器设计姓名:班级:学号:同组人:1、系统需求PC 个人计算机ISE14.2软件D.V文件D.UCF 文件USB下载线Adept软件开发板Basys22、实验内容:接线:NET "CP" LOC = N3;NET "D" LOC = E2;NET "Q" LOC = G1;NET "QN" LOC = P4;NET "RD" LOC = F3;NET "SD" LOC = G3;3、实验目的:当你完成整个项目之后,你将学会以下的功能.(1)利用ISE14.2的软件开启一个Spartan3E的项目.(2)撰写一个简单的Schematic原理图,利用语法检查器(Syntax Check)来修正语法的错误(3)产生测试模板(Test Bench) 来辅助你的设计.(4)加入系统所需的Constraints 文件.(UCF file)(5)完成整个设计流程.并产生D.bit文件。

(6)利用Adept软件来烧录D.bit文件到FPGA.4、实验过程4.1 新建工程(1)开启ISE14.2软件: 开始→程序→Xilinx ISE Design Suite 14.2→ISE→Project Navigator(2)在ISE14.2软件环境下,开启一个新的工程: File→New Project.[Project Name] :D[Project Location]: E:\Training\training_demo\Verilog\D (依使用者设定的目录).[Top-Level Module Type] : Schematic( 代表最上层的设计模块是以Schematic输方方式的模组.4.2 创建新的Schematic源4.2.1 创建一个新的Schematic源文件(1)此时出现一个项目的架构,可以允许使用者开始进行项目的设计.(2)创建新的设计文件: Project→New Source;选择Schematic Module,并设定文件名称为D(3)点击next,出现New Source Wizard,选择Schematic方式,文件名为“TOP”。

实验报告 触发器

实验报告触发器实验报告:触发器引言:触发器是数字电路中常见的重要元件,它可以存储和控制信号的传输。

本实验旨在通过实际搭建触发器电路,了解其工作原理和应用。

一、实验目的本实验的目的是通过实际搭建触发器电路,掌握触发器的工作原理、特性和应用。

二、实验器材和原理2.1 实验器材:- 电路实验板- 电源- 电压表- 电流表- 逻辑门芯片- 连接线2.2 实验原理:触发器是一种存储器件,可以存储和控制信号的传输。

它由多个逻辑门组成,根据输入信号的不同,可以分为RS触发器、D触发器、JK触发器和T触发器等多种类型。

三、实验步骤3.1 搭建RS触发器电路首先,将两个逻辑门芯片连接在电路实验板上,一个作为RS触发器的输入端,另一个作为输出端。

然后,将电源和适当的电阻连接到逻辑门芯片上,以提供所需的电压和电流。

最后,根据电路图连接连线,搭建完整的RS触发器电路。

3.2 检验和调试电路在搭建好电路后,使用电压表和电流表检验电路的电压和电流是否正常。

如果有异常,需要及时排除故障。

然后,通过改变输入信号,观察输出信号的变化。

根据实验结果,对电路进行调试,确保触发器的正常工作。

3.3 测试触发器的特性在调试完电路后,可以进行一些实验来测试触发器的特性。

例如,可以通过改变输入信号的频率和占空比,观察输出信号的变化。

还可以通过改变逻辑门芯片的类型,比较不同类型触发器的性能差异。

四、实验结果和分析通过实验,我们可以得到触发器的工作特性和性能数据。

根据实验结果,我们可以分析触发器的优缺点,以及在数字电路设计中的应用。

五、实验总结触发器作为数字电路中的重要元件,在现代电子技术中得到了广泛应用。

通过本实验,我们深入了解了触发器的工作原理、特性和应用。

同时,我们也学会了搭建触发器电路、调试电路和分析实验结果的方法。

六、实验心得通过本次实验,我深刻认识到了触发器在数字电路中的重要性。

触发器可以存储和控制信号的传输,是数字电路中的核心部件之一。

触发器设计实验的心得体会

触发器设计实验的心得体会触发器是数字电路中一种重要的组件,它可以在特定的时刻检测输入信号,并产生相应的输出信号。

在进行触发器设计的实验中,我学到了许多宝贵的经验和知识。

以下是我对这次实验的心得体会:首先,在实验之前,我对触发器的工作原理进行了充分的了解。

触发器是一种存储器件,它可以在时钟的边缘沿(上升沿或下降沿)时对输入值进行检测,并在满足特定条件时改变输出状态。

通过深入研究触发器的工作原理,我能够更好地理解实验中使用的各种触发器电路。

其次,在实验过程中,我意识到了设计的重要性。

触发器的设计需要考虑许多因素,如输入和输出的电压范围、时钟频率、逻辑功能等。

在设计触发器电路时,我需要根据具体的要求和限制,选择正确的逻辑门、电子元件和布局,以确保电路的性能和可靠性。

此外,我还学会了使用仿真软件进行电路设计和验证,这在实验之后的分析和修正中起到了很大的帮助作用。

此外,我还注意到了实验过程中的一些常见问题。

例如,触发器输入信号的时序关系可能会对电路的正确性产生影响。

一些特定的触发器类型,如JK触发器和D触发器,需要特定的输入信号序列来改变状态。

若输入信号的时序有误,可能导致触发器无法按预期的方式工作。

因此,在实验中,我学会了仔细检查信号的时序和电平,以确保触发器按照设计的逻辑来工作。

另外,我还学到了电路性能评估和优化的重要性。

触发器的性能可以通过多个参数进行评估,如响应时间、噪声容限、功耗等。

在实验中,我学会了使用性能评估工具来量化电路的性能,并通过调整电路结构、参数和时钟频率等方法来优化触发器设计。

这个过程不仅提高了我对触发器电路性能的理解,还培养了我的分析和问题解决能力。

最后,这次实验让我明白了团队合作的重要性。

触发器设计并非一项单独的任务,它通常需要多个人的协作和配合。

在实验中,我和我的同学一起合作,共同讨论问题、设计电路和进行实验。

通过团队合作,我们能够共享知识和经验,相互帮助和支持,最终完成了一个优秀的触发器设计实验。

触发器实验报告

触发器实验报告触发器实验报告引言触发器是数字电路中常用的组合逻辑电路,用于储存和记忆数据,并实现时序逻辑功能。

本实验通过实验板上的电路元件和电路模块,设计和配置不同类型的触发器电路,实现相应的功能,并加深对触发器的原理和应用的理解。

一、实验目的1. 理解触发器的工作原理;2. 掌握触发器的设计和配置方法;3. 掌握触发器的应用技巧。

二、实验仪器和器件1. 实验板:包括触发器模块、电源插座和数字电路板;2. 电源线;3. 按钮开关;4. LED灯;5. 连线。

三、实验内容与步骤1. J-K触发器的设计和配置(1)将J-K触发器模块插入实验板上的插口上;(2)将按钮开关和LED灯与J-K触发器连接,并根据需要配置J、K输入信号和时钟信号;(3)通过实验配置J-K触发器,并观察LED灯的亮灭情况。

2. D触发器的设计和配置(1)将D触发器模块插入实验板上的插口上;(2)将按钮开关和LED灯与D触发器连接,并根据需要配置D输入信号和时钟信号;(3)通过实验配置D触发器,并观察LED灯的亮灭情况。

3. T触发器的设计和配置(1)将T触发器模块插入实验板上的插口上;(2)将按钮开关和LED灯与T触发器连接,并根据需要配置T输入信号和时钟信号;(3)通过实验配置T触发器,并观察LED灯的亮灭情况。

四、实验结果与分析本次实验中,我成功设计和配置了J-K触发器、D触发器和T触发器电路,并通过实验得到了相应的结果。

在配置J-K触发器时,当J=1、K=1并且时钟信号上升沿到来时,LED灯亮起;当J=0、K=1并且时钟信号上升沿到来时,LED灯熄灭。

在配置D触发器时,当D=1并且时钟信号上升沿到来时,LED灯亮起;当D=0并且时钟信号上升沿到来时,LED灯熄灭。

在配置T触发器时,当T=1并且时钟信号上升沿到来时,LED灯状态取反;当T=0并且时钟信号上升沿到来时,LED灯保持原状态不变。

五、实验总结通过本次实验,我进一步掌握了触发器的原理和应用方法。

(集成电路应用设计实验报告)触发器

触发器一、实验器材(设备、元器件):1,数字、模拟实验装置(1台); 2,数字电路实验板(1块);3,74LS10、74LS00、74LS153、74LS74、74LS76芯片; 4,双踪示波器(1台); 5,函数信号发生器(1台)。

二、实验内容及目的:1,学习触发器逻辑功能的测试方法; 2,掌握集成触发器的逻辑功能;3,学习J —K 触发器和D 触发器的功能测试。

三、实验步骤:1、设计一个三人表决器(用74LS10和74LS00实现)74LS00是集成了四个单元的三输入端、一个输出端口的与非门,74LS10是集成了三个单元的三输入端、一个输出端口的与非门。

由三人表决器真值表得出其输出表达式为:CA BC AB ∙∙。

故右用74LS10和74LS00实现三人表决器连接。

2,设计一个三人表决器(用74LS153实现)74LS153是集成了两个单元的四选一数据选择器。

对三人表决器的表达式为ABC C AB C B A BC A F +++=,分析表达式知该逻辑函数含有三个逻辑变量,可选其中的两个(A ,B )作为数据选择器的地址输入变量,一个(C )作为数据输出变量。

则3210ABD D B A BD A D B A Y +++=,将逻辑函数F 整理后与Y 比较可得:1,,,03210====D C D C D D 。

故可实现用74LS153完成三人表决器。

3,基本R —S 触发器功能测试基本R —S 触发器是由两个与非门交叉耦合组成,当1==D D S R 时,两个与非门的工作都尤如非门,Q 接至与非门2G 的输入,使2G 输出为Q ;Q 接至与非门1G 的输入,使1G 输出为Q 。

故实验时用74LS00搭出R —S 触发器电路,R 、S 分别接逻辑开关,Q 、Q 分别接LED 灯,按其功能真值表验证R —S 触发器的功能。

4,用74LS10实现三人抢答器的设计根据三个抢答器的原理及R —S 触发器原理,及74LS10是集合了三个单元的三输入与非门,故可将三个与非门的一个输入作为三人抢答器的输入,三个与非门的其余两个输入端连接另外两个与非门的输出端,三个与非门输出端作为三个抢答器的输出。

实验六:触发器设计实验

实验六:触发器设计实验实验六:触发器设计实验一、实验目的:掌握触发器编写方法,能运用设计的触发器实现对数据表中数据完整性约束的控制。

二、实验内容:要求为Course表编写一个名为CourseTrigger插入触发器,当插入记录到Course表时,该触发器检查新插入记录的userid字段,如果插入这个字段的值不存在于Teacher表中,则从Course 表中删除这个新插入记录。

Teacher(userid char(20), name char(20),department char(20), age) Course(courseid int, userid char(20), name char(20), grade int) 说明:1.对表Teacher和Course之间不允许建立外键约束;2.本实验属于设计型实验,要求学生设计一个符合实验内容要求的触发器。

拓展训练: 1.在Student、Course和SC表中创建以下触发器(1)创建一个after触发器,在Student表中删除某学生的记录时,删除其相应的选课记录(不允许使用外键级联删除约束)。

(2)创建一个触发器,不允许删除Course表中的任何数据。

2.利用实验五中的Work表,分别建立以下触发器:(1)为worker表建立触发器T1,当插入或更新表中的数据时,保证所操作的记录的sage值大于0。

(2)为worker表建立触发器T2,禁止删除编号为“0001”的职工。

(3)worker 表中的人员的编号是唯一且不可改变的,为worker表建立触发器T3实现更新中编号的不可改变性。

(4)为worker表建立触发器T4,要求插入记录的sage值必须比表中已记录的最大sage 值大。

三、实验学时2学时四、实验设备与环境Windows 2003平台+ SQL Server 2008系统--建立test 数据库create database test on (name=student, filename=‘d:\\db\\’, size=10MB, maxsize=50MB,filegrowth=1MB ); use test; --要求为Course表编写一个名为CourseTrigger插入触发器,当插入记录到Course表时,该触发器检查--新插入记录的userid字段,如果插入这个字段的值不存在于Teacher表中,则从Course表中删除这个新插入记录。

D触发器的设计实验报告

EDA实验报告书姓名xxx 学号 xxxxxxx 实验时间课题名称上升沿触发的D触发器的设计实验目的1.初步掌握QuatusⅡ软件的使用方法2.掌握采用VHDL语言设计常见时序逻辑电路的方法3.理解时钟信号和使能信号在VHDL语言中的表述方法。

4.进一步熟悉VHDL语言的常见语句设计要求1.设计一个带使能信号的上升沿触发的D触发器。

其中EN=1时触发器正常工作.2.设计带有使能端的JK触发器设计程序设计思路D触发器的四个端口CLK,D,en,Q数据类型定义为STD_LOGIC,再根据各输入输出的功能编写程序。

使上升沿触发,en为控制端。

设计原理图及源程序源程序:LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY DF ISPORT (CLK,D,EN: IN STD_LOGIC;Q: OUT STD_LOGIC);END ;ARCHITECTURE bhv OF DF ISSIGNAL Q1 : STD_LOGIC;BEGINPROCESS (CLK,Q1)BEGINIF CLK'EVENT AND CLK = '1'THEN IF EN = '1'THEN Q1 <= D ;END IF;END IF;END PROCESS ;Q <= Q1;END bhv ;带有使能端的JK触发器设计程序LIBRARY IEEE ;USE IEEE.STD_LOGIC_1164.ALL ;ENTITY JKF ISPORT (CLK,J,K,EN: IN STD_LOGIC;Q,NQ: OUT STD_LOGIC);END ;ARCHITECTURE bhv OF JKF ISSIGNAL Q_S,NQ_S :STD_LOGIC;BEGINPROCESS (CLK,J,K)BEGINIF CLK'EVENT AND CLK = '0' THENIF EN = '1' THENIF J='0' AND K='1' THEN Q_S<='0';NQ_S<='1';ELSIF J='1' AND K='0' THEN Q_S<='1';NQ_S <='0';ELSIF J='1' AND K='1' THEN Q_S<=NOT Q_S;NQ_S<=NOT NQ_s;END IF;END IF;END IF;END PROCESS ;Q<=Q_S;NQ<=NQ_S;END bhv ;仿真波形图问题讨论列举QuatusII和Maxplus II软件在使用过程中的不同之处1、推荐用于所有新的CPLD、FPGA和结构化ASIC设计1)支持新的MAX® II CPLD以及Cyclone™、Stratix™和Stratix II FPGA 以及HardCopy ™结构化Asic2)支持MAX、FLEX® 和ACEX® 设计2、更快的按键式性能表现,更适用于引脚锁定的情况3、出众的集成化综合支持4、友好的MAX+PLUS II look-&-feel 选项5、转换MAX+PLUS II工程的增强功能6、许多设计人员使用Quartus II软件,并且对其印象深刻教师评分教师签名日期操作成绩报告成绩。

T触发器课程设计实验报告

课程设计报告课程名称数字逻辑课程设计课题T触发器的设计专业计算机科学与技术班级计算机1001班学号姓名指导教师刘洞波陈华光陈多2011年12月08日课程设计任务书课程名称数字逻辑课程设计课题T触发器的设计专业班级计算机1001班学生姓名学号指导老师刘洞波陈华光陈多审批任务书下达日期:2011年12月08日任务完成日期:2011年12月17日一、设计内容与设计要求1.设计内容:本课程是一门专业实践课程,学生必修的课程。

其目的和作用是使学生能将已学过的数字电子系统设计、VHDL程序设计等知识综合运用于电子系统的设计中,掌握运用VHDL或者Verilog HDL设计电子系统的流程和方法,采用Quartus II等工具独立应该完成1个设计题目的设计、仿真与测试。

加强和培养学生对电子系统的设计能力,培养学生理论联系实际的设计思想,训练学生综合运用数字逻辑课程的理论知识的能力,训练学生应用Quartus II进行实际数字系统设计与验证工作的能力,同时训练学生进行芯片编程和硬件试验的能力。

题目一4线-16线译码器电路设计;题目二16选1选择器电路设计;题目三4位输入数据的一般数值比较器电路设计题目四10线-4线优先编码器的设计题目五8位全加器的设计题目六RS触发器的设计;题目七JK触发器的设计;题目八D触发器的设计;题目九十进制同步计数器的设计;题目十T触发器的设计;每位同学根据自己学号除以10所得的余数加一,选择相应题号的课题。

参考书目1 EDA技术与VHDL程序开发基础教程雷伏容,李俊,尹霞清华大学出版社978-7-302-22416-7 2010 TP312VH/362 VHDL 电路设计技术王道宪贺名臣刘伟国防工业出版社7-118-03352-9 2004 TN702/623 VHDL 实用技术潘松,王国栋7-81065 7-81065-290-7 2000 TP312VH/14 VHDL 语言100 例详解北京理工大学ASIC研究所7-900625 7-900625-02-X 1999 TP312VH/35 VHDL编程与仿真王毅平等人民邮电出版社7-115-08641-9 2000 73.9621/W38V7 VHDL电路设计雷伏容清华大学出版7-302-14226-2 2006 TN702/185社2.设计要求:●课程设计报告规范课程设计报告应包含如下几个部分1)功能描述说明设计器件的功能,包括真值表(功能表),函数表达式,逻辑电路图2) 详细设计按照VHDL语言开发流程写出整个开发的详细过程,可以根据如下步骤适当导出程序,程序界面截图到课程设计报告对应模块。

触发器的认识和应用实验报告

触发器的认识和应用实验报告摘要:本实验报告旨在介绍和探讨触发器的概念、分类及其在电子电路中的应用。

通过实验验证触发器的工作原理和功能,并分析不同类型的触发器在不同应用场景下的优劣势。

实验结果表明触发器在数字电路设计中具有重要的作用,可实现存储、计数、时序等功能,且应用广泛。

1. 引言触发器是一种能够存储和改变输入信号状态的电子元件,其在数字电路中应用广泛。

触发器可用于存储数据、实现电平变换、计数和时序控制等功能,是数字电路设计中不可或缺的组成部分。

2. 基本概念触发器是由逻辑门电路构成的,其输入和输出可以采用不同的电平表示,如低电平表示0、高电平表示1。

触发器一般由几个逻辑门组成,包括主门和辅助门。

常见的触发器有RS触发器、D触发器、JK触发器等。

3. 实验设备和方法本实验使用LogicWorks软件进行模拟实验,搭建了RS触发器、D触发器和JK触发器的电路图,并通过输入不同的信号进行触发器的触发和状态变化观察。

实验过程中,通过改变输入信号和时钟信号频率,观察触发器的输出变化。

4. 实验结果和分析实验结果表明RS触发器适用于简单的状态存储和电平变换,但容易出现互锁现象;D触发器可以实现数据的存储和变换,并解决了RS 触发器的互锁问题;JK触发器则更加灵活,可实现计数和时序控制等功能。

5. 应用实例触发器在数字电路设计中有广泛的应用。

例如,D触发器可用于实现数据锁存器、寄存器和移位寄存器等;JK触发器可用于实现计数器、时序控制器和频率分频器等。

触发器还可以在时序电路、时钟同步电路和时序逻辑电路等领域发挥重要作用。

6. 结论本实验对触发器的概念、分类及其在电子电路中的应用进行了介绍和探讨。

通过实验验证了触发器的工作原理和功能,并分析了不同类型触发器的优劣势。

触发器在数字电路设计中具有重要的作用,可实现存储、计数、时序等功能,应用广泛。

触发器实验报告

触发器实验报告实验目的:本实验旨在设计和实现一个简单的触发器电路,触发器能够在输入信号满足特定条件时切换输出状态。

实验原理:触发器是由逻辑门组成的电路,输入信号作为触发器的控制信号,当输入信号满足特定条件时触发器切换输出状态。

常见的触发器有RS触发器、JK触发器、D触发器等。

本实验使用RS触发器作为示例。

RS触发器是由两个交叉连接的反馈AND门和非门组成。

输入引脚R和S用于控制RS触发器的切换状态。

当输入信号R=0,S=1时,触发器置位,输出Q=1;当输入信号R=1,S=0时,触发器复位,输出Q=0;当输入信号R=0,S=0时,触发器保持当前状态。

实验材料:- 7404反相器芯片- 与门芯片- LED灯- 电阻- 杜邦线实验步骤:1. 根据实验原理,搭建RS触发器电路。

使用7404芯片作为反相器,使用与门芯片作为交叉连接的反馈AND门和非门。

2. 将反相器的输入端和与门的输入端连接,形成交叉连接。

3. 将R和S输入信号引脚接到对应的输入开关上,将Q输出引脚接到LED灯。

4. 打开电源,通过调节R和S输入信号的开关,观察LED灯的亮灭变化。

实验结果:根据输入信号R和S的不同组合,可以观察到LED灯的亮灭变化。

当输入信号R=0,S=1时,LED灯亮;当输入信号R=1,S=0时,LED灯灭;当输入信号R=0,S=0时,LED灯保持当前状态。

实验结论:通过搭建RS触发器电路,成功实现了一个简单的触发器。

触发器能够根据输入信号的不同组合,切换输出状态。

触发器在电子电路中有广泛应用,常用于存储和传输信息。

触发器设计实验报告

数字电路与EDA实践教程实验报告系部名称:电子工程学院学生姓名:专业名称:光电信息工程班级:时间:2011.10.27学号: 31实验六 触发器设计一、实验目的(1)认识RS 触发器、JK 触发器、D 触发器和T 触发器。

(2)掌握RS 触发器、JK 触发器、D 触发器和T 触发器的逻辑功能及动作特点。

(3)能够通过CPLD 开发实现具有触发器功能的数字电路。

二、实验原理及内容实验一 JK 触发器要求设计一个合理的电路,通过MAX+plus Ⅱ软件仿真和CPLD 实现验证JK 触发器的逻辑功能,并掌握其动作特点。

此次设计的JK 触发器如图所示。

JK 触发器功能表如下。

异步置位端PRNJ 端 输出端QCP 端K 端异步复位端CLRNPRN CLRN CP J K Q 0 1 × × × 0 1 0 × × × 1 0 0 × × × 1 1 1 0 0 保持 1 1 0 1 01 1 1 0 1 1 1 1 1 翻转电路程序 SET J Q K Q CLR仿真图实验一 D 触发器要求设计一个合理的电路,通过MAX+plus Ⅱ软件仿真和CPLD 实现验证D 触发器的逻辑功能,并掌握其动作特点。

此次设计的D 触发器如图所示。

D 触发器功能表如下。

异步置位端PRND 端 输出端Q CP 端异步复位端CLRNPRN CLRN CLK D Q0 1 × × 1 1 0 × × 00 0 × × 11 1 1 11 1 0 01 1 0 × 保持SET D Q Q CLR电路程序仿真图5.实验心得在本次试验中首先是要清楚了解JK触发器和D触发器的功能,其各个管脚的功能;其次,分清楚异步与同步在编程上的差别,从而可以更好的设计程序。

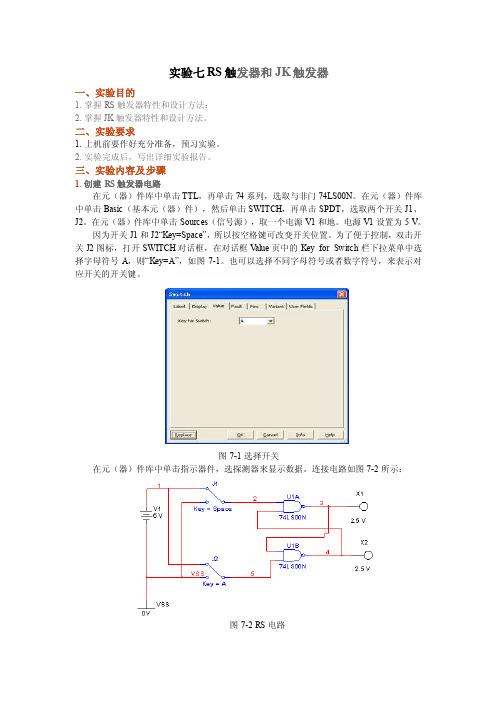

实验七rs触发器和jk触发器

实验七 RS触发器和JK触发器一、实验目的1. 掌握RS触发器特性和设计方法;2. 掌握JK触发器特性和设计方法。

二、实验要求1. 上机前要作好充分准备,预习实验。

2. 实验完成后,写出详细实验报告。

三、实验内容及步骤1. 创建RS触发器电路在元(器)件库中单击TTL,再单击74系列,选取与非门74LS00N。

在元(器)件库中单击Basic(基本元(器)件),然后单击SWITCH,再单击SPDT,选取两个开关J1、J2。

在元(器)件库中单击Sources(信号源),取一个电源V1和地。

电源V1设置为5 V。

因为开关J1和J2“Key=Space”,所以按空格键可改变开关位置。

为了便于控制,双击开关J2图标,打开SWITCH对话框,在对话框V alue页中的Key for Switch栏下拉菜单中选择字母符号A,则“Key=A”,如图7-1。

也可以选择不同字母符号或者数字符号,来表示对应开关的开关键。

图7-1 选择开关在元(器)件库中单击指示器件,选探测器来显示数据。

连接电路如图7-2所示:图7-2 RS电路2. 观测输出通过两个开关改变输入数据,按对应的开关的开关键符号,即可改变开关位置,从而改变输入数据,电源V1和地分别表示数据1和0。

探测器亮表示数据为“1”,探测器灭表示数据为“0”。

当触发器的输入R=0、S=1时,触发器的输出Q=0、=1。

只要不改变开关J6、J7的状态,RS触发器的输出和Q将保持不变。

取其他输入数据,即可列出RS触发器真值表。

RS触发器真值表如表7-1所示:表7-1 RS电路真值表3. 创建JK触发器电路JK触发器是数字电路触发器中的一种电路单元。

JK触发器具有置0、置1、保持和翻转功能,在各类集成触发器中,JK触发器的功能最为齐全。

在实际应用中,它不仅有很强的通用性,而且能灵活地转换其他类型的触发器。

由JK触发器可以构成D触发器和T触发器。

在元(器)件库中单击TTL,再单击74系列,选中JK触发器7473N。

实验报告——触发器及其应用

实验四项目名称:触发器及其应用一、实验目的1、了解基本RS、JK和D触发器的逻辑功能2、了解时钟对触发器的触发作用3、能用触发器设计基本的时序逻辑电路二、实验设备1、数字电路实验箱2、74LS112 74LS00 74LS74三、实验内容及步骤1、测试基本RS触发器的逻辑功能本实验是选取74LS00芯片(引脚如图4-7所示)中两个与非门交叉耦合而成,如图4-8所示。

根据图4-8连线,d S、d R端分别接在实验箱上的逻辑电平选择开关上,输出Q和Q分别接在实验箱上的LED电平指示上。

按表4-5选择输入状态,测试并记录结果。

图4-7 74LS00引脚图图4-8 基本RS触发器表4-5d S d R Q Q011110112、JK触发器(1) 测试置位端S D和复位端R D 的功能按表4-6,将74LS112芯片(引脚如图4-9所示)的R D、S D、J、K端分别接逻辑电平选择开关,CP 接实验箱中的单脉冲下降沿触发输出端,Q、Q端分别接至实验箱的LED电平指示上。

根据表4-6,确定R D,S D、J、K端状态,按下单脉冲触发按钮,测试并记录实验结果(表中“×”表示无关项,即可置于任意状态)。

图4-9 74LS112引脚图表4-6(2) 测试JK触发器的逻辑功能按表4-7,测试JK触发器的逻辑功能。

将CP接单脉冲下降沿触发输出端,J、K、R D、S D端分别接逻辑电平选择开关,Q端接在实验箱的LED电平指示上。

利用置位端S D和复位端R D的功能,根据表4-6预置现态Q n ,然后R D 、S D 端同时置“1”,J 、K 状态按表4-7设定。

按下单脉冲触发按钮,测试并记录结果。

表4-73、D 触发器(1) 测试置位端S D 、复位端R D 的功能。

将74LS74芯片(引脚如图4-10所示)的D 、S D 、R D 端分别接逻辑电平选择开关,CP 接实验箱中的单脉冲上升沿触发端输出端,Q 、Q 分别接在实验箱的LED 电平指示上。

触发器设计灵感:激发创意火花

触发器设计灵感:激发创意火花在创意设计领域,触发器是一种非常重要的元素。

触发器可以是任何引起人们思考、激发灵感的事物或事件。

在设计中使用触发器可以帮助设计师跳出常规思维,创造出更加独特和创新的作品。

本文将探讨触发器设计的概念,并分享一些激发创意火花的方法和实践经验。

什么是触发器设计?触发器设计是一种设计方法,通过使用特定的触发器来激发创意,促使设计师产生新的想法和视角。

这些触发器可以是来自于自然、艺术、音乐、文学等各个领域的元素,可以是感官刺激、情感体验或思维启发。

在设计过程中,设计师可以利用触发器来打破固有的思维模式,挑战常规的观念,从而创造出更具创意和独特的作品。

触发器设计的核心在于引起设计师内心的共鸣和触发情感反应,通过情感的涌动来激发创造力。

在设计中灵活运用触发器,可以帮助设计师打破沉闷的创作状态,重燃设计的激情,让创意如泉涌般涌现。

激发创意火花的方法1. 观察生活生活是最丰富多彩的触发器。

走出办公室,走进大自然,感受阳光、雨水、微风,观察身边的人和事物。

生活中的细微之处往往蕴藏着无限的灵感,从中汲取能量,激发创作的动力。

2. 多元化学习不断学习不同领域的知识和技能,可以为设计师提供更广阔的视野和更多的思维碰撞。

阅读书籍、观看电影、欣赏艺术品等,都是激发创意的途径。

跨界融合,可以创造出更具创新性的设计作品。

3. 创造良好的工作环境设计师的工作环境对创意的产生和发展至关重要。

一个充满灵感和创造力的工作空间可以激发设计师无限的创意火花。

保持环境整洁、舒适,让自己沉浸在设计的世界中,可以有效地激发创意。

4. 和他人交流与他人交流是激发灵感的有效途径。

和同事、朋友或导师交流自己的想法和观点,听取他们的建议和反馈,可以帮助设计师打破思维的局限,获取新的创意灵感。

实践经验分享案例一:自然风景的启发设计师在户外散步时,看到一片美丽的花海,被花海中精致的花朵深深吸引。

回到办公室后,设计师以花朵的形态为灵感,设计了一款花瓶的产品原型。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验8 触发器设计一、实验目的:通过本实验了解数据库触发器的概念,掌握触发器完整性设计方法。

二、实验原理触发器(Trigger)是用户定义在关系表上的一类由事件驱动的特殊过程,由服务器自动激活可以进行更为复杂的检查和操作,具有更精细和更强大的数据控制能力。

创建触发器语法格式CREATE TRIGGER <触发器名>{BEFORE | AFTER} <触发事件> ON <表名>FOR EACH ROW[WHEN <触发条件>]<触发动作体>触发时间:Before, AFTER触发事件:insert,update, delete删除触发器:drop trigger <触发器名>显示创建触发器脚本>show create trigger <触发器名>>show triggers;三、实验内容及方法实验平台操作系统:win7,数据库管理平台:mysql5.6或者mysql8,实验用数据库:老师提供的数据库脚本TradeDBSQL.txt(一)触发器应用于数据库完整性设计实体完整性-PK参照完整性-FK用户定义完整性1.参照完整性级联约束在订单表Orders(主表)与订单细节表OrderDetails(副表)中实现更新、删除级联是通过下列方式实现的foreign key(OrderID) references Orders (OrderID)on delete cascade on update cascade用下面的更新、删除触发器实现上面的更新、删除级联1)更新级联触发器orderd_updDELIMITER %% /* 用%% 代替; 作为命令结束符*/Create trigger orderd_upd /* 创建触发器名为orderd_upd */after update on Orders /* 在表orders 上建立更新后触发器*/for each row /* 对于每一行*/begin/* 在表orders上更新后自动更新OrderDetails 表*/ update OrderDetails set OrderID = new.OrderID where OrderID=old.OrderID; end %%特别要注意new,old 的区别old 表示更新前的一行记录(for each row)new 表示更新为新的数据的一行记录。

DELIMITER ; /* 恢复; 命令行结束符*/设计测试用例,测试是否生效:例如将orderid 从10400 改为14400select * from orders where orderid=10400;update orders set orderid=14400 where orderid=10400select * from orders where orderid=14400;select * from orderdetails where orderid=14400;2)删除级联触发器orderd_delDELIMITER %%Create trigger delt1after delete on Ordersfor each rowbegindelete from OrderDetails where OrderID=old.OrderID; end %%设计测试用例,测试是否生效。

2.用户定义完整性Mysql 没有check 约束,只能通过触发器实现check 约束例如产品表Products 中,规定单价UnitPrice的范围是大于0,小于100,设计触发器实现该约束delimiter %%create trigger prod_insbefore insert on Productsfor each rowbeginif new.UnitPrice <=0 or new.UnitPrice>=100 thenSIGNAL SQLSTATE '45000'SET MESSAGE_TEXT = '不能插入数据,单价只能是大于0小于100';end if;end;%%测试是否生效:单价超过100,及等于0delimiter ;insert into Products values (88,'梅州金柚',1,1,'每箱20个',110,39,0,10,TRUE);insert into Products values (89,'梅州金柚2',1,1,'每箱20个',0,39,0,10,TRUE);(二)触发器应用于业务逻辑1.新增加订单例如客户ID为ALFKI的客户下了一个订单,订单号为11088,订购了3种产品,具体数据如下:产品ID,单价,数量,折扣13,6,10,0.118, 62.5,15,0.1327,43.5,5, 0雇员ID为6 的雇员处理订单,订购日期:今天到货日期:5天后发货日期:2天后运货商:2,运货费:38,业务逻辑1)在订单orders中添加一条新纪录2)在订单细节Orderdetails表中添加订购产品的相关记录3)更新修改产品表中相关产品的库存量,减去订购的数量在OrderDetails 表上设计一个插入触发器,自动实现3)的更新库存的操作。

DELIMITER %%create trigger insertorderbefore insert on OrderDetailsfor each rowbeginupdate Products set UnitsInStock = UnitsInStock -new.Quantity where ProductID = new.ProductID;end%%测试用例DELIMITER ;insert into Orders values (11088,'ALFKI',6,'2018-10-14','2018-10-21','2018-10-19',3,32.38 ,'余小姐','光明北路124 号','北京','华北','111080','中国');记录Products 表中13,18,27的库存量select UnitsInStock from Products where ProductID=13;填写新订单// 订单ID, 产品ID,单价,数量,折扣insert into OrderDetails values (11088, 13, 6, 10, 0.1);insert into OrderDetails values (11088, 18, 62.5, 15, 0.13);insert into OrderDetails values (11088, 27, 43.5, 5, 0);完成上述插入操作后,比较Products 表中13,18,5的库存量2.修改订单修改订单客户ID为ALFKI的客户对订单号为11088 的订单做如下修改1 取消了27号产品,2.增加了14号产品,单价为23.5,数量8,折扣为0.13. 将18号产品的数量改为10,折扣改为0.11修改订单的业务逻辑1)从订单细节表中取消了某个产品,在产品表中返还该产品的库存量delete from OrderDetails where OrderID=11088 and ProductID=27;update Products set UnitsInStock= UnitsInStock + 5 where ProductID=27;2)从订单细节表中增加了某个产品,增加了14号产品,单价为23.5,数量8,折扣为0.1insert into OrderDetails values (11088, 14, 23.5, 8, 0);update Products set UnitsInStock= UnitsInStock - 8 where ProductID=14;3)将18号产品的数量改为10,折扣改为0.11update OrderDetails set Quantity=10, Discount=0.11 where ProductID=18 and OrderID=11088;或者update OrderDetails set Quantity=Quantity -5 Discount=0.11 where ProductID=18 and OrderID=11088;对于1)增加删除触发器DELIMITER %%Create trigger deletorderafter delete on OrderDetailsfor each rowbeginupdate Products set UnitsInStock = UnitsInStock + old.Quantity where ProductID = old.ProductID;end %%对于2)插入触发器(已经存在!)对于3)增加更新触发器10-> 810 ->20DELIMITER %%Create trigger Updateorderafter update on OrderDetailsfor each rowbeginupdate Products set UnitsInStock = UnitsInStock + old.Quantity -new.Quantity where ProductID = old.ProductID;end %%//注意old,new 在此的用法设计用例测试。

3 撤销订单客户ID为ALFKI的客户撤销一个订单(订单号为11088)业务逻辑删除相关记录1)在Orders表中删除记录delete from Orders where OrderID=11088 and CustomerID='ALFKI';2)在OrderDetails做级联删除delete from OrderDetails where OrderID=11088;3)在products表中必须恢复相关产品的库存。

应该是:update Products set UnitsInStock= UnitsInStock + 10 where ProductID=13;update Products set UnitsInStock= UnitsInStock + 8 where ProductID=14;update Products set UnitsInStock= UnitsInStock + 5 where ProductID=18;触发器设计在Orders上建立删除触发器-实现级联删除!DELIMITER %%Create trigger deletcscdafter delete on Ordersfor each rowbegindelete from OrderDetails where OrderID=old.OrderID;end %%//将在OrderDetails 中触发删除触发器DELIMITER ;特别要注意触发器串联:在Orders删除触发级联删除触发器deletcscd,而deletcscd 触发器将进一步触发deletorderdeletcscd -> deletorder根据上述要求,设计测试用例,测试实际效果。