DVB_T_H调谐器中鉴频鉴相器和电荷泵的设计

一种用于电荷泵锁相环的电荷泵

0 引言电荷泵锁相环具有捕捉范围宽、捕捉时间短、线性范围大、高速低功耗等优点,已广泛地应用于现代通信领域及射频领域[1]。

电荷泵锁相环主要由鉴频鉴相器、电荷泵、低通滤波器、压控振荡器和分频器等五部分组成[2]。

鉴频鉴相器的作用是将输入的基准信号和分频器输出的反馈信号进行比较,检测两个信号的相位差,并将这个相位差转换为脉冲形式UP及DN信号,进而控制电荷泵中的开关管,实现对后级电路的充放电。

电荷泵的充放电电流经过低通滤波器,进而将电流转化为电压,同时过滤充放电电流中的高频分量;低通滤波器输出的直流电压控制压控振荡器,实现随电压变化的输出频率;分频器接收压控振荡器的输出信号,并反馈到鉴频鉴相器输入端,构成负反馈。

但是系统实际工作过程中,电荷泵有电流失配、电荷共享、电荷注入和时钟馈通等非理想因素,系统在锁定后参考时钟和反馈时钟存在相位差。

基于此,本文将设计一种低失配的电荷泵。

1 电荷泵电路设计图1为一种基本电荷泵电路,主要由MOS管M1~M4构成。

其中,MOS管M1与MOS管M4分别构成电流源,MOS管M2与MOS管M3分别构成开关管。

图1所示电路的电路存在三种有效状态:(1)U P=0,DN=0时,M2导通,电荷泵对负载电容充电,控制电压升高;收稿日期:2018-12-11作者简介:王程程(1994—),男,安徽亳州人,硕士研究生,研究方向:模拟集成电路。

一种用于电荷泵锁相环的电荷泵王程程(重庆邮电大学光电工程学院,重庆 400065)摘要:基于SMIC 0.18μm CMOS工艺,采用自偏置共源共栅电流镜和正反馈技术,设计了一种用于电荷泵锁相环的电荷泵。

仿真结果显示,所设计的电荷泵能实现正常的充放电功能;在0.42V到1.22V输出电压范围内充放电电流的误差小于1%。

关键词:CM OS电荷泵;电流失配;自偏置中图分类号:TN911.8文献标识码:A文章编号:1007-9416(2019)01-0158-02设计开发DOI:10.19695/12-1369.2019.01.81图1 电荷泵基本结构图(a) (b) (c) (d) (e)图2 本文设计的电荷泵电路图3 自偏置共源共栅复合管1581592019年第 01 期A Charge Pump for Charge Pump Phase Locked LoopWANG Cheng-cheng(College of Optoelectronic Engineering, Chongqing University of Posts and Telecommunications, Chongqing 400065)Abstract:A charge pump for charge pump phase locked loop is designed by adopting these techniques of self-cascode current mirror and positivefeedback in SMIC 0.18μm CMOS. Simulation results showed that the designed charge pump can realize the characterize of charging and discharging.The error of charging and discharging current is less than 1% when the output voltage is in the range of 0.42V to 1.22V.Key words:CMOS charge pump;current mismatch;self-bias(2) U P =1, DN =1时,M3导通,电荷泵对负载电容放电,控制电压降低;(3) U P =1, DN =0时,M2、M3关断,电荷泵不工作,控制电压保持不变。

数字电视调谐器中鉴频鉴相器与电荷泵的研究与设计解读

数字电视调谐器中鉴频鉴相器与电荷泵的研究与设计伴随着科技的突飞猛进,锁相技术的理论研究和实际应用出现了蓬勃发展的局面。

由于电视机高频调谐器的本机振荡器是由LC振荡电路所组成的,存在很多的缺点。

所以要采用锁相环(Phase-Locked Loop,PLL)技术对本机振荡器的输出波形进行自动跟踪、控制,使得系统具有较高的稳定度及较宽的频率调节范围。

由锁相环组成的频率合成器一般由本振、固定分频器、可编程分频器、鉴相器和低通滤波器构成,其中鉴相器是由鉴频鉴相器和电荷泵组成的数字式鉴相器。

本文仅对鉴频鉴相器和电荷泵进行深入分析与研究,提出一种高性能的电路结构,并对两者的版图进行了设计。

其主要内容如下:论文首先介绍锁相环的基本原理。

系统阐述锁相环的工作原理,分析锁相环路的主要性能,通过对电荷泵锁相环的介绍深入分析鉴相器、电荷泵对系统性能的影响。

具体而言,鉴相器作为高度非线性的器件,它对系统的影响主要表现在两个方面:一是输入信号的泄漏,二是对输入增加噪声;电荷泵对系统性能的影响主要是由于电荷泵的非理想性造成的,表现为其漏电流和不匹配对杂散水平的影响,从而说明设计高性能鉴相器、电荷泵的重要意义。

鉴频鉴相器最突出的作用是它能显著的加快锁相环的速度,增大锁相环的捕获范围。

论文通过对国内外各种PFD电路结构性能的综合分析与比较,采用三态鉴相器的结构,并对传统的三态鉴相器进行改进:这里的D触发器是由动态D触发器改进的,通过将输入与输出路径缩短的方法,使速度得到提高;通过在反馈回路增加延时的方法来消除鉴相器存在鉴相死区的问题;在输出端增加延时单元与互补传输门,从而得到稳定、延时时间相同的输出信号。

电荷泵的主要功能是将鉴频鉴相器输出的数字信号Up和Down转换成连续的模拟信号。

通过对各种类型适用情况的分析与比较,选用差分输入单端输出的正反馈互补型结构,这种结构是从一种新型的采用电流控制技术的电荷泵结构改进得到的。

给出正反馈互补型电荷泵电路的仿真结果,从瞬态分析可以看出,不管是上拉还是下拉的电流都很稳定,输出电压也很稳定,没有电压跳变;而且由于电路采用正反馈技术,使得电荷泵充放电所需要的时间缩短。

高性能CMOS鉴频鉴相器和电荷泵的设计

[3]

些小的脉冲电流形成了输出信号噪声 。

信号,另一路输入信号是来自于通过分频器后的输

点:泄漏电流、电荷泵充放电电流的差异、锁定状态

信号从而修正振荡器信号和石英晶体参考信号的

下电荷泵充电脉冲和放电脉冲的不匹配。

频率和相位差。

PFD 的导通时间和延时失配是由 PFD 的结构决

定的,而电流失配和电荷泵电流大小是由电荷泵的

a phase frequency detector and charge pump circuit which is applied to atomic clock’s 3.4 GHz excitation

source is designed. The phase frequency detector consists of two edge ⁃ triggered,resettable D flipflops

里,由于脉冲电平没有到达足够开启 MOS 管的电平

要求,导致电荷泵无法正常工作,也就无法通过改变

压控振荡器的控制电压使得输入信号稳定。死区效

平,那么 S2 管导通,CP 通过 I2 放电,Vout 减小 [6-8]。如图 2

(b)所示,信号 A 频率大于信号 B,则 UP 产生连续的高

电 平 ,推 动 Vout 增 大 ,通 过 环 路 反 馈 使 得 信 号 B 频 率

2. College of Electrical Engineering,Zhejiang University of Water Resources and Electric Power,

Hangzhou 310018,China;3. School of Electical and Control Engineering,North University of China,

一种应用于电荷泵锁相环的高性能鉴频鉴相器

u i

变化。 信号 的上升沿使 P D由低状态跳变到下 F 个 高状态 。而 信 号 的上 升 沿使 P D 由高 状态 F

一

跳 变到 下 一个 低 状 态 。理论 上 来看 ,F P D的输 出是

三态 逻辑信 号 , 当今 绝 大 多 数逻 辑 电路产 生 的是 二

第 1 期

2 1 年 2月 01

微

处

理

机

No 1

M1 CROPROC S ES ORS

F b 2 1 e ., 0 1

一

种 应 用 于 电荷 泵 锁 相 环 的高性 能 鉴 频 鉴 相器

孙 鹏 , 元 旭 , 恩 义 , 永 双 徐 姚 胡

( 尔滨工 业 大学微 电子科 学 与技术 系 , 尔滨 10 0 ) 哈 哈 5 0 6 摘 要 : 频鉴 相器 是 电荷 泵锁 相环 中的一个 重 要模块 , 的 死 区 、 度 、 鉴 它 速 鉴相 范 围 、 鉴相 灵敏

Ph s r q e y Dee t ri sg e a e F e u nc t co sde i n d.Th e in i s d o e d sg sba e n TSMC 0. . RF CMOS t c n lg .Th 1 pm 8 e h o o y e smu ai n r s t t i l t e u] wi ADS s w o d p a e d t ci g c r c e nd hg a to e a in s e d,t a o s h ho g o h s ee tn ha a tra ih fs p r t p e o hede d

是: 速、 高 无死 区 、 功 耗 、 噪声 和宽 线性 鉴相范 围 低 低

超高频RFID阅读器电荷泵锁相环设计

超高频RFID阅读器电荷泵锁相环设计锁相环是在模拟/数字电路设计中的一种非常重要和实用的电路结构[1]。

锁相环[2-3]由鉴频鉴相器、电荷泵、滤波器、压控振荡器以及分频器等构成,在具体电路设计中还可能涉及到基准(PTAT)电路和一些简单的数字电路。

由于锁相环正常工作时能通过内部电路中精准的负反馈机制提供稳定的输出频率作为本振信号,因此,该结构广泛应用于数字及模拟电路设计之中。

1 电荷泵锁相环电路设计1.1 电荷泵锁相环原理与整体结构图1所示为电荷泵锁相环[4]的系统结构图。

620)this.style.width=620;" border=0 alt=超高频RFID阅读器电荷泵锁相环设计src="技术2021/ddk0lludrsi2021.gif"> 锁相环系统的基本原理为:最初外部参考信号与分频器输出信号同时输入给系统,送入鉴频鉴相器;鉴频鉴相器检测ωout与ωin两路信号的相位差和频率差以及上升沿和下降沿,并随时根据它们的上升、下降变化决定电荷泵的开启和关断状态;电荷泵的输出电压Ud经过滤波器滤波,产生输出电压Vctrl,Vctrl作用在压控振荡器上,产生输出频率;压控振荡器的作用是使输出频率随输入控制电压的变化按照一定比例变化,分频比为N的分频器保证:fvco=fref×N,其中fvco为VCO的输出频率,fref为参考频率。

锁相环内部负反馈机制使整个系统达到锁定状态。

620)this.style.width=620;" border=0 alt=超高频RFID阅读器电荷泵锁相环设计src="技术2021/5ojmqpg2zol2021.gif"> 出信号被送入鉴频鉴相器,初始相位差使环路无法锁定,经过一段时间的相位积累就能达到频率捕获。

针对死区问题,本设计所采用的去死区的方法是增加延时单元,延时单元应用串联连接的反相器链。

应用于DVB—T的0.18μmCMOS工艺数字可编程分频器芯片设计

可编 程分 频器 最终 的分频 比可表示 为 :

N =A P +1 ( )+( 一A) = M +A P P

改变 A和 的值 就 可 以实 现 不 同的 分 频 比。本 设 计 中 P的取 值 为 1 , 值范 围为 0~1 , 的取值 范 围 6A取 5M 为5 7—8 , 过 改变 二 者 预置 值 并结 合 D P 实 际上 6通 M , 可 以实现 92~19 1 3 1范 围 的 4 0个 不 同分 频 比 , 值 8 该 可 以覆盖 系统指 标要 求 的分频 范 围。 由于 常规 的 D MP从 P+1分 频 切 换 到 P分 频 或 从 P分频 切换 到 P+1 频都 会产 生一 个相位 移 4。 分 。

・

( 压控 振荡 器 ) 和分 频 器 ( 分频 比为 Ⅳ) 组成 , 中要求 其

V O输出 1 8 H ~ 8 . H 范围的本振信号。 C 9M z 2 0 5 z 3 0 M 分频器 Ⅳ 由 D ( 模前 置 分 频器 ) MP 双 和可 编 程 分频 器

构成 , 同将 139MH 一 8 . z 共 8 z 2005MH 本振 信号 完成

收 稿 日期 : 080 —2 修 回 日期 : 0 81 — 。 2 0 -91 ; 20 -02 7

1 ・ 7

・

微 电 子 与基 础 产 品 ・

电 子 工 蠢 师

20 08年 1 2月

如果 简单地先 进行 A次 P+1分 频后 做 一 4次 P分 频, 将会产 生 大的相 位 波 动 。本 次设 计 采用 改 进 的分 频算法将 D MP的两种 分频输 出均匀 混合 , 就可 以减 小 相 位波 动。这 种 “ 均匀 ” 工作是 通过 计数器 来完成 的 。 下 面简要介 绍这 种 改进 分 频 算法 的设计 思 想 J 。 额外 创建 一个 计数 器 S M。D P每进 行 一 次 分频 输 U M 出, 计数器 S M 都将 累加 预 置值 之 差 ( —A) U 。若 累 加结 果小 于 , 进 行 P +1分 频 , 大 于 或 等 于 则 若

DAB射频接收机中的高性能电荷泵设计

DAB射频接收机中的高性能电荷泵设计唐路;王志功;朱存良;徐建;俞菲【摘要】A type of improved charge pump for digital audio broadcasting ( DAB) radio frequency (RF) tuner is realized. An improved cascode current mirror with operational amplifier is used to enable the charge pump current to be well matched in the core part of the proposed circuit. The self-biasing wide-swing current mirror is adopted in the band-gap of the proposed charge pump to offer a wider range output voltage. The folded operational amplifier in the circuit is realized with folded cascode topology for wider common-mode input range and higher gain. The chip is realized in 0. 18 jxm complementary metal oxide semiconductor ( CMOS) process. Measurement results show that the charge pump current is 0. 3 mA. The measured current mismatching can be less than 1% in the output voltage range of 0. 3 to 1.6 V. The power consumption is 4 mW under a 1. 8 V supply voltage. The experimental results show that the proposed topology structure has realized the match of the charge and discharge current and the lower power consumption.%实现了一种用于DAB数字广播射频接收机的改进型电荷泵电路.电路核心部分采用带有运算放大器的改进型的共源共栅极电流镜结构实现,以改善电荷泵的电流匹配度.电荷泵中的带隙基准源采用自偏置宽摆幅电流镜结构以增加输出电压的范围.电荷泵中的运算放大器采用叠式共源共栅极结构以获得更大的输入共模范围与更高的增益.芯片采用0.18 μm CMOS工艺实现.测试结果显示,电荷泵的电流为0.3 mA.电流失配率在0.3~1.6V输出电压范围内小于1%.在1.8V供电电压下,芯片功耗约为4 mW.实验结果显示,所设计的电路结构实现了充放电电流的匹配,且功耗较低.【期刊名称】《东南大学学报(自然科学版)》【年(卷),期】2012(042)006【总页数】5页(P1047-1051)【关键词】电荷泵;锁相环;电流失配;运算放大器【作者】唐路;王志功;朱存良;徐建;俞菲【作者单位】东南大学射频与光电集成电路研究所,南京210096;东南大学信息科学与工程学院,南京210096;东南大学射频与光电集成电路研究所,南京210096;东南大学信息科学与工程学院,南京210096;东南大学射频与光电集成电路研究所,南京210096;东南大学射频与光电集成电路研究所,南京210096;东南大学信息科学与工程学院,南京210096;东南大学信息科学与工程学院,南京210096【正文语种】中文【中图分类】TN432目前模拟广播正在逐步实现数字化,数字音频广播(DAB)是最主要的数字广播标准之一,其标准的工作频段包括Ⅲ波段(174~240 MHz)和L波段(1 452~1 492 MHz)[1].DAB 射频接收机中关键电路的设计对于模拟广播的数字化具有重要的意义.在DAB射频接收机中,本振信号通常是由锁相环(PLL)频率合成器产生的.电荷泵作为PLL的关键部分,其性能对于整个系统性能具有重要的影响[2].在频率合成器中,参考信号由于频率调制作用在压控振荡器输出信号中会产生参考杂散,造成输出信号频谱不纯.而系统受频率调制干扰的程度主要由电荷泵非理想效应决定[3].因此在设计电荷泵电路时,应注意抑制其非理想效应[4].本文在经典源极开关型电荷泵电路的基础上,提出了一种基于改进型共源共栅极结构的用于DAB射频接收机的高性能电荷泵电路,并采用0.18 μm CMOS 工艺实现了该电路.图1为DAB射频接收机中的锁相环型频率合成器的系统结构,其中电荷泵的作用是将鉴频鉴相器(PFD)输出的信号转化为稳定的模拟电压,用于控制压控振荡器(VCO)的输出频率[5].电荷泵的基本模型如图2所示.在锁相环型频率合成器中,鉴频鉴相器与电荷泵的总增益为IP/(2π),其中 IP为电荷泵充放电的电流值[6].电荷泵将鉴频鉴相器的2个输出信号up与down合并为一个输出信号out以驱动低通滤波器.滤波器将电荷泵输出电流积分成压控振荡器(VCO)的输出电压,该积分电压直接影响电荷泵的输出电压.为增加VCO的调谐范围,电荷泵的输出电压摆幅应尽可能大.在相同的频率调节范围内,增加输出电压范围可降低电路对噪声的敏感度,但同时会增加电荷泵设计难度.电流失配是电荷泵非理想效应之一.在传统的电荷泵电路中,当信号up和down开启和关闭,电流注入环路滤波器时,由于器件失配及沟道长度调制等效应,电流Iup和Idown不可避免地存在失配状况,而且随着输出电压不同失配状况也不相同,因此会造成压控振荡器控制电压产生周期性纹波.在设计电荷泵电路时,另一个应抑制的非理想效应是电荷泄漏.电荷泄漏是由电荷泵本身或其他在片元器件或电路造成的.电荷泵输出电流包括2部分:① 大小正比于相位差的直流分量;②由参考频率的各次谐波构成的交流分量.当相位差为零时,电荷泵输出的直流分量和交流分量均为零,这正是理想电荷泵锁相环锁定后的状态.然而在实际的电荷泵锁相环中,电荷泵存在电流失配、漏电流和时间失配等非理想因素,导致锁相环锁定后存在一定的相差,从而使得锁相环的输出信号中存在杂散.综上所述,由电流失配、漏电流和时间失配等电荷泵中的各种非理想效应所产生的相位误差为式中,ICP为电荷泵的电流;Δton为鉴频鉴相器开通时间;Ileak为泄漏电流;Δi为充放电流偏差;Tref为输入参考时钟周期.通过改进电荷泵电路提高电流的匹配状况,或者减少开启时间,都可以在很大程度上降低总的参考杂散,从而改善整个锁相环路的噪声性能[7].其他造成参考杂散的原因还包括PFD开关控制信号时间失配等,但与上述原因相比较,其影响基本上可不需考虑.由于电荷泄漏主要是由工艺器件的物理特性造成的,因此电荷泵电路设计应加强电流匹配并减少电荷共享.为了克服电荷泵的各种非理性效应,在电荷泵的电路设计中应采用合理的结构.图3中的电荷泵称为源极开关型电荷泵[8].其中,开关管M4与M1分别直接与电源和地连接,避免了漏极电荷泵的电荷共享和电荷分配的影响.同时,开关管与其他晶体管并联,有效地提高了开关速度,并且镜像电流偏置也不受到开关时间常数的影响.此外,该电路还采用了增益自举方式来提高电流源的输出电阻.该结构能够实现更有效的充放电电流匹配,并适合低电压情况.源极开关型电荷泵对电荷共享、电荷注入效应有抑制作用,因此被广泛使用.但在该电路结构中,与NMOS和PMOS的跨导及输出电阻等工艺参数不同,若两者输出电阻的增加程度不完全相同,将导致电流失配.本设计中的电荷泵电路采用了带有运算放大器的改进型共源共栅极结构,电路结构如图4所示.由图可知,本文所设计的电荷泵电路的输入信号为 up和 down,输出信号为 VOUT.信号 up和down是由PFD输出的2路信号经过缓冲电路后得到的.其中up信号控制P型开关管 M10,down信号控制N型开关管M14,2个开关管都没有直接和负载连接,以避免电荷共享.它们的栅极长度被设为最小以减小时钟馈通.为了保证充放电电流的完全匹配,电路中引入一条参考电流的复制支路.各晶体管的尺寸满足如下关系:M9,M14,M19尺寸相同;M8,M13,M18尺寸相同;M7,M12,M17尺寸相同;M11,M16尺寸相同;M10,M15尺寸相同.有3种因素会使该复制支路产生非理想情况:沟道长度调制效应、2个晶体管间存在的阈值偏差、非理想的几何图形匹配.对于沟道长度调制效应,应当保证相同的漏-源电压和高的输出电压,并使用较大尺寸的晶体管,以减小其影响.因此除开关管之外,其余晶体管的栅极长度都尽量避免被设为最小值,尤其是共源共栅极结构中的器件,这样可以有效地避免由于沟道调制效应引起的电流偏差.利用共源共栅极电流镜的结构,能够实现I3=Iref=I4.在由晶体管 M15,M16,M17,M18,M19所构成的支路中,开关管M19和M15始终处于导通状态,能够得到I2=Iref=I4,从而实现了对参考电流的精确复制.当开关管M10开启时,电荷泵电路向负载充电.这时M10,M11所在支路和 M15,M16所在支路的状态完全相同.因此,得到I1=I2=I4.同理,在放电的状态下可以得到表达式I2=I4=I3.从而确保了I1=I3,即电荷泵的充放电电流得到很好的匹配.为了提高系统的稳定性,运算放大器的正信号输入点和信号输出点间并联了电容C1,以保证可靠的相位裕度.电荷泵的带隙基准源由晶体管M1,M2,M3,M4,M5构成.该带隙基准源的设计采用了自偏置宽摆幅的管联电流镜结构.M1的栅极不直接连接M3的源极,从而使得M3的源极电压不包含M1开启电压分量.这样可使得所有晶体管饱和工作的输出电压的最小值仅为2Von,从而增加了后级滤波器输出电压的范围.此外,设计中适当增加了带隙基准源中晶体管的尺寸,从而降低了沟道调制效应,并提高了电流匹配特性,使输出电流更加平坦[9].电荷泵电路中,运算放大器的主要作用是实现充放电电流的精确一致,并避免电荷共享等问题.同时,为了使电荷泵中作为复制电流的支路节点电压与电荷泵输出点电压保持一致,运放需要足够的输入范围以确保电荷泵输出电压匹配范围.本设计中电荷泵中的运算放大器采用了叠式共源共栅极结构,该结构具有较大的输入共模范围以及更高的增益[10].其电路结构如图5所示.该运算放大器中几个重要节点的偏置电压由片内偏置电路产生.其中晶体管M21和M22采用了二极管接法,产生偏置电压Vb3和Vb2.晶体管M17与M18构成了共源共栅极支路,可有效提高电源抑制比,使得所产生的偏置电压在电源变化时基本保持恒定,保障电路工作正常.采用同样的方法可以产生偏置电压Vb1和Vb4.可求得该运放的增益与输出电阻分别为式中,gM1为晶体管M1的跨导;gM9为晶体管M9的跨导;gbM9为晶体管M9漏极与衬底间的跨导;rdsM9为晶体管M9源极与漏极间电阻;rdsM3为晶体管M3源极与漏极间电阻;rdsM8为晶体管M8源极与漏极间电阻;gM10为晶体管M10的跨导;gbM10为晶体管M10源极与衬底间的跨导;rdsM10为晶体管M10源极与漏极间电阻.图5中运放电路的相频特性的开环仿真结果如图6所示,其中运放的增益为70 dB,表明所设计的运放已经具有较高的增益.运放的共模抑制比仿真结果如图7所示.运放的共模抑制比达62 dB,表明输出点电压受输入点信号变化的影响较小.由图6、图7可知,所设计的运放在低频段可提供较大的增益,并且保持了较为稳定的输出电压,并对电荷泵的直流电压进行了有效钳制,因而此设计满足电荷泵电路对增益和稳定性的要求.图8为在不同工艺角下电荷泵的充放电电流仿真结果.由图可知在0.3~1.6 V电压范围内,电流在0.3 mA左右,充放电电流失配小于 0.5% .电荷泵电路采用0.18 μm CMOS工艺实现,芯片的显微照片如图9所示.电荷泵的测试采用在晶圆测试,所获得的充放电电流匹配特性曲线如图10所示.测试结果表明,电源电压为1.8 V时,充放电平均电流为0.3 mA,电路的输出电压范围在0.3~1.6 V内时电流失配率小于1%,功耗约为4 mW.与文献[11]中结果相比,本文的电流失配率更小.本文设计了一种基于CMOS工艺的具有高充放电电流匹配度与低功耗的高性能电荷泵电路.电荷泵电路采用了带有运算放大器的改进型共源共栅极结构实现.其中带隙基准源的设计采用了自偏置宽摆幅的管联电流镜结构;运算放大器采用了具有较大输入共模范围及更高增益的叠式共源共栅极结构.测试结果表明,上述各项措施有效地降低了电荷泵电路的非理性特性,提高了电荷泵的充放电电流匹配度.该电荷泵可用于实现DAB数字广播射频接收机的设计.【相关文献】[1]周建政,王志功,李莉,等.DRM 接收机射频前端芯片的频率规划设计[J].高技术通讯,2008,18(5):480-486.Zhou Jianzheng,Wang Zhigong,Li Li,et al.Frequency planning of RF front-end for DRM receivers[J].Chinese High Technology Letters,2008,18(5):480-486.(in Chinese) [2] Musa A,Murakami R,Sato T,et al.A low phase noise quadrature injection locked frequency synthesizer for MM-wave applications[J].IEEE Journal of Solid-State Circuits,2011,46(11):2635-2649.[3] Hwang M S,Kim J,Jeong D K.Reduction of pump current mismatch in charge-pump PLL[J].Electronics Letters,2009,45(3):135-136.[4] Yin Xizhen,Xiao Shimao,Jin Yuhua,et al.A constant loop bandwidth fractional-N frequency synthesizer for GNSS receivers[J].Journal of Semiconductors,2012,33(4):045007.[5] Tang Lu,Wang Zhigong,Xue Hong,et al.A low-jitter RF PLL frequency synthesizer with high-speed mixed-signal down-scaling circuits[J].Journal of Semiconductors,2010,31(5):055008.[6] Gardner F M.Charge-pump phase-lock loops[J].IEEE Transactions on Communications,1980,28(11):1849-1858[7] Rhee W.Design of high performance CMOS charge pumps in phase-locked-loops [C]//Proceedings of the 1999 IEEE International Symposium on Circuits and SystemsVLSI.Orlando,FL,USA,1999,2:545-548.[8] Huang Q T,Rogenmoser R.Speed optimization of edge-triggered CMOS circuits for gigahertz singlephase clocks[J].IEEE Journal of Solid-State Circuits,1996,31(3):456-465.[9] Wang C C,Wu J C.Efficiency improvement in charge pump circuits[J].IEEE Journal of Solid-State Circuits,1997,32(6):852-860.[10]Johns D,Martin K.Analog integrated circuit design[M].New York:John Wiley&Sons,1997:266-273.[11]薛红,李智群,王志功,等.低杂散锁相环中的电荷泵设计[J].半导体学报,2007,28(12):1988-1992.Xue Hong,Li Zhiqun,Wang Zhigong,et al.A charge pump design for low-spur PLL [J].Chinese Journal of Semiconductors,2007,28(12):1988-1992.(in Chinese)。

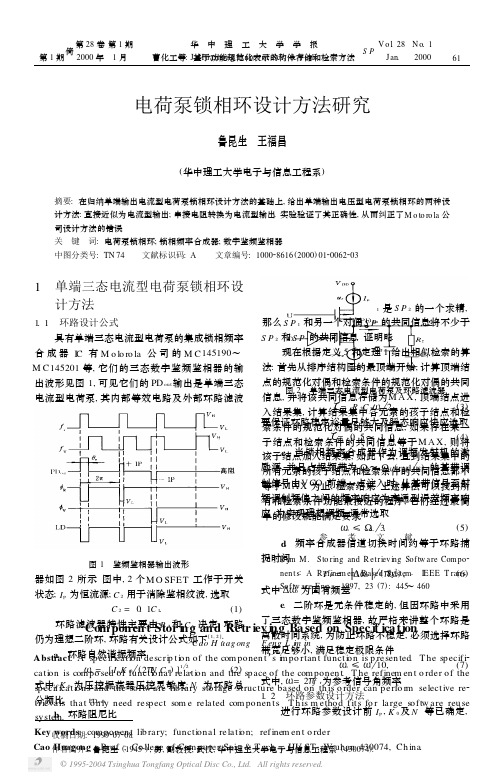

电荷泵锁相环设计方法研究

(15)

第 1 节中式 (1) , (4)~ (7) , (9) 及本节式

则在图 3 所示V DD = 5 V 条件下的曲线中, 可查得 充放电电流近似为 Ip = 2. 5 mA , 这与实测值一 致[3]. 在 V DD 等于其他值时可查资料中曲线或实测 得出 Ip 值, 然后可用第 1 节的方法设计环路.

( 12)~ (15) 是单端三态电压型电荷泵锁相频率 合成器设计方法 2 的设计公式.

例 1 某 CT 1 无绳电话调频发射机实验样机 采用集成锁相频率合成器M C 145162, f r= 5 kH z;

© 1995-2004 Tsinghua Tongfang Optical Disc Co., Ltd. All rights reserved.

Ip = V DD (2R 1) ,

(11)

放电电流- Ip = - V DD (2R 1 ) , 可见 R 1 将三态电

压型电荷泵转换成为三态电流型电荷泵, 则第 1

节所有的公式都适用.

当然, 要保证 PD out 为恒压源, 必须保证内部 M O SFET 饱和导通, 则导通电流应足够小, 可查 得 Ip ≤0. 36 mA , 由此可选择 Ip = 0. 2 mA , 代入 式 (11) 得

式sp e中ci,fiKca0t为ion压s a控nd振t荡he器so压ftw控a灵re敏lib度ra; rNy

s为to环rag路e 总st ru

c

t

式中, Ξr= u re ba sed

2oΠnf

r为参考信号角频率. th is o rder can p erfo

rm

select ive

re2

分t rie频va比ls. tha t PoDnoulty need resp ect som e rela ted com pon1e.n2t s. 环T 路h is参m数et设ho计d 方fit法s fo r la rge softw a re reu se

锁相环频率合成器中的电荷泵设计

流镜 电路 实现 了充放电 电流的高度 匹配。仿真结果表 明:电源电压 1 V时,电荷泵 电流为 0 mA;在 . 8 . 5

03 16 输 出 电压 范 围 内电 流 失 配 小 于 1 A,功 耗 为 68 .V~ .V .mW 。

关键 词 :电流 失配 ; 电荷 泵 ;运 算放 大 器 ; 自偏 置 电流镜 中图分类号 :T 7 2 N 0 文献标 识码 :A 文章编号 :1 8 -0 0 (0 7 90 1_4 6 11 7 2 0 )0 _0 50

( 东南大 学射频 与光 电集 成电路研究 所 ,南京 2 0 9 1 0 6)

摘

要 :用 T MC 01 m C S .8 MOS工 艺设计 了一种 电荷泵 电路 。传统 的电荷 泵电路 中充放 电电流有

较 大的电流失配 , 文章采用与电源无 关的基准 电流源 电路 , 运用运算放 大器和 自偏置 高摆 幅共源共栅 电

Absr t A h r ep m pcr u t ih c lb s di tac : c a g - u ic i wh c al eu e PLL y t e ie sd sg e M C . 1 n s n h sz r e in di TS i n 0 1 CM OS 8m

度匹配的电荷泵 电路 。

能要求越来越高 , 频率合成器是射频单元尤为重要 的部 分。 无论是信号的发送还是接收 , 都要求频率合成器能

产生高稳定性 、 高精度的本振信号 , 采用锁相环结构的

频率合成器是获得高性能本振信号的理想选择 。 在各种

锁相环电路 中, 电荷泵锁相环具有快速鉴频 、 捕获频率 范围广 、 零锁定相位误差 、 高速 、 低功耗 的优点 , 比 是 较流行的锁相环实现方式。 衡量锁相环系统最重要的指

导航接收机中鉴频鉴相器的设计

第9卷第2期2021年4月Vol.9,No.2Apr.,2021导航定位学报Journal of Navigation and Positioning引文格式:张治国,黄海生,李鑫,等.导航接收机中鉴频鉴相器的设计[J].导航定位学报,2021,9(2):35-40.(ZHANGZhiguo,HUANG Haisheng,LI Xin,et al.Design of phase frequency detector based on navigation receiver[J].Journal of Navigation and Positioning,2021,9(2): 35-40.)D01:10.16547/ki.l0-1096.20210206.导航接收机中鉴频鉴相器的设计张治国,黄海生,李鑫,党成(西安邮电大学电子工程学院,西安710121)摘要:为了提高导航接收机中本振频率的精度和稳定性,避免本振信号在锁相环电路中发生漂移,锁相环的低噪声、快速锁定等性能是电路设计的关键,而鉴频鉴相器作为锁相环系统的重要模块之一,其鉴相死区的存在,极大地恶化了锁相环的噪声特性。

基于中芯国际(SMIC)0.18nm互补金属氧化物半导体(CMOS)工艺,设计了一种复位脉宽可调节的无死区鉴频鉴相器,根据压控振荡器反馈频率信号调节复位脉冲宽度,实现了4种不同的复位延时,在降低抖动的同时,能够有效地消除鉴相死区。

当供电电压为1.8V时,其最大工作频率为530MHz,最大相位噪声为-142.2dBc/Hz o 电路鉴频鉴相功能正确,并具有良好的频率和噪声特性,可应用到导航接收机中的锁相环电路中。

关键词:导航接收机;锁相环;鉴频鉴相器;死区;低噪声中图分类号:P228文献标志码:A文章编号:2095-4999(2021)02-0035-06Design of phase frequency detector based on navigation receiverZHANG Zhiguo,HUANG Haisheng,LI Xin,DANG Cheng(School of Electronic Engineering,Xi'an University of Posts and Telecommunications,Xi'an710121,China)Abstract:In order to improve the accuracy and stability of the local oscillator frequency in navigation receivers,to avoid the drift of the local oscillator signal in the phase-locked loop circuit,the paper designed a phase frequency detector:based on China's Semiconductor Manufacturing International Corp.(SMIC)0.18p,m Complementary Metal-Oxide-Semiconductor (CMOS)process,a dead-zone-free phase frequency detector with adjustable reset pulse width was given;and the reset pulse width was adjusted to achieve4different reset delay according to the feedback frequency signal of the voltage-controlled oscillator,which could effectively eliminate the phase discrimination dead zone while reducing jitter.Experimental result showed that:when the voltage was1.8V,the maximum operating frequency of the detector would be530MHz,with the maximum amplitude noise-142.2dBc/Hz;and the frequency and phase discrimination function of this circuit could be correct with good frequency and noise characteristics,indicating the feasibil辻y of the detector for the phase-locked loop circuit of navigation receivers.Keywords:navigation receiver;phase-locked loop;phase frequency detector;dead zone;low noise0引言导航接收机的灵敏度、首次定位时间等性能,直接影响着卫星通信的质量,信号捕获与跟踪能力决定了系统的整体性能。

电荷泵式鉴频鉴相器电路

电荷泵式鉴频鉴相器电路电荷泵式鉴频鉴相器是一种常用的电子电路,用于频率测量和相位检测。

它可以将输入信号的频率和相位信息转换为直流电压输出。

该电路结构简单,性能稳定可靠,因此在通信、测量等领域得到广泛应用。

一、电荷泵式鉴频鉴相器原理电荷泵式鉴频鉴相器是基于电容器充放电原理的电路。

它由两个电容器和两个开关组成。

其中,一个电容器与电源正极相连,另一个电容器与电源负极相连。

两个开关可以根据输入信号的频率和相位信息控制电容器的充放电过程。

当输入信号频率较低时,电容器可以充电并保持电荷。

当输入信号频率较高时,电容器无法充电并且电荷会逐渐耗尽。

通过测量电容器上的电压变化,可以判断输入信号的频率。

当输入信号相位与电容器充放电过程相匹配时,电容器上的电压变化最大。

通过测量电容器上的电压变化,可以判断输入信号的相位。

二、电荷泵式鉴频鉴相器电路实现电荷泵式鉴频鉴相器的基本电路如下:1. 输入端:将待测频率信号输入到电荷泵式鉴频鉴相器。

2. 两个电容器:用于存储电荷。

3. 两个开关:根据输入信号的频率和相位信息控制电容器的充放电过程。

4. 输出端:将测量得到的直流电压输出。

电荷泵式鉴频鉴相器的工作过程如下:1. 当输入信号的频率较低时,电容器可以充电并保持电荷。

2. 当输入信号的频率较高时,电容器无法充电并且电荷会逐渐耗尽。

3. 通过测量电容器上的电压变化,可以判断输入信号的频率。

4. 当输入信号的相位与电容器充放电过程相匹配时,电容器上的电压变化最大。

5. 通过测量电容器上的电压变化,可以判断输入信号的相位。

三、电荷泵式鉴频鉴相器的应用电荷泵式鉴频鉴相器广泛应用于通信、测量等领域。

它可以用于频率测量、频率锁定、相位检测和相位锁定等应用。

1. 频率测量:通过测量电容器上的电压变化,可以准确测量输入信号的频率。

2. 频率锁定:通过调节电容器的充放电过程,使得电容器上的电压变化与输入信号频率相匹配,从而实现频率锁定。

3. 相位检测:通过测量电容器上的电压变化,可以准确检测输入信号的相位。

用于锁相环路的鉴频鉴相器及电荷泵电路[发明专利]

![用于锁相环路的鉴频鉴相器及电荷泵电路[发明专利]](https://img.taocdn.com/s3/m/0af76b1ac8d376eeafaa31ac.png)

专利名称:用于锁相环路的鉴频鉴相器及电荷泵电路专利类型:发明专利

发明人:晏进喜,李玺

申请号:CN200910054640.X

申请日:20090710

公开号:CN101944909A

公开日:

20110112

专利内容由知识产权出版社提供

摘要:用于锁相环路的鉴频鉴相器及电荷泵电路,涉及通信技术领域。

现有技术存在线性度与噪声性能不佳的缺陷,本发明当第一串联电路与电流泵的输出端相连接时,上路偏置电路作为所述上路电流源的偏置电路,当第二串联电路与电流泵的输出端相连接时,下路偏置电流源作为所述下路电流源的偏置电路。

通过加入两个固定的偏置电流并根据电荷泵输出电压然选择适合的偏置电流,使PLL 环路锁定后,鉴频鉴相器两输入端的相位差偏离零值,达到了增强鉴频鉴相器和电荷泵的线性度、改善了小数分频锁相环的噪声性能的目的。

申请人:智迈微电子科技(上海)有限公司

地址:200433 上海市杨浦区国定路335号2号楼1710

国籍:CN

代理机构:上海光华专利事务所

代理人:余明伟

更多信息请下载全文后查看。

应用于DVB-T调谐器的CMOS可变增益中频放大器设计

应用于DVB-T调谐器的CMOS可变增益中频放大器设计郭峰;李智群;李晟;唐路;王志功

【期刊名称】《中国集成电路》

【年(卷),期】2007(16)10

【摘要】采用TSMC 0.18 μm RF CMOS工艺设计了一种适用于DVB-T调谐器的可变增益中频放大器.该放大器以信号相加式单元为主体电路,采用三级级联结构,实现了对数增益随控制电压连续、近似线性地变化和51dB的增益动态范围.仿真结果表明,在1.8V电源电压下,电路工作电流为30mA,3dB带宽为2-156MHz.增益调节范围为7.4-58.4 dB,噪声系数小于8.6dB,输出三阶互调点大于0.6 dBm.【总页数】5页(P42-45,50)

【作者】郭峰;李智群;李晟;唐路;王志功

【作者单位】东南大学,射频与光电集成电路研究所;东南大学,射频与光电集成电路研究所;东南大学,射频与光电集成电路研究所;东南大学,射频与光电集成电路研究所;东南大学,射频与光电集成电路研究所

【正文语种】中文

【中图分类】TN4

【相关文献】

1.应用于导航接收机的CMOS可变增益放大器设计 [J], 剧梦婕;张晓林;申晶

2.应用于DVB-T/H调谐器的0.13μm CMOS混频器设计 [J], 吴晨健;李智群

3.具有60dB动态范围的CMOS可变增益放大器设计 [J], 李斌

4.高频调谐器中的CMOS可变增益放大器的设计 [J], 吴秀龙;陈军宁;柯导明;蒋先伟

5.2.4GHz可变增益CMOS低噪声放大器设计 [J], 丘聪;叶甜春;范军

因版权原因,仅展示原文概要,查看原文内容请购买。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2010年4月刊

计算机工程应用技术

信息与电脑

China Computer&Communication

1. 引言

随着集成电路设计技术的实用技术突破,数字电视技术逐渐成熟并普及,DVB-T (Digital Video Broadcasting-Terrestrial ),作为一种将数字电视技术和移动设备相结合的国际标准,已经被提出并且得到了一定的发展。

随后,人们又提出了一种DVB-H (Digital Video Broadcasting Handheld )的制式专门用于移动接收,利用手机、电脑等便携设备,随时随地收看数字电视已经成为当今世界的潮流。

数字电视调谐器专用芯片的集成度越来越高,全集成锁相环(PLL ,Phase locked-loop )被广泛应用在数字电视调谐器芯片中,电荷泵PLL 是当今最流行的锁相环结构,具有捕获频率范围宽,锁定时相位误差小等优点,被广泛应用于现代通信和射频领域中。

鉴频鉴相器和电荷泵作为锁相环电路的关键模块,其设计已成为研究热点。

本文采用SMIC 0.13μm CMOS 工艺,设计了一种结构简单且低功耗的鉴频鉴相器电路和充放电电流高度匹配的电荷泵电路。

2. 电荷泵锁相环的基本原理

电荷泵锁相环由五部分组成:鉴频鉴相器(PFD )、电荷泵(CP )、低通滤波器(LPF )、压控振荡器(VCO )和分频器(Divider ),如图1所示。

PFD 对参考信号和PLL 分频信号进行鉴频和鉴相,并输出信号控制电荷泵充、放电脉冲电流,CP 把PFD 输出的数字信号转化为脉冲电流,LPF 对CP 提供的电流脉冲积分,产生对VCO 的控制电压,从而构成反馈回路[1]。

图1 电荷泵锁相环原理图

当输入信号的频率f ref 与VCO 的输出信号频率f out 相差很大时,PFD 起鉴频的作用,产生一个与ωin -ωout 成正比的直流电压分量,通过CP 和LPF 加到VCO 的控制端,使VCO 输出信号频率迅速接近f ref 。

当频率差减到足够小时,相位锁定功能开始工作,这时PFD 相当于鉴相器,使环路锁定。

电荷泵锁相环是当今最流行的锁相环结构,具有捕获范围宽,锁定时相位误差小的优点。

3. 鉴频鉴相器电路设计

边沿触发式PFD 在[-2π,+2π]范围内输出与输入相位误差成线性关系,应用于大多数电荷泵锁相环电路中[2]。

本文设计的PFD 电路为一种经典的上升沿边沿触发式PFD 结构,整个PFD 结构如图2所示,该PFD 电路包括带有复位端的D 触发器、或非门、延时单元等模块。

该PFD 电路中D 触发器电路原理图如图3所示,该D 触发器电路结构简单,无静态功耗,动态功耗很低[3]。

PFD 电路中的复位信号由D 触发器的输出端Qn 经过或非门反馈到复位端,由于实际的PFD 电路中存在鉴相死区,本文采用两级反相器

级联构成延时单元,来增加D 触发器复位信号的回路延时,使得PFD 的输出信号的脉宽始终大于固有脉冲宽度,从而消除鉴相死区。

在CMOS 工艺中,电荷泵通常使用PMOS 管和NMOS 管分别组成电流源和电流沉,电流源需要低电平开关信号打开,而电流沉则需要高电平开关信号打开。

本文中PFD 的输出信号UP 经过一级反相器和传输门得到UPI 信号,另一路输出信号DW 经过两级反相器得到DWI 信号,分别接到电荷泵的输入端。

4. 电荷泵电路设计

电荷泵是电荷泵锁相环中非常重要的模拟电路模块,它的主要功能是将PFD 输出的数字信号UP 和DW 转换成连续的模拟信号,来控制VCO 的振荡频率。

传统的电荷泵电路都使用MOS 管开关,并由两个带开关的电流源组成。

本文在传统电荷泵电路的基础上[4],采用与电源电压无关的基准电流源电路,引入运算放大器和共源共栅电流镜电路,设计实现

DVB-T/H调谐器中鉴频鉴相器和电荷泵的设计

王丹 东南大学集成电路学院,江苏 南京 210096

李智群 东南大学射频与光电集成电路研究所,江苏 南京 210096

摘要:采用SMIC 0.13μm CMOS 工艺,设计了一种低功耗的鉴频鉴相器和电荷泵电路。

其中电荷泵采用与电源电压无关的基准电流源电路,引入运算放大器和共源共栅电流镜电路,实现了电荷泵充放电电流的高度匹配。

后仿真结果表明,在1.2V 电源电压下,电荷泵的输出电压在[0.18,1.12] V 范围内时,CP 的充放电电流为100μA ,电流失配率为0.08%。

鉴频鉴相器和电荷泵电路的总功耗为1.4mW 。

关键词:锁相环;鉴频鉴相器;电荷泵;电流匹配

中图分类号:TP39 文献标识码:A 文章编号:1003-9767(2010)04-0189-02

图2 PFD整体电路结构图

图3 D触发器电路原理图

2010年4月刊

计算机工程应用技术

信息与电脑

China Computer&Communication

了一个充放电电流高度匹配的电荷泵电路

[5]

,电路结构如图4所示。

电荷泵电路中

的OPA 采用文献[6]中的n 沟道输入折叠共源共栅运算放大器的电路结构,其中运放的增益为77dB ,相位裕度大于85度。

5. 芯片版图设计及后仿真结果

版图设计时,PFD 版图的MOS 管以及金属走线采用完全对称结构,避免不对称而带来的延时不同所造成的影响。

CP 电路版图中镜像电流源采用对称结构设计,

从而实现电流的精确镜像。

PFD 作为数字电路,对噪声比较敏感,故PFD 和CP 采用独立电源供电。

本次设计采用的是SMIC 公司的0.13μm 双阱、单层多晶硅、八层金属标准CMOS 工艺,基于Cadence 软件平台使用Spectre RF Virtuoso 工具进行版图设计。

对电荷泵充放电电流的匹配度进行后仿真,仿真结果如图5所示。

后仿真结果表明,在1.2V 电源电压下,电荷泵的输出电压在[0.18,1.12] V 范围内时,电荷泵的充放电电流为100μA ,电流失配率为0.08%。

PFD 和CP 的总功耗为1.4mW。

图4 电荷泵电路结构图

6. 结论

本文设计了一种低功耗的鉴频鉴相器和电荷泵电路,电荷泵电路实现了充放电电流的高度匹配,提高了电荷泵锁相环的性能。

参考文献:

[1] 李智群,王志功编著。

射频集成电路与系统。

科学出版社,2008年8月

[2] 毕查德.拉扎维著,陈贵灿,程军,张瑞智译。

模拟CMOS 集成电路设计。

西安交通大学出版社,2003年2月

[3] Won - Hyo Lee, Jun - Dong Cho, and Sung - Dae Lee. A High Speed and Low Power Phase-Frequency Detector and Charge – pump. Design Automation Conference Asia and South Pacific, V ol.1, pp: 269-272, 1999

[4] Jae-Shin Lee, Min-Sun Keel, Shin-I1 Lim and Suki Kim. Charge pump with perfect current matching characteristics in phase-locked loops. ELECTRONICS LETTERS, V ol. 36, No. 23, pp: 1907, Nov 2000

[5] 薛红,李智群,王志功等。

低杂散锁相环中的电荷泵设计。

半导体学报,第28卷第12期,2007年12月,页码:1988-1992

[6] Phillip E. Allen, Douglas R. Holberg 著,冯军,李智群译。

CMOS 模拟集成电路设计。

电子工业出版社,2005年3

月

图5 CP的充放电电流匹配曲线

方法。

采用负反馈以后,通常可以把PSSR 提高到70dB 以上。

六、D类放大器的应用

D 类放大器的应用十分广泛,总的来说,只要是有进行音频放大需要的场合,都能运用到D 类放大器。

因此,从最初的电话机、收音机、电视机、音响设备,直至到现代的手机、MP3播放机、LCD 电视机、电脑音响都可以采用D 类放大器。

然而和现代的模拟音频放大器相比,D 类放大器目前的价格还略为高些。

因为D 类放大器的最大优点是效率高、节电。

对于它来说使用干电池比较合适。

如:手机、笔记本电脑、携带型DVD 播放机等。

这些设备在采用了D 类放大器同时也大大延长电池的寿命。

其它如大功率的音响设备, 因为耗电很大,所以也是非常需要采用高效率的D 类放大器。

结语

总体来说,D 类放大器经过了近些年来的发展,已经成功地运用到了手机及一般便携式产品中。

D 类放大器今后的发展会取代普通的AB 类产品,高级D 类放大器的可选择的范围正在不断扩大,使得各种消费类终端设备(如平扳显示器、PDA 、智能电话、移动电话、汽车无线电等)的设计者可以提高产品的功率性能,同时保持甚至减小产品体积和成本。

D 类放大器时代的到来使设计人员能够在产品中实现高性能音频,给消费者带来更好的体验。

参考文献:

[1]吴忠智,吴加林.中(高)压大功率变频器应用手册[M].北京:机械工业出版社,2003.11

[2]丁明.实作D 类功率放大器[J].无线电与电视,2002(2):29-32.[3]韩宪柱.数字音频技术及应用[M].北京:中国广播电视出版社

(上接第188页)。