全差分CMOS运算放大器的设计毕业设计

一种高增益CMOS全差分运算放大器的设计

邮局订阅号:82-946360元/年技术创新电子设计《PLC 技术应用200例》您的论文得到两院院士关注一种高增益CMOS 全差分运算放大器的设计Design of a High-gain CMOS Fully Differential Operational Amplifier(江南大学)李杨先顾晓峰浦寿杰LI Yang-xian GU Xiao-feng PU Shou-jie摘要:设计了一种用在高精度音频Σ-ΔA/D 转换器中的高增益CMOS 全差分运算放大器。

该运算放大器采用了套筒式共源共栅结构和开关电容共模反馈电路。

通过分析和优化电路性能参数,实现了高增益和低功耗。

采用SMIC 0.35μm CMOS 工艺,经Spectre 仿真验证,电路在3.3V 电源电压和2.6pF 负载电容条件下,单位增益带宽为110MHz,开环直流电压增益达76dB,功耗为1.4mW 。

关键词:运算放大器;套筒式共源共栅;高增益;A/D 转换器中图分类号:TN402文献标识码:AAbstract:A high -gain CMOS fully differential operational amplifier has been designed for the application to high -resolution audio Σ-ΔA/D converters.The telescopic cascade structure and the switched capacitor common -mode feedback circuit were adopted in this operational amplifier.High gain and low power dissipation were achieved by analyzing and optimizing the circuit parameters.The Spectre simulation using SMIC 0.35μm CMOS process shows that,with 3.3V power voltage and 2.6pF capacitor load,the circuit has a unity-gain bandwidth of 110MHz,an open-loop gain of 76dB and a power dissipation of 1.4mW.Key words:Operational amplifier;Telescopic cascade;High-gain;A/D converter文章编号:1008-0570(2009)10-2-0207-031引言运算放大器作为模拟系统和混合信号系统中的一个重要电路单元,广泛应用于数/模与模/数转换器、有源滤波器、波形发生器和视频放大器等各种电路中。

全差分运算放大器设计

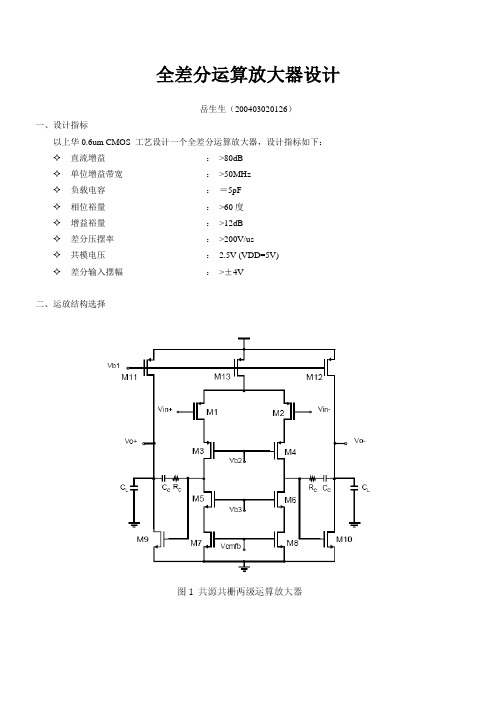

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

全差分运算放大器设计

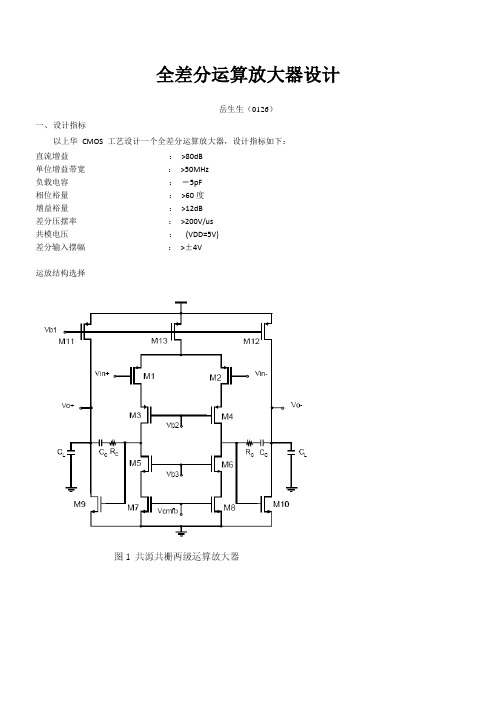

全差分运算放大器设计岳生生(0126)一、设计指标以上华CMOS 工艺设计一个全差分运算放大器,设计指标如下:直流增益:>80dB单位增益带宽:>50MHz负载电容:=5pF相位裕量:>60度增益裕量:>12dB差分压摆率:>200V/us共模电压:(VDD=5V)差分输入摆幅:>±4V运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于,输出端的所有PMOS 管的,DSAT PV之和也必须小于。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

性能指标分析差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12)第一级增益 1351113571135135753()m m m o o o o o m m m m o o o o m m g g g g g g G A R r r r r g g r r r r=-=-=-+P第二级增益92291129911()m o o o m m o o g g G A R r r g g=-=-=-+P 整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

cmos运算放大器设计

目

录

摘要 ................................................................... 3 Abstract ................................................................ 4 0 文献综述 ............................................................ 5 0.1 0.2 0.3 0.4 0.5 0.6 1 集成电路概述 ................................................... 5 集成电路的发展 ................................................. 5 集成电路应用领域 ............................................... 6 CMOS 集成电路................................................ 9 运算放大器 ..................................................... 9 CMOS 运算放大器............................................. 10

4

CMOS 运算放大器版图设计 .......................................... 25 4.1 版图设计流程 ................................................... 25 4.2 工艺设计规则 ................................................... 26 4.3 单元器件的绘制——图元 ......................................... 27 4.4 4.5 CMOS 放大器的版图设计........................................ 31 T-Spice 仿真 ................................................... 34

一种高增益宽带CMOS全差分运算放大器

conlbming the s仃uctllre Offolded cascode、two d洎奄rential-pa趣CMFB aIld gain-

boos锄g technique.The operational amplifier is desi弘ed i11 TSMC 0.25叫l 2P5P

CMOS process and simulated wim cadence spec仃e llIlder the condition of 2.5V sin百e

cMOS全差分运算放大器。基于TSMc O.25岫2P5M cMOS工艺,利用cadence

spec仃e仿真工具分别对所设计的运放电路进行了仿真分析。结果表明,在2.5V的 单电源电压下,运算放大器的直流开环增益为104dB,单位增益带宽为385MHz, 达到并超出了最初提出的增益和带宽的要求。论文还分析了一种电荷定标的D缓 转换器以及带自举开关的采样保持器原理,利用本文设计的全差分运算放大器作 为口核分别应用于一个8位的D/A转换器和50MsPS的采样保持器中,并取得了

叩erational锄plifier、common mode fcedback a11d gain.boosting technique,and desi印

a cMOS fhlly di船rential operational锄plmer with hi幽gaill and wide band、Ⅳidth by

并基于TsMc 0.25岫cMOs工艺的sⅡ讧3V3模型,利用Cadence spec仃e工具对所设

计的电路进彳亍了仿真分析,其结果己满足并超出所设计的要求。 本文的结构就是按照作者在论文完成中的工作顺序进行安排的。 第二章,主要介绍了几种常用的CMOs全差分运算放大器结构以及共模反馈

CMOS运算放大器版图设计毕业论文

CMOS运算放大器版图设计毕业论文目录前言 (5)第1章绪论 (6)1.1 课题背景 (6)1.1.1 研究背景 (6)1.1.2研究容 (7)1.2 电路设计流程 (8)1.3 主要工作以及任务分配 (10)1.3.1主要工作 (10)1.3.2 任务分配 (10)第2章版图基础知识 (11)2.1 版图的设计简介 (11)2.1.1 版图的概念 (11)2.1.2 版图中层的意义 (11)2.2 CMOS工艺技术 (14)2.2.1概述 (14)2.2.2 CMOS工艺的一些主要步骤 (15)2.2.3 CMOS制造工艺的基本流程 (16)2.3 设计规则 (18)2.4 MOS集成运放的版图设计 (22)第3章 CMOS运算放大器简介 (23)3.1 概述 (23)3.2两级CMOS运算放大器的优点 (24)3.3 两级运算放大器原理简单分析 (24)第4章 CMOS运算放大器的仿真 (27)4.1 概述 (27)4.2 MOS运算放大器技术指标总表 (27)4.3仿真数据 (29)4.3.1 DC分析 (29)4.3.2测量输入共模围 (30)4.3.3 测量输出电压围 (31)4.3.4 测量增益与相位裕度 (33)4.3.5 电源电压抑制比测试 (34)4.3.6 运放转换速率和建立时间分析 (36)4.3.7 CMRR的频率响应测量 (38)第5章算放大器版图设计 (40)5.1 Cadence使用说明 (40)5.2 版图设计 (42)5.3 CMOS运放版图 (43)第6章总结 (44)参考文献 (44)致谢词 (45)外文资料原文 (45)外文资料译文 (46)第1章绪论1.1 课题背景1.1.1 研究背景运算放大器(简称运放)是具有很高放大倍数的电路单元。

在实际地电路中,通常结合反馈网络共同组成某种功能模块。

由于早期应用于模拟计算机中,用以实现数字运算,故得名“运算放大器”。

毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]

![毕业设计(论文)-cmos运算放大电路的版图设计[管理资料]](https://img.taocdn.com/s3/m/15f996a177232f60dccca185.png)

目录摘要 (3)第一章引言 (3)§ (3)§ CMOS 电路的发展和特点 (5)第二章CMOS运算放大器电路图 (8)§Pspice软件介绍 (8)Pspice运行环境 (12)Pspice功能简介 (12)§CMOS运算放大器电路图的制作 (14)§小结 (20)第三章版图设计 (20)§L-EDIT软件介绍 (20)§设计规则 (21)§集成电路版图设计 (24)PMOS版图设计 (24)NMOS版图设计 (27)CMOS运算放大器版图设计 (27)优化设计 (32)第四章仿真 (40)§DRC仿真 (41)§LVS 对照 (42)第五章总结 (48)附录 (50)参考文献 (52)致谢 (53)摘要介绍了CMOS运算放大电路的版图设计。

并对PMOS、NMOS、CMOS运算放大器版图、设计规则做了详细的分析。

通过设计规则检查(DRC)和版图与原理图对照(LVS)表明,此方案已基本达到了集成电路工艺的要求。

关键词:CMOS 放大器 NMOS PMOS 设计规则检查版图与原理图的对照AbstractThe layout desigen of CMOS operation amplifer is presented in this the layouts and design rules of PMOS,NMOS, and CMOS operation amplifer. The results of design rule check(DRC)and layout verification schmatic(LVS) shown that the project have already met to the needs of IC fabricated processing. Keywords: CMOS Amplifer NMOS PMOS DRC LVS第一章引言1.1 集成电路版图设计的发展现状和趋势集成电路的出现与飞速发展彻底改变了人类文明和人们日常生活的面目。

全差分运算放大器设计

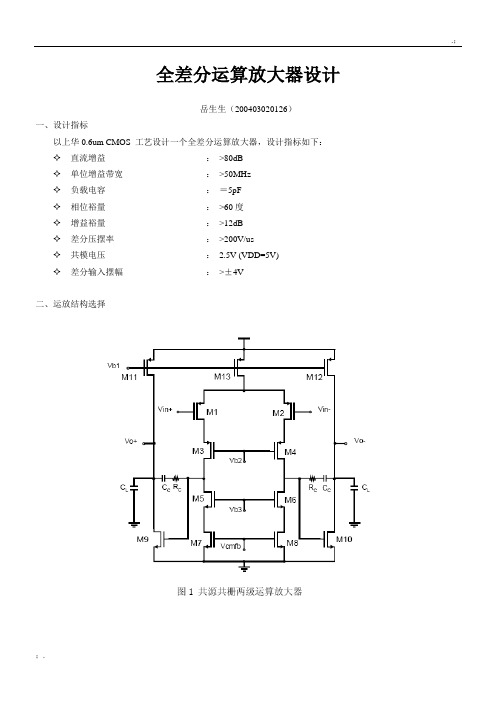

全差分运算放大器设计岳生生(200403020126)一、设计指标以上华0.6um CMOS 工艺设计一个全差分运算放大器,设计指标如下:✧直流增益:>80dB✧单位增益带宽:>50MHz✧负载电容:=5pF✧相位裕量:>60度✧增益裕量:>12dB✧差分压摆率:>200V/us✧共模电压:2.5V (VDD=5V)✧差分输入摆幅:>±4V二、运放结构选择运算放大器的结构重要有三种:(a )简单两级运放,two-stage 。

如图2所示;(b )折叠共源共栅,folded-cascode 。

如图3所示;(c )共源共栅,telescopic 。

如图1的前级所示。

本次设计的运算放大器的设计指标要求差分输出幅度为±4V ,即输出端的所有NMOS 管的,DSAT NV之和小于0.5V ,输出端的所有PMOS管的,DSAT PV之和也必须小于0.5V 。

对于单级的折叠共源共栅和直接共源共栅两种结构,都比较难达到该要求,因此我们采用两级运算放大器结构。

另外,简单的两级运放的直流增益比较小,因此我们采用共源共栅的输入级结构。

考虑到折叠共源共栅输入级结构的功耗比较大,故我们选择直接共源共栅的输入级,最后选择如图1所示的运放结构。

两级运算放大器设计必须保证运放的稳定性,我们用Miller 补偿或Cascode 补偿技术来进行零极点补偿。

三、性能指标分析1、 差分直流增益 (Adm>80db)该运算放大器存在两级:(1)、Cascode 级增大直流增益(M1-M8);(2)、共源放大器(M9-M12) 第一级增益1351113571135135753()m m m o o o o o m m m m o o o o m m g g gg gg G A R r rr r g g r r r r=-=-=-+第二级增益92291129911()m o o o m m o o gg G AR r rgg=-=-=-+整个运算放大器的增益:4135912135753911(80)10m m m m overallo o o o m m o o dB g g g gAA A g g g gr r r r ==≥++2、 差分压摆率 (>200V/us )转换速率(slew rate )是大信号输入时,电流输出的最大驱动能力。

(完整word)全差分高增益、宽带宽CMOS运算跨导放大器的设计

目录1 引言 (1)2 软件介绍 (3)3 运算放大器设计基础 (5)3.1运放的主要性能指标 (5)3.2运算放大器的基本结构 (6)3.2.1全差分运放 (6)3.2.2套筒式结构 (7)3.2.3折叠式结构 (8)4 系统总体设计 (10)4.1电路设计的整体结构 (10)4.2 主放大电路设计 (11)4.3 偏置电路的设计 (13)4.4 输出级的设计 (13)4.5 共模反馈的设计 (14)4.6 总体布局 (15)5 仿真与分析 (17)5.1运放直流与交流特性 (17)5.2噪声特性分析 (19)5.3电源抑制比 (19)5.4设计指标 (20)5.5放大器参数 (21)6 版图设计与分析 (22)6.1 L-Edit介绍 (22)6.2版图设计规则 (22)6.3基本器件版图设计 (23)6.3.1 NMOS版图设计 (23)6.3.2 电容电阻版图设计 (24)6.4版图的总体设计 (26)6.4.1主电路模块版图 (26)6.4.2偏置模块版图 (27)6.4.3输出模块版图 (27)6.4.4整体模块版图 (28)6.5 LVS版图比对 (29)7 结论 (31)谢辞 ................................................................................................... 错误!未定义书签。

参考文献 .. (32)附录1 (33)附录2 (35)1 引言集成运算放大器(Integrated Operational Amplifier)简称集成运放,是由多个CMOS管与电容电阻通过耦合方式实现提高增益的模拟集成电路[1]。

集成运放具有增益高、输入阻抗大、输出阻抗低、共模抑制比高和失调与漂移性小等优点,而且当输入电压值为零时,输出值也为零。

集成运放是构成常用集成电路系统的通用模块[2] [3]。

基于CMOS全差分运算放大器的全集成有源滤波器的设计_解读

天津大学硕士学位论文基于CMOS全差分运算放大器的全集成有源滤波器的设计姓名:刘莉申请学位级别:硕士专业:电路与系统指导教师:滕建辅20090501摘要随着集成电路技术和通信技术的发展,全集成有源滤波器的设计已经成为国际学术界所关注的前沿课题之一。

特别是近年来,片上系统(System…on a Chip 的发展也迫切需要解决有源滤波器的全集成问题。

本文在全面归纳总结国内外全集成有源滤波器的研究现状和发展动态的基础上,从网络综合理论出发,较系统地研究了基于信号流图模拟法的全集成有源滤波器的设计技术,利用双端接载的无源LC梯形滤波电路具有响应对元件变化灵敏度低的优点,将其作为原型滤波器,详细地推导了六阶Butterworth低通滤波器和六阶Chebyshev带通滤波器的信号流图,并实现了相应的基于反相积分器的有源RC滤波器和全差分有源RC滤波器。

并从全集成的角度出发,着重研究了作为滤波器的关键部分的全差分运算放大器的特性对全集成有源滤波器的性能的影响,在此基础上设计了一种适合于本文中所设计的全集成有源RC低通和带通滤波器的宽摆幅、低功耗的全差分运算放大器。

在设计及仿真过程中,具体的研究了运算放大器的各项性能指标对全集成有源滤波器的选频特性和稳定性的影响,给出了在滤波器设计过程中如何选择适当的运算放大器的方法。

滤波器电路采用了特许半导体(Chartered0.35urn CMOS工艺进行设计。

通过使用Cadence设计环境下的Spectre工具仿真,运放单位增益带宽达到 128MHz,相位裕度为61。

,低频增益78dB,功耗小于1.3mW,保证了全集成有源滤波器的选频特性和稳定性。

仿真结果表明,全集成有源RC低通和带通滤波器的各项性能指标都满足设计要求,并实现了滤波器的低功耗设计。

关键词:全集成有源滤波器信号流图CMOS全差分运算放大器AB STRACTWith the development of integrated circuit and telecommunication technologies, the design of full-integrated active filters has become one of the mo st important advances in analog VLSI and attracted much attention in the academic world. Particularly,in recent years,the problem,which cries for solving,isthe full.integration of the active filters,for the development of System-on-a-Chip.In this dissertation,the international and national researches status quo and the developing trends ofthe full-integrated active filters are systematically reviewed.The design technology of full-integrated active filters that based on the theory of network synthesis and signal flow graph is deeply studied.On the basis of the doubly terminated LC ladder prototype,whose magnitude response is extraordinarily insensitive to perturbations of the LC elements and to the terminating resistances,the detailed signal flow graphs of sixth-order Butterworth low-pass fiker and sixth—order Chebyshev band-pass filter are derived respectively,and the corresponding active RC filters based on inverting integrator and full-differential active RC filters are realized. Focusing on the full-integration,special emphasis is laid tO po缸OUt the influence that the performance of the fully differential operational amplifier makes to the active filters.According tO the analysis,a fully differential operational amplifier with wider unity・gain bandwidth and low power is designed for the sixth-order Butterworth low-pass filter and sixth-order Chebyshev band—pass filter inthis paper,and then a practical method for choosing the suitable operational amplifieris proposed.Filter ckcuk is designed with Chartered O.35I_tm CMOS technology ckcuit is simulated by the Spectre in Cadence,Unity-gain bandwidth of operational amplifier is reached 128MHz,phase margin is 61。

全差分CMOS运算放大器的设计

全差分CMOS运算放大器的设计全差分CMOS运算放大器(Fully Differential CMOS Operational Amplifier)是一种常用于模拟、混合信号和通信电路中的放大器。

全差分运算放大器结合了差分放大器和普通运算放大器的优点,具有更好的共模抑制、抗干扰能力和更高的增益。

1.设计差动放大器:差动放大器是全差分CMOS运算放大器的核心部分,其一般由两个输入差分对和一个负载电阻组成。

在设计差动放大器时,首先需要确定放大器的增益、带宽和功耗等要求。

然后,选择适当的晶体管尺寸和偏置电流来满足这些要求。

2.设计电流镜:电流镜主要用于稳定差动放大器的工作点。

常用的电流镜电路有P型电流镜和N型电流镜。

在设计电流镜时,需要考虑放大器的输入阻抗、输出阻抗和功耗。

3.设计共模反馈电路:共模反馈电路主要用于提高全差分CMOS运算放大器的共模抑制比。

在设计共模反馈电路时,需要确定合适的电压分压比例和电容值,以及选择合适的晶体管尺寸和偏置电流。

4.偏置电流源设计:5.电源设计:6.输入和输出接口设计:7.稳定性分析和优化:在设计全差分CMOS运算放大器时,还需要进行稳定性分析和优化。

常用的稳定性分析技术有迭代法、校正法和频率响应法。

稳定性优化技术有补偿电容法、极点分布法和增益调整法。

8.仿真和验证:最后,设计完成的全差分CMOS运算放大器需要进行仿真和验证。

常用的仿真和验证工具有SPICE软件、电路仿真器和实验测量仪器。

通过仿真和验证,可以评估放大器的性能和电路的可靠性。

最后,需要注意的是,在进行全差分CMOS运算放大器的设计时,应遵循设计规范和标准,如功耗规范、电压规范和噪声规范,以确保设计的可靠性和一致性。

同时,应密切关注工艺制程、温度变化等因素对电路性能的影响,并进行相应的校准和补偿。

CMOS全差分低噪声运算放大器的研究与设计方案(运放的理论性文章)

CMOS全差分低噪声运算放大器的研究与设计摘要运算放大器在现代科技的各个领域得到了广泛的应用,如A/D与D/A转换器、有源滤波器、自动增益控制器等,针对不同的应用领域出现了不同类型的运放。

本文详细介绍了一种可以用在微弱信号测量系统和高保真要求的音频系统中的全差分结构低噪声运放,使用0.18微M的CMOS工艺实现,供电电压是1.8V,根据低噪声的要求选择了合适的结构,在第一级采用PMOS作为输入端的套筒式共源共栅放大电路,第二级使用共源电路,在减少运放内部器件产生的噪声同时,考虑了减少外界的电源串扰噪声影响,完成了主电路的设计,另外为了使差分电路的输出直流电压偏置在理想位置,分析并设计了基于负反馈原理的共模反馈电路。

文章的最后对电路的重要参数如直流增益、相位裕度及输入参考噪声做了比较详细的分析与推导,并在SUN工作站上使用Cadence的模拟设计工具IC5033对电路进行了全面的仿真,仿真的结果显示在1 KHz处的输入参考噪声可以达到6nV币弧左右,这是一个相当好的结果。

关键词:运放低噪声全差分CMOS工艺目录摘要1目录1前言2第一章运算放大器的原理与应用31.1运算放大器的原理31.1.1理想运放31.1.2实际运放51.2全差分运放61.3运放的基本应用71.4低噪声运放的应用8第二章MOS器件工作原理102. 1 MOS器件基础102. 2 MOSFET的闭值电压112. 3 MOSFET的工作区域112. 3. 1线性区112. 3. 2饱和区132. 4二级效应152. 4. 1体效应152. 4. 2沟道长度调制效应162. 4. 3亚阈值效应172. 5 MOS管的小信号模型17第三章CMOS单级放大器193.1反相器193.1.1有源负载反相器193. 1. 2电流源负载反相器203. 2差分放大器203. 2. 1共模输入范围213. 2. 2差分放大器的增益213. 3共源共栅放大器22第四章电路噪声234. 1噪声幅值分布234. 2系统对噪声的影响244. 3器件噪声254. 3. 1电阻的热噪声254. 3. 2 MOS管的沟道热噪声254. 3. 3 MOS管闪烁噪声25第五章全差分低噪声运算放大器的设计255. 1低噪声运算放大器的结构设计255.1.1低噪声运算放大器的整体结构255.1.2主电路的设计265. 1. 3共模反馈电路的设计275. 2运放主要参数的仿真分析285. 2. 1运放的开环增益的仿真与分析285. 2. 2运放频率补偿的仿真与分析295.2.3运放电源纹波抑制比的仿真与分析325.2.4运放噪声的仿真与分析325.2.5运放线性度的仿真与分析335. 2. 6运放速度的仿真与分析345.2.7运放的温度特性35结束语36参考文献36前言运算放大器的本质是一个高增益的放大器,它可能是现代模拟电路中最通用和重要的单元,其地位可以相当于数字电路中的“门”电路,在外部反馈网络的配合下,它的输出与输入电压(或电流)不需要依赖开环关系,而是可以灵活地实现各种特定的函数关系,因此可以对不同的信号进行组合、处理。

快速全差分CMOS 运算放大器的设计

《IC课程设计》报告快速全差分CMOS 运算放大器的设计姓名:学号:班级: 1院系:专业:同组人姓名:李四王二目录1设计目标 (1)2相关背景知识 (1)3设计过程 (2)3.1 电路结构设计 (2)3.1.1 电路结构的选择 (2)3.1.2 折叠式共源共栅 (4)3.1.3 共模反馈电路 (5)3.1.4 偏置电路 (6)3.1.5 频率补偿 (7)4 电路仿真 (7)5 讨论 (9)6 收获和建议 (9)参考文献 (9)1设计目标设计一带宽为500MHz的全差分CMOS运算放大器。

设计指标如下:工作电源电压:3.3V开环增益:≥65 dB单位增益带宽: ≥500MHz相位裕量:≥50 degree差分压摆率: ≥200V /μs负载电容: =2pF差分输出摆幅: ≥±2V谐波失真:≤0.1%静态功耗:尽可能小2相关背景知识科学技术的发展带来了各行各业的改革,各种新型的高科技产品不断被应用到我们生活和生产中。

科技进步同样也带来了电表行业的改革,传统的老式机械表已经不适应现代的生活需求,更先进的数字电表将取而代之。

电表计量芯片是数字电表的核心,它的性能在很大程度上决定了该电表的性能。

而在电表计量芯片中需要将电流、电压信号转换成数字信号以便进行高精度的后续处理,这就需要用到数模转换器(Analog to Digital Converter)。

一个高性能的数模转换器则是先进的电表计量芯片必不可少的。

目前随着大规模集成电路的发展,Sigma -delta 数模转换器(Sigma-delta ADC)得到了迅速的发展并广泛应用于通讯、音频处理和精密测量方面。

在电表计量芯片中也广泛采用这用结构以实现高精度的数模转换。

3设计过程3.1 电路结构设计3.1.1 电路结构的选择根据上表所提供的性能要求,由于普通的单级结构运放无法提供这么大的增益,而三级或更多级结构将带来稳定性的问题,对此我们选择具有两级放大功能的运算放大器。

高增益CMOS全差分运放的研究和设计

possession of the market and their performance are in high challenge.To solve this problem,we had to take care in such aspect as circuit structure、material、teclmology.

operational amplifier will enhance the properties of the system.Now,the research

focus on the high speed signal processing and low power dissipation,which are appropriate domains we can make breakout.

1.3本文的工作以及文章组织

本文就是对工作在3V的运放放大电路进行研究,并分析各类 运放的性能指标。按照所提出的性能指标选择电路结构,这里我们 采用的是运算放大电路中的套筒式(telescopic)结构。通过对其性 能的分析,并进行器件参数上的优化,设计出一个增益在78dB, 功耗只有l 5roW的运算放大器单元,基本能够满足了设计的要求, 最后在CADENCE上画出版图。

这里我们具体的介绍一下目前运放的性能中一些重要的指标参 数,主要有开环增益、单位增益带宽、输出摆幅、建立时间、噪声等。 在后面的设计中,我们将进一步说明对每个参数的取舍以及折中的处 理办法。

全差分运算放大器设计

ϕ2 = 180° − PM − ϕ1 ≤ 30°

ωu ≤ tan 30° =0.577 ⇒ ω p2 ≥ 1.73 ,取 ω p2 = 2

ω p2

ωu

ωu

3

《通信系统混合信号 VLSI 设计》课程设计报告

2003 年 12 月 31 日

作者: 唐长文, 菅洪彦

( ) ( ) go1go3 + go5go7

流镜及输出负载。这样,一方面降低了功耗;另一方面保证共模放大器与差模放大器在交流特 性上保持完全一致。因为共模放大器的输出级与差模放大器的输出级可以完全共用,电容补偿 电路也完全一样。只要差模放大器频率特性是稳定的,则共模负反馈也是稳定的。这种共模负 反馈电路使得全差分运算放大器可以像单端输出的运算放大器[7]一样设计,而不用考虑共模负 反馈电路对全差分运算放大器的影响。

=

Cgs3

gm3 + Cgd1 + Cdb1 + Csb3

6. 共模负反馈: CMFB 为了稳定全差分运放输出共模电压,必须设计共模负反馈电路。在设计输出平衡的全差分

运算放大器的时候,必须考虑到以下几点[1]: 共模负反馈的开环直流增益要求足够大,最好能够与差分开环直流增益相当; 共模负反馈的单位增益带宽也要求足够大,最好接近差分单位增益带宽; 为了确保共模负反馈的稳定,一般情况下要求进行共模回路补偿; 共模信号检测器要求具有很好的线性特性; 共模负反馈与差模信号无关,即使差模信号通路是关断的。 图 4 是一种共模负反馈实现结构[1],该结构共用了共模放大器和差模放大器的输入级中电

等效输入噪声

: 20 nV Hz

输入失调电压 差分输出摆幅

: <10mV : > ± 4V

CMOS全差分跨导运算放大器的建模与设计

CMOS全差分跨导运算放大器的建模与设计傅文渊;凌朝东【摘要】Research of high-speed and high-gain transconductance amplifier with the structure of gain-boost, the mathematical modeling and Matlab simulation is presented for gain-boost operational amplifier. Designed operational amplifier is used in 12 bit 100 M SPSADC, and the optimal design on the auxiliary amplifier bandwidth can be obtained. Simulation results show that gain is 106 dB which increses of 55 dB if an auxiliary operational amplifier is added. Besides, if we the auxiliary operational, dominant pole is greatly reduced and non-dominant pole slightly decreases, but the addition of auxiliary amplifier does not affect the speed of the operational amplifier.%研究带增益自举结构的高速、高增益跨导运算放大器,并对增益自举运放建立数学模型和进行Matlab仿真验证.将设计的运算放大器应用于12 bit 100 M SPS模数转换器(ADC)中,可得到辅助运放的带宽的最佳设计.仿真结果表明:添加辅助运放后,可以达到106 dB的增益,增加了55 dB;添加辅助运放后的主极点较之前大大减小,次主极点略有减小,但辅助运放的添加并不会影响运放使用时的速度.【期刊名称】《华侨大学学报(自然科学版)》【年(卷),期】2012(033)001【总页数】4页(P23-26)【关键词】运算放大器;全差分跨导;增益自举;模数转换器;互补金属氧化物半导体【作者】傅文渊;凌朝东【作者单位】华侨大学信息科学与工程学院,福建厦门361021;厦门市专用集成电路系统重点实验室,福建厦门361008;华侨大学信息科学与工程学院,福建厦门361021;厦门市专用集成电路系统重点实验室,福建厦门361008【正文语种】中文【中图分类】TP722.770.2在高速、高精度流水线型模数转换器中,模拟信号经采样保持后得到的信号将经过多级流水线级进行处理.每个流水线级的输入信号经过Flash模数转换器(ADC)得到对应的数字码,而其中无法被分辨的残余信号被本级放大后再输出到下一级进行处理[1],得到残差信号并将其放大的电路即为残差放大器(MDAC).残差放大器是以运放为基础搭建的开关电容放大器,其精度和速度直接影响到整个流水线ADC的速度和精度.为满足高精度,要求运算放大器必须具有非常高的开环增益,倾向于选择多级结构和长沟道器件[2];为了实现高速,要求运算放大器具有大的单位增益带宽,而单级运放结构和短沟道器件是能够满足的[3].然而,两者不可避免会产生冲突,解决问题的关键是寻找一种满足要求的折衷结构.增益自举技术大大增加了输出阻抗以提高运放增益[4],但并不增加额外的共源共栅器件,不会影响主运放的输出摆幅、单位增益带宽.基于增益自举结构的运算放大器[5]利用辅助运放来提高增益,且不会影响运放的输出共模范围和速度,适用于高速、高精度模数转换器.本文基于12bit 100MSPS模数转换器,设计全差分跨导运算放大器,并对增益自举运放建立数学模型和Matlab仿真验证.采用增益自举运算放大器结构,其频率响应特性近似为单极点系统,并能实现高增益、大带宽和快速建立时间,如图1所示.该运算放大器由一个套筒式共栅共源主运放和两个辅助运放构成.M1的工作像一个反馈电阻,检测输出电流并把电流转换为电压;然后,将电压经辅助放大器A1通过M2的栅端反馈到输出电流上,以此减小M2漏极电压的变化对Vx的影响,从而使输出电流更加稳定,得到更高的输出阻抗.设辅助运放直流增益为Aadd,根据电流-电压反馈原理,电路的输出阻抗增大了Aadd倍.因此,主运放的套筒式共栅共源结构加上辅助运放后,其运放的直流增益增大为在增益自举技术中,辅助运放A1的添加会影响主运放的性能,因此需要分析两者的关系,使整体运放达到最好的指标.考虑整体运放的开环特性,为简单计,设辅助运放为单极点系统,其传输函数为此时,增益自举运放的增益可以表示为式(3)中:gm1为输入管 M1 管跨导;CL 为负载电容;Rout(s)是频率的函数.Rout(s)的表示式为式(4)中:gm2为 M2 管跨导;rds1与rds2分别为 M1 与 M2 管的输出阻抗.将式(4)代入式(3),可得到把式(2)代入式(5)并化简,可得到总的开环增益为从式(6)可以看到,增益自举运放存在一个左半平面零点,其值等于辅助运放的单位增益带宽(WGB),即ωZ=Aaddω1=WGBadd.由式(6)可以推导出其主极点和次主极点分别为式(8)中:第1项为辅助运放的单位增益带宽;第2项为没有添加增益自举技术时主运放的主极点.当次主极点的第1项远大于第2项时,第2个极点p1≈Aaddω1≈ωZ.由此可以看出,辅助运放对整体运放产生了位置很相近的一个零极点对.进一步考虑其闭环特性.在首级残差放大器中,运算放大器处于反馈系数为β的闭环结构中.此时,闭环传输函数可表示为从式(10)中可以看出,零极点对的存在给运放的建立特性带来了影响.为了尽量减小其影响,必须使τ1>τ2,则要求β·WGBmain<WGBadd,同时确保Vout 数值有效,则有.由此可得当满足上述要求时,辅助运放的频率特性对整个放大器的频率特性没有太大的影响.增益自举的单位增益带宽主要由主运放的单位增益带宽决定,可表示为针对辅助运算放大器的主极点,编写Matlab程序,得出辅助运放的主极点和整体运放的建立时间、峰值电压和峰值时间的关系图,如图2所示.由图2可知,当辅助运放的主极点增大时,运放的峰值时间将减少,且减少趋势逐步降低;在300~750MHz时,峰值时间变化最小.同时,运放的峰值电压随着辅助运放主极点增大而增加.在320~890MHz之间,运放的建立时间随着辅助运放主极点的增加而减少,但变化幅度较少(低于0.003 7%).因此,可以得出辅助运放的主极点在320~890MHz之间变化时,对增益自举运算放大器的建立时间影响不大,而在220~230MHz之间,运放建立时间减少1ns,变化幅度较为剧烈(10%).此时,辅助运放的主极点将对整体运放产生迟滞作用,增大整体运放的建立时间.由此得到设计时在满足式(13)条件的基础上,辅助运算放大器的单位增益带宽不需太大,可以得到功耗和速度的优化.除了考虑辅助运放的频域、时域特性外,还必须考虑到其对整体运放共模输入范围和输出摆幅的影响[6-7].辅助运算放大器采用折叠型共栅共源运放结构,不会影响整体运放的输出摆幅.由于两个辅助输入共模电平的不同,其输入管分别为PMOS管和NMOS管.图3是输入对管为NMOS管的辅助运放A1.图3中,A2也同为折叠式共栅共源运放,只是输入对管类型不同.运放仿真性能指标:开环增益为102dB;单位增益带宽为1.95GHz;相位裕度为62°;建立时间为4.8ns;负载电容为3.5pF;供电电源为3.3V.在有、无增益自举结构情况下,套筒运放在添加增益自举结构前后的幅频特性和相频特性,如图4所示.图4中:A为振幅增益;φ为相位裕度;f为频率.从图4中可知,仿真结果和理论研究基本相符.在未加增益自举结构时,运放仅能达到51dB的增益;添加辅助运放后,可以达到106dB的增益,满足首级MDAC 对运放增益的要求.在图4中还可以看到,添加辅助运放后的主极点较之前大大减小,次主极点略有减小.这是由于辅助运放的添加增大了该点的寄生电容.但是,由于增益的提高,运放的单位增益带宽及相位裕度在两种情况下基本不变,证明辅助运放的添加并不会影响运放使用时的速度.系统分析了在Pipeline ADC设计中增益自举结构的跨导运算放大器特性,揭示了辅助运算放大器对整体运算放大器带宽影响的数学机理,对模数混合信号电路设计者有较大的参考价值.【相关文献】[1]GALTON S E.A digitally enhanced 1.8-V 15-bit 40-MSample/s CMOS Pipelined ADC[J].IEEE Journal of Solid-State Circuits,2004,39(12):2126-2138.[2]QUINN P J,VAN ROERMUND A H M.Design and optimization of multi-bit front-end stage and scaled back-end stages of pipelined ADCs[J].IEEE ISCAS,2005,40(3):1964-1967.[3]BULT K,GEELEN G J G M.A fast-settling CMOS op amp for SC circuits with 90-dB DC gain[J].IEEE Journal of Solid-State Circuits,1990,25(6):1379-1384.[4]LOTFI R,TAHERZADEH-SANI M,AZIZI M Y,et al.Systematic design for power minimization of pipelined analog-to-digital converters[C]∥International Conference on Computer Aided Design.San Jose:[s.n.],2003:371-374.[5]CHOKSI O,CARLEY R L.Analysis of switched-capacitor common-mode feedback circuit[J].IEEE Transactions on Circuit and Systems(Ⅱ):Analog and Digital Signal Processing,2003,50(12)::906-917.[6]GRAY P R.Analysis and design of analog integrated circuits[M].New York:Wiley,2000.[7]凌朝东,黄群峰,张艳红,等.脑电信号提取专用电极芯片的设计[J].华侨大学学报:自然科学版,2007,28(3):260-263.。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

CMOS运算放大器的设计毕业设计(论文)原创性声明和使用授权说明原创性声明本人郑重承诺:所呈交的毕业设计(论文),是我个人在指导教师的指导下进行的研究工作及取得的成果。

尽我所知,除文中特别加以标注和致谢的地方外,不包含其他人或组织已经发表或公布过的研究成果,也不包含我为获得及其它教育机构的学位或学历而使用过的材料。

对本研究提供过帮助和做出过贡献的个人或集体,均已在文中作了明确的说明并表示了谢意。

作者签名:日期:指导教师签名:日期:使用授权说明本人完全了解大学关于收集、保存、使用毕业设计(论文)的规定,即:按照学校要求提交毕业设计(论文)的印刷本和电子版本;学校有权保存毕业设计(论文)的印刷本和电子版,并提供目录检索与阅览服务;学校可以采用影印、缩印、数字化或其它复制手段保存论文;在不以赢利为目的前提下,学校可以公布论文的部分或全部内容。

作者签名:日期:学位论文原创性声明本人郑重声明:所呈交的论文是本人在导师的指导下独立进行研究所取得的研究成果。

除了文中特别加以标注引用的内容外,本论文不包含任何其他个人或集体已经发表或撰写的成果作品。

对本文的研究做出重要贡献的个人和集体,均已在文中以明确方式标明。

本人完全意识到本声明的法律后果由本人承担。

作者签名:日期:年月日学位论文版权使用授权书本学位论文作者完全了解学校有关保留、使用学位论文的规定,同意学校保留并向国家有关部门或机构送交论文的复印件和电子版,允许论文被查阅和借阅。

本人授权大学可以将本学位论文的全部或部分内容编入有关数据库进行检索,可以采用影印、缩印或扫描等复制手段保存和汇编本学位论文。

涉密论文按学校规定处理。

作者签名:日期:年月日导师签名:日期:年月日目录第一章绪论 (7)1.1设计平台及软件介绍 (7)1.1.1PSPICE简介 (7)1.1.2 L-Edit简介 (7)1.1.3 Cadence OrCAD Capture简介 (7)1.2 设计方法 (8)1.2.1CMOS运算放大器设计方法 (8)1.2.2运算放大器的性能优化 (8)第二章全差分运算放大器基础 (10)2.1 MOS器件基本特性 (11)2.1.1 MOSFET的结构和大信号特性 (11)2.1.2 MOSFET的小信号模型 (12)2.2运算放大器概述 (13)2.3全差分运算放大器特点 (14)第三章CMOS模拟运放设计 (16)3.1设计目标 (16)3.2电路结构分析 (16)3.3.1 输入级设计 (18)3.3.2电流镜电路 (18)3.3.3偏置电路 (19)3.3.4 输出级 (20)3.3.5 整体电路 (20)第四章运放参数的模拟与测量 (22)4.1瞬态分析 (22)4.2 温度特性 (23)4.3输出阻抗 (24)4.4交流特性分析 (25)5.1版图设计基础 (26)5.1.1设计流程 (26)5.1.2 L-edit中的版图设计 (27)5.2 版图设计 (28)5.3版图参数的提取并仿真 (29)5.3.1版图参数的提取和修改 (29)5.3.2电路仿真 (29)第六章总结 (31)【参考资料】 (32)附录: (33)一、Pspice仿真代码: (33)1、原理层次仿真代码(偏置电压由直流电压直接替代) (33)2、MOS分压电路中MOS宽长比确定电路 (35)3、最终Pspice仿真代码 (35)二、版图生成代码 (37)三、版图修改代码 (40)第一章绪论1.1设计平台及软件介绍1.1.1 PSPICE简介PSPICE是由SPICE(Simulation Program with Intergrated Circuit Emphasis)发展而来的用于微机系列的通用电路分析程序。

于1972年由美国加州大学伯克利分校的计算机辅助设计小组利用FORTRAN语言开发而成,主要用于大规模集成电路的计算机辅助设计。

PSPICE仿真软件具有强大的电路图绘制功能、电路模拟仿真功能、图形后处理功能和元器件符号制作功能,以图形方式输入,自动进行电路检查,生成图表,模拟和计算电路。

它的用途非常广泛,不仅可以用于电路分析和优化设计,还可用于电子线路、电路和信号与系统等课程的计算机辅助教学。

与印制版设计软件配合使用,还可实现电子设计自动化。

被公认是通用电路模拟程序中最优秀的软件,具有广阔的应用前景。

1.1.2 L-Edit简介L-Edit是专用集成电路设计软件TannerTools中的主要版图设计软件,是一个用来制造集成电路掩膜的版图设计工具。

L-Edit中的层与掩膜生产过程相关联,不同的层能被方便地显示为不同的颜色和样式,并且每层间相互独立。

L-Edit 以文件、单元、简单的掩膜的形式描述版图设计。

其最大的特点是速度快、功能强、使用方便和分层设计。

1.1.3 Cadence OrCAD Capture简介Cadence、OrCAD、Capture 是线路图输入系统,具有快捷、通用的设计输入能力,针对设计一个新的模拟电路、修改现有的一个 PCB 的线路图、或者绘制一个 HDL 模块的方框图,都提供了所需要的全部功能。

它运行在 PC 平台,用于 FPGA 、 PCB 和Cadence、OrCAD、PSpice设计应用中,它是业界第一个真正基于 Windows 环境的线路图输入程序,易于使用的功能及特点已使其成为线路图输入的工业标准。

1.2 设计方法1.2.1CMOS运算放大器设计方法CMOS运算放大器的设计通常包括结构设计和器件设计两个状态。

首先,寻找可行的结构,如果选择的结构不符合要求,则需要修改结构或重新设计。

一旦符合条件,接着进行器件设计,确定直流工作点、器件尺寸和偏置网络,必须仔细计算器件的尺寸以满足运放的交、直流要求。

为了满足所有的设计指标,这两个设计步骤需要重复的进行。

下图给出了运算放大器的设计流程:图1.1:模拟运算放大器设计流程1.2.2运算放大器的性能优化“理想”运放具有以下的特性:无限大的输入阻抗和输出电流;无限大的转换速率和开环增益;无噪声、失调、功耗浪费和信号失真;无负载、频率和电源电压的限制。

事实上,没有运放能达到以上所有的特性。

在实际的设计中,运放参数中的大多数都会互相牵制,这将导致设计变成一个多维优化的问题。

如下图“模拟电路设计八边形法则”所示,这样的折衷选择、互相制约对高性能放大器的设计提出了许多难题,要靠理论和经验才能得到一个较佳的折衷方案。

图1.2:模拟电路设计八边形法则第二章全差分运算放大器基础本章主要介绍MOS器件的一些特性,以及运算放大器的相关内容。

2.1 MOS 器件基本特性2.1.1 MOSFET 的结构和大信号特性下面为N 沟道增强型MOS 管的剖面图及其输出特性曲线。

图2.1:强反型时增强型NMOS 管的剖面图图2.2:NMOS 管的i-u 特性CMOS 管的强反型区:当MOS 器件的栅源电压大于阈值电压时,称之为强反型状态。

当TH GS DS u u u ->时,器件饱和区,这里的DS u ,GS u 与TH u 分别指MOS管的漏源电压、栅源电压和阈值电压。

实际上,在MOS 运放设计中,大部分的MOS 管都是工作在饱和状态,因为对于给定的漏极电流和器件尺寸来说,工作在饱和区可以提供稳定GS u 的电流和比较大的电压增益。

在饱和区,MOS 器件的漏极电流d i 和栅源电压的关系由下式决定:()()2221TH GS N TH GS ox n D u u K u u LWC i -=-=μ 式中uN 为NMOS 沟道中电子迁移率,COX 为栅氧化区单位面积电容,W 为有效沟道宽度,L 是有效沟道长度,KN 为NMOS 管的导电因子。

在模拟电子电路中,MOSFET 的跨导gm 是一个重要的参数。

根据上式可求得MOSFET 在饱和区静态工作点处的小信号跨导:()THGS DTH GS oxn GS D m u u i u u L W C u i g -=-=∂∂=2μ或者Dox n m i LW C u g 2=可见MOSFET 的饱和区的跨导m g 不仅与它的工作电流D i 有关,而且可通过选择器件尺寸LW加以改变。

正因为如此,使MOS 模拟IC 的设计更为灵活。

2.1.2 MOSFET 的小信号模型当NMOS 管在直流偏置作用下工作于饱和区时,其交流小信号等效模型如下 图所示,在电路计算中,由MOS 管的大信号模型算出电路的静态工作点后,就必须由小信号等效模型来分析电路。

小信号模型是能简化计算工作的线性模型,它是在一定的电压电流下有效,它的各项参数依赖于大信号模型参数和直流变量。

图2.3:MOSFET 的小信号模型上图列出手工设计时的简化等效电路模型,各参数定义如下:栅-衬底电容DB C 和源-衬底电容SB C ;GB C 、GS C 、栅-漏电容GD C ;()TH GS oxn GS D m u u LWC u i g -=∂∂=μ 饱和区跨导:令 LW C oxn μβ=m g 可以表示为:()D TH GS m i u u g ββ2=-=输出电阻为:Do i r λ1=输出电阻影响模拟电路的许多特性,例如,它限制着大多数放大器的最大电压增益。

在简化的手工分析中,可以使用近似表达式:GS m D u g i =2.2运算放大器概述运算放大器是模拟电路设计中用途最广/最重要的部件,大量的具有复杂程度的运放被用来实现各种功能:从直流偏置产生到高速放大或滤波。

运算放大器是具有足够正向增益的放大器(受控源),当加负反馈时,闭环传输函数与运算放大器的增益几乎无关。

利用这个原理可以设计出很多有用的模拟电路和系统。

对运算放大器最主要的一个要求是有一个足够大的开环增益以符合负反馈的概念。

单级放大器大多没有足够大的增益,因此多数CMOS 运放采用两级或多级增益。

最常用的运算放大器之一是两级运算放大器,下图为最常用的两级运算放大器的框图。

图2.4:运算放大器的基本结构上图描述了运算放大器的重要组成部分,CMOS运算放大器在结构上非常类似于双极型运算放大器。

输入级——主要作用是放大差模输入信号,由差分放大电路组成,有时会提供一个差分到单端的转换,利用它的对称性可以提高整个电路的共模抑制比,可以改善噪声和失调性能,且具有很强的抗干扰能力,并具有温度漂移下、级间易直接耦合。

增益级——这一级的主要作用是提高电压的增益,如果差分输入级没有完成差分到单端的转换,那么这个工作应该由这级来完成。

输出级——输出级一般由源极跟随器或推挽放大器组成,用于降低输出阻抗,维持大的信号摆幅。

偏置电路——主要用于为每只晶体管建立适当的静态工作点。

补偿电路——在运算放大器中加负反馈,用以保持整个电路工作的稳定。