最新计算机体系结构试卷试题(答案全)

计算机体系结构考试卷子及答案

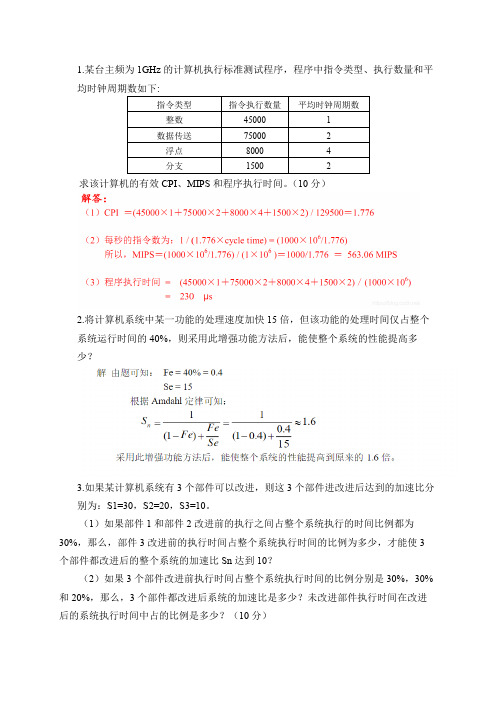

1.某台主频为1GHz的计算机执行标准测试程序,程序中指令类型、执行数量和平均时钟周期数如下:求该计算机的有效CPI、MIPS和程序执行时间。

(10分)2.将计算机系统中某一功能的处理速度加快15倍,但该功能的处理时间仅占整个系统运行时间的40%,则采用此增强功能方法后,能使整个系统的性能提高多少?3.如果某计算机系统有3个部件可以改进,则这3个部件进改进后达到的加速比分别为:S1=30,S2=20,S3=10。

(1)如果部件1和部件2改进前的执行之间占整个系统执行的时间比例都为30%,那么,部件3改进前的执行时间占整个系统执行时间的比例为多少,才能使3个部件都改进后的整个系统的加速比Sn达到10?(2)如果3个部件改进前执行时间占整个系统执行时间的比例分别是30%,30%和20%,那么,3个部件都改进后系统的加速比是多少?未改进部件执行时间在改进后的系统执行时间中占的比例是多少?(10分)4.假设某应用程序中有4类操作,通过改进,各操作获得不同的性能提高。

具体数据如下表所示:(1)改进后,各类操作的加速比分别是多少?(2)各类操作单独改进后,程序获得的加速比分别是多少?(3)4类操作均改进后,整个程序的加速比是多少?5.一台模型机的9条指令的使用频度如下:(10分)ADD(加):26%SHR(右移):2%SUB(减):17%CLL(循环左移):5%JOM(按页转移):11%CLA(累加器清零):15%STO(存):2%STP(停机):12%JMP(转移):10%试设计这9条指令的Huffman编码的操作码表示以及其等长扩展操作码表示,并计算这两种表示的平均操作码长度。

6.有一个“Cache-主存”存储层次。

主存共分为8个块(0~7),Cache为4个块(0~3),采用直接映像方式。

(1)对于如下主存块地址流:0、2、6、1、3、7、0、1、4、5、4、6、0、7、2,如主存中内容一开始未装入Cache,请列出每次访问后Cache中各块的分配情况;(2)对于(1),指出既发生块失效又发生块争用的时刻;(3)对于(1),求出此期间的Cache命中率。

计算机体系结构基础知识试题及

计算机体系结构基础知识试题及答案解析一、选择题1. B2. A3. D4. C5. B6. C7. A8. D9. B 10. C二、填空题1. 互联网2. 中央处理器3. 存储器4. 输入/输出设备三、简答题1. 计算机体系结构是指计算机硬件与软件之间的逻辑结构和功能关系,即计算机的整体结构和组成方式。

2. CPU(中央处理器)是计算机体系结构的核心,它负责执行计算机的指令并控制计算机的运行。

3. 存储器是计算机中用于存储数据和程序的部件,包括主存储器(RAM)和辅助存储器(硬盘、固态硬盘等)。

4. 输入/输出设备用于实现计算机与外部设备之间的数据交换,包括显示器、键盘、鼠标、打印机等。

四、论述题计算机体系结构是计算机科学中的重要组成部分,它对于计算机的设计和开发具有重要意义。

计算机体系结构的基本原理可以通过一系列试题来进行检测和考察。

下面是一套基础的计算机体系结构试题及其答案解析。

首先是选择题部分,这部分试题主要考察对计算机体系结构基础知识的理解和应用能力。

通过选择正确的答案来判断考生对相关知识的掌握情况。

根据试题解析,我们可以得出正确的答案和解释。

接下来是填空题部分,这部分试题主要考察考生对计算机体系结构相关术语的理解和记忆能力。

通过填写正确的术语来补全句子,从而测试考生对相关知识的熟悉程度。

最后是简答题部分,这部分试题通过提出开放式问题,要求考生对计算机体系结构的相关概念和原理进行简要的叙述。

考生需要用清晰、准确的语言来回答问题,展示自己对知识的理解和运用能力。

综上所述,计算机体系结构基础知识试题及答案解析是一套用于考察计算机科学学习者对计算机体系结构基本原理的掌握程度的试题。

通过做题和解析,考生可以检测自己的学习效果,并加深对相关知识的理解。

希望这套试题能为广大学习者提供帮助,推动计算机科学的进一步发展。

【上海交通大学(上海交大)计算机组成与系统结构】【习题试卷】2

一.单项选择题(每个空格只有一个正确答案,35分,每题5分)1. B 的基本任务是按照 H 所排的指令序列,从 F 取出指令操作码到 B 中,对指令操作码译码分析,执行指令操作。

适配器的作用是保证 A 用计算机系统特性所要求的形式发送或接收信息。

A. I/O设备B. 控制器C. 缓冲器D. 译码器E. 寄存器F. 存储器G. 地址H. 程序2.在奇偶校验中,只有当数据中包含有 A 个1时,奇校验位C=0;只有当数据中包含有 B 个1时,偶校验位C= C 。

奇偶校验可提供单个错误检测,但无法检测 E 错误,更无法识别错误信息的 G 。

A. 奇数B. 偶数C. 0D. 1E. 多个F. 内容G. 位置H. 来源3.MOS半导体存储器中, D 的外围电路简单,速度 G ,但其使用的器件多,集成度不高; C 可大幅度提高集成度,但由于 F 操作,外围电路复杂,速度 H 。

A. ROMB. RAMC. DRAMD. SRAME. 读写F. 刷新G. 快H. 慢4.指令格式就是 G 用二进制代码表示的结构形式,通常由 A 字段和 F 字段组成,前者表征指令的操作特性与功能,后者通常指定参与操作的 B 的 E 。

A. 操作码B. 操作数C. 操作特性D. 数据字E. 地址F. 地址码G. 指令字H. 功能字5.根据设计方法不同, B 控制器可分为三种:第一种称为 G 控制器,它是采用时序逻辑技术来实现的;第二种称为 A 控制器,它是采用 E 逻辑来实现的;第三种是前两种方式的 F 。

A. 微程序B. 操作C. 指令D. 时间E. 存储F. 组合G. 硬布线H. 软布线6.一条 C 是由若干条 G 组成的序列(通常叫做 E )来实现的,而 E 的总和便可实现整个的 D 。

A. 微操作B. 宏操作C. 机器指令D. 指令系统E. 微程序F. 宏程序G. 微指令H. 宏指令7.奔腾CPU的大多数简单指令用 E 控制实现,在 A 个时钟周期内执行完毕。

计算机组成原理试卷含答案

计算机组成原理试卷含答案提⽰:答案⼀律在答题纸上书写!⼀、选择题:(每题1分,共20分)1.已知Cache的容量为16KB,内存的容量为1MB,每块16B,则在直接映像⽅式下⼀个Cache块可以与个内存块对应。

A.1B. 32C. 128D. 642.下列_____是正确的。

A.为了充分利⽤存储器空间,指令的长度通常可取字节的整数倍B.⼀地址指令是固定长度的指令C.单字长指令会降低取指令的速度3.冯诺依曼结构的计算机由以下组成部分______。

A.控制器和存储器 B.运算器和控制器 C.运算器、控制器和主存 D. CPU、主存和I/O 4.下列说法中_______不正确的。

A.指令周期等于机器周期整数倍B.指令周期⼤于机器周期C.指令周期是机器周期的两倍5.在CPU的寄存器中,____对⽤户是完全透明的。

A.PC B.MAR C.PSW6.已知 100H: MOV A,#30 (双字节指令,100H为该指令的⾸地址)在取指令操作之后,PC的值是_____.A. 0FFHB.101HC. 102H7.磁盘的转速为3600转/分,则平均等待时间是秒。

A.1/60 B. 1/120 C. 60D.1208.在对W寄存器的实验中,将数据11H存储到W寄存器,则要求WEN为。

A. 1B. 09.下列叙述中是正确的A.控制器产⽣的所有控制信号称为微命令 B.组合逻辑控制器⽐微程序控制器更加灵活专业:计算机科学与技术课程名称:计算机组成原理学分:3.5 试卷编号(G)课程编号: 1311082 考试⽅式:闭卷考试时间: 100 分钟拟卷⼈(签字):拟卷⽇期: 2011-05-29 审核⼈(签字):C.微处理器的程序称微程序10.在浮点加减运算中,结果的溢出判断⽅法是______。

A.尾数运算是否产⽣溢出B.阶码运算是否产⽣溢出C.尾数最后⼀位舍去11.CPU响应中断的时间是_______。

A.⼀条指令执⾏结束 B.外设提出中断 C.取指周期结束12.在总线的独⽴请求⽅式下,若N个设备,则。

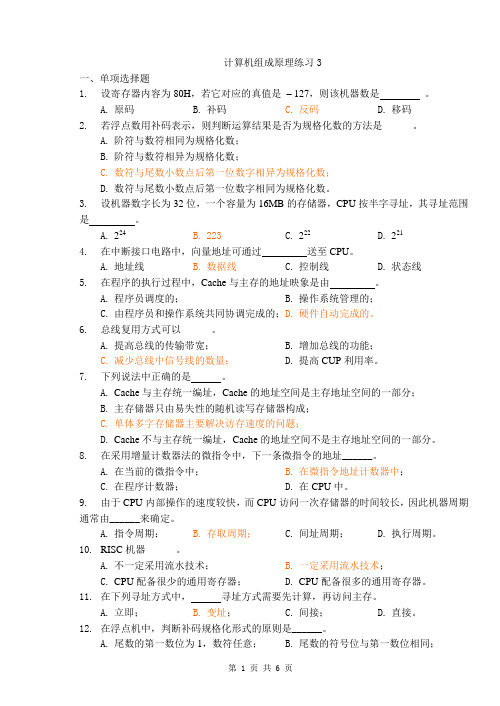

计算机组成原理练习(3)答案.

计算机组成原理练习3一、单项选择题1. 设寄存器内容为80H,若它对应的真值是– 127,则该机器数是。

A. 原码B. 补码C. 反码D. 移码2. 若浮点数用补码表示,则判断运算结果是否为规格化数的方法是______。

A. 阶符与数符相同为规格化数;B. 阶符与数符相异为规格化数;C. 数符与尾数小数点后第一位数字相异为规格化数;D. 数符与尾数小数点后第一位数字相同为规格化数。

3. 设机器数字长为32位,一个容量为16MB的存储器,CPU按半字寻址,其寻址范围是。

A. 224B. 223C. 222D. 2214. 在中断接口电路中,向量地址可通过送至CPU。

A. 地址线B. 数据线C. 控制线D. 状态线5. 在程序的执行过程中,Cache与主存的地址映象是由。

A. 程序员调度的;B. 操作系统管理的;C. 由程序员和操作系统共同协调完成的;D. 硬件自动完成的。

6. 总线复用方式可以______。

A. 提高总线的传输带宽;B. 增加总线的功能;C. 减少总线中信号线的数量;D. 提高CUP利用率。

7. 下列说法中正确的是。

A. Cache与主存统一编址,Cache的地址空间是主存地址空间的一部分;B. 主存储器只由易失性的随机读写存储器构成;C. 单体多字存储器主要解决访存速度的问题;D. Cache不与主存统一编址,Cache的地址空间不是主存地址空间的一部分。

8. 在采用增量计数器法的微指令中,下一条微指令的地址______。

A. 在当前的微指令中;B. 在微指令地址计数器中;C. 在程序计数器;D. 在CPU中。

9. 由于CPU内部操作的速度较快,而CPU访问一次存储器的时间较长,因此机器周期通常由______来确定。

A. 指令周期;B. 存取周期;C. 间址周期;D. 执行周期。

10. RISC机器______。

A. 不一定采用流水技术;B. 一定采用流水技术;C. CPU配备很少的通用寄存器;D. CPU配备很多的通用寄存器。

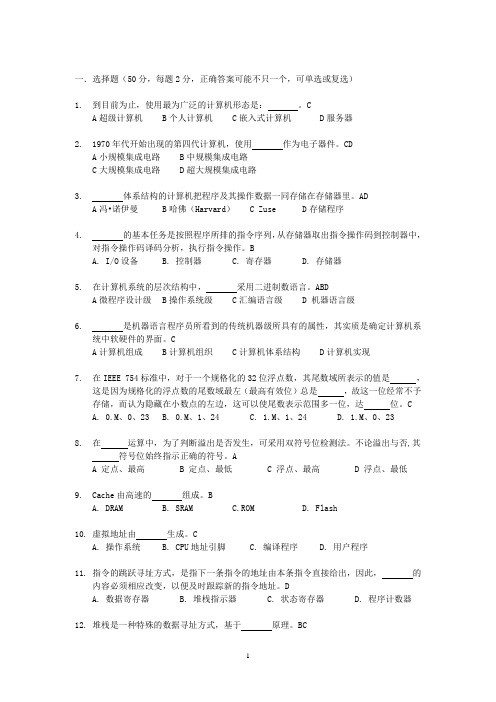

【上海交通大学(上海交大)计算机组成与系统结构】【习题试卷】10

一.选择题(50分,每题2分,正确答案可能不只一个,可单选或复选)1.到目前为止,使用最为广泛的计算机形态是:。

CA超级计算机B个人计算机C嵌入式计算机D服务器2.1970年代开始出现的第四代计算机,使用作为电子器件。

CDA小规模集成电路B中规模集成电路C大规模集成电路D超大规模集成电路3.体系结构的计算机把程序及其操作数据一同存储在存储器里。

ADA冯•诺伊曼B哈佛(Harvard) C Zuse D存储程序4.的基本任务是按照程序所排的指令序列,从存储器取出指令操作码到控制器中,对指令操作码译码分析,执行指令操作。

BA. I/O设备B. 控制器C. 寄存器D. 存储器5.在计算机系统的层次结构中,采用二进制数语言。

ABDA微程序设计级B操作系统级C汇编语言级 D 机器语言级6.是机器语言程序员所看到的传统机器级所具有的属性,其实质是确定计算机系统中软硬件的界面。

CA计算机组成B计算机组织C计算机体系结构D计算机实现7.在IEEE 754标准中,对于一个规格化的32位浮点数,其尾数域所表示的值是,这是因为规格化的浮点数的尾数域最左(最高有效位)总是,故这一位经常不予存储,而认为隐藏在小数点的左边,这可以使尾数表示范围多一位,达位。

CA. 0.M、0、23B. 0.M、1、24C. 1.M、1、24D. 1.M、0、238.在运算中,为了判断溢出是否发生,可采用双符号位检测法。

不论溢出与否,其符号位始终指示正确的符号。

AA 定点、最高B 定点、最低C 浮点、最高D 浮点、最低9.Cache由高速的组成。

BA. DRAMB. SRAMC.ROMD. Flash10.虚拟地址由生成。

CA. 操作系统B. CPU地址引脚C. 编译程序D. 用户程序11.指令的跳跃寻址方式,是指下一条指令的地址由本条指令直接给出,因此,的内容必须相应改变,以便及时跟踪新的指令地址。

DA. 数据寄存器B. 堆栈指示器C. 状态寄存器D. 程序计数器12.堆栈是一种特殊的数据寻址方式,基于原理。

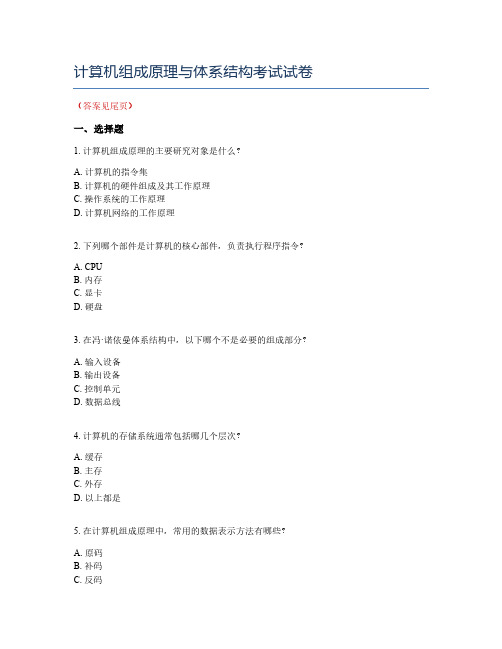

计算机组成原理与体系结构考试试卷

计算机组成原理与体系结构考试试卷(答案见尾页)一、选择题1. 计算机组成原理的主要研究对象是什么?A. 计算机的指令集B. 计算机的硬件组成及其工作原理C. 操作系统的工作原理D. 计算机网络的工作原理2. 下列哪个部件是计算机的核心部件,负责执行程序指令?A. CPUB. 内存C. 显卡D. 硬盘3. 在冯·诺依曼体系结构中,以下哪个不是必要的组成部分?A. 输入设备B. 输出设备C. 控制单元D. 数据总线4. 计算机的存储系统通常包括哪几个层次?A. 缓存B. 主存C. 外存D. 以上都是5. 在计算机组成原理中,常用的数据表示方法有哪些?A. 原码B. 补码C. 反码D. 移码6. 以下哪个是计算机的输入/输出设备?A. 键盘B. 显示器C. 打印机D. 网络接口卡7. 在计算机组成原理中,CPU的主要功能是什么?A. 存储数据B. 进行算术运算和逻辑运算C. 控制和管理计算机其他部件D. 传输数据8. 下列哪种存储器具有最快的读写速度?A. RAMB. 硬盘C. 缓存D. CD9. 在计算机组成原理中,中断是指什么?A. 计算机在执行程序时,由于某些紧急事件需要立即处理,而暂时中止当前程序的执行过程B. 计算机在执行程序时,由于某些紧急事件需要立即处理,而将程序的执行顺序暂时改变C. 计算机在执行程序时,由于某些紧急事件需要立即处理,而将程序的执行状态暂时保存D. 计算机在执行程序时,由于某些紧急事件需要立即处理,而将程序的执行内容暂时复制到另一个部件10. 在计算机组成原理中,为了提高计算机的性能,通常会采用多种技术手段,如并行处理、流水线技术等。

以下哪种技术不是常见的提高计算机性能的技术手段?A. 多核处理器B. 缓存技术C. 串行通信D. 异步I/O11. 计算机组成原理的主要内容包括哪些?A. 信息的表示与存储B. 控制器的设计与实现C. 总线与接口技术D. 操作系统的基本原理E. 以上都是12. 下列哪个部件不属于计算机的中央处理器(CPU)?A. 寄存器B. 运算器C. 控制器D. 缓存E. 输入/输出设备13. 在冯·诺依曼体系结构中,计算机由哪五个主要部分组成?A. 输入设备、输出设备、控制器、算术逻辑单元、内存B. 输入设备、输出设备、运算器、内存、外部存储器C. 输入设备、输出设备、控制器、算术逻辑单元、内存D. 输入设备、输出设备、运算器、内存、硬盘E. 输入设备、输出设备、控制器、内存、缓存14. 以下哪个不是计算机内部的信息表示方式?A. 原码B. 补码C. 反码D. ASCII码E. 二进制编码15. 在计算机组成原理中,通常使用哪种寻址方式来访问内存中的数据?A. 索引寻址B. 间接寻址C. 直接寻址D. 寄存器寻址E. 堆栈寻址16. 计算机的存储系统通常分为哪两部分?A. 主存储器B. 辅助存储器C. 随机存取存储器D. 磁盘存储器E. 光盘存储器17. 在输入/输出(I/O)系统中,中断的作用是什么?A. 提高系统的运行效率B. 实现多任务处理C. 允许计算机在等待I/O操作完成时继续执行其他任务D. 增加I/O设备的利用率E. 以上都是18. 在计算机组成原理中,为了提高指令的执行速度,通常会采用哪种技术?A. 流水线技术B. 哈希技术C. 缓存技术D. 动态调度技术E. 以上都是19. 以下哪个是计算机的输入设备?A. 显示器B. 键盘C. 打印机D. 扬声器E. 数字相机20. 在计算机体系结构中,超标量处理器的主要特点是什么?A. 支持分支预测B. 提高指令流水线的执行速度C. 增加寄存器数量D. 支持浮点运算E. 减少指令周期21. 在计算机组成原理中,以下哪个不是计算机的基本逻辑电路?A. 与门B. 或门C. 异或门D. 触发器E. 计数器22. 计算机的存储系统通常包括哪几个部分?A. 寄存器B. 缓存C. 主存储器D. 辅助存储器E. 高速缓冲存储器F. 以上都是23. 在计算机体系结构中,以下哪个是用于解释指令执行过程的概念?A. 指令集B. 指令流水线C. 数据通路D. 控制单元E. 以上都不是24. 下面关于冯·诺依曼结构的描述,哪个是正确的?A. 存储器只用于存储数据和指令B. 控制单元负责解释指令并控制整个计算机系统C. 输入/输出设备只能位于计算机的主板上D. 堆栈是用于数据存储的E. 以上都不对25. 在计算机组成原理中,以下哪个是用于表示字符的编码方式?A. ASCII码B. 汉字编码C. 国际码D. 以上都是E. 以上都不是26. 计算机的指令集是指什么?A. 计算机能够执行的全部指令的集合B. 计算机内部所有硬件部件的总和C. 计算机程序的集合D. 计算机内存中的数据集合E. 以上都不是27. 在计算机体系结构中,以下哪个是用于提高指令执行效率的技术?A. 流水线技术B. 循环展开技术C. 指令乱序执行D. 以上都是E. 以上都不是28. 计算机组成原理中的“存储程序”概念是由谁提出的?A. 图灵B. 冯·诺依曼C. 比尔·盖茨D. 以上都不是E. 以上都是29. 在计算机组成原理中,以下哪个是用于描述计算机系统各部件之间连接方式的模型?A. 系统总线B. 数据总线C. 控制总线D. 以上都是E. 以上都不是30. 计算机组成原理的主要目的是什么?A. 计算机内部电路的设计与优化B. 计算机硬件的逻辑设计C. 描述计算机硬件系统的组成和工作原理D. 计算机软件的开发与维护31. 在冯·诺依曼体系结构中,以下哪个部分不是必需的?A. CPUB. 内存C. 磁盘D. 输入输出设备32. 在计算机组成原理中,存储器的编址单位通常是:A. 字节B. 字C. 块D. 位33. 下列哪个部件不属于CPU的内部组成部分?A. 寄存器B. 指令寄存器C. 数据寄存器D. 输出缓冲器34. 在计算机的存储系统中,缓存通常位于哪个层次?A. L1缓存B. L2缓存C. 主存D. 硬盘35. 在计算机组成原理中,以下哪个概念是指CPU一次能处理的二进制数据的位数?A. 字长B. 总线宽度C. 主频D. 进程数36. 在冯·诺依曼体系结构中,程序和数据通常存储在哪里?A. RAMB. 硬盘C. ROMD. CD37. 在计算机组成原理中,以下哪个设备不是输入设备?A. 键盘B. 鼠标C. 打印机D. 显示器38. 在计算机组成原理中,以下哪个术语描述了CPU执行指令的速度?A. 主频B. 延迟C. 吞吐量D. 时序39. 在计算机的存储系统中,RAM的特点是什么?A. 速度快,但断电后数据会丢失B. 速度慢,但断电后数据不会丢失C. 速度快,断电后数据不会丢失D. 速度慢,断电后数据会丢失二、问答题1. 远程通信模块:如Wi-Fi、蓝牙等,用于与远程设备通信。

计算机体系结构试卷试题(答案全)

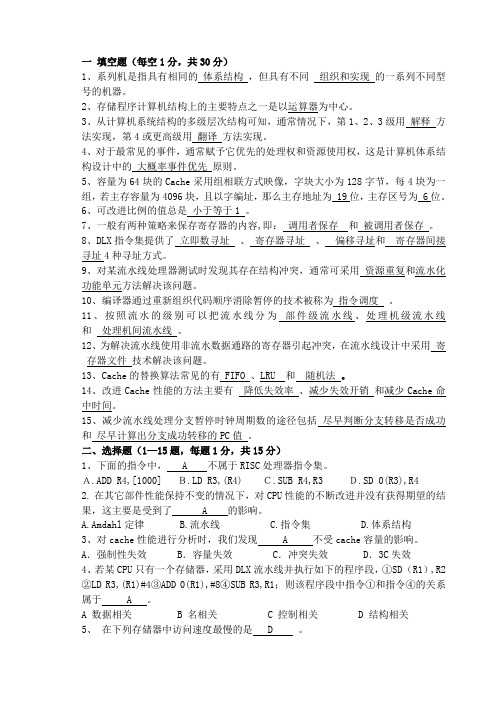

一填空题(每空1分,共30分)1、系列机是指具有相同的体系结构,但具有不同组织和实现的一系列不同型号的机器。

2、存储程序计算机结构上的主要特点之一是以运算器为中心。

3、从计算机系统结构的多级层次结构可知,通常情况下,第1、2、3级用解释方法实现,第4或更高级用翻译方法实现。

4、对于最常见的事件,通常赋予它优先的处理权和资源使用权,这是计算机体系结构设计中的大概率事件优先原则。

5、容量为64块的Cache采用组相联方式映像,字块大小为128字节,每4块为一组,若主存容量为4096块,且以字编址,那么主存地址为 19 位,主存区号为 6 位。

6、可改进比例的值总是小于等于1 。

7、一般有两种策略来保存寄存器的内容,即:调用者保存和被调用者保存。

8、DLX指令集提供了立即数寻址、寄存器寻址、偏移寻址和寄存器间接寻址4种寻址方式。

9、对某流水线处理器测试时发现其存在结构冲突,通常可采用资源重复和流水化功能单元方法解决该问题。

10、编译器通过重新组织代码顺序消除暂停的技术被称为指令调度。

11、按照流水的级别可以把流水线分为部件级流水线、处理机级流水线和处理机间流水线。

12、为解决流水线使用非流水数据通路的寄存器引起冲突,在流水线设计中采用寄存器文件技术解决该问题。

13、Cache的替换算法常见的有 FIFO 、LRU 和随机法。

14、改进Cache性能的方法主要有降低失效率、减少失效开销和减少Cache命中时间。

15、减少流水线处理分支暂停时钟周期数的途径包括尽早判断分支转移是否成功和尽早计算出分支成功转移的PC值。

二、选择题(1—15题,每题1分,共15分)1、下面的指令中, A 不属于RISC处理器指令集。

A.ADD R4,[1000] B.LD R3,(R4) C.SUB R4,R3 D.SD 0(R3),R42. 在其它部件性能保持不变的情况下,对CPU性能的不断改进并没有获得期望的结果,这主要是受到了 A 的影响。

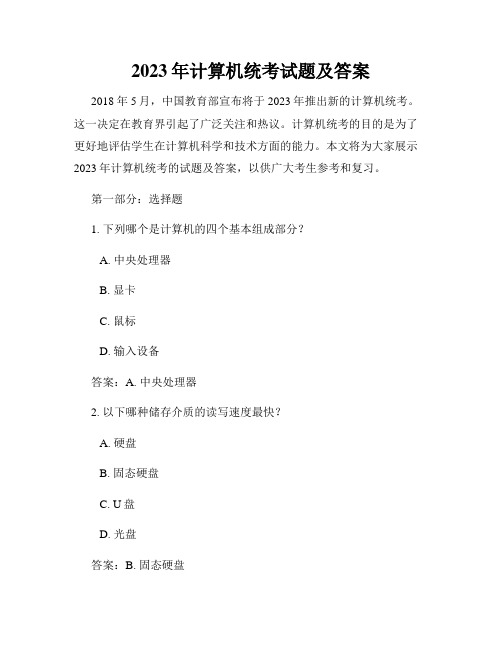

2023年计算机统考试题及答案

2023年计算机统考试题及答案2018年5月,中国教育部宣布将于2023年推出新的计算机统考。

这一决定在教育界引起了广泛关注和热议。

计算机统考的目的是为了更好地评估学生在计算机科学和技术方面的能力。

本文将为大家展示2023年计算机统考的试题及答案,以供广大考生参考和复习。

第一部分:选择题1. 下列哪个是计算机的四个基本组成部分?A. 中央处理器B. 显卡C. 鼠标D. 输入设备答案:A. 中央处理器2. 以下哪种储存介质的读写速度最快?A. 硬盘B. 固态硬盘C. U盘D. 光盘答案:B. 固态硬盘3. 在计算机网络中,HTTP协议用于什么目的?A. 传输网页文件B. 传输电子邮件C. 进行即时通讯D. 进行网络安全加密答案:A. 传输网页文件第二部分:填空题1. 以下是一个合法的IP地址:________答案:192.168.0.1(示例)2. “WWW”代表的是________答案:World Wide Web第三部分:计算题1. 设计一个算法,求出1到100之间所有偶数的和。

答案:sum = 0for i in range(1, 101):if i % 2 == 0:sum += iprint(sum)第四部分:应用题你是一家互联网公司的程序员,负责开发一款网页浏览器。

请简要描述你将如何设计并实现这个网页浏览器。

答案:首先,我们需要确定网页浏览器的基本功能,如访问网页、显示网页内容、支持浏览历史记录等。

然后,我们可以采用开发语言如HTML、CSS、JavaScript来编写网页浏览器的用户界面。

接下来,我们需要实现网页的加载和显示功能,可以利用网络协议如HTTP来获取网页内容并使用HTML解析和渲染引擎来显示网页。

另外,我们还可以加入一些附加功能,如书签管理、密码管理、广告屏蔽等,以提升用户体验。

最后,我们需要对网页浏览器进行测试和优化,确保其稳定性和性能。

通过以上试题的展示和答案的解析,希望能够对广大考生对2023年计算机统考有所了解和准备。

全国自考(计算机系统结构)模拟试卷10(题后含答案及解析)

全国自考(计算机系统结构)模拟试卷10(题后含答案及解析)题型有:1. 单项选择题 2. 填空题 3. 简答题 4. 简单应用题 5. 综合应用题单项选择题1.不属于阵列处理机构形1的典型机器的是( )A.MPPB.DAPC.DAP600D.BSP正确答案:D解析:阵列处理机构形l的典型机器有MPP、DAP、DAP600,而BSP属于阵列处理机构形2。

2.阵列处理机与流水线处理机相比,其特点是( )A.并发性B.时间重叠C.资源不重复D.靠增大处理单元数来提高速度正确答案:D解析:阵列处理机利用的是资源重复、并行性中的同时性,调高速度主要是靠增大处理单元数。

3.阵列处理机有两种构形,差别主要在于哪项和互连网络的作用不同( )A.存储器的组成方式B.存储器的数据分布C.存储器的响应速度D.存储器的容量大小正确答案:A解析:阵列处理机有两种构形,差别主要在于存储器的组成方式和互连网络的作用不同。

4.不属于向量的流水处理方式的选项是( )A.向量垂直处理方式B.向量纵向处理方式C.向量横向处理方式D.分组纵横处理方式正确答案:C解析:向量处理的三种方式分别是:向量纵向处理方式、向量垂直处理方式和分组纵横处理方式。

5.下列不属于各自独立型操作系统的优点是( )A.灵活性高B.各类资源可以较好地做到负荷平衡C.减少对大型控制专用处理机的需求D.可靠性上具有分布控制的优点正确答案:C解析:各自独立型操作系统是将控制功能分散给多台处理机,共同完成对整个系统的控制工作。

其优点为减少对大型控制专用处理机的需求,某个处理机发生故障,不会引起整个系统瘫痪,访问系统表格的冲突较少,有较高的系统效率。

6.下列关于多处珲机的描述有错误的选项是( )A.有两台以上处理机B.共享I/O子系统C.协同工作D.独立操作系统正确答案:D解析:多处理机是指有两台以上的处理机,共享I/O子系统,机间经共享主存或高速通信网络通信,在统一操作系统控制下,协同求解。

计算机系统结构试题及答案

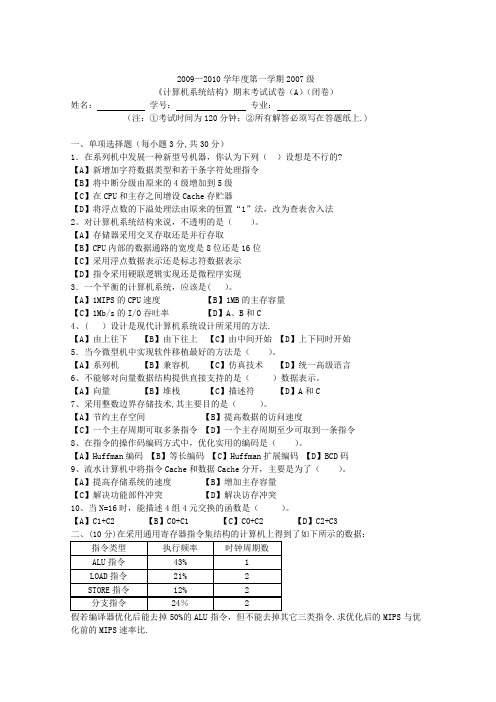

2009—2010学年度第一学期2007级《计算机系统结构》期末考试试卷(A)(闭卷)姓名:学号:专业:(注:①考试时间为120分钟;②所有解答必须写在答题纸上.)一、单项选择题(每小题3分,共30分)1.在系列机中发展一种新型号机器,你认为下列()设想是不行的?【A】新增加字符数据类型和若干条字符处理指令【B】将中断分级由原来的4级增加到5级【C】在CPU和主存之间增设Cache存贮器【D】将浮点数的下溢处理法由原来的恒置“1”法,改为查表舍入法2。

对计算机系统结构来说,不透明的是()。

【A】存储器采用交叉存取还是并行存取【B】CPU内部的数据通路的宽度是8位还是16位【C】采用浮点数据表示还是标志符数据表示【D】指令采用硬联逻辑实现还是微程序实现3.一个平衡的计算机系统,应该是( )。

【A】1MIPS的CPU速度【B】1MB的主存容量【C】1Mb/s的I/O吞吐率【D】A、B和C4、( )设计是现代计算机系统设计所采用的方法.【A】由上往下【B】由下往上【C】由中间开始【D】上下同时开始5.当今微型机中实现软件移植最好的方法是()。

【A】系列机【B】兼容机【C】仿真技术【D】统一高级语言6、不能够对向量数据结构提供直接支持的是()数据表示。

【A】向量【B】堆栈【C】描述符【D】A和C7、采用整数边界存储技术,其主要目的是()。

【A】节约主存空间【B】提高数据的访问速度【C】一个主存周期可取多条指令【D】一个主存周期至少可取到一条指令8、在指令的操作码编码方式中,优化实用的编码是()。

【A】Huffman编码【B】等长编码【C】Huffman扩展编码【D】BCD码9、流水计算机中将指令Cache和数据Cache分开,主要是为了()。

【A】提高存储系统的速度【B】增加主存容量【C】解决功能部件冲突【D】解决访存冲突10、当N=16时,能描述4组4元交换的函数是()。

【A】C1+C2 【B】C0+C1 【C】C0+C2 【D】C2+C3假若编译器优化后能去掉50%的ALU指令,但不能去掉其它三类指令.求优化后的MIPS与优化前的MIPS速率比.三、(10分)设某机器系统指令字长12位,每个操作码和地址均占3位,试提出一种分配方案,使该指令系统有4条三地址指令,8条二地址指令和180条单地址指令。

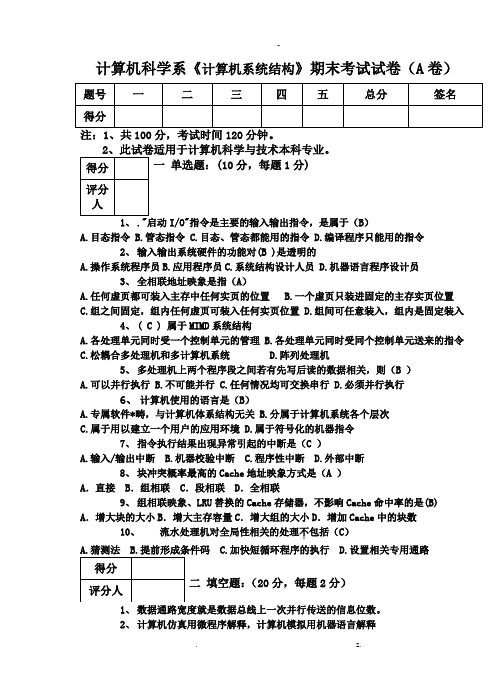

计算机系统结构期末考试试题及其答案

计算机科学系《计算机系统结构》期末考试试卷(A 卷)一 单选题:(10分,每题1分) 1、 ."启动I/O"指令是主要的输入输出指令,是属于(B )A.目态指令B.管态指令C.目态、管态都能用的指令D.编译程序只能用的指令2、 输入输出系统硬件的功能对(B )是透明的A.操作系统程序员B.应用程序员C.系统结构设计人员D.机器语言程序设计员3、 全相联地址映象是指(A )A.任何虚页都可装入主存中任何实页的位置B.一个虚页只装进固定的主存实页位置C.组之间固定,组内任何虚页可装入任何实页位置D.组间可任意装入,组内是固定装入4、 ( C ) 属于MIMD 系统结构A.各处理单元同时受一个控制单元的管理B.各处理单元同时受同个控制单元送来的指令C.松耦合多处理机和多计算机系统D.阵列处理机5、 多处理机上两个程序段之间若有先写后读的数据相关,则(B )A.可以并行执行B.不可能并行C.任何情况均可交换串行D.必须并行执行6、 计算机使用的语言是(B )A.专属软件*畴,与计算机体系结构无关B.分属于计算机系统各个层次C.属于用以建立一个用户的应用环境D.属于符号化的机器指令7、 指令执行结果出现异常引起的中断是(C )A.输入/输出中断B.机器校验中断C.程序性中断D.外部中断8、 块冲突概率最高的Cache 地址映象方式是(A )A.直接 B .组相联 C .段相联 D .全相联9、 组相联映象、LRU 替换的Cache 存储器,不影响Cache 命中率的是(B)A .增大块的大小B .增大主存容量C .增大组的大小D .增加Cache 中的块数10、 流水处理机对全局性相关的处理不.包括(C ) C.加快短循环程序的执行 D.设置相关专用通路1、 数据通路宽度就是数据总线上一次并行传送的信息位数。

2、 计算机仿真用微程序解释,计算机模拟用机器语言解释二 填空题:(20分,每题2分)3、阵列处理机按存贮器的组成方式可分为两种构形,分别为:分布式存储器和集中共享式。

计算机体系结构与高性能计算应用专升试题详解

计算机体系结构与高性能计算应用专升试题详解计算机体系结构与高性能计算应用是计算机专业中的一门重要课程,也是专升本考试的重点科目之一。

下面将详细解析一些典型的专升试题,帮助考生更好地理解和掌握相关知识。

一、单选题1. 下列关于计算机体系结构的说法正确的是:A. 计算机体系结构是指计算机硬件与软件之间的接口规范B. 计算机体系结构只包括硬件部分,不包括软件部分C. 计算机体系结构是指计算机的物理结构D. 计算机体系结构是指计算机硬件的组织和设计原理答案:A解析:计算机体系结构是指计算机硬件与软件之间的接口规范,它决定了计算机系统的功能、性能和可编程性,因此选项A正确。

2. 下列哪项不是计算机体系结构的典型特征:A. 指令集B. 数据格式C. 指令执行顺序D. 数据存储方式答案:C解析:指令执行顺序属于计算机微结构的范畴,不属于计算机体系结构的典型特征,因此选项C不是计算机体系结构的特征。

二、多选题1. 下列关于CISC和RISC的说法正确的是:A. CISC指令集复杂,其执行时间长B. RISC指令集简单,其执行时间短C. CISC适用于高性能计算需求D. RISC适用于低功耗计算需求答案:A、B、D解析:CISC指令集复杂,执行时间较长,RISC指令集简单,执行时间较短,适用于低功耗计算需求,因此选项A、B、D都是正确的。

2. 下列关于高性能计算应用的说法正确的是:A. 高性能计算应用可以加速科学计算和工程计算B. 高性能计算应用主要用于游戏和娱乐C. 高性能计算应用主要用于个人办公和娱乐D. 高性能计算应用与普通计算应用没有本质区别答案:A解析:高性能计算应用主要用于加速科学计算和工程计算等复杂计算任务,选项A正确。

选项B、C、D都是错误的。

三、填空题1. 计算机体系结构的目标是提高计算机的________和________。

答案:性能,可编程性解析:计算机体系结构的目标是提高计算机的性能和可编程性。

计算机体系结构试题及答案(Computer architecture questions and answers)

计算机体系结构试题及答案(Computer architecture questions andanswers)Questions and answers of computer architecture1, benefiting from the development of high performance computer: (1) the development of circuit technology; (2) the development of computer architecture technology.2, structure: computer systems can be classified by function of language as a multilevel structure, each layer in different language features. Sixth: the application of virtual machine language - > fifth: high-level language virtual machine assembly language - > Fourth: - > Third: virtual machine operating system virtual machine - level second: machine language (traditional machine level) - > Level 1: micro machine level program.3, computer architecture: see computer programmer attribute, namely the general structure and functional properties.4, transparency: in computer technology, the things or properties already exists, the concept from a point of view and have called transparency.5, the proposed architecture Amdahl attribute refers to the computer machine language level programmers see.The essence of 3 6, a classic computer architecture concept is to determine the computer system hardware and software interface, which is the instruction set design, above theinterface by software function realization, interface by hardware and firmware functions to achieve.7, computer organization is the logic of the computer system; computer is a physical computer system to achieve.The difference and connection between the 8, computer architecture, computer organization, computer?Answer: a system structure can have a variety of components, a component can have a variety of physical implementation, including system structure research on organization and implementation.9, a series of machine: refers to a system of the same structure but with different organization and implementation of a series of different types of machines.10, software compatibility: the same software can be run without change on the machine system of the same structure, and the results they get the same, the only difference is the different running time.11, compatible machine: different manufacturers, has the same computer architectures.12, backward compatibility is the basic characteristics of software compatibility, is the fundamental characteristics of series machine.13, in the field of computer market can be divided into threemajor areas: servers, desktop systems, embedded computing.14, Moore: integrated circuit density approximately doubled every two years.Technology based analysis of 15 quantitative performance evaluation: (1) (a) response time: from the beginning to the end of the time between events; all the time spent on the computer to complete a task. (b): the complete flow in unit time and workload. (c) x, y assumed two computers; X faster than y means: for a given task, the response time of X is less than y. The performance of X is several times the Y refers to the response time of X / y = n response time, response time and performance is inversely proportional to.16, the probability of event priority principle: (basic idea) for the probability of events (the most common event), giving priority to use it right and resource rights, to obtain the global optimal results.17, Amdahl Law: accelerate the execution speed of a component system performance obtained speedup, the importance is limited by the components in the system of. System acceleration ratio = total execution time (improved) / total execution time (improved) =......18, Amdahl law corollary: if only for a part of the computer in the performance improvement is more improved, the effect of the system. If only a part of the whole task is optimized, so much the acceleration ratio is not greater than 1 / (1- improvement ratio).19, the performance of CPU: Cpu time = total number of clock cycles / clock frequency Cpi = total number of clock cycles (IC / CPI: the number of clock cycles per instruction; the average IC implementation process: the number of instructions.)The performance of Cpu formula: total CPU time = CPI * IC / CPI clock frequency which reflects the computer architecture and computer technology, computer instruction set; Ic reflects the structure and technology of computer programming instruction set; clock frequency: reflect the implementation of computer technology, production technology and computer organization.20, parallelism refers to at the same time or two or more than two kinds of properties of the same or different work in the same time interval.The second chapter1, according to the CPU internal storage unit type of instruction set architecture for classification, can be divided into the stack based instruction set architecture, instruction set architecture and accumulator type general register type instruction set architecture.2, general register type instruction set machine is further subdivided into 3 types:Register to register type (R-R), register memory type (R-M), a memory register.3, addressing: (1) register addressing: example: ADD R4 R3, meaning Regs[R4]<-Regs[R4]+Regs[R3](2) immediate values: example: ADD R4, addressing 3 meanings: Regs[R4]<-Regs[R4]+3(3): offset cases: ADD R4, 100 (R1) meaning:Regs[R4]+Mem[100+Regs[R1]](4) register indirect addressing: example: ADD R4 (R1) meaning: Regs[R4]<-Regs[R4]+Mem[Regs[R1]](5) index addressing: example: ADD R3 (R1+R2) meaning:Regs[R3]<-Regs[R3]+Mem[Regs[R1]+Regs[R2]](6) direct addressing or absolute addressing: for example: ADD R1, (1001): Regs[R1]<-Regs[R1]+Mem[1001] meaning(7) memory indirect addressing: example: ADD R1, a (R3) meaning: Regs[R1]<-Regs[R1]+Mem[Mem[Regs[R3]]](8) the increment addressing: example: ADD R1 (R2) + meaning: Regs[R1]<-Regs[R1]+Mem[Regs(9) decrement addressing(10) zoom addressingThe function of structure design of the instruction set, 4:The instruction set classification structure in operationThe type of operation example(1) arithmetic and logical operations on integer arithmetic and logic operations: addition, subtraction, and, or etc.(2) data transmission LOAD/STORE(3) control branch, jump, procedure call and return, trap(4) operating system calls, virtual memory management.(5) floating point addition and subtraction operation(6) is converted to decimal decimal decimal decimal add, multiply, to characters(7) string string comparison, mobile(8) the pixel operation, compression operation5, complex instruction machine (CISC): refers to strengthen the instruction function, realize the function of software to hardware design, computer system to realize the instruction set architecture based on.The shortcomings of the CISC instruction set:(1) in the command system, the frequency of use of all kinds of orders is different.(2) the CISC instruction set architecture complexity brings complexity of computer architecture, which not only increases the development time and cost, but also easy to cause the design error.(3) the CISC instruction set architecture complexity brings great burden to the VLSI design, is not conducive to the monolithic integration.(4) in the CISC instruction set architecture, many complex instructions require very complex operation, so slow.(5) in the CISC instruction set architecture, because of the directive function is not balanced, not conducive to the use of computer architecture technology (such as advanced water technology) to improve the performance of the system.In 1980s 6, reduced instruction set computer developed: its purpose is to reduce the instruction set of the complexity of the structure as far as possible, in order to simplify the realization of the goal of improving performance, but also in today's instruction set is a main trend of the structure and function of design.Follow the design principles:(1) choose to use the highest frequency of instruction, and added some of the most useful instructions.(2) the function of each instruction is as simple as possible, and completed in one machine cycle.(3) all have the same length as the instruction.(4) only the LOAD and STORE operating instructions to access memory and other instruction operation is performed in the register between.(5) in a simple and effective way to support advanced language.7 operand types: integer, decimal, floating point (point), characters, strings, vectors, stack etc..There are two ways to express 8, operand types: (1) specified by the operation code encoding. (2) data can be a mark by the hardware to explain the type of the operand specified by these tags, so as to choose the appropriate operation.9, the operand type size: byte (8), the word (16b), the word (32b), double word (64b)The third chapter1, pipeline technology: refers to a repeat of the timing process is decomposed into several sub processes, and each process can be effective in its special function with other processes executing at the same time.2, pipeline classification: (1) according to the function of the number of points: single function pipeline, multifunctional pipeline;(2) according to the connection between the same time segments to static and dynamic pipeline pipeline(3) according to the line level: component level pipeline (operation line), pipelined processor (instruction pipelining), inter processor pipeline (macropipeline)(4) according to whether there is water between each section of a feedback loop: linear and nonlinear pipeline pipeline(5) according to the data representation: scalar processor, vector processor3, the first processor controller structure comprises three independent controllers and four buffer stack. The three controller: memory controller, controller, controller operation instruction. Four: the first instruction buffer buffer stack stack, linear buffer stack, stack current readings, then write the number of stack.4, the throughput is the number: the number of tasks or output per unit time of the pipeline. TP = n / TkThe actual throughput rate is less than the maximum throughput of Tk = (k+n-1) t5, speedup: refers to the speed of the line and the function of non line speed ratio (s);Efficiency: refers to the utilization rate of pipeline equipment (E).6, if the line segment is equal to the time: throughput rate: TP=n/ (k+n-1) t TPmax=1/ tIf each execution time is not equal, complete several tasks: TP=n (sigma / Ti + (n-1) max (delta T1, Delta t2... Delta TK)7, the speedup and efficiency of the relationship: E = s/m or S = mE8, efficiency and throughput of the relationship: E = TP t0 TP = E/ or T11, efficiency: K E = n a task flow segment occupied area of the total space / time zones = T0 / K Tk?E = n/ (k+n-1) S = k? N / TP / (k+n-1) = n (k+n-1) t12, single function pipeline stack: refers to only perform one fixed function pipeline stack.13, multi functional water: water each stack stack to achieve different functions through different connections.14, nonlinear pipeline scheduling task: to find a minimum cycle, according to a new task to the input line cycle, each function section line are not in conflict, and the pipeline throughput and maximum efficiency.15, nonlinear pipeline: between some water section of feedback loop or feed-forward loop.16, start distance: continuous input even intervals between tasks.17, pipeline conflict: several tasks competing for the same water section.18, forbidden vector: distance between sets of appointments each row in the table of any of the two "x".19, conflict vector: C = (Cm? Cm-1?... C1? C2? M) which allowed maximum value in the vector20, the relevant data: in the process of execution of the instructions, if the instructions used, the number of variables, such as the operation is in front of the results of the implementation of the relevant instructions, called data.21, control: caused by conditional branch instructions, rotor program instructions, the relevant interrupt.22, three kinds of data: limit write, read after write, write.The fourth chapter1, ILP: when there are correlation between instructions in the pipeline, they can overlap parallel execution, the potential parallelism is called instruction level parallelism exists in this sequence of instructions.2, in a variety of technical development loop level parallelismin the most basic techniques are: instruction scheduling, loop unrolling technique and technical change.The fifth chapter (storage system)1, the definition method of memory storage system: two or more than two speed, capacity and price vary with hardware, software or hardware and software combination connected into a storage system. And the memory system is transparent to application programmers, and to the application programmer, it is a memory, the memory of the memory close to the speed of the fastest, the storage capacity and the storage capacity of the largest equal unit capacity price close to the lowest memory.2, the storage system is divided into two categories: (1): Cache storage system composed of Cache and main memory, the purpose is to improve the speed of memory. (2) virtual storage system consists of a main memory and hard disk, to expand memory capacity.3, the price of storage system: C = (C1S1+C2S2) / (S1+S2)4, the storage system speed: Representation: access cycle, access cycle, storage period, access time, etc..5, the hit rate of definition: probability in M1 memory access toU = N1 / (N1+N2) N1 of M1 memory access times, N2 is on the M2 memory access times.6, the efficiency of access:T1 1E = T1/T = = = f (U, T2/T1)U? T1+ (1-u) T2 u+ (1-u) T2/T1?7, using prefetching to improve the hit rate (method).Do not hit, a block of data in a plurality of adjacent M2 memory units taken out into the M1 memory.U (u+n-1 / N) = 'U' is the pre shooting technique after u is the original hit rate;The product of n as the data block size and the number of data reuse.8, accelerate the internal address transformation method: (1) the table of contents: with a small capacity high speed memory storing the page table; (2): fast and slow speed of table table table to form a two level storage system; (3): the hash function associative access into the access address access.9, the page replacement algorithm: (1) random algorithm (RAND);(2) FIFO algorithm (FIFO); (3) least recently used (LFV); (4) LRU (LRV); (5) the optimal replacement algorithm (OPT).10, "bump" phenomenon: a page is just out of the main memory, but also to be transferred.11, the stack type replacement algorithm: for an arbitrary program page address stream for the two main memory page number distribution, a memory allocated m page and n a memory page, and M = n. If at any time t, main memory page number set Bt satisfy the relation: Bt (m) = Bt (n) is a type of this kind of algorithm stack replacement algorithm.12, Cache address mapping method: (1) fully associative mapping;(2) direct mapping; (3) set associative mapping;(4) choose a set associative mapping mapping section (5).13, Cache memory replacement algorithm: (1) rotation method (2) LRV algorithm (3) comparing (4) stack method.The consistency of Cache 14, single processor:Direct method: [including write write through method, CPU writes data to Cache, while the page is written to main memory.And write back: "conflict modify method, CPU data into Cache, do not write memory, only when the replacement when the modified Cache block write back to main memory.Comparing the advantages and disadvantages of the two:(1) reliability: write direct method is better than the write back.(2) the amount of memory and communication, write back and writeless than direct method.(3) the complexity of control, direct write back write is simple.(4) the hardware implementation cost is written back to the write through law.The consistency of 15, multiprocessor: (1) the directory protocol (2) and listen to the agreementThe sixth chapter (input / output system)1, measure the performance index of I/O system mainly has the response time and reliability.Data transmission, 2 disk external transfer rate and internal transfer rate.3, the external transmission rate (burst data transmission rate): computer read from the cache data into the hard disk by disk interface, to the corresponding speed controller.4, internal transfer rate (sustained transfer rate): hard disk data from disk read, to buffer memory on the hard disk speed.5, reliable performance parameters reflecting storage peripherals are reliability, availability and credibility.6, reliability measure: mtbf.7, availability metrics: mean time between failure.8, bus: bus communication link between each subsystem shared, the two has the advantages of low cost and diversity.The main disadvantage of the 9 bus: it has exclusive use, causing the bottleneck equipment information exchange, thus limiting the total throughput of I/O system.10, split transaction bus: there is a plurality of devices, available through the packaging technology to improve the bus bandwidth, so that each I/O operation will not have to occupy the bus in the transmission process, the basic idea of the bus transaction is divided into two parts of requests and responses, such as the bus idle time interval to request and response in the a bus transaction between other bus transaction is used. (also known as water bus, bus, bus suspension packet switching)11, the control of external equipment input / output mode is divided into: direct transfer procedures, query, interrupt, DMA, channel mode.Addressing mode 12, I/O equipment: (1) memory mapped I/O or unified addressing (2) I/O addressing individual equipment13, channel: to perform limited I/O instruction, and can be a plurality of peripheral devices share a small dedicated DMA processor.14, channel function: (1) received from the CPU I/O command, and according to the peripheral equipment and the channelinstruction requires the selection of the specified connection.(2) CPU channel organization channel program, remove channel instructions from the main memory, decode the channel command, and issued a command to the device controller is selected according to the needs of. (3) as the main memory and peripheral assembly and disassembly information, data transmission and memory I/O control equipment and provide a transmission path, indicating the data memory address and send byte number. (4) specify the transfer at the end of the operation to be carried out. (5) check the peripheral equipment working state, normal or fault.(6) complete the format conversion required in data transmission process.15, types of channels: (1) channel multiplexer (2) selects the channel (3) multi channel array.The working process, 16 channels: (1) using SVCI into management program in the user program by CPU, through the management procedures to organize a channel program, and start the channel. (2) channel processor implementation of CPU for which the organization's channel program, complete the assigned work data I/O. Channel processor execute channel program was performed with the CPU user program in parallel.(3) channel program after the end to the CPU interrupt request, CPU responding to an interrupt request after second times to enter the operating system, call management program of the I/O interrupt request processing.The seventh chapter (multiprocessor)1, Cache coherence protocol: (1) the directory protocol and listen to the agreement; (2) laterally divided into: write Invalid Protocol and write update protocol; (3) longitudinally divided into single treatment protocol and single data stream protocol.2, the classification of parallel computer architecture: single instruction single data stream (SISD), single instruction multiple data stream (SIMD) and multiple instruction single data stream (MISD) and multiple instruction multiple data stream (MIMD).3, the directory protocol is divided into three categories: full map directory, the directory, the directory chain co..4, the chain Directory: by maintaining a directory pointer chain to track shared data copy.Thought: when P1 read x memory, X sent to cachel, a chain and write cachel end pointer CT also holds a pointer to a cachel in memory, P2 to read x, memory holds a pointer to a cachel2, a processor need to write x, he must be along the whole a directory even send a data information in the received signal to answer the invincible, all processors, memory to allow the processor to write rightThe cachel data block in need of replacement, to delete the cache directory from the chain, there are solutions;(1) the cachei+1 pointer to cachei+1, store the new data blockin cachel (2) cachel and cachel in the chain seat all subsequent units in X is invalid (3) using two-way chain, when replacing the no longer need to traverse the entire chain, but the pointer has doubled, agreement more perfectAdvantages: B does not limit the sharing of copy number data blocks while maintaining scalability, pointer length has the number of processors on the relation between growth, the number of processors and the number of pointers for each block of data is independent of the cacheDisadvantages: complex chain directory in Chengdu more than two directory5 definition: Internet; is symmetric systems or distributed system nodes may like processor, memory module or other devices, they exchange information through the Internet, in the topology, the Internet provides a set of interconnected or image as input and output between two groups of nodes6 (1) the number of nodes is called the network scale(2) the number of edges and nodes interconnected to the maximum value of the node is called the network diameter(3) any network nodes even the maximum length of the shortest path is called the network diameter(4) equal width (b) in the network into a two phase digestion method, the minimum number of edges cut along the road is called channel bisection width(5): refers to the designation of the routing path selection in network communication7 function: if the Internet Interconnection Network N a end and N end respectively with the integer 0, 1,...... .N algebra, is said to work with the interconnection function number and number of symmetric relations such asSaid method 8 interconnection network(1) the interconnection function representation (2) graphical representation (3) input and output the corresponding representation9 common data routing (or interconnection function) function:(1) the replacement cycle (2) (3) (4) uniform shuffle hypercube routing function (5) broadcasting and communication。

计算机3级考试题库及答案

计算机3级考试题库及答案随着计算机技术的快速发展和广泛应用,越来越多的人开始关注计算机等级考试。

计算机3级考试作为一项相对较高级别的考试,对考生的计算机知识和应用能力提出了较高的要求。

本文将为大家提供一份计算机3级考试题库及答案,以供参考和学习。

一、计算机组成与体系结构1. 什么是计算机的硬件系统?它包括哪些组成部分?答案:计算机的硬件系统是指计算机中各种物理设备的总称。

它包括中央处理器(CPU)、主存储器(内存)、输入设备、输出设备和辅助存储器等组成部分。

2. 简述冯·诺依曼体系结构的基本原理。

答案:冯·诺依曼体系结构是一种计算机体系结构,基于存储程序的概念。

它的基本原理包括程序和数据存储在同一存储器中、以二进制形式表示指令和数据、按照指令序列的顺序执行程序、程序可以通过跳转和循环控制执行的流程。

二、操作系统1. 什么是操作系统?它的主要功能是什么?答案:操作系统是计算机系统中的核心软件,负责管理和控制计算机的各种资源,并为用户提供一个方便、高效的工作环境。

它的主要功能包括进程管理、内存管理、文件系统管理、设备管理和用户接口等。

2. 请简述进程和线程的概念及区别。

答案:进程是指计算机中正在运行的一个程序的执行实例。

它拥有独立的内存空间和系统资源,是系统进行资源分配和调度的基本单位。

线程是进程中的一个执行单元,是进程中的一个指令流。

与进程相比,线程之间共享同一进程的内存空间和系统资源,可以提高程序的运行效率。

三、数据库概论1. 什么是数据库?数据库管理系统(DBMS)的主要功能是什么?答案:数据库是指存储有组织的数据的集合,具有数据共享和数据独立性的特点。

数据库管理系统是一种管理和组织数据库的软件,它的主要功能包括数据定义、数据操纵、数据控制和数据查询等。

2. 请简述关系数据库模型的基本概念。

答案:关系数据库模型是一种以关系为基础的数据库模型。

它将数据组织成一张表格形式的结构,表格中的每一行代表一个实体记录,表格中的每一列代表一个属性。

计算机体系结构CISC与RISC原理试卷

计算机体系结构CISC与RISC原理试卷(答案见尾页)一、选择题1. 计算机体系结构中的CISC和RISC分别代表什么?A. 简单指令集计算机和大指令集计算机B. 复杂指令集计算机和简单指令集计算机C. 高性能计算机和低性能计算机D. 通用计算机和专业计算机2. 在CISC架构中,下列哪个选项不是其特点?A. 指令集中包含大量的通用指令B. 指令执行速度快C. 指令长度不固定D. 哈佛架构3. RISC架构的设计原则中,哪项是错误的?A. 设计更少的指令集B. 指令流水线处理C. 使用大量的寄存器D. 提高指令的执行效率4. CISC和RISC架构的主要区别是什么?A. 指令集的大小B. 指令的执行速度C. 系统的复杂性D. 编程的难易程度5. 下列哪个选项是RISC架构的特点?A. 指令集中包含大量的通用指令B. 指令执行速度慢C. 指令长度不固定D. 使用大量的寄存器6. 在CISC架构中,为了提高指令执行效率,通常会采用哪种技术?A. 指令乱序执行B. 指令并行处理C. 指令分支预测D. 指令流水线处理7. RISC架构中,为了减少指令的执行时间,通常会采用哪种技术?A. 指令乱序执行B. 指令并行处理C. 指令分支预测D. 指令流水线处理8. 在RISC架构中,为了提高指令吞吐量,通常会采用哪种技术?A. 指令乱序执行B. 指令并行处理C. 指令分支预测D. 指令流水线处理9. CISC和RISC架构在设计计算机系统时各有优势,下列哪个选项是RISC架构的优势?A. 指令集大小固定B. 指令执行速度慢C. 系统复杂性低D. 编程难度低10. 在CISC架构中,处理器需要执行多少条指令才能完成一个任务?A. 一条B. 有限的几条C. 很多条D. 不固定11. RISC架构的主要特点是什么?A. 大量不同的指令集B. 流水线处理C. 复杂的控制逻辑D. 所有以上选项12. 在RISC架构中,哪类指令通常被设计成单周期执行?A. 控制指令B. 数据处理指令C. 调用指令D. 所有以上选项13. CISC和RISC在指令执行时间上的主要区别是什么?A. CISC的指令执行时间较长B. RISC的指令执行时间较短C. 两者指令执行时间相同D. 无法确定14. 在CISC架构中,哪种类型的指令通常用于执行复杂的操作?A. 简单指令B. 复杂指令C. 控制指令D. 数据处理指令15. RISC架构中,为了提高指令流水线的效率,通常会采用哪两种技术?A. 指令预取和动态调度B. 动态分支预测和流水线控制C. 指令合并和寄存器重命名D. 所有以上选项16. CISC和RISC在指令集设计上的主要区别是什么?A. CISC具有更多的指令B. RISC具有更多的指令C. CISC具有更少的指令D. RISC具有更少的指令17. 在RISC架构中,为了减少指令执行时间,通常会采用哪项技术?A. 单指令多数据(SIMD)操作B. 多线程处理C. 指令流水线D. 动态调度18. CISC和RISC在设计理念上的主要区别是什么?A. CISC注重指令集的复杂性B. RISC注重指令集的简单性C. CISC注重指令的执行速度D. RISC注重指令的并行处理19. 在CISC架构中,以下哪个不是其显著特点?A. 大量通用寄存器B. 复杂的指令集C. 指令执行速度快D. 通常需要更多的内存20. CISC和RISC的主要区别是什么?A. 指令集的大小B. 指令的执行速度C. 处理器的功耗D. 以上都是21. 在RISC架构中,通常采用哪种方式来提高指令的处理效率?A. 简化指令集B. 增加指令的数量C. 缩短指令的运行时间D. 降低指令的执行频率22. CISC架构的处理器通常需要多少个时钟周期来完成一条指令的执行?A. 很少B. 几个C. 几十D. 几百23. RISC架构的一个主要优点是:A. 更高的指令集密度B. 更高的处理器速度C. 更高的内存访问效率D. 更好的能耗比24. 在CISC架构中,为了提高指令集的利用率,通常会采用哪种技术?A. 指令流水线技术B. 动态调度技术C. 哈希映射技术D. 以上都是25. RISC架构的一个设计目标是:A. 实现高速的数据处理B. 降低处理器的功耗C. 提高指令集的复杂性D. 增加处理器的复杂性26. 在设计嵌入式系统时,为什么CISC架构可能比RISC架构更合适?A. 嵌入式系统的资源通常有限B. 嵌入式系统的任务通常简单C. CISC架构的指令集更适合复杂任务的处理D. RISC架构的指令集不适合嵌入式系统27. CISC(复杂指令集计算机)的主要特点是什么?A. 指令执行速度快B. 指令种类多,指令长度不固定C. 适用于高并行处理任务D. 代码体积小28. RISC(精简指令集计算机)的设计理念是什么?A. 提供高性能B. 缩小指令集以减小芯片面积C. 提高指令流水线效率D. 增加寄存器数量29. 在CISC架构中,通常哪种类型的指令执行速度最快?A. 短指令B. 长指令C. 控制指令D. 数据处理指令30. RISC架构中,为了提高指令执行效率,通常采用什么技术?A. 指令流水线技术B. 动态调度技术C. 流水线分支预测技术D. 多线程技术31. 在RISC架构中,倾向于使用大量寄存器来存储哪些类型的数据?A. 整数B. 浮点数C. 字节D. 指针32. RISC架构中的指令通常具有较短的地址空间,这是为了什么?A. 提高指令寻址速度B. 减少内存访问开销C. 降低硬件复杂性D. 增加指令集的长度33. 计算机体系结构中的CISC和RISC是指什么?A. 计算机的中央处理单元(CPU)的架构B. 计算机的指令集架构(ISA)C. 计算机的存储设备D. 计算机的输入/输出设备34. 在CISC和RISC体系中,哪一种更倾向于使用大量的寄存器?A. CISCB. RISC35. CISC架构中,指令的执行通常涉及多个阶段,这被称为?A. 指令流水线B. 指令并行性C. 指令集并行性D. 以上都不是36. RISC架构的一个关键特性是什么,它使得它在某些情况下比CISC更有效率?A. 大量的通用寄存器B. 高效的指令流水线C. 指令集中只有少数几种常见的指令D. 内置的硬件乘法器37. 在RISC设计中,为了减少指令执行的时间,通常会采用哪种技术?A. 指令分散B. 堆栈操作C. 管道技术D. 以上都不是38. CISC和RISC在指令集设计上有何不同?请举例说明。

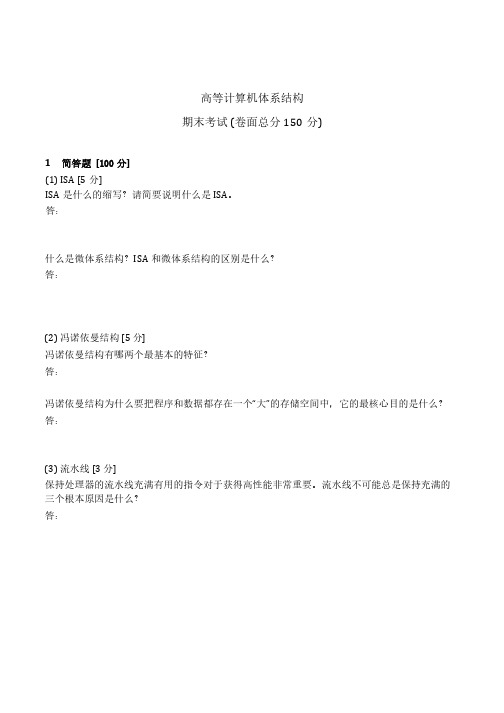

高等计算机体系结构期末考试试卷

高等计算机体系结构期末考试 (卷面总分150分)1简答题 [100分](1)ISA [5分]ISA是什么的缩写?请简要说明什么是ISA。

答:什么是微体系结构?ISA和微体系结构的区别是什么?答:(2)冯诺依曼结构 [5 分]冯诺依曼结构有哪两个最基本的特征?答:冯诺依曼结构为什么要把程序和数据都存在一个“大”的存储空间中,它的最核心目的是什么?答:(3)流水线 [3 分]保持处理器的流水线充满有用的指令对于获得高性能非常重要。

流水线不可能总是保持充满的三个根本原因是什么?答:(4) 异常 vs. 中断 [6 分]我们说当处理器检测到异常就需要处理,而中断可以在“方便的时候”处理。

为什么异常在检测到之后就要处理?答:说在“方便的时候”处理中断是什么意思?答:为什么很多中断可以在“方便的时候”处理?答:(5) 分支预测 [6 分]分支目标缓冲(BTB)的目的是什么?答:假设一台机器的流水线有10个流水段流水线,分支的解决在第8个流水段。

同时,假设20%的指令是分支。

对于这台机器,每个分支预测错误时会浪费多少条指令的工作?答:(6) 乱序 vs. 数据流 [7分]在乱序执行处理器中,什么时候会发生取指令的动作?答:在数据流处理器中,什么时候会发生取指令的动作?答:在乱序执行处理器中有一个结构叫做保留站,请问保留站本质上是解决什么问题的?答:通常,在数据流机器中有一个结构叫做“matching store",与乱序执行处理器中的保留站功能类似,你能不能猜一下“matching store"是用来做什么的?☺答:(7) 减少停顿 [4分]编译器能够重排序指令以减少流水线处理器的停顿。

编译器做这样的优化目的是找到独立的指令插入相关的指令之间,使得当消费者指令进入流水线时,生产者指令已经生产出结果。

控制相关会阻碍编译器重排序指令能力的发挥,为什么会这样?答:(8) DRAM [5 分]DRAM预充电(precharge)命令的目的是什么?答:DRAM刷新的目的是什么?通常DRAM刷新有哪三种基本的方法?答:(9) TLB [4分]TLB 缓存的是什么内容?答:TLB缓存的这些信息在什么位置?答:(10) 互连网络[6分]互连网络的路径多样性概念是指从源节点到目的节点可以存在许多不同路径的现象。

计算机体系结构试题及答案免费版本

计算机体系结构试题及答案1、计算机高性能发展受益于:(1)电路技术的发展;(2)计算机体系结构技术的发展。

2、层次结构:计算机系统可以按语言的功能划分为多级层次结构,每一层以不同的语言为特征。

第六级:应用语言虚拟机 ->第五级:高级语言虚拟机 ->第四级:汇编语言虚拟机 ->第三级:操作系统虚拟机->第二级:机器语言(传统机器级) ->第一级:微程序机器级。

3、计算机体系结构:程序员所看到的计算机的属性,即概括性结构及功能特性。

4、透明性:在计算机技术中,对本来存在的事物或属性,从某一角度来看又好像不存在的概念称为透明性。

5、Amdahl提出的体系结构是指机器语言级程序员所看见的计算机属性。

6、经典计算机体系结构概念的实质3是计算机系统中软、硬件界面的确定,也就是指令集的设计,该界面之上由软件的功能实现,界面之下由硬件和固件的功能来实现。

7、计算机组织是计算机系统的逻辑实现;计算机实现是计算机系统的物理实现。

8、计算机体系结构、计算机组织、计算机实现的区别和联系?答:一种体系结构可以有多种组成,一种组成可以有多种物理实现,体系结构包括对组织及实现的研究。

9、系列机:是指具有相同的体系结构但具有不同组织和实现的一系列不同型号的机器。

10、软件兼容:即同一个软件可以不加修改地运行于系统结构相同的各机器,而且它们所获得的结果一样,差别只在于运行时间的不同。

11、兼容机:不同厂家生产的、具有相同体系结构的计算机。

12、向后兼容是软件兼容的根本特征,也是系列机的根本特征。

13、当今计算机领域市场可划分为:服务器、桌面系统、嵌入式计算三大领域。

14、摩尔定律:集成电路密度大约每两年翻一番。

15、定量分析技术基础(1)性能的评测:(a)响应时间:从事件开始到结束之间的时间;计算机完成某一任务所花费的全部时间。

(b)流量:单位时间内所完成的工作量。

(c)假定两台计算机 x、y;x比 y 快意思为:对于给定任务,x的响应时间比y少。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

一填空题(每空1分,共30分)

1、系列机是指具有相同的体系结构,但具有不同组织和实现的一系列不同型号的机器。

2、存储程序计算机结构上的主要特点之一是以运算器为中心。

3、从计算机系统结构的多级层次结构可知,通常情况下,第1、2、3级用解释方法实现,第4或更高级用翻译方法实现。

4、对于最常见的事件,通常赋予它优先的处理权和资源使用权,这是计算机体系结构设计中的大概率事件优先原则。

5、容量为64块的Cache采用组相联方式映像,字块大小为128字节,每4块为一组,若主存容量为4096块,且以字编址,那么主存地址为 19 位,主存区号为 6 位。

6、可改进比例的值总是小于等于1 。

7、一般有两种策略来保存寄存器的内容,即:调用者保存和被调用者保存。

8、DLX指令集提供了立即数寻址、寄存器寻址、偏移寻址和寄存器间接寻址4种寻址方式。

9、对某流水线处理器测试时发现其存在结构冲突,通常可采用资源重复和流水化功能单元方法解决该问题。

10、编译器通过重新组织代码顺序消除暂停的技术被称为指令调度。

11、按照流水的级别可以把流水线分为部件级流水线、处理机级流水线和处理机间流水线。

12、为解决流水线使用非流水数据通路的寄存器引起冲突,在流水线设计中采用寄存器文件技术解决该问题。

13、Cache的替换算法常见的有 FIFO 、LRU 和随机法。

14、改进Cache性能的方法主要有降低失效率、减少失效开销和减少Cache命中时间。

15、减少流水线处理分支暂停时钟周期数的途径包括尽早判断分支转移是否成功和尽早计算出分支成功转移的PC值。

二、选择题(1—15题,每题1分,共15分)

1、下面的指令中, A 不属于RISC处理器指令集。

A.ADD R4,[1000] B.LD R3,(R4) C.SUB R4,R3 D.SD 0(R3),R4

2. 在其它部件性能保持不变的情况下,对CPU性能的不断改进并没有获得期望的结果,这主要是受到了 A 的影响。

A.Amdahl定律

B.流水线

C.指令集

D.体系结构

3、对cache性能进行分析时,我们发现 A 不受cache容量的影响。

A.强制性失效 B.容量失效 C.冲突失效 D.3C失效

4、若某CPU只有一个存储器,采用DLX流水线并执行如下的程序段,①SD (R1),R2

②LD R3,(R1)#4③ADD 0(R1),#8④SUB R3,R1;则该程序段中指令①和指令④的关系属于 A 。

A 数据相关

B 名相关

C 控制相关

D 结构相关

5、在下列存储器中访问速度最慢的是 D 。

A Cache

B SDRAM

C DRAM

D Flash

6、最近计算机上采用的SSD(固态硬盘)实质上是 A 存储器。

A.Flash B.磁盘 C.磁带 D.光盘

7、计算机使用总线结构的主要优点是便于实现积木化,同时 C 。

A.减少了通信传输量B.提高了通信传输的速度

C.减少了通信传输线的条数D.有利于芯片中布线

8、下面关于流水线的说法不正确的是 D 。

A 流水线由若干个“段”或“级”组成

B 流水线有“通过时间”

C 流水线的“各段时间”应尽量相等

D 流水线的”深度”越多越好

9、我们常说的32位处理器是指处理器的 A 是32位的。

A 数据总线

B 控制总线

C 地址总线

D 所有的总线

10、科学计算中采用向量处理机的主要原因是 A 较少。

A数据相关B控制相关C结构相关D非向量处理机

11、为了便于实现多级中断,保存现场信息最有效的方法是采用_B__.。

A.通用寄存器B堆栈C.存储器D.外存

12、在下面描述的RISC指令系统基本概念中不正确的表述是 A 。

A.选取使用频率低的一些复杂指令,指令条数多。

B.指令长度固定

C.指令功能简单

D.指令运行速度快

13、在下述I/O控制方式中,主要由程序实现的是 B 。

A.I/O处理机方式B.中断方式C.DMA方式D.通道方式

14、以下属于降低Cache失效率的方法是 B 。

A.子块放置技术 B.编译器优化 C.采用两级Cache D.虚拟Cache

15、现有一个Web服务器,其它部分不变的情况下,若采用如下的增强方式:采用40个CPU,想要达到30的加速比,则串行部分的比率最大是 A 。

A.0.11 B.0.12 C.0.10 D.0.13

三、简述题(每题5分,共25分)

1、解释如下几个缩写:RISC、ISA、MIMD、RAID、Cache。

RISC精简指令集计算机

ISA工业标准结构

MIMD多指令流多数据流

RAID廉价磁盘冗余阵列

Cache高速缓冲存储器

2、试说明名相关的两种类型。

反相关:指令i先执行,指令j写的名是指令i读的名。

反相关指令之间的执行顺序是必须保证的,反相关就是先读后写相关。

输出相关:指令j和指令i写相同的名。

输出相关指令的指令顺序是不允许颠倒的。

输出相关就是写后写相关。

3、试说明定向技术的思想。

定向技术的思想是:在某条指令产生一个计算结果之前,其他指令并不真正需要该计算结果,如果将该计算结果产生的地方直接送到其他指令需要他的地方,那么就可以避免暂停。

4、试说明伪相联Cache的特点。

伪相联Cache既能获得多路组相联Cache的低失效率,又能保持直接映像Cache的命中速度。

采用这种方法时,在命中情况下,访问Cache的过程和直接映像Cache 中的情况相同,而发生失效时,在访问下一级存储器之前会先检查Cache另一个位置,看是否匹配。

5、试说明分布式共享多处理机的优缺点。

分布式存储器结构的优点:

(1)如果大多数的访问是针对本结点的局部存储器,则可降低对存储器和互连网络的带宽要求;

(2)对局部存储器的访问延迟低。

主要缺点:处理器之间的通信较为复杂,且各处理器之间访问延迟较大。

四、图表题(第一题6分,第二题9分,共15分)

1、(6分)下图是写操作流水化的硬件结构,试说明采用该技术的原因及其工作特点。

每个写操作过程分为两个阶段完成,第一阶段进行标识比较,并把标识和数据存入延迟写缓冲器中,第二阶段再进行写入,这两个阶段按流水方式工作。

这样,当前的写标识比较就可以和上一个写的数据写入并行起来,实现每个时钟周期完成一个写操作

2、(9分)下面是采用DLX浮点部件的Tomasulo算法执行过程中用到的状态表,试填写状态表中的相关空白。

假定:浮点流水线的延迟如下:加法2个时钟周期,乘法10个时钟周期,除法40个时钟周期。

给出SUBD 将要写结果时状态表的信息。

只填写相关部分空格。

五、计算题(第一题7分,第二题8分,共15分)

1.某RISC处理机各类指令使用频率和理想CPI(指令和数据访问Cache命中率为100%时的CPI)如下表所示。

而实际测得的指令访问Cache缺失率(miss rate)为5%,数据访问的Cache缺失率为10%,Cache的缺失损失(miss penalty)为40个时钟周期。

1)该机器在无Cache缺失(理想情况)时的CPI是多少?(3分)

1)CPI=43%X1+21%X2+12%X2+24%X2=1.57

2)对指令讲,指令Cache的访问占全部访问的100%/(100%+21%+12%)=75%

对数据来讲,数据Cache的访问占全部访问的(21%+12%)/(100%+21%+12%)=25% 非理想平均访存时间=命中时间+失效率X失效开销

=1.57+(75%X5%+25%X10%)X40=1.57+2.5=4.07

则:4.07/1.57=2.59=2.6 大约快2.6倍

2.在一台单流水线处理机上执行下面的程序。

每条指令都要经过“取指令”、“译码”、“执行”和“写结果”4个流水段,每个流水段的执行时间都是10ns。

采用基本的DLX流水线,执行如下指令段:

1 SUB R0, R0 ;R0←0

2 LD R1, #4 ;R1←向量长度4

3 LOOP: LD R2, A(R1) ;R2←A向量的一个元素

4 MUL R2, R1 ;R2←(R2)×(R1)

5 ADD R0, R2 ;R0←(R0)+(R2)

6 BNEZ R1, LOOP ;R1←(R1)-1,若(R1)≠0 转向LOOP

7 SD (R3), R0 ;保存结果

采用“预测分支失败技术”。

画出指令流水线的时空图(中间部分可以省略,图中可用指令序号表示),计算流水线的加速比。

(8分)。