学习笔记-candence16.6-原理图部分

Altium Designer 16电路设计 第六章 绘制层次电路原理图

6.3层次电路原理图的绘制方法

(3)放置显示模块图纸入口,如图6-16所示。

图6-16 显示模块放置了3个图纸入口,说明有三个通过需要跟其他图纸符号连接,一个是+5V 电源端口,一个GND地线端口,PA[2..5]是代表PA2、PA3、PA4、PA5的总线端口。 放置图纸入口前,先规划好子电路图与子电路图之间电气连接的端口类型、名称、数 量,采用何种方式连接,在AD16中,连接方式可分为三种:导线连接、总线连接、信 号线束连接,三者之间的区别将在绘制子原理图详细讲解。

母原理图 一级子图 二级子图

图6-1

图6-2

6.1 层次电路原理图简介

二、层次电路图产生的原因: 对于结构复杂的、元器件较多的、规模庞大的电路系统,很难在一张电路 原理图上完整的绘制出来;企业或者公司在电子产品的开发与研究上,为了缩 短周期,往往是一个团队同时在工作,需要把完整复杂的电路系统分割成不同 的电路模块,分派给不同的设计组完成。因此,层次电路原理图的设计方式应 运而生。 母原理图由图表符连接而成,而一个图表符对应一个子电路图,如图6-3所 示:

图6-20

6.3层次电路原理图的绘制方法

用同样的方法,产生并绘制其他子原理图。绘制好的层次电路原理图如图6-20、 图6-21、图6-22、图6-23所示。

图6-21

6.3层次电路原理图的绘制方法

图6-22

6.3层次电路原理图的绘制方法

图6-23

6.3层次电路原理图的绘制方法

6.3.2 层次原理图之间的切换 绘制完成的层次原理图一般包含了顶层原理图和多张子原理图, 在编辑时,常常需要在这些原理图之间互相切换,实现层次性原理图 之间的切换,一般有两种方式:

① ②

单击此标创建图纸符号

蚊子Cadence16.6粗略笔记 (1)

1 原理图笔记 (1)2 PCB笔记 (6)1 :原理图画完处理:1:检查连接性(眼睛看)2 重新编号,tool--->anotate3 DRC检查, tool---->Design rules check4 tools--->create netlist--->allegro(破解的不完全,有时候需要自己创建一个allgero文件夹。

2:PCB完成后处理事项:1 看连接线是否都铺完,tools->quick reqorts->unconnected pinsshape dynamic stateshape no netshape islandsDRC2 tools-->database check3 display-->state(保证全为绿色)4丝印层显示准备(把需要生成丝印的东西提取到丝印层):(显示stack-up(选pin/via/drc)/geometry(选outline/assemble_top/bottom/pin_number)/manufacturing(选autosilk_top/bottom))先把所有电气层关掉,stach-up-->所有etch关掉略去:5 生成丝印层---->manufacture-->silkscreen-->layer(选both)/elements(选both)/classes and subclasses(把那些东西提取出来放到丝印层,改package geometry和reference designator为silk 其余为none-->执行silkscreen6:提取之后,调整丝印信息,例如器件编号位置。

7 添加文字说明:add-->text-->manufacturing-->autosilk_top-->点击要添加文字的位置,输入文字就可以了8 设置钻孔文件数据参数——>manufacture-->nc-->nc parameters-->点击closed就自动把参数文件放置到设置好的目录下。

cadence allegro 16.6入门学习参考步骤

1

2 2

3

第一章 封装

一、建 焊盘

打开建立焊盘的软件 Pad Designer 路径:

, 进入下图所示,设定相关参数:

包括采用的制式,现在选公制单位毫米,精度 3,右侧问是否需要多重钻孔,这个 功能一般是用于做非圆孔。一般圆孔不用勾选。 下面设定钻孔样式,一般是圆孔,钻孔内部是否镀铜 plated(no plated 即为不镀铜,一 般用于塑胶件定位孔),再是钻孔直径,设置精度,是否偏移等。 如果是表贴元件,钻孔直径设为 0。

1

Allegro 16.6 的学习笔记

更改历史: .................................................................................................... 错误!未定义书签。 第一章 建封装 ................................................................................................................................ 3

cadenc_Allegr_16.6_培训教程_简体

第一章 User Interface本章的主要内容介绍allegro 操作接口,透过本章学习可以对Allegro 的工作接口有了大致的了解,同时也能体验出Allegro PCB Layout 时的强大功能。

A. 程序的启动点选除了以上Allegro 主程序,我们还会常用到以下几个常用工具:• Padstack DesignerPadstack Designer 的作用是建立和修改Pad ,具体会在下面章节中讲到。

• DB doctorDB doctor 的作用有三个:1.板子Data-base 的检查2.板子Data-base 的修复3.更新板子上的DRC支持的文件种类为: .brd .mcm .mdd .psm .dra .pad and . sav databases.B. Cadence SPB ToolsPCB Designer 在 V16.5 分成2个基本等级,用户可以根据自己的需求购买不同等级的Tool 及搭配的option (Onlyfor Allegro),主要功能差别见下表:在开启 Allegro 时,系统会先跳出如下图的对话框,让您选取要使用的软件等级。

123窗口中所列出的软件项目是依据系统所能选取的 License 功能來决定 以下也列出几个常用的Option 来介绍:PCB High-Speed option :针对高速设计能提供更多的功能 Miniaturization option :针对HDI 设计能提供更多的功能如果在使用过程中想更改产品,可以在点选下拉菜单File 项目下面的Change Edit ,就会出现如上图所示的对话框时,选择所需产品。

C. Allegro 常用档类型的介绍D. Allegro的目录结构Allegro的文件目录可以分为三部分:安装路径、工作路径和用户环境路径。

安装路径:系统默认的安装路径为:C:\Cadence\SPB_16.6,在安装时使用者可以根据自己随意更改安装路径。

Cadence 16.6 PCB Edit 新功能连载(三)(转载)

Cadence 16.6 PCB Edit 新功能连载(三)今天我要和大家继续学习一下capture其它的一些新功能。

一.Browsing Old Design Versions and Modifying Message 大家知道,以前如果我们用新版本打开以前老版本做的设计,那么这个design就会自动被升级成新版本。

这样的话被打开的设计就无法用老版本软件打开了,那么都是16.x的还可以接受,我们可以降版本下去。

如果是15.x的版本,那么。

就麻烦了哈哈。

16.6版本下载允许客户打开以前的老版本设计,同时不将原来设计升级,只达到用来看的目的。

这样我们回头还是可以用低版本继续打开此设计。

但是这个要在软件里面做个小小的更改。

我们不妨做个试验。

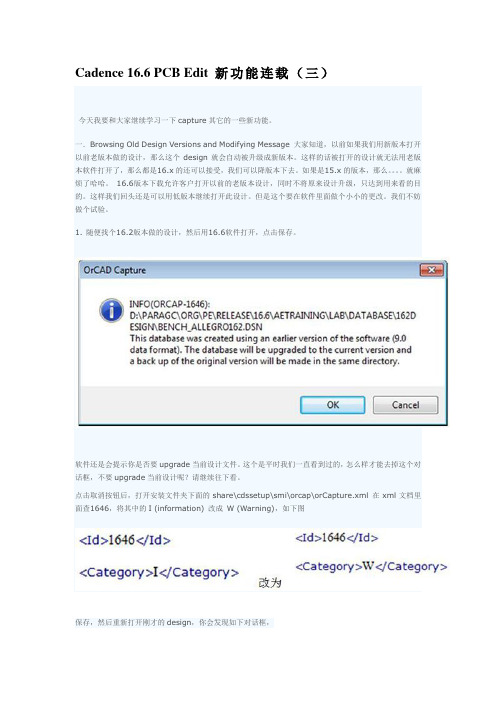

1. 随便找个16.2版本做的设计,然后用16.6软件打开,点击保存。

软件还是会提示你是否要upgrade当前设计文件。

这个是平时我们一直看到过的,怎么样才能去掉这个对话框,不要upgrade当前设计呢?请继续往下看。

点击取消按钮后,打开安装文件夹下面的share\cdssetup\smi\orcap\orCapture.xml 在xml文档里面查1646,将其中的I (information) 改成W (Warning),如下图保存,然后重新打开刚才的design,你会发现如下对话框,这时候软件自动会在同一目录下产生一个老版本的备份文档,以便用旧版本打开。

二,Capture – Design SaveAs我们知道在平时我们做完设计后copy给别人用来查看,修改等是比较方便的,我们只需copy一个dsn 文件给对方即可。

对方打开后会自动产生project,同时设计里面的所有library在design cache里面也都有。

那么当我们的设计用用到很多等级的层次原理图的时候,将变得不再简单。

我们要copy母图,子图等,很容易忘掉相关文件而design不完整。

16.6的save as解决了这一问题。

Cadence软件学习:绘制原理图

Cadence软件学习:绘制原理图基本操作:1、 Place Part(P):放置元件2、 Place wire(W):连接相连的pin脚3、 Place Auto wire:自动连线4、 Place bus(B):总线连接5、 Place junction(J):交叉点连接,两条wire相交有两种连接关系:连或不连,加J为连6、Place bus entry(E):可以理解为总线入口,有bus必有entry7、 Place net alias(N):相当于wire,用于连接距离远的Pin 脚,仅限于同一page电气连接8、 Place power(F):放置电源9、 Place ground(G):放置地10、 Place off-page connector:类似alias,但alias仅用于同一页面,而off-page用于不同页面之间的电气连接11、Place no connect(X):用于无电气连接的pin脚,不放会报错12、 Place text(T):放置文本常用操作:1、按住Ctrl滚动鼠标滚轮放大缩小原理图(以鼠标指针为中心);直接滚动鼠标滚轮上下移动;按住Shift滚动左右移动2、改变原理图尺寸大小:options->Schematic Page Properties->Page Size3、旋转器件:放置器件前直接按R可旋转,放置后选中按R旋转4、选中单个或者多个器件,按住Ctrl,鼠标左键在选择器件上按住拖动可复制所选器件5、连线时改变连线角度需先按shift键6、元件镜像:选定后V键(垂直)和H键(水平)7、鼠标右键选End mode结束当前操作8、连线时,终点如不是管脚脚,双击结束9、管脚之间不要直接相连,通过线连接以防出错(软件设置不允许连接的方法:Options/Preferences->Miscellaneous->Wire Drag 打钩去掉)10、总线命名规则:后期处理:1、浏览原理图:选中 .dsn , edit->browse可以浏览parts、nets等,主要检查是否有漏掉的信息,双击可以打开原理图并高亮显示所选内容2、元件替换和更新:右键需要修改的元件,选择Replace cache 或Update CacheReplace cache:用于替换Update Cache:用于更新1、 Cleanup Cache:右键Design Cache选择Cleanup Cache 用于检测Design Cache与原理图是否一致,并删除多余的内容2、移动:默认连线与移动元件一同移动,按住Alt 移动仅元件移动3、自动编号:右键.dsn 选Annotate 。

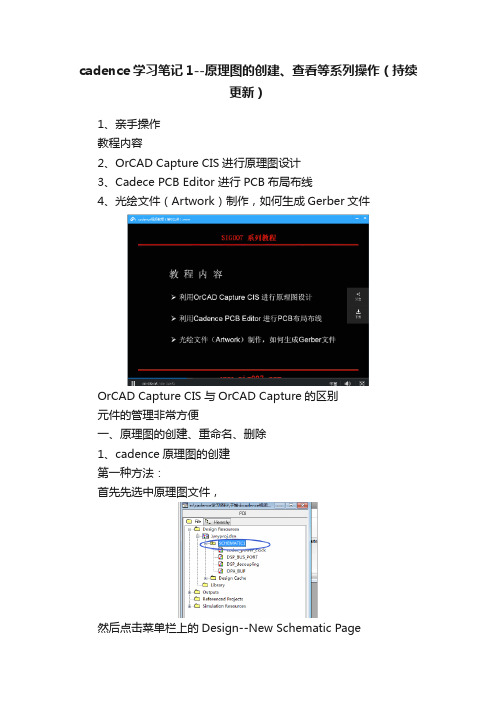

cadence学习笔记1--原理图的创建、查看等系列操作(持续更新)

1、亲手操作教程内容2、OrCAD Capture CIS进行原理图设计3、Cadece PCB Editor 进行PCB布局布线4、光绘文件(Artwork)制作,如何生成Gerber文件OrCAD Capture CIS与OrCAD Capture的区别元件的管理非常方便一、原理图的创建、重命名、删除1、cadence原理图的创建第一种方法:首先先选中原理图文件,然后点击菜单栏上的Design--New Schematic Page输入原理图名称第二种方法:先选中原理图文件,然后右键单击,选择New Page输入原理图名称2、删除原理图文件第一种方法:首先选择你要删除的原理图文件,然后点击菜单栏上的Edit---Delete,点击Delete之后,就会弹出下面的对话框。

点击确定之后,原理图2就删除了。

第二种方法:首先选择你要删除的原理图文件,然后鼠标右键点击Delete,如下图所示弹出如下所示,点击确定,原理图即删除。

3、cadence原理图的重命名第一种方法:选择需要更改原理图文件名的文件,然后点击菜单栏中的Design---Rename在弹出的对话框中,输入名称,点击OK即可。

第二种方法:选择需要更改原理图文件名的文件,然后右键点击Rename弹出对话框,在弹出的对话框中,输入名称,点击OK即可。

二、原理图的放大、缩小方法一: 直接按下快捷---i /o方法二:选择需要放大、缩小的原理图,然后选择菜单栏上的View---Zoom----In 放大Out 缩小方法三:按住键盘上的CTRL键,鼠标上的滑轮,向前滑动,原理图放大;向后滑动,原理图缩小。

如果原理图放的很大,可以移动滚动条进行原理图的上下左右的滚动。

也可以利用快捷键进行滚动条的移动,按住CTRL+PAGEUP,原理图向左移动;按住CTRL+PAGEDOWN,原理图向右移动;按住PAGEUP,原理图向上移动;按住PAGEDOWN,原理图向下移动。

cadence学习笔记1--原理图的创建、查看等系列操作(持续更新)

cadence学习笔记1--原理图的创建、查看等系列操作(持续更新)1、亲手操作教程内容2、OrCAD Capture CIS进行原理图设计3、Cadece PCB Editor 进行PCB布局布线4、光绘文件(Artwork)制作,如何生成Gerber文件OrCAD Capture CIS与OrCAD Capture的区别元件的管理非常方便一、原理图的创建、重命名、删除1、cadence原理图的创建第一种方法:首先先选中原理图文件,然后点击菜单栏上的Design--New Schematic Page输入原理图名称第二种方法:先选中原理图文件,然后右键单击,选择New Page输入原理图名称2、删除原理图文件第一种方法:首先选择你要删除的原理图文件,然后点击菜单栏上的Edit---Delete,点击Delete之后,就会弹出下面的对话框。

点击确定之后,原理图2就删除了。

第二种方法:首先选择你要删除的原理图文件,然后鼠标右键点击Delete,如下图所示弹出如下所示,点击确定,原理图即删除。

3、cadence原理图的重命名第一种方法:选择需要更改原理图文件名的文件,然后点击菜单栏中的Design---Rename在弹出的对话框中,输入名称,点击OK即可。

第二种方法:选择需要更改原理图文件名的文件,然后右键点击Rename弹出对话框,在弹出的对话框中,输入名称,点击OK即可。

二、原理图的放大、缩小方法一: 直接按下快捷---i /o方法二:选择需要放大、缩小的原理图,然后选择菜单栏上的View---Zoom----In 放大Out 缩小方法三:按住键盘上的CTRL键,鼠标上的滑轮,向前滑动,原理图放大;向后滑动,原理图缩小。

如果原理图放的很大,可以移动滚动条进行原理图的上下左右的滚动。

也可以利用快捷键进行滚动条的移动,按住CTRL+PAGEUP,原理图向左移动;按住CTRL+PAGEDOWN,原理图向右移动;按住PAGEUP,原理图向上移动;按住PAGEDOWN,原理图向下移动。

CADENCE学习笔记6

CADENCE学习笔记11后仿真布线完成后的仿真。

1在元件厂家网站所搜IBIS模型文件2打开Model Integrity,选择File-Open打开IBIS文件,经常出现如下非单调的错误,一般忽略。

Pulldown Minimum data is non-monotonic3在physical view,单击最顶部的元件-右键,选择IBIS to DML,实现IBIS到DML的转化,将.dml文件拷贝到PCB工程目录下4打开PCB SI,打开PCB文件,Analyze-PDN Analysis,一次执行以下四项:1)Identify DC Nets:给电源网络赋予电压值。

设置好之后点击Apply,再点击OK2)Cross section,设置板层结构3)DML manage Library:管理dml模型库,其中devices.dml和interconn.iml是默认的。

将新的模型库放在工程目录下,默认能够识别到。

4)model assignment仅设置用到的元件即可,用不到的不用指定模型。

Create model适用于阻容类,find model为元件指定dml模型,auto setup自动为元件添加系统默认的模型;单击REFDESPINS:不仅可以为元件指定模型,还可以对元件的每个引脚指定模型。

使用find model为元件或引脚指定dml模型5在约束管理器中选中一个net-右键-sigxplorer1)Analyze-preferences,设置switching frequency,Measurement Cycle指的是仿真几个信号周期;Switching Frequency指的是仿真方波的周期;Duty Cycle指的是占空比;Offset指的是偏移时间。

2)在sigxplorer窗口,可以看到NET的网络拓扑,其中的TL是微带线,阻值是特征阻抗,T1是T型连接点,该拓扑可以修改,单击走线可以删除走线,从元件引脚可以直接拖拉添加走线,可以添加元件等。

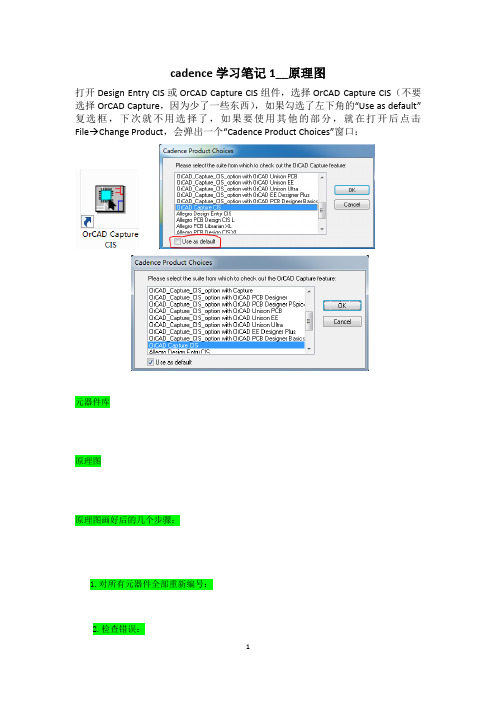

Cadence学习笔记1__原理图

cadence学习笔记1__原理图打开Design Entry CIS或OrCAD Capture CIS组件,选择OrCAD Capture CIS(不要选择OrCAD Capture,因为少了一些东西),如果勾选了左下角的“Use as default”复选框,下次就不用选择了,如果要使用其他的部分,就在打开后点击File→Change Product,会弹出一个“Cadence Product Choices”窗口:元器件库File→New→Library新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是New Part From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCB Footprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

中间的虚线框是这个元件的区域,右边会有一个工具栏,画直线、方框、圆、曲线,也可以输入一些字符,或者点放置一组引脚,放置结束后鼠标右击选择End Mode或按键盘左上角Esc键使命令结束,放置一组引脚的时候,还可以设置引脚的类型,比如输入、输出、双向、电源等等,这个没有区分电源和地,电源和地都是power型的,现在输入下面的几个数字,线型都是默认的Passive,引脚间距Pin Spacing设为1,点击ok,放置好后成为下面的样子,有些部分不需要显示,双击空白处弹出一个属性对话框,虚框里面的数字是PinName,虚框外面的数字是PinNumber,如果可视属性改成False就不显示了。

如果想改变其中一个引脚的引脚名、引脚编号、引脚类型,选中该引脚,右击选择Edit Properties,或者双击该引脚,如下图:画直线的时候,这里默认是按照栅格点为最小单位的,可以改变这种限制,画出任意长度任意角度的线,在工具栏Options Grid Display中,不要勾选Pointer snap to grid就可以了,记得画完想要的任意直线后,再将这里勾选,这是一个好习惯,可以让画出的线更规则整齐。

Cadence绘制PCB流程

Cadence绘制PCB流程使用软件版本号:Cadence 16.6一、SCH原理图设计1.1原理图设计1.2标注、DRC电气规则检测1.3网络表netlist生成 (设置元件封装)二、PCB绘制2.1零件库开发零件库开发包括:1、创建焊盘 2、创建零件封装2.1.1 pad结构和零件文件类型在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。

元件封装大体上分两种,表贴和直插。

针对不同的封装,需要制作不同的Padstack。

首先介绍Pad焊盘的结构,详见下图:pad焊盘结构1. Regular Pad,规则焊盘。

● Circle 圆型● Square 正方型● Oblong 拉长圆型● Rectangle 矩型● Octagon 八边型● Shape形状(可以是任意形状)。

2. Thermal relief,热风焊盘。

● Null(没有)● Circle 圆型● Square 方型● Oblong 拉长圆型● Rectangle 矩型● Octagon 八边型● flash形状(可以是任意形状)。

3. Anti pad,隔离PAD。

起一个绝缘的作用,使焊盘和该层铜之间形成一个电气隔离,同时在电路板中证明一下焊盘所占的电气空间。

● Null(没有)● Circle 圆型● Square 方型● Oblong 拉长圆型● Rectangle 矩型● Octagon 八边型● Shape形状(可以是任意形状)。

4. SOLDERMASK:阻焊层,作用:为了避免相邻铜箔导线短路和减缓铜箔氧化,在PCB板覆盖绿油解决问题。

如果将绿油覆盖待焊盘上,则焊盘无法焊接。

所以提出阻焊层概念,即在覆盖绿油位置 为焊盘开个窗口,使绿油不覆盖窗口(该窗口的大小必须大于焊盘尺寸)。

可以理解成去阻焊层(即使用模具上绿油时,将焊盘位置遮挡,其他位置上绿油)(1)负片时,Allegro使用Thermal Relief和Anti-Pad;(VCC和GND层)(2)正片时,Allegro使用Regular Pad。

学习笔记-candence16.6-原理图部分

学习笔记目录一、原理图设计部分1.针对原理图界面的操作2.对原理图进行编辑3.对制作原件的编辑4.生成网表5.生成清单和打印设置针对原理图界面的操作Design entry CIS:进行板级设计时用来画原理图的。

PCB Editor:cadence进行布局布线的软件。

Cadence product choices-----OrCAD capture CIS进行原理图页面个性化设置(整体设置)Options-->design template..(即原理图页面模板). 进行原理图页面个性化设置(单页设置)Options-->schematic page propertise..5. .drn文件是建立的工程的数据库文件,包括电路原理图(schematic)、元件库(design cache)、输出文件(outputs)。

6.工具栏的显示、隐藏和自定义View-->toolbar7.更改原理图背景颜色Option-->Preferences..8.原理图的放大、缩小快捷键i、o。

View-->zoom-->in/out按住ctrl,滚动鼠标。

对原理图进行编辑旋转元器件:快捷键R画线:places -->wire快捷键W任意角度画线:画线时按住shift网络节点:junction删除网络节点:按住“s”键,鼠标左键单击节点,此时出现一个方框,这时按“delete”键,即可删除。

浏览命令browse整体浏览:选中.drn文件Edit-->browse-->parts/nets......点击原件标号可以直接定位到该原件。

对制作原件的编辑1.批量放置管脚:place--pin array2.批量修改管教:选中需要修改的管脚---右键---editproperties..3.查看元件的属性:options-->part propertise..Options-->edit part propertise..(可以改写footprint)相同的不同的4.查看一个package里的几个部分:View--packageView--package propertisesCtrl+B:package的上一级Ctrl+N:package的下一级5.画线时任意起点和终点画线:options--->prefences..-->grid display---取消pointer snap to grid6.按组编号:Tool-->annotate..四、生成网表Netlist---PCB Editor生成清单和打印设置TOOLS---Bill OF materials针对allegro原理图界面的操作allegro的5种应用模式(application mode)general edit 普通模式Placement edit 排零件模式。

cadence学习笔记-画原理图库

cadence学习笔记-画原理图库Candence 学习笔记龚昌盛2014.04.11⼀、使⽤OrCAD Capture CIS来画原理图1.基本操作1).使⽤OrCAD Capture CIS2).原理图的放⼤缩⼩:I、OCtrl + ⿏标,滚轮。

⿏标所在位置,它以⿏标所在的位置为中⼼进⾏放⼤和缩⼩。

3).原理图上下滚动,Page UP、Page Down4).原理图左右滚动,Ctrl + Page UP、Ctrl + Page Down2.简单设置在画原理图之前,进⾏简单设置,Options -> Design Template,⽤于原理图的模版设置。

3.创建⼯程⽂档1.修改背景颜⾊Options ->Preferences ->Colors/Print -> Background2.修改原理图⼤⼩、栅格、单位Options ->Schematic Page Properties⼆、使⽤OrCAD Capture CIS来画规则的元件库→创建库→创建元件→1.基本操作File ->New ->Library2.更换路径选中C:\Library1.olb,File -> Save As或右键Save As ,MyLib.OLB3.创建新元件选中MyLib.OLB,右键,New PartPart Reference Prefix,器件的索引Parts per Pkg:⼀个元器件分成多个⼩部分来画。

4.放引脚5.放引脚排6.批量修改引脚信息选择引脚后,右键,Edit ProportiesNC,可以选择SHOT属性。

7.放⽅形BODY8.调整引脚位置9.修改⽅形BODY⼤⼩10.保存11.熟悉元件属性Options →Part ProportiesOptions →Package ProportiesView → Package⽤于显⽰⼀个元件有多少个⼦部分。

Cadence学习笔记1__原理图

新建元件时选择Heterogeneous,A部分和上面的一样画法,但是按键盘上的ctrl+N切换到B部分时,B部分是空白的,需要再画一次。

不管是Homogeneous还是Heterogeneous,点击工具栏ViewPakage,可以将A和B同时显示出来,如下图:

保存后,一个元件就画好了,画原理图时直接调用即可。

如果是由两部分组成的分裂元件,要在新建元件时在Parts per Pkg写2,这里分为Homogeneous和Heterogeneous两种。Homogeneous是只要画出A部分,B部分会默认的和A部分完全一样,Heterogeneous是画好A部分后,B部分仍然是空白的,需要再画。如果一个芯片包含了2个功能完全相同的部分,像下图中NE5532中的两个运放,就需要用到Homogeneous了,这里先选Homogeneous,点击ok。

元器件

FileNewLibrary新建一个库,如下图,显示了路径和默认库名library1.olb,右击选择Save As可以改变路径和库名,右击新建一个元件,可以选择New Part或者是NewPart From Speadsheet,是两种不同的方式,先介绍New Part的操作。

右击选择New Part后,弹出下面的对话框,在Name中填入元件名,还可以指定PCBFootprint,下面Parts per Pkg表示这个元件有几部分,1表示普通的元件,如果元件是两部分组成的分裂元件就写2,这里先操作1,点击ok。

点击左侧工具栏make图标 ,所有的横线和竖线都变成粉红色的,这就生成了一个表格,鼠标右击选择Tag Pin Name,在引脚名这一列点一下,会在这一列最上面出现“Name”,同样的,右击选择TagPin Number,在引脚编号这一列点一下,会在这一列最上面出现“Num”,如果放错了,比如说该放Name的地方放成了Num,可以在放Num之后再点一次,Num就消失了,产生的结果如上图右。

cadence 原理图学习笔记

Design Entry CIS :板基设计的原理图设计Design Entry HDL Rules Checker 芯片设计工具Design Entry HDL 芯片设计工具PCB Editor:PCB布局布线的软件PCB Router:自动布线的工具PCB SI:线路板的完整性分析SigXplorer:线路板的完整性分析平时画原理图工具:OrCAD Capture CIS原理图模板设置:创建原理图元件库新建的原理库存储到指定的位置新建元件库元件新建元件的属性,包括名称,索引号,封装,多元件共体,等信息元件库原理图编辑界面单个引脚放置:弹出引脚属性设置阵列引脚放置:单个引脚双击修改属性多个引脚选中后在spreadsheet一起修改。

放置填充多边形按住shift可以画任意角多边形双击调出多边形属性选择实体就好了放置元件方体画方框结束鼠标重复放置命令,右击End Mode 或者Esc元件属性,设置引脚管脚显示等。

元件封装属性修改,原理图与pcb封装的映射就在这里修改。

多元件共体浏览分裂元件浏览。

不规则元件第3讲:分裂元件制作创建Homogereous双运放元件,每个单元件都一摸一样,引脚编号不同,电源脚编号可以重复。

新建元件画好第一个单元件快捷键Ctrl+n 自动生成另一部分单元件。

需要全部重新定义引脚编号。

引脚名称隐藏快捷键Ctrl+b 可以返回查看A部分元件图形。

创建Heterogeneous元件,每部分图形可以不一致。

快捷键Ctrl+n 会完全留空,全部要重新画。

分裂元件整体浏览第4讲分裂元件的自动编号的问题解决。

分裂元件的组定义,在元件库中操作,使同组元件具备同一属性。

第一步:创建元件第二步:给元件创建一个可以区分“分组”的属性完成了单个元件的新属性的创建依次创建同组的其它元件的新属性。

要求同名同参数第三步:在原理图中双击元件使同组的元件都新属性参数相同即可。

配对时不能冲突,比如双运放就只能有两个运放,同一参数有三个运放相同的话就出错了。

使用Cadence绘制PCB流程(个人小结)

使用Cadence绘制PCB流程(个人小结)之前使用过cadence画过几块板子,一直没有做过整理。

每次画图遇到问题时,都查阅操作方法。

现在整理一下cadence使用经历,将遇到问题写出来,避免重复犯错。

使用软件版本号:Cadence 16.6一、SCH原理图设计1.1原理图设计1.2标注、DRC电气规则检测1.3网络表netlist生成(设置元件封装)二、PCB绘制2.1零件库开发零件库开发包括:1、创建焊盘 2、创建零件封装2.1.1 pad结构和零件文件类型在Allegro系统中,建立一个零件(Symbol)之前,必须先建立零件的管脚(Pin)。

元件封装大体上分两种,表贴和直插。

针对不同的封装,需要制作不同的Padstack。

首先介绍Pad焊盘的结构,详见下图:pad焊盘结构1. Regular Pad,规则焊盘。

● Circle 圆型● Square 正方型● Oblong 拉长圆型● Rectangle 矩型● Octagon 八边型● Shape形状(可以是任意形状)。

2. Thermal relief,热风焊盘。

● Null(没有)● Circle 圆型● Square 方型● Oblong 拉长圆型● Rectangle 矩型● Octagon 八边型● flash形状(可以是任意形状)。

3. Anti pad,隔离PAD。

起一个绝缘的作用,使焊盘和该层铜之间形成一个电气隔离,同时在电路板中证明一下焊盘所占的电气空间。

● Null(没有)● Circle 圆型● Square 方型● Oblong 拉长圆型● Rectangle 矩型● Octagon 八边型● Shape形状(可以是任意形状)。

4. SOLDERMASK:阻焊层,作用:为了避免相邻铜箔导线短路和减缓铜箔氧化,在PCB板覆盖绿油解决问题。

如果将绿油覆盖待焊盘上,则焊盘无法焊接。

所以提出阻焊层概念,即在覆盖绿油位置为焊盘开个窗口,使绿油不覆盖窗口(该窗口的大小必须大于焊盘尺寸)。

Cadence16.5学习笔记之(一)—器件库、原理图

Cadence16.5学习笔记之(一)—器件库、原理图Cadence16.5学习笔记之(一)—器件库、原理图一、简单快捷键R—旋转器件方向(选中时)V—元件的镜像(水平)H—元件的镜像(竖直)F—放置电源G—放置地W—放置连线J—放置节点N—放置网络标号T—放置文本备注(Ctrl + Enter:换行)B—放置总线X—放置电器不连接F4—自动放置线,一直按一直放。

元件的复制:Ctrl + C或按住Ctrl,拖动元件即可。

放置全局网络标号(级联多个原理图):Place—Off-Page Connector放置线、总线时,任意角度走线—按住Shift键,再走线。

二、查找元件、网络连接等对整个工程、或单个的页面进行如下类似操作。

Edit->Browse->Parts:原理图画好了,选中工程,检查、查找定位器件Edit->Browse->Nets:网络连接,对于检查电源连接有帮助Edit->Browse->Off-Page Connector:显示工程中所有,原理图页面之间的网络连接(即归纳显示出所有全局网络标号)Edit->Browse->DRC Markers:DRC检查,显示出DRC电器检查的错误。

(删掉这些错误:Tools->Designe Rules Cheak->Yes->Action->Delete existing DRC marker->Yes)Ctrl + F:搜索定位元件、网络,如在PCB布局、布线时(勾选)。

以下类型选项:Parts:查找元件Nets:查看网络连接Power/GND:查看电源、地的网络连接Flat Nets:查看电源、地的网络连接(功能更强大)三、元件的更新或替换选择工程对话框中的File ->Design Cache->右键->Replace Cach->....->是否保留元件的遗留属性,可以将封装更新过来同样的操作,如果器件库中器件属性有改动,则更新元件(但不能将封装更新过来):File ->Design Cache->右键->Updata Cach四、选中元件1、单个选中、Ctrl + 选中元件、区域选中(整体移动),移动时电气连接是存在的,如果按住Alt再移动,则电气连接断开。

Cadence16.6教程——PCB篇

Cadence16.6教程——PCB篇PCB操作教程一、导入网表先从原理图导出网表Tools-CreateNetlist只导出网表需要不勾选Create orUpdate PCB Editor Board(Netrev)确认后,在原理图根目录下会生成一个allegro的文件夹,网表就保存在这个文件里。

网表导出后,打开PCB(建议把PCB文件放在allegro刚才生成的allegro文件夹里)File-Import-Logic在Cadence选项卡里Import logic type选Design entry CIS(Capture)Import directory选择网表的文件夹allegro的路径点Import Cadence后导入网表完成二、设置图纸大小Setup-Design Parameters...Display选项卡设置格点大小单击Display选项卡中Setup Grids后面的 ...建议在公制的时候把格点都设为0.1mm,英制的时候格点设为5mil。

不宜过大或过小。

Design选项卡中User Units:选Miles(英制)或Milimeter(公制)Size下其他选项默认即可Extents:LeftX和LeftY是指图纸左下角的坐标,建议用负值Width和Height是图纸大小如果PCB中有器件或其他东西,设置图纸时,需要大于器件的位置,不然会设置不了。

建议图纸大小约为板子大小的2~4倍左右,不宜过大。

三、设置层叠结构Setup-Cross-sectionSubclass Name是叠层的名称,Top和BOTTOM不能修改Type: CONDUCTOR 导电层(一般用于走线层)PLANE 平面层(一般用于电源和地层)两层中间都是DIELECTRICMaterial: AIR 空气COPPER 铜FR-4 玻璃布基板Thickness:厚度(可以不修改)添加或删除叠层,在想添加或删除的叠层上右键Add Layer Above 添加在此叠层的上面Add Layer Below 添加在此叠层的下面Remove Layer 删除此叠层添加叠层后需要把Type和Material设置好设置好后点OK,在Visibility里会显示出来新添加或删除的CONDUCTOR或PLANE层注意:板子的叠层为偶数,不能出现单数叠层,板厂无法制作。

学习笔记-candence16.6-原理图部分

Candence16.6学习笔记目录一、原理图设计部分1.针对原理图界面的操作2.对原理图进行编辑3.对制作原件的编辑4.生成网表5.生成清单和打印设置一、针对原理图界面的操作1.Design entry CIS:进行板级设计时用来画原理图的。

2.PCB Editor:cadence进行布局布线的软件。

3.Cadence product choices-----OrCAD capture CIS4.进行原理图页面个性化设置(整体设置)Options-->design template..(即原理图页面模板)4.1. 进行原理图页面个性化设置(单页设置)Options-->schematic page propertise..5. .drn文件是建立的工程的数据库文件,包括电路原理图(schematic)、元件库(design cache)、输出文件(outputs)。

6.工具栏的显示、隐藏和自定义View-->toolbar7.更改原理图背景颜色Option-->Preferences..8.原理图的放大、缩小①快捷键i、o。

②View-->zoom-->in/out③按住ctrl,滚动鼠标。

二、对原理图进行编辑1.旋转元器件:快捷键R2.画线:places -->wire快捷键W3.任意角度画线:画线时按住shift4.网络节点:junction5.删除网络节点:按住“s”键,鼠标左键单击节点,此时出现一个方框,这时按“delete”键,即可删除。

6.浏览命令 browse整体浏览:选中.drn文件 Edit-->browse-->parts/nets...... 点击原件标号可以直接定位到该原件。

三、对制作原件的编辑1.批量放置管脚:place--pin array2.批量修改管教:选中需要修改的管脚---右键---editproperties..3.查看元件的属性:options-->part propertise..Options-->edit part propertise..(可以改写footprint)相同的不同的4.查看一个package里的几个部分:View--packageView--package propertisesCtrl+B:package的上一级Ctrl+N:package的下一级5.画线时任意起点和终点画线:options--->prefences..-->grid display---取消pointer snap to grid6.按组编号:Tool-->annotate..四、生成网表1.Tools---creat Netlist---PCB Editor生成清单和打印设置TOOLS---Bill OF materials1.针对allegro原理图界面的操作1)allegro的5种应用模式(application mode)1.general edit 普通模式2.Placement edit 排零件模式。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Candence16.6学习笔记目录

一、原理图设计部分

1.针对原理图界面的操作

2.对原理图进行编辑

3.对制作原件的编辑

4.生成网表

5.生成清单和打印设置

一、针对原理图界面的操作

1.Design entry CIS: 进行板级设计时用来画原理图的。

2.PCB Editor:cadence 进行布局布线的软件。

3.Cadence product choices-----OrCAD capture CIS

4.进行原理图页面个性化设置(整体设置)

Options-->design template.. (即原理图页面模板)

4.1. 进行原理图页面个性化设置(单页设置)

Options-->schematic page propertise..

5. .drn 文件是建立的工程的数据库文件,包括电路原理图(schematic)、元件库(design cache)、输出文件(outputs)。

6.工具栏的显示、隐藏和自定义

View-->toolbar

7.更改原理图背景颜色

Option-->Preferences..

8.原理图的放大、缩小

①快捷键i、o。

②View-->zoom-->in/out

③按住ctrl ,滚动鼠标。

二、对原理图进行编辑

1.旋转元器件:快捷键R

2.画线:places -->wire

快捷键W

3.任意角度画线:画线时按住shift

4.网络节点:junction

5.删除网络节点:按住“s”键,鼠标左键单击节点,此时出

现一个方框,这时按“delete”键,即可删除。

6. 浏览命令browse

整体浏览:选中.drn 文件Edit-->browse-->parts/nets......

点击原件标号可以直接定位到该原件。

三、对制作原件的编辑

1.批量放置管脚:place--pin array

2. 批量修改管教:选中需要修改的管脚--- 右键---edit

properties..

3.查看元件的属性:options-->part propertise..

Options-->edit part propertise..( 可以改写footprint)

相同的

不同的

4.查看一个package 里的几个部分:View--package

View--package propertises

Ctrl+B:package 的上一级

Ctrl+N:package 的下一级

5.画线时任意起点和终点画线:options--->prefences..-->grid display--- 取消pointer snap to grid

6.按组编号:Tool-->annotate..

1.Tools---creat Netlist---PCB Editor

TOOLS---Bill OF materials

1.针对allegro 原理图界面的操作

1)allegro 的5 种应用模式(application mode)

1.general edit 普通模式

2.Placement edit 排零件模式。

主要用于placement

3.etch edit 走线模式。

主要用于routing

4.Ifp ( 即flow planning)

5.Signalintegrity

另外,右键--application mode, 也可进行应用模式的切换;另外,setup--application mode, 也可进行应用模式的切换。

2)切换平台

File--change editor...

3)脚本

File--script...( 没用过,不知道干嘛的)。