LCD1621(屏驱动)

LCD驱动芯片TM1621D『官方最新规格书』

80

150

5V VOL=0.5V

150

250

IOH2 LCD 公共口源电流 3V VOH=2.7V

-80

-120

5V VOH=4.5V

-120

-200

IOL3 LCD 段管脚漏电流 3V VOL=0.3V

60

120

5V VOL=0.5V

120

200

IOH3 LCD 段管脚源电流 3V VOH=2.7V

-40

-70

5V VOH=4.5V

-70

-100

RPH 上拉电阻

3V DATA,/WR, 40

80

5V /CS

30

60

TM1621D

3.0

V

5.0

V

mA

mA

mA

mA uA uA

uA uA

uA uA

uA

uA

150

Kohm

100

Kohm

交流电气特性

符号

描述

fSYS1

系统时钟

fSYS2 fSYS3 fLCD

BIAS 1/3

TOPT TNORMAL 注: X:0或1;

101

D

写数据到RAM

a5a4a3a2a1a0d0d1d2d3

10000000000X

C

关闭系统振荡器和LCD 偏压

发生器

10000000001X

C

打开系统振荡器

10000000010X

C

关闭LCD 偏压发生器

10000000011X

C

打开LCD 偏压发生器

I 负电源、地 I LCD 电源输入 I 正电源 O LCD 公共输出口

用HT1621驱动LCD的方法

用HT1621驱动LCD的方法HT1621是一种专门用于驱动液晶显示屏的电路芯片。

它主要由一个128x32位的RAM、一个系统控制单元、一个液晶电压驱动器和一个驱动信号产生器组成。

下面将详细介绍如何使用HT1621来驱动液晶显示屏。

首先,我们需要了解HT1621的引脚和功能。

HT1621具有36个I/O引脚,其中包括数据线D0-D15、片选线CS、读/写线WR、串行时钟线CLK、复位线RESET和外部时钟线CLOCK。

可以通过这些引脚来与HT1621进行通信和控制。

接下来,我们需要了解液晶显示屏的工作原理。

一般来说,液晶屏主要由一个像素矩阵和一个驱动电路组成。

驱动电路负责根据控制信号来控制像素的亮度。

液晶显示屏的像素矩阵可以根据需要进行修改,以显示所需的图形或文本。

基于以上原理,我们可以开始使用HT1621来驱动液晶显示屏。

以下是一个基本的步骤:1.连接电路:首先,将HT1621和液晶显示屏连接起来。

根据液晶显示屏的引脚分配表和HT1621的引脚分配表,进行正确的连接。

确保电路在工作时不会发生短路或其他问题。

2.初始化HT1621:在开始使用HT1621之前,需要执行一些初始化操作。

这包括设置像素矩阵的大小、选择使用的驱动模式(静态或动态)以及配置其他相关参数。

可以通过向HT1621发送一系列特定的配置命令来完成这些初始化操作。

3.发送数据:一旦HT1621完成初始化,就可以开始向液晶显示屏发送数据了。

可以通过编程将所需的图形或文本数据写入HT1621的RAM中。

注意,HT1621的RAM大小为128x32位,所以需要将图形或文本数据适当地分割和映射到RAM中的相应位置。

4.刷新液晶显示屏:一旦数据写入HT1621的RAM中,需要根据需要刷新液晶显示屏以显示所需的图形或文本。

可以通过向HT1621发送刷新命令来触发刷新操作。

HT1621将读取RAM中的数据并根据驱动电路的要求控制液晶显示屏中的像素亮度。

AIP1621 TM1621中微爱芯LCD显示驱动芯片

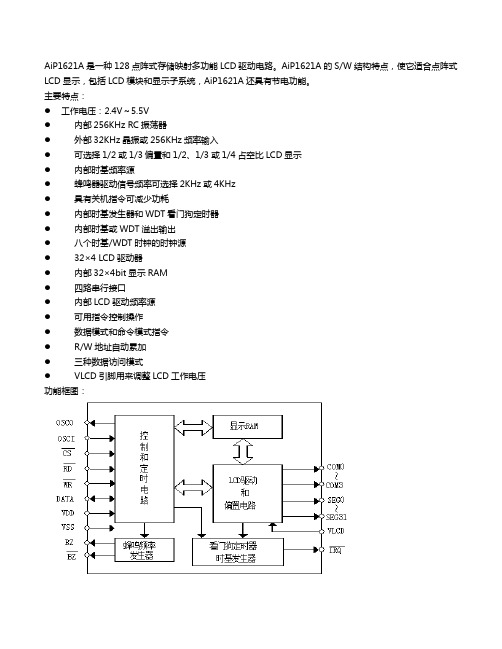

AiP1621A是一种128点阵式存储映射多功能LCD驱动电路。

AiP1621A的S/W结构特点,使它适合点阵式LCD显示,包括LCD模块和显示子系统,AiP1621A还具有节电功能。

主要特点:●工作电压:2.4V~5.5V●内部256KHz RC振荡器●外部32KHz晶振或256KHz频率输入●可选择1/2或1/3偏置和1/2、1/3或1/4占空比LCD显示●内部时基频率源●蜂鸣器驱动信号频率可选择2KHz或4KHz●具有关机指令可减少功耗●内部时基发生器和WDT看门狗定时器●内部时基或WDT溢出输出●八个时基/WDT时钟的时钟源●32×4 LCD驱动器●内部32×4bit显示RAM●四路串行接口●内部LCD驱动频率源●可用指令控制操作●数据模式和命令模式指令●R/W地址自动累加●三种数据访问模式●VLCD引脚用来调整LCD工作电压功能框图:注::芯片选择 BZ,:蜂鸣器输出,,DATA:串行接口COM0~COM3,SEG0~SEG31:LCD输出:时间基准或WDT溢出输出引脚排列图:应用线路概述TM1621是内存映象和多功能的LCD驱动器,TM1621的软件配置特性使它适用于多种LCD应用场合,包括LCD模块和显示子系统。

用于连接主控制器和TM1621的管脚只有4或5条,TM1621还有一个节电命令用于降低系统功耗。

功能特性工作电压2.4~ 5.2V内嵌256KHz RC 振荡器可外接32KHz晶片或256KHz频率源输入可选1/2或1/3偏压和1/2、1/3或1/4的占空比片内时基频率源蜂鸣器可选择两种频率节电命令可用于减少功耗内嵌时基发生器和看门狗定时器(WDT)时基或看门狗定时器溢出输出八个时基/看门狗定时器时钟源一个32x4的LCD 驱动器一个内嵌的32x4位显示RAM 内存四线串行接口片内LCD驱动频率源软件配置特征数据模式和命令模式指令三种数据访问模式提供VLCD管脚用于调整LCD操作电压封装形式:SSOP48、LQFP44结构图/CS 为片选信号线BZ,/BZ 声音输出/WR,/RD,DATA:串行接口COM0~COM3,SEG0~SEG31:LCD 输出/IRQ:时基或WDT溢出输出管脚图:TM1621_SSOP482管脚功能定义:3供应电压: -0.3V~0.5V 贮存温度:-50~125度输入电压: VSS-0.3V~VDD+0.3V 工作温度:-25~75度直流电气参数4交流电气特性:5应用图:主控制器与TM1621组成显示系统,参见下图注意: 1、VLCD的电压必须低于VDD电压;2、VR电阻用于调节VLCD输出电压,当VDD=5V,VLCD=4V,VR=15KΩ+20%3、R为外部上拉电阻,上拉到VDD,R=10KΩ+20%4、C1、C2 为外部晶振电容,建议值如下:晶振误差电容值(C1、C2)+10ppm 0~10p10~20ppm 10~20p系统结构:1、显示内存(RAM)静态显示内存(RAM)以32x4位的格式储存所显示的数据。

AIP1621TM1621中微爱芯LCD显示驱动芯片

AIP1621TM1621中微爱芯LCD显示驱动芯片AiP1621A是一种128点阵式存储映射多功能LCD驱动电路。

AiP1621A的S/W结构特点,使它适合点阵式LCD显示,包括LCD 模块和显示子系统,AiP1621A还具有节电功能。

主要特点:●工作电压:2.4V~5.5V●内部256KHz RC振荡器●外部32KHz晶振或256KHz频率输入●可选择1/2或1/3偏置和1/2、1/3或1/4占空比LCD显示●内部时基频率源●蜂鸣器驱动信号频率可选择2KHz或4KHz●具有关机指令可减少功耗●内部时基发生器和WDT看门狗定时器●内部时基或WDT溢出输出●八个时基/WDT时钟的时钟源●32×4 LCD驱动器●内部32×4bit显示RAM●四路串行接口●内部LCD驱动频率源●可用指令控制操作●数据模式和命令模式指令●R/W地址自动累加●三种数据访问模式●VLCD引脚用来调整LCD工作电压功能框图:注::芯片选择 BZ,:蜂鸣器输出,,DATA:串行接口COM0~COM3,SEG0~SEG31:LCD输出:时间基准或WDT溢出输出引脚排列图:应用线路概述TM1621是内存映象和多功能的LCD驱动器,TM1621的软件配置特性使它适用于多种LCD应用场合,包括LCD模块和显示子系统。

用于连接主控制器和TM1621的管脚只有4或5条,TM1621还有一个节电命令用于降低系统功耗。

功能特性工作电压2.4~ 5.2V内嵌256KHz RC 振荡器可外接32KHz晶片或256KHz频率源输入可选1/2或1/3偏压和1/2、1/3或1/4的占空比片内时基频率源蜂鸣器可选择两种频率节电命令可用于减少功耗内嵌时基发生器和看门狗定时器(WDT)时基或看门狗定时器溢出输出八个时基/看门狗定时器时钟源一个32x4的LCD 驱动器一个内嵌的32x4位显示RAM 内存四线串行接口片内LCD驱动频率源软件配置特征数据模式和命令模式指令三种数据访问模式提供VLCD管脚用于调整LCD操作电压封装形式:SSOP48、LQFP44结构图/CS 为片选信号线BZ,/BZ 声音输出/WR,/RD,DATA:串行接口COM0~COM3,SEG0~SEG31:LCD 输出/IRQ:时基或WDT溢出输出管脚图:TM1621_SSOP48管脚功能定义:3供应电压: -0.3V~0.5V 贮存温度:-50~125度输入电压: VSS-0.3V~VDD+0.3V 工作温度:-25~75度直流电气参数4交流电气特性:5应用图:主控制器与TM1621组成显示系统,参见下图注意: 1、VLCD的电压必须低于VDD电压;2、VR电阻用于调节VLCD输出电压,当VDD=5V,VLCD=4V,VR=15KΩ+20%3、R为外部上拉电阻,上拉到VDD,R=10KΩ+20%4、C1、C2 为外部晶振电容,建议值如下:晶振误差电容值(C1、C2)+10ppm 0~10p10~20ppm 10~20p系统结构:1、显示内存(RAM)静态显示内存(RAM)以32x4位的格式储存所显示的数据。

1621

CS1621RAM映射32×4点阵式液晶显示驱动电路概述CS1621是一种128点阵式存储器映射多功能LCD驱动电路CS1621的S/W 结构特点使它适合点阵式LCD 显示包括LCD 模块和显示子系统CS1621具有关闭电源功能功能特点工作电压 2.4V 5.2V内部256kHz RC振荡器外部32kHz晶振或256kHz频率输入可选择1/2或1/3偏置和1/21/3或1/4占空比LCD显示内部时间基准频率蜂鸣器驱动信号频率可选择2kHz或4kHz 具有关机指令可减少功耗内部时基发生器和WDT看门狗定时器时基或WDT溢出输出时基/WDT时钟源有八种32×4 LCD驱动器内部32×4 bit显示RAM 3端串行接口内置LCD驱动信号源可用指令控制操作数据模式和命令模式指令R/W地址自动累加3种数据存取模式VLCD引脚用来调整LCD工作电压采用封装形式SSOP48CS1621GO CS1621BGO PDIP48CS1621BGP SKDIP28CS1621DGPLQFP44CS1621CGN片选信号输入端为逻辑高电平时数据和命令不能读出和写入并且串行接口电路复位但当CS1621之间可以传输数据和命令时钟输入端带上拉电阻RAM DATA 线上主控制器可以在下一个上升沿锁存这个时钟输入在DATA 上的数据被锁存到CS1621带上拉电阻VSS - GND OSCI I 和OSCO 晶振如果使用片内可以悬空VLCD I LCD BZ COM0输出端CS 芯片选择BZ BZ 蜂鸣器输出WR RD DATA 串行接口COM0COM3SEG0SEG31LCD 输出IRQ 时间基准或WDT 溢出输出功能说明1.工作原理CS1621是一种具有微控制器接口由存储器映射的324点阵式LCD 控制驱动器电路上电时清零复位通过命令端进行工作状态设置通过片选读写端对RAM 数据进行读写修改操作按照一一对应的原则驱动LCD 显示器该电路可用于点阵式LCD 显示驱动各SEG 端是互相独立的且容易对RAM 数据进行修改所以显示点阵内容灵活可随用户任意定制 2.系统结构1RAM 静态显示存储器RAM 结构为324位贮存所显示的数据RAM 的内容直接映射成LCD 驱动器的内容RAM 中的数据可被READ WRITE 和READ MODIFY WRITE2系统振荡器CS1621系统时钟用来产生时基/WDT 电路的时钟LCD 驱动时钟和蜂鸣频率时钟可以来自片内RC振荡器256kHz 晶体振荡器32.768kHz 或由S/W 设置的外部256kHz 的时钟系统振荡器结构如图执行SYS DIS 命令后系统时钟停止LCD 偏置发生器也停止工作此命令只适用于片内RC 振荡器256kHz 和晶体振荡器一旦系统时钟停止LCD 显示变暗时基/WDT 将失去功能LCD OFF 命令用来关闭LCD 偏置发生器LCD OFF 命令关闭LCD 偏置发生器后用SYS DIS 命令减少功耗相当于系统POWER DOWN 命令但当外部时钟用作系统时钟时SYS DIS 命令既不能关闭振荡器也不能进入POWER DOWN 模式晶体振荡器可用来连接一个32kHz 外部频率源到OSCI 管脚因此系统进入POWER DOWN 模式有点状态3时间基准和看门狗定时器时基发生器是由8级递增计数器构成用来设计产生一个精确的时间基准看门狗定时器WDT 由8级时基发生器和一个2级递增计数器组成在非正常状态下未知的或不希望发生的跳转执行错误等用来停止主控制器或其它子系统WDT 暂停将设置一个WDT 暂停标志时基发生器的输出和WDT 暂停标志的输出可以用命令输出到IRQ 的输出端总共有8个频率源适合时基发生器和WDT 时钟其频率由下列公式得出nWDT 2kHz32f =n 的值通过命令在07之间变化等式中的32kHz 表明系统时钟由一个32.768kHz 的晶体振荡器一个片内振荡器256kHz 或外部256kHz 频率驱动如果一个片内振荡器256kHz 或外部256KHz 频率作为系统时钟系统时钟被一个3级分频器预置成32kHz 由于时基发生器和WDT 使用同一个8级计数器因此需小心使用与时基发生器和WDT 相关的命令例如调用WDT DIS 命令对时基发生器无效而WDT EN 不但适用于时基发生器而且可以激活WDT 暂停标志输出WDT 暂停标志连接到IRQ脚输入TIMER EN 命令后WDT 和IRQ 脚断开时基发生器的内容由CLR WDT 或CLR TIMER 命令清零CLR WDT 或CLR TIMER 命令分别相应的在WDT EN 或TIMER EN 命令之前执行CLR TIMER 命令必须在WDT 模式转换到时基模式之前执行一旦出现WDT 暂停模式IRQ 脚将处于逻辑低电平直到出现CLR WDT 或IRQ DIS 命令IRQ 输出无效后IRQ 脚将处于悬浮状态通过执行IRQ EN 或IRQ DIS 命令使IRQ 输出处于有效或无效状态IRQ EN 使得时基发生器或WDT 暂停标志的输出作用到IRQ 脚DOWN 模式减少功耗在POWER DOWN 模式下时基/WDT 的一切功能都无效另一方面如果使用外部时钟作为系统频率SYS DIS 命令不起作用而不执行POWER DPWN 模式那就是说CS1621将一直运行到系统失效或外部时钟取消系统开启后IRQ 被禁用 4蜂鸣输出在CS1621中提供了一个简单的蜂鸣振荡器蜂鸣振荡器可提供一对蜂鸣驱动信号BZ 和BZ 用来产生一个简单的蜂鸣执行TONE4K 和TONE2K 命令可产生两种蜂鸣频率TONE4K 和TONE2K 命令设置蜂鸣频率分别为4kHz 和2kHz 蜂鸣驱动信号可以调用TONE ON 或TONE OFF 命令来开启或关闭BZ 和BZ 是一对反相驱动输出用来驱动压电蜂鸣器一旦系统失效或蜂鸣输出停止BZ 和BZ 输出处于低电平 5LCD 驱动器CS1621是一个128324点阵式LCD 驱动器它可以驱动1/2或1/3偏置23或4个COM 端的LCD 显示器这个特性使得CS1621适合于多种LCD 显示器LCD 驱动时钟产生于系统时钟不管系统时钟是来源于32.768kHz 晶振频率还是片内RC 振荡器频率或外部频率LCD 驱动时钟的频率总是256Hz 与LCD 相应命令见下表名 称 指 令 代 码 功 能LCD OFF 1 0 0 0 0 0 0 0 0 1 0 X 关闭LCD 输出 LCD ON 1 0 0 0 0 0 0 0 0 1 1 X 打开LCD 输出BIAS ﹠COM1 0 0 0 0 1 0 a b X c Xc =01/2偏置状态 c =11/3偏置状态 ab =002COM 端 ab =013COM 端 ab =104COM 端黑体形式的1 0 0表明是命令模式ID 如果发送连续命令命令模式ID 除第一个命令将被忽略LCD OFF 命令通过中断LCD 偏置发生器来关闭LCD 显示而LCD ON 命令通过启动LCD 偏置发生器来开启LCD 显示BIAS 和COM 命令是与LCD 显示器相关的命令通过该命令CS1621可驱动许多类型的LCD 显示器 6指令格式CS1621可以通过S/W 来设置设置CS1621和传送LCD 显示数据的指令共有两种模式分别为命令模式和数据模式对CS1621的设置称作命令模式其ID 是1 0 0由系统设置命令系统频率选择命令LCD 结构命令蜂鸣频率选择命令和操作命令组成数据模式包括READ WRITE 和READ MODIFY WRITE 操作下表是数据模式ID和命令模式ID操作模式ID READ 数据 1 1 0WRITEREAD MODIFY WRITE 数据数据1 0 11 0 1COMMAND 命令 1 0 0 模式命令出现在数据和命令传送之前如出现连续指令命令模式ID 1 0 0 可以被忽略当系统工作在不连续命令或不连续地址数据模式CS管脚应设置为1而之前的工作模式将被复位一旦CS管脚为0将出现一个新的工作模式ID7接口CS1621共有4线需要接口CS初始化串行接口电路和在主控制器和CS1621之间终接通信端CS为1时主控制器和CS1621之间数据和命令被禁止和初始化出现命令模式和模式转换之前需要一个高电平脉冲初始化CS1621的串行接口数据线是串行输入/输出线读写数据或写入命令必须通过数据线RD线是READ时钟输入RAM中的数据在RD信号的下降沿被读出读出数据将显示在DATA线上主控制器在READ信号上升沿和下一个下降沿之间读出正确数据WR线是WRITE时钟输入数据线上的数据地址命令在WR信号上升沿全被读到CS6121IRQ线被用作主控制器和CS1621之间的接口IRQ脚作为定时器输出或WDT溢出标志输出由S/W设定主控制器通过连接CS1621的IRQ脚执行时间基准或WDT功能8时序图000110LCD1/3000110蜂鸣频率4kHz2kHz输出时钟输出2Hz时钟输出4Hz时钟输出8Hz1/2s名 称ID命 令 代 码D/C功 能上电预 置复位F16 100 101X-X100-X C时基/WDT 时钟输出16HzWDT 暂停标志延时1/4s F32 100 101X-X101-X C时基/WDT 时钟输出32HzWDT 暂停标志延时1/8s F64 100 101X-X110-X C时基/WDT 时钟输出64HzWDT 暂停标志延时1/16s F128 100 101X-X111-X C时基/WDT 时钟输出128HzWDT 暂停标志延时1/32sYes TOPT 100 1110-0000-X C 测试模式 TNORMAL 100 1110-0011-X C 标准模式Yes注1. X 忽略2. A5A0RAM 地址3. D3D0RAM 数据4. D/C 数据/命令模式5. Def.上电预置复位6. 所有黑体即1 1 0, 1 0 1和 1 0 0均是摸式命令如出现连续命令命令模式ID 1 0 0 可以被忽略(除第一个命令ID 1 0 0 )7. 建议由主控制器在上电复位后对CS1621进行初始化否则若上电复位失败将导致CS1621误动作极限参数项目额定值单位电源电压-0.3 5.5 V输入电压V SS-0.3V DD+0.3 V储存温度-50125工作温度-2575电参数3V 0CS3V 2.4CSDATA BZDATA BZ3V 40COM3V 150串行数据时钟PIN蜂鸣器输出频率t串行数据到WR钟的建立时间图WR RD时钟的保持时间图RD时钟的建立时间RD时钟的保持时间1/2或1/3偏置1/21/31/4占空比注IRQ和RD引脚的连接视主控制器的要求而定VLCD引脚的电压必须低于V DD调节VR以适应LCD显示器V DD=5V V LCD=4V VR=15kΩ20%调节R外接上拉电阻以适应用户的基准时钟DD无锡华润矽科微电子有限公司江苏省无锡市梁溪路14号电话+865105810118-3321传真+865105810118-3560市场营销部电话+865105887467 传真+865105874503深圳办事处电话+867552057244传真+867552058144广州办事处电话+862086391906传真+862086391906注意本资料中的信息如有变化恕不另行通知本资料提供的应用线路仅供参考矽科不承担任何由此而引起的损失希望您经常和矽科有关部门进行联系索取最新资料因为矽科产品在不断更新和提高在使用矽科产品之前应仔细阅读本说明书严格遵照技术指标和技术参数进行设计和生产确保矽科产品应用于最新产品规范规定的工作范围内同时请谨记产品资料中提出的注意事项和工作环境矽科不承担任何在使用过程中引起的侵犯第三方专利或其它权力的责任矽科并未默许或以其它方式授予任何专利或权利。

LCD1621(屏驱动)

Pad No.

25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48

X

58.14 58.14 58.14 58.14 58.14 58.14 58.14 58.14 55.55 48.92 42.29 35.66 29.03 22.40 15.77 9.14 2.42 -4.21 -10.84 -17.47 -24.10 -30.73 -38.17 -45.39

1

48

2

47

3

46

4

45

5

44

6

43

7

42

8

41

9

40

10

39

11

38

12

37

13

36

14

35

15

34

16

33

17

32

18

31

19

30

20

29

21

28

22

27

23

26

24

25

H T1621 - 48 S S O P

SEG 8 SEG 9 S E G 10 S E G 11 S E G 12 S E G 13 S E G 14 S E G 15 S E G 16 S E G 17 S E G 18 S E G 19 S E G 20 S E G 21 S E G 22 S E G 23 S E G 24 S E G 25 S E G 26 S E G 27 S E G 28 S E G 29 S E G 30 S E G 31

4

July 26, 1999

HT1621 LCD 驱动程序

HT1621 LCD 驱动程序用得最多的一款段码LCD驱动控制器HT1621的C51程序2009-04-17 10:30:59| 分类:单片机| 标签:|字号大中小订阅HT1621是台湾Holtek公司推出的段码LCD驱动控制芯片,带同步串行接口,最多可以控制128段驱动方式可选1/2、1/3、1/4 Duty 和1/2、1/3 Bias。

供电电压为2.4~5.2V,无需外部振荡电路。

简单易用。

以下是应用HT1621驱动的LCD模块串行模式的C51范例。

/*HT1621 for C51 */#include /* 8051 寄存器定义请修改为自己用的文件 */typedef unsigned char uchar;typedef unsigned int uint;sbit _CS =P2^0;sbit _WR =P2^1;sbit _DAT=P2^4;/*-----------------*/DELAY(int t) /**/{int i,j;for (i=0;ifor (j=0;j}/*-----------------*/WRITE_COM(uchar com) /*Write a command to LCD*/{uchar i,k;_CS = 0;k=0x80;for(i=0;i!=3;i++) /*Write CMD code:100*/{ if(k&0x80==0)_DAT=0;else_DAT= 1;_WR = 0;_WR = 1;k=k<<1;}k=com;for(i=0;i!=9;i++) /*Write CMD */{if(k&0x80==0) _DAT=0;else _DAT=1;_WR=0;_WR=1;k=k<<1;}_CS=1;}/*------------------*/WRITE_DAT(uchar addr,uchar dat) /*Write display data to LCD*/ {uchar i,k;_CS = 0;k=0xa0;for(i=0;i=!3;i++) /*Write CMD code:101*/{ if(k&0x80==0)_DAT=0;else_DAT= 1;_WR = 0;_WR = 1;k=k<<1;}k=addr<<2;for(i=0;i!=6;i++) /*Write RAM address: xxA5~A0*/{if(k&0x80==0) _DAT=0;else _DAT=1;_WR=0;_WR=1;k=k<<1;}k=dat<<4;for(i=0;i!=4;i++) /*Write Display data :xxxxC0~C3*/{if(k&0x80==0) _DAT=0;else _DAT=1;_WR=0;_WR=1;k=k<<1;}_CS=1;}DISP_NUM(uchar dat) /*Write a number*/{uchar i,j,addr;for (i=8;i!=28;i++){WRITE_DAT(i,dat<<4);WRITE_DAT(++i,dat);}}DIS(uchar dat){uchar i,j;for(i=0;i!=28;i++)WRITE_DAT(i,dat);}SETUP_LCD(void){DELAY(100);WRITE_COM(0x01); /*Enable system*/WRITE_COM(0x18); /*CLOCK SOURCE IS 256kRC ON CHIP*/ WRITE_COM(0x29); /*BIAS=1/3 DUTY=1/4*/WRITE_COM(0x03); /*Display on*/DIS(0x00); /*Clear LCD*/DELAY(20);}main(){uchar i,j,temp;DELAY(100);SETUP_LCD();DELAY(10);while(1){DELAY(200);DIS(0x0f);DELAY(200);DIS(0x00);temp=0xf8;for(i=0;i!=8;i++) /*Display ICONs*/{for(j=0;j=4;j++){WRITE_DAT(i,temp>>1);DELAY(20);}}WRITE_DAT(13,0x01);WRITE_DAT(19,0x01);WRITE_DAT(23,0x01);DELAY(200);DISP_NUM(0xbe); /*0*/DELAY(200);DISP_NUM(0x06); /*1*/DELAY(200);DISP_NUM(0x7c); /*2*/DELAY(200);DISP_NUM(0x5e); /*3*/DELAY(200);DISP_NUM(0xc6); /*4*/DELAY(200);DISP_NUM(0xda); /*5*/DELAY(200);DISP_NUM(0xfa); /*6*/DELAY(200);DISP_NUM(0x0e); /*7*/DELAY(200);DISP_NUM(0xfe); /*8*/DELAY(200);DISP_NUM(0xde); /*9*/ }}。

tm1621段码液晶屏工作原理

tm1621段码液晶屏工作原理The TM1621 is a popular segment LCD screen controller that is widely used in various electronic devices. TM1621是一种流行的段码液晶屏控制器,广泛应用于各种电子设备。

The working principle of the TM1621 segment LCD screen is relatively simple. It utilizes a combination of segment drivers and common drivers to control each individual segment of the display. TM1621段码液晶屏的工作原理相对简单。

它利用段驱动器和公共驱动器的组合来控制显示器的每个单独段。

The segment drivers are used to turn on or off specific segments of the LCD, while the common drivers are responsible for selecting the specific common line to display the desired information. 段驱动器用于打开或关闭液晶屏的特定段,而公共驱动器负责选择特定的公共线以显示所需的信息。

One of the key features of the TM1621 is its ability to control LED displays with a lower power consumption, making it an ideal choicefor battery-powered devices. TM1621的一个关键特性是它能够以较低能耗控制LED显示,使其成为使用电池供电设备的理想选择。

超小体积段码液晶显示屏LCD驱动IC-VK1621S-1裸片及VK1088B QFN32 封装片

超小液晶显示屏产品-段码LCD液晶显示驱动IC:VK1088B/VK1621S-1裸片小体积产品对于PCB板的体积要求比较高,由于体积小,PCB板上的元器件也都必须用超小体积的,如电子角度尺、电子智能腰围尺、电子迷你倾角仪、电子深度尺、电子深度规、电子水平尺、电子游标卡尺、U盾、蓝牙盾、动态令牌、护颈仪等,由于液晶显示模块体积很小,一般选用VK1088B QFN32 4*4MM 封装的段码LCD液晶显示驱动IC;或者选用VK1621S-1/1622S/1623S等裸片进行邦定。

今天分享一下段码LCD液晶显示驱动IC- VK1621S-1及VK1088B的资料简介VK1621S-1概述:VK1621S-1是一个点阵式存储映射的LCD驱动器,可支持最大128点(32SEGx4COM)的 LCD屏,也支持2COM和3COM的LCD屏。

单片机可通过3/4个通信脚配置显示参数和发送显示数据,也可通过指令进入省电模式。

特点:•陈锐鸿:188/2466/2436-同步• QQ:361/888/5898•工作电压 2.4-5.2V•内置256 kHz RC振荡器(上电默认)•可外接32.768kHz晶体振荡器(OSCO,OSCI)•可外接256kHz时钟源(OSCI)•偏置电压(BIAS)可配置为1/2、1/3• COM周期(DUTY)可配置为1/2、1/3、1/4•内置显示RAM为32x4位•蜂鸣器频率可配置为2kHz、4kHz•省电模式(通过关显示和关振荡器进入)•时基和看门狗共用1个时钟源,可配置8种频率•时基或看门狗溢出信号输出脚为/IRQ脚 (开漏)• 3/4线串行接口•软件配置LCD显示参数•写命令和读写数据2种命令格式•读写显示数据地址自动加1• 3种显示数据的访问方式• VLCD脚提供LCD驱动电压(<VDD)•封装:SSOP48(300mil)(15.9mm x 7.5mm PP=0.635mm)LQFP48(7.0mm x 7.0mm PP=0.5mm)LQFP44(10.0mm x 10.0mm PP=0.8mm)SDIP28(288mil)(35.3mm x 7.3mm PP=2.54mm)DICE裸片触摸触控IC系列简介如下:标准触控IC-电池供电系列:VKD223EB --- 工作电压/电流:2.0V-5.5V/5uA-3V 感应通道数:1 通讯接口最长响应时间快速模式60mS,低功耗模式220ms 封装:SOT23-6VKD223B --- 工作电压/电流:2.0V-5.5V/5uA-3V 感应通道数:1通讯接口最长响应时间快速模式60mS,低功耗模式220ms 封装:SOT23-6VKD233DB ---工作电压/电流:2.4V-5.5V/2.5uA-3V 1感应按键封装:SOT23-6 通讯接口:直接输出,锁存(toggle)输出低功耗模式电流2.5uA-3VVKD233DH ---工作电压/电流:2.4V-5.5V/2.5uA-3V 1感应按键封装:SOT23-6 通讯接口:直接输出,锁存(toggle)输出有效键最长时间检测16SVKD233DS ---工作电压/电流:2.4V-5.5V/2.5uA-3V 1感应按键封装:DFN6通讯接口:直接输出,锁存(toggle)输出低功耗模式电流2.5uA-3VVKD233DR ---工作电压/电流:2.4V-5.5V/1.5uA-3V 1感应按键封装:DFN6 通讯接口:直接输出,锁存(toggle)输出低功耗模式电流1.5uA-3VVKD233DG --- 工作电压/电流:2.4V-5.5V/2.5uA-3V 1感应按键封装:DFN6 通讯接口:直接输出,锁存(toggle)输出低功耗模式电流2.5uA-3VVKD233DQ --- 工作电压/电流:2.4V-5.5V/5uA-3V 1感应按键封装:SOT23-6通讯接口:直接输出,锁存(toggle)输出低功耗模式电流5uA-3VVKD233DM --- 工作电压/电流:2.4V-5.5V/5uA-3V 1感应按键封装:SOT23-6 (开漏输出)通讯接口:开漏输出,锁存(toggle)输出低功耗模式电流5uA-3VVKD232C--- 工作电压/电流:2.4V-5.5V/2.5uA-3V 感应通道数:2 封装:SOT23-6通讯接口:直接输出,低电平有效固定为多键输出模式,內建稳压电路——————————————————————————————————MTP触摸IC——VK36N系列抗电源辐射及手机干扰:VK3601L --- 工作电压/电流:2.4V-5.5V/4UA-3V3 感应通道数:1 1对1直接输出待机电流小,抗电源及手机干扰,可通过CAP调节灵敏封装:SOT23-6VK36N1D --- 工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:1 1对1直接输出触摸积水仍可操作,抗电源及手机干扰,可通过CAP调节灵敏封装:SOT23-6VK36N2P --- 工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:2 脉冲输出触摸积水仍可操作,抗电源及手机干扰,可通过CAP调节灵敏封装:SOT23-6VK3602XS ---工作电压/电流:2.4V-5.5V/60UA-3V 感应通道数:2 2对2锁存输出低功耗模式电流8uA-3V,抗电源辐射干扰,宽供电电压封装:SOP8VK3602K --- 工作电压/电流:2.4V-5.5V/60UA-3V 感应通道数:2 2对2直接输出低功耗模式电流8uA-3V,抗电源辐射干扰,宽供电电压封装:SOP8VK36N2D --- 工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:2 1对1直接输出触摸积水仍可操作,抗电源及手机干扰,可通过CAP调节灵敏封装:SOP8VK36N3BT ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:3 BCD码锁存输出触摸积水仍可操作,抗电源及手机干扰,可通过CAP调节灵敏封装:SOP8VK36N3BD ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:3 BCD码直接输出触摸积水仍可操作,抗电源及手机干扰,可通过CAP调节灵敏封装:SOP8VK36N3BO ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:3 BCD码开漏输出触摸积水仍可操作,抗电源及手机干扰封装:SOP8/DFN8(超小超薄体积)VK36N3D --- 工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:3 1对1直接输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N4B ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:4 BCD输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N4I---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:4 I2C输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N5D ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:5 1对1直接输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N5B ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:5 BCD输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N5I ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:5 I2C输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N6D --- 工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:6 1对1直接输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N6B ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:6 BCD输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N6I ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:6 I2C输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N7B ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:7 BCD输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N7I ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:7 I2C输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N8B ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:8 BCD输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N8I ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:8 I2C输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N9I ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:9 I2C输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)VK36N10I ---工作电压/电流:2.2V-5.5V/7UA-3V3 感应通道数:10 I2C输出触摸积水仍可操作,抗电源及手机干扰封装:SOP16/DFN16(超小超薄体积)——————————————————————————————————1-8点高灵敏度液体水位检测IC——VK36W系列VK36W1D ---工作电压/电流:2.2V-5.5V/10UA-3V3 1对1直接输出水位检测通道:1可用于不同壁厚和不同水质水位检测,抗电源/手机干扰封装:SOT23-6备注:1. 开漏输出低电平有效2、适合需要抗干扰性好的产品应用VK36W2D ---工作电压/电流:2.2V-5.5V/10UA-3V3 1对1直接输出水位检测通道:2可用于不同壁厚和不同水质水位检测,抗电源/手机干扰封装:SOP8备注:1. 1对1直接输出 2、输出模式/输出电平可通过IO选择VK36W4D ---工作电压/电流:2.2V-5.5V/10UA-3V3 1对1直接输出水位检测通道:4可用于不同壁厚和不同水质水位检测,抗电源/手机干扰封装:SOP16/DFN16 备注:1. 1对1直接输出 2、输出模式/输出电平可通过IO选择VK36W6D ---工作电压/电流:2.2V-5.5V/10UA-3V3 1对1直接输出水位检测通道:6可用于不同壁厚和不同水质水位检测,抗电源/手机干扰封装:SOP16/DFN16 备注:1. 1对1直接输出2、输出模式/输出电平可通过IO选择VK36W8I ---工作电压/电流:2.2V-5.5V/10UA-3V3 I2C输出水位检测通道:8可用于不同壁厚和不同水质水位检测,抗电源/手机干扰封装:SOP16/DFN16。

用HT1621驱动LCD的方法

ApplicationNoteTM58XX_16S PRODUCT NAMETM58XXTITLETM58XX 用HT1621驱动LCD的方法APPLICATION NOTE1. 说明2. 程序3. LCD Layout4. 应用线路图1. 对HT1621初始化:主要是对HT1621使用频率、音频选择、是否打开蜂鸣器等进行选择先使能片选位(CS\=0),ID为4即格式命令为100然后送相应的命令字,送完后将CS\脚置1,即不对HT1621操作时CSP为1。

2. 清屏:HT1621内部有32*4位的RAM单元,也可以说是输出缓冲区,将其清0,即LCD不显示。

3. 输出:Demo板使用的LCD为五个显示位,本程序实现后两位固定输出dE,前三位输出000-->111...-->FFF后动态停机输出数据时先置片选位有效(CS\=0)――>然后送ID为5(101)即命令格式为写操作――>接着将欲显段地址送1621――>将要显的数据送1621输出――>最后关闭片选位即CS\脚置1。

其它说明:(1)对1621写操作问题:对1621操作时先置片选位有效(CSP=0),不对1621操作时置片选位无效(CSP=1)。

(2)注意地址、数据或命令的长度问题。

2 tenx technology, inc.;---------------------------;Title: Write HT1621;Function:;Note: The voltage applied to Vlcd pin must be lower than Vdd.;Clock: 4m;Config word: xt_osc & _wdt_off & _cpt_on & _type_general & _lv_don't use;Data: 2004_5_9; list p=tm58p20;---------------------------00hindf equ01htmr0 equ02hpc equstatus equ 03hfsr equ04h05hporta equportb equ 06hcsp equ 4wrp equ 5dtp equ 607hportc equwakeup equ 20hirqm equ 21hirqf equ 22h;---------------------------;status bits definec equ 00hdc equ 01hz equ 02hpd equ 03hto equ 04hpa0 equ 05hpa1 equ 06hpa2 equ 07h;---------------------------;option bits define00hps0 equps1 equ 01hps2 equ 02hpsa equ 03hrte equ 04hrts equ 05h;---------------------------cnt equ 08hid equ 09htemp equ 0ahcmd equ 0bh3 tenx technology, inc.temp1 equ 0chaddr equ 0dhdat equ 0ehtemper equ 0fhorg 7ffhlgoto mainorg 00hnop;---------------------------lcd_tablehaddam pc,1retla b'00000101' ;0retla b'00000000' ;1retla b'00000110' ;2retla b'00000010' ;3retla b'00000011' ;4retla b'00000011' ;5retla b'00000111' ;6retla b'00000000' ;7retla b'00000111' ;8retla b'00000011' ;9retla b'00000111' ;aretla b'00000111' ;bretla b'00000110' ;cretla b'00000110' ;dretla b'00000111' ;eretla b'00000111' ;fretla b'00000111' ;flcd_tableladdam pc,1retla b'00001111' ;0retla b'00000110' ;1retla b'00001011' ;2retla b'00001111' ;3retla b'00000110' ;4retla b'00001101' ;5retla b'00001101' ;6retla b'00000111' ;7retla b'00001111' ;8retla b'00001111' ;9retla b'00000111' ;aretla b'00001100' ;bretla b'00001000' ;cretla b'00001110' ;dretla b'00001001' ;eretla b'00000001' ;f4 tenx technology, inc.retla b'00000001' ;f;---------------------------dispwriteid_:movla 3movam cntbcm status,crlm id,mrlm id,mrlm id,mrlm id,mrlm id,mmovm id,amovam templcall dispwritebits_ret;---------------------------dispwritecmd_:movla 8movam cntmovm cmd,amovam templcall dispwritebits_ret;---------------------------dispwritebits_:rlm temp,mbtmsc status,clgoto highslow:bcm portb,dtp ;写数据'0'bcm portb,wrpnopnopnopnopnopnopbsm portb,wrpnopnopnopnopnopnopnoplgoto loop1highs:bsm portb,dtp ;写数据'1'5 tenx technology, inc.bcm portb,wrpnopnopnopnopnopnopbsm portb,wrpnopnopnopnopnopnoploop1:decmsz cnt,mlgoto dispwritebits_ret;---------------------------dispwritebit_:movla 1movam cntmovla 80hmovam templcall dispwritebits_ret;---------------------------writeto46addr_:movla 7movam cntbcm status,crlm addr,mmovm addr,amovam templcall dispwritebits_retdispwriteaddr_:movla 6movam cntbcm status,crlm addr,mrlm addr,mmovm addr,amovam templcall dispwritebits_ret;---------------------------dispwritedata_:6 tenx technology, inc.movla 4movam cntmovm dat,amovam templcall dispwritebits1_ret;---------------------------;input: temp,cnt;func:only for write dat low nibble;-------------dispwritebits1_:loop00:rrm temp,mbtmsc status,clgoto high11low00:bcm portb,dtpbcm portb,wrpnopnopnopnopnopnopnopbsm portb,wrpnopnopnopnopnopnopnoplgoto loop10high11:bsm portb,dtpbcm portb,wrpnopnopnopnopnopnopnopbsm portb,wrpnopnopnopnop7 tenx technology, inc.nopnopnopnoploop10:decmsz cnt,mlgoto loop00ret;---------------------------initdisp_:;turn on lcd display id:100bcm portb,csp ;使能ht1621movla 4movam idlcall dispwriteid_movla 3movam cmd ;turn on lcd bias gereratorlcall dispwritecmd_lcall dispwritebit_movla b'00011000' ;rc 256kmovam cmdlcall dispwritecmd_lcall dispwritebit_movla b'00101001' ;select bias ,dutymovam cmd ;1/4duty,1/3biaslcall dispwritecmd_lcall dispwritebit_movla b'11100011' ;normal modemovam cmdlcall dispwritecmd_lcall dispwritebit_movla 1 ;turn sys osc onmovam cmdlcall dispwritecmd_lcall dispwritebit_movla b'01100000' ;set buzzer 2khzmovam cmdlcall dispwritecmd_lcall dispwritebit_movla b'00001000' ;close buzzermovam cmdlcall dispwritecmd_8 tenx technology, inc.lcall dispwritebit_movla b'00000101' ;close watch dogmovam cmdlcall dispwritecmd_lcall dispwritebit_bsm portb,csp ;不对HT1621操作时CSP为1nopret;---------------------------clearall_:movla d'24' ;清除地址08h后的24个单元movam temp1 ;08h前的单元因为本程序未用,可以不理会bcm portb,cspmovla d'5'movam idlcall dispwriteid_ ;3位idmovla d'8'movam addrlcall dispwriteaddr_;6位地址bbb:clrm datlcall dispwritedata_ ;8位数据decmsz temp1,1lgoto bbbbsm portb,cspnopnopret;---------------------------;seg10 seg9 显示第1位数据;seg8 seg13 显示第2位数据;seg17 seg21 显示第3位数据;seg25 seg29 显示第4位数据;seg31 seg30 显示第5位数据;前三位数据显示从000-->111-->...FFF;后两位数据为固定显示dEoutputseg10:movla d'5' ;D'5'为101即为写命令movam idbcm portb,csp ;片选位有效lcall dispwriteid_movla d'10'movam addr ;将欲显段地址送HT1621lcall dispwriteaddr_9 tenx technology, inc.movm temp1,alcall lcd_tableh ;将欲显数据高半位送HT1621movam dat ;因为HT1621的RAM为四位长lcall dispwritedata_ ;所以分两次送bsm p ortb,cspnopnopseg9:movla d'5'movam idbcm portb,csplcall dispwriteid_movla d'9'movam addrlcall dispwriteaddr_movm temp1,alcall lcd_tablel ;将欲显数据低半位送HT1621movam datlcall dispwritedata_bsm portb,cspnopnopseg8:movla d'5' ;以下显示位处理方法同上movam idbcm portb,csplcall dispwriteid_movla d'8'movam addrlcall dispwriteaddr_movm temp1,alcall lcd_tablehmovam datlcall dispwritedata_bsm portb,cspnopnopseg13:movla d'5'movam idbcm portb,csplcall dispwriteid_movla d'13'movam addrlcall dispwriteaddr_movm temp1,alcall lcd_tablelmovam dat10 tenx technology, inc.lcall dispwritedata_bsm portb,cspnopnopseg17:movla d'5'movam idbcm portb,csplcall dispwriteid_movla d'17'movam addrlcall dispwriteaddr_movm temp1,alcall lcd_tablehmovam datlcall dispwritedata_bsm portb,cspnopnopseg21:movla '5'movam dbcm ortb,csplcall dispwriteid_movla '21'movam ddrlcall dispwriteaddr_movm emp1,alcall cd_tablelmovam atlcall dispwritedata_bsm ortb,cspnopnopseg25:movla '5'movam dbcm ortb,csplcall dispwriteid_movla '25'movam ddrlcall dispwriteaddr_movla dhlcall cd_tablehmovam atlcall dispwritedata_bsm ortb,cspnop11 tenx technology, inc.nopseg29:movla '5'movam dbcm ortb,csplcall dispwriteid_movla '29'movam ddrlcall dispwriteaddr_movla dhlcall cd_tablelmovam atlcall dispwritedata_bsm ortb,cspnopnopseg31:movla '5'movam dbcm ortb,csplcall dispwriteid_movla '31'movam ddrlcall dispwriteaddr_movla ehlcall cd_tablehmovam atlcall dispwritedata_bsm ortb,cspnopnopseg30:movla '5'movam dbcm ortb,csplcall dispwriteid_movla '30'movam ddrlcall dispwriteaddr_movla ehlcall cd_tablelmovam atlcall dispwritedata_bsm ortb,cspbcm ortb,wrpbcm ortb,dtpret;---------------------------12 tenx technology, inc.main:clrm orta ;I/O口初始化movla 0hiodir rtaclrm ortbmovla 0hiodir ortbclrm ortcmovla 0hiodir ortcclrm mr0movla 7hselectstart:lcall initdisp_ ;初始化1621lcall clearall_ ;清屏clrm temp1lp0lcall output ;输出000-->111...-->fff后动态停机incm temp1, 1movla 10hsubam temp1, 0btmss status, cgoto lp0aaa:lgoto aaa;---------------------------end;---------------------------13 tenx technology, inc.14 tenx technology, inc.LCD LayoutSEG9SEG8SEG7SEG6SEG5SEG4SEG3SEG2SEG1SEG0COM0COM1COM2COM3应用线路图15 tenx technology, inc.。

中微爱芯CS1621 32列4行LCD驱动控制电路产品说明书

江苏省无锡市滨湖区建筑西路777号无锡国家集成电路设计中心B4楼 第 1 页 共 27 页http://www.i-core. cn 邮编:214072版本:2019-07-A1CS162132列4行LCD 驱动控制电路产品说明书说明书发行履历:圳富瑞世嘉 中微爱芯一级代理(微信):13530167943 址:www.forchip.cn江苏省无锡市滨湖区建筑西路777号无锡国家集成电路设计中心B4楼第 2 页 共 27 页http://www.i-core. cn 邮编:214072版本:2019-07-A11、概 述CS1621是一种128点阵式存储映射多功能LCD 驱动电路。

CS1621的S/W 结构特点,使它适合点阵式LCD 显示,包括LCD 模块和显示子系统,CS1621还具有节电功能。

其主要特点如下: ● 工作电压:2.4V ~5.5V ● 内部256kHz RC 振荡器● 外部32kHz 晶振或256kHz 频率输入● 可选择1/2或1/3偏置和1/2、1/3或1/4占空比LCD 显示 ● 内部时基频率源● 蜂鸣器驱动信号频率可选择2kHz 或4kHz ● 具有关机指令可减少功耗● 内部时基发生器和WDT 看门狗定时器 ● 内部时基或WDT 溢出输出 ● 八个时基/WDT 时钟的时钟源 ● 32×4 LCD 驱动器 ● 内部32×4bit 显示RAM ● 四路串行接口 ● 内部LCD 驱动频率源 ● 可用指令控制操作 ● 数据模式和命令模式指令 ● R/W 地址自动累加 ● 三种数据访问模式● VLCD 引脚用来调整LCD 工作电压 ● 工作环境温度:-40~85℃● 封装形式:SOP16/SOP24/SSOP24/SOP28/QFP44/SSOP48/LQFP48深圳富瑞世嘉 中微爱芯一级代理手机(微信):13530167943网 址:www.forchip.cn江苏省无锡市滨湖区建筑西路777号无锡国家集成电路设计中心B4楼 第 3 页 共 27 页http://www.i-core. cn 邮编:214072版本:2019-07-A1订购信息: 管装:注:如实物与订购信息不一致,请以实物为准。

HT1621 LCD液晶显示驱动IC

HT1621 LCD液晶显示为HT品牌IC,是一款存储器映射和多功能 LCD 控制/ 驱动芯片。

该芯片显示模式有 80 点 (20×4) 或128 点 (16×8)。

HT1621 的软件配置性使得它适用于多种 LCD 应用,包括 LCD 模块和显示子系统。

HT1621 通过双线双向 I2C 接口与大多数微处理器 / 微控制器进行通信。

应用领域主要用于:电表, 水表,气表,热能表, 家用电器,游戏机,电话机, 消费类电子产品.

产品特性

●工作电压:2.4 ~ 5.5V

●内部 32kHz RC 振荡器

● Bias:1/3 或 1/4;Duty:1/4 或 1/8

●带电压跟随器的内部 LCD 偏置发生器

● I2C 接口

●两个可选 LCD 帧频率:80Hz 或 160Hz

●多达 16×8 位 RAM 用来存储显示数据

●显示模式:

– 20×4 模式:20 SEGs 和 4 COMs

– 16×8 模式:16 SEGs 和 8 COMs

●多种闪烁模式

●读 / 写地址自动增加

●内建 16 级 VLCD 电压调整电路

●低功耗

●提供 VLCD 引脚用来调整 LCD 工作电压

●采用硅栅极 CMOS 制造工艺

封装形式有:LQFP44,SSOP48,LQFP48,DIP28,DICE裸片。

另外可以定制COB邦定片,或其他特殊规格封装。

HT1621LCD 驱动芯片资料

Prepared: __________ Checked: __________ Approved: _________Fax:(0752)2634396E-mail:LCM@CASILSEMI .COMOPTO0230CTL LCD MODULE1、FEATURESDisplay Type: TNDisplay Format: 4-digits 7 segments “8” & several iconsInput Data: 3-wire serial interfaceDisplay Mode: Positive ModeDriving Mode: 1/4 Duty, 1/3 BiasOperating Voltage: Single Power Supply (3.0V±5%)Viewing Direction: 6 O’clockBacklight: LED2、ABSOLUTE MAXIMUM RATINGSUnitMax.Min.Item SymbolPower Supply for Logic Vdd -0.3 3.5 VPower Supply for LCD Drive Vlcd Vdd-0.3 Vdd+0.3VInput Voltage Vi -0.3 Vdd+0.3VOperating Temperature Topr 0 +50 ℃Storage Temperature Tstg -10 +60 ℃3、MECHANICAL PARAMETERSUnit Item Description LCM Outline Dimension 37.6(L) x 22.0(W) mmViewing Area 25.0(L) x 10.0(W) mmg20Weight About4、SYSTEM BLOCK DIAGRAME-mail:LCM@CASILSEMI .COM5、DC CHARACTERISTICS (Ta=25℃; Vdd=3.0V ±5%,Vss=0V)Item SymbolTest Condition Min.Typ. Max. Unit LCM Operating Voltage Vdd -- -- 3.0 -- V LCD Operating Voltage Vlcd Vdd-Vo -- 3.0 -- V LCM Operating Current Idd Vdd=3.0V/LCD ON -- 0.9 1.2 mAStandby Current Istb No loadPower down mode -- 2 16 uAInput High Voltage Vih DATA, /WR, /CS, /RD 2.0-- Vdd V Input Low Voltage Vil DATA, /WR, /CS, /RD 0 -- 0.6 V BZ, /BZ, /IRQ Iol1 Vol=0.5V 1.7 3.0 -- mA BZ, /BZ Ioh1 Voh=2.5V -1.7-3.0 -- mADATA Iol1 Vol =-0.5V 250500 -- uADATA Ioh1 Voh = 2.5V -250-500 -- uALCD Common Sink Current Iol2 Vol=0.5V 100200 -- uA LCD Common Source Current Ioh2 Voh=2.5V -45-90 -- uA LCD Segment Source Current Iol3 Vol=0.5V 70 150 -- uA LCD Segment Source Current Ioh3 Voh=2.5V -20-40 -- uAPull-high Resistor Rph DATA, /WR, /CS, /RD 50 100 150 K Ω6、PIN ASSIGNMENTNO. Symbol Level Function1 CS L, H/L Enable selection inputH—Disabled L—Enabled2 WR L, L-H Write Signal3 DATA H/L Serial data input/output4 VDD H Positive power supply5 VSS L Negative power supply, ground6 BL+ 3.0V LED Backlight (+)7 BL- 0V LED Backlight (-)8 IRQ O Time base or WDT overflowflag NMOS opendrain output9 BZ+ 10 BZ-2kHZ or4kHZ tone frequency output pairE-mail:LCM@CASILSEMI .COM7、AC CHARACTERISTICS(Vdd=3.0V±5%,Vss=0V ,Ta=25℃)UnitMax.Parameter Symbol Min.Typ.Clock Fsys 24 32 40 KHZ SystemLCD Frame Frequency Flcd 48 64 80 KHZSerial Data Clock (/WR pin) Fclk1 -- -- 300 KHZSerial Data Clock (/RD pin) Fclk2 -- -- 150 KHZSerial Interface Reset Pulse WidthTcs -- 250 -- ns (Figure 3)/WR, /RD Interface Pulse WidthTclk 3.34 -- -- us (Figure 1)Rise/Fall Time Serial Data ClockTr,Tf -- 120 -- ns Width (Figure 1)Setup Time for Data to /WR, /RD,Tsu -- 120 -- ns Clock Width (Figure 2)Hold Time for Data to /WR, /RD,Clock Width (Figure 2) Th -- 120 -- nsSetup Time for Data to /WR, /RD,Tsu1 -- 100 -- ns Clock Width (Figure 3)Hold Time for /CS to /WR, /RD,Clock Width (Figure 3) Th1 -- 100 -- ns8、CONTROL AND DISPLAY COMMANDName ID CommandCode D/C Function Def.READ 110 A5A4A3A2A1A0D0D1D2D3D Read data from the RAM WRITE 101 A5A4A3A2A1A0D0D1D2D3D Write data to the RAMREAD-MODIFY-WRITE101 A5A4A3A2A1A0D0D1D2D3D Read and Write data to the RAMSYS DIS 100 0000-0000-X C Turn off both system oscillator And LCD bias generatorYSYS EN 100 0000-0001-X C Turn on system oscillatorLCD OFF 100 0000-0010-X C Turn off LCD display Y LCD ON 100 0000-0011-X C Turn on LCD displayTIMER DIS 100 0000-0100-X C Disable time base output TIMER EN 100 0000-0110-X C Enable time base outputCLR TIMER 100 0000-1101-X C Clear the contents of time basegeneratorWDT DIS 100 0000-0101-X C Disable WDT time-out flag output Y WDT EN 100 0000-0111-X C Enable WDT time-out flag output CLR WDT 100 0000-1111-X C Clear the contents of WDT stageRC 32K 100 0001-10XX-X C System clock source, on-chipRC oscillatorY/IRQ DIS 100 100X-0XXX-X C Disable /IRQ output Y /IRQ EN 100 100X-1XXX-X C Enable /IRQ outputF1 100 101X-0000-X C Time base clock Output: 1HzThe WDT time-out flag after: 4sF2 100 101X-0001-X C Time base clock Output: 2HzThe WDT time-out flag after: 2sF4 100 101X-0010-X C Time base clock Output: 4HzThe WDT time-out flag after: 1sF8 100 101X-0011-X C Time base clock Output: 8HzThe WDT time-out flag after: 1/2sF16 100 101X-0100-X C Time base clock Output: 16HzThe WDT time-out flag after: 1/4sF32 100 101X-0101-X C Time base clock Output: 32HzThe WDT time-out flag after: 1/8sF64 100 101X-0110-X C Time base clock Output: 64HzThe WDT time-out flag after: 1/16sF128 100 101X-0111-X C Time base clock Output: 128HzThe WDT time-out flag after: 1/32sY NORMAL 100 1110-0011-X C Normal mode Y Note: X: Don`t care, A5~A0: RAM address, D3~D0: RAM dataD/C: Data/Command mode, Ref.: Power on reset default9、ASSEMBLY DIAGRAM。

HOLTEK HT1621 LCD驱动器驱动器驱动器驱动器

系统结构

显示内存 RAM 静态显示内存 RAM 以 32 4 位的格式储存所显示的数据 RAM 的数据直接映象 到 LCD 驱动器 可以用 READ WRITE 和 READ-MODIFY-WRITE 命令访问

RAM 映象图

系统振荡器 HT1621 系统时钟用于产生时基/看门狗定时器 WDT 时钟频率 LCD 驱动时钟和声 音频率 片内 RC 振荡器 256KHz 晶振(32.768KHz)或一个外接的由软件设定的 256KHz 时钟可以产生时钟源 系统振荡器配置图参见下图 执行 SYS DIS 命令可以停止系统时钟 和 LCD 偏压发生器工作 SYS DIS 命令只适用于片内 RC 振荡器或晶振 当系统时钟停止 工作时 LCD 将显示空白 时基/看门狗定时器功能也将失效

插口号

25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48

X

58.14 58.14 58.14 58.14 58.14 58.14 58.14 58.14 55.55 48.92 42.29 35.66 29.03 22.40 15.77 9.14 2.42 -4.21 -10.84 -17.47 -24.10 -30.73 -38.17 -45.39

WRITE 脉冲输入 接一上拉电阻 在 /WR 信 号 的 上 升 沿 DATA 线 上 的 数 据 写 到

HT1621 外接上拉电阻的串行数据输入/输出 负电源; 地 OSCI 和 OSCO 外接一个 32.768KHz 晶振用于产生系 统时钟 若用另一个外部时钟源, 应接在 OSCI 上 若用片内 RC 振荡器 OSCI 和 OSCO 应悬空 LCD 电源输入 正电源

LCD驱动芯片TM1621D『官方最新规格书』

最大 值

单位

KHz KHz KHz KHz KHz KHz Hz

fSYS2 /128

Hz

n/ fLCD

s

300 KHz

500 KHz

2

us

1

us

系统结构

1、显示内存(RAM) 静态显示内存(RAM)以23x4位的格式储存所显示的数据,但是只有SEG9~SEG22所对

应的显示内存是有用的。RAM的数据直接映象到LCD驱动器。

80

150

5V VOL=0.5V

150

250

IOH2 LCD 公共口源电流 3V VOH=2.7V

-80

-120

5V VOH=4.5V

-120

-200

IOL3 LCD 段管脚漏电流 3V VOL=0.3V

60

120

5V VOL=0.5V

120

200

IOH3 LCD 段管脚源电流 3V VOH=2.7V

©Titan Micro Electronics

V1.0

1

14x4 LCD 驱动器

TM1621D

管脚描述

管脚号

管脚名

I/O

功能描述

10

11

12 13 14 15 16~19 1~9 20~24

/CS

/WR

DATA VSS VLCD VDD COM0~COM3 SEG9~SEG22

粗体100即“100”,表示命令模式类型。如果执行连续的命令,除了第一个命令,其它命

令的模式类型码将被忽略。LCD OFF命令使LCD偏压发生器失效,从而关闭LCD显示;LCD ON

命令使LCD偏压发生器有效,从而打开LCD显示。BIAS&COM是LCD模块相关命令,可以使

lcd液晶驱动芯片wt1621[资料]

![lcd液晶驱动芯片wt1621[资料]](https://img.taocdn.com/s3/m/a79423d60408763231126edb6f1aff00bed5706a.png)

LCD液晶驱动IC WT1621使用资料000咨询TEL:135****2879,QQ:176544390000目录0001、产品特点 (200)2、概述 (200)3、管脚说明 (300)4、电气参数 (400)4.1、直流特性 (400)4.2、交流特性 (400)5、环境绝对极限参数 (500)6、功能描述 (500)6.1、显示内存 (500)6.2、系统振荡器 (500)6.3、Time Base and Watchdog Timer (WDT) (600)6.4、蜂鸣器输出 (600)6.5、LCD Driver (700)7、指令格式 (700)8、Timing Diagram (800)9、Interfacing (900)10、应用电路 (900)11、指令索引 (1000)12、历史版本记录 (1100)1、产品特点00工作电压2.4V~5.5V内建256KHz RC oscillator可外接32.768KHz 石英震荡器或256KHz 频率可选择1/2, 1/3 偏压, 亦可选择1/2, 1/3 或1/4 的COM 周期两种蜂鸣器频率(2KHz/4KHz)省电模式内建time base generator 以及WDTTime base or WDT 溢位输出8 种的time base/WDT 的时钟输入32x4 LCD驱动器内建32x4 bit 显示内存3-wire serial interface软件程控资料及指令模式自动增加读写地址VLCD 脚位可用来调整LCD输出电压2、概述000WT1621是一个32x4的LCD驱动器. 可软件程控使其适用于多样化的LCD应用线路. 仅用到3至4条讯号线便可控制LCD驱动器,除此之外亦可介由指令使其进入省电模式内部框图00标识说明CSB 芯片致能BZ,BZB 蜂鸣器输出WRB,RDB,DA TA 控制讯号线LCD 输出COM0~COM3SEG0~SEG31IRQB Time base or WDT溢位输出3、管脚说明004、电气参数00 4.1、直流特性000Symbol Parameter Test Conditions Min Typical Max Unit VDD ConditionsLstb1 Standby Current 5V No loadPower down mode- 5 30 uALstb2 Standby Current 3V No loadPower down mode- 2 15 uALdd1 Operation Current 5V No load,internal RCoscillator on- 120 - uALdd2 Operation Current 3V No load,internal RCoscillator on- 48 - uALo1 LCD Common SinkCurrent5V VOL=2.5V - 2.36 - mA Lo2 LCD CommonSource Current5V VOH=2.5V - 1.51 - mA Lo3 LCD Segment SinkCurrent5V VOL=2.5V - 1.58 - mALo4 LCD SegmentSource Current5V VOH=2.5V - 0.9 - mA 4.2、交流特性000SymbolParameter VDD Min Typical Max UnitFint3 Internal RC oscillator 3V 133 KHz Fint5 Internal RC oscillator 5V 256 KHz Fext5 External input clock 5V 3.5 MHz Trdbl3 Minimum read low pulse 3V 350 ns Trdbl5 Minimum read low pulse 5V 350 ns Twrbl3 Minimum read low pulse 3V 350 ns Twrbl5 Minimum write low pulse 5V 350 ns Tcsbh5 Minimum CSB high pulse 5V 50 ns5、环境绝对极限参数00参数标记环境条件额定值单位电源V DD —V SS- -0.3~+5.5 V输入电压V IN所有输入V SS-0.3~V DD+0.3 V存储温度T STG- -50~+125 °C使用温度T OPR- -25~+75 °C6、功能描述006.1、显示内存000显示内存共计可存32x4 bits 资料. 显示内存资料可介由READ, WRITE, and READ-MODIFY-WRITE 等指令存取. 以下是显示内存的资料与common, segment间的对照表6.2、系统振荡器00WT1621系统的时脉是用以产生time base/Watchdog, common, segment以及蜂鸣器所需的频率. 系统时脉的来源可介由指令切换成内建的RC oscillator (256 KHz), crystal oscillator (32.768 KHz), 或者是external 256 KHz clock. 在下达SYS DIS这个指令后, 系统时脉便会停止(当使用的时脉是内建的RC oscillator 或是crystal oscillator时),LCD的偏压线路也会关掉.一旦时脉停止, LCD显示器便显示空白, time base/WDT也失去功能. LCD OFF这个指令可用来将偏压线路关掉. SYS DIS这个指令可以让LCD驱动器进入省电模式, 但是如果使用external 256K oscillator时便无法达到省电功能.刚通电时LCD驱动器是在SYS DIS 的状态006.3、Time Base and Watchdog Timer (WDT) 000Time base generator 是由8阶的计数器所组成, 其功能是用来产生正确的时基. The watch dog timer (WDT)则是由8阶的计数器以及另外的2阶计数器共同组成,其功能是中断控制器或其它副系统的不正常状态, 例如不想要的跳跃,程序执行错误. The WDT time out 会设定内部的WDT time out旗标. Time base generator 以及WDT time out 旗标的输出为IRQB这个讯号脚位. 总共有8种不同的频率可供Time base generator 以及WDT 使用. WDT的输出频率为f WDT=32kHz/2n.方程式中的n 范围从0到7可介由指令控制. 方程式中的32 KHz是LCD驱动器系统时脉的来源有3种:crystal oscillator of 32.768 KHz, 内建RC chip oscillator (256 KHz), 或是external frequency of 256 KHz. 使用与Time base generator 以及WDT 相关的指令时,须注意这两个功能共享一组8阶的计数器. 举例来说, 使用到WDT DIS也会把time base generator 关掉,但是执行WDT EN指令时同时致能time base generator以及WDT. 执行TIMER EN这个指令后WDT与IRQ间的联机会呈断路而与time base generator的输出连接. WDT可介由CLR WDT这个指令做清除的动作, time base generator可介由CLR WDT或CLR TIMER等两个指令做清除CLR WDT或CLR TIMER应该在WDT EN或TIMER EN等两个指令前执行。

HT1621液晶显示驱动详细原理及程序

Ht1621液晶显示详细驱动使用说明以及程序1.概述HT1621是128点内存映象和多功能的LCD驱动器,HT1621的软件配置特性使它适用于多种LCD应用场合,包括LCD模块和显示子系统。

用于连接主控制器和HT1621的管脚只有4或5条,HT1621还有一个节电命令用于降低系统功耗。

在虎风所做的这个系统中ht1621用于驱动一个静态的LCD液晶显示器。

液晶显示的方式分为静态显示和动态显示。

静态与动态的区别在于静态显示是持续供电的,而动态显示是利用人的视觉停留效果,快速扫描数码管各个段,让人在视觉上感觉到数码管是同时显示的。

2.HT1621接线原理图3.静态LCD结构图4.几个曾经纠结的概念Time base:时基,即时间基准,可以用来输出,作为外部时钟的时间基准。

占空比:将所有公共电极(COM)各施加一次扫描电压的时间叫一帧,单位时间内扫描多少帧的频率叫帧频,将扫描公共电极(COM)选通的时间与帧周期之比叫占空比。

通常占空比等于公共电极数N的倒数,即1/N。

这就是说假如你要驱动4个液晶,就需要4个COM,那么你的占空比就要设定为1/4。

偏压比:指的是液晶的偏压系数,可以看看专业技术文章,偏压目的是克服交叉效应,通过把半选择点与非选择点的电压平均,适度提高非选择点的电压来抵消半选择点上的一部分电压,使半选择点上的电压下降,从而提高显示对比度;最终行半选择点和非选择点上的电压均为显示电压的1/a,1/a就称为偏压系数,也称为偏压。

此方法称为1/a偏压的平均电压法,简称为1/a偏压法。

VLCD(LCD驱动电压): LCD的驱动电压为加在点亮部分的段电压与公共电压之差(峰-峰值)。

5.关于RAM地址映射的概念为了这个问题困扰了很久,虎风太愚钝啦……Ht1621有一个32*4的LCD驱动,映射到32*4的RAM地址。

上图中写命令101后面跟6位RAM地址,那么这个地址是如何确定的呢?其实说白了也很简单,RAM地址就是SEG的序号。

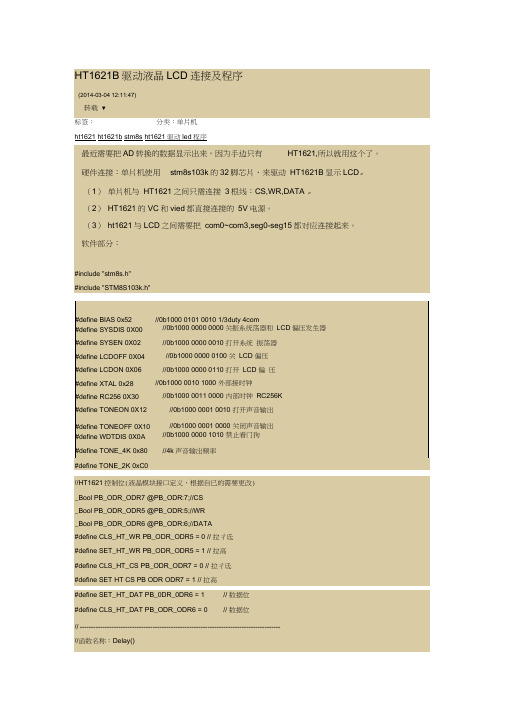

HT1621B驱动液晶LCD连接及程序

〃参数说明:Addr为写入初始地址,Num为写入数据

〃说 明:因为HT1621的数据位4位,所以实际写入数据为参数的后

//

void Ht1621WrOneNum(uchar Addr,uchar num)

{

CLS_HT_CS;//HT1621_CS=0;

Ht1621Wr_Data(0xa0,3);//写入数据标志101

Ht1621Wr_Data(Addr<<2,6); //写入地址数据

Ht1621Wr_Data(num,8);〃写一个完整的数。就是连续写两个数。

SET_HT_CS;//

}

//

//函数名称:void Ht1621WrAIIData()

{

i = 0x21;

}

〃PE_ODR=PE_ODRA0x20;

DelayMS(200);

}

}

(1) 单片机与HT1621之间只需连接3根线:CS,WR,DATA。

(2)HT1621的VC和vied都直接连接的5V电源。

(3)ht1621与LCD之间需要把com0~com3,seg0-seg15都对应连接起来。

软件部分:

#include "stm8s.h"

#include "STM8S103k.h"

#define BIAS 0x52

//0b1000 0101 0010 1/3duty 4com

#define SYSDIS 0X00

//0b1000 0000 0000关振系统荡器和LCD偏压发生器

#define SYSEN 0X02

//0b10000000 0010打开系统 振荡器

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

RAM Mapping 32´4 LCD Controller for I/O mC

Features

· Operating voltage : 2.4V~5.2V · Built-in 256kHz RC oscillator · External 32.768kHz crystal or 256kHz

48 S E G 8 47 S E G 9 46 S E G 10 45 S E G 11 44 S E G 12 43 S E G 13 42 S E G 14 41 S E G 15 40 S E G 16 39 S E G 17 38 S E G 18 37 S E G 19 36 S E G 20 35 S E G 21 34 S E G 22 33 S E G 23 32 S E G 24 31 S E G 25 30 S E G 26 29 S E G 27 28 S E G 28 27 S E G 29 26 S E G 30 25 S E G 31

SEG 7 1 SEG 6 2 SEG 5 3 SEG 4 4 SEG 3 5 SEG 2 6 SEG 1 7 SEG 0 8

CS 9 R D 10 W R 11 D A TA 12 V S S 13 O S C O 14 O S C I 15 V LC D 16 V D D 17 IR Q 1 8 B Z 19 B Z 20 C O M 0 21 C O M 1 22 C O M 2 23 C O M 3 24

5

July 26, 1999

HT1621

Pad Description

Pad No. Pad Name

1

CS

2

RD

3

WR

4

DATA

5

VSS

பைடு நூலகம்

7

OSCI

6

OSCO

8 9 10 11, 12 13~16 48~17

VLCD VDD IRQ BZ, BZ COM0~COM3 SEG0~SEG31

I/O

Function

1

48

2

47

3

46

4

45

5

44

6

43

7

42

8

41

9

40

10

39

11

38

12

37

13

36

14

35

15

34

16

33

17

32

18

31

19

30

20

29

21

28

22

27

23

26

24

25

H T1621 - 48 S S O P

SEG 8 SEG 9 S E G 10 S E G 11 S E G 12 S E G 13 S E G 14 S E G 15 S E G 16 S E G 17 S E G 18 S E G 19 S E G 20 S E G 21 S E G 22 S E G 23 S E G 24 S E G 25 S E G 26 S E G 27 S E G 28 S E G 29 S E G 30 S E G 31

SEG 7 SEG 9 S E G 11 S E G 13 S E G 15 S E G 17 S E G 19 S E G 21 S E G 23 S E G 25 S E G 27 S E G 29 S E G 31 COM 2

3

July 26, 1999

Pad Assignment

HT1621

S E G 15 S E G 14 S E G 13 S E G 12 S E G 11 S E G 10

SEG 9 SEG 8 SEG 7 SEG 6 SEG 5 SEG 4 SEG 3 SEG 2

SEG 1 SEG 0

CS

1 48 47 46 45 44 43 42 41 40 39 38 37 36 35 34 33

T o n e F re q u e n c y G e n e ra to r

W a tc h d o g T im e r and

T im e B a s e G e n e r a to r

COM 0 COM 3 SEG 0

S E G 31 V LC D

IR Q

Notes:

CS: Chip selection BZ, BZ: Tone outputs WR, RD, DATA: Serial interface COM0~COM3, SEG0~SEG31: LCD outputs IRQ: Time base or WDT overflow output

pad, the data and command transmission between the host con-

troller and the HT1621 are all enabled.

READ clock input with pull-high resistor Data in the RAM of the HT1621 are clocked out on the falling I edge of the RD signal. The clocked out data will appear on the DATA line. The host controller can use the next rising edge to latch the clocked out data.

S E G 29 S E G 30 S E G 31 COM 3 COM 2 COM 1 COM 0

BZ

BZ

IR Q

Chip size: 127 ´ 129 (mil)2 * The IC substrate should be connected to VDD in the PCB layout artwork.

Chip selection input with pull-high resistor

When the CS is logic high, the data and command read from or

I

written to the HT1621 are disabled. The serial interface circuit is also reset. But if CS is at logic low level and is input to the CS

Selection Table

HT162X HT1620 HT1621 HT1622 HT16220 HT1623 HT1625 HT1626 HT1627 HT16270

COM

4

4

8

8

8

8

16

16

16

SEG

32

32

32

32

48

64

48

64

64

Built-in Osc.

Ö

Ö

Ö

Ö

Ö

Ö

Crystal Osc. Ö

6.33 12.96 19.59 58.14 58.14 58.14 58.14 58.14

Y

59.46 22.18 15.56 5.36 -4.51 -11.14 -34.76 -41.90 -49.13 -59.08 -59.08 -59.08 -59.08 -59.08 -59.08 -59.08 -59.08 -59.08 -59.08 -58.44 -51.81 -45.18 -38.55 -31.92

RD 2 WR 3

D ATA 4

(0 ,0 )

VSS 5

O SCO 6

O SCI 7 V LC D 8

VDD 9

10

11

12

13 14 15 16 17 18 19

32 S E G 16 31 S E G 17 30 S E G 18 29 S E G 19 28 S E G 20 27 S E G 21 26 S E G 22 25 S E G 23 24 S E G 24 23 S E G 25 22 S E G 26 21 S E G 27 20 S E G 28

H T1621B - 4 8 S S O P /D IP

HT1621

SEG 5 SEG 3 SEG 1

CS RD WR D ATA VSS V LC D VDD IR Q BZ COM 0 COM 1

1

28

2

27

3

26

4

25

5

24

6

23

7

22

8

21

9

20

10

19

11

18

12

17

13

16

14

15

H T1621D - 2 8 S k in n y

4

July 26, 1999

Pad Coordinates

Pad No.

1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24

X

-55.04 -58.52 -58.52 -58.52 -58.52 -58.52 -58.52 -58.52 -58.52 -58.52 -44.07 -31.58 -20.70 -13.98 -7.05 -0.34

instructions · R/W address auto increment · Three data accessing modes · VLCD pin for adjusting LCD operating

voltage

General Description