CMOS集成电路电流源负责的差分放大器

模拟cmos集成电路设计拉扎维第4章差分放大器

Rin =

RD + rO

RD

+1

1 + ( g m + g mb )rO ( g m + g mb )rO g m + g mb

R = {[1 + (g + g )r ]R + r } || R 路漫漫其修远兮,

吾将上下而求索

out

m

mb o S

o

D

西电微电子学院-董刚-模拟集成电路设计

11

上一章

西电微电子学院-董刚-模拟集成电路设计

5

上一章

二极管接法的MOS 管做负载的共源级

线性度好,输出摆幅小,增益不能太大(否 则摆幅小、带宽小)

Av =

路漫漫其修远兮, 吾将上下而求索

(W / L)1 1

(W / L)2 1 +

Av =

n (W / L ) 1 p (W / L ) 2

西电微电子学院-董刚-模拟集成电路设计

6

上一章

电流源做负载的共源级

增益大

路漫漫其修远兮, 吾将上下而求索

Av = m ro1 || ro2

西电微电子学院-董刚-模拟集成电路设计

7

上一章

深线性区MOS管做负载的共源级

输出摆幅大(可以为VDD)

得到精准的Ron2比较困难;受工艺、温度变 化影响比较大,产生稳定、精确的Vb比较 难

路漫漫其修远兮, 吾将上下而求索

=

g mR D

路漫漫其修远兮, 吾将上下而求索

1 + g mR S

西电微电子学院-董刚-模拟集成电路设计

9

上一章

共漏级-源跟随器

Rin大,Rout小,输出摆幅 小,增益有百分之几非线性; PMOS管能消除体效应,提高 线性度,但输出阻抗大,带宽 降低;电压缓冲器、电压平移

CMOS模拟集成电路设总复习

I VT ln(n) R1

Vout

mR2 R1

VT

ln(n) VEB3

Vout 2 ln(n) k VEB3 2m ln(n) 8.67 102 2.2 0

T

q T

只要满足右式的所有m,n均可 mln(n) 12.7

知识点

1.MOS器件原理 2.电流镜 3.带隙基准 4.反相器(三种类型) 5.差分放大器 6.共源共栅放大器 7.输出放大器 8.运算放大器

0.7

0.91V

M1饱和:VDS1 VGS1 VT

Vb VGS2 VGS1 VT

Vb VGS1 VGS2 VT

2I REF

K ' (W / L)2

2I REF K '(W / L)1

VT

2 0.1103

2 0.1103

110106 40 0.7 110106 40

1.11V

例题

L

COX

OX

tOX

K': 跨导参数

K ' COX 0

MOS管的大信号模型

饱和区电流(以NMOS为例):

iD

K'

W 2L

(vGS

VT

)2

线性区电流(以NMOS为例):

iD

K'W L

[(vGS

VT

)

( vDS 2

)]vDS

PMOS的饱和区和线性区电流表达式?

小信号模型

MOS管的小信号模型

输出电阻

VSG3 VDD VICmax VTN 2.5 2 0.7 1.2

VSG3

K 'P

2ID (W /

L)3

| VTP

| 1.2

模拟CMOS集成电路设计第四章差分放大器分解

模拟CMOS集成电路设计第四章差分放大器分解差分放大器是CMOS集成电路设计中非常重要的一部分,它在电信号放大、差分信号处理和模拟信号传输等领域具有广泛的应用。

本文将对CMOS集成电路设计中的差分放大器进行分解,以帮助读者更好地理解和应用这一核心电路模块。

差分放大器是一种由两个输入端和一个输出端组成的放大器,它的特点是能够放大两个输入信号的差值,并抑制共模信号(即两个输入信号的平均值)。

差分放大器常用的两种结构是共源共栅结构和共源共栅共源共栅结构。

下面将详细介绍这两种结构的分解方法。

1.共源共栅结构的分解共源共栅结构的特点是输入信号通过共源极放入电路,输出信号通过共栅极输出。

它的优点是输入电阻高、增益稳定,适用于高频和宽频带应用。

首先,我们来看一下共源共栅结构的电路原理图。

它由一个共源极M1、一个共栅极M2和一个负载电阻RL组成。

其中,M1的栅、漏极与输入信号相连,M2的源极与M1的源极相连,并通过电流源IB偏置。

负载电阻RL连接在M2的漏极和M1的源极之间。

接下来,我们对这个电路进行分解。

首先,将M1和M2的直流工作点确定。

假设输入信号为微弱的交流信号,可以将M1和M2视为理想可变电阻,其中M1的栅极和漏极之间的电压为vgs1,M2的栅极和源极之间的电压为vgs2、根据共源共栅和平衡电流假设,可以得到:id1 = id2 = id/2gm1vgs1 = gm2vgs2其中,id为分配给两个MOS管的总漏源电流,gm1和gm2分别为M1和M2的跨导。

然后,通过公式计算共源共栅结构的增益,可以得到:Av = -gm2RL最后,在进行差分模式和共模模式的分析。

差分模式下,输入信号为vcm-vd,其中vcm是共模信号,vd是差模信号。

共模模式下,输入信号为(vcm1+vcm2)/2、根据共模模式下输出电流为零的条件,可以得到共模抑制比CMRR与差分增益Av的关系为CMRR = Av/2gm.2.共源共栅共源共栅结构的分解共源共栅共源共栅结构是一种衍生自共源共栅结构的放大器,它包含两对共源共栅结构,具有更高的增益和更稳定的工作特性。

集成电路运算放大器-电流源-差分放大电路

Avd = −

β ( Rc // rbe

1 RL ) 2

PDF 文件使用 "pdfFactory Pro" 试用版本创建

3. 主要指标计算 (1)差模情况

<B> 双入、单出 Avd1

vo1 vo1 = = v id 2vi1

差分式放大电路对共模信号有很强抑制作用

PDF 文件使用 "pdfFactory Pro" 试用版本创建

3. 主要指标计算 (1)差模情况

<A> 双入、双出

vo1 − vo2 vo = Avd = vi1 − vi2 vid 2vo1 βR =− c = rbe 2vi1

2. 抑制零点漂移原理 温度变化和电源电压波 动 , 都 将 使 集电极电 流 产 生 变 化 。 且 变 化趋势是相 同的, 其 效果相当 于 在 两 个 输入端加入了共模信号。

PDF 文件使用 "pdfFactory Pro" 试用版本创建

2. 抑制零点漂移原理

6.1 集成电路运算放大器中的电流源

在模拟集成电路中,广泛地使用电流源,为放大电路 提供稳定的偏置电流,或作为放大电路的有源负载。

• 镜像电流源 • 微电流源 • 多路电流源 • 电流源用作有源负载

PDF 文件使用 "pdfFactory Pro" 试用版本创建

6.1.1 BJT电流源电路

PDF 文件使用 "pdfFactory Pro" 试用版本创建

PDF 文件使用 "pdfFactory Pro" 试用版本创建

6.1.2 FET电流源

模拟集成电路设计基础62MOS电流源及CMOS运算放大器

❖

2) 设计举例

❖

已知下列条件:

❖ ·Ir=10 μA, Io1=5 μA, Io2=20 μΑ, 电源电 压UDD=3.3 V;

❖ ·已知KN=μnCox=17 μΑ/V2, UTH=0.9 V;

❖ ·1 μm工艺。

❖ 试设计一个如图 6 - 2 所示的恒流源电路。

表 6 - 1 各MOS管的尺寸

6.1 引 言

❖

随着微电子技术和计算机技术的发展,

数字化已成为信号处理的主流技术, 显示出

越来越多的优越性。 那么, 是否模拟信号处

理从此变成无用的技术而被数字技术全部代

替了呢? 事实并不是这样的, 模拟技术在某

些领域反而“热”了起来, 这是因为:

❖

·自然界的物理量绝大部分都是以

模拟量的形式呈现的, 如电、 磁、 光、

❖ 6.2.2 CMOS运算放大器

❖

1. MOS管有源负载放大器

❖

为了增大增益, 避免集成电路

制造大电阻, 往往采用有源负载。 由于

NMOS管的性能优于PMOS管, 所以放

大管都用NMOS, 而负载管可用增强型

NMOS管、 耗尽型NMOS管和PMOS管,

后者构成互补型CMOS放大器。 差分放

大器有其独特的优点, 所以有源负载

(μn、 Cox相同, UTH相同), 栅源电压也 相同, 所以

Io1 Ir

I D1 Ir

W1 W0

/ /

L1 L0

1 1

U DS1 U DS 0

(6 - 3)

如果UDS1≈UDS0, 或沟道调制效应很弱 , 那么

1 UA

0

Io1 W1 / L1 1

(6 - 4)

恒流源及CMOS差分放大器原理及电路分析

U

EE

IC1Q

IC 2Q

1 2

I

I

IC3

IE3

U R2

U BE R3

UCE1Q UCE2Q UCC U BE IC1Q RC

一.带恒流源差分电路的信号放大性能分析

共模输出电压 uoc=0

一.带恒流源差分电路的信号放大性能分析

一.带恒流源差分电路的信号放大性能分析

[例3] 信号由单边输入(Ui2=0),其它条件不变.

一.带恒流源差分电路的信号放大性能分析

一种用单管电流源代替RE的差动放大电路如图所

示。

RC

RC UCC

RC

RC UCC

Ui1

- Uo1 + Uo

Uo2

V1

V2

Ui2

V3 UB3 R1

简化 电路

- Ui1

Uo1 + Uo

Uo2

V1

V2

Ui2

I Ro

R3

R2 -UEE

-UEE

U R2

R1

R2 R2

cmos差差分电路的信号放大性能分析2共模电压增益12iiicuu?u所以共模输出电压uoc0共模电压增益auc0共模抑制比kcmr结论cmos差分电路虽然为单端输出但差模增益及共模抑制比与双端输出相同这称为恒流源有源负载的单端化功能

恒流源及CMOS差分放大器 原理及电路分析

您清楚吗?

<<西电丝路云课堂>>

小结:

[例4]电路在各自射极增加一个负反馈小电阻r,

各项指标有何变化?

一.带恒流源差分电路的信号放大性能分析

[例5]有源负载差分放大器分析

CMOS 模拟集成电路课件-差分放大器

21

• 6.5.3 采用MOS电流镜负载的差分对

• 大信号分析

– 当vD足够负,M1关断,没有电流流经晶体管M1,因此M3 关断,M4也关断。由于没有电流流经M4,M2和M5都工 作在深线性区,vDS2 ≈ 0,vDS5≈ 0,因此,vOUT ≈ 0;

– 当vIN1变化到与vIN2接近时,M1管导通,使得尾电流源的 电流ID5一部分流经M3,并且使M4开启,vOUT开始上升.

vIN1 (单位V)

vIN,CM=1.5V

vIN,CM=2V

2020/5/6

偏置电流和输出电平受VIN,CM影响!

6

• “差分对”

6.3 基本差分对

ID1+ID2独立于VIN,CM 如果vIN1=vIN2, ID1=ID2=ISS/2, 输出共模电平为VDD-RISS/2

2020/5/6

7

6.3 基本差分对

iD1

ISS 2

4

vD

4ISS

vD2

nCox (W / L)

iD2

ISS 2

4

vD

4ISS

vD2

可以得到最大差分电压范围,

| vD |≤

2ISS

| vD |≤

2

2iD1,2

2VOD1,2

当vIN1=vIN2,

gm

(iD1 iD2 ) vD

vD 0

则差分增益

ISS

2nCox

W L

ISS 2

• 当vD为正时,流经M1管的电流大于流经M2管的电流,vOUT1

将小于vOUT2。对于足够正的vD,所有ISS都流经M1,此时,

2020/5/6

vOUT1 = VDD – RiD1 = VDD – RISS,而vOUT2 = VDD.

cmos 差分放大电路 镜像电流源 -回复

cmos 差分放大电路镜像电流源-回复文章标题:CMOS差分放大电路及镜像电流源详解引言:在现代电子领域中,差分放大电路凭借其优异的抗干扰能力和放大性能而得以广泛应用。

而在CMOS技术中,镜像电流源担当着重要的角色,为差分放大电路的正常工作提供了稳定的电流源。

本文将详解CMOS差分放大电路和镜像电流源的工作原理和设计技巧。

一、差分放大电路的基本原理差分放大电路主要由两个输入端和一个输出端组成,分别为非反相输入端(+)和反相输入端(-),通过放大两个输入信号的差值实现输出信号的放大。

其基本原理如下:1. 输入双极性:差分放大电路具有对称的输入,能够同时接收正负极性的信号。

2. 共模抑制比(CMRR)高:差分放大电路可以有效抑制输入信号的共模干扰,并放大差模信号。

3. 抗干扰能力强:差分放大电路能够抵御来自外部环境的电磁干扰和噪声。

二、CMOS差分放大电路的结构CMOS(互补金属氧化物半导体)技术是制造集成电路的常用技术之一,在差分放大电路中也广泛应用。

CMOS差分放大电路由一对互补MOS场效应晶体管(NMOS和PMOS)构成,其结构如下:- 输入级:由一对NMOS和PMOS晶体管组成,通过这对晶体管构成差分输入。

- 中间级:由一对PMOS和NMOS晶体管构成,起到放大差模信号和抑制共模信号的作用。

- 输出级:由PMOS和NMOS晶体管组成,输出受中间级放大的信号。

三、CMOS差分放大电路的工作原理CMOS差分放大电路的工作原理如下所述:1. 输入信号传输:通过差分输入级的NMOS和PMOS晶体管,将输入信号转换为电流信号。

2. 中间级放大:差分信号经过中间级的PMOS和NMOS晶体管放大,并通过并联的电容实现阻隔直流分量。

3. 输出信号形成:经过输出级的PMOS和NMOS晶体管放大的差分信号,形成最后的输出信号。

四、镜像电流源的作用镜像电流源在CMOS差分放大电路中起到了稳定输入电流的作用。

在差分放大电路中,使用镜像电流源可以确保输入级的工作电流恒定,并且提供了高的抗干扰能力。

CMOS集成电路设计-拉扎维4 差分放大器解析

2

又V01-V02=RD △ID = RD Gm △Vin,故 平衡态下的小信号差动电压增益AV为:

ISS A V = βISS R D = 2β( )R D 2

差动放大器 Ch.4 # 34

差分放大器的增益

ΔID 2ISS -βΔVin Gm = = ΔVin 4ISS 2 -ΔVin β V01 - V02 ISS AV = = βISS R D = 2β( )R D Vin1 - Vin2 2

M1和M2线性

Ι ISS SS + Vb VinCM VDD R D + VTN β 2 1(2)

共模输入电压与输出摆幅

M1饱和要求: VX ≥ VinCM - VTN

X Y

上式表明, 输入共模电平越大,Vx 越大, 允许输出的输出摆幅就 越小。幸运的是, 因运放通常需 至少两级放大才能获得实际可 使用的放大倍数, 因此对前级的 摆幅要求大大降低。

Vin1和Vin2是差动相位信号

• 当Vin1和Vin2存在很大的 共模干扰

• 各自的直流电平设置的 不好时, 随着共模电平 VinCM变化, M1 和M2的 偏置电流会变化

简单差动电路

共模电平VinCM变化, M1 和 M2的偏置电流会变化, 导致 跨导和输出共模电平变化 跨导变化会改变小信号增益, 输出共模电平偏离会降低最 大允许输出摆幅, 导致输出端 出现严重失真 应使M1 和M2偏置电流受输 入共模电平的影响尽可能小

– Rs使Gm和增益变为gm的弱函数,提高线性度 – 输出电阻大

ROUT [1 (gm gmb )ro ]RS ro

– 牺牲了增益

gmRD RD Av 1 g mRS 1 / g m RS

CMOS模拟电路基本单元

i

VGS

VT

2

rout

1 gm

7

有源电阻分压电路及并联电阻

8

三、电流源和电流沉

电流沉与电流源电路是两端元件,其电流值受栅电压控制, 和加在MOS两端的电压无关。 一般来说,电流沉的负端电压接VSS,而电流源的正端电 压接Vdd。

MOS工作在饱和区。

V VMIN Vg VTN VSS

AV g m1 RD

28

六、CMOS差分放大器

在现代模拟集成电路设计中,CMOS差分放大器是一种应用非常广泛 的子电路; 差分放大器只对两个不同电压的差进行放大而不管其共模值 ; 在CMOS差分放大器中,最严重的是电压失调,其主要由MOS晶体管 尺寸的不匹配性及工艺偏差等因素造成的; 如果将差分放大器的两个输入端连在一起,在输出端所测到的电压为 输出失调电压。如果将这个电压除以放大器的差分电压增益,所得到 的失调电压称为输入失调电压; 在实际集成电路设计中,一般将直接测到的输出失调电压称为失调电 压,CMOS差分放大器的失调电压一般为2~20mV ;

电流源输出电阻提高技术

11

电流源输出电阻提高技术——Cascode

12

四、电流镜(电流放大器)

基本原理:如果两个NMOS(PMOS)的栅源电压相同,则沟道电流 13 也相同。

NMOS基本电流镜电路及特性

(1)输出输入电流比值是MOS晶体管尺寸的比例关系,完 全由集成电路设计人员控制; (2)当NMOS处于饱和态工作时,输出电流是随着VDS2的增 14

如果输入电流保持不变,当输出电流增加时,M3的栅电压减小,抑制 输出电流增加,所以保持了输出电流的恒定性

cmos放大器原理

cmos放大器原理

CMOS放大器是一种基于互补金属-氧化物-半导体(CMOS)

技术设计的放大器。

这种放大器可以在集成电路中实现,并且具有低功耗、高增益和广泛的应用范围。

CMOS放大器的原理是利用N沟道和P沟道两种类型的MOS

管来构成放大电路。

它由一个差分对和输出级组成,其中差分对接收输入信号,输出级将放大后的信号输出。

在差分对中,两个NMOS管和两个PMOS管组成了一个差分

放大器。

差分对的输入直流电平由输入共模电压确定,差分输入信号的变化将导致输出电压的非线性响应。

差分对的输出信号被送入一个共源放大器,这个放大器由一个NMOS管和一个PMOS管组成。

这个放大器对输入信号进行

进一步放大,并提供一个高输入阻抗,使其可以驱动后级负载。

在输出级,一个共源共排放大器被用来进一步放大信号,并提供适当的输出阻抗。

这个放大器由一个PMOS管和一个

NMOS管组成,其中PMOS管负责输出信号的放大,NMOS

管负责提供电流放大。

最终,输出信号由这个共源共排放大器输出。

需要注意的是,CMOS放大器需要一个稳定的直流工作点来

确保放大器的线性响应和稳定性。

为了实现这个目标,通常需要引入偏置电路来提供合适的直流偏置电压。

总之,CMOS放大器通过利用CMOS技术的特点,在集成电路中实现了高度集成和低功耗的放大功能。

它的原理是基于差分放大器和共源共排放大器的组合,使得它成为现代电子设备中不可或缺的关键组件。

恒流源及CMOS差分放大器原理及电路分析

V1

V2

Ui2

I Ro

R3

R2 -UEE

-UEE

U R2

R1

R2 R2

U

EE

IC1Q

IC 2Q

1 2

I

I

IC3

IE3

U R2

U BE R3

UCE1Q UCE2Q UCC U BE IC1Q RC

一.带恒流源差分电路的信号放大性能分析

共模输出电压 uoc=0

一.带恒流源差分电路的信号放大性能分析

三. CMOS差分电路的信号放大性能分析

(2) 共模电压增益

ui1= ui2 uic

所以,共模输出电压uoc=0,共模电压增益Auc=0,

共模抑制比KCMR=∞ [结论] CMOS差分电路虽然为单端输出,但差模增益及共模抑制比与

双端输出相同这称为恒流源有源负载的”单端化”功能.因为负载管为 PMOS,衬底可直接接源极,在集成电路中十分方便,故CMOS差分电路 在集成电路中应用极广.

一.带恒流源差分电路的信号放大性能分析

[例3] 信号由单边输入(Ui2=0),其它条件不变.

小结:

[例4]电路在各自射极增加一个负反馈小电阻r,

各项指标有何变化?

一.带恒流源差分电路的信号放大性能分析

[例5]有源负载差分放大器分析

二.场效应管差分电路的信号放大性能分析

I

[解]

电路由结型场效应差分对管构成, 由双极型管组成镜像电流源提供

恒流源及CMOS差分放大器 原理及电路分析

您清楚吗?

<<西电丝路云课堂>>

一.带恒流源差分电路的信号放大性能分析

cmos模拟集成电路设计-实验报告

cmos模拟集成电路设计-实验报告————————————————————————————————作者:————————————————————————————————日期:北京邮电大学实验报告实验题目:cmos模拟集成电路实验姓名:何明枢班级:2013211207班内序号:19学号:2013211007指导老师:韩可日期:2016 年 1 月16 日星期六目录实验一:共源级放大器性能分析 (1)一、实验目的 (1)二、实验内容 (1)三、实验结果 (1)四、实验结果分析 (3)实验二:差分放大器设计 (4)一、实验目的 (4)二、实验要求 (4)三、实验原理 (4)四、实验结果 (5)五、思考题 (6)实验三:电流源负载差分放大器设计 (7)一、实验目的 (7)二、实验内容 (7)三、差分放大器的设计方法 (7)四、实验原理 (7)五、实验结果 (9)六、实验分析 (10)实验五:共源共栅电流镜设计 (11)一、实验目的 (11)二、实验题目及要求 (11)三、实验内容 (11)四、实验原理 (11)五、实验结果 (15)六、电路工作状态分析 (15)实验六:两级运算放大器设计 (17)一、实验目的 (17)二、实验要求 (17)三、实验内容 (17)四、实验原理 (22)五、实验结果 (23)六、思考题 (24)七、实验结果分析 (25)实验总结与体会 (26)一、实验中遇到的的问题 (26)二、实验体会 (26)三、对课程的一些建议 (27)实验一:共源级放大器性能分析一、实验目的1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法;2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真;3、输入共源级放大器电路并对其进行DC、AC分析,绘制曲线;4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响二、实验内容1、启动synopsys,建立库及Cellview文件。

cmos模拟集成电路设计基础

cmos模拟集成电路设计基础CMOS模拟集成电路(Complementary Metal-Oxide-Semiconductor Analog Integrated Circuit)是一种基于CMOS技术的模拟电路集成化设计。

以下是CMOS模拟集成电路设计的基础知识:1.CMOS技术:CMOS是一种集成电路制造技术,其中包含两种类型的晶体管:NMOS(N型金属氧化物半导体)和PMOS(P型金属氧化物半导体)。

通过将NMOS和PMOS 晶体管结合,可以实现低功耗、高集成度和高性能的模拟集成电路设计。

2.基本元件:CMOS模拟集成电路设计中使用的基本元件包括晶体管、电容器和电阻器。

NMOS和PMOS晶体管用于实现放大和开关功能,电容器用于存储电荷和控制频率响应,电阻器用于调整电路的工作条件。

3.偏置电路:CMOS模拟集成电路中的偏置电路用于提供恒定和稳定的电流或电压。

它包括电流镜(Current Mirror)电路和电压源(Voltage Reference)电路。

这些电路通过调整电流和电压的偏置,使电路在不同工作条件下具有可靠的性能。

4.放大电路:CMOS模拟集成电路中的放大电路用于增强输入信号的幅度。

放大电路通常由差分放大器(Differential Amplifier)和级联的共尺寸(Common-Source)放大器组成。

放大电路的设计需要考虑输入电阻、增益、带宽和稳定性等因素。

5.反馈电路:CMOS模拟集成电路中的反馈电路用于控制电路的增益和稳定性。

反馈电路通过将一部分输出信号反馈到输入端,调整输入和输出之间的关系,实现精确的控制和稳定性。

6.输出级:CMOS模拟集成电路的输出级用于驱动负载并提供所需的电流或电压。

输出级通常包括驱动电路和输出级晶体管。

7.噪声和功耗:在CMOS模拟集成电路设计中,需要注意噪声和功耗的控制。

减小噪声可以通过优化偏置电路和减小环境干扰来实现。

降低功耗可以通过优化电路结构、选择合适的电源电压和电流等方式来实现。

cmos放大器的原理

cmos放大器的原理CMOS放大器是一种常见的集成电路,用于放大输入信号。

它由CMOS晶体管组成,可以带来很高的增益和稳定性。

本文将详细解释CMOS放大器的原理、工作模式和设计。

一、CMOS放大器的原理CMOS放大器的核心是差分对,它由两个对称的晶体管组成。

当输入电压V1和V2不同时,晶体管的输出差异将被放大并转换成单端输出。

这个特性是因为,采用CMOS技术可以非常容易地控制晶体管的电阻。

在差分对中,输入电压被分成两个相等的信号,并接到晶体管的栅极上。

这时,晶体管会形成一个半导体开关,输出电压将从高电平到低电平高速切换。

另一端晶体管的输出与这个相反。

将两端输出连接在一起,就可以得到一个差分放大器。

二、CMOS放大器的工作模式CMOS放大器的工作模式有两种,共源极和共基极。

共源极放大器是CMOS放大器最常见的形式。

输入信号在栅极上放大,通过源级和负载电阻传送到输出。

由于输出电压与输入电压的差异,差分对被激活并且通过放大器放大。

共基极放大器则是将整个差分对的晶体管作为输入端点的一部分。

与共源极不同,共基极放大器的输入级仅由一个晶体管构成。

三、CMOS放大器的设计总体设计策略是,利用差分对提供的放大器来增加电路电压增益。

这种策略可以被应用于各种不同的放大器拓扑结构,并且是实现CMOS 放大器硅片上集成的必要条件。

CMOS放大器设计的关键要素是电压增益、带宽和线性度。

其中,单个差分对的增益会受到固有的部分值限制。

该限制可以通过增加放大器中差分对的数量来克服。

要达到较大的带宽,则需要通过设置适当的负载来调整带宽。

在线性度方面,CMOS放大器可以通过降低电源电压来提高线性度。

低电源电压会降低放大器的动态范围,但同时会减少非线性失真。

总的来说,CMOS放大器是一种可靠的放大器设计。

它的优点是低电源电压、低功耗和高带宽。

由于CMOS放大器扩展到集成电路,它已成为低成本和可大规模生产的最佳选择。

模拟CMOS集成电路设计第四章差分放大器剖析

模拟CMOS集成电路设计第四章差分放大器剖析第四章差分放大器是模拟CMOS集成电路设计中的重要内容。

差分放大器是一种基本的电路结构,用于放大差分信号,具有功率增益高、抗干扰能力强等特点。

在本章中,将对差分放大器的原理、结构以及常用的设计方法进行剖析。

差分放大器的基本原理是利用两个互补的输入信号来放大差分信号,以提高共模信号的抵抗能力。

其硅上集成电路结构是由两个互补的差分对称结构组成,输入端与输出端相互交错连接。

在输入端,通过两个电流源提供定电流给差分对称结构,从而形成了输出端的差分输出信号。

通过合理的电路设计和调整输入电流、电压等参数,可以实现差分放大器的不同功能和性能。

差分放大器的结构主要由输入级、中间级和输出级组成。

输入级主要起到放大差分信号的作用,输入对称性好,起到抵消共模信号的作用。

中间级是为了提高放大倍数和频率响应而设计的,起到归一化和驱动输出级的作用。

输出级是为了放大电流而设计的,输出电流只与力度源的电流有关,可以通过调整力度源的电流大小来改变输出电流。

在差分放大器的设计中,需要注意一些关键的参数和指标。

其中,差分增益是指输入差分信号与输出差分信号之间的比例关系,一般用dB来表示。

共模抑制比是指在输入信号中存在共模信号时,输出信号中共模信号的相对衰减程度,一般用dB来表示。

输入偏置电流是指输入电流偏离理想值的程度,一般用nA级别来表示。

输入电阻和输入电容是指输入端对于差分信号和共模信号的阻抗和容性,一般用Ω和F来表示。

在差分放大器的设计中,可以采用多种方法来实现不同的功能和性能。

例如,可以通过引入电流源、电阻、电容等器件来调整放大倍数和频率响应。

可以通过选择不同的电流源来改变差分放大器的工作模式,例如共基极模式、共射极模式等。

可以通过串联和并联电阻、电容等元件来调整放大器的输入和输出阻抗。

可以通过使用不同的差分对称结构来实现不同的特性,例如双极性、互补型等。

综上所述,差分放大器是模拟CMOS集成电路设计中的重要内容。

CMOS两级运算放大器设计

CMOS两级运算放大器设计CMOS(互补金属氧化物半导体)两级运算放大器是一种常用的放大器设计,可以用于信号放大、滤波、放大器链路等应用。

本文将对CMOS两级运算放大器的设计进行详细叙述。

首先,设计CMOS差动对。

差动对由两个MOSFETs组成,其中一个为p-MOSFET,另一个为n-MOSFET。

这两个MOSFETs的栅极交叉,源极相连,并接入一个电流源。

这样可以使输入信号以差分模式进入放大器。

然后,设计CMOS差动对的偏置电路。

偏置电路主要是为了使CMOS差动对能够正常工作。

其中,主要包括两个电流源和一个电流镜。

电流源为差动对提供恒定电流,电流镜用于分配输入级和输出级的电流。

通过适当选择偏置电流的大小,可以控制放大器的增益和输出幅度。

接下来,设计中间电压增益级。

增益级主要由两个共尺极级组成,通过增加电阻、电容等元件来实现电压放大。

增益级的输出连接到输出级的输入,将中间电压信号传递到输出级进行电流差分放大。

最后,设计输出级。

输出级主要由两个MOSFETs组成,其中一个为p-MOSFET,另一个为n-MOSFET。

这两个MOSFETs的栅极相连,并连接到输入级的输出。

通过适当控制输出级电压的变化,可以实现电流信号的放大。

在CMOS两级运算放大器的设计过程中,需要考虑的因素包括放大器的增益、带宽、输入输出阻抗、偏置电流等。

根据具体的应用需求,可以平衡这些因素来进行合适的设计。

在设计完成后,需要进行电路仿真和调试。

可以使用软件工具如Spice来进行电路模拟,并根据模拟结果进行调整和优化。

在实际测试中,可以通过改变输入信号的频率和幅度,观察输出信号的响应,并与设计要求进行对比。

总结起来,CMOS两级运算放大器设计是一个复杂的过程,需要考虑多个因素,并进行合适的优化。

通过合理的设计和调试,可以获得满足设计要求的放大器电路。

模拟cmos集成电路设计拉扎维第4章差分放大器ppt课件

16

差分放大器

优点

抗干扰能力强,高线性度等 和单端电路相比,差分电路规模加倍

与获得的性能提高相比,这个不算做缺点

西电微电子学院-董刚-模拟集成电路设计

17

本讲

差分放大器简介 简单差分放大器 基本差分对放大器

大信号差分特性 大信号共模特性 小信号差分特性 小信号共模特性

MOS管做负载的基本差分对放大器 差分放大器的应用-Gilbert单元

西电微电子学院-董刚-模拟集成电路设计

12

本讲

差分放大器简介 简单差分放大器 基本差分对放大器

大信号差分特性 大信号共模特性 小信号差分特性 小信号共模特性

MOS管做负载的基本差分对放大器 差分放大器的应用-Gilbert单元

西电微电子学院-董刚-模拟集成电路设计

13

差分放大器简介

AIC中非常重要的电路模块 对两个信号的差值进行放大

(V X V )Y Vin 2引起的 = g m RDVin 2

西电微电子学院-董刚-模拟集成电路设计

36

小信号差分特性-用叠加法求全差分时的 差模增益

(VX V ) = Y Vin1引起的 gm RDVin1 (VX VY )Vin 2引起的 = gm RDVin2

(VX V ) = Y Vin1和Vin2共同引起的 gmRD (Vin1 Vin2 )

Rout

=

g

1 m+ g

mb

西电微电子学院-董刚-模拟集成电路设计

10

上一章

共栅级

Rin小,Rout大

Av = gm(1+ )RD

Rin = 1/[gm (1+ )]

Rin =

RD + rO

CMOS差分放大器

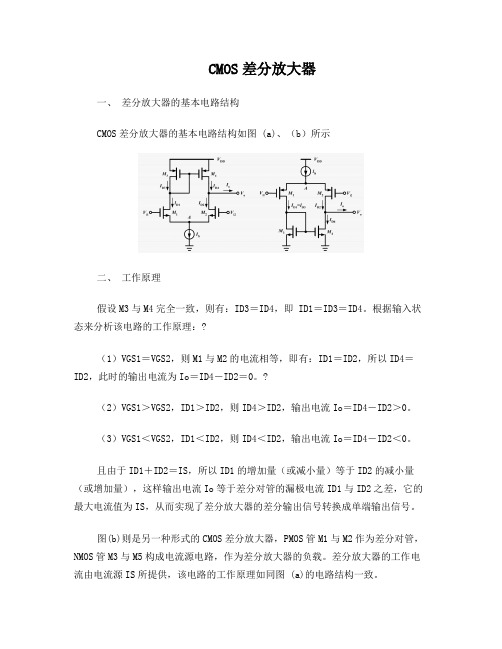

CMOS差分放大器一、差分放大器的基本电路结构CMOS差分放大器的基本电路结构如图 (a)、(b)所示二、工作原理假设M3与M4完全一致,则有:ID3=ID4,即 ID1=ID3=ID4。

根据输入状态来分析该电路的工作原理:?(1)VGS1=VGS2,则M1与M2的电流相等,即有:ID1=ID2,所以ID4=ID2,此时的输出电流为Io=ID4-ID2=0。

?(2)VGS1>VGS2,ID1>ID2,则ID4>ID2,输出电流Io=ID4-ID2>0。

(3)VGS1<VGS2,ID1<ID2,则ID4<ID2,输出电流Io=ID4-ID2<0。

且由于ID1+ID2=IS,所以ID1的增加量(或减小量)等于ID2的减小量(或增加量),这样输出电流Io等于差分对管的漏极电流ID1与ID2之差,它的最大电流值为IS,从而实现了差分放大器的差分输出信号转换成单端输出信号。

图(b)则是另一种形式的CMOS差分放大器,PMOS管M1与M2作为差分对管,NMOS管M3与M5构成电流源电路,作为差分放大器的负载。

差分放大器的工作电流由电流源IS所提供,该电路的工作原理如同图 (a)的电路结构一致。

三、电路分析——大信号分析以处于饱和区的NMOS管M0作为电流源。

转换特性(1) Vi1<<Vi2:M1截止,M3也截止,由于M4与M3完全相同,则M4截止,因此无电流从VDD中抽取,M2与M0工作在深线性区,电流也为 0,因此Vo=0。

?(2)当Vi1接近Vi2:M1导通,通过M3对ID0分流并使M4导通,则其输出电压依赖于ID4与ID2之间的差值。

对于Vi1与Vi2间差值很小时,M2、 M4饱和,产生了高增益,如图(b)所示,当Vi1大于Vi2时,ID1 、|ID3| 、|ID4|增大而ID2减小,最终驱动M4进入线性区。

?(3) Vi1>>Vi2:VGS2<Vth2,M2截止,M1、M3、M0饱和,M4工作于深线性区,并为零电流,故Vo=VDD。

差分放大器 cmos

学院模拟集成电路分析与设计题目:差分放大器院系:专业年级:学生姓名:学号:2012年12月8日差分放大器一,差分放大器的概况能把两个输入电压的差值加以放大的电路,也称差动放大器。

这是一种零点漂移很小的直接耦合放大器,常用于直流放大。

它可以是平衡(术语“平衡”意味着差分)输入和输出,也可以是单端(非平衡)输入和输出,常用来实现平衡与不平衡电路的相互转换,是各种集成电路的一种基本单元。

由两个参数特性相同的晶体管用直接耦合方式构成的放大器。

若两个输入端上分别输入大小相同且相位相同的信号时,输出为零,从而克服零点漂移。

适于作直流放大器。

差分放大器电路图,未显示偏置等电路差分放大器是一种将两个输入端电压的差以一固定增益放大的电子放大器,有时简称为“差放”。

差分放大器通常被用作功率放大器(简称“功放”)和发射极耦合逻辑电路 (ECL, Emitter Coupled Logic) 的输入级。

差分放大器是普通的单端输入放大器的一种推广,只要将差放的一个输入端接地,即可得到单端输入的放大器。

很多系统在差分放大器的一个输入端输入信号,另一个输入端输入反馈信号,从而实现负反馈。

常用于电机或者伺服电机控制,以及信号放大。

在离散电子学中,实现差分放大器的一个常用手段是差动放大,见于多数运算放大器集成电路中的差分电路。

下图为差分放大器电路图,未显示偏置等电路。

二,差分放大器举例差分放大器可以用晶体三极管(晶体管)或电子管作为它的有源器件。

输出电压u0=u01-u02,是晶体管T1和T2集电极输出电压u01和u02之差。

当T1和T2的输入电压幅度相等但极性相反,即us1=-us2 时,差分放大器的增益Kd(称差模增益)和单管放大器的增益相等,即Kd≈Rc/re,式中Rc=Rc1=Rc2,re是晶体管的射极电阻。

通常re很小,因而Kd较大。

当us1=us2 ,即两输入电压的幅度与极性均相等时,放大器的输出u0应等于零,增益也等于零。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

目录必做项目:与非门电路的设计一设计目的与指导二设计及过程分析三结果分析四体会五任务分工选做项目:电流镜负载的差分放大器设计一设计目的与要求二设计及过程分析三结果分析四体会五任务分工必做项目:与非门电路的设计一、设计目的与指导本项目要求基于csmc 0.35um 工艺,完成一个二输入与非门(2NAND)的电路设计。

设计要求如下:1、为了给顶层设计留出更多的布线资源,版图中只能使用金属1 和多晶硅作为互连线,输入,输出和电源、地线等pin 脚必须使用金属12、版图满足设计规则要求,并通过LVS 检查3、设计分析分析二输入与非门(2NAND)的电路,确定器件的宽长比。

设置华大九天环境启动 Aether建立自己的设计库用 Schematic Editor 画电路原理图形成符号图在 MDE 中进行电路仿真分析仿真结果,是否满足要求,若不满足要求,修正电路的参数,重新仿真。

4、版图设计用 Layout Editer 画版图利用 Aeolus 工具进行版图验证和提取DRC 规则检测LVS 检查5、Tape out增加焊盘等外围电路输出 GDSII 版图结果。

二设计及过程分析(一)电路原理图设计电路原理图由两个NMOS和两个PMOS组成。

两个PMOS并联,两个NMOS串联,然后将两个NMOS和两个PMOS串联起来。

最后加上相应的引脚(包括input、output、inputoutput),原理图如下图所示:在给5V电压时,对V0与V1进行直流仿真分析直到VOUT斜率变化最大值在2.5V左右。

不断调节管子宽长比,直至其满足要求,测得NMOS的W/L=0.8/0.5,PMOS的W/L=2/0.5.仿真图如下图所示(二)生成符号图在schematic editor工作界面,创建symbol view,生成符号图。

符号图如下图所示:符号图创建完成后,重新建立一个schematic editor,调用刚刚创建的符号图,并加上相应的输入信号,然后进行仿真,查看波形。

(三)版图设计打开最初的电路原理图,通过菜单栏的SDL创建版图Layout,然后进行版图的绘制,绘制过程中注意进行DRC验证。

版图完成并且DRC验证通过后,进行LVS验证,若验证不成功,多次改正知道验证成功。

版图如下图所示:三结果分析本次设计的最终结果是实现了一个二输入与非门的功能,功能如下:四体会必做项目是与非门电路的设计,这算比较简单的设计了,这是集成电路设计中基本的电路。

首先在开始前,做好充分的准备,尤其是理论知识是掌握,要对以前所学的知识有一个系统的了解,看到一个新问题要知道如何转化为学过的知识。

由于对这个电路比较熟悉,在画电路图和分析结果时遇到的问题都能够解决,问题不大。

主要是版图设计的时候问题多,通常是对版图设计不熟悉而不知道如何解决。

与非门电路的版图,虽然总体上电路比较简单,但是在版图的绘制过程之中还是要细心,注意工艺的最小线宽或者最小的距离的要求。

画图过程很考验耐心与细心程度,一不小心就要出差错。

所以在绘制过程中要细心。

在版图的布局中要注意布局的要求,尽量能够减小面积并且避免出错。

由于这次我们三个人团队工作,所以要分工。

当然,分工不是说只做这一部分,而且,如果对其他部分不了解,做自己的部分时候也会很困难。

我们每个队员都要对这个课程设计有一个宏观的了解和把握,知道自己负责的部分所处的阶段,对其他队员负责的部分要有一定的了解,然后对自己负责的部分花大工夫,保质保量,不拖沓,才能使项目顺利地进行。

五任务分工我们组三人,主要分工如下:根据原理图形成符号图,最后在 MDE 中进行电路仿真并分析结果。

:进行版图设计用 Layout Editer 画版图,利用 Aeolus 工具进行版图验证和提取,最后DRC 规则检测,LVS 检查。

:启动 Aether建立设计库,用 Schematic Editor 画电路原理图并完成实训报告。

选做项目:电流镜负载的差分放大器设计一 设计目的与要求设计一款差分放大器,要求满足性能指标:● 负载电容pF C L 2=● V VDD 5=● 对管的m 取4的倍数● 低频开环增益>100● GBW(增益带宽积)>25MHz● 输入共模范围>3V● 功耗、面积尽量小参考电路图如下图所示设计步骤:1、仿真单个MOS 的特性,得到某W/L 下的MOS 管的小信号输出电阻和跨导。

2、根据上述仿真得到的器件特性,推导上述电路中的器件参数。

3、手工推导上述尺寸下的差分级放大器的直流工作点、小信号增益、带宽、输入共模范围。

4、如果增益和带宽不符合题目要求,则修改器件参数,并重复上述计算过程。

5、一旦计算结果达到题目要求,用Hspice仿真验证上述指标。

如果仿真得到的增益和带宽不符合要求,则返回步骤2,直至符合要求二设计及过程分析据题目所述,电流镜负载的差分放大器的制作为0.35um CMOS工艺,要求在5v的电源电压下,负载电容为2pF时,增益带宽积大于25MHz,低频开环增益大于100,同时功耗和面积越小表示性能越优。

我们首先根据0.35um CMOS工艺大致确定单个CMOS的性能,即在一定值的W/L下确定MOS管在小信号模型中的等效输出电阻和栅跨导,然后记下得到的参数并将其带入到整体电路中计算,推导电流镜负载的差分放大器电路中的器件参数,例如,小信号模型的增益、带宽、功耗等,再分析是否满足题目中的各项指标的要求。

若不满足,则依据摘要理所说的,调节晶体管的宽度,然后用调整后的参数进行仿真、验证,直到符合要求为止。

2.电流镜负载差分放大电路分析与设计(一)电路原理图设计在不考虑沟道长度及体效应时,Av=gm3*(ro1//ro2)gm2=gm3=(2UnCoxW/LID2)1/2ID2=ID3=0.25mA =ID1=ID0UnCox=1.3405*10(-4)ro1和ro2 均可从网表中读取的gm1=676.6u gm3=1.2067m(W/L)M0,1 =10/1,(W/L)M2,3=9/1,(W/L)M4,5=2/1用两个PMOS管构成一个电流镜,作为差分电路的负载。

用两个NMOS管构成电流镜连接在Iref上。

然后加上相应的引脚,为后序生成符号图和版图做好准备。

如下图所示:(二)生成符号图并加上相应的输入信号,然后进行仿真,查看波形。

瞬态分析:直流分析:打开最初的电路原理图,通过菜单栏的SDL创建版图Layout,然后进行版图的绘制,绘制过程中注意进行DRC验证。

版图完成并且DRC验证通过后,进行LVS验证,若验证不成功,多次改正知道验证成功。

版图如下图所示:三结果分析hierarchy xi0 xi0 xi0 xi0 xi0device 1:mm0 1:mm1 1:mm2 1:mm3 1:mm4region Saturati Saturati Saturati Saturati Saturatiid -247.1656u -247.1656u 247.1656u 247.1656u 500.0000uibs 3.6994a 3.6994a -265.1234a -265.1234a -4.0746aibd 387.9501a 387.9501a -788.9777f -788.9777f -785.3774avgs -1.6490 -1.6490 1.6586 1.6586 2.1686vds -1.6490 -1.6490 2.0096 2.0096 2.1686vbs 0.0000 0.0000 -1.3414 -1.3414 0.0000vth -999.1591m -999.1591m 1.3070 1.3070 763.0809mvdsat -594.2612m -594.2612m 315.0436m 315.0436m 874.8337mvod -649.8448m -649.8448m 351.5394m 351.5394m 1.4055gm 676.6466u 676.6466u 1.2067m 1.2067m 564.1959ugds 10.4276u 10.4276u 5.1034u 5.1034u 4.1931ugmb 221.7669u 221.7669u 371.2275u 371.2275u 248.3114ucdtot 48.0864f 48.0864f 37.0387f 37.0387f 10.3659fcgtot 98.7657f 98.7657f 94.0683f 94.0683f 24.1734fcstot 164.8637f 164.8637f 124.8378f 124.8378f 37.6006fcbtot 126.6913f 126.6913f 84.1348f 84.1348f 27.9905fcgs 88.2701f 88.2701f 76.6250f 76.6250f 20.4368fcgd 8.1782f 8.1782f 10.7137f 10.7137f 2.6065fi1 -247.1656u -247.1656u 247.1656u 247.1656u 500.0000ui2 0.0000 0.0000 0.0000 0.0000 0.0000i3 -247.1656u -247.1656u 247.1656u 247.1656u 500.0000ui4 6.5964p 6.5964p -19.5590p -19.5590p -8.6752phierarchy xi0device 1:mm5region Saturatiid 494.3312uibs -4.0297aibd -100.0039avgs 2.1686vds 1.3414vbs 0.0000vth 763.5805mvdsat 874.5969mvod 1.4050gm 554.2542ugds 13.4333ugmb 244.9113ucdtot 11.1731fcgtot 24.2181fcstot 37.5983fcbtot 28.6691fcgs 20.4425fcgd 2.6653fi1 494.3312ui2 0.0000i3 494.3312ui4 -5.3659p四体会本次的集成电路课程设计使我们组受益匪浅。

一直以来我们已经深入的学习过《模拟电子技术基础》和《模拟CMOS集成电路》课程的理论知识了,但是对于实践方面的知识我们只在实验课上用过。

这次的实训,使我们学会将课堂上的纯理论灵活运用到生活。

刚看到题目时不知道从何下手。

然后开始看书,仔细的找相关的资料,看到底题目的用意是什么,幸好在课本上已经学过差分放大器。

我们了解了相关理论知识,便开始分工合作,进行手工分析,用 Schematic Editor 画电路原理图并进行仿真,随后就是版图设计,主要是这三个步骤,花了不少时间,设计过程中出现很多差错,不断改正,不断虚心请教,实在修改不了,让老师来指导。