计算机组成原理 实验4

计算机组成原理实验

计算机组成原理实验一、实验目的本实验旨在通过实际操作,加深对计算机组成原理的理解,掌握计算机硬件的基本原理和工作方式。

二、实验设备和材料1. 计算机主机:型号为XXX,配置了XXX处理器、XXX内存、XXX硬盘等。

2. 显示器:型号为XXX,分辨率为XXX。

3. 键盘和鼠标:标准配置。

4. 实验板:包括CPU、内存、存储器、输入输出接口等模块。

5. 逻辑分析仪:用于分析和调试电路信号。

6. 示波器:用于观测电路信号的波形。

三、实验内容1. 实验一:CPU的工作原理a. 将实验板上的CPU模块插入计算机主机的CPU插槽中。

b. 连接逻辑分析仪和示波器,用于观测和分析CPU的工作信号和波形。

c. 打开计算机主机,启动操作系统。

d. 运行一段简单的程序,观察CPU的工作状态和指令执行过程。

e. 通过逻辑分析仪和示波器的数据分析,了解CPU的时钟信号、数据总线、地址总线等工作原理。

2. 实验二:内存的存储和读写a. 将实验板上的内存模块插入计算机主机的内存插槽中。

b. 打开计算机主机,启动操作系统。

c. 编写一个简单的程序,将数据存储到内存中。

d. 通过逻辑分析仪和示波器的数据分析,观察内存的写入和读取过程,了解内存的存储原理和读写速度。

3. 实验三:存储器的工作原理a. 将实验板上的存储器模块插入计算机主机的存储器插槽中。

b. 打开计算机主机,启动操作系统。

c. 编写一个简单的程序,读取存储器中的数据。

d. 通过逻辑分析仪和示波器的数据分析,观察存储器的读取过程,了解存储器的工作原理和数据传输速度。

4. 实验四:输入输出接口的工作原理a. 将实验板上的输入输出接口模块插入计算机主机的扩展插槽中。

b. 打开计算机主机,启动操作系统。

c. 编写一个简单的程序,通过输入输出接口实现数据的输入和输出。

d. 通过逻辑分析仪和示波器的数据分析,观察输入输出接口的工作过程,了解数据的传输和控制原理。

四、实验结果分析1. 实验一:通过观察CPU的工作状态和指令执行过程,可以验证CPU的时钟信号、数据总线、地址总线等工作原理是否正确。

计算机组成原理实验4进位实验实验5移位实验

实验4 进位控制实验一、实验目的1. 理解带进位控制的电路图。

2.验证带进位控制的算术运算发生器的功能。

3.按给定数据,完成实验几种指定的算术运算。

二、实验原理1.在算术逻辑运算实验的基础上,增加了进位控制部分,进位控制部分电路。

它主要由一个74LS74锁存器构成。

2.AR是74LS74琐存器的控制信号,低电平有效,与T4脉冲信号配合,可打开琐存器,把74LS181运算的进位结果存入其内。

(3)CY是高位进位标志信号,连接一个发光二极光,能显示其进位情况。

当进位时此灯“亮”,无进位时指示灯“灭”。

具体电路见图4-1带进位运算器通路图。

图4-1带进位运算器通路图图4-1带进位运算器通路三、实验注意事项(1)本实验使用T4脉冲信号,实验时将“W/R UNIT”的T4接至“STA TE UNIT”中KK2的正脉冲冲插头上,按下微动开关KK2(可产生T4正脉冲),即可获得本实验所需的单脉冲信号。

(2)S3、S2、S1、S0、Cn、M、LDDR1、LDDR2、AUL-B、SW-B、AR均为电平信号,与“SWITCH UNIT”中的二进制开关对应相连接,用于产生模拟信号。

(3)ALU-B、SW-B为低电平有效;LDDR1,LDDR2为高电平有效。

(4)实验仪上进位指示灯CY为“亮”时,表示有进位,“灭”表示无进位。

(5)实验仪上ZI(zero indicator)是判零标志灯,当两片74LS181输出全为“0”时,ZI灯亮,当两片74LS181输出不全为“0”时,ZI灯灭。

(6)每次做进位操作前都必须先对进位标志清零。

清零后,注意观看实验仪上进位指示灯CY是否已灭,若清零后CY不灭,要检查原因。

(7)进位清零操作时,有关控制端的状态是:S3、S2、S1、S0、M、AR、LDDR1、LDDR2 置为00000000,然后按下微动开关KK2即可。

(8)做清零操作时,DR1寄存器的内容不能为11111111。

四、实验内容和步骤1. 实验连线实验连线图见图4-2:图4-2 带进位运算实验接线图接线完成后,检查无误,方可接通电源,要养成一个好习惯,通电前要细心检查电路,以防短路发生,造成实验设备的损坏。

计算机组成原理实验报告

计算机组成原理实验报告实验目的,通过本次实验,深入了解计算机组成原理的相关知识,掌握计算机硬件的基本组成和工作原理。

实验一,逻辑门电路实验。

在本次实验中,我们学习了逻辑门电路的基本原理和实现方法。

逻辑门电路是计算机中最基本的组成部分,通过逻辑门电路可以实现各种逻辑运算,如与门、或门、非门等。

在实验中,我们通过搭建逻辑门电路并进行实际操作,深入理解了逻辑门的工作原理和逻辑运算的实现过程。

实验二,寄存器和计数器实验。

在本次实验中,我们学习了寄存器和计数器的原理和应用。

寄存器是计算机中用于存储数据的重要部件,而计数器则用于实现计数功能。

通过实验操作,我们深入了解了寄存器和计数器的内部结构和工作原理,掌握了它们在计算机中的应用方法。

实验三,存储器实验。

在实验三中,我们学习了存储器的原理和分类,了解了不同类型的存储器在计算机中的作用和应用。

通过实验操作,我们进一步加深了对存储器的认识,掌握了存储器的读写操作和数据传输原理。

实验四,指令系统实验。

在本次实验中,我们学习了计算机的指令系统,了解了指令的格式和执行过程。

通过实验操作,我们掌握了指令的编写和执行方法,加深了对指令系统的理解和应用。

实验五,CPU实验。

在实验五中,我们深入了解了计算机的中央处理器(CPU)的工作原理和结构。

通过实验操作,我们学习了CPU的各个部件的功能和相互之间的协作关系,掌握了CPU的工作过程和运行原理。

实验六,总线实验。

在本次实验中,我们学习了计算机的总线结构和工作原理。

通过实验操作,我们了解了总线的分类和各种总线的功能,掌握了总线的数据传输方式和时序控制方法。

结论:通过本次实验,我们深入了解了计算机组成原理的相关知识,掌握了计算机硬件的基本组成和工作原理。

通过实验操作,我们加深了对逻辑门电路、寄存器、计数器、存储器、指令系统、CPU和总线的理解,为进一步学习和研究计算机组成原理奠定了坚实的基础。

希望通过不断的实践和学习,能够更深入地理解和应用计算机组成原理的知识。

计算机组成原理实验报告4

上海大学计算机学院实验名称:指令系统实验一、实验目的1. 读出系统已有的指令,并理解其含义。

2. 设计并实现一条新指令。

二、实验原理微程序和机器指令,实验箱的机器指令系统,实验箱机器指令系统的布线,实验箱机器指令系统的工作原理,实验箱PC的打入原理,程序存储器模式下的操作。

三、实验内容1. 考察机器指令64的各微指令信号,确定该指令的功能。

(假设R0=77, A=11, 77单元存放56H数据,64指令的下一条指令为E8)2. 修改机器指令E8,使其完成“输出A+W的结果左移一位后的值到OUT”操作。

3*. 修改机器指令F0,使其完成“A+R2的结果右移一位的值到OUT”的操作四、实验步骤实验任务一:考察机器指令64的各微指令信号,确定该指令的功能。

实验步骤:1.初始化系统(Reset),进入μEM,在Adr字段送入64,按NX键,可查看其对应的微指令:64: FF 77 FF65: D7 BF EF66:FF FE 9267:CB FF FF2.分析其二进制代码,分析其控制功能64: 1111 1111 0111 0111 1111 1111从寄存器R?中取出地址打入地址寄存器MAR。

65: 1110 0111 1011 1111 1110 1111把地址寄存器MAR的存储器值EM打入寄存器W。

66:1111 1111 1111 1110 1001 0010把寄存器A和寄存器W中的数据进行或运算后打入寄存器A和标志位C,Z。

67:1100 1011 1111 1111 1111 1111读出下一条指令并立即执行。

四条指令功能:把寄存器A和寄存器R?中地址内存的数据进行或运算,结果保存在寄存器A中,然后执行下一条指令。

实验任务二:1.分解任务:修改机器指令E8,使其完成“输出A+W的结果左移一位后的值到OUT”操作的操作。

第一步完成A+W;并把“左移一位的值送OUT”;第二步完成取指令。

2.编制微指令:由“控制总线功能对应表”,可确定这四步基本操作的微指令码为:① FFDFD8 ②CBFFFF ③FFFFFF ④FFFFFF3.操作:程序存储器EM模式下,将E8指令送入A0单元,则在Adr下打入A0, DB下打入E8。

实验4:双端口存储器实验 ----独立方式

河北环境工程学院

《计算机组成原理》实验报告

作者:

系(部):

专业班级:

学号:

成绩:__________________

评阅教师:__________________

年月日

一、实验目的

1、了解双端口静态存储器IDT7132的工作特性及其使用方法;

2、了解半导体存储器怎样存储和读取数据;

3、了解双端口存储器怎样并行读写;

4、熟悉LK-TEC-9模型计算机存储器部分的数据通路;

二、预习内容

1.掌握双端口存储器的使用方法

2. 掌握TEC-8模型计算机存储器的部分的数据通路

三、实验环境及主要器件

1.TEC-8实验系统 1台

2. 逻辑测试笔 1支

3. 双踪示波器 1台

4. 逻辑测试笔 1支

四、实验内容

1、从存储器地址10H开始,通过左端口连续向双端口RAM中写入3个数:85H,60H,38H。

在写的过程中,在右端口检测写的数据是否正确。

2、从存储器地址10H开始,连续从双端口RAM的左端口和右端口同时读出存储器的内容。

五、实验步骤

六、实验结果分析与讨论。

计算机组成原理实验报告(四个实验 图)

福建农林大学计算机与信息学院计算机类实验报告课程名称:计算机组成原理姓名:周孙彬系:计算机专业:计算机科学与技术年级:2012级学号:3126010050指导教师:张旭玲职称:讲师2014年06 月22日实验项目列表序号实验项目名称成绩指导教师1 算术逻辑运算单元实验张旭玲2 存储器和总线实验张旭玲3 微程序控制单元实验张旭玲4 指令部件模块实验张旭玲福建农林大学计算机与信息学院信息工程类实验报告系:计算机专业:计算机科学与技术年级: 2012级姓名:周孙彬学号: 3126010050 实验课程:实验室号:_______ 实验设备号:实验时间:指导教师签字:成绩:实验一算术逻辑运算单元实验实验目的1、掌握简单运算器的数据传输方式2、掌握74LS181的功能和应用实验要求完成不带进位位算术、逻辑运算实验。

按照实验步骤完成实验项目,了解算术逻辑运算单元的运行过程。

实验说明1、ALU单元实验构成(如图2-1-1)1、运算器由2片74LS181构成8位字长的ALU单元。

2、2片74LS374作为2个数据锁存器(DR1、DR2),8芯插座ALU-IN作为数据输入端,可通过短8芯扁平电缆,把数据输入端连接到数据总线上。

运算器的数据输出由一片74LS244(输出缓冲器)来控制,8芯插座ALU-OUT 作为数据输出端,可通过短8芯扁平电缆把数据输出端连接到数据总线上。

图2-1-1图2-1-22、ALU单元的工作原理(如图2-1-2)数据输入锁存器DR1的EDR1为低电平,并且D1CK有上升沿时,把来自数据总线的数据打入锁存器DR1。

同样使EDR2为低电平、D2CK有上升沿时把数据总线上的数据打入数据锁存器DR2。

算术逻辑运算单元的核心是由2片74LS181组成,它可以进行2个8位二进制数的算术逻辑运算,74LS181的各种工作方式可通过设置其控制信号来实现(S0、S1、S2、S3、M、CN)。

当实验者正确设置了74LS181的各个控制信号,74LS181会运算数据锁存器DR1、DR2内的数据。

计算机组成原理实验报告四

实验报告实验四数据通路组成实验一、实验目的1.将运算器模块于存储器模块联机2.进一步熟悉计算机的数据通路3.将存储器的两个存储单元的内容通过运算器相加并且将结果送回存储单元。

二、实验设备1.TDN-CM+计算机组成原理实验系统一套2.若干导线和排线三、实验电路四、实验数据并完成以下运算:( 01H )+( 02H ) →03H( 01H )⊕(02H )→04H五、实验结果分析与体会这次实验是这学期最后一次实验, 也是最为复杂的一次实验, 因为是将实验一中运算器的算术运算和实验三中的存储器结合到一起, 所以实验内容很多, 实验步骤很复杂。

然而颜老师在我们是眼前首先对实验的各环节作了详细的说明, 对我们可能在会哪些地方出错也做了明确的指导和提示, 特别是在T4和T3连接脉冲的连线上给我们做了很详细的说明。

虽然我们对实验电路图理解的很是模糊, 也基本上看不懂图的含义。

但是由于对以前两次实验的原理及步骤了解的都十分到位, 而且实验前颜老师又做了特别指点, 所以我们对本次实验的步骤大致知道了。

1、在明确步骤后我和刘佳兵开始了实验, 由于是将第一次和第三次的实验图连接到一块, 所以很多控制开关上出现了重复, 不能有效控制信号。

我们根据老师的提示将重复的开关重新定义。

具体实验步骤如下:2、按照实验一和实验三的电路图连接电路, 重新定义了线路WB、CB、LDAR的二进制控制开关(由PC-B控制WB, 由LDPC控制CB, 由LOAD控制LDAR)。

3、验证试验三写入存储器的实现。

4、将数据AAH、55H分别写入到RAM的01H和02H单元中。

(1)将数据01H作为地址置入AR中;(2)重新设置模拟开关位置, 把数据AAH置入RAM的01H;(3)将数据02H作为地址置入AR中;(4)把数据55H置入RAM的02H;5、从RAM的01H和02H单元中读出刚刚写入的数据。

(1)再一次将数据01H作为地址置入AR中;(2)把置入在RAM的01H数据的AAH读出;(3)将数据02H作为地址置入AR中;(4)把置入RAM的02H数据55H读出;6、讲读出的数据分别放入寄存器DR1和DR2中。

计算机组成原理 实验报告

计算机组成原理实验报告计算机组成原理实验报告引言计算机组成原理是计算机科学与技术专业中的一门重要课程,通过实验学习可以更好地理解和掌握计算机的基本原理和结构。

本实验报告将介绍我在学习计算机组成原理课程中进行的实验内容和实验结果。

实验一:二进制与十进制转换在计算机中,数据以二进制形式存储和处理。

通过这个实验,我们学习了如何将二进制数转换为十进制数,以及如何将十进制数转换为二进制数。

通过实际操作,我更深入地了解了二进制与十进制之间的转换原理,并且掌握了转换的方法和技巧。

实验二:逻辑门电路设计逻辑门电路是计算机中的基本组成部分,用于实现不同的逻辑运算。

在这个实验中,我们学习了逻辑门的基本原理和功能,并通过电路设计软件进行了实际的电路设计和模拟。

通过这个实验,我深入理解了逻辑门电路的工作原理,并且掌握了电路设计的基本方法。

实验三:组合逻辑电路设计组合逻辑电路是由多个逻辑门组合而成的电路,用于实现复杂的逻辑功能。

在这个实验中,我们学习了组合逻辑电路的设计原理和方法,并通过实际的电路设计和模拟,实现了多个逻辑门的组合。

通过这个实验,我进一步掌握了逻辑电路设计的技巧,并且了解了组合逻辑电路在计算机中的应用。

实验四:时序逻辑电路设计时序逻辑电路是由组合逻辑电路和触发器组合而成的电路,用于实现存储和控制功能。

在这个实验中,我们学习了时序逻辑电路的设计原理和方法,并通过实际的电路设计和模拟,实现了存储和控制功能。

通过这个实验,我进一步了解了时序逻辑电路的工作原理,并且掌握了时序逻辑电路的设计和调试技巧。

实验五:计算机指令系统设计计算机指令系统是计算机的核心部分,用于控制计算机的操作和运行。

在这个实验中,我们学习了计算机指令系统的设计原理和方法,并通过实际的指令系统设计和模拟,实现了基本的指令功能。

通过这个实验,我深入了解了计算机指令系统的工作原理,并且掌握了指令系统设计的基本技巧。

实验六:计算机硬件系统设计计算机硬件系统是由多个模块组成的,包括中央处理器、存储器、输入输出设备等。

计算机组成原理实验教程

计算机组成原理实验教程计算机组成原理实验是计算机科学与技术专业中非常重要的一门实践课程。

通过实验,学生可以深入了解计算机的基本构成和工作原理,并且培养实际操作的能力。

本教程旨在提供一系列详细的实验指导,帮助学生顺利完成计算机组成原理实验。

序言计算机组成原理是计算机科学与技术专业的一门核心课程,作为理论和实践相结合的实验教程,对于学生深入了解计算机的内部结构和工作原理至关重要。

本教程将介绍计算机组成原理实验的基本内容和实验报告的撰写要求,帮助学生更好地掌握实验技巧和理论知识。

实验一:数字逻辑电路设计与仿真本实验旨在让学生学会使用Verilog HDL设计数字逻辑电路,并通过仿真验证电路的正确性。

首先,学生需要了解Verilog HDL的基本语法和仿真工具的使用方法。

然后,根据实验要求,设计并仿真一个简单的数字逻辑电路,如全加器或比较器。

最后,学生需要撰写实验报告,详细介绍电路设计的过程、仿真结果和分析。

实验二:单周期CPU设计与实现本实验要求学生设计并实现一个单周期的CPU。

在实验过程中,学生需要了解指令的执行过程和控制信号的生成原理,设计CPU的数据通路和控制逻辑,并编写Verilog HDL代码进行实现。

实验完成后,学生需要进行功能仿真和时序仿真,验证CPU的正确性和性能。

实验报告应包括CPU设计的思路、关键问题的解决方法和仿真结果的分析。

实验三:多周期CPU设计与实现本实验要求学生进一步完善CPU的设计,实现一个多周期的CPU。

在实验过程中,学生需要改进单周期CPU的设计,引入时序控制信号和状态机,实现指令的多周期执行。

实验完成后,学生需要进行功能仿真和时序仿真,验证CPU的正确性和性能提升。

实验报告应包括多周期CPU设计的过程、关键问题的解决方法和仿真结果的分析。

实验四:流水线CPU设计与实现本实验要求学生设计并实现一个流水线CPU。

在实验过程中,学生需要了解流水线技术的基本原理和数据冒险的处理方法,设计流水线CPU的数据通路和控制逻辑。

(完整word版)计算机组成原理实验1~4

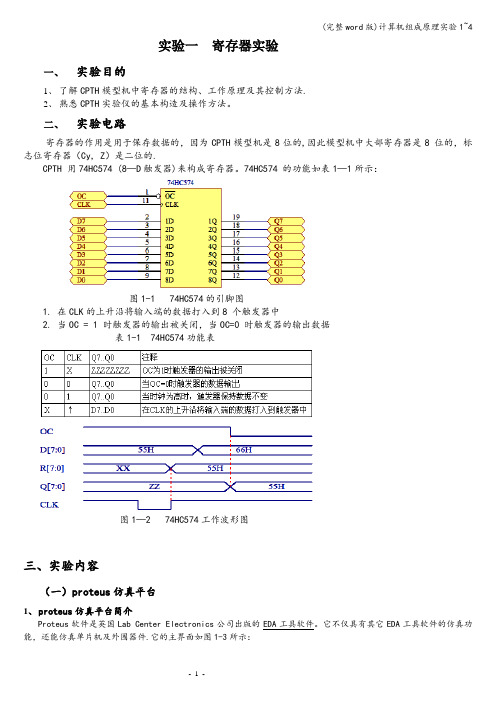

实验一寄存器实验一、实验目的1、了解CPTH模型机中寄存器的结构、工作原理及其控制方法.2、熟悉CPTH实验仪的基本构造及操作方法。

二、实验电路寄存器的作用是用于保存数据的,因为CPTH模型机是8位的,因此模型机中大部寄存器是8 位的,标志位寄存器(Cy, Z)是二位的.CPTH 用74HC574 (8—D触发器)来构成寄存器。

74HC574 的功能如表1—1所示:图1-1 74HC574的引脚图1. 在CLK的上升沿将输入端的数据打入到8 个触发器中2. 当OC = 1 时触发器的输出被关闭,当OC=0 时触发器的输出数据表1-1 74HC574功能表图1—2 74HC574工作波形图三、实验内容(一)proteus仿真平台1、proteus仿真平台简介Proteus软件是英国Lab Center Electronics公司出版的EDA工具软件。

它不仅具有其它EDA工具软件的仿真功能,还能仿真单片机及外围器件.它的主界面如图1-3所示:图1—3 proteus仿真平台主界面2、在proteus平台上运行电路:寄存器_1.DSN。

拨动开关,观察灯的亮灭,回答思考题1。

思考题1:先使OC=1,拨D0~D7=00110011,按下CK提供CLK上升沿;再拨D0~D7=01000100,OC=0,此时Q0~Q7为多少?3、CPTH模型机上,寄存器A的电路组成如图1-4所示。

在proteus平台上运行电路:寄存器_2.DSN,回答思考题2。

图1-4 寄存器A原理图思考题2:数据从D端传送到Q端,相应的控制端如何设置?3、CPTH模型机上,寄存器组R0~R3的电路组成如图1-5所示。

在proteus平台上运行电路:寄存器_3。

DSN,回答思考题3。

图1—5 寄存器组R0~R3 原理图74LS139是2—4线译码器,由A、B两个输入端选择控制4个输出端Y0~Y3,使能端E低电平有效,允许译码输出。

74HC32是或门,两个输入端同时为低电平,输出为低电平.具体的控制方式见表1-2。

计算机组成原理实验

计算机组成原理实验计算机组成原理实验报告1. 引言计算机组成原理实验是计算机类专业学生进行的重要实践课程之一。

通过实验,学生可以深入了解计算机系统的各个组成部分以及它们的功能和工作原理。

2. 实验目的本次实验的主要目的是探究计算机中的主要组成部分,包括中央处理器(CPU)、内存、输入输出设备以及硬盘等,并了解它们的相互连接与调度方式。

3. 实验装置和材料本实验使用了一台计算机,配备有Intel Core i7处理器、8GB 内存和500GB硬盘。

实验中还使用了键盘、鼠标和显示器等输入输出设备。

4. 实验过程及结果4.1 CPU实验在这个实验中,我们通过编写汇编语言程序来实现简单的数值运算。

实验结果显示,CPU能够根据程序逐条执行指令,并正确计算出结果。

4.2 内存实验通过编写C语言程序,我们对内存进行读写操作。

实验结果显示,内存可以正确存储和读取数据,并且能够保持数据的一致性。

4.3 输入输出设备实验在这个实验中,我们测试了键盘和鼠标的输入功能以及显示器的输出功能。

实验结果显示,输入设备能够正确识别用户的输入,而输出设备能够正确显示结果。

4.4 硬盘实验通过读写文件的操作,我们测试了硬盘的存储和检索功能。

实验结果显示,硬盘能够正确存储和读取文件,并且能够在短时间内进行大量的数据传输。

5. 结论通过本次实验,我们深入了解了计算机系统的各个组成部分以及它们的功能和工作原理。

实验结果表明,计算机的各个组件能够正常工作,并且能够协同工作以完成复杂的任务。

6. 参考文献[1] 《计算机组成原理实验指导书》[2] Smith, J.E., & Jones, P. 《Computer Organization and Design: The Hardware/Software Interface》. Morgan Kaufmann, 2014.。

计算机组成原理实验报告

计算机组成原理实验报告计算机组成原理实验报告引言:计算机组成原理是计算机科学与技术专业的重要课程之一,通过实验可以更好地理解和掌握计算机的组成原理。

本篇实验报告将介绍我们在计算机组成原理实验中所进行的实验内容和实验结果。

实验一:逻辑门电路设计在这个实验中,我们学习了逻辑门电路的设计和实现。

通过使用门电路,我们可以实现与门、或门、非门等基本逻辑运算。

我们首先学习了逻辑门电路的真值表和逻辑代数的基本运算规则,然后根据实验要求,使用逻辑门电路设计了一个简单的加法器电路,并通过仿真软件进行了验证。

实验结果表明,我们设计的加法器电路能够正确地进行二进制数的加法运算。

实验二:数字逻辑电路实现在这个实验中,我们进一步学习了数字逻辑电路的实现。

通过使用多路选择器、触发器等数字逻辑元件,我们可以实现更复杂的逻辑功能。

我们首先学习了多路选择器的原理和使用方法,然后根据实验要求,设计了一个4位二进制加法器电路,并通过数字逻辑实验板进行了搭建和测试。

实验结果表明,我们设计的4位二进制加法器能够正确地进行二进制数的加法运算。

实验三:存储器设计与实现在这个实验中,我们学习了存储器的设计和实现。

存储器是计算机中用于存储和读取数据的重要组成部分。

我们首先学习了存储器的基本原理和组成结构,然后根据实验要求,设计了一个简单的8位存储器电路,并通过实验板进行了搭建和测试。

实验结果表明,我们设计的8位存储器能够正确地存储和读取数据。

实验四:计算机硬件系统设计与实现在这个实验中,我们学习了计算机硬件系统的设计和实现。

计算机硬件系统是计算机的核心部分,包括中央处理器、存储器、输入输出设备等。

我们首先学习了计算机硬件系统的基本原理和组成结构,然后根据实验要求,设计了一个简单的计算机硬件系统,并通过实验板进行了搭建和测试。

实验结果表明,我们设计的计算机硬件系统能够正确地进行指令的执行和数据的处理。

结论:通过这些实验,我们深入学习了计算机组成原理的相关知识,并通过实践掌握了计算机组成原理的基本原理和实现方法。

计算机组成原理实验三~四

计算机学院学院计算机科学与技术专业班___组、学号姓名协作者______________ 教师评定_______________ 实验题目实验三存储器部件教学实验一、实验目的:1.熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处。

学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。

2.理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案。

3.了解静态存储器系统使用的各种控制信号之间正常的时序关系。

4.了解如何通过读、写存储顺的指令实现对58C65 ROM芯片的读、写操作。

加深理解存储器部件在计算机整机系统中的作用。

二、实验设备与器材:TEC-XP+教学实验系统和仿真终端软件PCEC。

三、实验说明和原理:1、内存储器原理内存储器是计算机中存放正在运行中的程序和相关数据的部件。

在教学计算机存储器部件设计中,出于简化和容易实现的目的,选用静态存储器芯片实现内存储器的存储体,包括唯读存储区和随读写存储区两部分,ROM存储区选用4片长度8位、容易8KB的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分成3组,其地址空间分配关系是:0-1777h 用于第一组ROM,固化监控程序,2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作监控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩展内存容量的教学实验。

地址总线的低13位送到ROM芯片的地址线引脚,用于选择芯片内的一个存储字。

用于实现存储字的高位字节的3个芯片的数据线引脚、实现低位字节的3个芯片的数据线引脚分别连接在一起接到数据总线的高、低位字节,是实现存储器数据读写的信息通路。

数据总线要通过一个双向三态门电路与CPU一侧的内部总线IB相连接,已完成存储器、接口电路和CPU之间的数据通讯。

2、扩展教学机的存储空间四、实验内容:1)要完成存储器容量扩展的教学实验,需为扩展存储器选择一个地址,并注意读写和OE等控制信号的正确状态。

计算机组成原理_实验报告四(含答案)

湖南科技学院电子与信息工程学院实验报告课程名称:姓名:学号:专业:班级:指导老师:实验四微程序控制组成实验一、实验目的及要求1.将微程序控制器同执行部件(整个数据通路)联机,组成一台模型计算机。

2.用微程序控制器控制模型计算机的数据通路。

3.执行给定的简单程序,掌握机器指令与微指令的关系,牢固建立计算机的整机概念。

二、实验电路本次实验将前面几个实验中的所模块,包括运算器、存储器、通用寄存器堆等同微程序控制器组合在一起,构成一台简单的模型机。

这是最复杂的一个实验,也将是最有收获的一个实验。

在前面的实验中,实验者本身作为“控制器”,完成了对数据通路的控制。

而在本次实验中,数据通路的控制将交由微程序控制器来完成。

实验机器从内存中取出一条机器指令到执行指令结束的一个指令周期,是由微程序完成的,即一条机器指令对应一个微程序序列。

实验电路大致如下面框图所示。

其中控制器是控制部件,数据通路是执行部件,时序发生器是时序部件。

需使用导线将各个部件控制信号与控制器相连。

三、实验主要仪器设备1.TEC-5计算机组成实验系统1台2.逻辑测试笔一支(在TEC-5实验台上)四、实验任务1.对机器指令组成的简单程序进行译码。

将下表的程序按机器指令格式手工汇编成二进制机器代码,此项任务请在预习时完成。

2.3.使用控制台命令将寄存器内容初始化为:R0=11H,R1=22H,R2=0AAH。

4.使用控制台命令将任务1中的程序代码存入内存中(注意起始地址为30H),以及将内存地址为11H的单元内容设置为0AAH。

5.用单拍(DP)方式执行一遍程序,执行时注意观察各个指示灯的显示并做好记录(完成实验表格),从而跟踪程序执行的详细过程(可观察到每一条微指令的执行过程)。

6.用连续方式再次执行程序。

这种情况相当于计算机正常的工作。

程序执行到STP指令后自动停机。

读出寄存器中的运算结果,与理论值比较。

五、实验步骤和实验结果记录1.程序译码。

计算机组成原理TEC-4实验手册(含实验步骤)完整6个实验-三个程序设计

地址寄存器AR1(U37)和AR2(U27、U28)提供双端口存储器的地址。AR1是1片GAL22V10,具有加1功能,提供双端口存储器左端口的地址。AR1从数据总线DBUS接收数据。AR1的控制信号是LDAR1和AR1_INC。当AR1_INC = 1时,在T4的上升沿,AR1的值加1;当LDAR1 = 1时,在T4的上升沿,将数据总线DBUS的数据打入地址寄存器AR1。AR2由2片74HC298组成,有两个数据输入端,一个来自程序计数器PC,另一个来自数据总线DBUS。AR2的控制信号是LDAR2和M3。M3选择数据来源,当M3 = 1时,选中数据总线DBUS;当M3 = 0时,选中程序计数器PC。LDAR2控制何时接收地址,当LDAR2 = 1时,在T2的下降沿将选中的数据源上的数据打入AR2。

一、TEC—4计算机组成原理实验系统特点

1.计算机模型简单、实用,运算器数据通路、控制器、控制台各部分划分清晰。

2.计算机模型采用了数据总线和指令总线双总线体制,能够实现流水控制。

3.控制器有微程序控制器或者硬布线控制器两种类型,每种类型又有流水和非流水两种方案。

4.寄存器堆由1片ispLSI1016组成,运算器由1片ispLSI1024组成,设计新颖。

1.运算器ALU

运算器ALU由一片ispLSI1024(U47)组成,在选择端S2、S1、S0控制下,对数据A和B进行加、减、与、直通、乘五种运算,功能如下:

表1运算器功能表

选择

操作

S2

S1

S0

0

0

0

A & B

0

0

1

A & A(直通)

0

1

0

A + B

杭电计组实验4-寄存器堆设计实验

W_Addr = 0;

Write_reg = 0;

W_Data = 0;

end

endmodule

RTL图

二、结果

思考题:(1)根据8个寄存器执行读、写操作,实验结果符合预期

(2)always@(posedge Clk or posedge Reset)

begin

实验位置(机号):

实验日期:指导教师:

实验内容(算法、程序、步骤和方法)

1、实验目的

(1)学会使用Verilog HDL进行时序电路的设计方法。

(2)掌握灵活应用Verilog HDL进行各种描述与建模的技巧和方法。

(3)学习寄存器堆的数据传送与读/写工作原理,掌握寄存器堆得设计方法。

2、实验仪器

ISE工具软件

);

initial begin

// Initialize Inputs

R_Addr_A = 0;

R_Addr_B = 0;

Clk = 0;

W_Addr = 0;

W_Data = 0;

Reset = 0;

Write_reg = 0;

// Wait 100 ns for global reset to finish

output wire[0:31]R_Data_B;

integer i=0;

always@(posedge Clk or posedge Reset)

begin

if(Reset)

begin

for(i=0;i<=31;i=i+1)

REG_Files[i]<=32'b0;

end

else

计算机组成原理实践环节第4部分计算机组成原理实验

ALU为8位逻辑运算部件,它的输出为F0~F8,

(其中F8为进位输出)。它可有如下8种功能,具体

由开关K13、K14、K16选择: F=A+B 允许有进位输入(K9)和进位输出(L9)。 F=A+l 允许有进位输入(K9)和进位输出(L9)。 F=A∧B, F=A∨B, F=B, F=A, F=全1, F=全零。

三 存储部件实验 存储器部件实验请大家自己参考实验讲义。

使数码管的小数点全亮。

(4).实验操作: a.使K8~K16处于非有效状态。 b.置K0~K7为10010110,使74244导通

至IDB,并使74373接数。 c.置KO~K7为11110000,使74244导通,

并使74374接数。 d.关闭74244。

e.使74373输出至IDB,并写入M(6116)中。 f.使74374输出至IDB,并使74373接数。 g.读出M至IDB,并使74374接数 。 h.使74373输出至IDB,并使74377接数, L0~L7为11110000使74374输出至IDB,并使 74377接数,L0~L7为10010110。

(3). 74377、74374等D触发器,需定义它 们的NODE为REG类型(ISTYPE‘REG')。

(4). 对D触发器,需定义D端输人和时钟输 入的表达式,例对74374可如下定义:

[U374Q0...U374Q7]=[IDB0...IDB7]; [U374Q0...U374Q7].CLK=U374CK;

据。

74244为8位三态门,OE=0时,把K7~K0的数 据输入到IDB上。

74377为8位D触发器,CK为上跳有效时钟,EN 为允许输入(恒接为0),它的输出接L8~Ll5。

计算机组成原理实验4.1_实验报告

学生实验报告学院:软件学院专业:软件工程年级:2010级学号:24320102202460 24320102202441 学生姓名:高伟同组学生姓名:陈紫桓实验课程名称:计算机组成原理实验名称:系统总线和具有基本输入输出功能的总线接口指导教师:曾文华、蔡艺军、廖凌宇实验时间: 2012.3.12 实验地点:漳州校区生化楼6032012年 3月12日一、实验目的与要求1.理解总线的概念及其特性。

2.掌握控制总线的功能和应用。

二、实验设备1、TD-CMA教学实验系统1台(通过USB串行接口与PC微机相连)2、PC微机1台三、实验原理由于存储器和输入。

输出设备最终是要挂接到外部总线上,所以需要外部总线提供数据信号、地址信号以及控制信号。

在该实验平台中,外部总线被分为数据总线、地址总线和控制总线,分别为外设提供上述信号。

外部总线和CPU内总线之间通过三态门连接,同时实现了内外总线的分离和对于数据流向的控制。

地址总线可以为外设提供地址信号和片选信号。

由地址总线的高位进行译码,系统的I/O地址译码原理见图1.由于使用A6、A7进行译码,I/O地址空间被分为四个区,如表1图1 I/O地址译码原理图表1 I/O地址空间分配为了实现对于MEM和外设的读写操作,还需要一个读写控制逻辑,使得CPU能控制MEM和I/O设备的读写,实验中的读写控制逻辑如图2,由于T3的参与,可以保证写脉冲宽与T3一致,T3由时序单元的TS3 给出。

IOM用来选择是对I/O设备还是对MEM进行读写操作,IOM=1时对I/O设备进行读写操作,IOM=0时对MEM进行读操作。

RD=1时为读,WR=1时为写。

图2 读写控制逻辑四、实验步骤1、读写控制逻辑设计实验。

(1)按照图3实验接线图进行接线。

图3 实验接线图(2)具体操作步骤首先将时序与操作台单元的开关KK1、KK3置为‘运行’档,开关KK2置为‘单拍’档,按动CON单元的总清按钮CLR,并执行下述操作。

计算机组成原理实验报告(4个)

上海建桥学院本科实验报告课程名称:计算机组成原理学号:姓名:专业:班级:指导教师:课内实验目录及成绩序号实验名称页码成绩1 八位算术逻辑运算 12 静态随机存取存储器实验63 数据通路114 微程序控制器的实现16总成绩信息技术学院2014年03 月20 日上海建桥学院实验报告课程名称:计算机组成原理实验类型:验证型实验项目名称:八位算术逻辑运算实验地点:实验日期:年月日一、实验目的和要求1、掌握运算器的基本组成结构;2、掌握运算器的工作原理。

二、实验原理和内容实验采用的运算器数据通路如图1-1所示,ALU逻辑功能表如表1-1所示。

图1-1运算器原理图ALU部件由一片 CPLD实现,内部含有三个独立的运算部件,分别为算术、逻辑和移位运算部件。

输入数据IN[7..0](由插座JP22引出)通过拨动开关sK7..sK0产生(开关由插座JP97引出)。

数据存于暂存器A或暂存器 B中(暂存器A和B的数据可在 LED灯上实时显示),三个部件可同时接受来自暂存器 A和 B的数据。

各部件对操作数进行何种运算由控制信号S3…S0和CN_I来决定(S3…S0由插座JP18引出;CN_I由插座JP19引出),可通过拨动开关sK23..sK20和sK12设置(开关由插座JP89、JP19引出)。

运算结果由三选一多路开关选择,任何时候,多路开关只选择三个部件中的一个部件的运算结果作为ALU的输出。

ALU的输出ALU_D7..ALU_D0通过三态门74LS245送至CPU内部数据总线(iDBus)上(由插座JP25引出),并通过扩展区单元的的二位数码管和DS94..DS101LED灯显示(LED灯由插座JP62引出)。

如果运算影响进位标志FC、零标志FZ、正负标志FS,则在T3状态的下降沿,相应状态分别锁存到FC、FZ、FS触发器中,实验仪设有LED灯显示各标志位状态。

操作控制信号wA(允许写暂存器A)、wB(允许写暂存器B)、rALU(允许ALU结果输出到内部数据总线(iDBus)上)由JP19引出,都为低电平有效,实验时可通过连接开关sK15..sK13设置(开关由插座JP92引出)。

计算机组成原理实验报告4-微程序计数器uPC实验

千里之行,始于足下。

计算机组成原理实验报告4-微程序计数器uPC实验计算机组成原理实验报告4-微程序计数器uPC实验一、实验目的本次实验的目的是通过设计和实现微程序计数器uPC,加深对计算机组成原理中微程序控制的理解和掌握。

二、实验原理微程序控制是一种使用微操作指令来实现指令解码和控制的方法。

其基本原理是将指令的每个微操作独立编码,并存放在存储器中,再通过微程序计数器uPC逐步读取并执行这些微操作指令,从而实现对硬件的控制。

本次实验中,我们设计的微程序计数器uPC采用基于有限状态机的方式。

其工作流程如下:1. 在上升沿时,根据当前状态和输入,更新下一个状态。

2. 在状态更新完成后,判断是否需要进行微指令计数器的更新,如果需要,则计数器自增。

3. 根据计数器的值,从微指令存储器中读取相应的微指令。

4. 执行微指令。

三、实验步骤本次实验的主要步骤如下:第1页/共3页锲而不舍,金石可镂。

1. 设计微指令的编码对应的控制信号,并将其存储在微指令存储器中。

2. 设计并实现基于有限状态机的微程序计数器uPC。

3. 将uPC与微指令存储器、数据通路、输入设备等连接起来,以实现对硬件的控制。

四、实验结果在实验过程中,我们完成了微指令的编码,并将其存储在微指令存储器中,设计并实现了基于有限状态机的微程序计数器uPC,并将uPC与其他模块连接起来。

经过测试,我们发现uPC能够正确地执行微指令,并能够对硬件进行正确的控制。

五、实验总结通过本次实验,我们深入了解了微程序控制的原理和工作方式,加深了对计算机组成原理中微程序控制的理解和掌握。

在实验过程中,我们通过设计和实现微程序计数器uPC,对于掌握微程序控制有了更深入的认识,并且锻炼了自己的设计和调试能力。

虽然在实验过程中遇到了一些困难和问题,但通过思考和团队合作,我们最终成功地完成了实验并取得了满意的结果。

通过本次实验,我们不仅提高了对计算机组成原理的理论理解,也增强了自己的动手实践能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验四模型机设计1 实验目的(1) 掌握一个简单CPU的组成原理。

(2) 在掌握部件单元电路的基础上,进一步将其构造一台基本模型计算机。

(3) 为其定义五条机器指令,编写相应的微程序,并上机调试掌握整机概念。

2 实验设备PC机一台,TD-CMA实验系统一套。

3 实验原理本实验要实现一个简单的CPU,并且在此CPU的基础上,继续构建一个简单的模型计算机。

CPU由运算器(ALU)、微程序控制器(MC)、通用寄存器(R0),指令寄存器(IR)、程序计数器(PC)和地址寄存器(AR)组成,如图4-1所示。

这个CPU在写入相应的微指令后,就具备了执行机器指令的功能,但是机器指令一般存放在主存当中,CPU必须和主存挂接后,才有实际的意义,所以还需要在该CPU的基础上增加一个主存和基本的输入输出部件,以构成一个简单的模型计算机。

图4-1 基本CPU构成原理图除了程序计数器(PC),其余部件在前面的实验中都已用到,在此不再讨论。

系统的程序计数器(PC)和地址寄存器(AR)集成在一片CPLD芯片中。

CLR连接至CON单元的总清端CLR,按下CLR按钮,将使PC清零,LDPC和T3相与后作为计数器的计数时钟,当LOAD为低时,计数时钟到来后将CPU内总线上的数据打入PC。

T3CLR图4-2 程序计数器(PC)原理图本模型机和前面微程序控制器实验相比,新增加一条跳转指令JMP,共有五条指令:IN(输入)、ADD(二进制加法)、OUT(输出)、JMP(无条件转移),HLT(停机),其指令格式如下(高4位为操作码):助记符机器指令码说明IN0010 0000IN R0ADD0000 0000R0 + R0 R0OUT0011 0000R0 OUTJMP addr1110 0000 ********addr PCHLT0101 0000停机其中JMP为双字节指令,其余均为单字节指令,********为addr对应的二进制地址码。

微程序控制器实验的指令是通过手动给出的,现在要求CPU自动从存储器读取指令并执行。

根据以上要求,设计数据通路图,如图4-3所示。

本实验在前一个实验的基础上增加了三个部件,一是PC(程序计数器),另一个是AR(地址寄存器),还有就是MEM(主存)。

因而在微指令中应增加相应的控制位,其微指令格式如表4-1所示。

图4-3 数据通路图 表4-1 微指令格式A字段B字段C字段141312选择000001LDA 010LDB 011LDR0100保留10111023M232221201918-1514-1211-98-65-0WR RD IOM A 字段B 字段C 字段MA5-MA0S3-S0NOP 111LDIRLDAR LOAD 11109选择000001ALU_B 010R0_B 011保留100保留101110NOP 111保留保留PC_B 876选择000001P<1>010保留011保留100保留101110NOP 111保留保留LDPC M22系统涉及到的微程序流程见图4-4所示,当拟定“取指”微指令时,该微指令的判别测试字段为P<1>测试。

指令译码原理见图3-2-3所示,由于“取指”微指令是所有微程序都使用的公用微指令,因此P<1> 的测试结果出现多路分支。

本机用指令寄存器的高6位(IR7—IR2)作为测试条件,出现5路分支,占用5个固定微地址单元,剩下的其它地方就可以一条微指令占用控存一个微地址单元随意填写,微程序流程图上的单元地址为16进制。

图4-4 简单模型机微程序流程图当全部微程序设计完毕后,应将每条微指令代码化,表4-2即为将图4-4的微程序流程图按微指令格式转化而成的“二进制微代码表”。

表4-2 二进制微代码表设计一段机器程序,要求从IN单元读入一个数据,存于R0,将R0和自身相加,结果存于R0,再将R0的值送OUT单元显示。

根据要求可以得到如下程序,地址和内容均为二进制数。

地址内容助记符说明00000000 00100000 ; START: IN R0 从IN单元读入数据送R000000001 00000000 ; ADD R0,R0 R0和自身相加,结果送R000000010 00110000 ; OUT R0 R0的值送OUT单元显示00000011 11100000 ; JMP START 跳转至00H地址00000100 00000000 ;00000101 01010000 ; HLT 停机4 实验步骤1. 按图4-5连接实验线路。

2. 写入实验程序,并进行校验,分两种方式,手动写入和联机写入。

1) 手动写入和校验(1) 手动写入微程序①将时序与操作台单元的开关KK1置为‘停止’档,KK3置为‘编程’档,KK4置为‘控存’档,KK5置为‘置数’档。

②使用CON单元的SD05——SD00给出微地址,IN单元给出低8位应写入的数据,连续两次按动时序与操作台的开关ST,将IN单元的数据写到该单元的低8位。

③将时序与操作台单元的开关KK5置为‘加1’档。

④ IN单元给出中8位应写入的数据,连续两次按动时序与操作台的开关ST,将IN单元的数据写到该单元的中8位。

IN单元给出高8位应写入的数据,连续两次按动时序与操作台的开关ST,将IN单元的数据写到该单元的高8位。

⑤重复①、②、③、④四步,将表4-2的微代码写入2816芯片中。

图4-5 实验接线图(2) 手动校验微程序①将时序与操作台单元的开关KK1置为‘停止’档,KK3置为‘校验’档,KK4置为‘控存’档,KK5置为‘置数’档。

②使用CON单元的SD05——SD00给出微地址,连续两次按动时序与操作台的开关ST,MC 单元的指数据指示灯 M7——M0显示该单元的低8位。

③将时序与操作台单元的开关KK5置为‘加1’档。

④连续两次按动时序与操作台的开关ST,MC单元的指数据指示灯 M15——M8显示该单元的中8位,MC单元的指数据指示灯 M23——M16显示该单元的高8位。

⑤重复①、②、③、④四步,完成对微代码的校验。

如果校验出微代码写入错误,重新写入、校验,直至确认微指令的输入无误为止。

(1)手动写入机器程序①将时序与操作台单元的开关KK1置为‘停止’档,KK3置为‘编程’档,KK4置为‘主存’档,KK5置为‘置数’档。

②使用CON单元的SD07——SD00给出地址,IN单元给出该单元应写入的数据,连续两次按动时序与操作台的开关ST,将IN单元的数据写到该存储器单元。

③将时序与操作台单元的开关KK5置为‘加1’档。

④ IN单元给出下一地址(地址自动加1)应写入的数据,连续两次按动时序与操作台的开关ST,将IN单元的数据写到该单元中。

然后地址会又自加1,只需在IN单元输入后续地址的数据,连续两次按动时序与操作台的开关ST,即可完成对该单元的写入。

⑤亦可重复①、②两步,将所有机器指令写入主存芯片中。

(2)手动校验机器程序①将时序与操作台单元的开关KK1置为‘停止’档,KK3置为‘校验’档,KK4置为‘主存’档,KK5置为‘置数’档。

②使用CON单元的SD07——SD00给出地址,连续两次按动时序与操作台的开关ST,CPU 内总线的指数据指示灯 D7——D0显示该单元的数据。

③将时序与操作台单元的开关KK5置为‘加1’档。

④连续两次按动时序与操作台的开关ST,地址自动加1,CPU内总线的指数据指示灯 D7——D0显示该单元的数据。

此后每两次按动时序与操作台的开关ST,地址自动加1,CPU内总线的指数据指示灯 D7——D0显示该单元的数据,继续进行该操作,直至完成校验,如发现错误,则返回写入,然后校验,直至确认输入的所有指令准确无误。

⑤亦可重复①、②两步,完成对指令码的校验。

如果校验出指令码写入错误,重新写入、校验,直至确认指令码的输入无误为止。

2) 联机写入和校验联机软件提供了微程序和机器程序下载功能,以代替手动读写微程序和机器程序,但是微程序和机器程序得以指定的格式写入到以TXT为后缀的文件中,微程序和机器程序的格式如下:机器指令格式说明:$P机器指令代码十六进制地址机器指令标志微指令格式说明:微指令代码十六进制地址微指令标志XX XX$M XX XXXXXX本次实验程序如下,程序中分号‘;’为注释符,分号后面的内容在下载时将被忽略掉:; //*************************************** //; // //; // CPU与简单模型机实验指令文件//; // //; // By TangDu CO.,LTD //; // //; //*************************************** //; //****** Start Of Main Memory Data ****** //$P 00 20 ; START: IN R0 从IN单元读入数据送R0$P 01 00 ; ADD R0,R0 R0和自身相加,结果送R0$P 02 30 ; OUT R0 R0的值送OUT单元显示$P 03 E0 ; JMP START 跳转至00H地址$P 04 00 ;$P 05 50 ; HLT 停机; //******* End Of Main Memory Data ******* //; //**** Start Of MicroController Data **** //$M 00 000001 ; NOP$M 01 006D43 ; PC->AR,PC加1$M 03 107070 ; MEM->IR, P<1>$M 04 002405 ; R0->B$M 05 04B201 ; A加B->R0$M 1D 105141 ; MEM->PC$M 30 001404 ; R0->A$M 32 183001 ; IN->R0$M 33 280401 ; R0->OUT$M 35 000035 ; NOP$M 3C 006D5D ; PC->AR,PC加1; //** End Of MicroController Data **//选择联机软件的“【转储】—【装载】”功能,在打开文件对话框中选择上面所保存的文件,软件自动将机器程序和微程序写入指定单元。

选择联机软件的“【转储】—【刷新指令区】”可以读出下位机所有的机器指令和微指令,并在指令区显示,对照文件检查微程序和机器程序是否正确,如果不正确,则说明写入操作失败,应重新写入,可以通过联机软件单独修改某个单元的指令,以修改微指令为例,先用鼠标左键单击指令区的‘微存’TAB按钮,然后再单击需修改单元的数据,此时该单元变为编辑框,输入6位数据并回车,编辑框消失,并以红色显示写入的数据。