最新DSP5在片外围电路汇总

DSP芯片及CCS环境

3.1.7 CPU状态和控制寄存器

‘C54x有三个状态和控制寄存器: 状态寄存器ST0 状态寄存器ST1 处理器工作方式状态寄存器PMST ST0和ST1包括了各种条件和方式的状态,PMST 包括了存储器配置状态和控制信息。

3.1.7 CPU状态和控制寄存器

处理器工作方式状态寄存器PMST: 设定并控制处理器的工作方式,反映处理器的工作状态

3、数字信号处理器的结构特点

④ 指令系统的多级流水线

可把指令周期减少到最小值,同时增加了数 字信号处理器的吞吐量,且流水线可以使用在任 何地方。 几条指令并行执行,每条指令处于其执行过 程中的不同状态。

⑤ 特殊的DSP指令

专用指令及其寻址方式,例如DMOV实现传 递数据,延迟的功能。

4、DSP系统设计与开发

DSP芯片概述及CCS环境初识

一、DSP概述

DSP:数字信号处理技术(Digital Signal Process)

DSP:数字信号处理器(Digital Signal Processor) 前者是理论技术 后者是实时实现 两者结合是解决实际问题的方案(DSPs)

数字信号处理的实现方法

1、软件编程 优点:灵活性强 缺点:速度慢,不能做到实时处理 2、采用专用的DSP芯片 优点:速度快,实时性强 缺点:灵活性差,动态范围和精度较差

国际上许多著名的集成电路生产厂商都相继推出了自己的 DSP器件,但在编程灵活性、软件调试、功耗、外部通信功能 等方面还不够理想。

DSP完善阶段 (2000)

不仅DSP的数字信号处理功能更加完善,而且在系统开发 的方便性、编程调试的灵活性、降低功耗等方面做了许多工作

2、DSP的应用领域

2、DSP的应用领域

四、TMS320C54X的片内外围电路

DSP典型硬件电路

19

附加内容

20

系统设计调试顺序

根据项目要求以及输入输出关系, 1 根据项目要求以及输入输出关系,确定 系统的方案。 系统的方案。总结您要进行的工作 2 仔细阅读手册,准备绘制原理图 仔细阅读手册, 3 对于以 对于以FPGA为核心的系统,事先最好 为核心的系统, 为核心的系统 将程序编写好, 将程序编写好,以便确定管脚分配是否正 确,并且选择器件的资源是否充裕。 并且选择器件的资源是否充裕。

DSP系统设计复习 DSP系统设计复习

宋华军 中国石油大学(华东) 中国石油大学(华东)信控学院

1

数据/ 数据/地址 总线和 控制信号

复位 信号 系统 控制 时钟

HOLD\ HOLD\ D(15D(15-0) HOLDA\ HOLDA\ A(15A(15-0) NM1\ NM1\ PS\ PS\ INT(0-3)\ INT(0-3)\ DS\ DS\ IA BIO\ BIO\ MSTRB\ MSTRB\ TOUT\ TOUT\ IOSTRB\ IOSTRB\ CLKX0\ CLKX0\ READY DX0 IAQ\ IAQ\ FSX0\ MSC\ MSC\ TMS320 FSX0\ CLKR0 DR0 C54x RS\ RS\ FSR0\ FSR0\ X1 CLKX1\ CLKX1\ X2\ X2\CLKIN DX1 CLKOUT FSX1\ FSX1\ CLKMD(1CLKMD(1-3) CLKR1 MP/MC\ MP/MC\ DR1 FSR1\ FSR1\

27

如何调试多片DSP? 如何调试多片DSP? DSP

对于有JTAG仿真口的DSP,可以将JTAG串接在一起 对于有JTAG仿真口的DSP,可以将JTAG串接在一起 JTAG仿真口的DSP 用一套仿真器同时调试多个DSP 每个DSP DSP, DSP可以用不 用一套仿真器同时调试多个DSP,每个DSP可以用不 同的名字,在不同的窗口中调试。 同的名字,在不同的窗口中调试。 注意:如果在JTAG和DSP间加入驱动,一定要用快速 注意:如果在JTAG和DSP间加入驱动,一定要用快速 JTAG 间加入驱动 的门电路,不能使用如LS的慢速门电路。 LS的慢速门电路 的门电路,不能使用如LS的慢速门电路。

TMS320C55X dsp原理及应用 汪春梅第5章

也可以通过函数设置PLL频率: PLL_setFreq (6, 1); 通过PLL_setFreq函数可以复位PLL锁相环,并改变倍频和分频数从而 得到所需的频率

CSL库中PLL_Config锁相环配置结构体声明如下:

CSL库中PLL_Config锁相环配置结构体

锁定模式(LOCK)

CLKOUT输出

频率由系统寄存器(SYSR)中的CLKDIV确定:

CLKDIV=000b, CLKOUT的频率等于CPU时钟的频率 CLKDIV=001b, CLKOUT的频率等于时钟的频率的1/2 CLKDIV=010b, CLKOUT的频率等于时钟的频率的1/3 CLKDIV=011b, CLKOUT的频率等于时钟的频率的1/4 CLKDIV=100b, CLKOUT的频率等于时钟的频率的1/5 CLKDIV=101b, CLKOUT的频率等于时钟的频率的1/6 CLKDIV=110b, CLKOUT的频率等于时钟的频率的1/7 CLKDIV=111b, CLKOUT的频率等于时钟的频率的1/8

计数器:对由TIN/TOUT引脚输入的脉冲信号 进行计数。

(2)如何利用片级支持库对通用定时器进行编程?

(2)如何利用片级支持库对通用定时器进行编程?

图 5-1

定时器CSL 库中的配置结构体声明与用户初始化实例

(2)如何利用片级支持库对通用定时器进行编程?

图 5-2

定时器CSL 库中的配置函数声明与调用示例

三、定时器的使用方法

2、 DSP复位时通用定时器状态

(1) 停止计时(TSS=1); (2)PSC =0; (3) TIM=FFFFh; (4) ARB=0; (5) TIN/TOUT为高阻抗状态; (6) 内部时钟源(FUNC=00b)。

定时器控制寄存器

专用的硬件乘法器

• 在通用的微处理器中,乘法指令是

由一系列加法来实现的,故需许多 个指令周期来完成 • DSP具有专用的硬件乘法器,乘法可 在一个指令周期内完成

1)多总线结构

2)40位算术逻辑单元(ALU)

3)17×17位并行乘法器

4)比较、选择和存储单元(CSSU) 5)指数编码器 6)两个地址发生器

为了快速实现数字信号处理运算,DSP芯片 一般都采用特殊的硬件结构,正是这种针对运算 的特殊的结构和设计,使它区别于通常的CPU或 MCU(微控制器)。 TMS320系列DSP芯片的主要硬件特点包括:哈 佛结构、流水线操作、多总线、多处理单元、硬 件配置强、耗电省。

DSP芯片的基本结构和特征

DSP芯片的基本结构 哈佛结构 流水线操作 专用的硬件乘法器 特殊的DSP指令 快速的指令周期

11

1B 1C 1D

1E 1E~

REA(块重复结束寄存器) PMST ( 处理器 工作 方式 ) XPC(程序计数器扩展) 保留

辅助寄存器(AR0~AR7):这8个16位的辅 助寄存器可以由算术逻辑单元(ALU)访 问,也可以由辅助寄存器算术单元(ARAU) 进行修改。它们主要的功能是产生16位的 数据地址,也可以同来作为通用寄存器和 计数器。

暂存器T

1.

2. 3. 4.

为乘法指令或乘/累加指令存放一个乘数; 为带有移位操作的指令(如:ADD ,LD,SUB 等)存放一个动态的移位数; 为BITT指令存放一个动态位地址; 参与EXP指令和NORM指令的操作。

状态转移寄存器TRN

1. 2.

为计算新的测量值存放中间结果; CMPS(比较、选择、存储单元)指令在累加 器高位和低位比较的基础上会修改TRN的内容

DSP原理与应用2011-第五章 TMS320F28335片内外设_ad转换SCI

掌握TMS320F28335内核结构,例如A/D转换、串行通信接口、 串行 外设接口。

重点:

TMS320F28335内部A/DC的正确使用,串行通信接口应用。

难点:

TMS320F28335的ADC寄存器操作和串行通信寄存器操作。

教学内容分两部分

§5.1:TMS320F28335内模拟/数字转换 §5.2 :TMS320F28335系列串行通信接口SCI和Modbus协议介绍

7

§5.1 .2 ADC有关的寄存器

控制寄存器

通道顺序选 择寄存器

结 果 寄 存 器

DSP原理与应用

2012年9月3日

8

ADC有关的寄存器(序)

控制寄存器 状态寄存器

参考电压选择寄存器 偏移电压调整寄存器

DSP原理与应用

2012年9月3日

9

§5.1.3 ADC 操作模式

根据采样模式划分,包括顺序采样和同步采样 1) 顺序采样模式(Sequential Sampling Mode)

DSP原理与应用

2012年9月3日

10

2) 同步采样模式(Simultaneous Sampling Mode)

DSP原理与应用

2012年9月3日

11

根据转换模式划分,包括: 级联模式转换和和双序列模式转换 1) 级联模式转换

DSP原理与应用

2012年9月3日

12

2) 双序列模式转换

DSP原理与应用

DSP原理与应用

4

Sequencer can be operated as two independent 8-state sequencers or as one large 16-state sequencer (i.e., two cascaded 8-state sequencers).

DSP原理及应用(C54X)

第一章绪论1.1 DSP的基本原理数字信号处理(简称DSP)是一门涉及多门学科并广泛应用于很多科学和工程领域的新兴学科。

数字信号处理是利用计算机或专用处理设备,以数字的形式对信号进行分析、采集、合成、变换、滤波、估算、压缩、识别等加工处理,以便提取有用的信息并进行有效的传输与应用。

数字信号处理是以众多学科为理论基础,它所涉及的范围极其广泛。

如数学领域中的微积分、概率统计、随机过程、数字分析等都是数字信号处理的基础工具。

它与网络理论、信号与系统、控制理论、通信理论、故障诊断等密切相关。

DSP可以代表数字信号处理技术(Digital SignalProcessing),也可以代表数字信号处理器(Digital Signal Processor)。

前者是理论和计算方法上的技术,后者是指实现这些技术的通用或专用可编程微处理器芯片。

数字信号处理包括两个方面的内容:1.法的研究 2.数字信号处理的实现数字信号处理(Digital Signal Processing,简称DSP)是一门涉及许多学科而又广泛应用于许多领域的新兴学科。

20世纪60年代以来,随着计算机和信息技术的飞速发展,数字信号处理技术应运而生并得到迅速的发展。

在过去的二十多年时间里,数字信号处理已经在通信等领域得到极为广泛的应用。

数字信号处理是利用计算机或专用处理设备,以数字形式对信号进行采集、变换、滤波、估值、增强、压缩、识别等处理,以得到符合人们需要的信号形式。

数字信号处理是围绕着数字信号处理的理论、实现和应用等几个方面发展起来的。

数字信号处理在理论上的发展推动了数字信号处理应用的发展。

反过来,数字信号处理的应用又促进了数字信号处理理论的提高。

而数字信号处理的实现则是理论和应用之间的桥梁。

数字信号处理是以众多学科为理论基础的,它所涉及的范围极其广泛。

例如,在数学领域,微积分、概率统计、随机过程、数值分析等都是数字信号处理的基本工具,与网络理论、信号与系统、控制论、通信理论、故障诊断等也密切相关。

DSP引脚及内部结构

EMU1/OFF:仿真器中断1引脚/关断所有 输出引脚。

9. NC引脚

NC:No Connection 1、2、12、15、35、36……143、144等

第2章 TMS320C54x的硬件结构

2.1 外部引脚 2.2 C54’的内部总线结构 2.3 ’C54x的中央处理器 2.4 ’C54x的存储空间结构 2.5 ’C54x的片内外设电路

2.8 ’C54x的主要特性

TMS320C54x的组成

中央处理器CPU

内部总线控制 特殊功能寄存器 数据存储器RAM

I/O功能扩展接口

串行口

主机通信接口HPI 定时系统 中断系统

程序存储器ROM

TMS320C54x的内部硬件结构图

系统 控制 接口

系统控制

PAGEN 程序地址生成器

DAGEN 数据地址生成器 特殊功能 寄存器 程序存储器 数据存储器 串行口 并行口 定时器 计数器 中断 外部 设备 接口 外部 存储器 接口

CPU

2.2 ’C54x的内部总线结构

TMS320C54x的结构是以8组16位总线为核心,形 成了支持高速指令执行的硬件基础。 1组程序总线PB 总线结构 3组数据总线CB、DB、EB 4组地址总线PAB、CAB、DAB、EAB

TMS320C54x的硬件结构图

系统 控制 接口

系统控制

PAGEN 程序地址生成器

(4) ALU的输出

ALU的输出为40位运算结果,通常被送至累加器 A或B。

HBIL:字节识别信号,用来判断主机送来的数据是 第1字节还是第2字节。 HCNTL0: HCNTL1:

用于主机选择所要寻址的寄存器;

HR/W : HRDY : HPIENA:

DSP-5

IIR的并联型

将因式分解的H(Z)展开成部分分式的形式,就可 得到IIR的并联型滤波器。

H ( z) H1 ( z) H2 ( z) H k ( z)

Hi(z)通常为一阶网络和二阶网络,网络系统均 为实数。 0i 1i z 1 Hi ( z) 1 a1i z 1 a2i z 2 输出Y(z)表示为

IIR 直接型

IIR 直接I型和IIR 直接II型,之所以称为“直接 型”,是因为它们的结构是直接从系统函数中得 到的,没有对系统函数做任何的重排。

遗憾的是:这样的结构对参数量化十分敏感。当 N较大时,数字滤波器会因参数量化(有限字长) 的微小变化,导致系统的零、极点位置出现重大 的变化。故通常不推荐使用在实际应用中。

引言

时域离散系统或网络可以用差分方程、单 位脉冲响应以及系统函数进行描述。

y (n ) bi x (n i ) ai y (n i )

i 0 i 1 M N

系统函数H(z)为

Y ( z) H ( z) X ( z)

M

1 ai z i

i 1

i 0 N

因为含有输出延时部分,它是反馈网络。IIR直接I型结 构 由下图可以看出,该网络是两部分的级联。第一网络对 应系统函数的分子,全零点系统;第二网络对应与系统 函数的分母,意味着这是系统函数的全极点系统。

IIR 直接 I型

该结构需要N+M级延时单元。

直接I型特点:直观、速度慢、不经济(需要N+M) 个延时器

b c

L L

k 流图特征余子式; 中除去与第k个前向通道接触的回

路后的剩余部分;

DSP实验5 epwm输出实验 胡恒 2016329600013

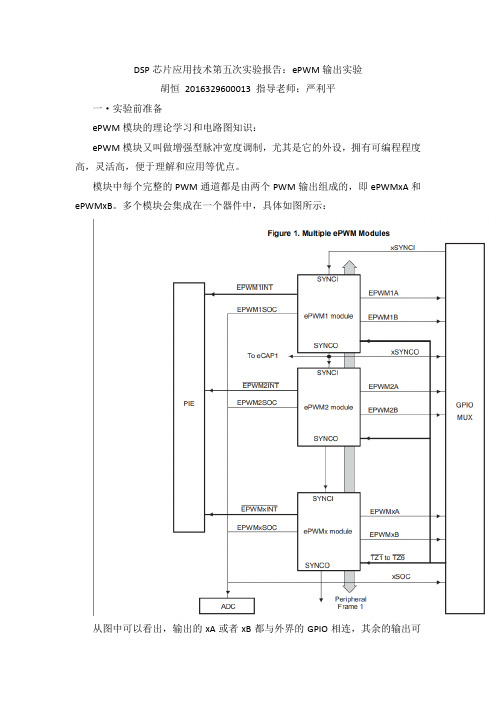

DSP芯片应用技术第五次实验报告:ePWM输出实验胡恒2016329600013 指导老师:严利平一·实验前准备ePWM模块的理论学习和电路图知识:ePWM模块又叫做增强型脉冲宽度调制,尤其是它的外设,拥有可编程程度高,灵活高,便于理解和应用等优点。

模块中每个完整的PWM通道都是由两个PWM输出组成的,即ePWMxA和ePWMxB。

多个模块会集成在一个器件中,具体如图所示:从图中可以看出,输出的xA或者xB都与外界的GPIO相连,其余的输出可以与AD模块,eCAP模块相连。

ePWM模块总共分为7个模块,分别为时间基准模块,技术比较器模块,动作限定模块,死区控制模块,斩波模块,错误控制模块和事件触发模块等。

模块的连接大致如此。

时基模块与计数模块比较,再根据结果确定输出的到底是CMPA还是CMPB波,也可以不经过计数比较,直接到达动作限定模块来触发事件与中断,主要就是AD模块。

通过死区之后再通过斩波和错误控制,最后到达输出端,输出的波形可以用示波器来检测。

分模块来讲,时基模块最重要。

通过寄存器与逻辑门电路的比较来决定输出的信号波形来控制下一个模块。

PWM周期与频率的计算主要有三种方式,分别为递增计数,递减计数,还有递增递减计数。

前两个的周期分别为T=(TBPRD+1)*TBCLK,F=1/T。

后者的T=2*TBPRD*TBCLK,F=1/T。

时间计数达到周期值TBPRD时,计数器会清空,然后再重复。

递增计数递减计数递增递减计数从图中的波形可以看出,每当计数完成的时候,SYNCI总会来一个脉冲,然后计数脉冲就会发生类似“抖动”,继续重复。

比较功能子模块主要通过CMPA和CMPB主寄存器中的值不断的与世间基准计数器TBTCR相比较,值相等时,A和B才会产生比较独立的两个事件。

供事件的独立控制。

二·实验内容本次实验主要是为了理解在EPWM模块中一些子模块的原理,可以在例程中进行一定的修改来达到目的。

第五章(2) TMS320C5x芯片的外部接口

对串行通讯口的控制是通过对内存映射 寄存器的操作实现的。 串口和CPU的联系是通过中断实现的。

C54系列DSP串口配置表:

串行通讯端口

在C54X的处理器中有四种不同类型串行通讯端口: BSP串口可以工作在自动缓冲方式和无缓冲方式,当工 作在无缓冲方式时,BSP串口和SP串口是相同的 ; TDM串口可以工作在 TDM 模式或 non-TDM 模式。当工 作在non-TDM 模式时,TMD串口和SP串口是相同的; 在所有的C54x DSP 串口中,发送和接收都是双缓冲的 (double-buffered),允许数据包以连续数据流的方 式传送; 对于标准串行通讯口,传输的最大速度CLROUT的1/4。

SOFT and FREE

13.RSRFULL:

接收移位寄存器满指示(read-only) 指示接收的移位寄存器是否溢出。当RSR装 入数据后,DRR中的数据仍未读取,即产生 溢出指示。 RSRFULL 是一个指示位(只读位), RSRFULL = 1时, RSR 是满的。

13.RSRFULL:

串行通讯接口

TMS320C54X串行接口分类(四种): 标准同步串行口 Standard synchronous serial port interface 缓冲串行口 Buffered serial port interface 多通道缓冲串行口 Multichannel buffered serial Port (McBSP) interface 时分多路串行口 Time-division multiplexed serial port interface

下面的任意一种情况都可以清除RSRFULL: 1、 DRR数据被读取; 2、 串口复位;(RRST = 0), 3、 DSP芯片复位;(RS = 0)

TMS320C54x数字信号处理器硬件结构

在片仿真接口 ● 具有符合IEEEll49.1标准的在片仿真接口(JTAG)。 速度 ● 单周期定点指令的执行时间为25/20/15/15/10-ns(40 MIPS/50 MIPS/66 MIPS/80 MIPS/100

MIPS)。

图1 TMS320C54x DSP的内部硬件组成框图1

返回本节

保留 (DROM=1) 外部(DROM=0)

FFFFH

MP/ MC=0 (微型计算机模式)

图2 TMS320VC5402存储器分配图

0 0000H

Page 0 64K

1 0000H

1 3FFFH 1 4000H

Page1: 低16K

外部

Page1: 高48K

外部

2 0000H

2 3FFFH 2 4000H

返回首页

3 TMS320C54x的存储器分配

● 3.1 存储器空间 ● 3.2 程序存储器 ● 3.3 数据存储器 ● 3.4 I/O存储器

返回首页

3.1 存储器空间

● TMS320C54x存储器由3个独立的可选择空间组成:程序空间、数据空间和I/O空间。 ● 程序存储器空间包括程序指令和程序中所需的常数表格;数据存储器空间用于存储需要程序处理

在片外围电路(如图1所示) ● 软件可编程等待状态发生器。 ● 可编程分区转换逻辑电路。 ● 带有内部振荡器。 ● 外部总线关断控制,以断开外部的数据总线、地址总线和控制信号。 ● 数据总线具有总线保持器特性。 ● 可编程定时器。并行主机接口(HPl)。

电源 ● 可用IDLEl、IDLE2和IDLE3指令控制功耗,以工作在省电方式。 ● 可以控制关断CLKOUT输出信号。

图1 TMS320C54x DSP的内部硬件组成框图2

TMS320C55x硬件设计实例

04

使用触发器或延迟链技术,实

现精确的时序控制。

05

通过仿真和测试,验证时序优

化效果并调整参数。

06

06

TMS320C55x常见问题 与解决方案

启动问题

启动问题

在TMS320C55x硬件设计过程中,有 时会出现启动失败的问题,这可能是 由于电源不稳定、复位电路故障、启 动配置错误等原因造成的。

解决方案

04扩Biblioteka 板设计扩展板是为了满足特定应用需 求而设计的,可以添加额外的

功能模块和接口。

扩展板的设计需要考虑与核心 板的接口匹配,以及与其他扩

展板的互操作性。

扩展板上的元件布局和布线同 样要合理,以确保信号完整性 和减小电磁干扰。

扩展板的尺寸和重量也需要考 虑,以满足实际应用的需求。

接口板设计

接口板是用于连接外部设 备的板卡,如串口、并口、 USB等。

详细描述

TMS320C55x系列DSP具有高速的运算能力和高效的数字信号 处理算法,能够快速处理大量的图像数据。通过使用 TMS320C55x,可以实现高效的图像压缩、图像增强和图像识 别等功能。

信号处理

总结词

TMS320C55x系列DSP在信号处理领域具有出色的实时信号处理能力和高效的算法,适用于通信信号 处理、雷达信号处理、振动信号处理等应用。

低功耗

TMS320C55x采用低功耗设计, 能够在保证性能的同时降低功耗, 延长设备的使用时间。

集成度高

TMS320C55x集成了丰富的外设 接口,如串口、GPIO等,方便与 其他硬件设备进行连接和控制。

应用领域

音频处理

TMS320C55x强大的数字信号处理能力使其成为音频处理领域的 理想选择,如音频编解码、音频效果处理等。

DSP-CH5

2.初始化、中断和复位信号引脚的说明

名称

IACK

I/O/Z 说

明

O/Z 中断响应信号。IACK有效时,表示接受一 次中断,程序计数器按照A15~A0所指令的 位置取出中断向量。当EMUl/OFF为低电平 时,IACK也变成高阻状态 INT0,1 外部中断请求信号。INT0~INT3的优先级为: INT0 最高,依次下去, INT3 最低。可以用 2,3 中断屏蔽寄存器和中断方式位屏蔽; IN 可 以通过中断标志寄存器进行查询和复位 NMI

TDI

I

IEEE标准1149.1测试数据输入端。带有内部上拉电阻。 在 TCK 时钟的上升沿,将 TDI 记录到所选定的寄存器 (指令寄存器或数据寄存器) IEEE标准1149.1测试数据输出端。在TCK的下降沿, 将所选定的寄存器中的内容移位到 TDO端。除了在进 行 数 据 扫 描 时 外 , TDO 均 处 在 高 阻 状 态 。 当 EMUl/OFF为低电平时,TDO也变成高阻状态 IEEE标准1149.1测试方式选择端。此引脚带有内部上 拉电阻。在 TCK时钟的上升沿,此串行控制输中断。NMI是一种外部中断,不能够 用中断屏蔽寄存器和中断方式位对其屏蔽。 当NMI而有效时,处理器从非屏蔽中断向量 位置上取指令。

引脚 I/O/ 说 名称 Z

明

RS

I

MP/M I C

复位信号。 RS 有效时, DSP 结束当前正在 执行的操作,强迫程序计数器变成 0FF80h; 从程序存储器的 0FF80h 单元开始执行程序。 RS对许多寄存器和状态位有影响。 微处理器/微型计算机方式选择引脚。如果复 位时此引脚为低电平,就工作在微型计算机 方式,片内程序ROM映象到程序存储器高地 址空间。在微处理器方式时,DSP对片外存 储器寻址

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

2 主机接口(HPI)

(1)HPI结构 HPI是一个8位并行口,是C54x与主处理器接口。

HPI数据锁存器

(HPID)

HPI控制寄存器

(HPIC)

HPI存储器

(

DARAM)

HPI地址寄存器

(HPIA)

HPI控制逻辑

• HPI存储器(2k*16的DARAM)

– 用于C54x与主机之间传输数据,作为双方通信的数据缓 冲区

Free soft

定时器状态

0

0 定时器立即停止工作

0

1 当计数器减到 0时停止工作

1 × 定时器继续运行

9~ PSC - 定 时 器 预 先 定 标 计 数 器 。 这 是 一 个 减 1 计 数 器 , 当 PSC 减

到 0 后 。 TD D R 位 域 中 的 数 加 载 到 PSC, TIM 减 1

(3)HPI控制寄存器HPIC(四个控制位)

BOB:字节选择位,BOB=1,第一个字节是低八位; BOB=0,第一个字节是高八位,只能主机读写。(0位)

SMOD:寻址方式选择位,确定HPI 中的DARAM存储单 元使用方式(1,共用(SAM);0,仅主机(HOM))。C54X可读 写,主机只能读。 (第0位)

(4)定时器的基本定时时间可由下式计算 定时周期=CLKOUT×(TDDR+1)×(PRD+1)

当系统复位时,TIM和PRD都为FFFFH,TCR 中的TDDR全部清零。 当使用定时器时,必须对其进行初始化 。

(5)初始化定时器的步骤如下:

①对寄存器TCR中的TSS位置1,停止定时器工作;

②装入TIM初值;

PRD :周期寄存器 TIM :定时寄存器(-

1计数器) TCR :定时器控制寄

存器 TDDR:定时器分频系

数寄存器 PSC:定时器预先定

标计数器

8

三个相关寄存器: TIM定时寄存器(0024H):加载定时值,减1计数器 ; PRD定时周期寄存器(0025H):存放定时时间常数 ; TRC定时器控制寄存器(0026H):存储定时器的控制及状态位;

5 TRB - 定 时 器 重 新 加 载 位 ,用 来 复 位 片 内 定 时 器 。当 TRB 置 1 时 ,

以 PRD 中 的 数 加 载 TIM , 以 及 以 TD D R 中 的 值 加 载 PSC。

TRB 总 是 读 成 0

4 TSS

0 定 时 器 停 止 状 态 位 , 用 于 停 止 或 启 动 定 时 器 。复 位 时 , TSS

期监测等功能。

例如:用定时器设计一个周期为4ms的方波信号发生器。

假设DSP主频为4MHZ(TCLKOUT=250ns), 方波信号周期为4ms,那么定时 中断周期应为T=2MS,每中断一次,输出端电平取反一次。

③装入PRD初值;

④装入TCR(初始化TDDR和启动定时器;使TSS清0可以产生 CLKOUT信号,使TRB置位,重新装入定时初值。

⑤对IMR中的TINT位置1,使能定时器中断;使ST1状态寄存器 INTM位清0,开放所有的中断。

(6)定时器的使用 用定时器可以实现方波发生器、脉冲频率监测器、周期信号周

Dr. JI ZHEN

10

(3)定时器的工作过程: 定时器的基准工作脉冲由CLKOUT提供,定时器的工作过程: 每来一个脉冲,预定标计数器PSC减1,当PSC减至0,下一个脉冲 到来时,PSC产生借位。借位信号分别控制TIM减1和重新将TDDR 的内容加载预定标计数器PSC,每次定时计数器TIM 减为0时产生 定时中断TINT 。

(2)TRC定时器控制寄存器各位含义

15-12

11

保留

soft

10

9-6

5

4

3-0

free

PSC

TRB

TSS TDDR

预定标 定时器重 定时器停 定时器分 新加载1 止状态1 频系数

定时器控制寄存器(TCR)的功能

位 15~12

11 soft 10 Free

功

能

- 保 留 ;读 成 0

0 Soft 和 Free 位 结 合 起 来 使 用 , 以 决 定 在 H LL 调 试 程 序 遇 0 到断点时定时器的工作状态。

• 引脚HCNL0=0、HCNL1=1,主机读写HPID,完成主机对 HPI存储器的读写。

(5) HPI中断过程

• 主机向C54X发中断:即主机向HPIC的DSPINT位写1。 • C54X向主机发中断:即CX54X向HPIC的HINT位写1。

2 定时器

(1)定时器结构

片内定时器方框图

Dr. JI ZHEN

DSPINT:主机向C54X发出的中断请求,只能主机写。 (第1位)

HINT: C54X向主机发出的中断请求,只能由主机复位, C54X置位。 (第3位)

(4) HPI工作过程

• 引脚HCNL0=0、HCNL1=0,主机写HPIC,确定HPI接收和 存储器读写方式。

• 引脚HCNL0=1、HCNL1=0,主机写HPIA,确定主机对HPI 存储器读写的首地址。

HD0--HD7: 双向数据总线; HCS:输入,片选信号,HPI使能输入端;(地址线或控制线) HAS:输入,地址选通信号;(ALE) HBIL:输入,字节识别; HCNL0、HCNL1:输入,主机控制信号,用来选择HPI寄存器

0、0,HPIC寄存器 0、1,HPID寄存器,读写HPID,HPIA+1 1、0,HPIA寄存器 1、1,HPID寄存器,HPIA不受影响。 HDS1、HDS2、数据选通信号;(读写选通) HINT:输出,HPI中断输出 HRDY:输出,HPI准备好 R/W:输入,读/写信号

位清零,定时器立即开始定时。

TSS=0 定 时 器 启 动 工 作

TSS=1 定 时 器 停 止 工 作

3~0 TDDR 0000 定 时 器 分 频 系 数 。 按 此 分 频 系 数 对 CLKOUT 进 行 分 频 , 以

政 变 定 时 周 期 。当 P S C 减 到 0 后 ,以 T D D R 中 的 数 加 载 P S C

– HPI地址寄存器(HPIA,只能由主机访问) – 主机当前寻址的DARAM存储单元地址(地址:1000H—17FFH)

• HPI数据锁存器(HPID,只能由主机访问)

– 主机读写数据的缓存

• HPI控制寄存器(地址:002Ch) • HPI控制逻辑(HPIC)

– 处理HPI与主机之间的接口信号

(2)主机与DSP的连接方式