综合测试题七

七年级上册生物综合测试试题附部分答案

七年级上册生物综合测试试题附部分答案一、单选题1.下列关于被子植物生长的描述,正确的是A.植株生长所需的水分主要由伸长区的根毛吸收B.植物的茎都能逐年加粗C.植物生长需要量最多的是含铁、磷、钾的无机盐D.植物的枝条及绿叶都是由芽发育而成的2.图所示的瓶子内装有正在萌发的种子,24小时后,把点燃的蜡烛放入瓶中,蜡烛熄灭,其原因是()A.种子进行呼吸作用,消耗了氧气B.种子进行蒸腾作用,放出了大量的水蒸气C.种子进行光合作用,放出了氧气D.种子进行呼吸作用,消耗了二氧化碳3.盐碱地不利于种植农作物是因为盐碱地()A.容易造成土壤缺水B.土壤温度过低C.土壤易于板结而缺氧D.土壤溶液浓度大于植物细胞液浓度4.2008年贺州市遭受罕见的冰冻灾害,造成某些植物死亡,这种现象说明()A.生物能影响环境B.环境能影响生物的生活C.生物能适应环境D.生物能生长、发育和繁殖5.含羞草受到刺激后会发生叶片合拢的现象,与此生理现象相同的是()A.植物的光合作用B.人的手被针刺后缩回C.人出汗和排尿D.母鸡下蛋6.世界人口不能无限制增加,否则人类就不能正常的生存,因为生物的生存需要()A.空气B.阳光C.适宜的温度D.一定的空间7.下列有关保卫细胞的说法中,正确的是()A.圆柱形细胞,含叶绿体B.半月形细胞,含叶绿体C.圆柱形细胞,不含叶绿体D.半月形细胞,不含叶绿体8.下列结构中,属于种子的主要部分是:A.胚乳B.胚C.胚芽D.种皮9.下图曲线表示一段时间内某植物叶片吸收二氧化碳与光照强度的关系。

以下分析正确的是()A.N点表示该植物既不进行光合作用也不进行呼吸作用B.MP段表示该植物的光合作用随光照强度的增强而增强C.MN段表示该植物只进行呼吸作用D.NP段表示该植物只进行光合作用10.夏季,植物体吸收的水分主要用于()A.进行光合作用B.进行呼吸作用C.进行蒸腾作用D.保留在植物体内11.叶芽中发育成叶的结构是()A.芽B.芽原基C.叶原基D.幼叶12.图中是某生态系统中的食物网示意图。

七年级数学综合测试题

七年级数学综合测试题一、选择题(每小题4分,共40分)1.2的相反数和绝对值分别是( )A.2,2B.-2,2C. -2,-2D.2,-2 2.如果a 和2b 互为相反数,且b ≠0,那么的a 的倒数是( )A.b 21-B.b 21C.b2- D. 2b3.计算22651251⨯+⨯-的值是( )A.0B.532C.54D.54-4.已知a 、b 两数在数轴上的位置如图所示,则化简代数式12a b a b +--++的结果是( )A. 1B.2b +3C.2a -3D.-15.已知有一整式与)2522-+x x (的和为)4522++x x (,则此整式为( ) A. 2 B.6 C.10x +6 D. 21042++x x6.下列四个说法中,正确的是( ) A .相等的角是对顶角B .平移不改变图形的形状和大小,但改变直线的方向C .两条直线被第三条直线所截,内错角相等D .两直线相交形成的四个角相等,则这两条直线互相垂直7.同一平面内的四条直线若满足a ⊥b ,b ⊥c ,c ⊥d ,则下列式子成立的是( ) A .a ∥d B .b ⊥d C .a ⊥d D .b ∥c 8.下列式子是因式分解的是( ) A .x (x ﹣1)=x 2﹣1 B .x 2﹣x=x (x +1) C .x 2+x=x (x +1)D .x 2﹣x=x (x +1)(x﹣1)9.如果x 2+kx +25是一个完全平方式,那么k 的值是( ) A .5B .±5C .10D .±1010.已知∠A ,∠B 互余,∠A 比∠B 大30度.设∠A ,∠B 的度数分别为x °、y °,下列方程组中符合题意的是 ( )A. B.C. D.二、填空题(每小题4分,共24分)11.如果)3(2+x 的值与)1(3x -的值互为相反数,那么x 等于_____.12.足球比赛的计分规则是:胜一场得3分,平一场得1分,负一场得0分.一队打14场,负5场,共得19分,那么这个队共胜了_____场.13.如图,AB ︰BC ︰CD=2︰3︰4,AB 的中点M 与CD 的中点N 的距离是3cm ,则BC=______.14.如图,直线l 1∥l 2,AB ⊥EF ,∠1=20°,那么∠2= .15.如图,已知a ∥b ,小亮把三角板的直角顶点放在直线b 上.若∠1=40°,则∠2的度数为 .16.对于任意两个实数对(a ,b )和(c ,d ),规定:当且仅当a=c 且b=d 时,(a ,b )=(c ,d ).定义运算“⊕”:(a ,b )⊕(c ,d )=(ac ﹣bd ,ad +bc ).若(1,2)⊕(p ,q )=(5,0),则p= ,q= .三、解答题(共36分)17.(4分)已知a 、b 互为相反数,c 、d 互为倒数,x 的绝对值是2, 求201220112)()()(cd b a x cd b a x -+++++-的值.A MB DC N第15题图18.(6分)先化简,再求值:(x+3)2+(x+2)(x﹣2)﹣2x2,其中x=﹣.19.(12分如图,△ABC中,∠B=10°,∠ACB=20°,AB=4cm,△ABC逆时针旋转一定角度后与△ADE重合,且点C恰好成为AD的中点.(1)指出旋转中心,并求出旋转的度数;(2)求出∠BAE的度数和AE的长.20.(14分某单位欲从内部招聘管理人员一名,对甲、乙、丙三名候选人进行了笔试和面试两项测试,三人的测试成绩如下表所示:根据录用程序,组织200名职工对三人利用投票推荐的方式进行民主评议,三人得票率(没有弃权票,每位职工只能推荐1人)如图所示,每得一票记作1分.(1)请算出三人的民主评议得分;(2)如果根据三项测试的平均成绩确定录用人选,那么谁将被录用;(精确到0.01)(3)根据实际需要,单位将笔试、面试、民主评议三项测试得分按4:3:3的比例确定个人成绩,那么谁将被录用?。

人教版七年级地理上册综合测试练习题(含答案)

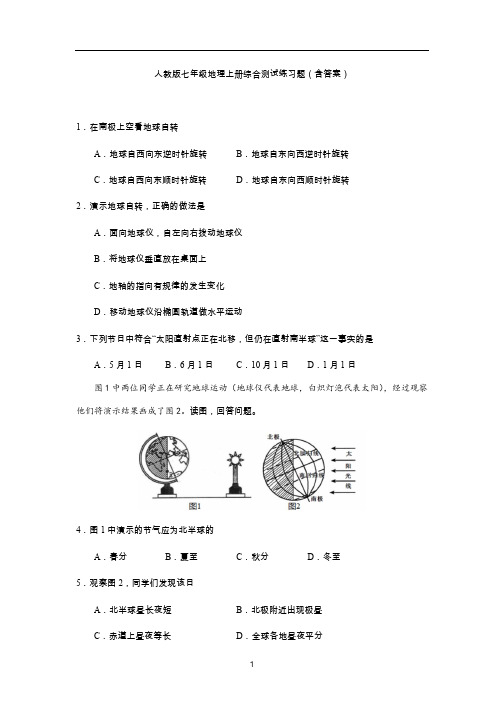

人教版七年级地理上册综合测试练习题(含答案)1.在南极上空看地球自转A.地球自西向东逆时针旋转B.地球自东向西逆时针旋转C.地球自西向东顺时针旋转D.地球自东向西顺时针旋转2.演示地球自转,正确的做法是A.面向地球仪,自左向右拨动地球仪B.将地球仪垂直放在桌面上C.地轴的指向有规律的发生变化D.移动地球仪沿椭圆轨道做水平运动3.下列节日中符合“太阳直射点正在北移,但仍在直射南半球”这一事实的是A.5月1日B.6月1日C.10月1日D.1月1日图1中两位同学正在研究地球运动(地球仪代表地球,白炽灯泡代表太阳),经过观察他们将演示结果画成了图2。

读图,回答问题。

4.图1中演示的节气应为北半球的A.春分B.夏至C.秋分D.冬至5.观察图2,同学们发现该日A.北半球昼长夜短B.北极附近出现极昼C.赤道上昼夜等长D.全球各地昼夜平分6.图示季节,下列现象在北京市可能出现的是A.同学们穿着短袖衣衫上学B.正在放暑假C.正午房屋的影子在一年中最长D.昼长夜短7.关于东西半球的叙述,正确的是A.东经度的范围都在东半球B.20°W~0°~160°E的经度范围为东半球C.180°经线在东半球D.本初子午线、180°经线是东西半球的界线下图中的阴影部分表示的是2022年世界杯举办国。

读图,完成下题。

8.该国位于A.南半球、高纬地区B.北半球、中纬地区C.东半球、低纬地区D.西半球、低纬地区9.小明查阅的三张地图图幅相同,其中比例尺最大的是A.甲图B.乙图C.丙图D.一样大10.在图例中,表示水库的是A.B.C.D.11.了解和正确选择、使用地图,可以方便我们的生活。

有关下列四幅地图的叙述,错误的是A.家住云南的小明想去北京旅游,可从乙图上查找乘车路线B.小明想知道世界甲型流感的疫情情况,可通过阅读甲图了解C.小明来到北京后,购买了丁图以便了解旅游景点的分布情况D.若四幅图的图幅面积相同,则比例尺大小应是甲>乙>丙>丁12.如图所示,某地等高线地形图所示,图中示坡线(虚线)表示山谷,若在山谷中突然发生泥石流,你认为哪条线路成功逃生的几率最大?A.甲B.乙C.丙D.丁13.世界海陆的分布特点是A.陆地全部集中在北半球B.地球表面陆地面积比海洋面积大C.南极地区是海洋,北极地区是陆地D.海洋主要集中在南半球,但南极周围却是一片陆地14.根据板块构造学说,印度与我国接壤的山地主要形成于A.印度板块与印度洋板块的挤压B.印度洋板块与亚欧板块的张裂C.印度洋板块与亚欧板块的挤压D.印度洋板块与南亚板块的张裂15.下列哪些措施可有效减少雾霾天气的形成①禁止使用煤炭、石油等化石能源②大力发展公共交通,减少汽车尾气排放③调整能源消费结构,使用清洁能源④倡导低碳生活,增强全民的减排意识A.①②③B.①③④C.②③④D.①②③④下图是北京天气预报软件截图。

七年级有理数综合测试题

七年级有理数综合测试题一、选择题(每题2分,共30分)1.1999年国家财政收入达到11377亿元,用四舍五入法保留两个有效数字的近似值为()元。

A.1.1⨯10B.1.1⨯10C.11.4⨯10.D.1.14⨯102.若a 、b 在数轴上对应的点在原点两侧,并且到原点的位置相等;c 、d 互为倒数,m 的绝对值为2,则代数式m -cd +212131112a +b 的值为()m A.-3 B.3 C.-5 D.3或-53.如果两个有理数的积是正数,和也是正数,那么这两个有理数()A.同号,且均为负数B.异号,且正数的绝对值比负数的绝对值大C.同号,且均为正数D.异号,且负数的绝对值比正数的绝对值大4.在下列说法中,正确的个数是()⑴任何一个有理数都可以用数轴上的一个点来表示;⑵数轴上的每一个点都表示一个有理数;⑶任何有理数的绝对值都不可能是负数;⑷每个有理数都有相反数。

A.1B.2C.3D.45.下列说法正确的是()A.几个有理数相乘,当因数有奇数个时,积为负;B.几个有理数相乘,当正因数有奇数个时,积为负;C.几个有理数相乘,当负因数有奇数个时,积为负;D.几个有理数相乘,当积为负数时,负因数有奇数个。

6.如果a <0,那么a 和它的相反数的差的绝对值等于()A.aB.0C.-aD.-2a7.下列说法错误的是()A.数轴的三要素是原点、正方向、单位长度。

B.数轴上的每一个点都表示一个有理数。

C.数轴上右边的点总比左边的点所表示的数大。

D.表示负数的点位于原点左侧。

8.下列运算结果属于负数的是()A.-(1-98×7)B.(1-9)×8-7C.-(1-98)×7D.1-(9×8)×(-7)9.若a <0,b >0,且︱a ︱<︱b ︱,那么下列式子中结果是正数的是()A .(a-b )(ab+a )B .(a+b )(a-b )C .(a+b )(ab+a )D .(ab-b )(a+b )10.若ab =|ab |,必有()A.ab 不小于0B.a ,b 符号不同C.ab >0D.a <0,b <011.下列说法不正确的是()A.0既不是正数,也不是负数B.1是绝对值最小的数C.一个有理数不是整数就是分数D.0的绝对值是012.下列交换加数的位置的变形中,正确的是()A.1-4+5-4=1-4+4-5B .-13111311+--=+--34644436C. 1-2+3-4=2-1+4-3D.4.5-1.7+1.8-2.5=4.5-2.5-1.7+1.813.下列说法中正确的是()A.最小的整数是0B.互为相反数的两个数的绝对值相等C.有理数分为正数和负数D.如果两个数的绝对值相等,那么这两个数相等14.学校、家、书店依次坐落在一条南北走向的大街上,学校在家的南边20米,书店在家北边100米,张明同学从家里出发,向北走了50米,接着又向北走了-70米,此时张明的位置在()A.在家B.在学校C.在书店D.不在上述地方15.有以下两个结论:①任何一个有理数和它的相反数之间至少有一个有理数;②如果一个有理数有倒数,则这个有理数与它的倒数之间至少有一个有理数。

人教版英语七年级下期末综合测试题

英语七年级下期末综合测试题The document was prepared on January 2, 2021七下期末综合测试题姓名________ 班级________ 学号________ 成绩________一、单选题20分1. —Can you play____ football—No, but I can play _____ piano well.A. the; /B. /; theC. /; /D. the;theis a big tree_____ our classroom .A. in the front ofB. in front ofC. at the back ofD. in the center of3.—What`s the weather like in Beijing now—It`s ______.A. snowingB. snowyC. snowsD. snow4. —______—It`s 9:30.A. What`s the date todayB.What time is itC. What day is it todayD. When were you born 5. —You look very tired. ______ stopping to have a rest— All right. A. Why not B. How about C. Why not to D. Why don`t6.—_____ do you play computer games —Once a week.A. How longB. How manyC. How oftenD. How much7. Maria enjoys _____ music. And she can sing a lot of songs.A. listeningB. to listen toC. to listeningD. listening to8. I`d like a bowl of noodles ________ beef.A. haveB. hasC. withD. of9. Bill is ____ 8-year-old boy.A. an C. the D. that`s about 2 kilometers ____ my home school.... as ......to... ...as......from.... Li lives on the ___ floor楼层.A. 13B. 13thC. 13nd12. My bag is small. Can I use ________A . yours, B. you, C. your, D. yourself13. —I can`t find my mobile phone, mom. _______ is it—Peter, it`s on your bed.A. WhatB. WhereC. WhenD. How14. _______ is my brother. ______ name is Jack.A.This ; heB. This; hisC. his; isD. he; this15.—I`m going to Guiyang for my holiday this weekend.—_____a great timeB. You can`t goC. Best wishes to youD. Please gois looking for the watch his uncle _______ him last month.give given17.—I’ll have a ten-day holiday. But I don’t know _______.—How about Paristo do to go to go D. how to dohouse is too _______ for me to buy. I don’t have so much money. feed grass ______horses.heard someone _______ in the classroom when I passed by just now. sing二、完形填空15分Do you think of your parents “Yes, of course. ” you may answer, “I buy a present for my mother on 1 . And I give my father a present on Father’s Day, too. ” Then what about the other days of a yearAlways 2 to think of your parents, not just on some 3 days. I have a friend. She 4 alone, because her parents live in a different city. One day I went to see her. We had a nice talk. Then she wanted to make a telephone call. She dialed 拨 the number, but then she put the phone 5 . After about ten seconds, she dialed the number ag ain. “Hi, Mom …”Later, I asked, “Why did you dial the number 6 ”She said, “My parents are old. They can`t get 7 the telephone quickly. I always do so when I call them. I just want to give them 8 time to answer the call. ”My friend is just such这样 a good girl. She is always 9 her parents, so why not 10her You`ll also be a good son or daughter.1. `s Day`s Day ’ Day `s Day2. A. ask B. forget C. stop D. remember3. A. specialB. InterestingC. difficultD. boring4. A. liveB. livesC. livedD. living5. A. upB. awayC. downD. on6. A. once B. twice C. three times D. four times7. A. far fromB. behindtothe end of8. A. few B. a littleC. manyD. little9. A. thinking about B. putting away for D. listening to10. A. ask B. learn fromC. talk aboutD. miss三、阅读理解20分AWang Xiaojun is 12 years old. He lives in the country in Hubei. Today is his birthday. His parents prepare a nice dinner for him, but the boy says, “I won’t have the dinner because after the dinner, today is over, and my parents are going to Shenzhen tomorrow. Idon’t want to let them go. ” Wang Xiaojun has the birthday with his parents for the first time in the past three years. Three years ago, his parents went to Shenzhen to work. They stayed and worked there for three years. Tomorrow they have to go back to is not the only stay-at-home child. In the country of China, there are many children staying at home without 没有 their parents. Stay-at-home children have a lot of problems. Most of them stay with their grandparents. Some of them don’t study well b ecause their parents can’t help them with their Chinese government 政府 now is trying to solve 解决 their problems.1. When was Wang Xiaojun bornA. In 2000.B. In 2006.C. In 2012.D. In 2007.2. Wang Xiaojun won`t have the birthday dinner because ___.A. there isn`t a birthday cakeB. the food is not deliciousC. his parents are going to Shenzhen tomorrowD. he doesn`t like the dinner3. Wang Xiaojun didn`t have the birthday with his parents in the past years.A. twoB. threeC. fourD. five4. The“stay-at-home child”means _______ in Chinese.A. 住家儿童B. 顽皮孩子C. 留守儿童D. 离家儿童of the following is NOT trueA. There are a lot of children like Wang Xiaojun in China.B. The Chinese government is trying to solve these problems.C. Wang Xiaojun’s parents go to Shenzhen to make money.D. Stay-at-home children don’t have any problems.BDo you like sandwiches Do you know the story of “sandwich”Many years ago, in England anEarl 伯爵 of Sandwich liked playing cards. He liked to play for money. He played very well and he often played all day and all night. Once曾经he played for 24 hours without stopping. He didn’t stop to eat. His servants had to bring food to him. They gave him some meat and some bread, but he didn’t want to stop playing cards to eat them. He put the meat between two pieces of bread. In this way, he needn’t stop playing cards when he had the bread with meat. Later people call this kind of food “sandwich” from his name.6. The word “sandwich” come from ____.A. AmericaB. EnglandC. ChinaD. Japan7. In Chinese, the underline word “servant” means ____.A. 仆人B. 父母C.牌友D.妻子8. The servants gave him some ____ to eat.A. meatB. breadC. fruit and B9. The Earl liked to play cards for ____.A. fun.B. moneyC. energyD. food10. The Earl of Sandwich didn’t stop to eat because he ____.A. wasn`t hungryB. didn`t like sandwichesC. didn`t want to stop playing cardsD. had no time四、用单词的适当形式填空10分1.The teacher is ________have a meeting now.2.–Where did you go3.-I _______go to the mountain.4.5.We decided _______visit friends.6.That made me _______feel very sad.7.Swimming in summer is _______real fun.8.I think she can _______dance very well.9.There are some ______tomato and some beef in the noodles.10.It’s 7:15 am. It’s time _______go to school.11.As a student, we can’t a_______ late for school.12.His uncle has medium b_______ with black hair.五、按要求完成句子10分1.汤姆正在唱一首英文歌.翻译成英文句子2. Jane played the piano last weekend.改一般疑问句3. He is late for school because his bike is broken. 对划线部分提问4. They are having a Chinese class in the classroom.改否定句5. They are playing football.反义疑问句六、情景交际10分T: What are your favorite sportsB: Well, __1__.T: Now, tell me what you like to eatB: Err, I like fish and eggs. But __2__ any meat.T: __3__B: Oh, yes. I love vegetables.T: Do you drink wine酒B: No, I never drink wine or coffee. __4__.T: __5__B: I drink a lot of milk. It’s very good for my health.morning, Bob goes to visit his grandmother with his parents. 2.__________His grandmother lived in a beautiful village. There Bob 3.__________went to the mountains with her cousin. After lunch, he 4.__________played chess with his father. In the evening, he watched a 5.__________exciting TV show. In Sunday morning, Bob wanted to 6.__________play soccer but the weather was bad. So he played guitar 7.__________with his uncle. In the afternoon, he did his homeworks. Then 8.__________he went shop at a supermarket. In the evening, he studied 9.__________to the math test. At about 10:00pm, it was time to go to bed. 10. __________。

七年级生物上册综合测试题及答案

七年级生物上册综合测试题及答案以下是给你推荐的七年级生物上册综合测试题及参考答案,希望对你有帮助!七年级生物上册综合测试题一、选择题:请将正确答案的序号填入下表的答题框中(每题3分,共45分)1.下列除哪项外,都是生命特征的表现( )A.蜻蜓点水 B.种子萌发 C.森林着火 D.人的呼吸 2.下列哪个区域不属于生物圈的范围( )A.大气圈的上部 B.大气圈的底部C.整个水圈D.岩石圈的上层3.地球上最大的生态系统是( )A. 海洋生态系统 B.生物圈 C.陆地生态系统 D.湿地生态系统 4.在下列影响兔子生存的环境因素中,哪种不属于非生物因素( )A.阳光 B.温度 C.狼 D.水5.“螳螂捕蝉,黄雀在后。

这句描述的是生物与生物之间的什么关系( )A.捕食B.竞争C.合作D.追逐6.发现DNA双螺旋结构的科学家是( )A.达尔文B.哈维C.林奈D.沃森和克里克7.现代生物学研究的重要方法是( )A.调查法B.实验法C.比较法 D.观察法8.下列哪项是探究“光对鼠妇生活的影响实验中的一组对照实验条件( )A.阴暗、明亮B.潮湿、干燥C.温暖、寒冷D.食物多、食物少9.苹果、梨等果树不能在热带地区栽种,主要受下列哪项因素的限制( )A. 温度 B.湿度 C.阳光 D.水分10.骆驼刺的地下根比地上部分长很多,因此适于生活在( )A.极地B.水中C.荒漠中D.高山上11.下列生态因素中,属于生物因素的是( )A.适宜的温度 B.土壤中的微生物C.水分D.阳光12.在下列生态系统中,自动调节能力最强的是( )A.温带草原B.热带雨林C.北方针叶林D.南方阔叶林13.玉米和水稻不能间作套种,起限制作用的生态因素是( )A.阳光B.空气C.水分D.温度14.影响小麦产量的生态因素不包括( )A.阳光和温度 B.植物高度和开花时间C.水分和土壤肥力D.害虫和田间杂草15.骆驼背上的驼峰是骆驼的一个重要标志,其驼峰的形成说明( )A.环境对生物的适应B.环境对生物的改造C.生物对环境的适应D.生物的结构与环境没有关系二、填空题(每空2分,共58分)16.生物的共同特征是多方面的,如绝大多数生物的生活需要吸人氧气,呼出_________;生物能对来自环境中的各种_________作出反应;除病毒外,生物都是由_________构成的。

七年级英语综合测试题及答案

七年级英语综合测试题及答案学而不思则罔,思而不学则殆,学习英语就是不断思考,不断进步的过程,以下是店铺为你整理的七年级英语综合测试题,希望对大家有帮助!七年级英语综合测试题一、.单项选择(共15小题;每小题1分,满分15分)1 My sister never ____ online .A goes b go C don’t go D doesn’t go2 Lily lives in Australia .I would like ___ an e-mail ___ her .A send ,toB to send , toC send ,forD to send ,with3 The boy ____ his homework ____ the weekend .He always plays in the computer .A don’t do, onB doesn’t do , atC isn’t do , onD does ,of4 ____ Lily or Lily want to download music from the Internet ?A DoB AreC DoesD Can5 I often help my mother ___ letters to my aunt in England .A sendsB sendC sendedD sending6 She likes ___ music ___ the Internet .A downloading , withB downloading ,fromC to download , useD to download , at7 My mother likes shopping ,___ my father doesn’t .A andB orC butD so8 There is ___ in my homes .I can only use it at school .A not computerB no computersC no computerD not computers9 He uses his laptops ___ his work .A toB onC aboutD for10 - ____ do you go to the cinema ?- Sometimes .A How manyB How longC How oftenD How much11____ the computer ,please .I’d like to go onlineA Turn onB Turn offC Turn upD Turn down12 - What abut ___ an email to Jack ?- OK .A sendB to sendC sendingD sends13 - I don’t know how to make tea .- First ,you get some hot water ready .___ put the tea in the cup .___ pour(倒) the hot water into the cup .A Then ,FinallyB And ,soC So ,butD And ,And14 - ____ do you go to the cinema ?- On Saturday evening .A How oftenB WhenC How longD What time15 Mr Chen ___ the door of the car for his wife .A openB opensC switchD switch on二、阅读理解(共20小题;每小题2分,满分40分)阅读下列短文,然后从每小题A、B、C、D四个选项中选出能回答所提问题或完成所给句子的最佳答案。

人教版七年级数学上册期末综合测试题(含答案)

一、单选题(每题3分,共30分)

1. 的相反数是( )

A.2022B. C. D.

2.下列结论成立的是( )

A.若 ,则 B.若 ,则 或

C.若 ,则 D.若 ,则 .

3.中国倡导的“一带一路”建设将促进我国与世界各国的互利合作,根据规划,“一带一路”地区覆盖总人口约为44亿人,这个数用科学记数法表示为()

∴ , ,

∴ .

20(1) (件),

∴产量最多的一天比产量最少的一天多生产35件,

故答案为:35.

(2)

(件),

(元),

∴本周该工厂应支付工人的工资总额是84500元.

21.(1)解:∵ 平分 , 平分 ,

∴ , ,

∴

,

故答案为: ;

(2) 平分 , 平分 ,

, ,即

;

(3) , ,

又 ,

,得 .

答: 为 秒.

A. B. C. D.

7.如图,下列说法正确的是( )

A.点 在射线 上B.点 是直线 的一个端点

C.射线 和射线 是同一条射线D.点 在线段 上

8.在平面内, , 在 的外部, 是锐角, 平分 , 平分 ,若 度数逐渐变大,则 变化情况是()

A.变大B.变小C.保持不变D.无法确定

9.在解方程 时,去分母正确的是( )

17.(1)

解:

;

(2)

解:

.

18.(1)解:2(2a2+9b)+(-3a2-4b)

;

(2)解:3x2y-[2xy2-2(xy-1.5x2y)+xy]+3xy2

当x=-3,y=-2时,

原式

.

七年级下册综合测试题带答案

生物七下册综合测试题班级:姓名:一、选择题(每题2分,共60分)1.在人的消化系统中,既有消化又有吸收功能的器官是()A.食道和大肠B.胃和小肠C.口腔和胃D.大肠和小肠2.下列有关小肠的结构特点与其吸收功能相适应的是( )。

①绒毛壁只有一层上皮细胞组成②小肠内表面有许多小肠绒毛③小肠绒毛内有毛细血管和毛细淋巴管④肠腺是黏膜上皮凹陷而成⑤小肠长5---6米⑥小肠内有胆汁、胰液、肠液等有多种消化液A.①④ B.①②③⑤ C.②④⑤ D.②③④⑥3.某人在阑尾炎手术后的康复期间,为了促进其伤口愈合,你建议他应该多吃一些()A.蔬菜 B。

水果 C。

粗粮 D。

奶、蛋、鱼、肉4.王婶的血液检验报告单上显示:红细胞为3.0(正常值3.5~5.0)×1012 个/L,血红蛋白为100(正常值110~150)g/L。

她除应多食用含蛋白质丰富的食物以外,还应多食用()A.含铁多的食物 B.含磷多的食物 C.含碘多的食物 D.含钙多的食物5. AA级绿色食品在生产过程中( )。

A.允许使用少量的化学合成物质 B.不允许使用任何化学合成物质 C。

允许添加增味剂 D.允许使用防腐剂6.前不久,网上出现一些“中、高考食谱”。

据《重庆晨报》报道,一女士听说“吃猪脑能补人脑而增加记忆”,于是,她天天给将参加考试的女儿做猪脑吃,结果,女儿吃得直拉肚子。

你认为下列哪道菜符合均衡膳食的要求()A.皮蛋肉丸汤B.豆腐白菜汤C.青菜排骨汤D.大骨鱼头汤7.在试管内加入2ml的食用油,再加入新配制的“X消化液”1mL,充分振荡后,置于37℃的温水中5分钟,发现植物油消失了。

则“X消化液”成分最可能是()A.唾液、胃液、肠液 B.胃液、胆汁 C.胰液、肠液、胆汁 D.胃液、胰液8.从下列哪个器官流出的血液中的氧气减少、废物增多、养料增多()A.肺 B.心脏 C.小肠 D.肾9.含细菌和灰尘的痰液产生于 ( )A.鼻腔黏膜 B.食道黏膜 C.喉腔侧壁 D.气管和支气管黏膜10.右图为人体血液循环过程中某物质含量在各血管内的变化情况。

七年级道德与法治上册 期末综合测试题

期末综合测试题(时间:60分钟总分:100分)第Ⅰ卷选择题(共45分)一、选择题(本大题共15小题,每小题3分,共45分。

在每小题列出的四个选项中,选出最符合题目要求的一项)1.中学生活把我们带进一个别样的天地,我们站在一个新的起点上。

下列对此认识正确的是( B )①中学生活,对我们来说意味着新的机会和可能②我们要珍惜这个新起点,体验初中生活的快乐③升入初中,我已经是个大人了,一切都要自己做主④我们需从点滴做起,付出努力,为以后的人生奠基A.①②③B.①②④C.①③④D.②③④2.生活在贫苦山村的小姜买不起颜料和画笔,但他怀揣着对家乡的热爱,用一支黑笔绘制了心中五彩斑斓的学校。

多年之后,他成为一位建筑设计师,建造出少年时想象的学校。

这启示我们( B )A.少年时的梦想最天真,不可能实现B.梦想要与个人的人生目标紧密相连C.少年许下的梦想与未来人生目标最接近D.只要在少年时有梦想,就一定能够成功3.右图给我们的启示是( C )A.学会学习,需要发现并保持对学习的兴趣B.学会学习,需要尽快掌握最好的学习方法C.学会学习,需要善于运用有效的学习方式D.学会学习,需要不断提升自己的学习能力4.终身学习,成就自己美好的未来;人人学习,成就祖国美好的明天。

终身学习对当代中学生的要求是( A )①珍惜在校学习机会②确立终身学习的观念③养成自主学习、合作学习的习惯④终身学习就是永远在校学习A.①②③B.②③④C.①③④D.①②④56.时候,会给你及时的支持和鼓励。

在你有缺点可能犯错误的时候,会给你正确的批评和帮助。

”这启示我们( D )A.最该结交那些见识广博的人B.与真正的朋友交往会减少犯错误C.只要真诚待人,就会交到真正的朋友D.要善交益友、不交损友、乐交诤友7.习近平总书记曾经指出,网络空间是亿万民众共同的精神家园。

但在网络交往中,信息良莠不齐,充满了许许多多的陷阱,这就需要青少年( A )①在网络交往中,学会理性辨别、慎重选择②沉溺于虚幻的网络,享受网上交友的快乐③把网上认识的朋友全都转化为现实中的朋友④增强自我保护意识,遇到问题学会求助A.①④B.②③C.①②D.③④8.一位老师看见一些同学只顾埋头刷题而忽视体育锻炼,就对同学们说:脑力劳动者每天至少要走十里路,这样看来占用了时间,实际上调剂了精神,增强了体质,会提高学习效率。

综合复习测试七

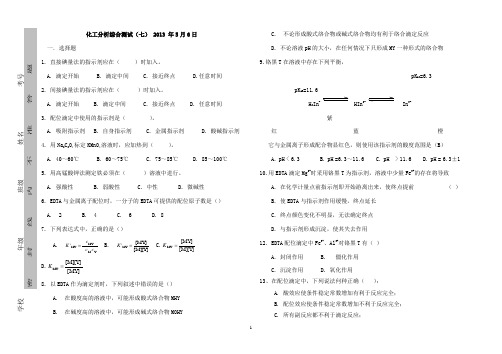

化工分析综合测试(七) 2013 年5月6日一.选择题1. 直接碘量法的指示剂应在( )时加入。

A. 滴定开始B. 滴定中间C. 接近终点D.任意时间 2. 间接碘量法的指示剂应在( )时加入。

A. 滴定开始B. 滴定中间C. 接近终点D. 任意时间 3. 配位滴定中使用的指示剂是( )。

A. 吸附指示剂B. 自身指示剂C. 金属指示剂D. 酸碱指示剂 4. 用Na 2C 2O 4标定KMnO 4溶液时,应加热到( )。

A. 40~60℃B. 60~75℃C. 75~85℃D. 85~100℃ 5. 用高锰酸钾法测定铁必须在( )溶液中进行。

A. 强酸性 B. 弱酸性 C. 中性 D. 微碱性 6. EDTA 与金属离子配位时,一分子的EDTA 可提供的配位原子数是() A. 2 B. 4 C. 6 D. 8 7. 下列表达式中,正确的是()A. Y M MY MY'c c c K = B. [Y ]]M [MY ]['MY =K C.[Y ]]M [MY ][MY =K D.MY ][M][Y ][MY =K 8. 以EDTA 作为滴定剂时,下列叙述中错误的是()A. 在酸度高的溶液中,可能形成酸式络合物MHYB. 在碱度高的溶液中,可能形成碱式络合物MOHYC. 不论形成酸式络合物或碱式络合物均有利于络合滴定反应D. 不论溶液pH 的大小,在任何情况下只形成MY 一种形式的络合物 9.铬黑T 在溶液中存在下列平衡,pK a2=6.3 pK a3=11.6H 2In -HIn 2- In 3-紫红 蓝 橙 它与金属离子形成配合物显红色,则使用该指示剂的酸度范围是(B ) A. pH < 6.3 B. pH =6.3~11.6 C. pH > 11.6 D. pH = 6.3±1 10.用EDTA 滴定Mg 2+时采用铬黑T 为指示剂,溶液中少量Fe 3+的存在将导致A. 在化学计量点前指示剂即开始游离出来,使终点提前 ( )B. 使EDTA 与指示剂作用缓慢,终点延长C. 终点颜色变化不明显,无法确定终点D. 与指示剂形成沉淀,使其失去作用 12. EDTA 配位滴定中Fe 3+、Al 3+对铬黑T 有( )A. 封闭作用B. 僵化作用C. 沉淀作用D. 氧化作用13、在配位滴定中,下列说法何种正确( ):A. 酸效应使条件稳定常数增加有利于反应完全;B. 配位效应使条件稳定常数增加不利于反应完全;C. 所有副反应都不利于滴定反应;D. 以上说法都不对。

人教版七年级下册数学期中综合测试题

七年级数学期中综合测试题一 选择题(每小题3分,共12题,共计36分)1.计算3的平方根是( )A.±3B.9C.3D.±9 2.下列运算中,正确的是( )A.9=±3B.283=-=2C.24=-D.8)8(2-=-3.在下列各数0、2.0 、π3、722、 1010010001.6、11131、27中,无理数的个数是( ) A.1 B.2 C.3 D. 4 4.平面直角坐标系中, 点(-2,4)关于x 轴的对称点在( )A. 第一象限B. 第二象限C. 第三象限D. 第四象限 5.如图,点E 在AC 的延长线上,下列条件中能判断...AB//CD ( )A.43∠=∠B.21∠=∠C.DCE D ∠=∠D. 180=∠+∠ACD D第5题图 第6题图6.如图,AB ∥CD ∥EF,AF ∥CG,则图中与∠A (不包括∠A )相等的角有( )A.1个B.2个C.3个D.4个7.某人在广场上练习驾驶汽车,两次拐弯后,行驶方向与原来相同,这两次拐弯的角度可能是( ) A.第一次左拐30°,第二次右拐30° B.第一次右拐50°,第二次左拐130° C.第一次右拐50°,第二次右拐130° D.第一次向左拐50°,第二次向左拐130°8.在平面直角坐标系中,线段A ′B ′是由线段AB 经过平移得到的,已知点A(-2,1)的对应点为A ′(3,1),点B 的对应点为B ′(4,0),则点B 的坐标为( )A .(9,0)B .(-1,0)C .(3,-1)D .(-3,-1)9.一个正方形的面积为21,它的边长为a,则a-1的边长大小为()A.2与3之间B.3与4之间C.4与5之间D.5与6之间10.一个长方形在平面直角坐标系中,三个顶点的坐标分别是(-1,-1)、(-1,2)、(3,-1),则第四个顶点的坐标是()A.(2,2)B.(3,3)C.(3,2)D.(2,3)11.给出下列说法:①两条直线被第三条直线所截,同位角相等;②平面内的一条直线和两条平行线中的一条相交,则它与另一条也相交;③相等的两个角是对顶角;④从直线外一点到这条直线的垂线段,叫做这点到直线的距离.其中正确的有()A.0个B.1个C.2个D.3个12.如图,如果AB//EF,EF//CD,下列各式正确的是()A.∠1+∠2﹣∠3=90°B.∠1﹣∠2+∠3=90°C.∠1+∠2+∠3=90°D.∠2+∠3﹣∠1=180°二填空题(每小题3分,共6题,共计18分)13.把命题“对顶角相等”改写成“如果……,那么……”形式为:;若x2=9,y3=-8,则x+y=__________;15.把一张长方形纸片ABCD沿EF折叠后ED与BC分别在M,N的位置上,若∠EFG=56°,则∠1=_______,16.已知点P(2a-6,a+1),若点P在坐标轴上,则点P17.如图,在平面直角坐标系上有个点P(1,0),点P 第1次向上跳动1个单位至点P 1(1,1),紧接着第2次向左跳动2个单位至点P 2(-1,1),第3次向上跳动1个单位,第4次向右跳动3个单位,第5次又向上跳动1个单位,第6次18.如图1,将三角板ABC 与三角板ADE 摆放在一起;如图2,固定三角板ABC,将三角板ADE 绕点A 按顺时针方向旋转,记旋转角∠CAE=α(0°<α<180°).当△ADE 的一边与△ABC的某一边平行(不共线)时,写出旋转角α的所有可能的度数为三 综合计算题(共7题,共计66分)19.(8分)计算:(1)364)13(23-+--- (2))63(2162+--+-20.(8分)解方程或方程组:(1)(1-2x)2 -36= 0(2)31252(1)4x -=-21.(8分)看图填空:已知如图,AD ⊥BC 于D,EG ⊥BC 于G,∠E =∠1.求证:AD 平分∠BAC 。

七年级数学上册期末复习综合测试题(含答案)

七年级数学上册期末复习综合测试题(含答案)一.精心选择(本大题有12小题,每小题2分,共24分)1.12021-的倒数是( ) A .2021- B .12021- C .2021 D .120212.关于直线,下列说法正确的是( )A .可以量长度B .有两个端点C .可以用两个小写字母来表示D .没有端点 3.下列说法不正确的是( )A .2a 是2个数a 的和B .2a 是2和a 的积C .2a 是偶数D .2a 是单项式4.下列各组中的两项,是同类项的为( ) A .25x y 与xyB .25x y -与2yxC .25ax 与2yx D .38与3x5.在下列方程中:①0x =;②21x y -=;③20n n +=;④532yy =+;⑤221x x -=+.其中一元一次方程的个数是( ). A .1 B .2 C .3 D .46.钟表上的时间指示为两点半,这时时针和分针之间的夹角为( ) A .120° B .105° C .100° D .90° 7.计算2136⎛⎫--- ⎪⎝⎭的结果为( ) A .12-B .12C .56-D .568.图(1)是一个长为2a ,宽为2b (a b >)的长方形,用剪刀沿图中虚线剪开,把它分成四块形状和大小都一样的小长方形,然后按图(2)那样拼成一个正方形,则中间空余的正方形的面积是( )A .abB .2()a b +C .22a b - D .2()a b -9.当1x =时,代数式31px qx ++的值为2021,则当1x =-时,31px qx ++的值为( ) A .2019- B .2021- C .2020 D .202110.如图,将一副三角板的直角顶点重合放置于点A 处(两块三角板看成在同一平面内),将其中一块三角板绕点A 旋转的过程中,下列结论一定成立的是( )A .BAD DAC ∠=∠B .BAD EAC ∠≠∠C .90BAE DAC ∠-∠=︒D .180BAE DAC ∠+∠=︒11.一件夹克衫先按成本价提高60%标价,再将标价打7折出售,结果获利36元,设这件夹克衫的成本价是x 元,那么根据题意,所列方程正确的是( ) A .0.7160%6()3x x +=- B .0.7160%6()3x x +=+ C .0.7160%6(3)x x +=-D .0.7160%6(3)x x +=+12.人行道用同样大小的灰、白两种不同颜色的小正方形地砖铺设而成,如图中的每一个小正方形表示一块地砖.如果按图①②③…的次序铺设地砖,把第n 个图形用图ⓝ表示,那么第50个图形中的白色小正方形地砖的块数是( )A .150B .200C .355D .505二.准确填空(本大题有6个小题,每小题3分,共18分)13.如果零上2℃记为2+℃,那么3-℃表示_______________. 14.3015︒'=__________°.15.一个长方形的宽为cm x ,长比宽的2倍多1 cm ,这个长方形的周长为__________cm .16.若27x a b 与3ya b -的和为单项式,则xy =_______.17.如图,线段AB 表示一根对折以后的绳子,现从P 处把绳子剪断,剪断后的各段绳子中最长的一段为32cm ,若12AP PB =,则这条绳子的原长为__________cm .18.做一个数字游戏:第一步:取一个自然数18n =,计算211n +得1a ; 第二步:算出1a 的各位数字之和得2n ,计算221n +得2a ; 第三步:算出2a 的各位数字之和得3n ,计算231n +得3a ;…,以此类推,则2021a =__________.三.细心解答(本大题有8个小题,共58分)19.(本小题满分6分)计算:()32142⎛⎫-⨯- ⎪⎝⎭20.(本小题满分6分)已知232A a ab b =-+-,22B a ab =-,化简2A B -.21.(本小题满分6分) 以下是小明解方程1323x x +--=1的解答过程. 解:去分母,得31231()()x x +--=.去括号,得31231x x +-+=.移项,合并同类项,得3x =-.小明的解答过程是否有错误?如果有错误,写出正确的解答过程. 22.(本小题满分6分)已知:如图,点D 、C 、E 是线段AB 上依次排列的三点,当点C 、D 分别是AB 和AE 的中点,且15AB =, 4.5CE =时,求线段CD 的长.23.(本小题满分8分)将连续偶数2,4,6,8,…排成如图数表.(1)十字框中的五个数的和与中间的数16有什么关系?(2)设中间的数为a ,用代数式表示十字框中的五个数的和.(3)若将十字框上下左右移动,可框住另外的五个数,所框五个数的和能等于2020吗?若能,写出这五个数;如不能,请说明理由. 24.(本小题满分8分)为了预防新冠肺炎的发生,学校免费为师生提供防疫物品.某校购进洗手液与84消毒液共400瓶.已知洗手液的价格是25元/瓶,84消毒液的价格是15元/瓶,总共消费了7200元.该校购进洗手液和84消毒液各多少瓶?25.(本小题满分9分)已知:点O 是直线AB 上的一点,90COD ∠=︒.OE 是BOD ∠的平分线. (1)当点C 、D 、E 在直线AB 的同侧(如图)时,①若35COE ∠=︒,求AOD ∠的度数. ②若COE α∠=,则AOD ∠=________.(用含α的式子表示) (2)当点C 与点D 、E 在直线AB 的两侧(如图)时,(1)中②的结论是否仍然成立?请给你的结论并说明理由.26.(本小题满分9分)如图,甲、乙两人(看成点)分别在数轴3-和5的位置上,沿数轴做移动游戏.每次的移动游戏规则如下:裁判先捂住一枚硬币,再让两人猜向上一面是正是反,而后根据所猜结果进行移动.①若都对或都错,则甲向东移动1个单位,同时乙向西移动1个单位; ②若甲对乙错,则甲向东移动4个单位,同时乙向东移动2个单位; ③若甲错乙对,则甲向西移动2个单位,同时乙向西移动4个单位.(1)若第一次移动游戏,甲、乙两人都猜对了,则甲、乙两人之间的距离是_______个单位; (2)若完成了10次移动游戏,发现甲、乙每次所猜结果均为一对一错.设乙猜对n 次,且他最终停留的位置对应的数为m .请你用含n 的代数式表示m ; (3)经过_______次移动游戏,甲、乙两人相遇。

七年级上册生物综合测试试题附部分答案

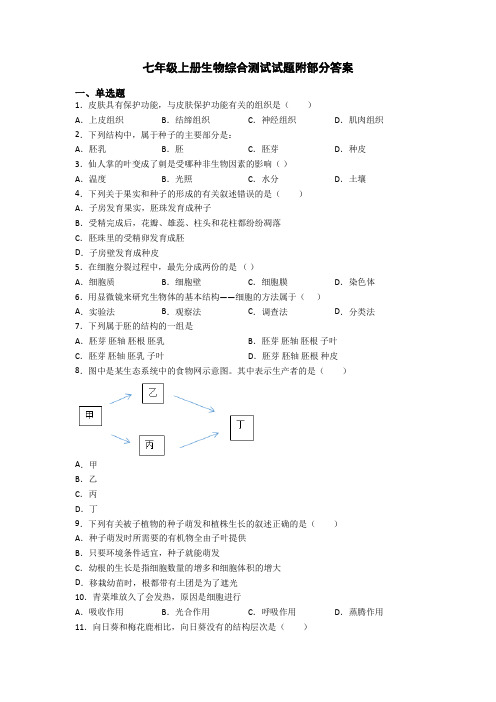

七年级上册生物综合测试试题附部分答案一、单选题1.皮肤具有保护功能,与皮肤保护功能有关的组织是()A.上皮组织B.结缔组织C.神经组织D.肌肉组织2.下列结构中,属于种子的主要部分是:A.胚乳B.胚C.胚芽D.种皮3.仙人掌的叶变成了刺是受哪种非生物因素的影响()A.温度B.光照C.水分D.土壤4.下列关于果实和种子的形成的有关叙述错误的是()A.子房发育果实,胚珠发育成种子B.受精完成后,花瓣、雄蕊、柱头和花柱都纷纷凋落C.胚珠里的受精卵发育成胚D.子房壁发育成种皮5.在细胞分裂过程中,最先分成两份的是()A.细胞质B.细胞壁C.细胞膜D.染色体6.用显微镜来研究生物体的基本结构——细胞的方法属于()A.实验法B.观察法C.调查法D.分类法7.下列属于胚的结构的一组是A.胚芽胚轴胚根胚乳B.胚芽胚轴胚根子叶C.胚芽胚轴胚乳子叶D.胚芽胚轴胚根种皮8.图中是某生态系统中的食物网示意图。

其中表示生产者的是()A.甲B.乙C.丙D.丁9.下列有关被子植物的种子萌发和植株生长的叙述正确的是()A.种子萌发时所需要的有机物全由子叶提供B.只要环境条件适宜,种子就能萌发C.幼根的生长是指细胞数量的增多和细胞体积的增大D.移栽幼苗时,根都带有土团是为了遮光10.青菜堆放久了会发热,原因是细胞进行A.吸收作用B.光合作用C.呼吸作用D.蒸腾作用11.向日葵和梅花鹿相比,向日葵没有的结构层次是()A.细胞B.组织C.器官D.系统12.一粒种子能长成参天大树,主要原因是()A.细胞分裂B.细胞数目增多C.细胞体积增大D.细胞数目增多,细胞体积增大13.下列关于植物类群的叙述,正确的是()A.银杏、苏铁、油松是裸子植物,其种子外面均有果皮包被B.海带和紫菜都是藻类植物,它们依靠其根固着在浅海岩石上C.油菜和石花菜都是利用种子进行繁殖,这是它们更适于陆地生活的原因D.卷柏的根、茎、叶内有输导组织,所以适应陆地生活的能力较强14.根吸收水分的主要部位是()A.根冠B.根毛区C.伸长区D.分生区15.北京香山红叶呈现红色,是由于细胞中存在花青素的缘故,那么,花青素这种物质存在于下列哪个结构中()A.叶绿体B.细胞核C.液泡D.细胞壁16.人的细胞核中有46条染色体,经过两次细胞分裂后形成四个细胞,每个细胞中染色体的数量()A.92条B.46条C.23条D.不能确定17.在洋葱鳞片叶表皮细胞和菠菜叶肉细胞中,分别含有的能量转换器是()A.叶绿体和线粒体;叶绿体和线粒体B.叶绿体;叶绿体和线粒体C.线粒体;线粒体和叶绿体D.叶绿体和线粒体;叶绿体18.农谚说:“有收无收在于水,多收少收在于肥”。

七年级英语下册Unit 7综合测试题-人教版(含答案)

七年级英语下册Unit 7综合测试题-人教版(含答案)Unit 7 It’s raining!I、单项选择(10分)1.—What's the weather like in Shanghai? —____.A. Sounds goodB. Thank youC. That's rightD. It's cloudy2.—Alice, long time no see! How's it going?—____. Many thanks.A. No ideaB. Help yourselfC. It doesn't matterD. Pretty good3.—Hello, this is Catie speaking. Is that Mrs Smith?—Sorry, she isn't here now. ____?A. Can I take a messageB. What are you saying to CatieC. May I speak to CatieD. Who's that speaking4.—____? —It's windy.A. How is it goingB. How is the weatherC. How is it likeD. Do you like the weather5.—Hello, ____ Frank? —Yes, this is Frank.A. are youB. is thatC. is heD. who's6.—__________________? —It's 12 January.A. What's the date todayB. What day is it todayC. What's the weather like todayD. What time is it7.It's ____ today. I think it's going to ____.A. cloud; rainB. cloudy; rainingC. cloudy; rainD. cloudy; rainy8.—____ the weather like in Moscow? —It's rainy.A. How'sB. What'sC. How doesD. What does9.When Peter comes, please ask him to leave a ____.A. noticeB. messageC. sentenceD. information10.—Hello! Is that Emily speaking?—Sorry, this is Jack, Emily's son. My mother ____ in the kitchen.A. cooksB. cookedC. is cookingD. has cookedII、根据句意及首字母提示填单词(5分)1.—What's the w____ like in Shenzhen?—It's raining.2.Can you take a m____ for my parents?3.Look! The sun is shining! It's s____.4.Is Miss Wang c____ in the kitchen (厨房) now?5.Look! There are many clouds in the sky. It's c____.III、选词填空(5分)watch, look, see, cook, snow1.The restaurant is very big. There are so many ____ in it.2.It is ____ hard. The ground is so white now.3.They go to ____ the old people at the Old People's Home every year.4.____ out! The car is running to you.5.My new ____ can tell me the right time.IV、用所给动词的适当形式填空(5分)1.—What’s Helen doing right now?—She is dancing. She __________ (dance) every Sunday.2.—Is Bob at home?—Yes, he is ___________ (study) his English.3.—How’s your vacation?—I’m having a good time _________ (swim) in the sea in Hainan.4.—How’s the weather in your city?—It’s cool and cloudy, just right for ___________ (walk).5.Everyone _________ (do) some cleaning every day.V、补全对话(5分)A: Hello, Lisa speaking.B: Hi, Lisa. (1)A: Oh, Ben. (2)B: I’m in Ca nada now.A: (3)B: It’s sunny but a little hot. (4)A: I’m watching TV at home. It’s kind of boring.B: (5)A: Because it’s raining now.B: I see. See you next week.A: See you.A. What are you doing now, Lisa?B. How’s the weather there?C. Why don’t you go out?D. This is Ben.E. Where are you now?VIAIt's sunny and cool in my city now. I'm studying at home. How's the weather in your city? And what are you doing?I'm visiting my uncle in Beijing. He works here. It's sunny in Beijing now. And it's warm. My two cousins are playing soccer in the yard. My uncle is reading a book at home.From Sally I live in New York City. It's hot now. Today is my birthday. My mother is cooking and my father is helping her. My brother is making a birthday cake.From Eric I'm in Florida. It's cool and sunny, too. I'm surfing the Internet in the library. Lots of students are in the library. Some are reading and some are writing. They all work very hard.From Jane1.How's the weather in Beijing?_______________________________________________2.Who is playing soccer in the yard?___________________________________________3.Where does Eric live?____________________________________________4.Is Eric's mother making a birthday cake?________________________________________5.What's Jane doing in the library?__________________________________________BIt's December. It's snowing and the weather is really cold in the north of China. You can see many children playing with snow. Some of them are making snowmen. Some are skating on the river, because it's so cold that the water in the river freezes (结冰). It's a white world. How beautiful! But in Australia now, the weather is hot. Many people go swimming in the sea. They are having a good time. Jim and his friends are playing soccer near the sea. They want to swim after playing soccer. Why are they swimming in December? That is winter, isn't it? Yes, it is in China. But it isn't in Australia. That's because we, Chinese and Australians, have different seasons in a year.6.What's the weather like in the north of China in December?_______________________________________________________7.What are the Chinese children doing on the river?_______________________________________________________8.Are Jim and his friends swimming in the sea now?_______________________________________________________9.Can you see white snow in Australia during Christmas Day?_______________________________________________________10.If it's June in China now, which season is it in Australia?_______________________________________________________CDear Jeff,I’m in London with my friend Tom. We are staying here for tour days. It was sunny and warm yesterday, but today it is rainy and a little cold. I’m drinking tea in my hotel room and Torn is out shopping.We are haying a great time in London. There are many interesting places here. My favorite places are the British Museum and Hyde Park. There are many beautiful old buildings (建筑物) here.We are really having a good time.It’s raining hard now. There are lots of cars in the street. The cars (小汽车) and buses are moving slowly (慢慢地). The people are walking or running. I think London is really a good place. I love it very much.Your s.Bob11.Who is writing the letter?_____________________________________________12.Where is Bob?___________________________________________________13.What’s the weather like today?____________________________________________________14.What are Bob’s favorite e places?____________________________________________________15.What are the people doing in the street?________________________________________________ VII、书面表达(20分)你的家乡天气如何呢?请你根据下面的提示,写一篇短文介绍你家乡的天气。

七年级上册期中综合测试语文试题(附答案)

期中综合测试题1.字词积累——下列加点字的读音完全正确的一项是( )A. 花苞.(bāo) 匿.笑(lì) 黄晕.(yūn) 踉.踉跄跄(niànɡ)B. 感慨.(kǎi) 拼凑.(zòu) 澄.清(chénɡ) 洗耳恭.听(ɡōnɡ)C. 棱.镜(lénɡ) 酝酿.(niànɡ) 静谧.(mì) 絮.絮叨叨(xù)D. 攲.斜(qī) 贪婪.(lán) 倜傥.(dǎnɡ) 宽宏.大量(hónɡ)2.字词积累——下列词语书写完全正确的一项是()A. 奥秘俯视荫蔽疲蜷不堪B. 贮蓄威慑决别煞有界事C. 憔悴辛辣和蔼拙拙逼人D. 吝啬屋檐诅咒喜出望外3.词语积累——下列加点成语使用有误的一项是()A. 他想不起把钥匙放在哪儿了,在抽屉里翻来覆去....地找了好几遍也没有找到。

B. 雾霾天气里,司机小心翼翼....地开着车。

C. 我们不能因为一次考试成绩不理想就灰心丧气....。

D. 美并不是要打扮得花枝招展....,作为中学生,朴素大方就是美。

4.文化积累——阅读下面的文字,完成后面的题目。

“哥儿,你牢牢记住!”她极其郑重地说。

“明天是正月初一,清早一睁眼睛,第一句话就得对我说:‘阿妈,恭喜恭喜!’记得么?你要记着,这是一年运气的事情。

不许说别的话!说过之后,还得吃一点福橘。

”她又拿起那橘子来在我眼前摇了两摇,“那么,一年到头,顺顺流流……”(1)以上文段出自《朝花夕拾》中的哪一篇?“她”是谁?(2)文段表现出“她”怎样的性格特征?5.语言运用——下列句子中的标点符号使用不正确的一项是()A. 《济南的冬天》是现代著名文学家、剧作家、小说家老舍先生创作的一篇散文,选自《一些印象》(人民文学出版社1999年出版)。

B. 现代著名散文家、诗人、学者、民主战士朱自清的散文《春》,主题明朗,语言优美,人们往往把它解读为一篇“春的赞歌”。

七年级上册综合测试题(含答案)

七年级上册综合测试题一选择题(40分)1. 成语是汉语中人们熟识并广泛使用很久的词组或短句,其中蕴含丰富的趣味生物学知识。

下列能说明“生物对环境是有影响的”成语是()A.风声鹤唳,草木皆兵 B.千里之堤,溃于蚁穴C.螳螂捕蝉,黄雀在后 D.不入虎穴,焉得虎子2、下列关于人体结构层次的排列中,正确的顺序是()A.组织—细胞—器官—系统—人体 B.组织—细胞—系统—器官—人体C.细胞—组织—器官—系统—人体 D.细胞—组织—系统—器官—人体3、禽流感病毒感染的鸡、鸭等家禽属于()A.两栖纲 B.爬行纲 C.鸟纲 D.哺乳纲4、把一片新鲜的叶片浸在盛有热水的烧杯中,会看到叶片的表面产生了许多气泡,而且实验显示叶片背面产生的气泡比正面的多。

由此可以说明()A、叶片背面的呼吸作用比正面强B、叶片背面的光合作用比正面强C、叶片背面表皮上的气孔数目比正面多D、叶片背面表皮上的气孔数目比正面少5、农作物增产的物质基础是()A、土壤中的无机盐B、空气中的氧气和土壤中的有机物C、土壤中的有机物D、空气中的二氧化碳和土壤中的无机物6、下列哪一项措施不是为了抑制植物呼吸作用?()A、低温贮藏水果蔬菜 B、农田土壤板结后及时松土C、贮藏粮食时在密闭粮仓内充加二氧化碳D、小麦种子入仓前晒干7、在阳光下检测呼吸作用,结果不显著,其原因是()A、呼吸作用停止B、呼吸作用减弱C、蒸腾作用旺盛D、光合作用较强8、细胞分裂后,新细胞的遗传物质( )A、和原细胞一样B、比原细胞多一倍C、比原细胞少一半D、差不多9、植物体内发生的生理现象,其中受气孔开闭影响的是()(1)水分的输导(2)无机盐的运输(3)光合作用(4)呼吸作用A、只有(1)(2)B、只有(3)(4)C、只有(1)(3)(4)D、(1)(2)(3)(4)10、探究“光照对黄粉虫幼虫生活的影响”过程中,主要采用()A.观察法B.实验法C.测量法D.调查法11、菟丝子的叶片退化,茎黄色或黄褐色,常生长于大豆、柑橘等植物体上。

七年级上册第2.1整式综合测试题

七年级上册第2.1整式综合测试题一、选择题(每小题3分,共24分)1、如果12221--n b a 是五次单项式,则n 的值为( ) A 、1 B 、2 C 、3 D 、42、多项式41232--+y xy x 是( ) A 、三次三项式 B 、二次四项式 C 、三次四项式 D 、二次三项式3、多项式23332--xy y x 的次数和项数分别为( )A 、5,3B 、5,2C 、2,3D 、3,34、对于单项式22r π-的系数、次数分别为( )A 、-2,2B 、-2,3C 、2,2π-D 、3,2π-5、下列说法中正确的是( )A 、3223x x x -+-是六次三项式B 、211x x x --是二次三项式 C 、5222+-x x 是五次三项式 D 、125245-+-y x x 是六次三项式6、下列式子中不是整式的是( )A 、x 23-B 、ab a 2- C 、y x 512+ D 、0 7、下列说法中正确的是( ) A 、-5,a 不是单项式 B 、2abc -的系数是-2 C 、322y x -的系数是31-,次数是4 D 、y x 2的系数为0,次数为2 8、下列用语言叙述式子“3--a ”所表示的数量关系,错误的是( )A 、a -与-3的和B 、-a 与3的差C 、-a 与3的和的相反数D 、-3与a 的差二、填空题(每小题3分,共24分)1、单项式342xy -的系数为____,次数为_____。

2、多项式1223+-+-y y xy x 是_____次__项式,各项分别为___,各项系数的和为____。

3、a 的3倍的相反数可表示为____,系数为____,次数为_____。

4、下列各式:13,,23,21,,21,3,124222+--+-++x x r b a x xy x b ab a π,其中单项式有____,多项式有_____。

5、下列式子3121,33,23,2,022--+--x b a yz x ab ,它们都有一个共同的特点是____。

七年级英语上册Unit 7综合测试题-人教版(含答案)

七年级英语上册Unit 7综合测试题-人教版(含答案)A类基础性练习一、请听下面5段对话。

每段对话后有一小题,从题中所给的A、B、C三个选项中选出最佳选项。

听完每段对话后,你都将有10秒钟的时间回答有关小题和阅读下一小题。

每段对话读两遍。

( )1.What color is Joe’s T-shirt?A.Blue.B.Green.C.Yellow.( )2.What does Mr. White want to buy?A.A hat.B.A bag.C.A hat and a bag.( )3.Where are David’s socks?A.In the bag.B.On the bed.C.On the chair.( )4.How much are the skirts?A.8 yuan.B.18 yuan.C.28 yuan.( )5.Where are they?A.In a clothes store.B.In a school.C.In a room.二、请听下面4段对话。

每段对话后有几个小题,从题中所给的A、B、C三个选项中选出最佳选项。

每段对话读两遍。

请听第1段对话,回答第6、7小题。

( )6.Who does the man want to buy the gloves for?A.His father.B.His brother.C.His son.( )7.What color gloves does the man take?A.Brown.B.Blue.C.Yellow.请听第2段对话, 回答第8、9小题。

( )8.Who is the boy?A.Susan’s brother.B.Susan’s cousin.C.Susan’s son.( )9.Which of the following is TRUE?A.The boy is thirteen years old.B.The boy likes apples.C.Susan likes Bananas.请听第3段对话,回答第10至第12小题。

高二数学综合测试题(文7)

第1页 共6页 ◎ 第2页 共6页高二文科数学综合测试题七1. 下列命题中的真命题是( )A .若d c b a >>,,则bd ac >B .若b a >,则22b a >C .若b a >,则22b a >D .若b a >,则22b a >2.下列结论错误的是( )A .命题“若p ,则q ”与命题“若,q ⌝则p ⌝”互为逆否命题;B .命题:[0,1],1x p x e ∀∈≥,命题2:,10,q x R x x ∃∈++<则p q ∨为真; C .“若22,am bm <则a b <”的逆命题为真命题; D .若q p ∨为假命题,则p 、q 均为假命题. 3.已知各项均为正数的等比数列}{n a 中,13213a ,a ,2a 2成等差数列,则=++1081311a a a a ( ) A. 27 B.3 C. 1-或3 D.1或27 4.在△ABC 中,内角A ,B ,C 所对的边长分别是a ,b ,c .若A A B C 2sin )sin(sin =-+,则△ABC的形状是( )A .直角三角形B .等腰三角形C .等腰直角三角形D .等腰三角形或直角三角形5.则该双曲线的离心率为( )ACD .6.在复平面内,向量AB →对应的复数是2+i ,向量CB →对应的复数是-1-3i ,则向量CA →对应的复数为( )A .1-2iB .-1+2iC .3+4iD .-3-4i7.有两个等差数列{},{}n n a b ,若12312321,3n n a a a a n b b b n b ++++==++++则 ( ) A .76 B .118 C .139 D .89 8.在ABC ∆中,内角,,A B C 所对的边分别为,,a b c ,其中120,1A b ==,且ABC ∆则sin sin a b A B +=+( )A..D. 9. 若数列{a n }的前 n 项和 S n = 2n 2 + 5n - 2,则此数列一定是( ).A. 递增数列B. 等差数列C. 等比数列D. 常数列 10.双曲线22221x y a b -=与椭圆22221(00)x y a m b m b +=>>>,的离心率互为倒数,则( ) A .a b m += B .222a b m += C .222a b m +< D .222a b m +> 11.若命题“R x ∃∈,使得2(1)10x a x +-+≤”为假命题,则实数a 的范围 . 12.一船以每小时15 km 的速度向东航行,船在A 处看到一个灯塔B 在北偏东60°,行驶4 h 后,船到达C 处,看到这个灯塔在北偏东15°,这时船与灯塔的距离为________ km 。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

综合测试题七

一、填空题

1.在数字电路中,逻辑变量的值只有个。

2.在逻辑函数的化简中,合并最小项的个数必须是个。

3.化简逻辑函数的方法,常用的有和。

4.逻辑函数A、B的同或表达式为A⊙B= 。

5.TTL三态门的输出有三种状态:高电平、低电平和状态。

6.4线—10线译码器又叫做进制译码器,它有个输入端和个输出端, 个不用的状态。

7.组合逻辑电路的输出仅取决于该电路当前的输入信号,与电路原来的状态。

8.T触发器的特性方程Q n+1= 。

9.组成计数器的各个触发器的状态,能在时钟信号到达时同时翻转,它属于计数器。

10.四位双向移位寄存器74LS194A的功能表如表所示。

由功能表可知,要实现保持功能,应使,当R D=1;S1=1,S0=0时,电路实现功能。

74LS194A的功能表

S1

工作状态

S0

11.若要构成七进制计数器,最少用个触发器,它有个无效状态。

12.根据触发器结构的不同,边沿型触发器状态的变化发生在CP 时,其它时刻触发器保持原态不变。

13.用中规模集成计数器构成任意进制计数器的方法通常有三种,它们是级连法,和。

14.由555定时器构成的单稳态触发器,若已知电阻R=500KΩ,电容C=10μF,则该单稳态触发器的脉冲宽度tw≈。

15.在555定时器组成的施密特触发器、单稳态触发器和多谐振荡器三种电路中,电路能自动产生脉冲信号,其脉冲周期T≈。

16.随机存储器RAM的电路结构主要由、和三部分组成。

二、选择题:请将正确答案的序号填在横线上。

1.下列一组数中,是等值的。

①(A7)16②(10100110)2③(166)10

A.①和③ B. ②和① C. ②和③

2.在逻辑函数中的卡诺图化简中,若被合并的最小项数越多(画的圈越大),则说明化简后。

A.乘积项个数越少 B. 实现该功能的门电路少

C.该乘积项含因子少

3.在逻辑函数的卡诺图化简中,合并相邻项(画圈)的方法必须画成形状。

A.三角形 B. 矩形 C. 任意

4.的最小项之和的形式是。

A.

B.

C.

5. 在下列各种电路中,属于组合电路的有。

A.编码器 B. 触发器 C. 寄存器

6.74LS138是3线-8线译码器,译码输出为低电平有效,若输入A2A1A0=100时,输出

=。

A.00010000, B. 11101111 C. 11110111

7.8线—3线优先编码器74LS148的优先权顺序是I7,I6,……I1,I0,输

出Y

Y1 Y0,输入低电平有效,输出为三位二进制反码输出。

当I7I6,……

2

I1I0为11100111时,输出Y

Y1 Y0为。

2

A.011 B.100 C. 110

8.在以下各种电路中,属于时序电路的有。

A.反相器 B. 编码器

C. 寄存器

D.数据选择器

9.RS触发器当R=S=0时,Q n+1= 。

A.0 B.1 C.Q n D. Q

10.施密特触发器常用于对脉冲波形的。

A.延时和定时 B. 计数与寄存C.整形与变换

三、逻辑函数化简与变换:

1.证明等式:

2.将下列逻辑函数化简成最简与或表达式

四.试写出图 4.1电路输出z的逻辑函数式。

4选1数据选择器74LS153的功能表达式见式 4.1。

(式4.1)

图4.1

五.3线-8线译码器74LS138逻辑功能表达式为,,……,

,,正常工作时,S1 =1, S

=S3=0。

试写出Z1和Z2

2

逻辑函数式。

(图5.1)

图5.1

六.触发器练习题:见数字电子技术基础主教材P202例4.2.6。

七.触发器练习题:见数字电子技术基础主教材P219习题4.12

八.画出图8.1(a)、(b)的状态转换图,分别说明它们是几进制计数器。

74LS161功能表见数字电子技术基础主教材P245表5.3.4。

(a) (b) 图8.1

九.试用四2输入与非门74LS00实现Y=AB+CD功能。

画出实验连线图,74LS00外部引线排列见图9.1所示。

图9.1。