Cyclone III原理图检查

Altera Cyclone III系列FPGA开发板简介

ETL-002 Altera Cyclone III系列FPGA开发板简介概述ETL-002 FPGA开发板是以Altera公司的最新系列Cyclone III中的3C10为主芯片,并提供了极为丰富的芯片外围接口资源以及下载线,数据线以及资料光盘等。

除了这些硬件外,我们还提供了十多个接口实验,并公开了电路原理图和实验的Verilog源代码,以便于大家对照学习,并可以在该开发板上进行二次开发。

单板描述主芯片EP3C10提供了10320个逻辑单元(LE),46块SRAM(每块9K bits), 23个18*18的乘法器。

开发板自带USB供电电路:您只需将USB线插上您的USB端口,无需外接+5V直流电源,开发板即可工作。

开发板同时支持AS模式下载和JTAG模式下载。

程序固化既可通过JTAG口也可直接对板上的FLASH进行编程。

丰富的外围接口可满足常用的外设的人机交互,我们还将剩下未用的40个用户I/O引脚全部引出,使得您可以通过这些信号对本开发板进行电路扩展。

这些接口主要包括:PS2鼠标接口:可以将PS2鼠标的任何移动的信息反应在数码管上PS2键盘接口:可以将PS2键盘上的任意按键以16进制的信息反应在数码管上VGA显示器接口:可以将FPGA产生的信息反映在VGA显示器上。

开发板自带了动态彩条显示的功能双串口接口:可以与任何的串口设备相接。

开发板自带的演示程序是将PC上的超级终端中输入的任何信息返回PC 4位数码管:可以实时显示任何的数字信息。

开发板自带的演示程序实时地显示分钟和秒钟的信息。

4位LED灯:用于指示状态。

开发板自带了跑马灯实验。

4位按键开关:可用于复位等作用。

4位拨码开关:可用于电路的选择作用教学实验除了开发板的丰富的硬件资源外,我们还提供了数十个学习实验。

通过这些实验,您可以学习FPGA芯片,Quartus II软件和设计仿真和下载等FPGA的设计流程,然后将试验中程序执行的信息通过数码管,LED 灯,串口等板上的硬件直观的显示出来。

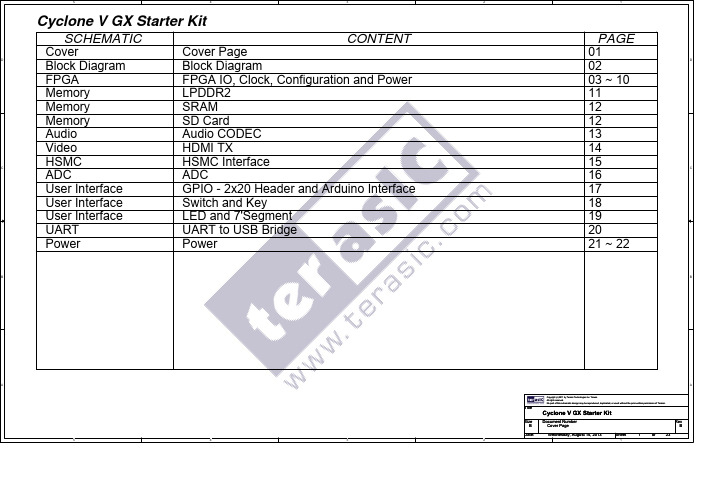

Cyclone V GX 开发板原理图 (5CGXFC5C6F27)

SRAMSD CardAudio CODECHDMI TXHSMC InterfaceADCGPIO - 2x20 Header and Arduino InterfaceSwitch and KeyLED and 7'SegmentUART to USB BridgePowerCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.All rights reserved.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.Title5432TitleSize Document Number Date:Copyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.Block DiagramCyclone V GX Starter KitB Friday, November 15, 2013SWITCH7-SEGMENTADC InterfaceDDR2LP_DQ7DDR2LP_DM0DDR2LP_DQ4DDR2LP_DQ5DDR2LP_DQ14DDR2LP_DQ15DDR2LP_CKE0DDR2LP_DM1DDR2LP_DQ12DDR2LP_DQ13DDR2LP_DQ11DDR2LP_CKE1DDR2LP_DQS_n1DDR2LP_DQS_p1DDR2LP_DQ8DDR2LP_DQ9GNDDDR2LP_DQ10DDR2LP_CA0DDR2LP_CA1SW[9..0]HEX0_D[6..0]HEX1_D[6..0]ADC_CONVST ADC_SCK ADC_SDO ADC_SDITitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.IO_4A/DIFFIO_RX_B30N/DQ4B/B_DQ_4Y13IO_4A/DIFFIO_RX_B30P/DQ4B/B_DQ_5W12IO_4A/DIFFIO_TX_B32N/DQ4B/B_DQ_7AF12IO_4A/DIFFIO_TX_B32P/DQ4B/B_DM_0AF11IO_4A/DIFFIO_TX_B33N/GND AC13IO_4A/DIFFIO_RX_B34N/DQ5B/B_DQ_8AC15IO_4A/DIFFIO_TX_B33P/DQ5B/B_DQ_10AC14IO_4A/DIFFIO_RX_B34P/DQ5B/B_DQ_9AB15IO_4A/DIFFIO_RX_B35N/DQSN5B/B_DQSN_1V14IO_4A/DIFFIO_TX_B36N/DQ5B/B_DQ_11AF13IO_4A/DIFFIO_RX_B35P/DQS5B/B_DQS_1U14IO_4A/DIFFIO_TX_B36P/B_CKE_1AE13IO_4A/DIFFIO_TX_B37N/DQ5B/B_CKE_0AF14IO_4A/DIFFIO_RX_B38N/DQ5B/B_DQ_12AB16IO_4A/DIFFIO_TX_B37P/DQ5B/B_DQ_14AE14IO_4A/DIFFIO_RX_B38P/DQ5B/B_DQ_13AA16IO_4A/DIFFIO_TX_B40N/DQ5B/B_DQ_15AF18IO_4A/DIFFIO_TX_B40P/DQ5B/B_DM_1AE18IO_4A/DIFFIO_RX_B46N/DQ6B/B_DQ_20IO_4A/DIFFIO_RX_B46P/DQ6B/B_DQ_21IO_4A/DIFFIO_TX_B48N/DQ6B/B_DQ_23IO_4A/DIFFIO_TX_B48P/DQ6B/B_DM_2IO_4A/DIFFIO_RX_B50N/DQ7B/B_DQ_24IO_4A/DIFFIO_TX_B49P/DQ7B/B_DQ_26IO_4A/DIFFIO_RX_B50P/DQ7B/B_DQ_25IO_4A/DIFFIO_RX_B51N/DQSN7B/B_DQSN_3IO_4A/DIFFIO_TX_B52N/DQ7B/B_DQ_27IO_4A/DIFFIO_RX_B51P/DQS7B/B_DQS_3IO_4A/DIFFIO_RX_B54N/DQ7B/B_DQ_28IO_4A/DIFFIO_TX_B53P/DQ7B/B_DQ_30IO_4A/DIFFIO_RX_B54P/DQ7B/B_DQ_29IO_4A/DIFFIO_TX_B56N/DQ7B/B_DQ_31IO_4A/DIFFIO_TX_B56P/DQ7B/B_DM_3IO_4A/DIFFIO_RX_B58N/DQ8B/B_DQ_32IO_4A/DIFFIO_TX_B57P/DQ8B/B_DQ_34IO_4A/DIFFIO_RX_B58P/DQ8B/B_DQ_33IO_4A/DIFFIO_RX_B59N/DQSN8B/B_DQSN_4IO_4A/DIFFIO_TX_B60N/DQ8B/B_DQ_35IO_4A/DIFFIO_RX_B59P/DQS8B/B_DQS_4IO_4A/DIFFIO_RX_B62N/DQ8B/B_DQ_36IO_4A/DIFFIO_TX_B61P/DQ8B/B_DQ_38IO_4A/DIFFIO_RX_B62P/DQ8B/B_DQ_37IO_4A/DIFFIO_TX_B64N/DQ8B/B_DQ_39IO_4A/DIFFIO_TX_B64P/DQ8B/B_DM_4IO_3B/DIFFIO_TX_B24N/DQ3B/B_CA_1AF6IO_3B/DIFFIO_TX_B24P/DQ3B/B_CA_0AE6SRAM_D0SRAM_D1SRAM_D2SRAM_D3SRAM_D4SRAM_D5SRAM_D6SRAM_D7SRAM_D8SRAM_D9SRAM_D10SRAM_D11SRAM_D12SRAM_D13SRAM_D14SRAM_D15HDMI_TX_VS HDMI_TX_HSHDMI_TX_D19HDMI_TX_D1HDMI_TX_D2HDMI_TX_D3HDMI_TX_D5HDMI_TX_D6HDMI_TX_D9HDMI_TX_D11HDMI_TX_D18HDMI_TX_D17HDMI_TX_D16HDMI_TX_D15HDMI_TX_D12HDMI_TX_D14TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NIO_6A/DIFFIO_TX_R34P/DQ5R E24IO_6A/DIFFIO_TX_R34N/DQ5R E25IO_6A/DIFFIO_RX_R35P/DQ5R K24IO_6A/DIFFIO_TX_R36P/DQ5R F24IO_6A/DIFFIO_RX_R35N/DQ5R K23IO_6A/DIFFIO_TX_R36N/DQ5R G24IO_6A/DIFFIO_RX_R37P/DQS5R L23IO_6A/DIFFIO_TX_R38PH23IO_6A/DIFFIO_RX_R37N/DQSN5R L24IO_6A/DIFFIO_TX_R38N/DQ5R H24IO_6A/DIFFIO_RX_R39P/DQ5R H22IO_6A/DIFFIO_TX_R40P/DQ5R F23IO_6A/DIFFIO_RX_R39N/DQ5R J23IO_6A/DIFFIO_TX_R40N G22IO_6A/DIFFIO_RX_R41P L22IO_6A/DIFFIO_RX_R41NK21IO_5B/DIFFIO_RX_R15P/DQ2R R24IO_5B/DIFFIO_TX_R16P/DQ2RU24IO_5B/DIFFIO_RX_R15N/DQ2R R25IO_5B/DIFFIO_TX_R16NV25IO_5B/DIFFIO_TX_R18P/DQ3R AB26IO_5B/DIFFIO_TX_R18N/DQ3R AA26IO_5B/DIFFIO_RX_R19P/DQ3R T26IO_5B/DIFFIO_RX_R19N/DQ3RR26IO_5B/DIFFIO_RX_R21P/DQS3R P21IO_5B/DIFFIO_TX_R22PW25IO_5B/DIFFIO_RX_R21N/DQSN3RP22IO_5B/DIFFIO_TX_R22N/DQ3R W26IO_5B/DIFFIO_RX_R23P/DQ3R N25IO_5B/DIFFIO_TX_R24P/DQ3RU25IO_5B/DIFFIO_RX_R23N/DQ3R P26IO_5B/DIFFIO_TX_R24NU26Audio CODECHSMC_D0HSMC_RX_n0HSMC_RX_p0HSMC_RX_n10HSMC_RX_p10HSMC_RX_p9HSMC_RX_n9HSMC_RX_p11HSMC_RX_n11HSMC_RX_n12HSMC_RX_p12HSMC_RX_p1HSMC_RX_n1HSMC_RX_n7HSMC_RX_p7HSMC_TX_n8HSMC_TX_p8HSMC_TX_p9HSMC_TX_n9HSMC_TX_p10HSMC_TX_n10HSMC_TX_p0HSMC_TX_n0HSMC_TX_p2HSMC_TX_n2HSMC_TX_n1HSMC_TX_p1HSMC_TX_n4HSMC_TX_p4HSMC_TX_n3HSMC_TX_p3HSMC_TX_n6HSMC_TX_p6AUD_XCK 13AUD_DACDAT 13AUD_ADCDAT 13AUD_DACLRCK 13AUD_ADCLRCK13AUD_BCLK 13TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NIO_7A/DIFFIO_TX_T6N/DQ1T/T_DQ_35IO_7A/DIFFIO_RX_T7P/DQ1T/T_DQ_33IO_7A/DIFFIO_TX_T8P/DQ1T/T_DQ_34IO_7A/DIFFIO_RX_T7N/DQ1T/T_DQ_32IO_7A/DIFFIO_TX_T10P/DQ2T/T_DM_3IO_7A/DIFFIO_TX_T10N/DQ2T/T_DQ_31IO_7A/DIFFIO_RX_T11P/DQ2T/T_DQ_29IO_7A/DIFFIO_TX_T12P/DQ2T/T_DQ_30IO_7A/DIFFIO_RX_T11N/DQ2T/T_DQ_28IO_7A/DIFFIO_RX_T13P/DQS2T/T_DQS_3IO_7A/DIFFIO_RX_T13N/DQSN2T/T_DQSN_3IO_7A/DIFFIO_TX_T14N/DQ2T/T_DQ_27IO_7A/DIFFIO_RX_T15P/DQ2T/T_DQ_25IO_7A/DIFFIO_TX_T16P/DQ2T/T_DQ_26IO_7A/DIFFIO_RX_T15N/DQ2T/T_DQ_24IO_7A/DIFFIO_TX_T22P/T_RESETN B15IO_7A/DIFFIO_TX_T22N/DQ3T/T_DQ_19C15IO_7A/DIFFIO_RX_T23P/DQ3T/T_DQ_17C14IO_7A/DIFFIO_TX_T24P/DQ3T/T_DQ_18A8IO_7A/DIFFIO_RX_T23N/DQ3T/T_DQ_16D15IO_7A/DIFFIO_TX_T24N/GNDA9IO_7A/DIFFIO_TX_T26P/DQ4T/T_DM_1C9IO_7A/DIFFIO_TX_T26N/DQ4T/T_DQ_15B9IO_7A/DIFFIO_RX_T27P/DQ4T/T_DQ_13E16IO_7A/DIFFIO_TX_T28P/DQ4T/T_DQ_14D10IO_7A/DIFFIO_RX_T27N/DQ4T/T_DQ_12D16IO_7A/DIFFIO_TX_T28N/DQ4T/T_CKE_0C10IO_7A/DIFFIO_RX_T29P/DQS4T/T_DQS_1N12IO_7A/DIFFIO_TX_T30P/T_CKE_1B10IO_7A/DIFFIO_RX_T29N/DQSN4T/T_DQSN_1M12IO_7A/DIFFIO_TX_T30N/DQ4T/T_DQ_11A11IO_7A/DIFFIO_RX_T31P/DQ4T/T_DQ_9F16IO_7A/DIFFIO_TX_T32P/DQ4T/T_DQ_10E10IO_7A/DIFFIO_RX_T31N/DQ4T/T_DQ_8E15IO_7A/DIFFIO_TX_T32N/GNDE11IO_7A/DIFFIO_TX_T34P/DQ5T/T_DM_0B12IO_7A/DIFFIO_TX_T34N/DQ5T/T_DQ_7A13IO_7A/DIFFIO_RX_T35P/DQ5T/T_DQ_5G12IO_7A/DIFFIO_TX_T36P/DQ5T/T_DQ_6A12IO_7A/DIFFIO_RX_T35N/DQ5T/T_DQ_4F12IO_7A/DIFFIO_TX_T36N/DQ5T/T_ODT_1B11IO_7A/DIFFIO_RX_T37P/DQS5T/T_DQS_0M11IO_7A/DIFFIO_TX_T38P/T_ODT_0C13IO_7A/DIFFIO_RX_T37N/DQSN5T/T_DQSN_0L11IO_7A/DIFFIO_TX_T38N/DQ5T/T_DQ_3C12IO_7A/DIFFIO_RX_T39P/DQ5T/T_DQ_1E13IO_7A/DIFFIO_TX_T40P/DQ5T/T_DQ_2D11IO_7A/DIFFIO_RX_T39N/DQ5T/T_DQ_0D13GXB L2 is C7 FPGA onlyHSMC_GXB_RX_p3HSMC_GXB_RX_n3HSMC_GXB_TX_p3HSMC_GXB_TX_n3SMA_GXB_TX_pSMA_GXB_RX_pREFCLK_p1REFCLK_n1SMA_GXB_RX_p SMA_GXB_RX_nSMA_GXB_TX_p SMA_GXB_TX_n TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.GXB_L1GXB_L25CGXFC5C6F27C7NREFCLK1LNP6REFCLK1LP N7GXB_TX_L5NK1GXB_TX_L5P K2GXB_RX_L5P,GXB_REFCLK_L5P M2GXB_RX_L5N,GXB_REFCLK_L5N M1GXB_TX_L4N P1GXB_TX_L4P P2GXB_RX_L4P,GXB_REFCLK_L4P T2GXB_RX_L4N,GXB_REFCLK_L4N T1GXB_TX_L3N W3GXB_TX_L3P W4GXB_RX_L3P,GXB_REFCLK_L3P V2GXB_RX_L3N,GXB_REFCLK_L3N V1RREF_TLB1GXB_RX_L8n,GXB_REFCLK_L8n D1GXB_RX_L8p,GXB_REFCLK_L8p D2GXB_RX_L7n,GXB_REFCLK_L7n F1GXB_RX_L7p,GXB_REFCLK_L7p F2GXB_RX_L6n,GXB_REFCLK_L6n H1GXB_RX_L6p,GXB_REFCLK_L6p H2GXB_TX_L6p G4GXB_TX_L6n G3GXB_TX_L7p E4GXB_TX_L7n E3GXB_TX_L8p C4GXB_TX_L8nC3REFCLK2Lp M6REFCLK2LnL5R1990R2042KJ12J7R1980C1360.01uVCCIO = 3.3VVCCIO = 3.3VVCCIO = 2.5VVCCIO = 2.5VHSMC_CLKIN_p1HSMC_CLKIN_n1CLOCK_50_B7A HSMC_CLKIN_n1HSMC_CLKIN_n2CLOCK_50_B5B CLOCK_50_B6A GPIO0GPIO2I2C_SDACLOCK_125_n GPIO8GPIO7GPIO6GPIO4CLOCK_50_B8A HSMC_CLKIN0HSMC_CLKIN_p2HSMC_CLKIN_n2VCC2P5VCC2P5VCC2P5VCC3P3VCC2P5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C2690.1u 10V C2680.1u 10VC1110.1u 10VR188100R197100R200100R11220KC2670.1u 10V Bank 5BBank 6ABank 7ABank 8A5CGXFC5C6F27C7NIO_5B/CLK7P,FPLL_BR_FBP/DIFFIO_RX_R9P T21IO_5B/CLK7N,FPLL_BR_FBN/DIFFIO_RX_R9NT22IO_5B/CLK6P/DIFFIO_RX_R17P R20IO_5B/CLK6N/DIFFIO_RX_R17NP20IO_5B/FPLL_BR_CLKOUT0,FPLL_BR_CLKOUTP,FPLL_BR_FB/DIFFIO_TX_R20P/DQ3RIO_5B/FPLL_BR_CLKOUT1,FPLL_BR_CLKOUTN/DIFFIO_TX_R20N/DQ3RIO_6A/CLK5P/DIFFIO_RX_R25P N20IO_6A/CLK5N/DIFFIO_RX_R25NM21IO_6A/FPLL_TR_CLKOUT0,FPLL_TR_CLKOUTP,FPLL_TR_FB/DIFFIO_TX_R28P/DQ4RIO_6A/FPLL_TR_CLKOUT1,FPLL_TR_CLKOUTN/DIFFIO_TX_R28N/DQ4RIO_6A/CLK4P,FPLL_TR_FBP/DIFFIO_RX_R33P K25IO_6A/CLK4N,FPLL_TR_FBN/DIFFIO_RX_R33NK26IO_7A/CLK11P/DIFFIO_RX_T25P G15IO_7A/CLK11N/DIFFIO_RX_T25NG14IO_7A/CLK10P/DIFFIO_RX_T33P H12IO_7A/CLK10N/DIFFIO_RX_T33N G11IO_8A/CLK9P/DIFFIO_RX_T41P N9IO_8A/CLK9N/DIFFIO_RX_T41NM10IO_8A/FPLL_TL_CLKOUT0,FPLL_TL_CLKOUTP,FPLL_TL_FB/DIFFIO_TX_T44P/DQ6T/T_CA_2IO_8A/FPLL_TL_CLKOUT1,FPLL_TL_CLKOUTN/DIFFIO_TX_T44N/DQ6T/T_CA_3IO_8A/CLK8P,FPLL_TL_FBP/DIFFIO_RX_T49P L8IO_8A/CLK8N,FPLL_TL_FBN/DIFFIO_RX_T49N K9U20MSEL Settings : MSEL[4:0] = 10010 Active serial (AS)(x1 and x4),no compression, no security, fast PORFPGAHSMCSD_DAT0SD_DAT1SD_DAT2SD_DAT3SD_CMD SD_CLK MSEL0MSEL1MSEL3MSEL2MSEL4BST_TDI BST_TDO JTAG_FPGA_TDI FPGA_CONF_DONE FPGA_nSTATUS FPGA_nCONFIGHSMC_JTAG_TDI HSMC_JTAG_TDO JTAG_FPGA_TDO FPGA_nCEGPIO34GPIO11GPIO23GPIO22GPIO21GPIO20GPIO19GPIO17GPIO15GPIO14GPIO13GPIO12GPIO31VCC3P3VCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R1730DNI R520R1770DNI RN2210K12345678Bank 9A5CGXFC5C6F27C7NIO_3A/DATA6/DIFFIO_RX_B1N/DQ1B T7IO_3A/DATA5/DIFFIO_TX_B2NU7IO_3A/DATA8/DIFFIO_RX_B1P/DQ1B T8IO_3A/DATA7/DIFFIO_TX_B2P/DQ1B V8IO_3A/DATA10/DIFFIO_RX_B3N/DQSN1B W8IO_3A/DATA9/DIFFIO_TX_B4N/DQ1BAB6IO_3A/DATA12/DIFFIO_RX_B3P/DQS1B Y9IO_3A/DATA11/DIFFIO_TX_B4PAA6IO_3A/DATA14/DIFFIO_RX_B5N/DQ1B R10IO_3A/DATA13/DIFFIO_TX_B6N/DQ1B AA7IO_3A/CLKUSR/DIFFIO_RX_B5P/DQ1B R9IO_3A/DATA15/DIFFIO_TX_B6P/DQ1B Y8IO_5A/PR_REQUEST/DIFFIO_TX_R1N/DQ1RAC23IO_5A/CVP_CONFDONE/DIFFIO_TX_R3N/DQ1RAA23IO_5A/nPERSTL1/DIFFIO_RX_R6N/DQSN1R U22MSEL0M7CONF_DONE A6MSEL1L6nSTATUS B5nCED5MSEL2A2MSEL3K5nCONFIG F5MSEL4J5IO_3A/PR_DONE/DIFFIO_RX_B7NR8IO_3A/PR_READY/DIFFIO_TX_B8N/DQ1BAD6IO_3A/PR_ERROR/DIFFIO_RX_B7P P8IO_3A/DIFFIO_TX_B8P/DQ1BAD7R530VCCAUX_VCCA_FPLLVCC2P5VCC3P3VREF_3P3_VCCIOTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.5CGXFC5C6F27C7NVCC VCC VCC VCC VCC VCCVCC VCC VCC VCC VCC VCC VCC VCC VCC VCC VCCPGM AA9VCCPGM W22VCCPGM F8VCCBATVCCPD5B R21VCCPD6A J22VCCPD6A L21VCCPD7A8AF19VCCPD7A8A F17VCCPD7A8A F13VCCPD7A8A F11VCCPD7A8A F9VCCA_FPLL W7VCCA_FPLL J6VCCA_FPLLY21VCCA_FPLL G21VCC_AUX G9VCC_AUX E14VCC_AUX G19VCC_AUXAB20VCC_AUX AB14VCC_AUX AA85CGXFC5C6F27C7NVCCIO4A U18VCCIO4A AE22VCCIO4A AA20VCCIO4A AD19VCCIO4A Y17VCCIO4A W14VCCIO4A AC16VCCIO4A AF15VCCIO4A AB13VCCIO4A AE12VCCIO5A V21VCCIO5A AB23VCCIO5B N26VCCIO5B T25VCCIO5B W24VCCIO5B R22VREFB4AN0AD15VREFB5AN0W23VREFB5BN0P25CYCLONE V GX XCVR PowerU14-122.5V2.5Vfor VCCIO_VCCPD 2.5Vfor VCCIO_VCCPD 3.3Vfor VCCIO 1.2VVCCH_GXBL VCCAUX_VCCA_FPLLVCC1P2VCC3P3VCC2P5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C2204.7n 50VC25522n 16VC1674.7u 6.3VC2510.01u 50VC1830.01u 50VC2320.47u 10VC1804.7n 50VC1782.2n 50VC1940.01u 50VC1701u 10VC1720.47u 10VC2504.7n 50VC1764.7u 6.3VC10510u 6.3VC2492.2n 50VC1910.01u 50VC1044.7u 6.3VC1820.1u 10VC2460.01u 50VC1900.1u 10VC25322n 16VC1851u 10VC2590.1u 10VC2130.01u 50VC25247n 25VNote:Place decoupling caps near LPDDR2 power pins place close to DDR2 chipDDR2LP_CKE0DDR2LP_CS_n0DDR2LP_DM0DDR2LP_DM1DDR2LP_DQ2DDR2LP_DQ3DDR2LP_DQ4DDR2LP_DQ5DDR2LP_DQ6DDR2LP_DQ7DDR2LP_DQ8DDR2LP_DQ9DDR2LP_DQ10DDR2LP_DQ11DDR2LP_DQ12DDR2LP_DQ13DDR2LP_DQ14DDR2LP_DQ15DDR2LP_DM3DDR2LP_DQ31DDR2LP_DQ24DDR2LP_DQ25DDR2LP_DQ26DDR2LP_DQ27DDR2LP_DQ28DDR2LP_DQ29DDR2LP_DQ30DDR2LP_DM2DDR2LP_DQ16DDR2LP_DQ17DDR2LP_DQ19DDR2LP_DQ18DDR2LP_DQ20DDR2LP_DQ22DDR2LP_DQ21DDR2LP_DQ23DDR2LP_ZQ0DDR2LP_ZQ1DDR2LP_CKE1DDR2LP_CS_n1DDR2LP_CK_nVCC1P2TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C1450.1u 10V240DNIC1580.1u 10VR169 4.7K R1684.7K DNIC15510u 10VDNU0A1DNU1A2NC0A3NC1A4NC2A5NC3A6NC4A7NC5A8NC6A9NC7A10DNU2A22DNU3A23DM2AB20DNU10AB22DNU8AB1DNU9AB2CS#0AB3CS#1AB4NC/ZQ AC11CKE0AC3CKE1AC4DNU4B1DNU5B2DM3B20DNU6B22DNU7B23NC8B4NC9B6NC10B7NC11B9NC12D1NC13D2NC14E1NC15E2NC16F1NC17G1NC18G2NC19H1NC20H2NC21J1NC22K1NC23K2NC24L1DM1L23DM0N23ZQ P1DQ30A13DQ29A14DQ26A16DQ25A17DQ16AB12DQ18AB14DQ20AB15DQ22AB17DQ17AC13DQ19AC14DQ21AC16DQ23AC17DQ31B12DQ28B14DQ27B15DQ24B17DQ15C22DQ14D23DQ12E22DQ13E23DQ11F22DQ10G23DQ8H22DQ9H23DQ6T22DQ7T23DQ5U22DQ4V23DQ2W22DQ3W23240C4010u 10VC14622n 16VMT42L128M32D1LF-25WTVSS A21VSS AA1VDD2AA2VDD2AB10VSS AB11VDD2AB21VSS AC21VSS AC5VSS/NC AC9VSS B10VDD2B21VSS/NC B5VSS/NC B8VSS C1VDD2C2VSS/NC F2VSS/NCJ2VDD2L22VSS M2VSS M23VSS R1VDD2R2VSSQ A12VSSQ A15VSSQ A18VDDQ AA22VDDQ AB13VDDQ AB16VDDQ AB19VSSCA AB7VSSQ AC12VSSQ AC15VSSQAC18VSSQ C23VDDQ D22VSSQ F23VDDQ G22VSSQ J23VDDQ K22VSSQ P23VDDQ R22VSSQ U23VSSCA V1VDDQ V22VSSQ Y23C1594.7u 6.3VC16222n 16VC1530.1u 10VSD_DAT1SD_DAT0SD_DAT3SD_DAT2SD_CMDSD_DAT2SD_DAT3SD_CMD SRAM_CE_n SRAM_OE_n SRAM_WE_n SRAM_LB_n SRAM_UB_nSRAM_D11SRAM_D12SRAM_D15SRAM_D13SRAM_D9SRAM_D10SRAM_D14SRAM_CE_nSRAM_A14SRAM_A16SRAM_A15SRAM_A17SRAM_A13VCC3P3_SDVCC3P3_SDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R185RN1010K 12345678L2130ohm, 3ASRAM 256Kx16nCE 6G N D 12nWE 17A1326A1427A1828D930D1031D1132G N D34D1235D1336D1437D1538nLB 39nUB40nOE 41A1542A1643A1744123J6c k e tDAT3CMD DAT2R11710KDefault :I2C Address 0x34/35AUD_XCKAUD_BCLKAUD_DACDAT AUD_DACLRCK AUD_ADCDATAUD_ADCLRCK I2C_SDA_3P3I2C_SCL_3P3AUD_MUTEAUD_CSBAUD_I2C_SDAT AUD_I2C_SCLK AGND AGNDVCC_AUDDVCC_AUDDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R18680R1502K DNIC22100u C13410u 6.3VU7SSM2603BCLK 7H P V D D 12XTO 2D C V D D 3MICBIAS21MICIN22RLINEIN 23LLINEIN24MUTE25CSB26SDIN27SCLK28ROUT 17A V D D18A G N D19VMID 20LOUT16P G N D 15RHPOUT 14LHPOUT13XTI/MCLK 1D G N D4RECLRC11RECDAT 10D B V D D5CLKOUT6PBDAT 8PBLRCK 9E P _G N D 29C1390.1u 10V DNIR2822R20330R3022R1512K DNIR174.7KC151u 10VDefault :I2C Address 0x72/0x73Pull-high to FPGA bank I/O powerNote:Place Capacitor near ADV7513 DVDD pinsHDMI_TX_CLK HDMI_TX_DE HDMI_TX_VS HDMI_TX_HS HDMI_HPD CEC_CLKHDMI_SPDIF HDMI_MCLK HDMI_I2S0HDMI_I2S1HDMI_I2S2HDMI_I2S3HDMI_SCLK HDMI_LRCLKHDMI_TX_D17HDMI_TX_D18HDMI_TX_D19HDMI_TX_D20HDMI_TX_D21HDMI_TX_D22HDMI_TX_D23CLK_12MHz VCC1P8VCC1P8_DVDDVCC1P8VCC1P8_AVDDVCC1P8_DVDDVCC1P8_PVDDVCC1P8_AVDDVCC3P3_DVDD VCC3P3_DVDDVCC1P8_AVDDVCC1P2VCC1P8_DVDDTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C3510u 6.3VR15349.9DNI R12822DNIR1242K X312MHZDNIVCC 4OUT 3GND2EN1C1490.1u 10VL910uH74479887310AC1520.1u 10VC1380.1u 10VR129R1252K DNIC1290.1u 10VDNIC1300.1u 10VL410uHR80R138887ADV7513BSWZD1743D1842D1941D2040D2139D2238D2337CLK 53DE63HSYNC 64VSYNC 2R_EXT 14HPD 16SPDIF 3MCLK 4I2S05I2S16I2S27I2S38SCLK 9LRCLK 10PD22DVDD_3V 29DVDD11DVDD211DVDD331DVDD451PVDD 12BGVDD 13AVDD115AVDD219AVDD325EPAD_GND65R130R127TX_n TX_p RX_p RX_nDefaultJumper OpenHSMC_RX_p5HSMC_RX_n5HSMC_TX_p5HSMC_TX_n5HSMC_CLKIN_p1HSMC_CLKIN_n1NET_HSMC_GXB_TX_p0NET_HSMC_GXB_TX_n0HSMC_TX_n0HSMC_CLKOUT_n1HSMC_CLKOUT_p1HSMC_RX_p6HSMC_RX_n6HSMC_TX_n6HSMC_TX_p6HSMC_RX_n1HSMC_RX_p1HSMC_RX_p7HSMC_RX_n7HSMC_TX_p7HSMC_TX_n7HSMC_TX_p1HSMC_TX_n1HSMC_RX_p2HSMC_RX_n2HSMC_CLKOUT0HSMC_JTAG_TCKHSMC_CLKIN0HSMC_JTAG_TDI HSMC_JTAG_TMS HSMC_JTAG_TDO HSMC_D1HSMC_TX_p2HSMC_TX_n2HSMC_GXB_TX_p0HSMC_GXB_TX_n0HSMC_D2HSMC_RX_p3HSMC_RX_n3HSMC_RX_p0HSMC_GXB_RX_n0HSMC_GXB_RX_p0HSMC_RX_n0HSMC_TX_n3HSMC_TX_p3HSMC_D3HSMC_RX_n4HSMC_RX_p4HSMC_TX_p4HSMC_TX_n4HSMC_TX_p0HSMC_D0HSMC_SDAHSMC_SCLI2C_SDA I2C_SCLHSMC_SDA HSMC_SCLVCC12_HSMCVCC12_HSMCVCC3P3_HSMCVCC3P3_HSMCVCC12_HSMCVCC3P3VCC3P3_HSMCTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R460C12010u 35V C2650.1u 25VTP1Dummy PinC2660.1u 25V R18722R49JP13HEADER 212C11510u 6.3V C24822u 25V 116416816516616729293131333335353737393930303232343436363838404041414343454547474949515153535555575759596161636365656767696971717373757577777979818183838585878789899191939395959797999942424444464648485050525254545656585860606262646466666868707072727474767678788080828284848686888890909292949496969898100100161161162162163163164164R18622XJ1Jumper-2.54mmVREF ADC_IN1ADC_IN2ADC_IN3ADC_IN5ADC_IN6ADC_IN7ADC_IN0ADC_IN4ex_ADC_SDO ADC_VREFADC_REFCOMP ex_ADC_CONVST ex_ADC_SDIex_ADC_SCK TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.C7810u 10V C800.1u 10VCH0CH1CH2CH3CH4CH5CH6CH7COMG N DG N D G N DG N DG N D G N DVREFREFCOMP SDISCKSDOCONVD V D DO V D DA V D D 1A V D D 1U17LTC2308CUF22232412345625910112018781516171412131921C1021n 50VC981n 50V C8210u 10VC991n 50V C1001n 50V TP13TP_YELLOWC790.1u 10VR8649.9C872.2u 10VC1011n 50V C840.1u 10VGPIO_D0GPIO_D2GPIO_D4GPIO_D6GPIO_D8GPIO_D1GPIO_D3GPIO_D5GPIO_D7GPIO_D9GPIO_D14GPIO_D12GPIO_D10GPIO_D18GPIO_D16GPIO_D22GPIO_D20GPIO_D24GPIO_D15GPIO_D13GPIO_D11GPIO_D19GPIO_D17GPIO_D23GPIO_D21GPIO_D25GPIO_D26GPIO_D28GPIO_D30GPIO_D32GPIO_D34GPIO_D33GPIO_D31GPIO_D29GPIO_D27GPIO_D35GPIO_D7GPIO_D11GPIO_D15GPIO_D19GPIO_D23GPIO_D27GPIO3GPIO20GPIO_D20Arduino_IO0CPU_RESET_n Arduino_Reset_nAnalog_In1Analog_In2Analog_In3Arduino_Reset_nAnalog_In0Arduino_AD4_IO14Arduino_AD5_IO15Analog_In6Analog_In7Arduino_IO11Arduino_IO12Arduino_IO13Arduino_Reset_nArduino_IO15Arduino_IO14GNDVCC5VCC12VCC3P3VCC3P3VCC5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.BAT54S D15BAT54S123JP14HEADER 2x3123456D38BAT54S123BAT54S D13BAT54S123R22222R2242.2K DNIRN418BAT54S BAT54S RN1118BAT54S D45BAT54S123BAT54S 3BAT54S R2252.2K DNID43BAT54S123JP9BOX Header 2X20M 12345678910111312141618202224262715171921232528293133353739303234363840Reserved 6x6mm tact switchSW1SW0SW2SW3BTN3BTN1BTN2BTN0VCC1P2VCC1P2TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.RN2318BUTTON1TACT SW DNI4321SW0SLIDE SW12345BUTTON3TACT SW DNI4321SW2SLIDE SW12345SW1SLIDE SW12345RN311RN2610K12345678BUTTON2TACT SW DNI4321RN2412012345678B2A2E1G0F0E0B1C1D1F1G1C0B0A0D0A1C2D2E2F2HEX0_D0HEX0_D1HEX0_D2HEX0_D3HEX0_D4HEX0_D5HEX0_D6HEX1_D0HEX1_D1HEX1_D3HEX1_D4HEX1_D2HEX1_D5HEX1_D6HEX2_D0HEX2_D1HEX2_D2HEX2_D3HEX2_D4HEX2_D5GPIO22GPIO23GPIO24GPIO25GPIO26GPIO27GPIO28GPIO30GPIO29HEX2_D0HEX3_D0HEX2_D1HEX3_D1HEX2_D2HEX2_D3HEX2_D4HEX2_D5HEX2_D6LEDR0LEDG1LEDG2LEDG3LEDG4LEDG5LEDG6LEDG7LEDR1LEDR2LEDR3LEDR4LEDR5LEDR6LEDR7VCC_HEX2VCC_HEXVCC_HEXVCC_HEX2VCC_HEXTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.e d dpc g b f a CA1CA2HEX07Segment Display12345610987ON1S2121615RN1868012345678e d c b f a CA1CA2HEX2124561098RN1668012345678RN1568012345678ON1S1SW DIP-812345678161514131211109RN1912345678e d dpc g b f a CA1CA2HEX17Segment Display12345610987R2010R20510kRN1768012345678Self Powered and Internal OSCUSB to UARTUART_CTSRX_LEDTX_LEDUART_RTSFT232_DP FT232_DM UART_RX UART_TX UART_RESET_nUART_RXLED UART_TXLED UART_CTS UART_RTSUART_CTSUART_RTSUART_PW_ENVCC5_UARTVCC3P3_UARTVCC5_UARTVCC5_USB_UARTVCCIO_UART VCC2P5VCC5TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.DNITP_YELLOWU4FT232R VCC19VCCIO 1G N D 4RESET 183V3OUT16USBDP 14USBDM15TXD 30RXD 2CTS#8RTS#32DSR#6DTR#31DCD#7RI#3CBUS022NC15A G N D 24NC212NC313NC525NC629NC423OSCI 27OSCO 28G N D 17G N D 20TEST26CBUS121CBUS311CBUS210CBUS49E P _G N D33R71M R14310kC140.1u 25VTPD2E001DRLRU2VCC 1NC2IO13GND4IO25D9LEDR21R220DNIC314.7u 6.3VL24321R142 4.7K C60.1u 25VR23R15733C330.1u 25VC80.1u 25V DNITP_YELLOWD8LEDG21R15633C254.7u 6.3VC270.1u 25VL2230ohm, 3A10kC184.7u 6.3VRamp TimeTsoft-start = 0.99 msec3.3V / 5AVCC1P1_PGOOD VCC3P3_PGOOD VCC3P3_INTVCCVCC3P3_INTVCCVCC12VCC1P1_INTVCCVCC3P3_INTVCCTitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.LTC3605EUF#PBFITH 6CLKIN24S G N D22P G N D 110E P _P G N D 225SW616FB4RT 1CLKOUT23R66316K R6910KC623.3n 50VR471050VU11PHMODE 2MODE 3TRACK/SS 5P V I N 117P V I N 218BOOST20PGOOD8SW111SW212SW313SW414SW515SW616RUN 7VON 9SVIN19I N T V C C21C4822u 25V C570.1u 25VD12CMDSH-3C17339p 50V 12.4K DNIC721n 50VR182100K+C656.3V330u 1239p 50V DNIR1940DNIPOWER SWC5022u 25VXJ3Jumper-2.54mmC58 2.2u 6.3VC7168p 50V2.5VTantalum330u 2L121uH 744311100R6715KR18411.5K DNIC510.1u 25VRamp Time = 1.2 msecVCC3P3VCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.R109200KC561u 10VC532.2u 10VLT3080-1U10OUT11OUT22OUT33SET 4IN28IN17NC6V_CONTROL 5OUT49DNIC494.7n 50VC521u 10VR44180KC5422u 6.3VC1124.7n 50V6.3VXJ6Jumper-2.54mmGND13URXFOSC_24BST_TMS URD UTXE UWR URXFSI_WU UD7EEPDATA EEPCSEEPCLK USB_RESETnBST_TDI BST_TDO ISP_TCK ISP_TMS ISP_TDI ISP_TDOUSB_RESETn TRGNST TRGNCSO TRGASDO TRGDCLK TRGNCE TRGTDO TRGTMSTRGOE TRGOEFPGA_nCEUART_RESET_nPWRONPWRON BST_TCK VCC5_USBVCC3P3TitleCopyright (c) 2011 by Terasic Technologies Inc. Taiwan.No part of this schematic design may be reproduced, duplicated, or used without the prior written permission of Terasic.All rights reserved.FT245BLLQFP-32TEST31RXF#12EEDATA 2XTIN 27XTOUT 28G N D17D718RD#16WR 15TXE#14A G N D 29EECS 32EESK 1RESET#4SI/WU 11PWREN#10USBDM 8G N D 9R14110KR2070DNIR13310KR1480DNIC14347p 50VBAT54SDW 123R13027EPM240M100C4N IO-B1-10G1IO-B1-11G2IO-B1-12F3IO-B1-13H1IO-B1-14H3IO-B1-15H2IO-B1-16L1IO-B1-17L2IO-B1-18K3IO-B1-19L3IO-B1-20K4IO-B1-21L4IO-B1-22K5IO-B1-23L5IO-B1-24L6IO-B1-25K6IO-B1-26J6IO-B1-27L7IO-B1-28K7IO-B1-29/DEV_OE L8IO-B1-30/DEV_CLRn K8IO-B1-31L9IO-B1-32K9IO-B1-33L10IO-B1-34K10IO-B1-35L11IO-B1-8/GCLK1E1IO-B1-9F1TCK K1TDI J2TDO K2TMS J1G N D I N TG 4G N D I N T E 8IO-B1-36J5IO-B1-37J7R14422。

Cyclone III资料

Cyclone III原型开发调试转载:/ilove314/1819329/Message.aspx 最近设计的Cyclone III原型板是特权同学第一次接触Cyclone III的器件。

原理图、PCB绘制、管脚分配上都碰到了一些问题,这些问题或多或少都是由于个人对新器件不熟悉、设计的时候有一些粗心大意造成的。

主要针对板级的硬件设计,这里凌乱的罗列一下,做一点总结,今后要多吸取教训,低级的失误要尽量避免。

1. 首先要提一个没有解决的问题,EP3C5E144/EP3C10E144/ EP3C16E144/ EP3C 25E144(是管脚完全兼容的不同资源的器件,Altera在这一点上是非常值得称道的)器件的PIIN11和PIN12存在不可同时使用的问题,这个问题出现在架构了一个NIOS2系统里集成了EPCS控制器的时候,在Cyclone II中是不需要分配这个EPCS控制器的管脚的(内部自动映射),而Cyclone III则需要手动分配(事先需要到Setting里动动手脚)。

EPCS的DCLK需要分配到PIN12上,工程中分配了一个SDRAM的D0脚给PIN11,编译到Fitting阶段就Error了。

在handbook里海找没什么成效,求助于搜索引擎,最终看到有人遇到相同的问题,但是给出的却是不是办法的解决办法:不用PIN11或者不用PI N12。

这个问题上特权同学也很是无可奈何,估计是Cyclone III器件的这两个脚做了一些信号耦合之类的检查,也不知道是否在工具选项里做一些设置可以取消此类检查。

也很期待有相同遭遇的朋友现身说法,告诉特权如何解决问题。

2. 再说两个很低级的错误,错的很傻,没有什么技术含量,只能给自己敲个警钟:干活的时候脑子一定要清醒。

两个错误分别和BOM表和网络标号有关。

先说和BOM表有关的,这个错误源于原理图上两个三端稳压器-1.2和-2.5的标示刚好反过来了,因为管脚定义和封装都一样所以也没留意,好在最后只影响BOM表的标示,但这也导致了第一块样板焊接的时候出现了1.2V和2.5V互换位置的惨剧,结果可想而知,EP3C10E144C7就这样挂了,非常的心疼。

将两层板进行到底,搞起CycloneIII

将两层板进行到底,搞起CycloneIII我以前DIY过两个FPGA的板子,都是Altera Cyclone II的。

几年前就买了的几片Cyclone III EP3C10一直没动,除了还没有DIY 项目必须要用到它外,还有个原因是Cyclone III系列需要3组电压供给,在两层板上走线不太好弄。

我也看到过别人在用两层PCB做的Cyclone III的设计,能跑起来说明也不是不可行。

今年已经DIY过两个带SDRAM的MCU板子,都是两层PCB。

这次我继续挑战一下,在两层板上把EP3C10加SDRAM搞起来,打算玩一玩NIOS II. 经过长时间的Layout斟酌,上个月总算把这个PCB 做出来了。

和我的前两个FPGA实验板不同的是,我这次设计成了核心板的形式,只保留FPGA+SDRAM以及必要的外围元件,把扩展GPIO接口和应用相关的接口件都挪到扩展板上去。

核心板和扩展板使用2.0 pitch的双排针/座来连接。

做出来是这个效果(简单做了几个2.54排针,以及JTAG座扩展卡):比如只需要用USB Blaster进行JTAG下载的时候,是这样用的(示意一下,另外还需要连3.3V电源)板子的背面:有2.5V和1.2V的LDO, 都是小封装的。

SDRAM还没有焊,待我把NIOS玩起来了再焊它调试。

扩展的排插是2.0 pitch,一方面是减小体积,另一方面是这种双排母比常见2.54的排母接触好。

正面:晶振也用3225的,比7050的省地方。

我手头恰好没有3225了,就焊了个2520更小尺寸的。

右边白色的插座是1.25 pitch 的连接器,可接6pin排线,用于少量I/O的扩展,连其它板子。

原理图:还是用我DIY一贯的EagleCyclone III 需要至少3组电压:1.2V的VCCINT, 2.5V的VCCA,以及平常3.0/3.3V的VCCIO. SDRAM只用到3.3V.Layout费了番心思。

cyclone3引脚整理

FLASH_nC E, nCSO

I/O, Output(A S, AP Note 13

DATA1, ASDO

PLL[1..4 ]_CLKOUT p Note 3

I/O, Output

Clock, Input

来自于 PLL [1..4]. 的可选 positive 正端外部 时钟输出 。该引脚 如果被用 作PLL输 出,能被 指定为单 端或差分 I/O标准 。

专用全局 时钟输入 引脚,用 于差分全 局时钟输 入或用户 输入引脚 的 negative 负端输入 。不支持 编程弱上 拉电阻。 不使用时 连接到 GND,注9.

MSEL[0.. 3]

Input

配置输入 引脚,用 来设置 Cyclone III 设备 配置方案 。一些较 小的设备 或包装选 项不支持 AP注 13flash 编程,不 使用 MSEL3引 脚。

这些引脚 内部连接 5-KΩ resistor to GND。 当未被使 用时,连 接至GND, 不悬空。 Device Family Handbook :配置, 设计安全 性, Cyclone III Devices 远程系统 升级。如 果使用 JTAG 配 置,连到 GND.

nCE 应 该接到 模式,则 GND

CONF_DON E

Bidirect ional (opendrain)

专用配置 状态引 脚,随着 状态输 出,在配 置前和配 置期间, CONF_DON E pin drives low 当状态输 入,所有 数据被接 收后, CONF_DON E变为高 。然后设 备初始 化,进入 用户使用 模式。该 引脚不可 做I/O引 脚,引脚 应被拉 高,通过 上拉电阻 被释放。 10-KΩ.

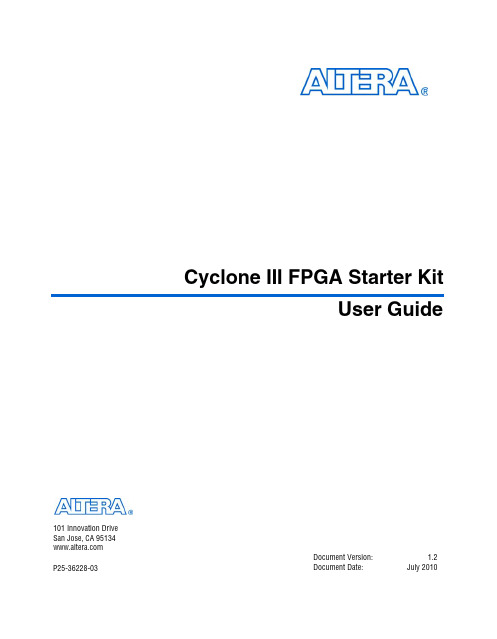

Cyclone III FPGA Starter Kit User Guide

101 Innovation DriveSan Jose, CA 95134Cyclone III FPGA Starter KitUser GuideDocument Version: 1.2Document Date: July 2010P25-36228-03© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX are Reg. U.S. Pat. & Tm. Off. and/or trademarks of Altera Corporation in the U.S. and other countries. All other trademarks and service marks are the property of their respective holders as described at /common/legal.html. Altera warrants performance of its semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of devicespecifications before relying on any published information and before placing orders for products or services.Part Number UG-01018-1.2ContentsChapter 1. Getting StartedIntroduction............................................................................................................................................1–1 Before You Begin...................................................................................................................................1–2 Further Information..............................................................................................................................1–2 Software Installation.............................................................................................................................1–2 Installing the Cyclone III FPGA Starter Kit..................................................................................1–2 Installing the Quartus II Web Edition Software..........................................................................1–4 Chapter 2. Development Board and Control Panel SetupDevelopment Board Setup...................................................................................................................2–1 Requirements....................................................................................................................................2–2 Powering Up the Development Board..........................................................................................2–2 Installing the USB-Blaster Driver........................................................................................................2–2 Control Panel Setup...............................................................................................................................2–3 Configuring the FPGA Using the Quartus II Programmer.............................................................2–3 Chapter 3. Using the Control PanelOverview.................................................................................................................................................3–1 Control Panel Start................................................................................................................................3–1 LEDs and Buttons..................................................................................................................................3–2 Illuminating LEDs............................................................................................................................3–2 Buttons Indicators............................................................................................................................3–3 DDR SDRAM/SSRAM/On-Chip Controller...............................................................................................................3–3 Read/Write Data..............................................................................................................................3–4 Read from a File................................................................................................................................3–5 Write to a File...................................................................................................................................3–5 Flash Memory Programmer.................................................................................................................3–5 Flash Memory Tab...........................................................................................................................3–6 CFI Query..........................................................................................................................................3–6 Read/Write Data..............................................................................................................................3–7ContentsChapter 4. Measuring Power on the Cyclone III Starter BoardIntroduction............................................................................................................................................4–1 Measuring Power...................................................................................................................................4–2 Changing the Example Design.......................................................................................................4–3 Appendix A. Programming the Configuration Flash DeviceOverview................................................................................................................................................A–1 Creating a Flash-Programmable POF File........................................................................................A–1 Programming the Flash Device..........................................................................................................A–5 Additional InformationRevision –i How to Contact –ii Typographic –ii1.Getting StartedIntroduction Welcome to the Altera® Cyclone®III FPGA Starter Kit, which includes afull-featured field-programmable gate array (FPGA) development board,hardware and software development tools, documentation, andaccessories needed to begin FPGA development.The development board includes an Altera Cyclone III FPGA and comespreconfigured with a hardware reference design stored in flash memory.You can use the development board as a platform to prototype a varietyof FPGA designs.The starter kit provides an integrated control environment that includesa software controller in a control panel application, a USB commandcontroller, a multi-port SRAM/DDR SDRAM/flash memory controller,and example designs specified in Verilog code. You can use this design asa starting point for test designs.This user guide addresses the following topics:■How to set up, power up, and verify correct operation of thedevelopment board.■How to install the Cyclone III FPGA Starter Kit.■How to install the Altera® Quartus II Web Edition software.■How to set up and use the control panel, a graphical user interface(GUI), to manipulate components on the board, implementapplications.■How to configure the Cyclone III FPGA.■How to set up and run example designs.f For complete details on the development board, refer to theCyclone III FPGA Starter Board Reference Manual.Before You BeginBefore You Begin Before proceeding, check the contents of the kit:■Cyclone III FPGA Starter Development Board ■12-V DC power supply■USB cablef For the most up-to-date information on this product, visit the Alterawebsite at /products/devkits/altera/kit-cyc3-starter.html.FurtherInformationFor other related information, refer to the following websites:Software Installation This section describes the following procedures:■“Installing the Cyclone III FPGA Starter Kit”■“Installing the Quartus II Web Edition Software” on page1–4 Installing the Cyclone III FPGA Starter KitThe license-free Cyclone III FPGA Starter Kit installer includes all the documentation and design examples for the kit.To install the Cyclone III FPGA Starter Kit, follow these steps:1.Download the Cyclone III FPGA Starter Kit installer from theCyclone III FPGA Starter Kit page of the Altera website.Alternatively, you can request a development kit DVD from theDevelopment Kits, Daughter Cards & Programming Hardware page of the Altera website.For More Information About Refer ToAdditional daughter cardsavailable for purchase/products/devkits/kit-daughter_boards.jspCyclone III handbook /literature/lit-cyc3.jspCyclone III reference designs /products/devkits/altera/kit-cyc3-starter.htmleStore if you want topurchase devices/buy/devices/buy-devices.htmlCyclone III Orcad symbols /support/software/download/pcb/pcbpcb_index.htmlNios® II 32-bit embeddedprocessor solutions/technology/embedded/emb-index.htmlGetting Started 2.Follow the on-screen instructions to complete the installationprocess.The installation program creates the Cyclone III FPGA Starter Kit directory structure shown in Figure1–1.Figure1–1.Cyclone III FPGA Starter Kit Default Installed Directory StructureTable1–1 lists the file directory names and a description of their contents.Table1–1.Installed Directory ContentsDirectory Name Description of Contentsboard_design_files Contains schematic, layout, assembly, and bill of materialboard design files. Use these files as a starting point for anew prototype board design.demos Contains demonstration projects that may or may notcontain up-to-date source code.documents Contains the development kit documentation.examples Contains the example design files for the Cyclone III FPGAStarter Kitfactory_recovery Contains programming files for returning board to factorydefault condition.Software InstallationInstalling the Quartus II Web Edition SoftwareThe Quartus II Web Edition software provides the necessary tools fordeveloping hardware and software for Altera FPGAs. Included in theQuartus II Web Edition software are the Quartus II software, the Nios IIEDS, and the MegaCore® IP Library. The Quartus II software (includingSOPC Builder) and the Nios II EDS are the primary FPGA developmenttools for creating the reference designs in this kit.To install the Quartus II Web Edition software, follow these steps:1.Download the Quartus II Web Edition software from the Quartus IIWeb Edition Software page of the Altera website. Alternatively, youcan request a DVD from the Altera IP and Software DVD RequestForm page of the Altera website.2.Follow the on-screen instructions to complete the installationprocess.f If you have difficulty installing the Quartus II software,refer to Quartus II Installation & Licensing for Windows andLinux Workstations.The Quartus II Web Edition software includes the following items:■Quartus II software—The Quartus II software, including the SOPCBuilder system development tool, provides a comprehensiveenvironment for system-on-a-programmable-chip (SOPC) design.The Quartus II software integrates into nearly any designenvironment and provides interfaces to industry-standard EDAtools.f To compare the Quartus II subscription and web editions,refer to Altera Quartus II Software—Subscription Edition vs.Web Edition. The kit also works with the subscriptionedition.■MegaCore IP Library—A library that contains Altera IP MegaCorefunctions. You can evaluate MegaCore functions with the OpenCorePlus feature to perform the following tasks:●Simulate behavior of a MegaCore function in your system●Verify functionality of your design, and quickly and easilyevaluate its size and speed●Generate time-limited device programming files for designs thatinclude MegaCore functions●Program a device and verify your design in hardwareGetting Started 1The OpenCore Plus hardware evaluation feature is anevaluation tool for prototyping only. You must purchase alicense to use a MegaCore function in production.f For more information about OpenCore Plus, refer toAN320: OpenCore Plus Evaluation of Megafunctions.■Nios® II Embedded Design Suite (EDS)—A full-featured tool set that allows you to develop embedded software for the Nios II processor which you can include in your Altera FPGA designs.Licensing ConsiderationsThe Quartus II Web Edition software is license-free and supports Cyclone III devices without any additional licensing requirement. This kit also works with the Quartus II Subscription Edition software, after you obtain the proper license file. To purchase a subscription, contact your Altera sales representative.Software Installation2.Development Board andControl Panel Setup DevelopmentBoard SetupThe development board is preloaded with an example design todemonstrate the Cyclone®III device and board features. At power-up,the preloaded design also enables you to quickly confirm that the boardis operating correctly.Figure2–1 shows the Cyclone III development board layout andcomponents.Figure2–1.Cyclone III Development Board Layout and Components1-Mbyte SSRAM (U5)DC PowerInput (J2)Power Switch (SW1)16-MbyteParallelFlash (U6)ConnectorFlash LEDUSBUART (U8)JT AG Header (J4)32-MbyteDDR SDRAM (U4)Reconfigureand ResetPush Buttons50-MHzSystem ClockUser LEDsUser Push Button SwitchesHSMCConnector (J1)Cyclone III Device (U1)Configuration Done LEDSense Resistor for FPGACore Power Measurement (JP6)Sense Resistorfor Shared I/OAltera Corporation 2–1Installing the USB-Blaster DriverRequirementsBefore you proceed, ensure that the follwing items are installed:■Altera® Quartus®II software on the host computer■Cyclone III FPGA Starter Kit■USB-Blaster™ driver software on the host computer. TheCyclone III FPGA starter development board includes an integratedUSB-Blaster circuitry for FPGA programming.Powering Up the Development BoardTo power-up the development board, follow these steps:1.Ensure that the ON/OFF switch (SW1) is in the OFF position (up).2.Connect the USB-Blaster cable from the host computer to theUSB-Blaster port on the development board.3.Connect the 12-V DC adapter to the development board and to apower source.w Only use the supplied 12-V power supply. Power regulationcircuitry on the board could be damaged by supplies greaterthan 12V.4.Press the power switch (SW1).5.Confirm that all four user LEDs are ON.Installing the USB-Blaster Driver The Cyclone III FPGA development board includes an integratedUSB-Blaster circuitry for FPGA programming. However, for the host computer and board to communicate, you must install the USB-Blaster driver on the host computer.Installation instructions for the USB-Blaster driver are available on the Altera website at /support/software/drivers/dri-index.html. On the “Altera Programming Cable Driver Information” page of the Altera website, locate the table entry for your configuration and click the link to access the instructions.2–2Altera CorporationDevelopment Board and Control Panel SetupControl Panel Setup Setting up the control panel involves the following:■Configuring the FPGA■Starting the control panel1Power up the board and ensure that is is operational.For more information about using the control panel, refer to the “Using the Control Panel” chapter.Configuring the FPGA Using the Quartus II Programmer You can use the Quartus II Programmer to configure the FPGA with a specific .sof. Before configuring the FPGA, ensure that the Quartus II Programmer and the USB-Blaster driver are installed on the host computer, the USB cable is connected to the development board, power to the board is on, and no other applications that use the JTAG chain are running.To configure the Cyclone III FPGA, follow these steps:1.Start the Quartus II Programmer.2.Click Add File and select the path to the desired .sof.3.Turn on the Program/Configure option for the added file.4.Click Start to configure the selected file to the FPGA. Configurationis complete when the progress bar reaches 100%.Altera Corporation 2–3Configuring the FPGA Using the Quartus II Programmer2–4Altera Corporationing the Control PanelOverview The control panel consists of the following:■The graphical user interface (GUI) application on the host computer■The standard Nios II hardware design running on the board'sCyclone III FPGA deviceAfter installing the Cyclone III FPGA Starter Kit, you can locate thecontrol panel for the hardware and software in the<kit path>\demos\control_panel directory.The design downloaded to the Cyclone III device implements acommand controller that processes board commands sent over theUSB-Blaster from the control panel. To perform the appropriate actions,the command controller communicates with the controller of the targetedboard I/O device.You can perform the following actions with the control panel:■Light up LEDs■Detect push button presses■Read from and write to the DDR SDRAM, SRAM, flash memory, andon-chip RAMThe following sections describe how to perform the above actions withthe control panel already open on the host computer. If not already open,launch the control panel as described in “Control Panel Start”.Control Panel Start The Cyclone III development board is shipped with an example design stored in the flash memory which configures the Cyclone III FPGA upon power-up with the standard Nios II design.1For an older version of the Cyclone III development board shipped with the Cyclone III FPGA Starter Kit v7.1.0, v7.2.0, or8.0.0 application, you must manually configure thecycloneIII_3c25_start_niosII_standard.sof into the FPGAbefore launching the control panel application.Altera Corporation 3–13–2Altera Corporation LEDs and ButtonsYou can locate the source for the example design in the <kitpath>\examples\cycloneIII_3c25_starter_board_standard directory. 1To launch the control panel user interface, run thecontrol_panel.exe program found in the <kitpath >\demos\control_panel directory (Figure 3–1).Figure 3–1.Control Panel WindowLEDs andButtons Illuminating LEDs To illuminate an LED, follow these steps:1.The LED & Buttons tab should be visible when the application runs.If it is not visible, click the LED & Buttons tab (Figure 3–2).2.Click on LEDs to individually turn on the LEDs.Using the Control PanelButtons Indicators1.Press the push-button switches on the board. Notice that buttons onthe GUI change accordingly.Figure3–2.Control Panel Window for LEDs and ButtonsDDR SDRAM/ SSRAM/On-Chip Controller You can perform the following types of memory read/write operations with the control panel:■Read from and write to the DDR SDRAM, SSRAM, or on-chip device ■Write entire contents of a file, to the DDR SDRAM, SSRAM, or on-chip device■Read contents of the DDR SDRAM, SSRAM, or on-chip device, to afileAltera Corporation 3–33–4Altera Corporation DDR SDRAM/ SSRAM/On-Chip ControllerThe following sections describe how to access the DDR SDRAM. You can use the same procedure to access the SSRAM.Read/Write DataTo read from and write to the DDR SDRAM, follow these steps:1.Click the DDR SDRAM tab (Figure 3–3). The Address columnindicates the hex address of the DDR SDRAM. The values inside the 0-3, 4-7, 8-B , and C-F columns are the DDR SDRAM contents in hex words format.Figure 3–3.Control Panel DDR SDRAM Tab2.To write a 32-bit word to the DDR SDRAM, click the desiredlocation, enter the desired value in hex format, and press Enter.Using the Control PanelRead from a FileTo read the contents of a file and load it to the DDR SDRAM, follow these steps:1.Click Load File.2.Browse to sample.txt located in the control_panel directory andclick Open. This step instantiates the DDR SDRAM controller and loads the text contents into the DDR SDRAM. Notice that the Data to Ascii-text column shows the DDR SDRAM contents in Asciivalue.Write to a FileTo write the contents of the DDR SDRAM to a file, follow these steps:1.Click Save File.2.Enter the start and end addresses of the DDR SDRAM.3.Choose a file name and click Save. This instantiates the controller toread the DDR SDRAM contents from the start address to the endaddress, and write the contents to a file.Flash Memory Programmer You can perform the following operations to read from and write to the board’s flash memory with the control panel:■Perform a CFI query of flash memory■Erase select blocks of flash memory■Write 32-bit hex word to flash memory■Write a binary file to flash memory■Load the contents of the flash memory into a filec Do not exit from the control panel while erasing the flashmemory.Altera Corporation 3–5Flash Memory ProgrammerFlash Memory TabTo use the flash memory functions, click the Flash Memory tab(Figure3–4).Figure3–4.Control Panel Flash Memory TabCFI QueryThe common flash interface (CFI) flash memory devices conform to basicflash commands. The most basic command is Query which switches thedevice into a ROM table mode so that features of the flash device aredetermined by reading values from the table.To perform a CFI query using the host application, click CFI Query.Notice that the memory table displays contents that correlate with thetable contents as described in the device datasheet.To put the flash device back in user mode, press Reset on the controlpanel.3–6Altera CorporationAltera Corporation 3–7Using the Control PanelRead/Write DataTo read from and write to the flash memory, follow these steps:Figure 3–5.Control Panel Flash Memory Tab1.Click Erase Block to perform a block erase of the flash memory. The Address column indicates the hex address of the flash memory. The values inside the 0-3, 4-7, 8-B , and C-F columns are the flash memory contents in hex words format.2.To write a 32-bit word to the flash memory, click the desired location, enter the desired value in hex format, and press Enter.Flash Memory Programmer3–8Altera Corporation4.Measuring Power on theCyclone III Starter BoardIntroduction One of the main features of the Cyclone®III device is its low powerconsumption. You can measure the power of the 3C25 device on theCyclone III starter board under various conditions with an exampledesign provided with the kit.The power example design allows you to control the amount of logicutilized in the FPGA, the clock frequency, the number of I/Os being used,and measure the effect on the power to the Cyclone III device. Because theCyclone III starter board has only four buttons and four LEDs, interactionwith the board is minimal as defined below.Table4–1 describes the functionality of the four input buttons that controlthe power example design.Tables4–2 and 4–3 describe how the LEDs indicate the example design’scurrent power state.Table4–1.Four Input Button FunctionalityButton FPGA Pin Type Description1F1Reset Resets the demo to the beginning, nodei_nrst.2F2Toggle Advances the example design to the next higherfrequency, node i_nfreq_next.3A10Toggle Advances the example design to the next higherresource utilization, node_i_nperc_next.4B10Press and Hold Enables the outputs to toggle, nodei_noutput_ena.Table4–2.LEDs Power State (Frequency)DisplaysLEDsStateClock Frequency(MHz)MSB LSBFrequency LED2 LED10000133106711100Altera Corporation 4–14–2Altera CorporationMeasuring PowerThe design used for power measurement is a replicated set of randomly filled ROMs that feed a multiplier block and a shift register that is fed by a signal that changes every clock cycle. Tables 4–2 and 4–3 show the power state which represent the percent of the full design used. As compiled, this full design uses:■Logic elements: 22,493/24,624 (91%)■Combinational functions: 1,961/24,624 (8%) ■Dedicated logic registers: 21,133/24,624 (86%) ■Total registers: 21,133 ■Total pins: 73/216 (34%)■Total memory bits: 524,288/608,256 (86%)■Embedded Multiplier 9-bit elements: 128/132 (97 %)■Total PLLs: 1/4 (25%)Measuring PowerThe example design is located in<kit install >\examples\cycloneIII_3c25_start_power_demo . Configure the FPGA with the .sof found in the directory. 1The input clock (i_clk PIN_B9) is the 50-MHz oscillator on the board, which generates the input clock for the reference design through a PLLfFor more information on configuring the FPGA, refer to “Configuring the FPGA Using the Quartus II Programmer” on page 2–3.Current sense resistors (0.010 ± 1%) are installed at locations JP6 (FPGA core power) and JP3 (FPGA I/O power + other device I/O power). With a digital multimeter set to mV measurement range, the resistor at location JP6 measures the core power. The resistor at location JP3 measures the I/O power. To measure the current being used in various configurations, use the following steps:Table 4–3.LEDs Power State (Resources)DisplaysLEDsState% of Design UsedMSBLSBResourcesLED4LED30025%0150%1075%11100%Measuring Power on the Cyclone III Starter Board1To obtain the power (P) in milliwatts, measure <MeasuredVoltage> (the voltage across the sense resistors at JP6 or JP3) inmV and calculate the nominal power using the equation:P = 100 x <Measured Voltage> x <Supply Voltage>where <Supply Voltage> is 1.2 V for JP6 and 2.5 V for JP3.You can use the four input buttons to advance through the various powerstate as outlined in Table4–2. Notice how current increases as frequencyand resource usage increase.You can also measure the I/O power consumed by measuring the voltageacross sense-resistor JP3 when Button 4 is pressed and held. Because this2.5-V power rail is shared with other devices, there is a nominal 100mWthat must be subtracted from the calculated I/O power to obtain theFPGA I/O power.The number of I/O pins used is controlled by the resource state (shownin Tables4–2 and 4–3). For each increment in resources, 16 additional I/Opins are added (refer to Table4–4).Table4–4.I/O Pin & Resource StateLED4/LED3Number of I/O Pins0016013210481164Similarly, the toggle-frequency of these I/O pins is set by the overalldesign frequency (refer to Table4–1).Changing the Example DesignThe source code for the Cyclone III power example design is alsoprovided so you can use it as a starting point for your own measurements.You can adjust the number of outputs by changing parameterNUM_OUTPUTS_PER_STAMP. The default is 16, which for four resourcepercentage steps equates to 16 x 4 = 64.The appropriate pins to be used as outputs are pre-assigned to the HSMCconnector (J1). If you would like to look at more than the 76 I/Os availableon J1, you need to make the appropriate pin assignments.Altera Corporation 4–3。

Cyclone III的LVDS接口注意事项

Cyclone III的LVDS接口注意事项对于Cyclone III器件,handbook中明确提到了以下的一些注意事项:1.对于作为LVDS传输的bank必须接2.5V的VCCIO。

2.左右bank(即1/2/5/6bank)的LVDS发送差分对信号无需外接匹配电阻,上下bank(即3/4/7/8bank)则需要。

3.分配管脚时,左右bank的LVDS差分信号在IO分配时选择IO标准为LVDS;上下bank的LVDS差分信号在IO分配时选择IO标准为LVDS_E_3R,好像没什么特殊含义,应该是帮助开发工具识别是哪个bank上的LVDS信号而已吧。

多谢网友iampeter在博文中提到这一点,帮助没太认真消化handbook的特权同学解决了这个问题。

除此以外,还有其它的一些技巧和注意事项,特权同学做了一点归纳:1.在分配管脚时,只要指定LVDS信号的p端(+),则n端(-)自动匹配;实际在verilog 中只要一个信号接口即可,无需一个差分对接口定义在源代码中。

2.可以使用MegaWizard中的IP核ALTLVDS实现并串转换的LVDS传输。

具体配置和说明建议参考相关手册。

3.接收部分没有进行测试和实验,不做归纳和整理。

4. 图1是一个7位并行输入的LVDS数据发送采集的波形,可以看到在默认输出时钟相位情况下,最高位bit6置1时为时钟上升沿后的第一个数据。

数据传送的效果大体如图2所示。

实际传输的相位是可以根据需要调整的。

图1 (上为时钟,下位数据)参考资料:1. /iampeter/240246/Message.aspx#2. Cyclone III handbook。

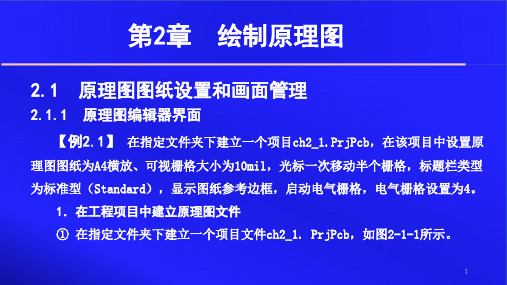

Altium Designer 14原理图与PCB设计教程 第二章 绘制原理图

★★ 2.2 绘制简单原理图

17

3.放置元器件符号 ① 执行菜单命令Place → Part,弹出Place Part放置元器件符号对话框, 如图2-2-14所示。 ② 将表2-1中R1的属性值分别输入到各自 对应项中,输入完毕单击【OK】按钮。 ③ 此时可按【空格】键旋转方向,按【X】 键水平翻转,按【Y】键垂直翻转,确定方向后, 在适当位置单击,放置好一个符号。 单击【Cancel】按钮退出。

② 按【Tab】键,弹出Power Port电源符

号属性对话框。

● Net:电源、接地符号的网络标号

● Style:电源、接地符号的各种显示形式

● Color:电源、接地符号的显示颜色

图2-2-21 Power Port电源符号属性对话框

★★ 2.2 绘制简单原理图

22

③ 在属性对话框的Net中输入GND,单击Style旁的下拉菜单按钮,从中选择 Power Ground,取消勾选Show Net Name右侧复选框,单击【OK】按钮。

★★ 2.1 原理图图纸设置和画面管理

2

③ 执行菜单命令File → Save,选择项目文件ch2_1.PrjPcb所在文件夹, 并将该原理图文件命名为li2-1.SchDoc,单击【保存】按钮。

EP3C16F484C6中文资料(Altera)中文数据手册「EasyDatasheet - 矽搜」

芯片中文手册,看全文,戳

1–2

电气特性

1

超出所列条件

表1-1 对器件造成永久性损坏.

此外,在延长时间周期绝对最大额定值设备操作具有设备不利影响.

表 1-1. Cyclone III器件绝对最大额定值

符

参数

VCCINT VCCIO

VCCA

电源电压为内部逻辑

电源电压为输出缓冲器

电源电压(模拟),用于锁相环 (PLL)调节器

Min –0.5 –0.5 –0.5 –0.5 –0.5 –25 —

— –65 –40

最大允许过冲或冲电压

在转换过程中,输入信号可以过冲到中列出电压 冲至-2.0 V电流小于100mA幅度和周期小于20纳秒短.

表1-2 列出所允许最大输入电压过冲和 过冲电压作为在装置寿命百分比持续时间. 允许最大过冲持续时间被指定为高时间比设备寿命百分比.

运行条件

当Cyclone III器件在一个系统中实现,它们是根据一组定义参数分级.为防护持 Cyclone III器件中最高性能和可靠性,系统设计人员必须考虑本文件中操 作要求. Cyclone III器件提供商用,工业和汽车级版本.商业设备在-6(最 快),-7和-8速度等级提供.工业和汽车设备仅在-7速度年级课程.

V

—

3.135出缓冲器,3.0-V

手术

—

2.85

3

3.15

V

VCCIO (3), (4)

电源电压为输出缓冲器,2.5-V

手术

电源电压为输出缓冲器,1.8-V

手术

电源电压为输出缓冲器,1.5-V

手术

—

2.375 2.5 2.625 V

—

1.71 1.8 1.89

Cyclone_III配置

Cyclone_III配置Cyclone III 的配置全文翻译自Altera公司Cyclone III的器件手册。

所有表格与图标标号与手册原文一致,以便于查对。

出于个人需要,仅翻译了AS与JTAG配置两部分,且仅都配置一片FPGA芯片。

可以通过压缩数据的方法以节约存储空间,并节省程序load时间(page 220);9通过Remote System Upgrade方式可以减少新产品面市的时间(page 221);9AS Configuration(Serial Configuration Devices)表10-6显示的是对各种配置电平来说,MSELx管脚的接法单一器件配置四个接口管脚包含了串口时钟(DCLK),串行数据输出(DATA),AS 数据输入(ASDI),以及低电平有效的片选信号(nCS)。

注:1)上拉一个电阻,连接到该管脚所在的bank的VCCIO;2)Cyclone III器件通过DATA[1]-to-ASDI路径控制配置芯片;3)nCEO管脚浮空,或者当没有连接到另一个器件的nCE管脚时,可以当作通用IO使用;4)MSEL管脚的设置,用于选择不同的电平标准和不同的POR时间;参考表10-6,选择接法;5)这些是复用管脚。

FLASH_nCE管脚在AS配置电路图中当作nCSO功能使用,DATA[1]管脚当作ASDO功能使用;6)这些串接的电阻尽可能靠近配置芯片当连接一个配置芯片到Cyclone III器件时,DATA[0]管脚必须串一个电阻,并应接近配置芯片。

配置器件和Cyclone III芯片间连线的长度应符合表10-8所推荐的值。

当选择AS配置方式的时候,BAMK 1的IO电压必须是3.3,3.0或2.5。

上电以后,CIII器件有一个POR时间的延迟,在此期间,nSTATUS和CONF_DONE 会一直为低,所有的IO也都是三态输出。

芯片配置的三个阶段分别是复位,配置和初始化。

CycloneIII使用注意事项V1.0

© 2008 Cytech Technology Ltd – Confidential

Notice6:在使用增量编译时的告警

在使用增量编译的时候,如果在子工程中分配了管脚,在导出.QXP网表 文件以及在定层导入网表的时候,QUARTUS会出现如下的警告,会造成 用户的误解,导出网表时的警告:

Warning: Complex I/O atoms found during Design Partition Export Warning: Node GZ_DATA[0] is a non-trivial IO atom Warning: Node GZ_DATA[1] is a non-trivial IO atom Warning: Node GZ_DATA[2] is a non-trivial IO atom Warning: Node GZ_DATA[3] is a non-trivial IO atom Warning: Node GZ_DATA[4] is a non-trivial IO atom Warning: Node GZ_DATA[5] is a non-trivial IO atom Warning: Node GZ_DATA[6] is a non-trivial IO atom Warning: Node GZ_DATA[7] is a non-trivial IO atom Warning: Node flash_d[0] is a non-trivial IO atom Warning: Node flash_d[1] is a non-trivial IO atom Warning: Node flash_d[2] is a non-trivial IO atom Warning: Node flash_d[3] is a non-trivial IO atom Warning: Node flash_d[4] is a non-trivial IO atom Warning: Node flash_d[5] is a non-trivial IO atom Warning: Node flash_d[6] is a non-trivial IO atom Warning: Node flash_d[7] is a non-trivial IO atom

011_C-III诊断仪介绍课件

印度 TATA公司生产

CONSULT-IIIplus

印度 TATA公司生产 日本 佳能软件生产

相同

21

目录

1 C3+ —基本诊断功能 2 C3+ —主要改进内容 3 C3+ —软硬件兼容性状况 4 C3+ —基本诊断功能使用 5 C3+ —主要菜单画面介绍 6 C3+ —相关文件夹介绍 7 C3+ —操作手册(OM)的改进 8 C3+ —NATS系统改进(计划) 9 C3+ —MI功能使用信息 10 C3+ —帮助功能

第四部分基本诊断功能的使用

1.屏幕截图与插入防盗卡后对应的画面有所不同。

备注:虽然未插入发动机防盗卡时不能 启动发动机防盗按钮,但本培训材料中 没有显示该状态。 如果插入发动机防盗卡,则无法使用非 防盗阻动系统的诊断菜单。

2.虽然我们努力使表达方式易于理解,但编制本培训材料时显示的字符仍未确定。因此, 所显示的字符可能与产品实际版本不同。

4.增加了菜单按键功能2/2

返回

NISSAN

发动机 启动(日产系列车辆) 启动(雷诺系列车辆)

子模式 突出 复制

启动

系统调用

突出

利用菜单按键显示与CONSULT-II的这个部分 对应的操作,因此像CONSULT-II一样容易理 解和使用。

15

选择系统 发动机 自动变速箱 安全气囊

选择诊断模式 工作支持 自诊断结果 数据监视器

画面结构易于理解,因此很容易访问用户需要使用的功能。

3.增加了分层显示区

示例)诊断(所有系统)的执行

-由于用户投诉无法判断当前画面所属的功能,因此增加了分层显示区并显 示先前画面的记录,因此可以判断当前画面所属的功能(画面)。

CYCLONE III EPCS使用方法

一、只使用FPGA硬件资源,不使用NIOS的时候

需要将nCEO引脚设为用户引脚,注意:一般编译器是默认它为程序下载的引脚的

将nCEO设为用户IO,其它的保留原样

二、使用NIOS的时候

由于CD0板子上没有设计FLASH。

所以在使用NIOS的时候,需要把程序存在EPCS器件中。

CYCLONE III器件跟其它器件的EPCS使用方法不同。

将DEVICE AND PIN OPTIONS页全部置为USER IO

在SOPC中添加epcs_flash_controller

在FPGA工程的顶层模块中添加EPCS控值器的接口

在NIOS的FLASH PROGRAMMER中做如下设置

将FPGA的SOF文件用QUARTUS的通过JTAG下载到FPGA后,

在NIOS的FLASH PROGRAMMER中点这时,NIOS的FLASH

PROGRAMMER会把.SOF文件和NIOS生成的.ELF文件合在一起,生成另一个配置文件下载到板子上的EPCS芯片中

重新上电,FPGA就以正常运行NIOS+FPGA的程序了

注意:在使用NIOS的时候FPGA的PIN_22因为太靠近PIN_23:DCLK(FPGA提供给EPCS 芯片的时钟)而不能再使用(使用时QUARTUS编译器会报错)。

PIN_22对应了CD0板子上的GPIO1[13],

所以在有NIOS的工程中都没有使用这一个引脚,对应的有NIOS的FPGA顶层也写成了如下:

跳过了…[12]这个引脚。

Cyclone III FPGA系列

Cyclone III FPGA系列:一切皆有可能前所未有的同时实现了低功耗、高性能和低成本Cyclone® III FPGA系列前所未有的同时实现了低功耗、高性能和低成本,大大提高了您的竞争力。

其特性以及Cyclone III FPGA体系结构为您的大批量、低功耗、低成本应用提供了理想的解决方案。

为满足您独特的设计需求,这一FPGA系列包括:∙Cyclone III:功耗最低、成本最低的高性能FPGA∙Cyclone III LS:具有安全特性、功耗最低的FPGA Cyclone III LS器件具有200K逻辑单元、8 Mbits嵌入式存储器以及396个嵌入式乘法器,是高性能处理、低功耗应用的理想选择,包括:轻松达到您的功耗目标具有200K逻辑单元(LE)、8-Mbits存储器,而静态功耗不到1/4瓦,该系列设立了功耗标准。

采用台积电(TSMC)的低功耗(LP)工艺技术进行制造,无论是通信设备、手持式消费类产品,还是软件无线电设备,这些FPGA都能够轻松满足您的功耗预算。

设计安全性Cyclone III LS FPGA利用低功耗、高性能FPGA平台,在硬件、软件和知识产权(IP)层面上率先实现了一系列安全特性。

一系列安全特性保护了您的IP不被篡改、逆向剖析和克隆。

而且,这些器件还使您能够通过设计分离特性,在一个芯片中实现冗余功能,从而减小了实际应用的体积、重量和功耗。

全面的设计资源为确保流畅、成功的设计流程,帮助您更快的将构思变为收益,Altera 提供全面的Cyclone III FPGA设计环境,包括:∙Quartus® II开发软件∙成熟的IP库∙Nios® II,世界上最通用的嵌入式处理器∙低成本开发套件∙专用参考设计将您的设计从构思变为产品,更迅速推向市场。

采用Cyclone III FPGA,一切皆有可能。

相关链接∙观看划分FPGA设计,实现冗余和信息安全网播∙下载Cyclone III FPGA手册(PDF)∙观看Cyclone III FPGA视频Cyclone III 器件系列体系结构Cyclone® III FPGA前所未有地同时实现了低功耗、低成本和高性能。

cyclone

配准实习报告(时间:11月8日)实习目的:掌握Cyclone软件的距离影像配准技术和操作过程。

实习要求:掌握连接点配准法、特征面配准法、公共点云配准法、混合法、控制点配准法。

提交结果:1.实验报告2.配准好的数据库操作步骤一、运行Cyclone添加服务器文件夹:将服务器的名称默认为文件夹的名称创建一个空的数据库,命名为Taihedian加载ptx文件,依次加载06.ptx,08.ptx,10.ptx,13.ptx到`Taihedian;手动配准过程1.首先检查原数据的精度;2.在导航条中,在工程目录下创建配准目标,一般为两个;3.在导航视窗中,运行Cyclon e软件;4.在以计算机名称命名的服务器下建立数据库,并命名为Taihedian;附图1 Cyclone 导航条5.对数据库中加载预配准的*.ptx格式文件;6.创建ScanWorld;7.双击打开配准视窗;8.添加需配准的ScanWorld,并设置其中一个为主ScanWorld;附图 2 配准选择视图9.运行点云约束向导;附图3 利用点云约束向导进行配准前选择两个点云图附图4 提示信息:进行配准前选公共点10.选择后点击更新,在ControlSpaces中加载点云;附图5 加载点云数据如上11.用多选模式功能手工添加ScanWorld间的约束,然后进行配准;12.开始配准;附图6 配准进程中(一)附图7 配准进程中(二)13.在配准视窗中,批准精度显示如下:图表 114.创建并打开模型空间ModelSpace;15.在导航视窗中,创建并打开模型空间如下:图表 2附图8 创建配准后模型空间如图示附图9 配准结果精度自动点配准1.用靶标点自动配准,其精度显示如下:图表 3 用靶标点自动进行配准精度显示面配准1.在模型空间创建ModelSpace视窗并打开;图表4 查看模型空间的视图2.在ModelSpace中创建同名面3.在ControlSpace中可以查看同名面4.图表7 用特征面匹配的结果关于配准的几点说明ControlSpace:与ModelSpace相似,用于观察,组织,移除对象;此外,也可用于手动添加约束。

CycloneIII EP3C25 引脚信息说明

41 42 43 44 45 46 47

L4 L3 M2 M1 M3 P2 P1 R2 R1 T2 T1 T3 DQS1L/CQ1L#, DPCLK1

DQ1L DQ1L DQS1L/CQ1L#, DPCLK1 DQ1L

DQ3L DQ3L DQ1L DQ1L DQ1L DQ1L DQ1L DQ1L DQ1L DQ3L

DQ1L DQ1L DQ1L

32 33 34

DQ3L

DQ1L

DIFFIO_L15p DIFFIO_L15n 35 36 37 DIFFIO_B1p 38 DIFFIO_B1n DIFFIO_B2p DIFFIO_B2n DIFFIO_B3p

40 41 42 43 44

PLL1_CLKOUTp PLL1_CLKOUTn DIFFIO_B4p DIFFIO_B4n

T2 R4 T4 N5 N6 M6

P6 U2 V2 N7 N8

DQS1B/CQ1B#, CDPCLK2

DQS1B/CQ1B#, CDPCLK2

DQS1B/CQ1B#, CDPCLK2

DQS1B/பைடு நூலகம்Q1B#, CDPCLK2

DQS1B/CQ1B#, CDPCLK2

DQS1B/CQ1B#, CDPCLK2

Bank Number B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B2 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 B3 VREFB Group VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB2N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 VREFB3N0 Pin Name / Function IO GND IO IO IO IO IO VCCIO2 IO GND IO IO IO IO IO VCCINT IO GND IO IO IO VCCA1 GNDA1 VCCD_PLL1 IO VCCINT IO GND IO IO IO VCCIO3 GND IO IO IO IO IO IO VCCINT GND IO IO VCCIO3 IO GND IO IO IO Optional Function(s) DIFFIO_L10p DIFFIO_L10n DIFFIO_L11p DIFFIO_L11n VREFB2N0 DIFFIO_L12p DIFFIO_L12n DIFFIO_L13p DIFFIO_L13n RUP1 RDN1 DIFFIO_L14p DIFFIO_L14n 54 55 56 57 58 59 60 61 P3 39 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 R3 T3 V1 M6 N6 T4 DM3B/BWS#3B DQ3B DM5B1/BWS#5B2 DQ5B R1 P2 P1 L5 M5 N4 N3 M5 R5 R4 N5 P5 P4 U1 DQS3L/CQ3L#, CDPCLK1 DQ1L DQS3L/CQ3L#, CDPCLK1 DQ1L DM1L/BWS#1L DQS3L/CQ3L#, CDPCLK1 DQS3L/CQ3L#, CDPCLK1 DM3L/BWS#3L DQS3L/CQ3L#, CDPCLK1 DM1L1/BWS#1L2 48 49 50 51 52 53 R3 DQ3L DQ1L N2 N1 K5 L4 30 31 Configuration Function E144 (4) Q240 F256/ U256 K2 K1 L2 L1 L3 F324 DQS for x8/x9 in E144 DQS for x8/x9 in Q240 DQS for x8/x9 in F256/U256 DQS for x16/x18 in F256/U256 DQS for x8/x9 in F324 DQ3L DQ1L DQS1L/CQ1L#, DPCLK1 DQ1L DQS1L/CQ1L#, DPCLK1 DQ3L DQS1L/CQ1L#, DPCLK1 DQS for x16/x18 in F324 DQ1L DQ1L DQS1L/CQ1L#, DPCLK1

Cyclone快速入门(中文版)

扫描 编号

包含标靶

扫描区域描述

A

SW1

1

S1, S2, S3, Tank room- 从左侧

S4

扫描

Cyclone Quick Start

注解

ModelSpace View 名称

SW1-A 从左边的 视图

B

SW2

1

S1, S2, S3, Tank room- 从右侧

S4

扫描

SW2-B 从右边的 视图

个点。

z 点击空格键或按 ESC 来释放选择的点云。

点的数量可通过如下操作调整:Preferences 窗口 – Edit | Preferences | ModelSpace 标签,然后选择 Viewer: Point Thickness, 和 Viewer: Point Thickness (Highlighted).

bohe@

Page 5 of 59

Copyright © 2009 Leica Geosystems HDS, Inc. All Rights Reserved

更新: 2009 年 3 月 15 日

Hale Waihona Puke Leica HDS Training Manual

Cyclone Quick Start

Leica HDS Training Manual

Cyclone Quick Start

Leica Geosystems

HDS

培 训 手 册

Cyclone 快速入门

bohe@; bin.li@

Page 1 of 59

Copyright © 2009 Leica Geosystems HDS, Inc. All Rights Reserved

教你怎么检查电路原理图

教你怎么检查电路原理图最近一直在做嵌入式系统,画原理图。

最后,为了保证原理图准确无误,检查原理图花费我近两周的时间,在此,把我在检查原理图方面的心得体会总结在此,供大家参考,说得不对的地方欢迎大家指出。

往往我们画完电路原理图后,也知道要检查检查,但从哪些地方入手检查呢?检查原理图需要注意哪些地方呢?下面听我根据我的经验一一道来。

1. 检查所有的芯片封装图引脚是否有误当然,我指的是自己画的芯片封装。

我在项目中曾经把一个芯片的2个引脚画反了,导致最后制版出来后不得不跳线,这样就很难看了。

所以,检查与原理图前一定要从芯片的封装入手,坚决把错误的封装扼杀在摇篮中!2. 使用protel的Tools->ERC电气规则检查,根据其生成的文件来排错这个指的是protel99的ERC电气规则检查,DXP应该也会有相应的菜单可以完成这样一个检查。

很有用,它可以帮你查找出很多错误,根据它生成的错误文件,对照着错误文件检查一下你的原理图,你应该会惊叹:“我这么仔细地画图,竟然还会有这么多错误啊?”3. 检测所有的网络节点net是否都连接正确(重点)一般容易出现的错误有:(1) 本来两个net是应该相连接的,却不小心标得不一致,例如我曾经把主芯片的DDR时钟脚标的是DDR_CLK,而把DDR芯片对应的时钟脚标成了DDRCLK,由于名字不一致,其实这两个脚是没有连接在一起的。

(2) 有的net只标出了一个,该net的另一端在什么地方却忘记标出。

(3) 同一个net标号有多个地方重复使用,导致它们全部连接到了一起。

4. 检测各个芯片功能引脚是否都连接正确,检测所有的芯片是否有遗漏引脚,不连接的划X芯片的功能引脚一定不要连错,例如我使用的音频处理芯片有LCLK、BCLK、MCLK三个时钟引脚,与主芯片的三个音频时钟引脚一定要一一对应,连反一个就不能工作了。

是否有遗漏引脚其实很容易排查,仔细观察各个芯片,看是否有没有遗漏没有连接出去的引脚,查查datasheet,看看该引脚什么功能,如果系统中不需要,就使用X把该引脚X掉。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。